LAWRENCE

LIVERMORE

NATIONAL

LABORATORY

LLNL-JRNL-698191

# A Survey on Software Methods to Improve the Energy Efficiency of Parallel Computing

C. Jin, B. R. de Supinski, D. Abramson, H. Poxon, L. DeRose, M. Dinh, M. Endrel, E. R. Jessup

July 20, 2016

International Journal of High Performance Computing Applications

## **Disclaimer**

---

This document was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor Lawrence Livermore National Security, LLC, nor any of their employees makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or Lawrence Livermore National Security, LLC. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or Lawrence Livermore National Security, LLC, and shall not be used for advertising or product endorsement purposes.

# **A survey on software methods to improve the energy efficiency of parallel computing**

**Chao Jin**

The University of Queensland and Monash University

**Bronis R. de Supinski**

Lawrence Livermore National Laboratory

**David Abramson**

The University of Queensland

**Heidi Poxon**

Cray Inc.

**Luiz De Rose**

Cray Inc.

**Minh Dinh**

The University of Queensland

**Mark Endrei**

The University of Queensland

**Elizabeth R Jessup**

University of Colorado Boulder

## **Abstract**

Energy consumption is one of the top challenges for achieving the next generation of supercomputing. Co-design of hardware and software is critical for improving energy efficiency for future large-scale systems. Many architectural power saving techniques have been developed, and most hardware components are approaching physical limits. Accordingly, parallel computing software, including both applications and systems, should exploit power saving hardware innovations and manage efficient energy use. In addition, new power-aware parallel computing methods are essential to decrease energy usage further. This article surveys software-based methods that aim to improve energy efficiency for parallel computing. It reviews the methods that exploit the characteristics of parallel scientific applications, including load-imbalance and mixed-precision of floating-point calculations, to improve energy efficiency. In addition, this paper summarizes widely used methods to improve power usage at different granularities, such as the whole system and per application. In particular, it describes the most important techniques to measure and to achieve energy efficient usage of various parallel computing facilities, including processors, memories, and networks. Overall, this article reviews the state-of-the-art of energy efficient methods for parallel computing to motivate researchers to achieve optimal parallel computing under a power budget constraint.

## **Keywords**

Parallel computing, high performance computing, power saving, energy efficiency, auto-tuning

## **Introduction**

Energy efficiency has become a primary concern for the design of modern computing systems, from large-scale supercomputers to multi-core laptops. In the context of high performance computing (HPC), power consumption has become a critical concern due to several factors. First, power consumption is a limiting factor that constrains processor frequency and the number of active cores. Second, high power consumption increases the total cost of ownership (TCO) of running a large-scale system, including expensive energy bills and costly cooling systems to keep temperature low. Third, the heat generated by high power consumption compromises the reliability of computing. Finally, high power consumption requires an excessive power supply that is expensive to build and to operate. The exascale supercomputer roadmap, which has identified energy efficiency as one of the top challenges, aims to achieve  $10^{18}$  floating-point operations per second with a 20 MegaWatt power budget [Kogge et al. 2008]. Although many architectural power-saving techniques have been

developed [Kaxiras and Martonosi 2008], including low frequency processors and accelerators, the power budget remains a critical challenge to exascale supercomputing [Amarasinghe et al. 2009; ASCAC 2014; Bates et al. 2013; Vaidyanathan et al. 2013]. Accordingly, parallel computing software, including system software and applications, must exploit hardware power saving advances and efficiently manage energy utilization [Dongarra et al. 2011]. In addition, new power-aware methods of parallel computing are essential to decrease energy consumption further. Consequently, understanding state-of-the-art software techniques to save energy for parallel computing is critical for researchers to propose more effective solutions to address the power challenge and to improve energy efficiency.

In this paper, we present a survey of research work that analyzes the relationship between power and performance for parallel computing and that improves the energy efficiency of parallel applications using software methods. However, a review of all research ideas proposed in the related literature is infeasible. We focus on those studies that analyze the overall system utilization and energy efficiency aspects of parallel applications, including power-aware algorithms and tools to optimize energy efficiency. This survey does not cover studies that only improve parallel computing performance although the performance improvement is likely to reduce energy usage.

Presently, hardware innovations provide a rich set of power-saving techniques that software can exploit. For example, heterogeneous systems offer the opportunity to exploit extremely high concurrency with modest energy consumption using accelerators such as GPUs (Graphic Processing Units), and coprocessors, such as the Intel Xeon Phi (also known as the MIC or Many Integrated Core architecture). Supercomputers are already equipped with these sorts of processors and the associated deep memory hierarchy. This paper reviews software methods that utilize several important hardware power-saving techniques, including DVFS (dynamic voltage and frequency scaling), NTV (near threshold voltage), low frequency processors like ARM, accelerators such as GPUs, coprocessors such as the Xeon Phi, and power-aware networks.

The energy consumption of a parallel application is closely correlated to its performance. However, improving performance and efficiently managing power may conflict with each other because faster speeds frequently come from using more resources less efficiently, which may excessively increase power consumption. In addition, the complexity of this relationship is exacerbated by the increasingly large number of CPU cores and new heterogeneous computing facilities, such as GPUs and Xeon Phi coprocessors. Therefore, this paper discusses energy and performance models to analyze parallel application energy efficiency. Most importantly, this paper presents software methods to save energy for the whole system and different applications, such as MPI [MPI Forum 2012], OpenMP [OpenMP ARB 2013], and hybrid programs. In addition, it surveys optimization techniques to tune the energy consumption of scientific applications, including auto-tuning frameworks and approximation-based methods to save energy by improving performance while maintaining the desired accuracy.

The rest of this paper is organized as follows. Section **power consumption and management** discusses the power dissipation of compute components and state-of-the-art hardware power-saving techniques for an HPC system. Section **power and energy measurement** presents the methods of measuring power and energy for parallel computing. Section **energy and performance models of parallel computing** reviews energy models for analyzing the power consumption of parallel computing and metrics to evaluate energy efficiency. Section **taxonomy of energy efficient methods for parallel computing** categorizes the most important software methods to improve energy efficiency for parallel computing. Section **saving**

**energy with power-aware resource management** presents techniques to improve the power usage for the whole system. Section **parallelism-specific methods of energy efficient parallel computing** presents power-saving techniques applied to a single application at different parallelism granularities, such as processes, threads, and hybridization. Section **communication-oriented power saving** summarizes energy efficient methods applied to the communication layer. Section **saving energy with automatic tuning** describes automatic energy tuning that improves the energy efficiency of parallel applications. Section **saving energy with approximation methods** presents approximate methods to improve the energy efficiency of parallel computing. We provide concluding remarks and future research trends in the **conclusions section**.

## Power consumption and management

This section reviews the most important hardware components and corresponding power-saving techniques that can be orchestrated by parallel software to improve energy efficiency. There are two main technical trends coupled with compute component power dissipation: power-bound and expensive data movement.

During the past decade, power constraints have transformed processor performance improvements from frequency increases to increases in the number of cores per chip. However, the future of multi-core CPUs is limited by the dark silicon phenomena [Esmaeilzadeh et al. 2011; Esmaeilzadeh et al. 2012], in which power constraints will eventually prevent the chip from using all of its cores simultaneously. In other words, even if more cores could be added on a chip, the number of inactive cores that must be powered down due to the lack of enough energy increases every process generation. To address this challenge, many different processor architectures have been developed to support extremely high concurrency with modest energy consumption, including NTV processors [Dreslinski et al. 2010; Karpuzcu 2013], ARM big.LITTLE processors [Greenhalgh 2011], GPUs, and the Intel Xeon Phi. Although which processor architecture will dominate in the future is unclear, future supercomputers will contain heterogeneous processors and a deep memory hierarchy.

The power bound affects the compute nodes of future supercomputers as well. Although future supercomputers will have more compute nodes, they potentially may not all be able to run simultaneously with peak performance due to the power limitation, which is imposed by either financial or physical reasons. *Hardware overprovisioning* [Patki et al. 2013] is also proposed for future supercomputers to fully utilize the procured power.

In addition, the computing model is gradually transforming from computationally expensive to data movement expensive [Patterson et al. 2013a]. In particular, moving a word of data, either across a node interconnection or through a deep memory hierarchy, can require orders of magnitude more time and energy than an arithmetic operation [Patterson et al. 2013a].

### *Power consumption of compute components*

The energy consumption of large-scale HPC facilities, such as supercomputers or data centers, mainly consists of two parts: powering cooling systems and running computers. The metric Power Usage Effectiveness (PUE) [Avelar et al. 2014] has been used to measure and to drive the energy efficiency of HPC facilities. PUE is defined as the ratio between the total energy of running an IT facility and the energy specifically used to power its IT equipment, as illustrated in Equation (1). By

definition, PUE is at least 1. Many recently built computing centers with advanced energy saving techniques possess a PUE close to 1 [Bates and Patterson 2013].

$$PUE = \frac{\text{Total Facility Energy}}{\text{IT Equipment Energy}} = \frac{\text{IT+Cooling+Power Distribution+Lighting+Misc}}{\text{IT Equipment Energy}} \quad (1)$$

In order to measure the HPC equipment's "inside" energy efficiency, ITUE (IT-power usage effectiveness) and TUE (total-power usage effectiveness) were proposed to highlight the ratio of entire energy used to power the compute components [Patterson et al. 2013b]. ITUE and TUE are defined as Equation (2), in which compute components include processors, memory, interconnection, and storage. ITUE mainly measures the energy overhead applied to IT equipment, such as the extra energy consumed by its internal fans, power supplies, and voltage regulators, while TUE is the total energy into the HPC facility divided by the energy used by the compute components inside the equipment. Patterson et al. [Patterson et al. 2013b] analyze the energy efficiency of the Jaguar system, which is a Cray XT5 supercomputer. The result shows that Jaguar's ITUE is 1.49 and its TUE is 1.86. According to current technological trends [Shalf et al. 2010; ASCAC 2014], the processors, memories, and interconnections of future supercomputers are the most significant energy consumption compute components. Therefore, parallel software should attempt to improve the energy efficient use of these compute components.

$$\text{ITUE} = \frac{\text{Total Energy into the IT Equipment}}{\text{Total Energy into the Compute Components}} ; \text{TUE} = \text{ITUE} \times \text{PUE} \quad (2)$$

#### *The power dissipation of CMOS components and DVFS*

The power consumption of CMOS (Complementary metal–oxide–semiconductor) circuits mainly consists of dynamic power and leakage power, denoted as Equation (3) [Kaxiras and Martonosi 2008]. Leakage power dissipation, also called static power, occurs regardless of switching activity, and is denoted as  $I_0V$  in Equation (3), where  $I_0$  is the leakage current and  $V$  is the supply voltage.

$$P_{\text{CMOS}} = I_0V + CV^2Af \quad (3)$$

Dynamic power is denoted as  $CV^2Af$  in Equation (3), where  $C$  is the load capacitance,  $V$  is the supply voltage,  $A$  is the activity factor, and  $f$  is the operating frequency. The aggregated load capacitance ( $C$ ) largely depends on the wire lengths of on-chip structures. Architectural design influences this metric in several ways. For example, smaller processor cores on-chip and independent banks of cache can reduce wire lengths. The activity factor ( $A$ ) is a fraction between 0 and 1 that refers to how often a wire actually transitions from 0 to 1 or 1 to 0. The clock frequency ( $f$ ) not only directly influences power dissipation, but also affects supply voltage ( $V$ ). Normally, a higher clock frequency is supported using a higher supply voltage. Therefore, supply voltage has a cubic impact on power dissipation through the  $V^2f$  portion of the dynamic power factor in Equation (3).

Typically, static power represents approximately 20% of overall power dissipation [Kaxiras and Martonosi 2008], while dynamic power dominates the power consumption of CMOS components. Using LULESH, a hydrodynamics application, Leon et al. [Leon et al. 2015] investigate the dynamic and static power consumption of several architectures, including IBM Blue Gene/Q, Intel Ivy Bridge, and AMD Piledriver. The dynamic power consumption for Ivy Bridge and Piledriver is 80% and 87% respectively. However, the static power consumption of Blue Gene/P, which is well known for its low power architecture, is more than 70%.

The dynamic power part of Equation (3) clearly illustrates the opportunity for saving power by adjusting voltage and frequency, also called dynamic voltage and frequency scaling (DVFS). In particular, scaling the supply voltage down offers the potential for a cubic reduction in power dissipation. However, it also linearly degrades performance. Therefore, scaling frequency down to save power using DVFS must recognize periods when lower processor performance is acceptable (e.g., in memory-bound or latency-tolerant regions of code). With OSPM (Operating System-directed configuration and Power Management) compatible operating systems, the performance of CPUs, including Intel and AMD processors, can be adjusted by controlling the performance state (P-State).

#### *Hardware-enforced power bound*

Many processor architectures support power capping to save power. For instance, IBM Power 6 and 7 architectures support “soft” power capping that runs the system at a lower power/performance point to save energy. AMD Bulldozer allows the user to specify a thermal design power limit for the processor. In contrast, the Intel Sandy Bridge processors allow a user to specify a time window and an associated maximum average power using the RAPL (Running Average Power Limit) interface [Intel 2011]. The processor guarantees that it will not exceed this average power during the time window. Rountree et al. [Rountree et al. 2012] investigate the variations of processor frequency under different power settings and analyze the potential power saving effect of applying this technique to parallel applications.

#### *Accelerators and coprocessors*

Accelerators, such as GPUs, and coprocessors, such as the Intel Xeon Phi, are currently the most power-efficient parallel computing architectures [Li et al. 2014]. Accordingly, heterogeneous systems equipped with NVIDIA or AMD GPUs or Intel Xeon Phi coprocessors offer the opportunity to exploit extremely high concurrency with modest energy consumption. Presently, hybrid machines equipped with GPUs dominate the Green500 list in 2015 [The Green 500]. According to the top 500 supercomputers announced in 2015 [Top 500], more than 20% of top 100 supercomputers, including 4 of the top 10 systems, are heterogeneous systems.

#### *Embedded processors*

Low power microprocessors that are used in smart phones and tablets, such as ARM processors, dominate the commodity market. The recently released ARMv8 Instruction Set Architecture (ISA) supports double-precision floating-point (FP-64) and SIMD instructions, which facilitate scientific computing. The cost and power advantage of these mobile processors have attracted the attention of the HPC community [Rajovic et al. 2013] and they have been adopted by data centers to process data-intensive applications [Li et al. 2011b]. The European Mont-Blanc project [Rajovic et al. 2013] seeks to build an energy-efficient supercomputer using ARM processors and GPU accelerators.

#### *Near-threshold Voltage (NTV) Computing*

ASIC (Application Specific Integrated Circuit) process scaling allows more transistors to be included on a chip. However, cooling limitations do not expand accordingly. As a result, although more cores can be added to a chip in the future, heat dissipation considerations may lead to some of them being inactive at any given time

[Esmaeilzadeh et al. 2012]. In addition, the gap between what can be integrated onto a chip and what can be operated keeps increasing every process generation.

A promising way to activate more cores is to reduce the supply voltage ( $V_{DD}$ ). Lowering the supply voltage to slightly above the threshold voltage ( $V_{th}$ ) can reduce power consumption by more than an order of magnitude. This unconventional operation regime, called near-threshold voltage computing (NTC), enables more cores to operate simultaneously under a given power budget at the cost of performance degradation [Dreslinski et al. 2010]. Moreover, NTC decreases the reliability of the system [Karpuzcu et al. 2013].

However, the increased parallelism of large-scale systems can compensate for the degraded performance of NTC. While the increase in computing errors must be tolerated, NTC is a promising way to reduce the power consumption of parallel computing. Recently, based on NTC, approximate computing, also called significance-based computing, has attracted attention in the HPC research community [Gschwandtner et al. 2014; ASCAC 2014].

### Memory

Heterogeneous architectures enable more parallelism, which demands more data movement between the logic and the cores. Moreover, the performance gap between moving a word and applying an arithmetic operation to it will grow exponentially according to current technological trends [Patterson et al. 2013a]. Accordingly, data movement will account for most of the energy consumption of parallel computations. In particular, the energy to move data increases proportionally to bandwidth and transport distance ( $energy = bitrate \times distance^2 / cross-section\ area\ of\ interconnect\ wiring$  [Miller and Ozaktas 1997]). Although moving a word of data across a node interconnect consumes more energy than through a deep memory hierarchy, accessing data from memory is more frequent. Actually, even with advanced memory techniques, the amount of energy consumed by the main memory subsystem could be comparable to that of the processors [Shalf et al. 2010]. To decrease the energy consumed by memory in the software layer, applications must increase data locality to avoid unnecessary data movement.

### Network

At exascale, the network can consume 10~20% of the total system power [Groves and Grant 2015]. Some experts even estimate that in the future the network may account for 30% of the total power budget of a supercomputer [Dickov et al. 2014]. In order to improve the energy efficiency of the interconnection network, many innovative technologies have been developed, including on-die interconnect fabric, inter-chip network integration, energy proportional network, and power-aware network [Alonso et al. 2006; Nedevschi et al. 2008; Saravanan et al. 2013; Saravanan et al. 2014; Groves and Grant 2015; Miwa et al. 2014; Miwa and Nakamura 2015]. Power-aware networks can save power consumed by the network fabric using techniques such as dynamic link width and frequency, and on/off links. Many experts estimate that power-aware networks will save significant energy for HPC applications [Miwa et al. 2014; Saravanan et al. 2013; Saravanan et al. 2014]. In particular, Energy Efficient Ethernet (EEE) [IEEE 802.3az. 2010] has attracted attention in the HPC community. Although these innovations can decrease energy consumed at the network layer, moving a word of data across a node interconnection can require orders of magnitude more time and energy than an arithmetic operation [Patterson et al. 2013a]. In the application layer, one of the best ways to save network energy consumption is to avoid or to reduce communication [Grigori et al. 2011; Demmel et al. 2013].

## Power and energy measurement

Accurate power and energy measurements are critical for the efficient management of parallel application energy use. In particular, fine-grained measurement of power consumption, such as per application, per hardware or software component, or even per instruction, and high sampling frequency are required to provide insights for energy usage optimization. The existing power measurement methods mainly consist of two groups: direct measurement, and model-based. Several projects [Intel 2011; David et al. 2010; Hart et al. 2014; Ge et al. 2009; Venkatesh et al. 2013; Yoshii et al. 2012] have explored APIs that make fine-grained power and energy consumption measurement for various granularities accessible at the application level so that programs can automatically make software engineering decisions to manage their power usage at runtime. Most direct power measurements use on-board sensors or external instruments [Feng et al. 2005; Ge et al. 2009; Laros et al. 2013]. The measurement granularity of these techniques is commonly too large to measure the energy consumed by instructions or basic computing functions. Model based methods, such as RAPL [Intel 2011, David et al. 2010], provide a viable alternative to physical measurements. Some methods, such as ALEA [Mukhanov et al. 2015], refine measurement granularities by improving direct power measurement with probabilistic models.

### *Power measurement of the whole system*

Feng et al. [Feng et al. 2005; Ge et al. 2009] created PowerPack, a software tool that automatically profiles the power consumption of scientific applications running on high-performance distributed systems. PowerPack can measure the power consumption of the major computing components, including CPU, memory, disk, and NIC (Network Interface Controller), on a cluster's computing nodes. In particular, a group of 0.1 Ohm sensor resistors are connected to the node using ATX extension cables. Each of ten digital meters per node collects four samples per second. Using RS232 ports, a data collection computer logs the power samples, which are subsequently analyzed using PowerPack. PowerInsight [Laros et al. 2013] is a similar project to measure power at the component level for a cluster by instrumenting hardware.

Power monitoring capabilities are available on IBM Blue Gene/P and Blue Gene/Q (BG/Q) systems [Yoshii et al. 2012; Hennecke et al. 2012]. Blue Gene systems have several sensors that monitor the voltage and current of service cards, node boards, bulk power modules, and cooling system boards. The sensor data are collected every 5 minutes and stored in a database. The power consumption of FPU (Floating-point Unit) and memory copy activity can be profiled using Environmental Monitoring (EMON) APIs on BG/Q.

The Cray Power Management Database tool [Hart et al. 2014] is available on Cray XC systems, which supports two ways to access power measurements: the Power Measurement Data Base (PMDB) and power management counters (pm\_counters). The database contains comprehensive power readings at a 1 Hz frequency for each node, GPU, blower and network chip, which can be queried per job and per component and which support easy derivation of per job power and energy consumption. In contrast, pm\_counters are provided as Sysfs files on Linux for power, accumulated energy, and power\_cap of both the CPUs and GPUs. The register files for the pm\_counters are updated at a frequency of 10 Hz.

IPMI (Intelligent Platform Management Interface) [Intel 2013] defines a set of low-level interfaces for remotely managing and monitoring the status of computer systems, including power consumption of different components. IPMI is supported in most Intel architectures, and many open source software libraries are available to collect IPMI sensor data. Hackenberg et al. [Hackenberg et al. 2013] find that the power samples collected using IPMI are accurate enough, but its estimation of energy consumption needs improvement for short period jobs.

In order to characterize HPC architectural trends for power consumption, several HPC benchmarks, such as the Top500, the Green500 and the Graph500, accept power metrics for running HPC workloads. The Energy Efficient HPC Working Group (EE HPC WG) conducted a survey on the power consumption listed for supercomputers on the Top500 and the Green500 in 2011. They find that the quality of power measurement varies widely. A three-level power measurement methodology is proposed [Scogland et al. 2014]. Among the proposed three levels, level 3 is the most rigorous measurement and is able to identify energy “hot spots” accurately and precisely. It requires continuous energy measurement of the whole system and each participating sub-system.

#### *CPU power measurement*

The Intel Sandy Bridge family of processors is equipped with onboard power meters. RAPL (Running Average Power Limit), a platform-specific power management interface [Intel 2011, David et al. 2010], is provided to allow users to measure energy consumption of processor, DRAM, and uncore devices in a non-intrusive manner. Users are allowed to measure and to control processor power usage using *model-specific registers* (MSRs). On Linux the *msr* kernel module supports reading and writing any MSR on the node using a file interface at `/dev/cpu/N/msr`. The precision of the power and energy measurements is architecture-specific and is provided by reading the `MSR_RAPL_POWER_UNIT` register. One limitation of RAPL is MSRs are 64-bit wide and are updated every millisecond. Typically, the power values wrap-around every 60 seconds. Venkatesh et al. [Venkatesh et al. 2013] addressed this limitation by extending RAPL and applied the extension to measure energy consumption for MPI operations.

#### *Fine-granularity power measurement*

ALEA (Abstract-Level Energy Accounting) [Mukhanov et al. 2015] uses a probabilistic approach to provide fine-grained energy profiling for basic computing blocks in order to overcome the coarse granularity of sampling period of direct power measurement. In particular, ALEA combines the sampling of physical power measurements and a probabilistic model to estimate the energy consumed by basic blocks at any granularity. ALEA assumes that basic blocks execute repeatedly during a program’s execution. It samples the program’s execution at a predefined rate and then extracts the basic block sampled each time. The latency of each basic block is varied at each iteration, which allows ALEA to build a probabilistic model to estimate the execution time and energy consumption for each block. Evaluated using both sequential and parallel benchmarks, the mean error rates of ALEA are between 1.4% and 3.5%, while the sampling overhead is around 1%.

## **Energy and performance models of parallel computing**

Improving energy efficiency for parallel computing requires pursuing optimal performance with moderate power usage. In the parallel computing domain, optimizing performance and energy consumption may conflict. The simple rule that

*Energy = Power × Time*, suggests two general ways to save energy: 1) faster speed, given a constant power; and 2) lower power without increasing run time. Given an ideal embarrassingly parallel application, running it on  $n$  cores at frequency  $2f$  requires the same execution time as running it on  $2n$  cores at frequency  $f$ . However, the latter option consumes less than half of the CPU energy. Unlike this simple example, most parallel applications' execution time and power and energy consumption are interdependent, which complicates the relationship. In particular, interactions between memory, communication, parallelism, and processor frequency affect execution time and energy consumption. Additionally, the characteristics of a parallel application, such as its parallelism portion and its bottlenecks (i.e., either compute-bound or memory-bound), impact its optimal execution time and minimal energy consumption. Generally, increasing the amount of computational resources lowers system utilization and decreases energy efficiency because extra energy is wasted as the number of nodes or CPUs per node increases. Several power models [Bingham and Greenstreet 2008; Woo and Lee 2008; Cho and Melhem 2010; Song et al. 2011; Choi et al. 2013] are proposed to analyze the relationship between power, energy, performance, and parallelism for parallel applications. Most of these power models are extensions of previous performance models, such as Amdahl's Law, iso-efficiency, and the Roofline model. These models focus on providing insights to optimize algorithms or to detect an appropriate system configuration to improve energy efficiency by changing several adjustable parameters, such as processor frequency, parallelism level, and the parallelism portion. Accordingly, various metrics [Weiser et al. 1994; Ge et al. 2005; Bingham and Greenstreet 2008] are proposed to evaluate energy efficiency.

#### *Energy efficiency metrics*

Several energy-performance efficiency metrics have been proposed to determine the effect of improving energy efficiency. Weiser et al. [Weiser et al. 1994] propose to use millions-of-instructions-per-joule (MIPJ) to measure CPU energy performance, specifically  $MIPJ = MIPS/W$  (millions of instructions per second/watt). Because reducing clock speed causes a linear decrease in performance, but a cubic reduction in energy consumption, lowering frequency generates a better MIPJ. The flops/watt (F/W) metric is successfully used as the de facto standard in measuring the energy efficiency of a computing system [The Green 500]. EDP (Energy-delay product), i.e.,  $et$  and ED2P (Energy-delay-squared product), i.e.,  $et^2$ , have been widely used to represent the energy-time tradeoff of applying DVFS to parallel applications. In comparison to EDP, ED2P focuses more on the performance effect. Ge et al. [Ge et al. 2005] use ED3P to select the optimal operating point when investigating an appropriate granularity of applying DVFS. Bingham and Greenstreet [Bingham and Greenstreet 2008] propose using  $et^\alpha$ , a generic energy complexity metric, to analyze the lower bound of execution time constrained by an energy budget for a number of basic algorithms, including sort, binary addition, and binary multiplication.

#### *Amdahl's law-based energy models*

Woo and Lee [Woo and Lee 2008] extend Amdahl's Law to analyze the energy efficiency of multicore processors. In particular, a new variable,  $k$ , is added to represent the fraction of power that the processor consumes in the idle state. Equation (4) illustrates energy efficiency in terms of *performance per watt* and *performance per joule* on  $n$  processors/cores, where  $s+p=1$ ,  $s$  and  $p$  are the sequential and parallel portion of the application respectively. The extended power model was

applied to investigate the energy efficiency of both symmetric and asymmetric multicore architectures, and they find that an asymmetric multicore architecture, i.e., a heterogeneous architecture, is more energy efficient.

$$\frac{Perf}{W} = 1/(1 + (n - 1) * k * s), \quad \frac{Perf}{J} = \frac{1}{s + \frac{p}{n}} \times \frac{1}{1 + (n - 1) \times k \times s} \quad (4)$$

Ge and Cameron [Ge and Cameron 2007a] propose a power-aware speedup model by extending Amdahls' Law to account for the effects of parallelism and power-aware techniques on speedup. The model decomposes the workload into on/off-chip characteristics and assumes a constant frequency for the off-chip workload. The model can predict the optimal EDP configuration for a given parallel application.

Similarly motivated by Amdahl's law, Cho and Melhem [Cho and Melhem 2010] propose a theoretical model to analyze the relationship between parallelism, performance, and energy consumption based on the portion of an application that executes in parallel. They analyze how parallelization improves energy consumption. The improvement of dynamic energy for running an application on  $n$  processors is illustrated as Equation (5), where the dynamic power consumption of a processor running at frequency  $f$  is proportional to  $f^\alpha$ .

$$Dynamic\ Energy\ Improvement = 1/(s + \frac{p}{n^{\alpha-1}/\alpha})^\alpha \quad (5)$$

Two machine models are examined using the proposed model:  $M_A$ , with which individual processors cannot be turned off; and  $M_B$ , with which individual processors can be turned off. For  $M_A$ , an optimal number of processors exists to minimize energy consumption. Depending on the size of sequential portion,  $s$ , and the portion of dynamic energy, adding more processors initially decreases energy consumption, while energy consumption increases after  $n$  is larger than a threshold. In contrast, the optimal configuration for  $M_B$  either does not exist, or its effect is much less than that for  $M_A$ . However, this model ignores the energy consumed to move data across processors.

#### Other energy models

Korthikanti and Agha [Korthikanti and Agha 2010] propose the use of a linear cost function,  $\alpha \times E + T$ , to evaluate the energy-time tradeoff for parallel algorithms while varying the number of cores and their frequencies. In particular, the proposed model accounts for several parameters of a parallel application, including its workload, concurrency degree, and communication cost. The energy-time tradeoff of quick sort, FU factorization, and minimum spanning tree algorithms are investigated.

Song et al. [Song et al. 2011] propose an iso-energy-efficiency model to analyze the power-performance tradeoffs of parallel applications by extending the concept of performance iso-efficiency. In particular, an *energy efficiency factor (EEF)* is defined as Equation (6), in which  $E_s$  is the total energy consumed by a sequential application,  $E_p$  is the energy consumed by its parallel execution on  $p$  processors,  $E_0 = E_p - E_s$ . Overall, a large *EEF* stands for low iso-energy-efficiency, and vice versa. This model can predict the total energy consumption of large-scale parallel applications while varying the parallelism degree and processor frequency.

$$Energy\ Efficiency\ Factor\ (EEF) = \frac{E_0}{E_s}; \quad Iso-energy-efficiency\ (EE) = \frac{E_s}{E_p} = \frac{1}{1+EEF} \quad (6)$$

Choi et al. [Choi et al. 2013] propose an energy roofline model to analyze the time, energy, and power costs for an algorithm from the *energy-balance* point of view. As an analogue to the time-balance proposed in the original performance Roofline model,

energy-balance measures the ratio of flops and bytes per unit-energy, i.e., Joule. The model identifies the relationship between *computational intensity*, i.e., flops per memory operation, and consumed energy. As a counterpart of the time-balance,  $B_T$ , in the performance Roofline model, the energy-balance,  $B_E$ , is detected using the energy Roofline model. Real world applications always have  $B_T > B_E$ . This implies that race-to-halt strategies are the first-order technology to achieve energy efficiency. With race-to-halt, the system runs at top speed to create long idle intervals, in which certain parts of hardware can be turned off to save energy.

#### *Performance prediction for energy analysis*

Adjusting CPU frequency to save energy depends on the accurate estimation of performance degradation. A small prediction error can fail to reduce energy consumption and cause extra power usage [Rountree et al. 2011]. Rountree et al. and Keramidas et al. [Rountree et al. 2011; Keramidas et al. 2010] proposed the use of a new performance counter, *Leading Loads*, to improve the accuracy of performance estimation under DVFS. In particular, a *load* is defined as a non-speculative read that results in a last-level cache miss and the first load is a *leading load*. Assume the performance at frequency  $f$  is observed and after adjusting frequency from  $f$  to  $f'$ , the degraded performance can be estimated using Equations (7)~(9), in which *execution time* consists of *CPU time* and *bus time*. With the Leading Load model, the estimation error is limited to within 0.3%.

$$\text{Predicted Execution Time at } f' = \text{Observed Bus Time} + (f'/f) \times \text{Observed CPU Time} \quad (7)$$

$$\text{Observed Bus Time at } f = \frac{\text{LeadingLoadCycles at } f}{f} \quad (8)$$

$$\text{Observed CPU Time at } f = \text{Observed Execution Time at } f - \text{Observed Bus Time at } f \quad (9)$$

#### *Insights of energy models*

Using the above theoretical models, the following general conclusions are achieved. First, the energy efficiency of parallel computing is both application and platform dependent. Second, energy consumption and performance are strongly correlated. Third, for parallel applications, adjusting processor frequency has less impact on energy efficiency than changing parallelism.

Experiments that evaluate the energy-time trade-off in parallel applications confirm these theory-detected relationships [Freeh et al. 2007b; Minartz et al. 2011; Rahman et al. 2012; Laros et al. 2013; Leon et al. 2015]. Rahman et al. [Rahman et al. 2012] study the potential power-saving effect of applying compiler optimization technologies, including loop and thread affinity optimizations, to multi-threaded applications. They demonstrate that the power-saving space for a multi-threaded application can be up to 28%. Leon et al. [Leon et al. 2015] analyze the effectiveness of code optimizations on the power and energy use of a hydrodynamics application, called LULESH. Several techniques of reducing data movement are investigated, including the loop fusion, data structure transformation, and global allocation optimizations. These optimizations are evaluated for IBM Blue Gene/Q, and for x86 server-class and consumer-class architectures. They find that the effect of same optimization methods depends on architectures. In addition, different code regions of LULESH demand different optimization techniques. However, finding a globally

optimal solution by applying different optimization techniques to different regions is challenging.

Freeh et al. [Freeh et al. 2007b] investigate the relationship between energy consumption and performance for the NPB Parallel Benchmarks on a power-scalable cluster with a variety of frequencies and a different number of processors. Given a number of processors, they detect an optimal configuration of processor frequency to minimize energy consumption. They find that energy savings depend on an application's speedup. For the case of good speedup, running the application at a higher frequency on more nodes can save energy. In contrast, for the case of poor speedup, increasing node count and processor frequency may not save much energy. Laros et al. [Laros et al. 2012; Laros et al. 2013] investigate the potential effect of power saving on the Cray XT architecture using processor frequency scaling and network bandwidth scaling. In particular, running a series of empirical experiments demonstrate up to 39% energy savings with little or no negative impact on performance. Minartz et al. [Minartz et al. 2011] investigated the power-saving opportunities of applying DVFS to AMD and Intel clusters for parallel computing. They find 4~8% overall system energy saving with slight increases in execution time. All of the above theoretical analyses and empirical experiments form a foundation to drive a large number of software techniques to improve the energy efficiency of parallel computing.

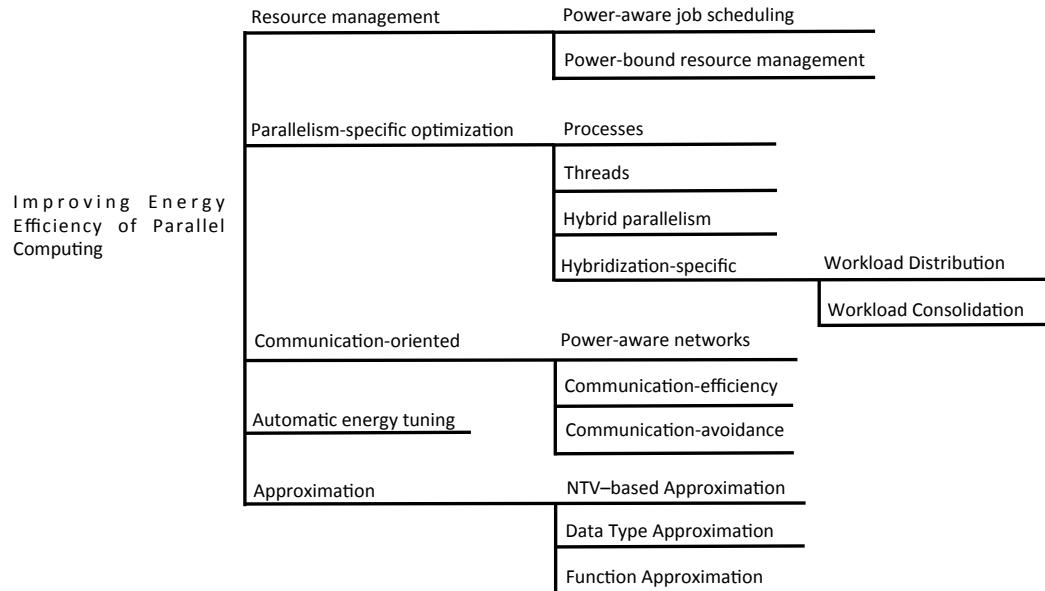

**Figure 1.** Taxonomy of software methods to improve the energy efficiency of parallel computing.

## Taxonomy of energy efficient methods for parallel computing

In order to improve energy efficiency, supercomputers need to take both instantaneous power usage and total energy consumption into account. Power saving can be achieved at different granularities, such as per job, per node and the whole system. Software stacks should utilize various hardware power-saving techniques efficiently by taking advantage of application characteristics. We classify the methods to improve the energy efficiency of parallel computing in the software layer into the following categories, as illustrated in Figure 1.

- 1) Resource management: typically, an HPC system is shared by a number of users and it frequently executes multiple jobs simultaneously. The first category consists of methods exploiting energy saving opportunities at the whole system level using a job scheduler or resource management system. By monitoring the energy consumed by a HPC system and the performance achieved by each application, the resource management system can take appropriate actions to save power or to improve energy efficiency according to job specifications [Georgiou et al. 2014; Martin et al. 2015; Pedretti et al. 2015]. In addition, mapping a number of waiting jobs to available nodes should consider the energy characteristics of each application and the power capability of the physical resources [Elnozahy et al. 2003; Lawson and Smirni 2005; Zhou et al. 2014; Mämmelä et al. 2010; Marathe et al. 2015]. As the performance provided by a supercomputer is becoming power-constrained, hardware overprovisioning has attracted significant attention in the HPC community [Etinski et al. 2010; Etinski et al. 2012; Patki et al. 2013; Patki et al. 2015; Sarood et al. 2013; Sarood et al. 2014; Ellsworth et al. 2015].

- 2) Parallelism-specific optimization: the second category consists of methods exploiting energy saving opportunities enabled at different levels of parallelism, such as processes, threads, and hybridization. Load imbalances between processes and threads generate significant opportunities to decrease energy consumption. DVFS has been applied to improve the energy efficiency of MPI programs by lowering the frequency of processors with light load [Ge et al. 2005; Hsu and Feng 2005; Hsu and Kremer 2003a; Kappiah et al. 2005; Freeh et al. 2005a; Freeh et al. 2005b; Li et al. 2010a; Rountree et al. 2007; Rountree et al. 2009; Rountree et al. 2011]. Dynamic Concurrency Throttling (DCT) is proposed to control the number of active CPU cores for multi-threaded programs, including OpenMP programs, at runtime [Curtis-Maury et al. 2006a; Curtis-Maury et al. 2006b; Curtis-Maury et al. 2007; Freeh et al. 2007a; Grant and Afsahi 2006; Li and Martinez 2006; Li et al. 2010b; Suleman et al. 2008]. The balance between performance and energy consumption is also investigated for hybrid MPI/OpenMP applications [Li et al. 2010b; Bailey et al. 2015]. Further, innovative hardware components, such as accelerators, FPGAs, and coprocessors, that provide vector level parallelism, frequently support improved energy efficiency compared to multicore CPUs [Enos et al. 2010; Wang and Ren 2010; Ghosh et al. 2012; Ma et al. 2012; Huang et al. 2009; Li et al. 2011; Collange et al. 2009; Suda and Ren 2009; Li et al. 2014; Luk et al. 2009; Fowers et al. 2013]. Some of these methods depend on energy improvement of compiler techniques [Hsu and Kremer 2003b; Saputra et al. 2002; Keramidas et al. 2010; Leon et al. 2015].

- 3) Improving communication energy efficiency consists of three groups of methods: a) saving power for network fabric using power-aware networks [Conner et al. 2007; Alonso et al. 2006; Nedevschi et al. 2008; Saravanan et al. 2013; Saravanan et al. 2014; Groves and Grant 2015; Miwa et al. 2014; Miwa and Nakamura 2015]; b) improving communication energy efficiency using energy-aware data transfer algorithms [Lim et al. 2006; Kandalla et al. 2010; Venkatesh et al. 2015; Alan et al. 2015]; and c) decreasing network traffic using communication-avoiding algorithms [Demmel et al. 2013; Grigori et al. 2011].

- 4) Automatic tuning: this category treats a parallel application as a black box and improves its energy efficiency by tuning several energy and performance parameters [Balaprakash et al. 2013; Gschwandtner et al. 2014b; Jordan et al. 2012; Miceli et al. 2012; Rahman et al. 2011; Tiwari et al. 2012].

5) Approximation: the last category is to improve energy efficiency using approximation, such as mixed floating-point precision [Anzt et al. 2010; Dongarra et al. 2012; Lam et al. 2013; Linderman et al. 2010; Rubio-González et al. 2013; Schkufza et al. 2014], significance-based computing using NTV [Dreslinski et al. 2010; Gschwandtner et al. 2014a], and providing approximated computing results for applications that can tolerate inaccurate computation [Baek and Chilimbi 2010; Sampson et al. 2011; Hoffmann et al. 2009; Hoffmann et al. 2011].

## Saving energy with power-aware resource management

The resource and job management system, which is also called the job scheduler, distributes waiting jobs to available compute nodes. Traditionally, it only considers improving job performance and maximizing overall system utilization. Because the job scheduler has a global view of the system, including compute resources, running jobs' termination times and waiting jobs' performance requirements, it is the best candidate for monitoring and controlling the energy consumed by parallel applications. To achieve this target, traditional job schedulers must be improved to track energy usage in real time and to predict power requirements. With these two enhancements, the job scheduler can allocate both compute nodes and power to waiting jobs by treating power and energy consumption as job characteristics. Initially, many power-aware job schedulers [Elnozahy et al. 2003; Lawson and Smirni 2005; Zhou et al. 2014; Mämmelä et al. 2010; Marathe et al. 2015] focus on optimizing overall energy usage. Recently, investigating the impact of a power bound imposed on future supercomputers has attracted more attention [Etinski et al. 2010; Etinski et al. 2012; Patki et al. 2013; Patki et al. 2015; Sarood et al. 2013; Sarood et al. 2014; Ellsworth et al. 2015]. The node variability of power consumption in supercomputers and its impact on job scheduling are also investigated recently [Inadomi et al. 2015; Scogland et al. 2015].

### *Power-aware job scheduling*

Compute nodes consume significant energy even when idle. For example, an idle Blue Gene/P rack consumes around 13kW [Zhou et al. 2014]. Turning off idle nodes during low system utilization is a straightforward way to save power. In addition, adjusting CPU frequencies on targeted compute nodes can also save significant energy [Etinski et al. 2010; Etinski et al. 2012; Mämmelä et al. 2010].

SLURM (Simple Linux Utility for Resource Management)'s existing resource utilization collection module is extended to track energy consumption using both RAPL and IPMI and to support energy accounting and control [Georgiou et al. 2014]. With these extensions, SLURM can profile power usage for each job and programmers can control the CPU frequency. Aiming to be deployed on large-scale systems, the overhead of energy monitoring in SLURM is optimized to be lower than 0.6% in energy consumption and less than 0.2% in execution time with less than 2% error rate in most cases.

Cray Advanced Platform Monitoring and Control (CAPMC) [Martin et al. 2015] supports monitoring and controlling of power consumption on Cray XC systems. It reports energy usage both per compute node and per job. In addition, CAPMC supports both CLI and HTTP APIs to allow users to collect energy reports and to control power usage per job. It also supports node-level power capping that enables external software to establish a maximum or a minimum bound on the amount of power consumed by the system or a selected subset of the system [Pedretti et al. 2015]. In addition, external software can modify CPU frequencies and sleep states

dynamically, which allows a job scheduler to reallocate power among nodes and to limit the system power consumption within a predefined range.

A power-aware job scheduler designed for IBM Blue Gene/P [Zhou et al. 2014] can reduce energy costs by allocating resources according to variable electricity prices and application power profiles. In particular, this job scheduler prefers allocating jobs demanding high power consumption during the off-peak electricity price period using a 0-1 knapsack model. With the online scheduling algorithm, a number of jobs within the scheduling window are allocated to available resources. The scheduling objective is to maximize system utilization without exceeding the predefined power budget and to make a trade-off between performance and fairness simultaneously. Simulation of the proposed scheduler using both synthetic and real job traces show reductions of energy costs can be up to 25% with slightly lower system utilization.

Different scheduling policies are investigated for power-aware job schedulers [Elnozahy et al. 2003; Lawson and Smirni 2005; Zhou et al. 2014; Etinski et al. 2010; Etinski et al. 2012; Mämmelä et al. 2010; Marathe et al. 2015]. Most of them extend the EASY (Extensible Argonne Scheduling system) backfilling policy and work in an online mode. In particular, the dynamic policies of turning on/off compute nodes according to workload fluctuation were studied [Elnozahy et al. 2003; Lawson and Smirni 2005]. An accurate workload prediction model is the key to the efficiency of these algorithms. In many cases, lowering CPU frequency using DVFS for each compute node based on jobs' power characteristics can allow more jobs to run simultaneously, which can save power and decrease average job waiting time [Etinski et al. 2010; Etinski et al. 2012; Mämmelä et al. 2010]. Elnozahy et al. [Elnozahy et al. 2003] investigate how to adjust CPU frequencies and dynamically turn compute nodes on or off simultaneously. Most of these scheduling algorithms rely on an accurate power and energy prediction model for applications. Conductor [Marathe et al. 2015] is a run-time system that intelligently allocates power, nodes, and cores to applications. Using DVFS and dynamically changing the number of threads, Conductor outperforms other power-constrained schedulers that adopt static power capping per node by up to 30%. Etinski et al. [Etinski et al. 2010; Etinski et al. 2012] investigate how to efficiently utilize the overall system resource given a power budget. The above power-aware schedulers are designed to optimize overall energy efficiency and to maximize system throughput, but do not consider the global power bound imposed on future supercomputers.

#### *Power-bound resource management*

The power that can be supplied to a supercomputer will reach a physical bound in the future. In addition, the energy cost of operating supercomputers may also be restricted. Some experts estimate each MW-year costs \$1M. Therefore, although future supercomputers will have more compute nodes, they potentially may not all be able to run simultaneously with peak performance. Similarly, the number of active cores on each chip may be restricted (i.e., "dark silicon").

Presently, most supercomputers are designed with *worst-case provisioning*, in which the maximum power draw per node decides the total power allocated to a computer and is designed to make all nodes run at peak power simultaneously. However, many studies show that most supercomputers are under-utilized in terms of power consumption. For example, *Vulcan*, a Blue Gene/Q at LLNL (Lawrence Livermore National Laboratory) consumes only 60% of allocated power on average over a 16-month period [Sarood et al. 2013]. Further, raising power allocated to CPU and memory does not generate a proportional increase in application performance

[Patki et al. 2013; Sarood et al. 2013]. In addition, most scientific applications do not fully utilize the maximum power allocated to each compute node [Sarood et al. 2013; Patki et al. 2015]. In order to utilize the allocated power more efficiently, *hardware overprovisioning* is proposed, initially by Patki et al. [Patki et al. 2013]. By overprovisioning, a supercomputer consists of compute capacity that is more than can be fully powered under the power constraint, but not all system components can run simultaneously at peak power. Instead, the system must be reconfigured dynamically according to the workload's power requirements and characteristics such as scalability and memory intensity. Patki et al. [Patki et al. 2013] show that overprovisioning can be leveraged to improve overall system throughput and to decrease average turnaround time. In particular, overprovisioning outperforms worst-case provisioning by up to 50%.

Sarood et al. [Sarood et al. 2014] proposed an online scheduler for an overprovisioned supercomputer that can constrain the power consumption of each node using RAPL and optimally allocate power and nodes to queued jobs. The goal is to maximize the job throughput for a supercomputer given a power budget. Each time a new job request arrives or currently running jobs terminate, the scheduler re-allocates resources to both running jobs and selected waiting jobs. Mapping nodes and power to jobs is formulated as a resource optimization problem that is solved using an Integer Linear Program (ILP). The scheduling scheme assumes each parallel job is malleable such that the job can shrink or expand across a different number of nodes or CPU cores at runtime. The scheduler also relies on a prediction model to estimate the power and performance characteristics for each job at different scales. The online scheduling uses the performance and power characteristics of each job to make resource allocation decisions that can change the resources allocated to a running job. Using simulation, job throughput is improved up to 5.2X in comparison to power-unaware SLURM. With real experiments on a small-scale cluster, 1.7X improvement of job throughput is obtained.

Patki et al. [Patki et al. 2015] propose a practical and low-overhead resource manager for power-constrained clusters, called RMAP (Resource MAnager for Power). With overprovisioning, RMAP supports power-aware backfilling. It aims to provide faster job turnaround times with increased overall system resource utilization. RMAP predicts the performance and power consumption for each application according to its profiling. Using the estimated power and performance for each application on different configurations, RMAP can allocate idle power to appropriate waiting jobs. But it does not change the configuration of running jobs. Simulation is performed to compare RMAP with traditional scheduling policy by investigating real world scientific applications, and the results show RMAP's new policy increases system power utilization with 18.5% faster average turnaround time.

Ellsworth et al. [Ellsworth et al. 2015] propose a power scheduler (POWsched) to enforce a system-wide power limit. POWshed maintains a system-wide power bound, and implements a dynamic policy to allocate wasted power to more power-intensive applications. POWshed does not predict the power consumption and performance for each application. Instead, it assumes the power consumption of each application is consistent during a short time period. At each round of scheduling, POWshed monitors the power consumption of each application in real time, and detects surplus power allocated to each node. When power is abundant, the surplus power is reallocated to power-scarce nodes. Otherwise, a fair allocation of power across nodes is achieved. The dynamic scheduling policy adjusts power capped for each application and guarantees each node is allocated with enough power to avoid significant performance degradation. Simulation demonstrates that POWshed can decrease overall workload execution time by around 14%.

## Parallelism-specific methods of energy efficient parallel computing

The parallelism-specific software methods of improving energy efficiency of parallel computing consist of four groups. The first group applies to process-level parallelism, which exploits imbalanced load distributions. An imbalanced workload across machines or CPU cores causes inefficient resource utilization. In addition, an application frequently consists of memory bound or I/O bound phases during the computation, in which lowering CPU frequency can save power with little or no performance degradation. The second group works at thread-level parallelism to improve the multi-threaded program's energy efficiency by controlling the number of active threads. The third group handles hybrid MPI and OpenMP applications by combining the technologies used to save power for MPI programs and for multi-threaded applications. The last group is for hybridization that exploits an energy efficient hybrid-computing component.

### *DVFS-based power-saving methods for MPI applications*

DVFS has been recognized as one of the most effective ways to reduce processor power dissipation. It has been applied to parallel computing, including MPI applications, to adjust the tradeoff between energy savings and performance dynamically. It works particularly well for applications with load imbalances, including load imbalances between compute nodes and between CPU, memory, and I/O, at a cost of negligible performance degradation.

DVFS can be applied at different levels, such as a whole program or a function call. Using the Wattch CPU energy and performance simulator [Brooks 2000], Hsu and Kremer [Hsu and Kremer 2003a] investigate the opportunity of applying DVFS to save energy for highly optimized scientific codes by taking advantage of memory stalls. In particular, using five SPECfp95 benchmark applications, they demonstrate that energy consumption can be reduced up to 60% with a performance penalty of 9.58% or less. Freeh et al. [Freeh et al. 2005b] investigated the opportunity to save energy for MPI programs in power scalable clusters by reducing processor frequency. However, the power saving depends on application characteristics, including the ratio of computation-to-communication and memory stalls. In the case of perfect speedup, both energy consumption and execution time can be saved using more nodes at a lower CPU frequency. Ge et al. [Ge et al. 2005] investigate the appropriate granularity of applying DVFS to HPC applications on power-aware clusters. They find applying DVFS to a whole program saves less overall energy than applying it to finer levels, because power saved during idle periods is offset by increased execution time of non-idle periods. In addition, they separate the FT application of the NPB Parallel Benchmarks to different regions using communication-to-computation ratio and apply DVFS to each region. This method can decrease up to 36% energy consumption without noticeable performance loss.

*Detection of finer granularities.* To apply DVFS to parallel applications at finer granularities, it needs to detect regions in the application with different degrees of idleness or load imbalances. Typically, a parallel application is split into a series of phases and a different CPU frequency is used for each phase. Identifying the idle and non-idle periods of a parallel application is typically based on the iterative nature of most scientific computation. Most methods that identify the idle periods of a parallel application are either profile-directed [Hsu and Feng 2005; Freeh et al. 2005a;] or trace-driven [Rountree et al. 2007]. The boundaries between different phases are determined using communication APIs, computing patterns, and memory access

patterns. The methods of applying DVFS to a parallel application consist of external methods and internal methods. The external methods monitor the execution of a parallel application to predict its behavior and accordingly adjust the CPU frequency of each machine [Hsu and Feng 2005; Lim et al. 2006]. In contrast, the internal methods allow parallel applications to adjust CPU frequency directly, which are typically achieved using instrumentation [Freeh et al. 2005a; Kappiah et al. 2005]. Finally, it is an NP-complete problem to apply appropriate CPU frequencies to different regions optimally. Frequently, it can be estimated using optimization algorithms, such as linear programming [Rountree et al. 2007] and heuristic-based searching algorithms [Freeh et al. 2005a].

Some methods that identify the different regions of an MPI application not only need to intercept MPI calls, but also rely on compiler support to detect memory or I/O bound phases. Saputra et al. [Saputra et al. 2002] propose energy-conscious compilation based on DVFS. In particular, they adapt many loop-oriented compiler optimizations such as loop permutation, tiling, and loop fusion and distribution [Wolfe 1996] to save energy. Hsu and Kremer [Hsu and Kremer 2003b] present a profile-driven compiler optimization technique to identify program regions using memory stalls. While executing these regions, the CPU frequency is reduced to save energy consumption. The target program is instrumented to detect the boundaries between regions based on analyzing loops and function calls. The profiling phase records the execution time of each region at different CPU frequencies and estimates the corresponding energy consumption.

*DVFS-enhanced MPI runtime systems.* Many MPI runtime systems [Hsu and Feng 2005; Freeh et al. 2005a; Kappiah et al. 2005; Rountree et al. 2007; Ge et al. 2007b; Rountree et al. 2009] are proposed to adjust CPU frequencies dynamically, most of which are online methods. Profile-driven methods detect workload characteristics for a program, then split the program into different regions by instrumentation and adjust CPU frequencies for each region at runtime. In contrast, non-profile methods monitor the execution of an application to detect idleness or to predict the performance and adjust CPU frequencies for different time intervals. Some methods focus on intra-node load imbalances [Hsu and Feng 2005; Freeh et al. 2005a; Ge et al. 2007b], while other methods [Kappiah et al. 2005; Rountree et al. 2007; Rountree et al. 2009] analyze inter-node load imbalances using a DAG (Directed Acyclic Graph) to represent the dependencies between computation and communication tasks and to lower CPU frequencies for tasks not on the critical path.

Hsu and Feng [Hsu and Feng 2005] propose a power-aware algorithm to schedule the execution of a parallel application running on a cluster by dynamically adjusting the CPU frequency of each compute node. In particular, each compute node asynchronously updates its CPU frequency periodically (every  $I$  seconds). Without profiling the targeted application, the preferred CPU frequency is estimated for the next period based on the MIPS rate observed during the current period. The proposed algorithm is evaluated on an AMD Athlon64-base cluster and an Opteron-based cluster respectively using the NAS-MPI benchmarks. On average, 12% CPU energy is saved with 4% performance slowdown on the AMD Athlon64-base cluster; while on the Opteron-based cluster, 8%~25% CPU energy is saved with 3% performance slowdown.

Freeh et al. [Freeh et al. 2005a] propose a method to change CPU frequencies in MPI programs dynamically on a power-scalable cluster. They split an MPI program into a series of phases and assign a preferred frequency to each phase. The program is partitioned according to detected CPU stall periods, during which the CPU waits for memory, disk or communication. A suitable performance-energy point, called a *gear*, is selected for each phase. Phase detection applies to iterative and predictable

parallel applications. The boundaries between different phases are determined mainly according to two rules: 1) any MPI operation; and 2) an abrupt *memory pressure* change, which is measured using the metric *operations per miss* (OPM). The detected phases are ordered according to the energy-time tradeoff. The MPI program is profiled using the MPI profiling layer. The proposed method is evaluated on an AMD Athlon-64s system using the NAS Parallel Benchmarks. The results show the proposed method can save up to 16% energy at a cost of 1% performance loss.

Kappiah et al. [Kappiah et al. 2005] propose a system, called Jitter, to save energy consumption in MPI programs by exploiting inter-node slack. Jitter applies to the case that the computational load is not perfectly balanced. In particular, it reduces the frequency on nodes that are assigned less computation. MPI processes that are not on the critical path can arrive at synchronization points early. Therefore, processes on the critical path determine overall execution time. Given an iterative program with stable iterations, early iterations are profiled to predict the behavior of subsequent iterations. Iteration boundaries are detected according to MPI calls. For every iteration loop, each compute node calculates its local *wait time* and *iteration time*. When the ratio of wait-to-iteration time exceeds a predefined threshold, the process identifies itself as a slack node and accordingly decreases its frequency. In contrast, when the ratio is small enough, the process may convert to a bottleneck process and increase its frequency. The predefined switching threshold is hand-tuned for each system. The proposed method is evaluated on an AMD Athlon-64s system for the ASCI Purple benchmarks and NAS Parallel Benchmarks. The results demonstrate that Jitter can save up to 8% energy usage for the ASCI Purple benchmarks at a cost of 2.6% performance loss.

Rountree et al. [Rountree et al. 2007] develop a system that determines a bound on the energy savings for an MPI application given an acceptable performance loss. Specifically, an MPI program is split into a series of tasks according to MPI calls. Accordingly, a task graph is created to represent the dependency/communication between tasks. Subsequently, heuristic-based linear programming determines an appropriate CPU frequency for each task in terms of the tradeoff between performance and energy. The proposed method is evaluated using 3 scientific applications: Jacobi iteration, a particle simulation, and an unstructured mesh application (UMT2K), in which the particle simulation and UMT2K exhibit load imbalance. With a bound of zero performance loss, Jacobi has no potential energy reduction. In contrast, an energy reduction of up to 15% is available with the particle simulation and the potential reduction for UMT2K is only 3%.

CPU Miser [Ge et al. 2007b] is an online method of applying DVFS to parallel applications on a power-aware cluster. It optimizes the energy consumption for a parallel application according to a given power budget and a user specified performance loss. In particular, CPU Miser splits the runtime into a series of time intervals. It monitors a parallel application's performance in the current time interval and predicts its performance for the next interval using the RELAX algorithm [Ge et al. 2007b]. Evaluation is conducted using the NAS Parallel Benchmarks and showed that CPU Miser can reduce energy consumption up to 20% and constrain performance loss to within 5%.

Rountree et al. [Rountree et al. 2009] develop Adagio to apply DVFS to an MPI program dynamically at runtime. Using MPI calls, Adagio splits an MPI application into a group of tasks that are represented using a DAG (Directed Acyclic Graph). Critical path analysis identifies non-critical tasks for which performance can be degraded to save power. Adagio does not profile the target application prior to its

execution. On the contrary, it deploys an online policy to monitor the execution of each task. For a real-world scientific application, Adagio assumes each task's behavior is identical at every invocation. The highest frequency is applied to a task for its first invocation and the lowest frequency is applied to its second invocation. The execution time of both invocations is recorded to estimate the task's performance degradation when applying different frequencies. An appropriate, reduced frequency is applied to the task's subsequent invocations if it is not on the critical path. The performance of Adagio is evaluated using two real-world applications, UMT2K, an unstructured mesh application assembled by LLNL, and ParaDis, a dislocation dynamics simulation. Adagio decrease total energy consumption by 8% and 20% for UMT2K and ParaDis respectively at a cost of less than 1% increase in execution time.

#### *Power-saving for multi-threaded applications*

Systems with multiple cores per node can use shared memory to parallelize threaded applications. In general, increasing the number of threads up to at least the number of cores on the node obtains the maximal performance. However, the optimal number of threads for an application depends on the maximum degree of its built-in parallelism and hardware characteristics, such as off-chip bandwidth. *Dynamic concurrency throttling* (DCT) [Curtis-Maury et al. 2006a; Curtis-Maury et al. 2006b; Curtis-Maury et al. 2007; Suleman et al. 2008; Li et al. 2010b] controls the active number of threads and switches off inactive cores to save energy for multi-threaded applications, including OpenMP programs. Grant and Afsahi [Grant and Afsahi 2006] investigate using AMP (asymmetric multiprocessors), the processors of which are not operating at the same frequency, to save energy for multi-threaded programs. After examining the NAS Parallel and SPEC benchmarks on a 4-way SMP server, they find that using an appropriate thread scheduler to apply an optimal frequency to each processor reduces energy consumption by an average 15.6% at a cost of 6.1% performance loss when hyper-threading (HT) is disabled. In contrast for a HT enabled case, 7.1% energy saving is achieved with a 4.8% performance loss.

Curtis-Maury et al. [Curtis-Maury et al. 2006a; Curtis-Maury et al. 2006b; Curtis-Maury et al. 2007] propose a dynamic phase-aware performance prediction (DPAPP) model to provide concurrency throttling for multi-threaded programs. DPAPP can predict application performance under different concurrency levels and thread placement strategies on NUMA nodes. In particular, a multivariate process is required to train the DPAPP model to select hardware events that reflect the scalability of each program phase across different hardware configurations. The proposed method is designed for the iterative execution of scientific applications and can support any application with repetitive behavior as long as the execution properties of each phase between executions remain relatively stable and the concurrency is modifiable. The DPAPP model is trained during early iterations. For subsequent iterations, the trained model steers concurrency throttling at runtime to identify phases in which energy can be saved without sacrificing performance.

The optimal thread count for an application depends on the input set and machine configuration. Suleman et al. [Suleman et al. 2008] investigate the optimal number of threads limited by data-synchronization and off-chip bandwidth. Specifically, when the number of threads exceeds a threshold determined by the contention for shared data or bus bandwidth, additional threads do not improve performance and waste chip power. In particular, Suleman et al. propose *feedback-driven threading* (FDT) to control the number of threads dynamically for applications with iterative loops. In terms of implementation, the first few loops (at most 1% of the total loops) are sampled to estimate the application behavior to adjust the thread count for subsequent loops.

Li and Martinez [Li and Martinez 2006] investigate the application of both DVFS and DCT to optimize the power consumption of a parallel application executing on a many-core CMP. They explore a two-dimensional optimization space for the run-time power-performance tradeoffs: 1) the possible number of active processors; and 2) the different voltage-frequency levels available. In particular, they study how to maximize power saving while delivering a specified level of performance. A heuristic-based search algorithm, a combination of binary search and hill-climbing optimization, is applied to each axis of the search space to converge quickly toward the global optimum. Freeh et al. [Freeh et al. 2007a] investigate the same problem, but they find that DVFS should be used first and then DCT should be considered. In addition, Freeh et al. observe the effectiveness of DCT is application-dependent and the improvement to parallel workloads ranges from small to negligible.

#### *Power-saving for hybrid MPI and OpenMP applications*

To handle hybrid MPI and OpenMP applications, the techniques used to save energy for MPI programs and for multi-threaded applications are typically combined together. Li et al. [Li et al. 2010b] propose a power-aware performance prediction model for hybrid MPI/OpenMP applications to support a power-efficient execution algorithm using a combined DCT/DVFS system. Each MPI task is partitioned into a number of OpenMP phases according to the boundaries delineated by MPI operations. DCT is applied to each MPI task with a coordination scheme. In addition, the slack period of non-critical MPI tasks is identified in order to apply DVFS. The effectiveness of the proposed method relies on the prediction of the energy consumption of each OpenMP phase. Using the NAS Parallel Benchmark Multizone suite, they find power saving opportunities increase with MPI task count under weak scaling but diminish under strong scaling. The method reduces energy consumption by 4.2% on average with negligible performance loss or even performance improvement up to 7.2%.

Bailey et al. [Bailey et al. 2015] investigate application performance limitations for power-constrained hybrid MPI and OpenMP applications. The dependencies between the communication and computation tasks of an application are represented using a DAG. A linear programming (LP) formulation is used to optimize the configuration for each task of a DAG. In particular, scheduling sets appropriate DVFS states and OpenMP thread counts for computational tasks between consecutive MPI calls. The proposed solution is evaluated using four fluid and molecular dynamics applications (CoMD, LULESH, and NAS-MZ SP and BT). The conclusion is that algorithms such as LP demonstrate significant opportunities to improve power-constrained performance of current runtime systems, by up to 41.1%.

#### *Hybridization-specific energy saving*

Hybrid computers that are equipped with heterogeneous computing components, such as GPUs, FPGAs, and Intel Phi coprocessors, support highly parallel execution for modest energy consumption. Many projects have demonstrated the superior power efficiency of these heterogeneous components. Several research projects [Williams et al. 2010; Fowers et al. 2013] compare GPUs and FPGAs in terms of both performance and energy consumption. Williams et al. [Williams et al. 2010] perform a device characterization analysis in which they find that FPGAs provide better performance for bit operations and 16-bit and 32-bit integer operations, while GPUs' performance is superior in single-precision and double-precision operations. In contrast, FPGAs are more energy efficient than GPUs. Using convolution as a

benchmark, Fowers et al. [Fowers et al. 2013] find FPGAs are superior to GPUs in both performance and energy consumption.