An Engineered Minimal-Set Stimulus for Periodic Information Leakage Fault Detection on a RISC-V Microprocessor

- Univ. of New Mexico, Albuquerque, NM (United States)

- Sandia National Lab. (SNL-NM), Albuquerque, NM (United States)

- US Dept. of Defense, Fort Meade, MD (United States

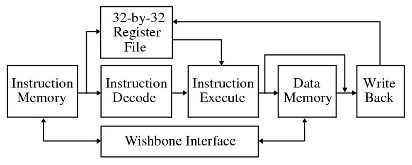

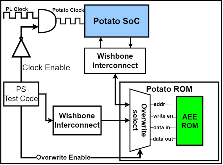

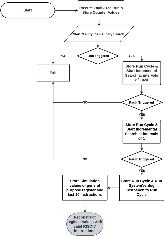

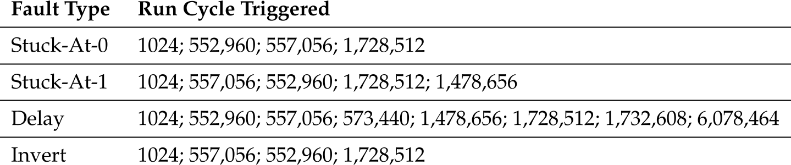

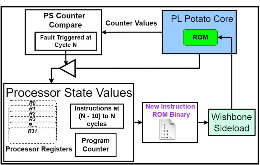

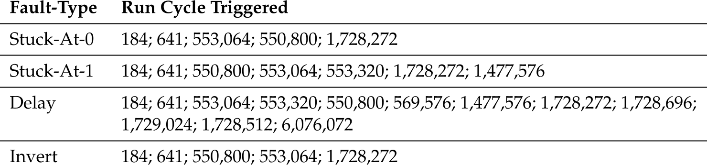

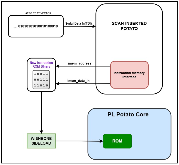

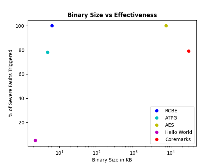

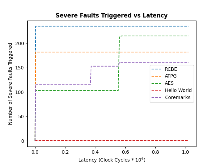

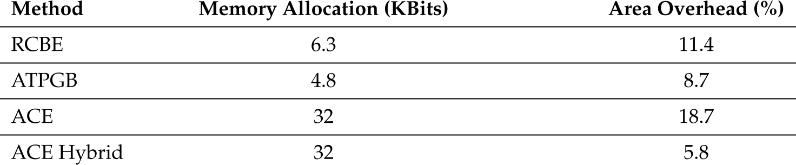

Recent evaluations of counter-based periodic testing strategies for fault detection in Microprocessor (μP) have shown that only a small set of counters is needed to provide complete coverage of severe faults. Severe faults are defined as faults that leak sensitive information, e.g., an encryption key on the output of a serial port. Alternatively, fault detection can be accomplished by executing instructions that periodically test the control and functional units of the μP. In this paper, we propose a fault detection method that utilizes an ’engineered’ executable program combined with a small set of strategically placed counters in pursuit of a hardware Periodic Built-In-Self-Test (PBIST). We analyze two distinct methods for generating such a binary; the first uses an Automatic Test Generation Pattern (ATPG)-based methodology, and the second uses a process whereby existing counter-based node-monitoring infrastructure is utilized. We show that complete fault coverage of all leakage faults is possible using relatively small binaries with low latency to fault detection and by utilizing only a few strategically placed counters in the μP.

- Research Organization:

- Sandia National Laboratories (SNL-NM), Albuquerque, NM (United States)

- Sponsoring Organization:

- USDOE National Nuclear Security Administration (NNSA); USDOD

- Grant/Contract Number:

- NA0003525

- OSTI ID:

- 2341388

- Report Number(s):

- SAND--2024-05026J

- Journal Information:

- Cryptography, Journal Name: Cryptography Journal Issue: 2 Vol. 8; ISSN 2410-387X

- Publisher:

- MDPICopyright Statement

- Country of Publication:

- United States

- Language:

- English

Similar Records

Information Leakage Analysis using a Co-design-Based Fault Injection Technique on a RISC-V Microprocessor

Concurrent detection of transient faults in microprocessors