Improved Double Pulse Test for Accurate Dynamic Characterization of Medium Voltage SiC Devices

Journal Article

·

· IEEE Transactions on Power Electronics

- University of Tennessee, Knoxville, TN (United States); University of Tennessee

- University of Tennessee, Knoxville, TN (United States)

- University of Tennessee, Knoxville, TN (United States); Oak Ridge National Laboratory (ORNL), Oak Ridge, TN (United States)

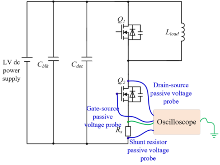

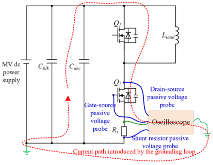

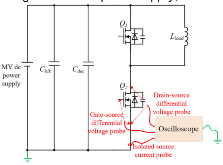

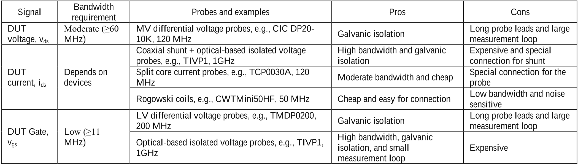

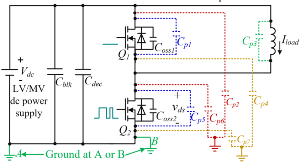

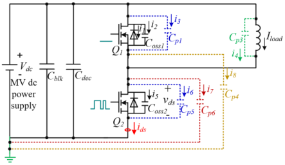

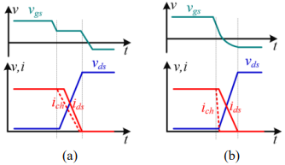

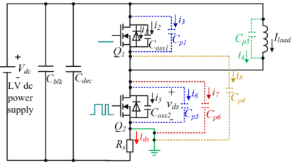

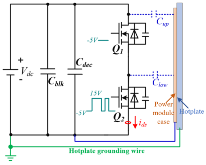

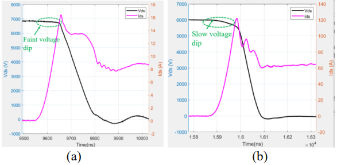

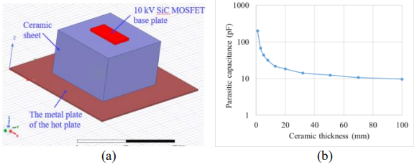

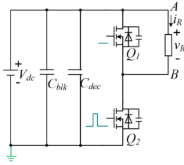

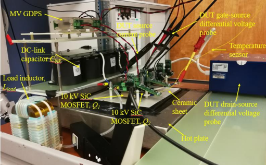

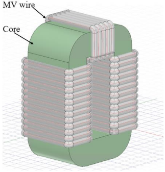

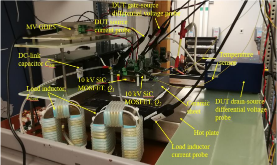

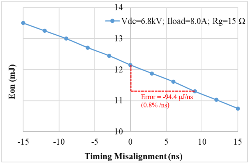

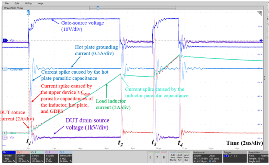

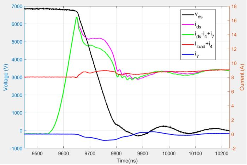

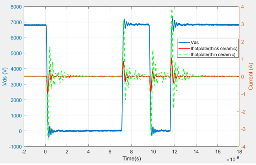

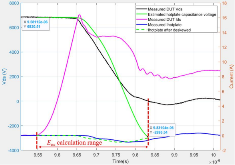

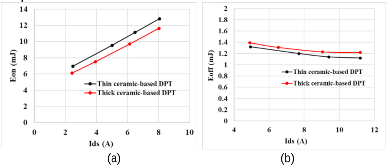

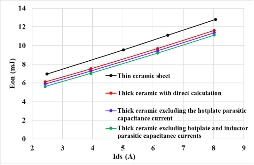

This article presents an improved double pulse test (DPT) for accurate dynamic characterization of the medium voltage (MV) silicon carbide device. The difference between low voltage (LV) and MV DPT setup grounding is first introduced, which results in different measurement considerations. Then, parasitic capacitances in the DPT and their impact on the DPT are discussed considering different grounding points and device connections. Approaches are proposed to minimize the impact of parasitic capacitances on DPT results. In addition, the impact of switching V-I timing alignment on the testing results is discussed, compared to that in the LV DPT; a V-I alignment approach is introduced for the MV DPT. A 10 kV/20 A SiC mosfet -based DPT is taken as an example of the improved DPT, and test results show that it can minimize the impact from parasitic and improve the accuracy of the device switching loss estimation.

- Research Organization:

- University of Tennessee, Knoxville, TN (United States)

- Sponsoring Organization:

- USDOE Office of Energy Efficiency and Renewable Energy (EERE), Energy Efficiency Office. Advanced Materials & Manufacturing Office (AMMTO)

- Grant/Contract Number:

- EE0008410

- OSTI ID:

- 1974605

- Journal Information:

- IEEE Transactions on Power Electronics, Journal Name: IEEE Transactions on Power Electronics Journal Issue: 2 Vol. 38; ISSN 0885-8993

- Publisher:

- IEEECopyright Statement

- Country of Publication:

- United States

- Language:

- English

Similar Records

Methodology for Wide Band-Gap Device Dynamic Characterization

A PWM Strategy for Cascaded H-bridges to Reduce the Loss Caused by Parasitic Capacitances of Medium Voltage Dual Active Bridge Transformers

Characterization and Comparison of Trench and Planar Silicon Carbide (SiC) MOSFET at Different Temperatures

Journal Article

·

Wed Jan 18 19:00:00 EST 2017

· IEEE Transactions on Power Electronics

·

OSTI ID:1399113

A PWM Strategy for Cascaded H-bridges to Reduce the Loss Caused by Parasitic Capacitances of Medium Voltage Dual Active Bridge Transformers

Conference

·

Sun Oct 09 00:00:00 EDT 2022

· 2022 IEEE Energy Conversion Congress and Exposition (ECCE)

·

OSTI ID:1974600

Characterization and Comparison of Trench and Planar Silicon Carbide (SiC) MOSFET at Different Temperatures

Conference

·

Fri Jun 01 00:00:00 EDT 2018

·

OSTI ID:1470888