A multi-layer SEU mitigation strategy to improve FPGA design robustness for the ATLAS muon spectrometer upgrade

Journal Article

·

· Nuclear Instruments and Methods in Physics Research. Section A, Accelerators, Spectrometers, Detectors and Associated Equipment

- Univ. of Michigan, Ann Arbor, MI (United States); University of Michigan, Ann Arbor MI

- Univ. of Michigan, Ann Arbor, MI (United States)

- Academia Sinica, Taipei (Taiwan)

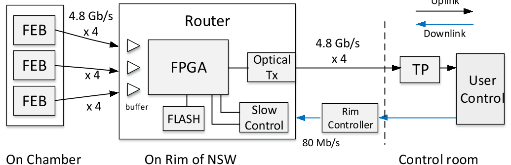

We present a multi-layer single-event upset mitigation strategy implemented in a low-cost Xilinx Artix-7 FPGA. The implementation is targeted for a trigger data router for the ATLAS muon spectrometer upgrade. The mitigation strategy employs three layers of protection to improve overall FPGA design robustness: use of triple-modular redundancy for FPGA fabric logic and embedded soft-error mitigation in the first layer; further enhancement with multi-boot FPGA reconfiguration across multiple copies of configuration memory in the second layer; and FPGA power cycling and configuration memory re-initialization in the third layer. Here, the effectiveness of this scheme has been evaluated at two different neutron facilities, LANSCE and NCSR ‘‘Demokritos’’, with 800 MeV and 25 MeV beam energies, respectively. Testing was performed with a similar configuration to that planned for final operation. We discuss the testing strategy and summarize the test results to estimate the expected data loss over 10 years of operation in the ATLAS experiment.

- Research Organization:

- Univ. of Michigan, Ann Arbor, MI (United States)

- Sponsoring Organization:

- USDOE; USDOE Office of Science (SC), High Energy Physics (HEP)

- Grant/Contract Number:

- AC02-98CH10886; SC0007859

- OSTI ID:

- 1643338

- Alternate ID(s):

- OSTI ID: 1523546

- Journal Information:

- Nuclear Instruments and Methods in Physics Research. Section A, Accelerators, Spectrometers, Detectors and Associated Equipment, Journal Name: Nuclear Instruments and Methods in Physics Research. Section A, Accelerators, Spectrometers, Detectors and Associated Equipment Journal Issue: C Vol. 939; ISSN 0168-9002

- Publisher:

- ElsevierCopyright Statement

- Country of Publication:

- United States

- Language:

- English

Similar Records

SEU mitigation for half-latches in xilinx virtex FPGAs.

SEU mitigation for half-latches in Xilinx Virtex FPGAs

Validation of an FPGA fault simulator.

Conference

·

Tue Dec 31 23:00:00 EST 2002

·

OSTI ID:976550

SEU mitigation for half-latches in Xilinx Virtex FPGAs

Journal Article

·

Sun Nov 30 23:00:00 EST 2003

· IEEE Transactions on Nuclear Science

·

OSTI ID:819344

Validation of an FPGA fault simulator.

Conference

·

Tue Dec 31 23:00:00 EST 2002

·

OSTI ID:976549