Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

A Systems Class Application

**DOE Award Number:**

DE -FC36-07GO17049.006

**Recipient:**

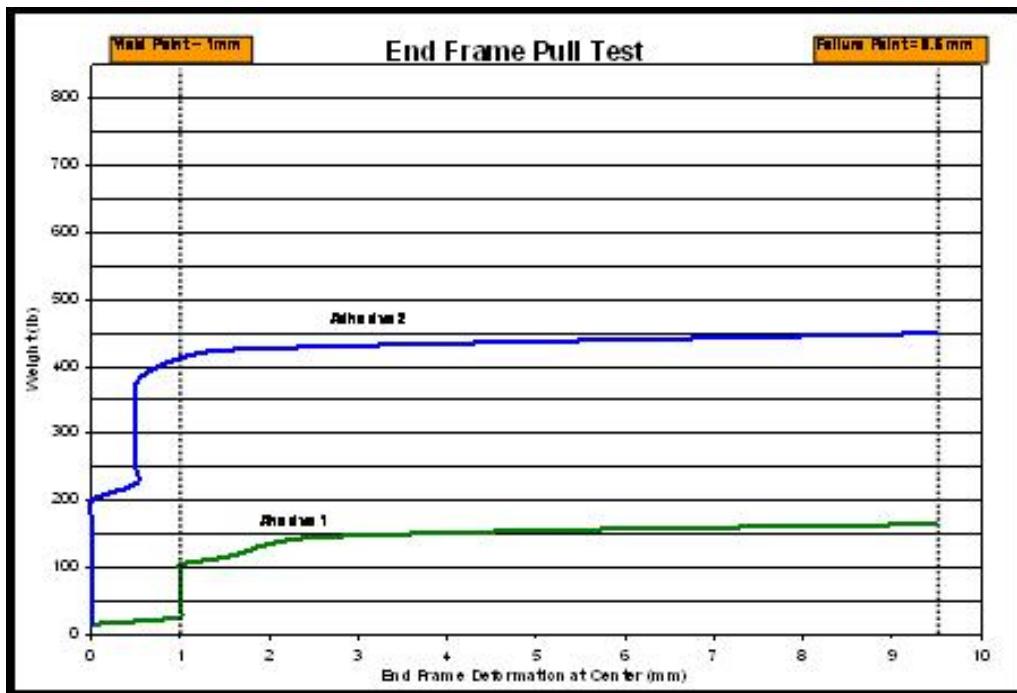

**Leon Fabick**

**Project Title:**

Reaching Grid Parity Using BP Solar Crystalline Silicon Technology:

A Systems Class Application

**Project Manager:**

Daniel W. Cunningham

**BP Solar team members**

Anderson, W; Amin, D; Carlson, D E; Clark, R F; Creager, J; Cunningham, D W; Daniels, E; Garvison, P L; Gleaton, M; Griffin, L; Hering, M; Kelly, G; Kobayashi, M; Koval, T D; Lewis, M; Bennett, M; Meyer, J; Miller, J; Placer, N; Posbic, J P; Poulin, W C; Roncin, S P; Shaner, J; Stoddard, N; Warfield, D B; Wohlgemuth, J; Wu, B; Zahler, J; Zuretti, H A.

**Consortium members**

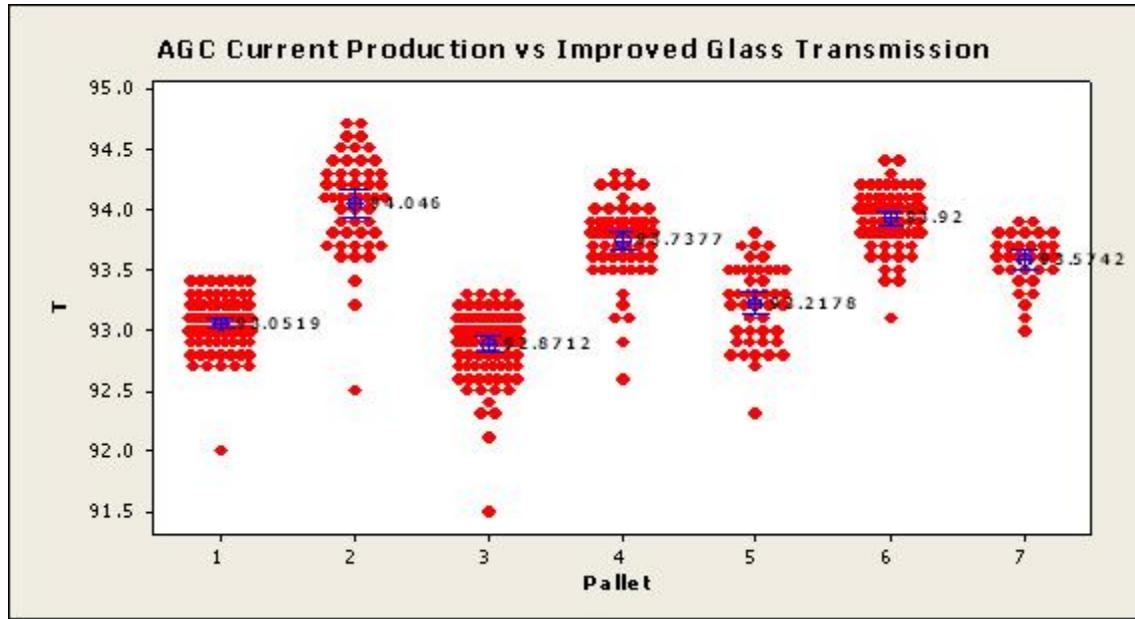

AGC Flat Glass NA, Arizona State University, BASF NA Corp, Ceradyne, Dow Corning Corp, Fat Spaniel Technologies, Florida Solar Energy Center, Georgia Institute of Technology, Komax Systems York, Recticel NA Inc., Sacramento Municipal Urban District, Specialized Technology Resources Inc., Zantrex.

**Executive Summary**

The primary target market for this program was the residential and commercial PV markets, drawing on BP Solar's premium product and service offerings, brand and marketing strength, and unique routes to market. These two markets were chosen because:

- in 2005 they represented more than 50% of the overall US PV market;

- they are the two markets that will likely meet grid parity first; and

- they are the two market segments in which product development can lead to the added value necessary to generate market growth before reaching grid parity.

Federal investment in this program resulted in substantial progress toward the DOE TPP target, providing significant advancements in the following areas:

- Lower component costs particularly the modules and inverters.

- Increased availability and lower cost of silicon feedstock.

- Product specifically developed for residential and commercial applications.

- Reducing the cost of installation through optimization of the products.

- Increased value of electricity in mid-term to drive volume increases, via the green grid technology.

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

- Large scale manufacture of PV products in the US, generating increased US employment in manufacturing and installation.

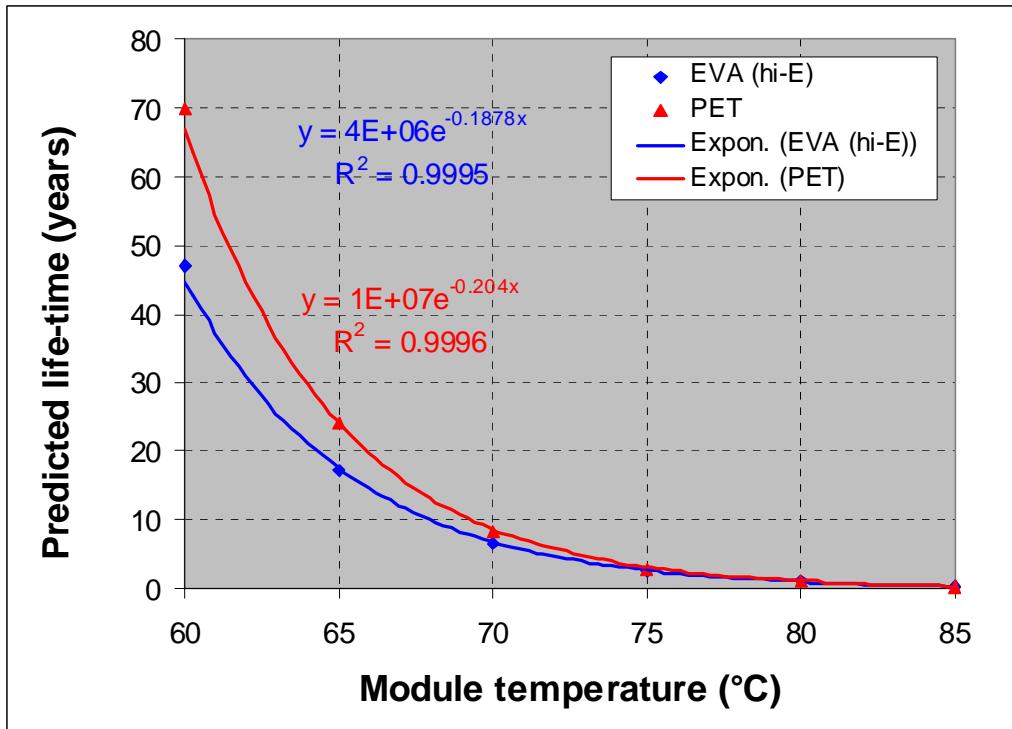

To achieve these goals BP Solar assembled a team that included suppliers of critical materials, automated equipment developers/manufacturers, inverter and other BOS manufacturers, a utility company, and University research groups. The program addressed all aspects of the crystalline silicon PV business from raw materials (particularly silicon feedstock) through installation of the system on the customers' site. By involving the material and equipment vendors, we ensured that supplies of silicon feedstock and other PV specific materials like encapsulation materials (EVA and cover glass) will be available in the quantities required to meet the DOE goals of 5 to 10 GW of installed US PV by 2015 and at the prices necessary for PV systems to reach grid parity in 2015.

This final technical report highlights the accomplishments of the BP Solar technical team from 2006 to the end of the project in February 2010. All the main contributors and team members are recognized for this accomplishment and their endeavors are recorded in the twelve main tasks described here.

*Dr Daniel W. Cunningham.* Frederick Maryland, November 2010.

### Table of Contents

|          |                                      |

|----------|--------------------------------------|

| Task 1:  | Silicon Feedstock Development        |

| Task 2:  | Casting                              |

| Task 3:  | Wafering                             |

| Task 4:  | Cells and Contacts                   |

| Task 5:  | Modules                              |

| Task 6:  | Manufacturing                        |

| Task 7:  | Inverter System Development          |

| Task 8:  | Monitoring and BOS                   |

| Task 9:  | Systems Engineering                  |

| Task 10: | Systems Installation and Maintenance |

| Task 11: | Deployment                           |

| Task12:  | Collaboration                        |

### Appendices

|             |                     |

|-------------|---------------------|

| Appendix 1: | Patent Applications |

| Appendix 2: | Publications        |

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

### Task 1: Silicon Feedstock Development

The goal of this task is to create silicon from an arc furnace operation that provides a suitable starting material for subsequent refining into solar grade silicon through non-gaseous intermediates, typically a directional solidification. Principal requirements for solar grade silicon place limits on dopant impurities such as boron (B) and phosphorus (P), as well as metals within the silicon. A significant portion of the development work for this task was completed by our subcontractor, Dow Corning Corporation.

#### Approach

Dow Corning's approach to solar grade silicon under this program is to couple the use of higher purity feedstock in the arc furnace with select downstream processing to remove any residual impurities. Calculations using the mass balance models predict that the desired levels of purity can be achieved with the right combination of feedstock and processing steps. This approach requires not only the identification of materials with the appropriate level of purity and reactivity but also processing them into a form that allows them to be used at manufacturing scale in furnaces designed around conventional materials. This development process for each raw material consists of the following sequence of steps:

- (1) Identification of a commercial source of the raw material or a process which can be used to make a material of requisite purity

- (2) Forming the raw material into a suitable form via a briquetting process

- (3) Testing the smelting characteristics of the feedstock in the small arc furnace

- (4) Large scale production of the briquettes

- (5) Evaluation of the briquettes in a commercial arc furnace

#### Arc Furnace Background and Development

Silicon metal is prepared by the carbothermic reduction of silica in an arc furnace. In this process a mixture of a carbon, quartz and wood chips (in larger arc furnaces) is continuously fed into the top of the furnace while silicon is removed from a tap hole at the bottom of the furnace. Limestone is also added to prevent slag buildup inside the furnace and make continuous tapping possible.

The key step in the carbothermic reduction of quartz is the conversion of carbon to silicon carbide according to the following reaction:

During the carbothermic reduction process trace impurities in the raw materials concentrate to various degrees in the silicon. In general most of the phosphorous and approximately 30-50% of the boron in the tapped silicon comes from the carbon source. The remainder of the boron, phosphorous and other impurities (trace metals, aluminum and calcium) comes from either the quartz or processing aids like limestone.

Mass balance curves have been developed for impurities introduced by the raw materials. In general only 10-20 % of the original phosphorous and 40-60 % of the boron content in the feedstocks are retained in the tapped silicon. The remainder of the boron and phosphorous are lost through the vent stacks. As a result, the impurity level of boron and

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

phosphorous in the tapped silicon can be predicted based on the level of boron and phosphorous in each feedstock, the retention factor of boron and phosphorous for each feedstock and the quantity of each feedstock used in the furnace.

An empirical model was developed which allows us to predict boron and phosphorous concentrations in the silicon directly tapped from the arc furnace based on the mass and purity of each feedstock, and the retention factor of boron and phosphorous in the furnace for each starting material. Assuming that no external contamination occurs, the model predicts that we should be able to make a material with less than 1.0 ppmw of boron and phosphorous if the boron concentration in the starting materials are less than 0.3 ppmw and the phosphorous concentration is less than 5 ppmw in the carbon source and less than 0.5 ppmw in the silica source.

### Materials

*Synthetic Carbon and Silica sources:* Initial tests completed by Dow Corning had successfully produced high purity silicon using 100% briquettes at a small pilot scale. The boron (B) and phosphorous (P) levels were higher than expected in the silicon and traced to a root cause of higher B and P in the silica briquette binder. Based on raw material to product ratios and determined retention factors, we have defined the need to have Si source (natural or briquette) with 0.2ppmw B and 1.5ppmw P.

In a typical arc furnace, the reductant (carbon) sources include use of coal/charcoal, wood chips, and erosion of the graphite arc electrodes, contributing carbon to the reaction in the approximate ratio of 70:20:10 weight percent, respectively. Evidence collected suggests reductant (carbon) source should focus on removal of alkali metals from the forming binders of these synthetic carbon sources.

A synthetic silica formulation with specific briquette geometry was developed with reasonable properties for briquette formation and finished briquette strength, critical to proper application within the arc furnace. This formulation was modified from initial silica briquette formulations and from carbon briquette formulation in order to provide lowered B and P while retaining mechanical properties.

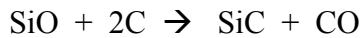

The Dow Corning chosen carbon sources for the briquetting work have very low levels of boron and according to our models do not significantly contribute boron to the tapped silicon. As a result, most of our efforts have focused on the purification of quartz. In addition to the quartz beneficiation studies, we have also evaluated a project on the digestion and re-precipitation of various silica sources with a reasonable degree of success, as shown in Figure 1.1.

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

**Figure 1.1:** Impurity content before and after processing

*Analytical Methods:* Development of analytical methods that allows fast turnaround and analysis of low levels of impurities are important for commercial scale production of these materials. An initial investigation of Laser Assisted Microwave Plasma Spectroscopy (LAMPS) and Laser Ablation ICP-MS as potential techniques for rapid analysis of raw materials was performed. It appears that LAMPS technology is still in the early stages of development so emphasis shifted to further evaluate Laser Ablation ICP-MS. Preliminary studies with Laser Ablation ICPMS are encouraging. The technique proved capable of detecting B and P concentrations in quartz above 0.5 ppmw.

*Limestone Sources:* In commercial arc furnaces, limestone is used as an additive to stabilize the tap hole and minimize the build-up of slag inside the furnace during normal operation. Although this improves the stability of the arc furnace, metals and other impurities in the limestone are transferred to the tapped silicon. To eliminate this source of contamination, samples of calcium carbonate were obtained from various sources and analyzed for their boron, phosphorous and iron content. In general, the precipitated calcium carbonates were purer than the ground materials which in turn, were much purer than bulk limestone. Based on this survey we have identified several sources of high purity calcium carbonate which can be used in a briquetting process to replace bulk limestone and its inherent impurities.

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

*Methods of making briquettes:* A feasibility study on using vibratory compaction molding to make shaped carbon and/or silica briquettes was completed. Vibratory compaction molding is often used in place of extrusion to make concrete block and other decorative moldings. In vibratory compaction molding the mold is vibrated at a high frequency before and/or during the compaction process. As a result, it is possible to make high green strength moldings at low water content.

Using a Dow Corning local sub-contractor set up to make 8" concrete blocks, we were able to manually process a lower water version of our carbon briquette formulation through their equipment and molds. We were also able to process an "all-in-one" formulation containing both carbon and quartz. Although the molded blocks were too large to be tested in an arc furnace, the trial was sufficiently promising that we have scheduled a follow-up trial, using a custom die that will make briquettes more suitable for use in an arc furnace.

*Trial with shaped briquettes:* 130 MT of extruded carbon briquettes were produced to support the first trial with shaped briquettes. However, the first trial had to be postponed until changes could be made to the furnace's feed handling system. The first attempt to feed the shaped briquettes into the furnace using the same procedure that was used with pillow shaped briquettes was unsuccessful. During the test, approximately 90 % of the briquettes were broken. A root cause analysis is currently being performed to see if a feeding system can be developed that will allow us to use the briquettes.

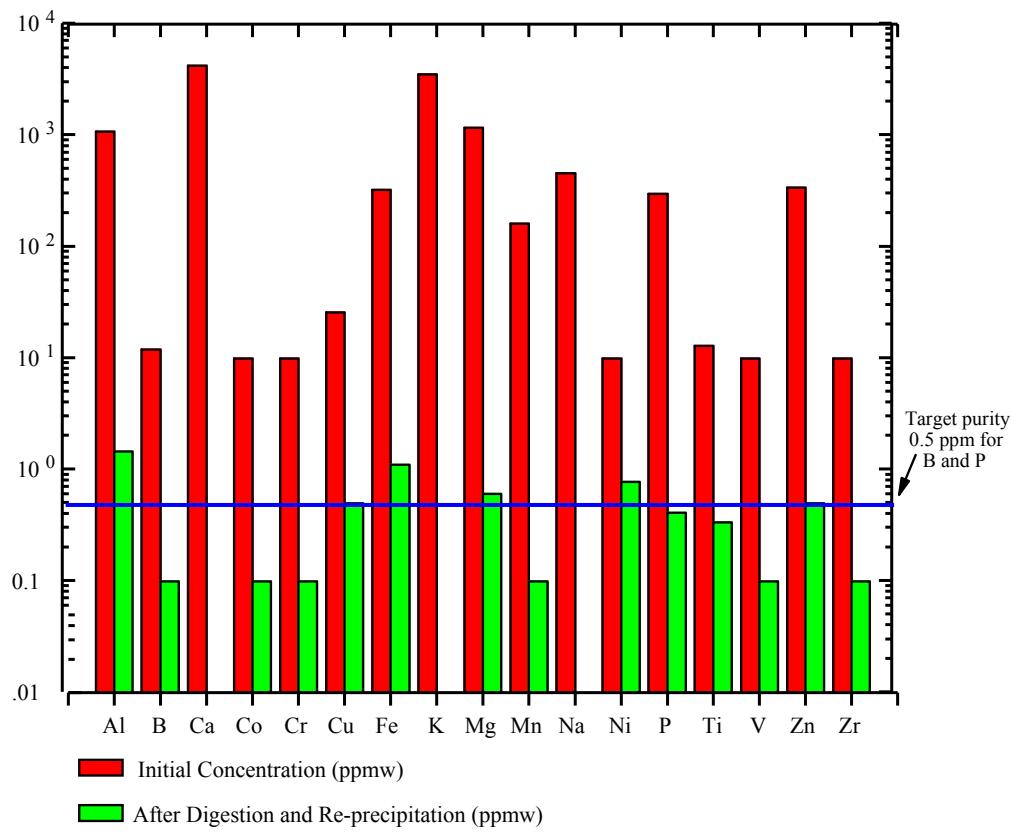

## Processes

*Directional solidification:* For further refining through directional solidification, Dow Corning has demonstrated the ability to control the solidification rate for a given crucible design and silicon mass. Ongoing solidification interface velocity studies suggest that the optimal velocity for high throughput with effective segregation will be between 0.5 and 1.2 mm per minute. By varying the operating conditions and configuration of the directional solidification furnace, Dow Corning has been able to vary the solidification rate between 0.25 mm/minute to over 2.95 mm/minute. However, at rates greater than approximately 1.2 mm/minute effective segregation of boron and phosphorous is compromised. At solidification rates below 0.7 mm/minute the segregation ratios for boron and phosphorous are near theoretical and can be used in an overall manufacturing scheme for controlling the final boron and phosphorous content. Figure 1.2 shows the solidification process for different growth rates.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

**Figure 1.2:** Control of Solidification Rate

The Unit Cost of crucibles for directional solidification is one key factor contributing to this route as a viable solution for purification. A test series on crucible materials of construction suggest that crucible liners of both quartz and graphite can be reused. Significant work was completed to evaluate many potential crucible lining materials in an effort to optimize the molten silicon release, minimize silicon contamination, and maximize the number of re-uses.

*Use of slags for refining:* Dow Corning has also evaluated the use of slags to remove boron and phosphorous. Through our contacts in the solar industry, Dow Corning have become aware of some small scale slagging studies which reduced boron and phosphorous levels to below 1 ppmw from starting levels of 5.5 and 14 ppmw, respectively. We are in the process of initiating a sub-contract to do trials to assess the viability of this technology in a manufacturing process. We have also been investigating the use of Alkaline-SiO<sub>2</sub> slags to remove boron. In one experiment the boron concentration was reduced by 35% after treating the silicon for one hour at 1540 °C with the slag. The concentration of other metals such as Ca, Al, Fe and Ti were also reduced.

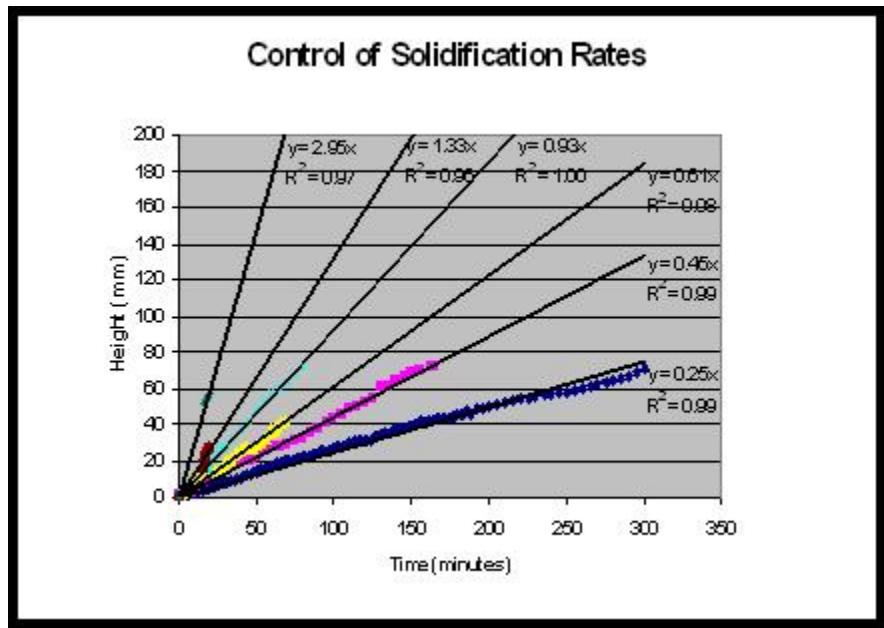

*Commercial smelting trials:* A smelting trial with carbon briquettes has been completed in a commercial arc furnace. In normal operation, a combination of charcoal and wood chips is used as the carbon sources. During the trial, part of the charcoal was replaced with carbon briquettes. At replacement levels up to 80%, the furnace could be operated although there were some issues around the tap hole. Attempts to run the furnace at higher replacement levels (100%) were unsuccessful even for short periods of time. On the other hand, at a replacement level of 50% the furnace operated close to normal. Boron levels in the tapped silicon dropped from an average of 3.3 ppmw with standard raw materials to 2.3 ppmw when 80% of the charcoal was replaced with carbon

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

briquettes. The drop was consistent with the predictions from mass balance models. See Figure 1.3.

During the same trial, the concentration of phosphorous in the tapped silicon was also followed. However, no correlation was seen between the percent of carbon briquettes in the feed and the phosphorous concentration in the tap. A drop in the phosphorous concentration was observed when the feedstock was initially switched to 50% carbon briquettes but the concentration slowly increased until the phosphorous level was similar to the levels seen using only charcoal. At this point, the phosphorous content leveled off and was more or less independent of the carbon briquette composition in the feedstock. We believe the phosphorous results can be explained by changes in the bed porosity (density). Since the briquettes are much smaller (1-2 inches) and uniform in shape compared to the other materials (~ 4 inches), the furnace charge packs more tightly and the gas flow through the bed is altered. During the trial, the bulk density of the feedstock changed from  $450 \text{ kg/m}^3$  (baseline) to  $735 \text{ kg/m}^3$  as the charge changed from 100% charcoal to 100% briquettes.

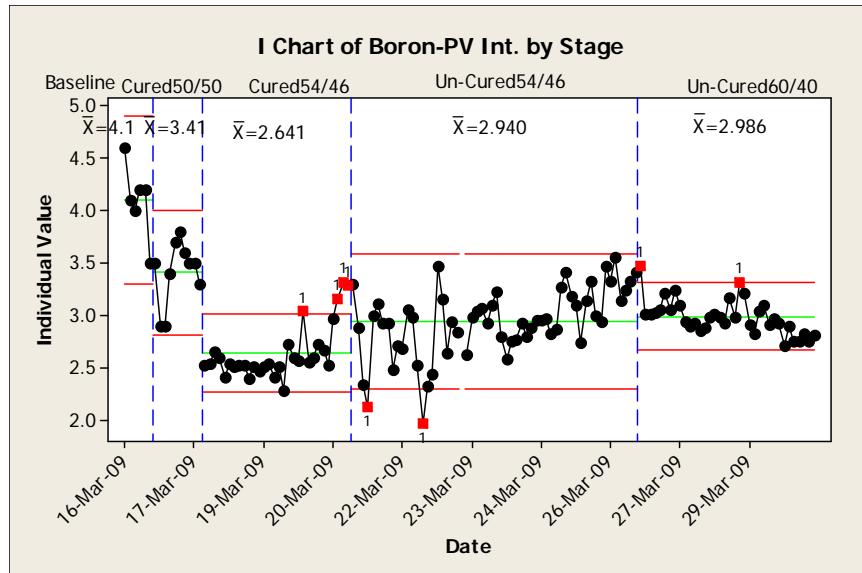

**Figure 1.3:** Boron Level during arc furnace run

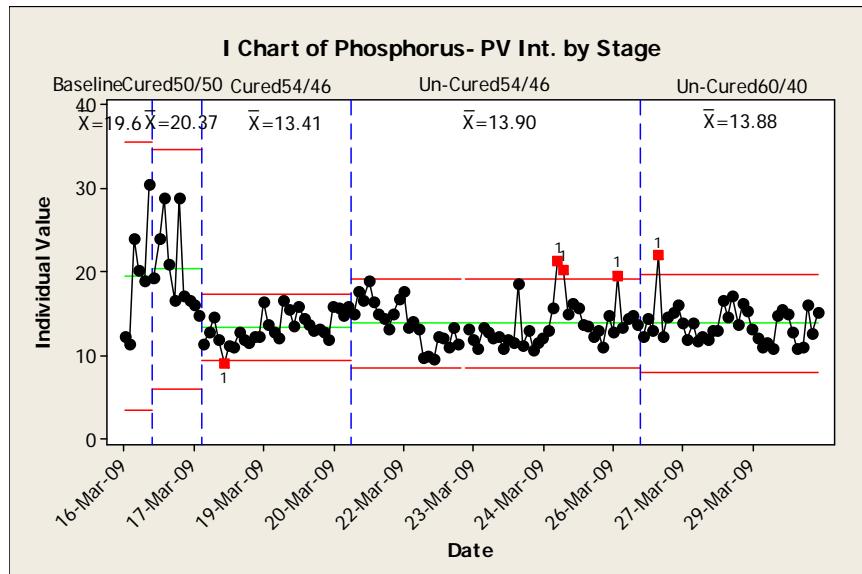

Dow Corning completed a twelve day smelting trial with uncured carbon briquettes. Prior to running the uncured briquettes, the furnace was burned out and run for three days with cured briquettes at a charcoal replacement level of 54 %. The cured briquettes were then replaced with an equivalent weight of uncured briquettes and the furnace run for an additional nine days. During the course of the trial 160 MT of uncured carbon briquettes were consumed. Overall the run was very successful. Power consumption was slightly lower and the tonnage of tapped silicon was slightly higher with the uncured briquettes.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

On the other hand, the electrode consumption was slightly higher as were the boron and phosphorous levels in the tapped silicon. (See Figures 1.4 and 5) We believe most of these variations were due to the higher level of fines (broken briquettes) in the uncured briquette charges.

**Figure 1.4:** Boron concentration during the smelting trial

**Figure 1.5:** Phosphorous concentration during the smelting trial

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

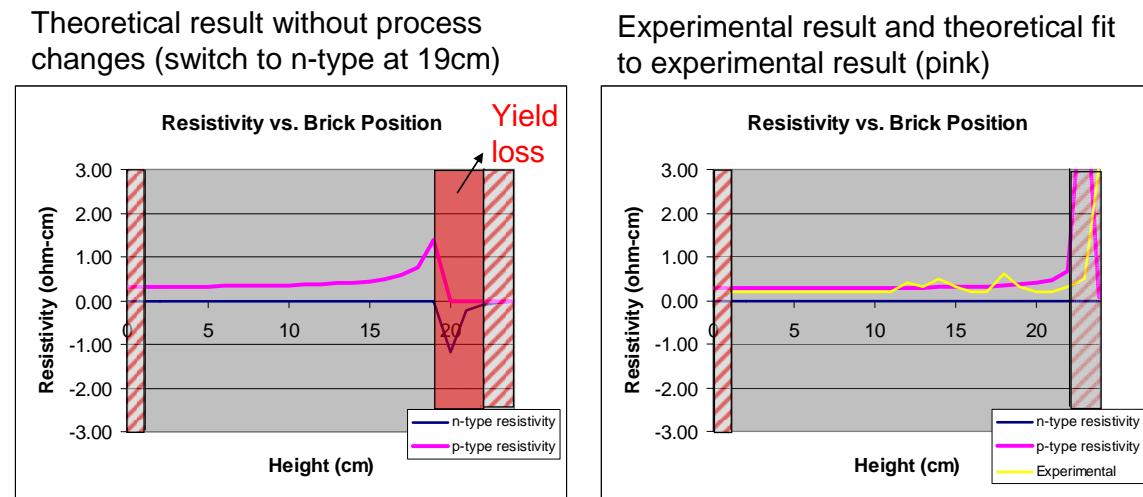

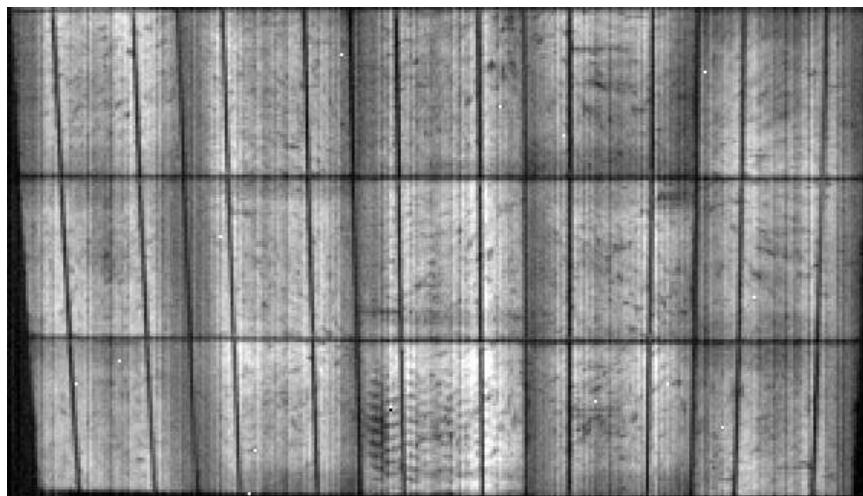

### Testing of Materials at BP Solar

Though BP Solar conducted some initial testing of Dow Corning solar grade materials, none were deemed suitable to process to solar cells in the contract period. In light of this, BP Solar procured solar grade silicon from two other sources to mitigate the schedule delays from Dow Corning. In casting trials, two main results have been achieved: First, a three-dopant system has been devised that has been proven to widen the process window for solar grade silicon. The results of this development are shown in Figure 1.6. Without the process change, we would expect the casting yield to be limited due to a switch to n-type material. The new doping method eliminated most of this yield loss.

**Figure 1.6:** Theoretical and experimental results using low resistivity SOG feedstock

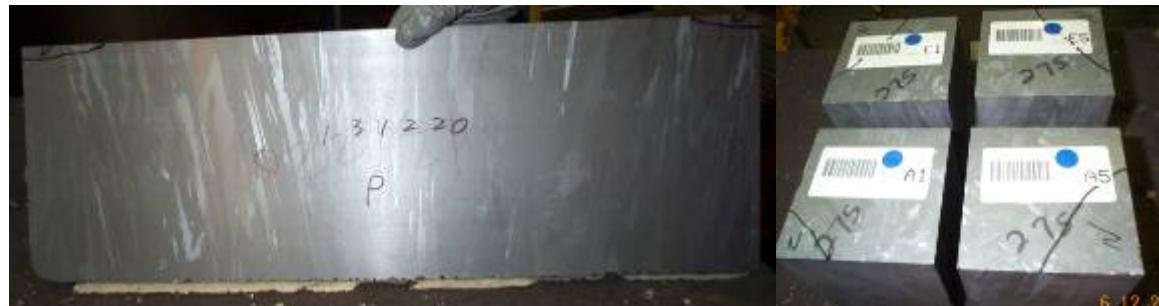

Second, solar grade silicon was mixed at 50% and cast to a 0.6 ohm-cm target. The target was met with <1% yield loss due to a switch from n-type to p-type at the ingot corners (see Figure 1.7).

**Figure 1.7:** Side plates (left) and corner bricks (right) showing p/n transition at the very top of the ingot

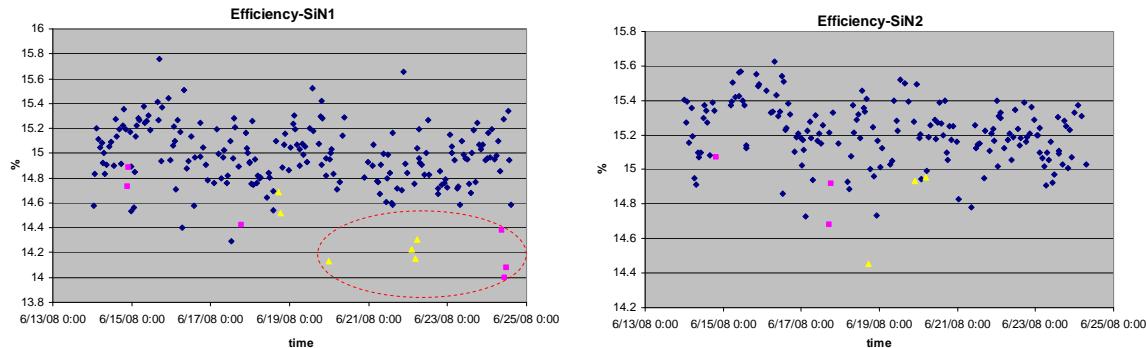

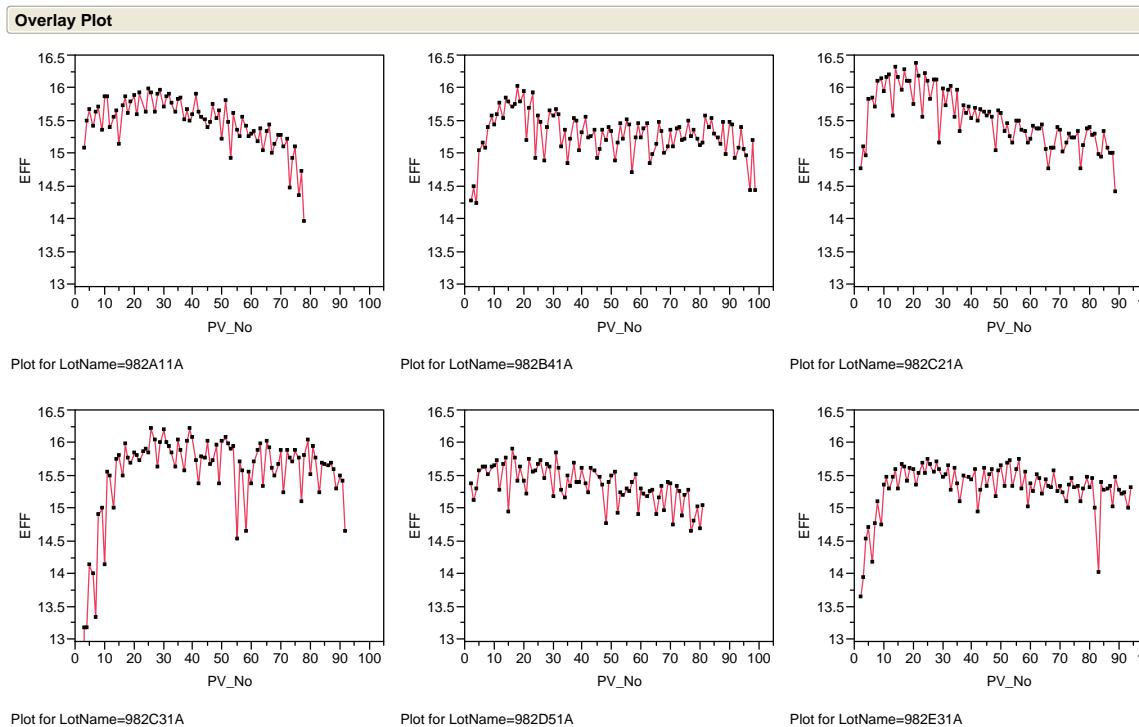

Ingots made using 43% SGS mixed with intrinsic polysilicon were cast and processed into cells. The cell efficiency was somewhat lower than average (see Figure 1.8).

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

**Figure 1.8:** Cell efficiency on normal production (blue) and for lots coming from solar grade silicon ingots (pink and yellow), normal cell process (left), varied cell process (right)

Results approached 15% but did not quite achieve it. Analysis of cells indicate higher recombination than normal at structural defects (grain boundaries and dislocation) which resulted in lower current and fill factor than usual. Efforts to measure dissolved metals by DLTS have turned up no traces in finished cells, indicating that any metal concentration is in precipitated form.

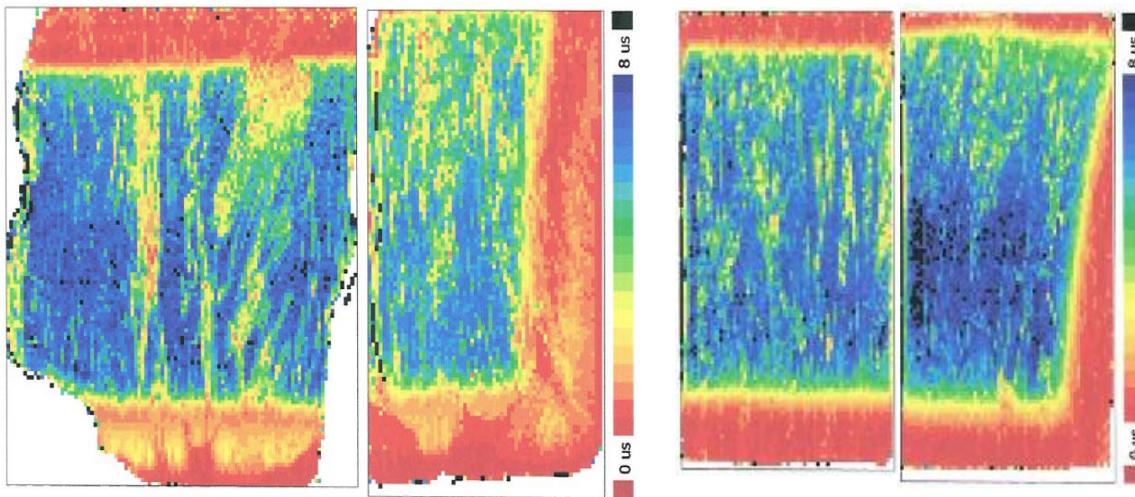

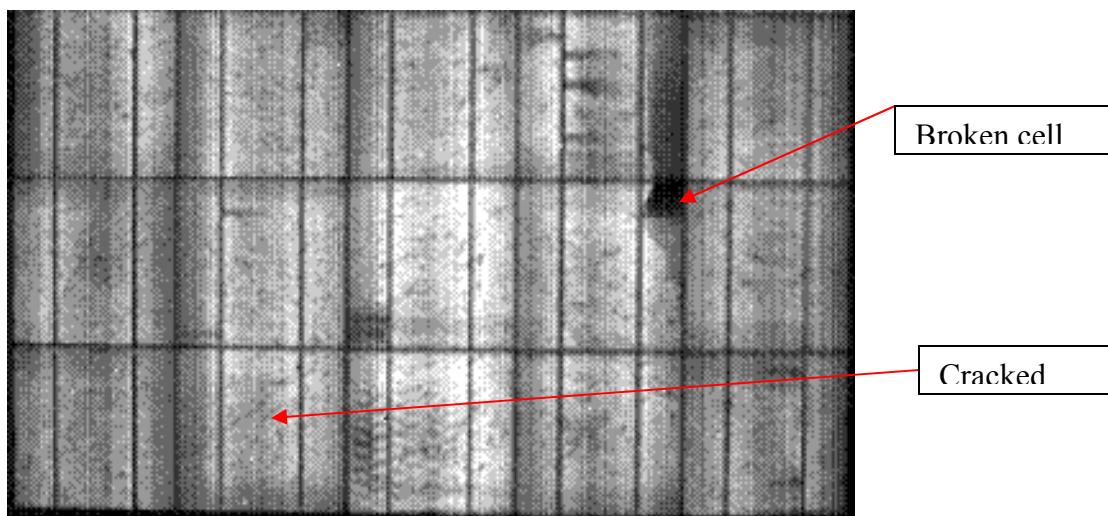

As part of metals analysis and contaminant reduction when working with solar grade silicon materials, testing of alternative no-fire release coatings resulted in some improvement of typical crucible induced “red-zone” low lifetime regions on the border of the ingot as shown in Figure 1.9.

**Figure 1.9: Brick lifetime maps:** An ingot with lowered contamination (left) and average contamination (right). The lifetime increase indicates a halving of the iron concentration, just by eliminating crucible process-induced contamination.

An additional ingot with 50% solar grade silicon has been cast using the Mono<sup>2</sup> <sup>TM</sup> casting technique. The wafers from this ingot were processed using our latest advances in screen print to meet the second year stage gate deliverable of 16% cell efficiency on a 50% SGS wafer. Initial concentrations of impurities in the SGS feedstock were measured

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

to be: 2.1 ppmw phosphorus, 0.4 ppmw boron. Additional dopant was added for precise control of the resistivity profile.

Part way through the second contact year, the subcontract with Dow Corning for solar grade silicon was terminated by mutual agreement. We elected not to issue another subcontract for solar grade silicon at this time, but instead to use commercially available materials from other suppliers that meet the requirements set forth in our goals.

The first ingot cast utilizing one supplier's solar grade silicon had lower lifetime at the brick level than expected and was not processed further.

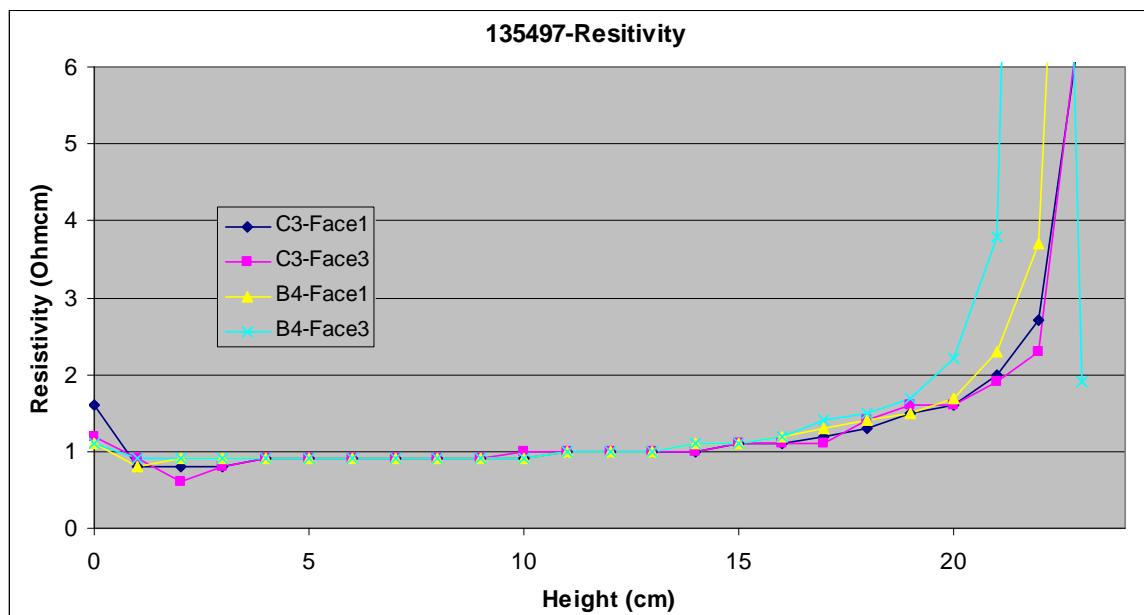

A second ingot was cast with a second supplier's material, having starting dopant concentrations of 0.3 ppmw B, 0.7 ppmw P. The target resistivity at 50% mixing was 1.1 ohm-cm, with a p-type yield of > 90%. In addition, multi crystalline ingots have been cast using 100% of this solar grade material. The resistivity was in-spec through the usable height of the ingot, as shown in Figure 1.10.

**Figure 1.10:** Resistivity of the ingot as a function of vertical position

The yield of good silicon from the ingot was lower than usual, with a 5% increase in inclusion-reject material, evaluated to be due to a higher level of carbon and nitrogen in the solar grade feedstock versus standard silicon. The cutting yield at wire saw was within normal ranges for seven of eight cuts. The other cut had lower yield, without a clear attributable cause. In the cell line, mechanical yield for 17 of 18 lots was in normal ranges, with one lot below average. In cell efficiency, there was a high level of rejects from shunts, averaging 6.7%, compared with normal values around 1%, which we attribute again to the presence of a higher level of carbon and nitrogen that formed many micron-scale inclusions within the solar cell device junction region. The remainder of the cells had good distributions, as shown in Table 1.1.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

|                                        | Efficiency    | Isc           | Voc           | Fill Factor   |

|----------------------------------------|---------------|---------------|---------------|---------------|

| <b>Normal Production</b>               | <b>1</b>      | <b>1</b>      | <b>1</b>      | <b>1</b>      |

| <b>Trial lots</b>                      | <b>0.9718</b> | <b>0.9839</b> | <b>0.9906</b> | <b>0.9804</b> |

| <b>Trial lots after shunts removed</b> | <b>1.0026</b> | <b>0.9899</b> | <b>1.0053</b> | <b>1.0089</b> |

**Table 1.1:** Cell performance of solar grade silicon multi lots normalized relative to production averages

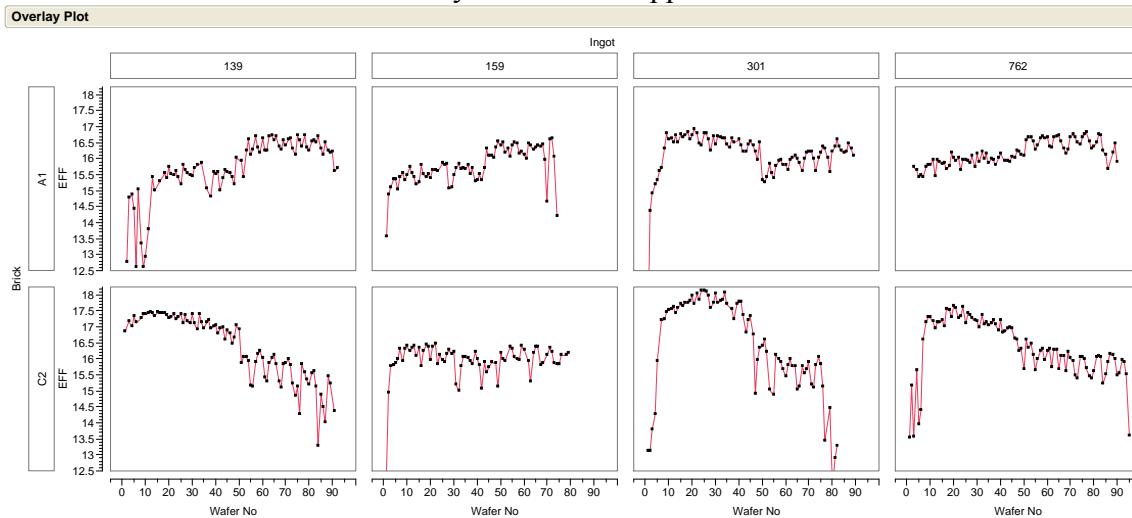

### Task 2: Casting

The goal of this task is to develop, optimize and commercialize the Mono<sup>2TM</sup> process, with focus on casting furnace improvements, next generation furnace designs, production improvement of enabling materials (crucibles and coatings) through our subcontractor Ceradyne, and defect analysis through our subcontractor North Carolina State University.

#### Background

The Mono<sup>2 TM</sup> process is a patent pending method and set of tools to produce near CZ-quality mono crystalline silicon utilizing traditional directional solidification process equipment with some modifications. Mono<sup>2 TM</sup> has the multi crystalline casting benefits of:

- high throughput

- lowered oxygen content and subsequent lowered light-induced degradation (LID) at the module level

- improved packing fraction in the module for improved power (no pseudo square loss of active area as with CZ)

#### Approach

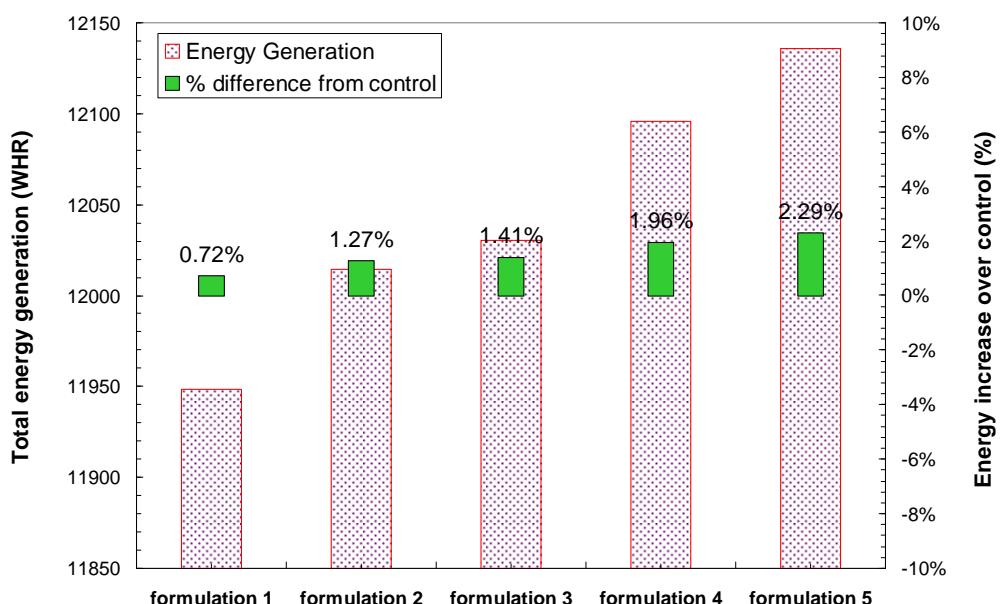

Delivering Mono<sup>2 TM</sup> as a new commercial product has required innovation and development not only in casting, but cell production, module processing, systems and marketing at BP Solar. Because it has had such a wide-ranging impact, the delivery was scheduled in a phased approach. The first commercial demonstration of the process was conducted in late 2007 with a total of 210 kW of modules produced and delivered to a customer. The array was instrumented to report on energy collection from the Mono<sup>2TM</sup> array in comparison to a multi crystalline array installed adjacent. During the demonstration the following performance parameters were achieved:

- Cell efficiency of 15.7% versus a goal of 16%, although the demonstration cells were not texture etched.

- Module maximum STC output power of 178 W versus a production goal of 180 W.

- The module yield matched the production goal.

- The cell yield was 4% lower than the production goal indicating the need to improve in line wafer and cell handling.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

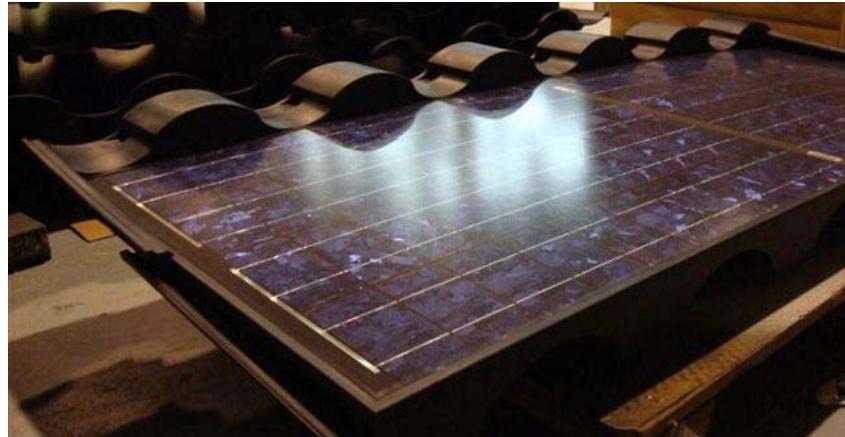

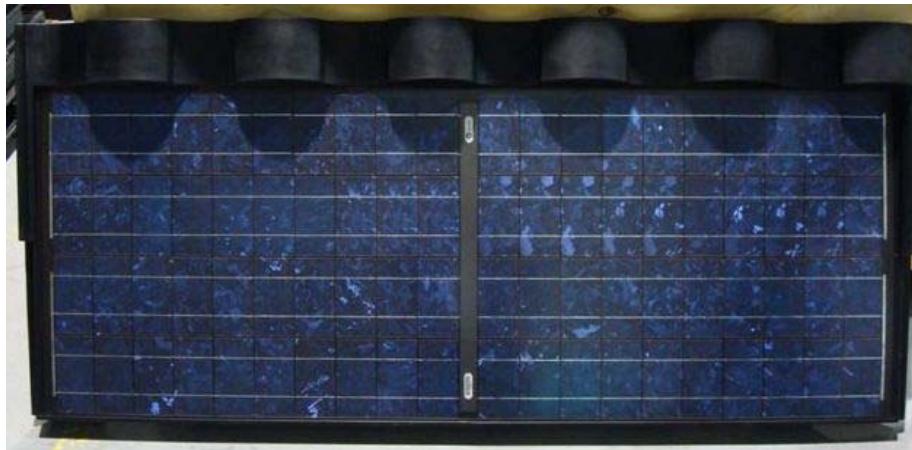

Second year production of 1.2MW of Mono<sup>2</sup>™ product was installed as a single standalone array at Colorado State University at Pueblo in November 2008, see Figure 2.1. All production of these cells and modules were completed at Frederick, MD, but resulted in suboptimal efficiency that will be discussed later in this section.

**Figure 2.1:** Installation as of 12 November 2008 at CSU-Pueblo

Third year production in October of 2009 produced 1.5MW of Mono<sup>2</sup>™ ingots and wafers in Frederick, MD, that was converted to cells and modules by some of our manufacturing partners with more advanced cell production capabilities. As of writing, cell production was complete with Mono<sup>2</sup>™ achieving median cell efficiency of 16.7%, with modules destined to end up in a European project before close of 2010.

### Process

BP Solar has developed a new measurement system for production of Mono<sup>2</sup>™ that has been integrated with the casting stations, both in hardware and most recently in software. The system is now fully operational and capable of operating without human intervention. At least eight ingots have been cast in 'hands-free' mode to produce a Mono<sup>2</sup>™ or seeded multi ingot. Numerous improvements have been made with timing elements and settings of the program, and the interface designed and documented for full for production operation.

As part of scale-up and process development, a cleaning and handling system to enable the Mono<sup>2</sup>™ casting operations was designed and installed into the raw materials processing portion of the casting facility. This allows for efficient processing and loading of both Gen4 (265kg) and Gen5 (400kg) ingots.

In mid-2008, we converted ten casting stations to Mono<sup>2</sup>™ operation. In order to be qualified on the new process, each station produced three Mono<sup>2</sup>™ ingots successfully without intervention. Nine of the ten stations were qualified immediately, with some

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

hardware delays before the 10<sup>th</sup> was certified. The qualification process transitioned to a pre-production trial run whose aim was the production of 1.2MW of Mono<sup>2</sup>™ modules. Through pre-production piloting, BP Solar confirmed the capability to run a process that allows more than 12 ingots to be grown from a single original seed layer. This is important to keep operational costs down in the overall economic model.

Early 2009, extensive work was completed on the investigation into the poor performance of Mono<sup>2</sup>™ cells made in late 2008. After a series of casting experiments that rolled back various changes to the casting process from 2007 and analyzed wafer and cell properties, it was determined that the cast ingot quality was not the driving factor for the low performance. Instead, a change in the cutting slurry and wafer cleaning operations at the beginning of 2008 was identified as the most likely culprit for the low performance. The performance effect was seen as low fill factors, with the structural defect appearing to be small areas of under-etched material from surface debris etch-masking (wire saw grit and kerf) that allowed higher than normal junction leakage currents. This was exacerbated by the (100) oriented crystal that allowed pyramids to form under these etch-mask initiators.

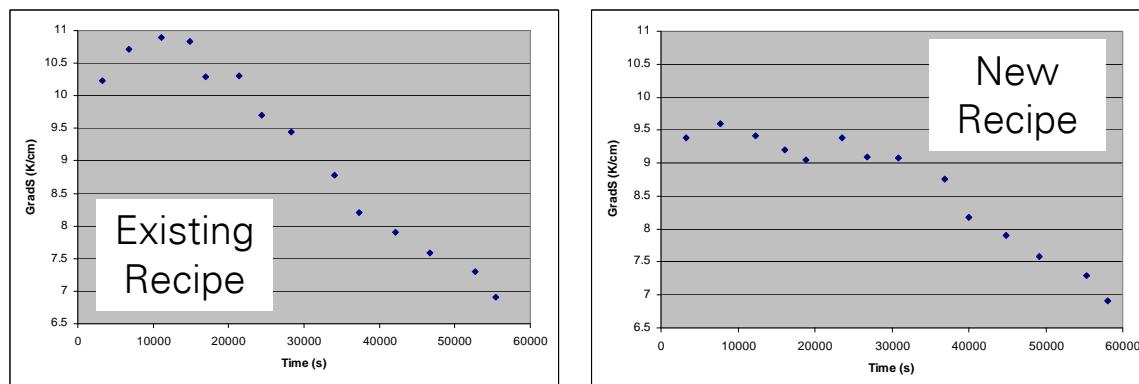

Subsequent to production trials, our development work has focused on how to further improve the quality and consistency of Mono<sup>2</sup>™ material. Analysis from our subcontract with NCSU showed there is not a significant build-up of metallic impurities in the seed material over the several casts of the recycling process, but that the crystalline quality of the seed material can degrade from an undercutting process that sometimes occurs. This information has been used to change the slab recycling process to maintain higher quality. We have also worked to decrease the prevalence of inclusions and the dislocation cascades that they create in the ingots. In one case, we cast two ingots using our low carbon technology to decrease inclusion-rich material. In another case, we analyzed our current growth profile and found the thermal gradient to exceed normal values. A new growth recipe was developed to maintain the current growth rate but decrease the gradient, as shown in Figure 2.2.

**Figure 2.2:** Thermal gradients as simulated in our 3D casting simulation package for the current Mono<sup>2</sup> recipe (left) and a newly developed one (right)

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

### Production furnace work and Simulation

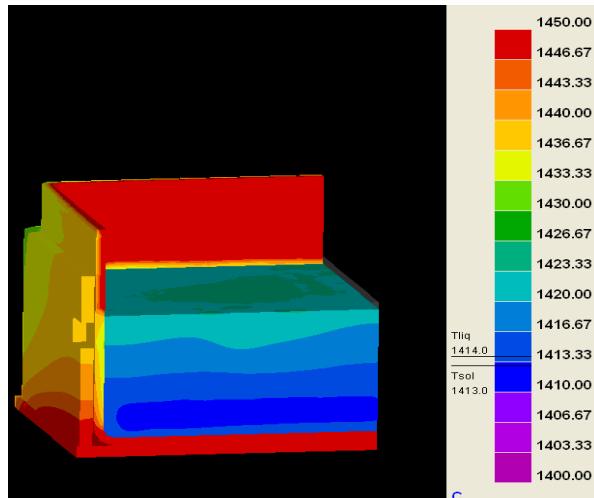

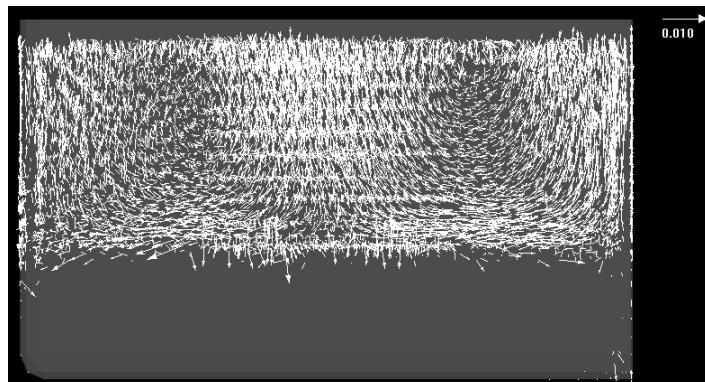

Significant work centered on development of capability at the 400kg (Gen5) ingot size, and a new casting station was purchased and installed as a comparison to the current underperforming Gen5 station. To better understand thermal and fluid flow issues inside the furnace, a 3D simulation model was set up. The preliminary results of temperature and velocity are shown in Figures 2.3 and 2.4 below. Since it is a symmetric system, only one quarter was calculated.

**Figure 2.3:** Temperature distribution in the furnace

**Figure 2.4:** Velocity vector in the molten silicon

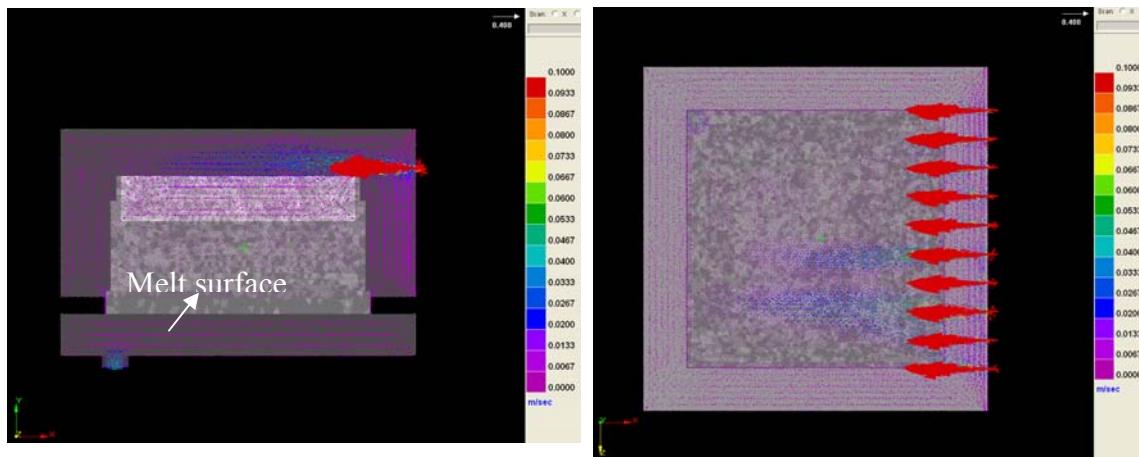

Through the development period, a total of 22 ingots have been cast in the Gen5 casting stations. One vendor's station has consistently performed poorly, mostly because of inclusion yield losses. The other vendor's station has performed better, but still yields below standard material due primarily to small crystal structure, identified in some cases as inclusions. To understand some of the crystallization issues, we studied the interaction of gas flow dynamics with the temperature profile of the furnace and its effect on crystallization. In Figure 2.5 the gas flow has been simulated with ten nozzles deploying high velocity argon into the furnace with a vacuum exhaust down below.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

**Figure 2.5:** Simulation of Gas Flow

Although significant argon flow comes from the nozzles, the flow velocity drops dramatically outside of the jet area, and only modest flow velocities are found at the surface of the silicon melt. Lack of clean argon flow at the melt surface can significantly increase the carbon and nitrogen concentration in an ingot.

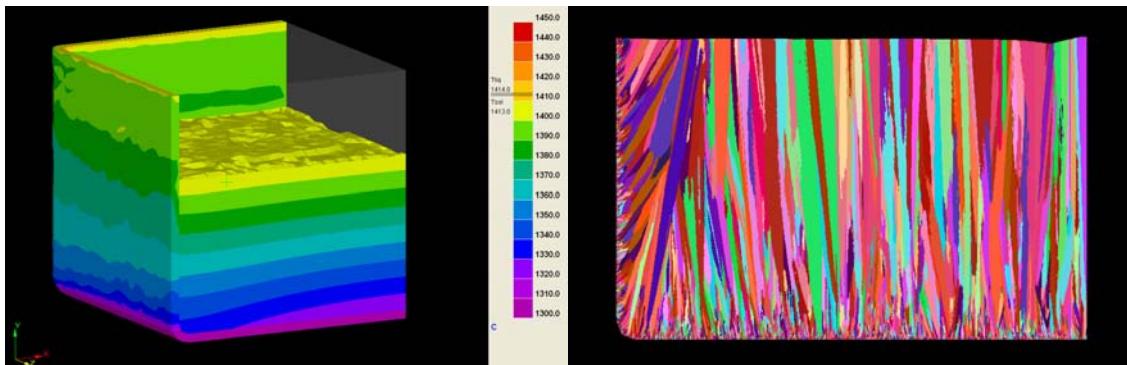

The thermal profile in an ingot just after solidification is shown in Figure 2.6 with a time series of the growth process used to simulate crystallization of the ingot using the CAFE methodology. The isotherms are generally flat, especially at the top, while near the bottom there is a slightly convex curvature.

**Figure 2.6:** Simulation of Thermal Profile and Crystallization

Even though the simulation package assumes dendritic crystal growth, the results for the crystallization pattern are remarkably good. The nucleation conditions still require fine tuning to match the behavior in some parts of the ingot, but the combination of thermal modeling with crystallization has proved fruitful so far. Significant future work is planned to optimize the grain structure with application to Mono<sup>2</sup>™.

### Next generation furnace design

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

To further improve casting and Mono<sup>2</sup>™ economics, the capital expenditure requirements per unit produced and process intensity as measured by equipment vessels per unit produced were identified as major factors to true large scale commercialization of silicon based PV and Mono<sup>2</sup>™ product. A comprehensive design package was commissioned by BP Solar to detail a new integrated design for and advanced casting system. Through the design process and BP safety reviews, nearly 1000 man-hours have been devoted to ensure process safety in scale-up and intensification through PHA (Process Hazard Assessment) and FMEA (Failure Mode and Effects Analysis) tools. A HAZOP (Hazard and Operability Study) and LOPA (Layers of Protection Analysis) have not yet been completed pending the final tool layout.

Project risk assessment also identified twelve critical technical items and plans were developed to address each one, including:

- Ability to fabricate large ceramic parts (>1m<sup>3</sup> volume, >3m total length)

- Viability of melter transfer tray concept

- Need for pre-heat chamber in melter design

- Ability to fabricate large C-C (carbon-carbon) composite parts and validate structural strength

- Identification and qualification of material of construction for melter charging tray

- Prototype validation of graphite heat exchanger concept

- Prototype validation of graphite cartridge heat concept

- Determination of dissolution rate of silica exposed to liquid silicon at elevated temperature

- Durability of C-C composite materials under proposed use conditions

- Determination of extent of reaction between C-C composite material and silica under proposed use conditions

- Modeling and identification of expected thermal profiles within vessels

Progress in each of these areas has included:

- Work with subcontractor Ceradyne resulted in successful fabrication of parts meeting both size criteria

- Vendors capable of manufacturing large C-C parts were identified and mechanical test completed

- Testing and modeling indicates no need for pre-heat chamber prior to introduction of silicon to melt chamber

- Prototyping of melter charging apparatus validated transfer concept

- Graphite heat exchanger mock-up completed and pressure-flows validated with cold test

- Graphite cartridge heater testing completed with peak temperature, power output, and longevity test validated

- 895 hours silicon contained in silica test validates correlation of silica dissolution rate with temperature and that the measured rate should be compatible with ceramic part lifetime assumptions

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

- Thermal modeling of the system identified some critical issues that had to be addressed and redesigned, particularly around thermal uniformity and cold spots that could allow silicon to solidify in unintended areas

### Large ceramics and improved release coatings

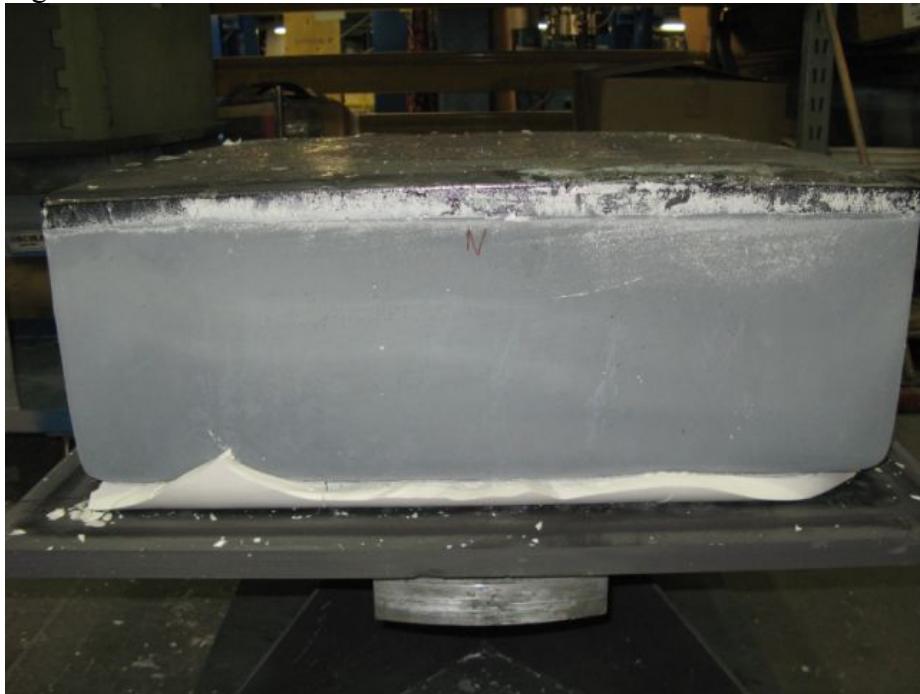

Testing of “hard coat” crucibles and have seen generally good release properties, with isolated sticking points. After additional feedback, Ceradyne continued working to perfect the  $\text{Si}_3\text{N}_4$  hard coat system. Numerous parts were supplied to BP Solar to determine the minimal coating layer thickness required, verify Ceradyne kiln firing parameters, and qualify first and second sources of  $\text{Si}_3\text{N}_4$  raw materials. Parts were supplied in both standard crucible sizes (Gen4, 720 x 720 x 420 mm) and in jumbo (Gen5, 877 x 877 x 420 mm) sizes. In casting nearly 30 ingots, lowered inclusions and higher minority carrier lifetime results were seen. It was discovered that one of the materials used in the “hard coat” formulation had potentially excessive levels of phosphorus that was modifying the resistivity of the ingot and producing the falsely increased minority carrier lifetimes. Alternative vendors were identified for this binder and qualified. An example of ingot cast using the Ceradyne release coating is shown in Figure 2.7.

**Figure 2.7:** Ingot cast using Ceradyne “hard coat” system

In addition to coating developments with our subcontractor Ceradyne, over the course of the contract have developed our own automatic spraying process for applying a BP Solar developed coating. With the reduction of operator intensity and increased consistency of coating it is estimated to have a investment payback of under one year.

Ceradyne delivered both high purity crucibles and crucibles manufactured by a novel casting process not yet disclosed. Both sets of crucibles performed well in casting trials.

### Defect Analysis - North Carolina State University

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

NCSU performed analysis on an edge cross-sectional slice of a Mono<sup>2</sup> <sup>TM</sup> ingot to evaluate microwave photoconductive decay minority carrier lifetime and to determine whether the lower performance areas were due to structural or chemical defects. At the base of the ingot, small localized low lifetime regions are caused by what appears to be a liquid under fill during the casting process with additional evidence of small gas pockets within the crystal. During initial growth phases, etch pits lining up on (100) planes are evidence that an interstitial-rich growth region is causing dislocation loops, most possibly due to slow initial growth rates or higher than equilibrium thermal gradients.

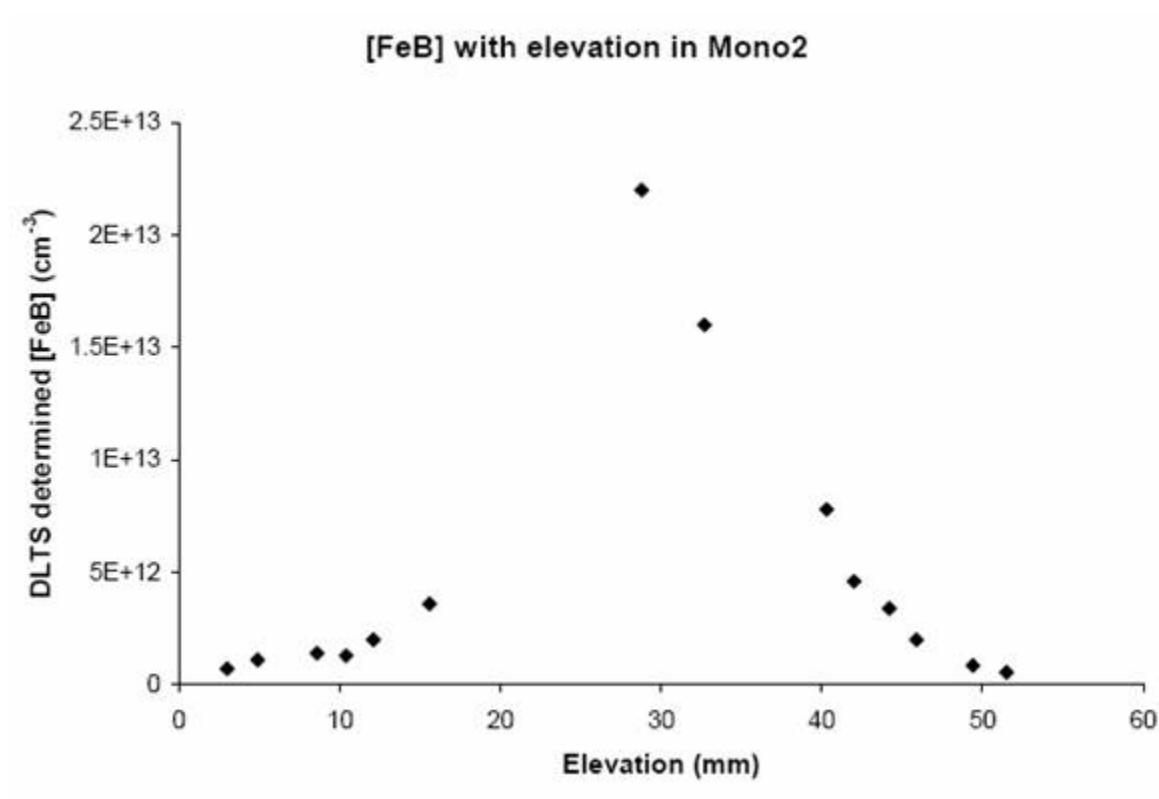

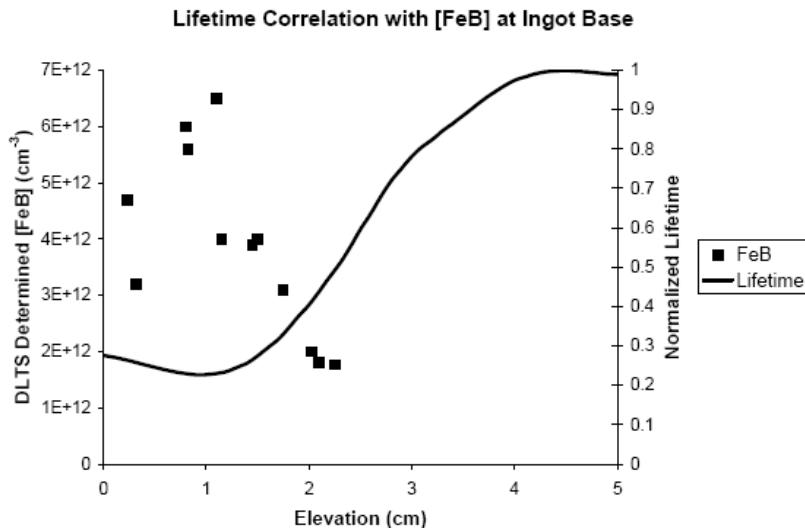

Deep-level transient spectroscopy (DLTS) of the base low lifetime regions confirmed results similar to other cast materials, that is the influence on lifetime and presence of iron, as Fe-B pairs, from the crucible. The distribution (shown in Figure 2.8) is influenced by at least one other characteristic of the silicon than distance from the crucible wall.

**Figure 2.8:** Concentration of FeB complex with elevation above the crucible base

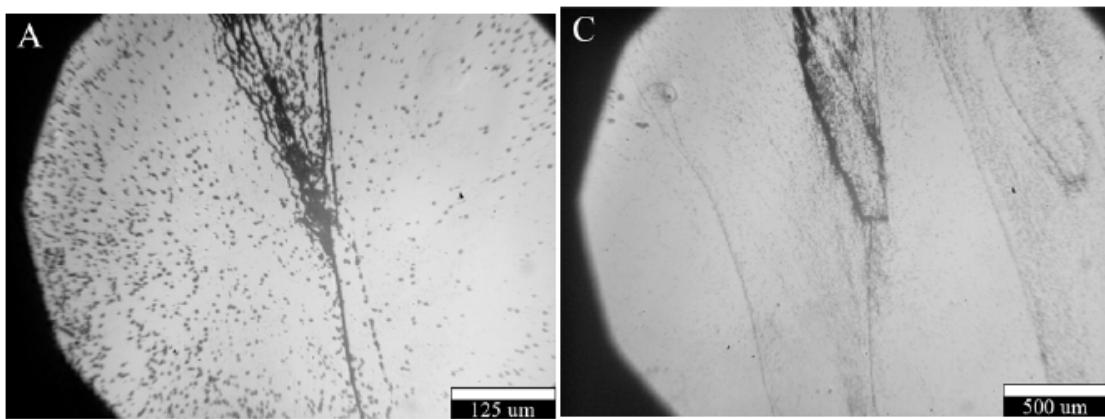

Further defect study also showed that particle defects typical of mc-Si casting, silicon carbide and silicon nitride, are present in the material and most likely the cause of the majority of dislocation cascades. Dislocation branching can be seen to occur in several distinct forms, acute and abrupt are shown in Figure 2.9, which will require further study to determine their exact cause.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

**Figure 2.9: Dislocation Cascades in Mono<sup>2</sup>™ Silicon**

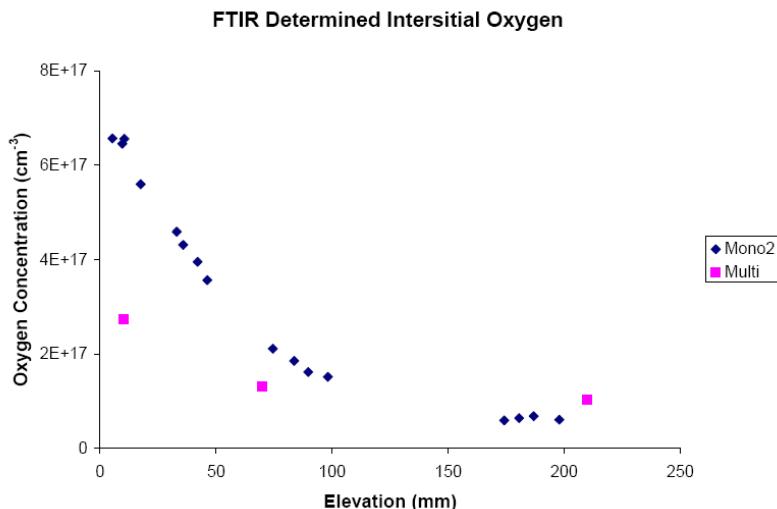

By FTIR, it has been shown that Mono<sup>2</sup>™ ingots have a higher concentration of oxygen by up to a factor of two in the lower half of the ingot compared with ingots cast using multi-crystalline silicon (Figure 2.10). While higher, the absolute values are still low relative to typical CZ concentrations. Lateral profiles of carbon and oxygen have shown a slight increase in oxygen in the first 2 cm from the side wall of the crucible, while carbon profiles remain flat.

**Figure 2.10:** Oxygen profiles from the bottom to the top of bricks from Mono<sup>2</sup>™ and multi ingots. The elevated oxygen is believed to be due to a lack of settling time at lower temperatures

There is a low lifetime region that extends some 3-4 cm from the side wall, but this is not related to oxygen concentration. Instead, Deep Level Transient Spectroscopy has shown a good match between the iron-boron pair concentration and the lifetime (see Figure 2.11), indicating that metallic contamination is the root cause.

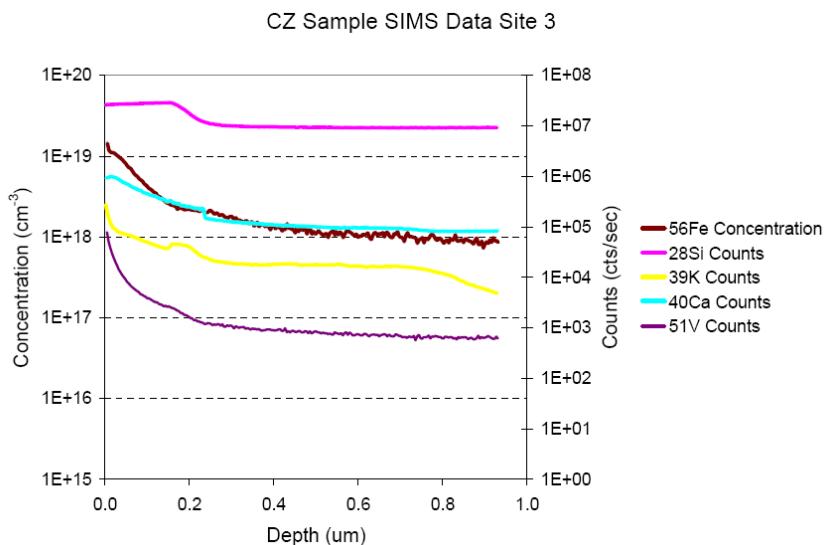

An analysis for sources for iron focused on the crucible firing furnaces, where Kanthal (Fe-Cr) type heaters are used to sinter the release coating at 1100 °C for two hours. To test the contamination in the furnace, we took two high purity CZ wafers and set them in the furnace for a normal cycle. Afterwards, the wafers were tested by SIMS at NCSU for

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

metal contamination. The results are shown in Figure 2.12, with extremely high concentrations (up to 20 ppma) of metals found extending deep into the wafer. This contamination source is significant, and potential ways to address it are being considered.

**Figure 2.11:** Scaled Minority carrier lifetime superposed with DLTS measurements of FeB pair concentration

**Figure 2.12:** SIMS metal depth profiles in a contaminated CZ wafer. Only the iron is calibrated to be quantitative

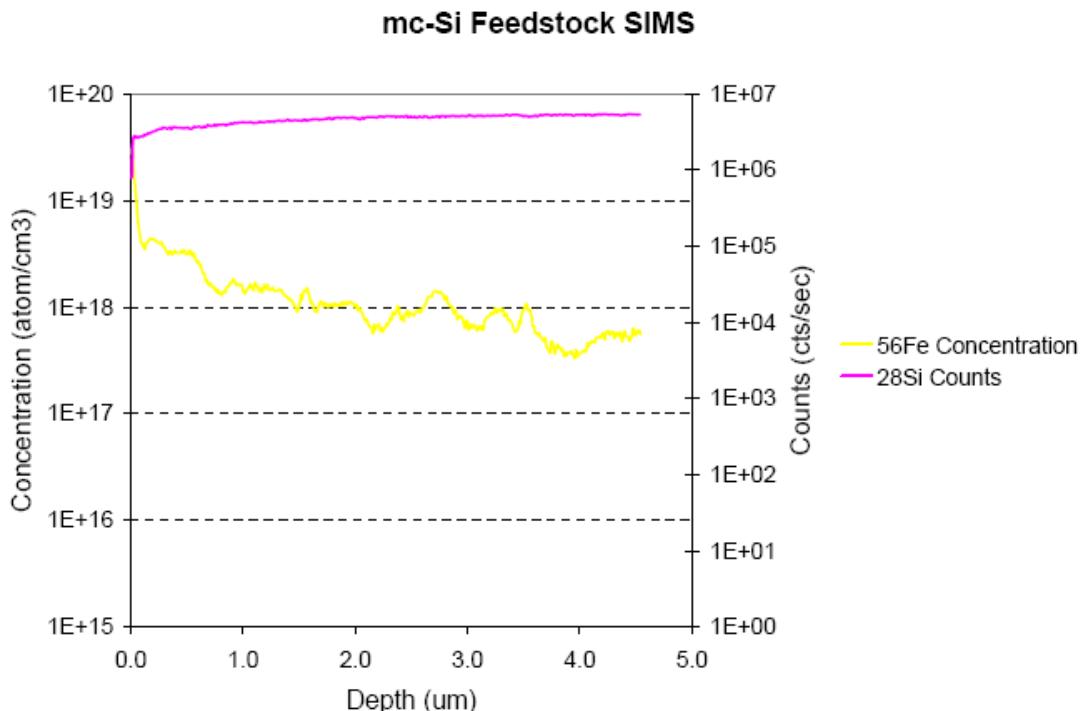

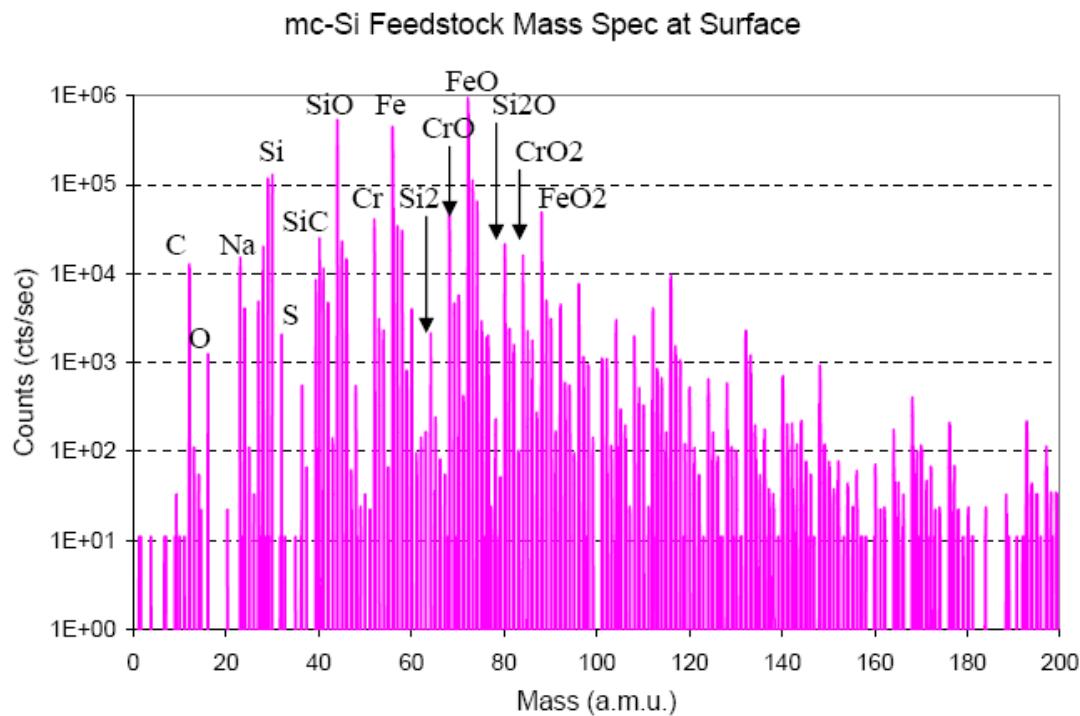

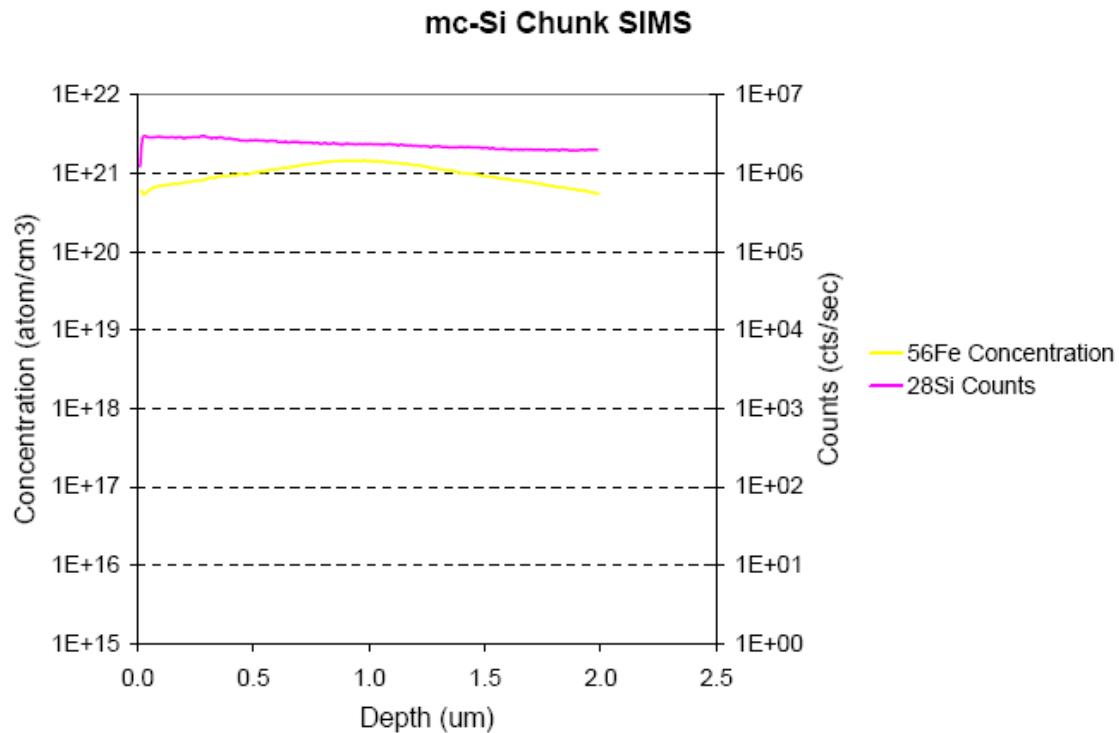

Two samples were received from BP Solar that had been contaminated in the furnaces used for casting. One sample was a feedstock piece from an aborted casting that was partially melted in the process. A dark gray coating was present on the surface. EDS was only able to detect carbon in this coating. A second sample was a chunk from a multi crystalline brick that was exposed to the casting furnace environment. EDS previously

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

detected oxygen, carbon, and iron within this coating. Since the sensitivity of EDS is relatively low (~1 atomic %), SIMS was performed on both samples. Figure 2.13 is the quantitative iron SIMS analysis of the surface coating on the feedstock piece exposed to the casting furnace environment. The iron concentration varies with depth, being as high as  $10^{19}$  cm<sup>-3</sup> near the surface and dropping to  $10^{18}$  cm<sup>-3</sup> just beneath the surface. The mass spectroscopy data shown in Figure 2.14 indicates that other elements are present as well. The largest peaks have been labeled up to a mass of 100 a.m.u. since higher masses are likely due to combinations of elements. The primary contaminants detected are C, S, Na, Fe, and Cr. Most peaks stay approximately the same height to at least a depth of six microns with the exception of slight drops in the C, Na, and Cr peaks.

Shown in Figure 2.15 is the quantitative iron concentration profile taken from the surface of the multi crystalline chunk which was originally part of a brick exposed to the casting furnace environment. Iron was detected at concentrations reaching  $10^{19}$  cm<sup>-3</sup> in this coating which is about 2 atomic %. The same elements are present in this sample's coating as were in the feedstock piece's coating. There are slight drops visible in the C related peaks with increased depth.

The concentration of iron in these surface coatings is incredibly high ranging from  $10^{19}$  to  $10^{21}$  cm<sup>-3</sup>. Iron has been identified in previous reports as the primary lifetime reducing impurity in BP Solar cast silicon, and the furnaces used during casting are significant sources of this contamination. The coating thickness on both samples has not been determined so it is difficult to say just how much total iron is present on the surface. It is at least 2 microns thick on both samples.

**Figure 2.13:** Quantitative Fe concentration data from SIMS on the surface of the partially melted feedstock piece.

Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

A Systems Class Application

**Figure 2.14:** SIMS mass spectra from surface of feedstock piece

**Figure 2.15:** Iron concentration SIMS data in mc-Si chunk surface layer

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

### Task 3: Wafering

The goal of this task are to develop a process for cutting 180  $\mu\text{m}$  thick wafers using thinner ( $< 130 \mu\text{m}$  thick) wire and develop an integrated demounting and cleaning process.

#### Approach

After initial testing, it was determined the primary limiting factor for the use of thin wire is the wire wear and survivability after transit through the cutting area of the saw. Thinner diameter wire allows a greater number of cuts per centimeter of mounted block, creating additional wire passes, contact, and wear on the wire. Most double table and double mount saws contain too much silicon to cut at high feed rates with thin wire, with the additional complication that thinner wire can transmit any cutting defects to adjacent mounts increasing saw defects. Initial test cutting performance on current equipment is unacceptable at 160  $\mu\text{m}$  wafer thickness. The saw manufacturer recommends lowering the temperature and density of the slurry, as well as lower table speed, which would impact production speed and costs. The cleaning performance of 160  $\mu\text{m}$  thick wafers is also unacceptable on our present equipment, with a significantly higher breakage rate. Therefore, we opted to purchase and install a new generation single table saw designed for cutting thin wafers using thin wire, Meyer Burger DS264, and examine alternate cleaning tools.

Also, slurry and its cutting performance to reduce wire wear was examined through testing of a water based slurry (as opposed to polyethylene glycol, PEG, based slurries), where heat removal, viscosity, and lubricity can be tailored independently of one another.

#### Cutting with 120 $\mu\text{m}$ thick wire

An initial twenty-three cuts were completed using 120  $\mu\text{m}$  wire to produce 200  $\mu\text{m}$  thick wafers. We also completed 9 cuts using 120  $\mu\text{m}$  wire to produce 180  $\mu\text{m}$  thick wafers. The initial wafering yields with the 120  $\mu\text{m}$  diameter wire were poor as a result of an adhesive problem. Once this was solved the results (for both 200 and 180  $\mu\text{m}$  thicknesses) were encouraging with most performance parameters (yield, thickness variation, etc.) statistically equivalent to the production yields for 200  $\mu\text{m}$  thick wafers using 140  $\mu\text{m}$  thick wire.

The Meyer Burger DS264 trial was compared with an HCT E500 SD-B and a Meyer Burger DS262C. The results of that comparison are shown in Table 3.1 below. The saw performance may have been better in the production trial had the slurry quality been controlled better. Several slurry samples taken during the trial showed elevated levels of fine particles in the slurry.

A trial of ten cuts was conducted using 120  $\mu\text{m}$  diameter wire, cutting 160  $\mu\text{m}$  wafers. The Average Total Thickness Variation (TTV), deviation of thickness, standard deviation of TTV, and number of broken wafers after cleaning was higher than normal when compared to cuts done at 180  $\mu\text{m}$  and 200  $\mu\text{m}$  thicknesses on the same saw.

Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

A Systems Class Application

| Item               | DS 264 |

|--------------------|--------|

| Yield              | 0      |

| % Thick            | ++     |

| % Thin             | ++     |

| % Saw mark groove  | --     |

| % Saw mark step    | --     |

| % TTV              | ++     |

| % Chips            | 0      |

| % Cracks           | --     |

| % Holes            | 0      |

| % Breakage         | ++     |

| % Glue             | 0      |

| % Wire break       | 0      |

| % Cassette broken  | --     |

| % Cassette thick   | 0      |

| % Missing          | 0      |

| Thickness st. dev. | ++     |

| TTV                | --     |

| TTV st. dev.       | ++     |

**Table 3.1:** Meyer Burger DS264 wire saw performance vs. HCT E500SD-B and Meyer Burger DS262C (++ favorable, -- unfavorable, 0 no statistical significance)

Four cuts were completed using slurry containing silicon carbide with an average particle size of 8  $\mu\text{m}$  in an effort to decrease kerf loss. No benefit was observed using the smaller particle size slurry. Cutting efficiency appears to be reduced with higher cutting temperatures and increased bow in the web during the cuts.

In an effort to reduce silicon waste across the saw room and with the inability for older saws to handle 120  $\mu\text{m}$  wire, 130  $\mu\text{m}$  wire from Tokusen USA was tested with three different elongation specifications – 2.3, 2.5, 2.7%. Testing indicated a decreased likelihood of wire breaks with the higher elongation specification. A complete conversion of the saw room took place during the period of this contract. Additional testing was carried out to certify wire production from two different Bekaert plants for 120  $\mu\text{m}$  wire.

After setup of new recipes in the sizing saws, brick grinders, and wire saws, ten development cuts have been completed on 156mm square wafers at 180 $\mu\text{m}$  thickness. Results are mixed with yields ~12% lower than the baseline production yield for 125mm square, 200  $\mu\text{m}$  thick wafers. During development, a preliminary wire saw recipe was determined along with a non-alkaline, ICT-compatible cleaning process. Key process inputs affecting wafer cleaning have been identified, and control of these inputs is being established.

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

### Brick grinding to improve wafer strength and reduce breakage yields

Experimentation indicated that both wafering and cell line mechanical yields can be improved by machining the brick faces to remove block cutting damage before wire sawing. We were able to improve the wafer strength (as determined by a 4-beam bending test) from ~7N for non-ground bricks to ~12N for the finely ground bricks.

A focused improvement effort continued to reduce wafer chip defects and increase the wafer strength. Specific items included:

- Improvements in wafer quality in regards to wafer total thickness variation (TTV) and thickness

- Purging of all damaged cassettes and the establishment of a cassette management system

- Modifying the demounting acid bath temperature and concentration to improve separation of wafers from mount and reduce breakage

Destructive wafer strength tests were performed on wafers cleaned in the Lab (low alkaline clean), Elma (NaOH clean), RENA (ultrasonic + detergent clean), and RENA-ICT (acid based etch) for comparison (See Table 3.2). The acid etched wafers were weaker than the wafers cleaned through ELMA (NaOH). This can be partially explained by the damage removal and micro crack tip widening in the NaOH-based ELMA process. We did not see any significant difference in wafer strength between those cleaned in RENA versus Lab cleaned. As expected, the thinner wafers deflected more than the thicker wafers, but also broke at lower loads. No conclusions can be made about the strength of Mono<sup>2</sup>™ vs. multi in this test.

**Table 3.2:** Mechanical results of cleaning experiment

| Test Date | Lot #   | Wafer Thk | Cleaning    | Multi/Mono <sup>2</sup> (mm) | Deflection | Breaking Load(N) |

|-----------|---------|-----------|-------------|------------------------------|------------|------------------|

| 5/22/2008 | 104665  | 200µm     | Not Cleaned | Multi                        | 7.46±1.6   | 8.0±2.0          |

| 5/15/2008 | 104429  | 200µm     | Acid Clean  | Multi                        | 8.1 ± 0.7  | 8.7 ± 1.5        |

| 5/15/2008 | 104429  | 200µm     | ELMA        | Multi                        | 9.7 ± 1.1  | 10.8 ± 2.6       |

| 5/15/2008 | RQ1     | 160µm     | RENA        | Mono <sup>2</sup>            | 10.9 ± 1.4 | 5.7 ± 1.3        |

| 5/15/2008 | 103857L | 160µm     | Lab         | Mono <sup>2</sup>            | 10.3 ± 1.4 | 5.2 ± 1.0        |

| 5/15/2008 | 108357L | 160µm     | ICT*        | Mono <sup>2</sup>            | 15.3 ± 3.0 | 5.9 ± 0.9        |

### Integrated demounting and cleaning

After initial tests indicated tank and cassette based washing was not capable of high yield with thin wafers, BP Solar procured new automated equipment for pre-washing, in-line washing, and wafer separation. Several development periods were needed to establish proper cleaning and demounting chemistry, proper setup, operation, and maintenance periods for the wafer separator, and process cleaning conditions for in-line cleaning.

BP Solar originally used a steel recoverable wire saw mounting plate but opted to a single use glass-filled epoxy plate for ease of operation, decreased labor requirements, and high reproducibility and consistency of mounting. With further thin wafer testing, the wire

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

saw manufacturers recommended a retest of steel mounting plates versus epoxy. A test of these steel beams resulted in a 1% improvement in wafer and cell yield, but required significant development of the demounting, cleaning, and recovery process for these steel beams to eliminate previous problems and operator hazards. An improved recovery process was developed during the course of this contract.

A low foaming detergent is under test as an ICT compatible wafer cleaning process. Laboratory testing had been successful, so a month-long cleaning trial was undertaken to evaluate the cleaning process in a production environment. The cell line efficiency, breakage and number of stained wafers did not show any significant difference between the two processes. The foaming issue was successfully eliminated. However, after a relatively short bath life there were certain lots that this detergent had trouble cleaning. With this reduced bath life, the cost per wafer is about four times the cost of the caustic process, but required to produce ICT-compatible wafers.

### Water based slurry cutting trials

Initial water-based slurry cutting trial was completed in three cuts performed with three different viscosities:

- The first cut used low viscosity slurry, during which wafers were sliced in half and fell from partially cut bricks at 61 mm into the cut, indicative of severe wire skips. The bowing of the wire web appeared high, indicating inefficient cutting. Many wafers fell at the end of the cut, and the end wafers cracked off.

- In the second cut with intermediate viscosity, wire bow appeared lower, but many wafers fell near the end of the cut, except where an endplate remained.

- The third cut had high viscosity and end plates on #1 and # 2 side. Unfortunately, there was a wire break at 104 mm into cut. Many wire skips were observed at this point, with bow in the web at ~5 mm. At 116 mm many wafers were observed falling down due to wire skips. Many wafers fell at the end of the cut. Wafers near the end plates and small gaps between bricks did not fall.

Altogether, the experiment was not successful and indicated both the mounting adhesive needed to be altered (wafers falling at end of cut) and the slurry reformulated to increase cutting efficiency. It was also noticed that a significant force to the wafers falling off the mount during cutting was due to hydrogen bubbles created between the wafers bowing them apart. The hydrogen forms in a reaction with the water-based carrier and the silicon swarf generated during cutting.

A second trial was run with water-based slurry, aimed at suppressing hydrogen formation during the cut. Two cuts resulted in the following conclusions:

- Need to determine how much surfactant is required for proper formulation

- Epoxy of sufficient bond strength and water-tolerance that survive under these cutting conditions

- The water-silicon reaction to generate hydrogen creates over-the-road transport issues for slurry recovery, the current method of freezing slurry is not time or cost effective

- A lower level of hydrogen suppressant reduced premature detachment of wafers for the mounting beam

- A carrier formulation to tolerate a higher kerf loading

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

### Task 4: Cells and Contacts

The goals of Task 4 were directed toward improvements in cell fabrication to utilize our Mono<sup>2</sup>™ wafer technology while driving performance improvement and cost reduction through thin cell processing, emitter improvement, advanced metallization, back contact cells, and device modeling and optimization. Each of these focus areas comprise subtasks and our efforts and results are described below. Finally, a section is added focusing on characterization of Mono<sup>2</sup>™ as this occupied significant resources during the second year of the program.

#### Thin Cell Processing

The aim objective to develop cell processes and materials required to move from the industry standard 200um wafer thickness toward 100um wafer thicknesses. Specific areas of focus at BP Solar were on iso-chemical texturing to improve light collection and minimize thickness reduction during the saw-damage removal process and qualification of low-bow Al-BSF paste materials and processes to minimize wafer deformation and yield loss after co-firing. Taken together these process changes would enable transition from 125mm, 200um wafers to 156mm, 180um wafers.

#### Iso-chemical Texturing

Iso-chemical texturing (ICT) process development was performed using our Frederick, MD, production facility with a RENA InTex prototype process tool. Activities focused on three principle areas efforts;

1. Process window definition around key parameters;

2. Cosmetic and reliability performance of modules with ICT cells;

3. Pilot production to validate performance of cells with ICT in our Frederick, MD, production facility.

Additionally, high yield of 99.5% was demonstrated at small volumes for 160um thick wafers.

Process window definition focused on assessing the impact of etch depth, etch process temperature, and wafer manufacturer on the cosmetic and electrical performance of ICT cells completed in our production facility. Results for the impact of etch depth is shown in Table 4.1. The 4.2um etch depth is consistent with Rena's recommended process target.

**Table 4.1.** Cell performance as a function of ICT etch depth

| Etch Depth<br>( $\mu\text{m}$ ) | L-a-b Color<br>(a-scale) | Efficiency<br>(%) | $I_{sc}$<br>(A) | $V_{oc}$ | FF    | n-factor |

|---------------------------------|--------------------------|-------------------|-----------------|----------|-------|----------|

| 3.5                             | 16.8                     | 14.41             | 5.17            | 0.601    | 0.725 | 1.26     |

| 4.2                             | 16.1                     | 14.47             | 5.16            | 0.600    | 0.730 | 1.22     |

| 4.9                             | 13.4                     | 14.41             | 5.17            | 0.601    | 0.725 | 1.23     |

| 5.3                             | 12.8                     | 14.47             | 5.20            | 0.601    | 0.724 | 1.25     |

| 6.3                             | 12.1                     | 14.33             | 5.15            | 0.600    | 0.725 | 1.28     |

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

In Table 4.2 the impact of bath temperature on etch rate and performance is shown.

**Table 4.2.** Cell performance as a function of ICT etch temperature

| ICT Temp (C) | Etch Rate (μm/min) | L-a-b Color (a-scale) | Efficiency (%) | Isc (A) | Voc (mV) | FF   | n-factor |

|--------------|--------------------|-----------------------|----------------|---------|----------|------|----------|

| 5.5          | 0.95               | 14.7                  | 14.74          | 5.21    | 599      | 73.9 | 1.25     |

| 7.5          | 1.11               | 11.9                  | 14.76          | 5.22    | 600      | 73.7 | 1.22     |

| 9.5          | 1.30               | 8.6                   | 14.17          | 5.19    | 598      | 71.2 | 1.26     |

| 12.0         | 1.48               | 9.8                   | 14.43          | 5.21    | 599      | 72.3 | 1.25     |

| 15.0         | 1.97               | 7.4                   | 14.63          | 5.18    | 599      | 73.6 | 1.25     |

Because ICT relies on the residual wire saw damage to form texture in the wafer surface, the wafer source and associated sawing and cleaning process is assumed to impact the ICT process. Table 4.3 summarizes these results.

**Table 4.3.** Cell performance as a function of wafer supplier

|                   | Etch Depth (microns) | L-a-b Color (a-scale) | Efficiency (%) | Isc (A) | Voc   | FF    | n-factor |

|-------------------|----------------------|-----------------------|----------------|---------|-------|-------|----------|

| <b>BP Solar</b>   | 4.0                  | 13.4                  | 14.23          | 5.145   | 0.598 | 0.723 | 1.28     |

| <b>Supplier 1</b> | 4.0                  | 14.6                  | 14.28          | 5.133   | 0.599 | 0.726 | 1.26     |

| <b>Supplier 2</b> | 4.0                  | 14.9                  | 14.44          | 5.173   | 0.602 | 0.724 | 1.26     |

| <b>Supplier 3</b> | 4.2                  | 17.0                  | 14.08          | 5.149   | 0.596 | 0.716 | 1.39     |

| <b>Supplier 4</b> | 4.0                  | 15.1                  | 13.97          | 5.106   | 0.594 | 0.720 | 1.35     |

| <b>Supplier 5</b> | 4.1                  | 18.1                  | 14.56          | 5.243   | 0.603 | 0.720 | 1.26     |

The ICT process was generally found to be robust with regard to the tested parameters and wide process windows were identified for the start of production.

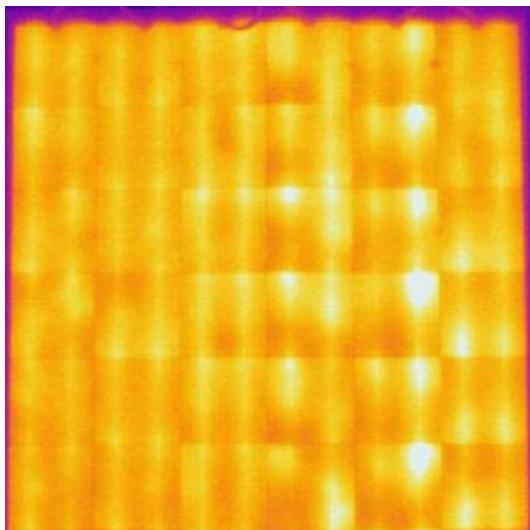

Before transitioning to ICT texturing in production in our Frederick facility, a pilot of ~6,000 cells was conducted to determine the impact of ICT on module power (Figure 4.4).

- Prior to running the pilot, the co-optimization of diffusion and co-fire settings showed a 0.4% absolute efficiency improvement at cell test for ICT relative to cells featuring BP Solar's standard planar NaOH-etch. This gain was due to an increase in Isc while Voc and FF showed decreases.

- When applying these conditions to the pilot run an efficiency increase of only 0.2% was seen relative to the NaOH-etch control. This was largely due to problems with front print and with replicating optimal temperature profile for co-fire and was primarily seen as decreased FF relative to the co-optimization results.

- Modules built in the pilot trial had an average of ~3W lower power than the Na-etch control. The key factor in this underperformance a relative gain of Isc for the NaOH-etched cells upon encapsulating.

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

## A Systems Class Application

**Table 4.4.** Cell and module performance for ICT cells vs. NaOH planar etched baseline

| Group              | Bin   | Module |        |        |        | Bare Cell |        |        |

|--------------------|-------|--------|--------|--------|--------|-----------|--------|--------|

|                    |       | Pmax   | FF     | Voc    | Isc    | FF        | Voc    | Isc    |

| ICT                | Bin 5 | 168.5  | 0.718  | 43.45  | 5.40   | 0.751     | 0.6015 | 5.324  |

|                    | Bin 6 | 173.0  | 0.726  | 43.61  | 5.46   | 0.7621    | 0.6053 | 5.3677 |

|                    | Bin 7 | 177.0  | 0.731  | 43.98  | 5.51   | 0.7683    | 0.6099 | 5.414  |

| NaOH               | Bin 5 | 173.4  | 0.733  | 43.70  | 5.41   | 0.7687    | 0.6046 | 5.167  |

|                    | Bin 6 | 177.3  | 0.742  | 44.00  | 5.43   | 0.7787    | 0.6094 | 5.211  |

|                    | Bin 7 | 180.0  | 0.746  | 44.31  | 5.44   | 0.785     | 0.6137 | 5.249  |

| ICT vs. NaOH %diff | Bin 5 | -2.83% | -2.05% | -0.57% | -0.18% | -2.30%    | -0.51% | 3.04%  |

|                    | Bin 6 | -2.43% | -2.16% | -0.89% | 0.55%  | -2.13%    | -0.67% | 3.01%  |

|                    | Bin 7 | -1.67% | -2.01% | -0.74% | 1.29%  | -2.13%    | -0.62% | 3.14%  |

On the basis of ICT performance with our Frederick process flow along with the change in BP Solar's business plans, the decision was made not to implement ICT in production.

### Low-Bow Al-BSF Paste

Assessment of low-bow paste offerings from two major manufacturers, including Ferro, was completed at both the laboratory scale and pre-production pilot scale. Verification of module stability using cells made with each low-bow paste was completed through BP Solar's Q6100 reliability test with each successfully passing the accelerated aging testing. In a pre-production pilot run in Frederick, MD, excessive cell breakage was observed during module assembly for cells made using the Ferro low bow paste resulting in lower than expected yield. Additionally, slight performance reduction was observed relative to the baseline process. Ultimately, because of the change in BP Solar's business plans along with not making a conversion to thinner cells, low-bow paste was not implemented in BP Solar's Frederick facility.

### Advanced Emitter

The objective of this subtask was to develop design and process modifications for emitter formation and contacting to improve "blue response" and open circuit voltage. This effort focused on two approaches – shallow emitter and selective emitter.

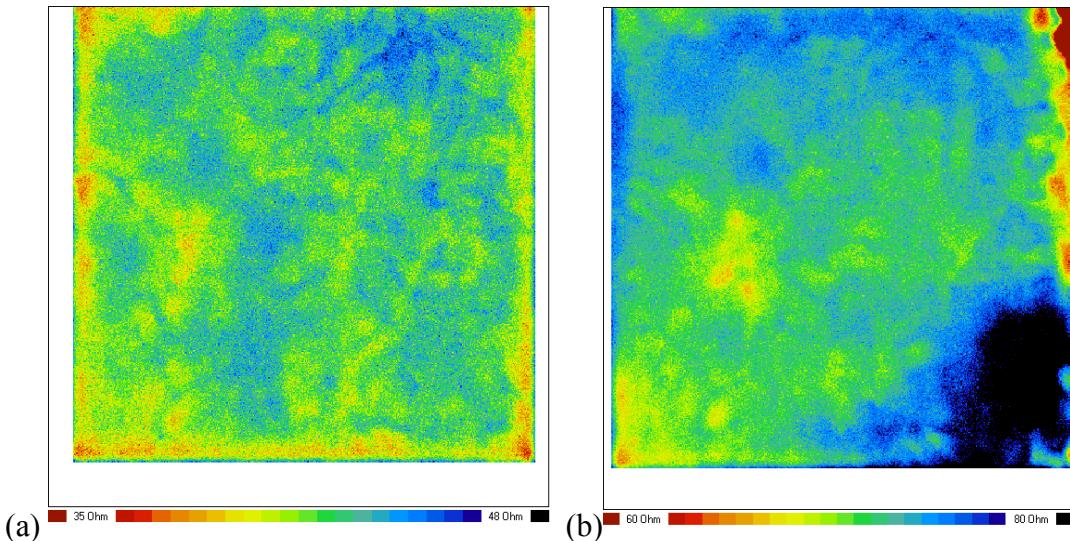

### Shallow Emitter

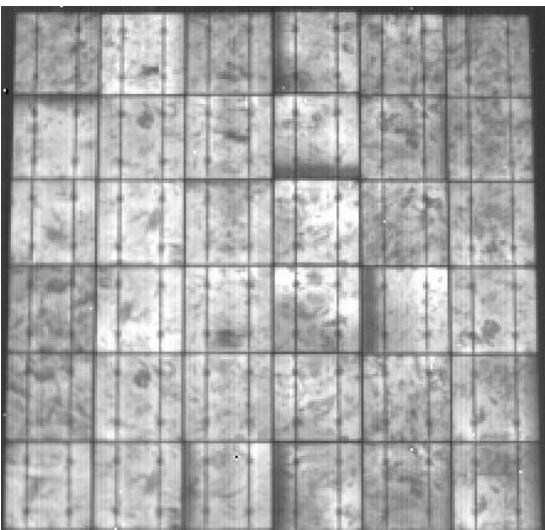

Work initially focused on the improvement of emitter performance by forming a "shallow" emitter with a higher sheet resistance than our standard 45 ohms per square. This effort would consist of diffusion process definition, contact redesign, and Ag paste and co-fire modification. Work at BP Solar principally focused on modification of our existing belt-diffusion process to adjust the emitter sheet resistance target while working with paste vendors to identify pastes that would contact 80 ohms per square emitters. The principal challenge for the paste was to avoid shunting while not sacrificing contact resistance. In the course of the work several candidate pastes were identified. However, the belt diffusion equipment in our Frederick facility was found to have inadequate process control to form a uniform, high quality shallow emitter. Figure 4.5 shows sheet resistance for our standard 45 ohms per square emitter (a) and for 75 ohms per square emitter (b). These are representative of the change in emitter sheet resistance uniformity encountered with transitioning to a higher sheet resistance. For this reason, selective emitter was pursued as a backup option.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

**Figure 4.5.** Sheet resistance uniformity for belt-diffused cells with 45 ohms per square (a) and 75 ohms per square (b) sheet resistance targets

### Selective Emitter

A dopant-ink based selective emitter formation process was evaluated for possible licensing from a technology developer. The results were promising for application to a baseline mono cell process with >0.5% absolute efficiency improvement demonstrated.

### Advanced Metallization

The objective of the advanced metallization subtask was to evaluate and select for further development non-screen print metallization techniques that are capable of printing narrow, high aspect ratio lines in a non-contact manner. In the course of the investigation four deposition techniques were evaluated – extrusion, aerosol jet, inkjet, and laser transfer. Most of these options were evaluated under non-disclosure agreements, so the partner identity can not be revealed. Co-extrusion was evaluated with our subcontractor, PARC. Of these options aerosol and inkjet printing suffered from an inability to rapidly deposit thick materials. Laser transfer printing was at a very early stage of development and its principle advantage was being non-contact. Line width and aspect ratio were not obviously superior to advanced screen-print. Only PARC's co-extrusion technology was compelling for near- to medium-term applications.

Over the course of the program PARC independently optimized their extrusion nozzle and materials, enabling the printing of fine lines with exceptional geometry. At the conclusion of year 2 activities, 50um wide and 50 um tall lines were demonstrated. Additionally, an efficiency increase of 1% absolute was demonstrated relative to our baseline process in a controlled experiment. The performance improvement was achieved principally through improved  $I_{sc}$  and fill factor with an attendant improvement in  $V_{oc}$ .

## Back Contact Cells

### Laser-Fired Back Contacts

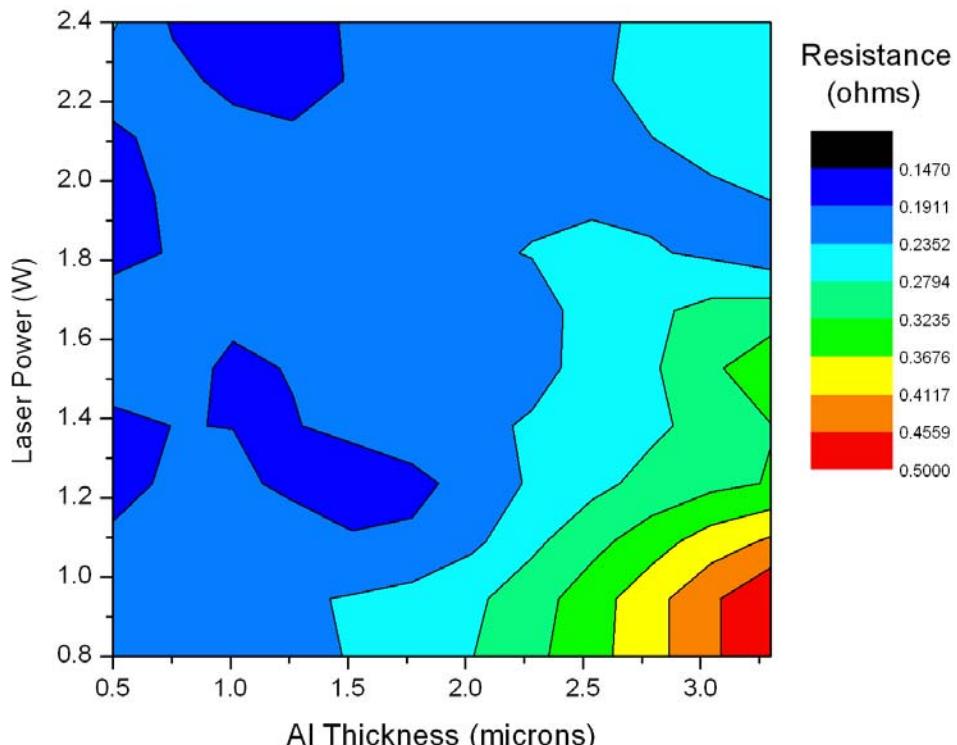

Fraunhofer ISE has demonstrated silicon solar cell conversion efficiencies as high as 21.8% by laser-firing localized aluminum rear contacts through a dielectric layer of thermally grown silicon dioxide. In a series of experiments, we formed localized contacts to p-type Si wafers ( $1.5 \Omega\text{-cm}$ ) by laser-firing aluminum through a dielectric passivation layer of intrinsic amorphous silicon (a-Si:H). In these experiments, the thickness of the aluminum was varied from 0.5 to 3.3  $\mu\text{m}$ , and the aluminum was laser-fired through 80 nm of intrinsic a-Si:H using a Nd:YAG laser with the power varying from 0.8 to 2.4 Watts.

As shown in the contour plot of Figure 4.6, a low series resistance was obtained over a wide range of aluminum thicknesses and laser powers. For the lowest laser power, the series resistance increased rapidly as the aluminum thickness increased since the energy density of the laser beam was insufficient to melt the thick aluminum film and fuse it through the a-Si:H into the Si wafer. Other experiments have shown that it is easier to form aluminum laser-fired contacts through a-Si:H than through other dielectrics such as silicon dioxide and silicon nitride. Moreover, a-Si:H has been shown to be an excellent passivation layer that can be deposited at relatively low temperatures ( $< 200^\circ\text{C}$ ).

**Figure 4.6.** Contour plot of laser power vs. Al thickness for laser firing Al contacts through a-Si:H on a p-type Si wafer.

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

In some cases a high resistance contact can result after laser firing of aluminum through a dielectric due to the removal of all the metal in an annular region near the outer periphery of the laser-fired region. By probing the electrical resistance from the front of the sample to an ohmic contact on the rear, we observe that the central region of the laser-fired region can make a good ohmic contact to the silicon wafer, but the presence of the metal-depleted annular region creates a high resistance path to the metal surrounding central region of the laser-fired region. A good low-resistance contact can often be obtained by depositing a 2<sup>nd</sup> layer of the metal.

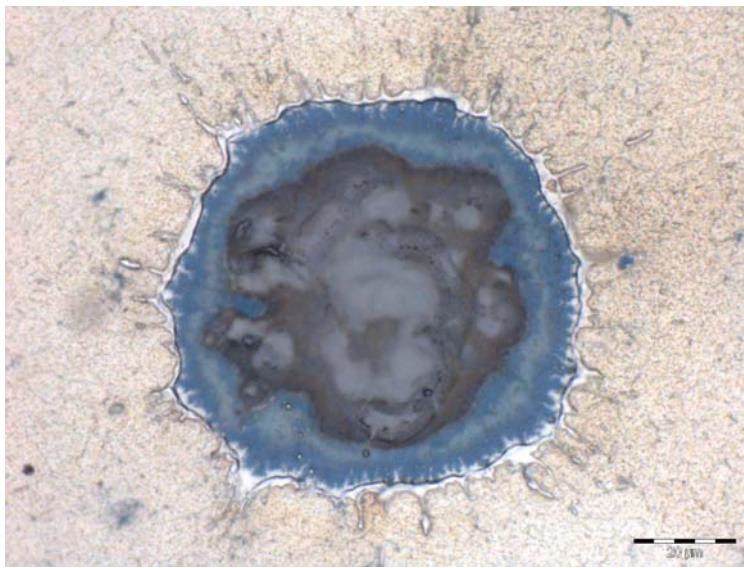

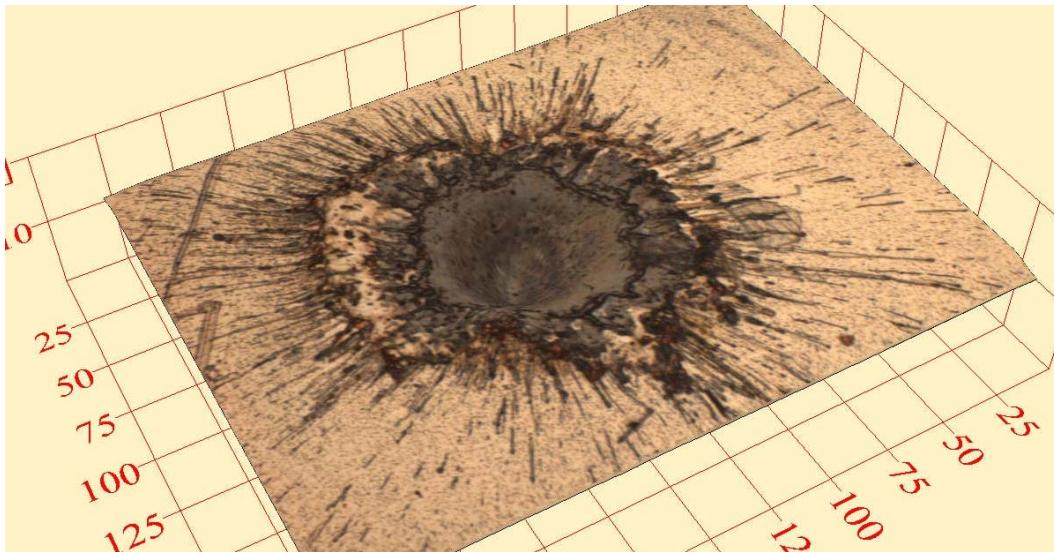

When high resistance laser-fired contacts are examined under a microscope, one often observes a blue dielectric ring just outside a crater formed by the ablation of silicon (see Figure 4.7). In this case a laser pulse was incident on a silver film (~ 1  $\mu\text{m}$  thick) that was deposited on top of a doped silicon wafer coated with a layer of silicon nitride (~ 80 nm thick). There are three distinct regions apparent in the figure. In the central region one can see a crater (~ 2  $\mu\text{m}$  deep) formed by laser ablation of the silicon. Just outside the crater, an annular bluish region is evident where the silicon nitride layer is exposed by laser ablation of the silver layer. Just outside this blue dielectric ring, one can see evidence of splattered silver streaking out from the laser-fired region. Thus, the contact exhibits a very high resistance since there is no conductive path from the surrounding silver film to the doped silicon in the crater.

**Figure 4.7.** A photograph of a laser-fired contact for a silver film deposited on a silicon wafer coated with silicon nitride.

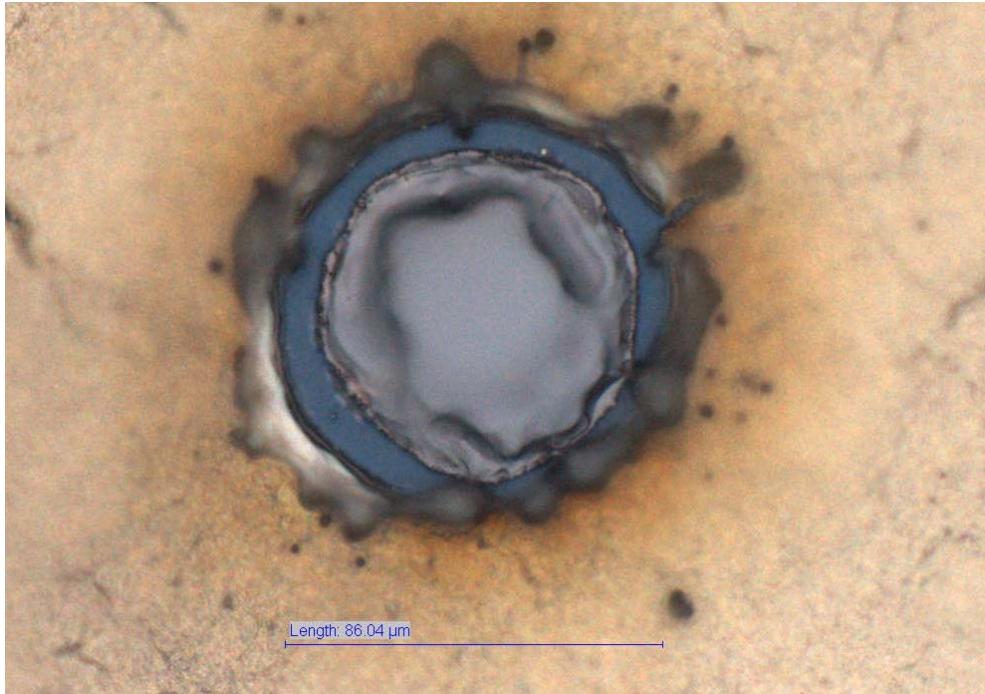

However, under some laser firing conditions, it is possible to obtain high quality, low resistance contacts. The photograph in Figure 4.8 shows a type of laser-fired contact that can exhibit a low resistance. In this case one observes a significant amount of material splattered across the dielectric ring region. Since this splattered material is a mixture of silver and doped silicon, it is very conductive and forms a number of conductive paths for current to flow between the doped silicon crater and the surrounding silver film. Splattering can occur due to phase explosion when the laser beam superheats the molten

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

silicon, and it becomes more energy efficient to explosively eject large molten clusters rather than evaporate atoms.

**Figure 4.8.** A photograph of a laser-fired silver contact where significant spattering of material occurred. The silver was deposited on a silicon wafer coated with silicon nitride

It is also possible to choose laser firing conditions where a low-resistance contact can be formed where the molten rim of the crater is pushed over the annular dielectric region (see Figure 4.9). In this photograph one can see that a portion of the crater rim covers the blue dielectric ring allowing the doped silicon to make a low resistance contact to the surrounding silver film.

Reaching Grid Parity Using BP Solar Crystalline Silicon Technology

A Systems Class Application

**Figure 4.9:** Photograph of a laser fired contact where the rim of the crater has been pushed across the blue dielectric ring (near the bottom right of the contact).

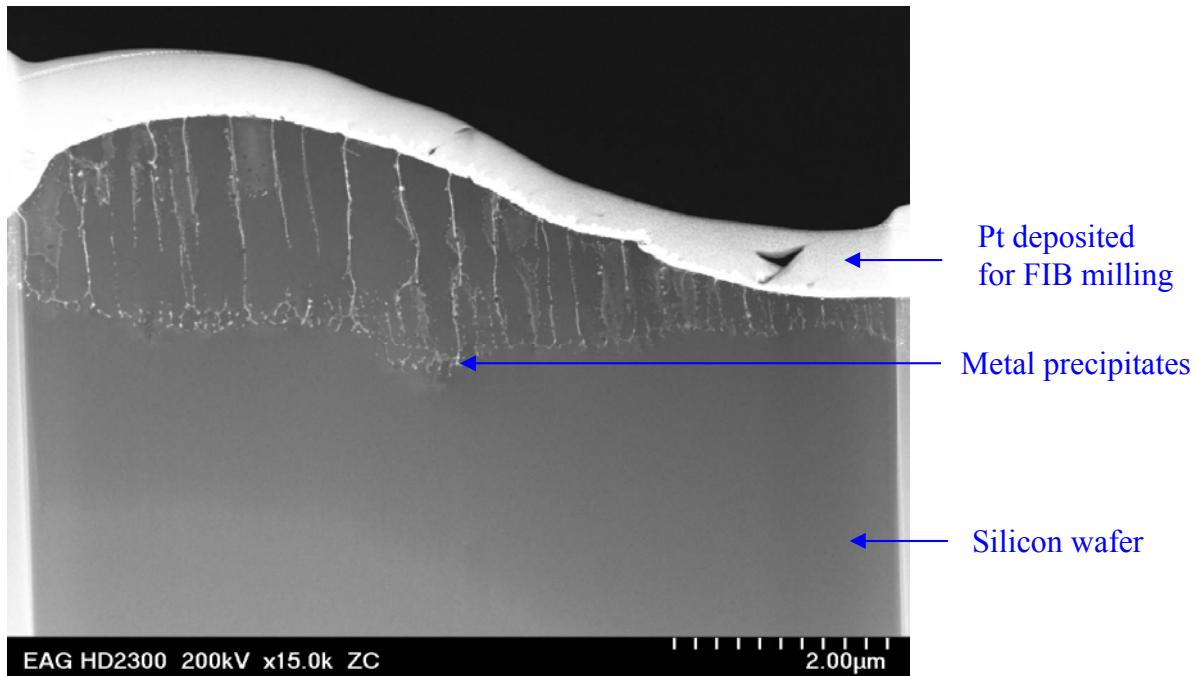

The Evans Analytical Group has analyzed the region under a laser-fired crater. The sample was prepared with the structure Ag/Al/SiN<sub>x</sub>/c-Si, and the laser ablated almost all the Ag/Al/SiN<sub>x</sub> from the surface leaving a crater about 1 - 2 microns deep and ~ 100 μm in diameter. There is clear evidence that the silicon melted to a depth of ~ 0.5 – 2.0 microns under the crater bottom and a number of filaments are evident extending to the bottom of the molten zone (see Figure 4.10). The filaments are rich in both Ag and Al indicating that the metals melted and were mixed together before penetrating the silicon. The filaments may be due to the accumulation of metals at grain boundaries within a re-crystallized region. Metal precipitates are also evident at the bottom of the molten zone.

# Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application

**Figure 4.10.** STEM image of the crater region at the bottom of a laser-fired contact

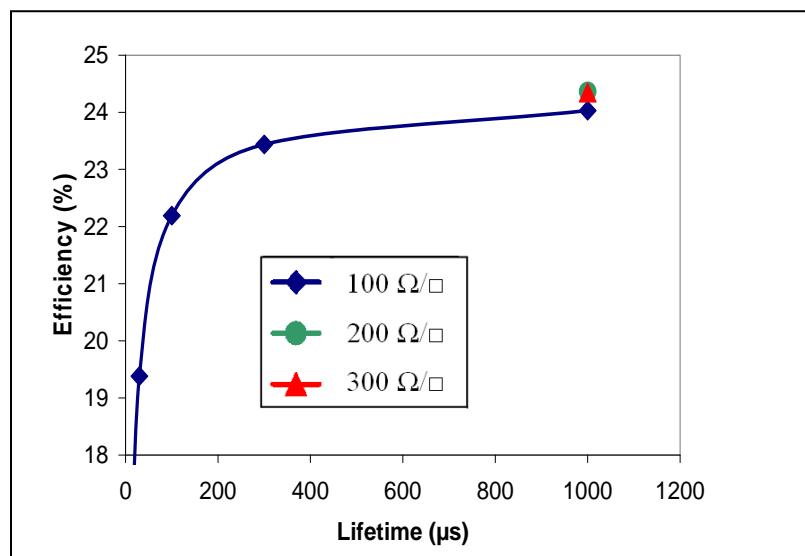

## Modeling of Back-Contact Solar Cells

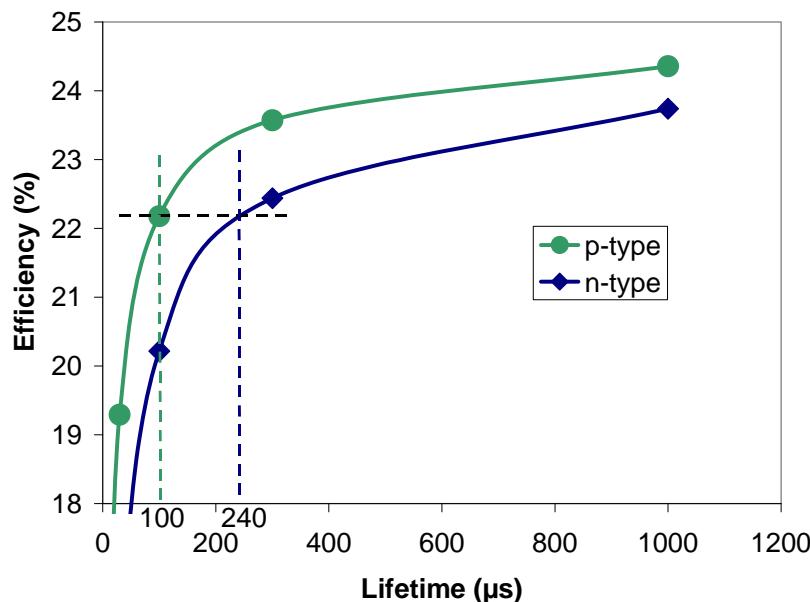

Georgia Tech has been performing some modeling for us on back contact cells where we assume that most of the rear surface is coated with a shallow emitter and the base and emitter rear contacts are made through localized  $n^+$  and  $p^+$  regions. The modeling shows that an efficiency of 24% can be obtained with p-type Si (1 ohm-cm, bulk lifetime = 1 ms) if the spacing of the localized contact regions (each 100 microns in diameter) is about 0.5 mm (see Figure 4.11). The model also assumes that the front surface is textured and is coated with a well-passivated ( $S_{eff} = 3$  cm/s) silicon nitride antireflection coating.

**Figure 4.11.** Efficiency vs. lifetime for a back contact solar cell (when the lifetime was 1000 μs, the sheet resistance of the rear shallow emitter was varied from 100 to 300 Ω/□)

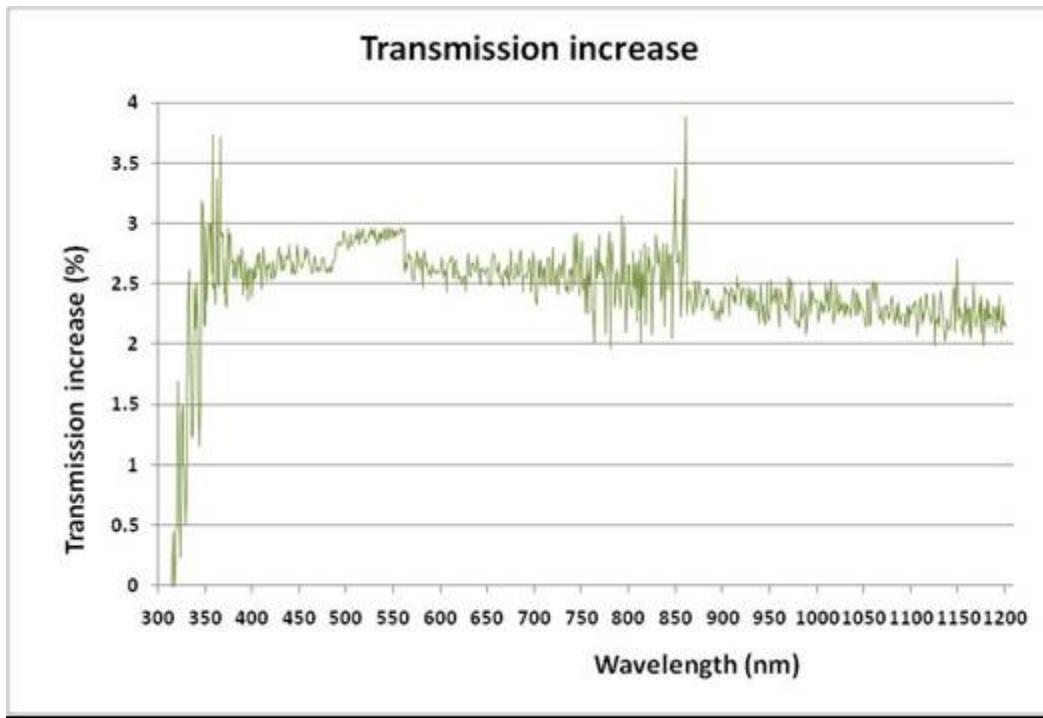

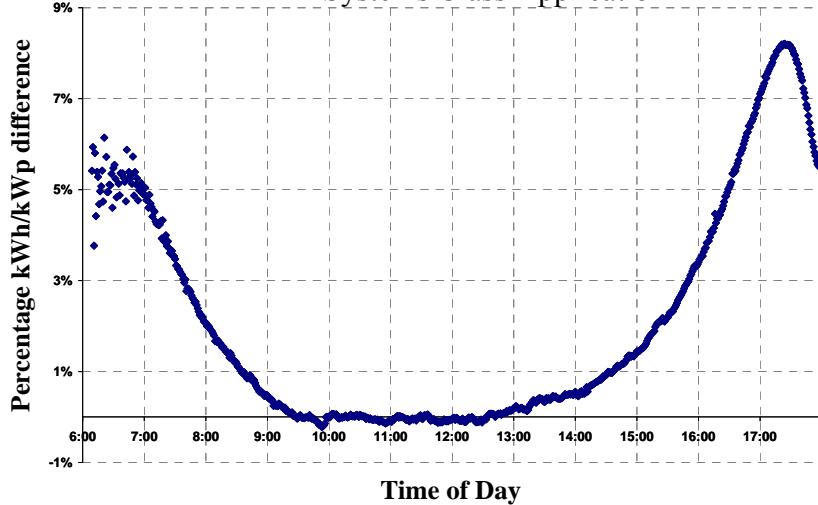

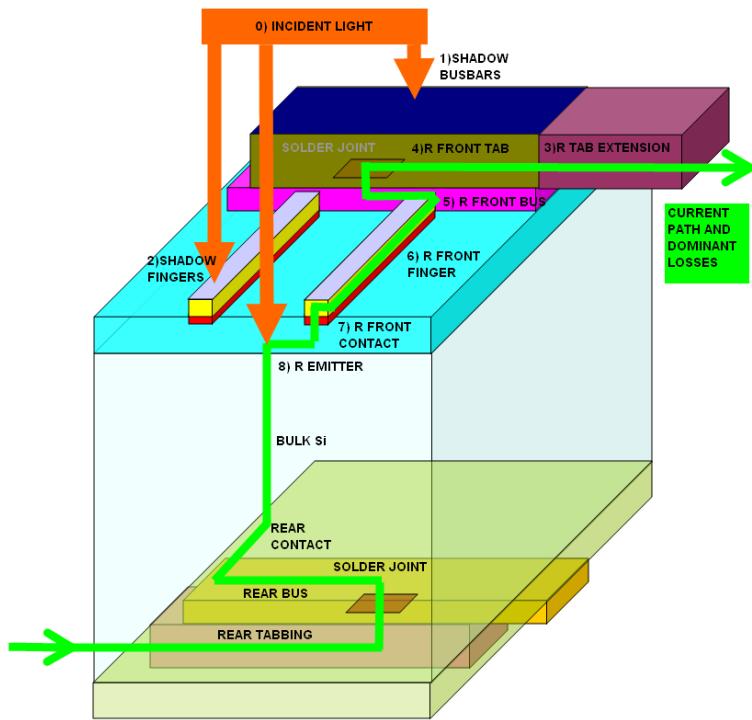

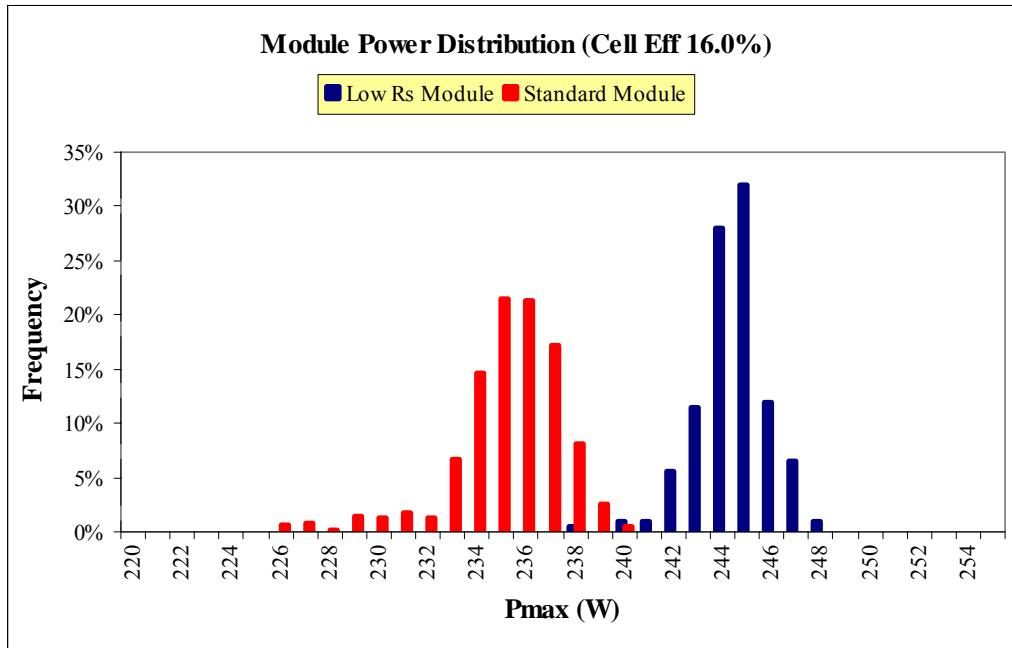

## Reaching Grid Parity Using BP Solar Crystalline Silicon Technology A Systems Class Application