# EUV Actinic Defect Inspection and Defect Printability at the Sub-32 nm Half-pitch

Sungmin Huh<sup>a</sup>, Patrick Kearney<sup>a</sup>, Stefan Wurm<sup>a</sup>,

Frank Goodwin<sup>a</sup>, Hakseung Han<sup>b</sup>, Kenneth Goldberg<sup>c</sup>,

Iacopo Mochi<sup>c</sup>, Eric Gullikson<sup>c</sup>

<sup>a</sup> SEMATECH 255 Fuller Road, Suite 309, Albany, NY 12203 USA

<sup>b</sup> Photomask Team, Samsung electronics, Ban-Wol, Hwasung, Kyunggi, 445-701Korea

<sup>c</sup> 2-400, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

## ABSTRACT

Extreme ultraviolet (EUV) mask blanks with embedded phase defects were inspected with a reticle actinic inspection tool (AIT) and the Lasertec M7360. The Lasertec M7360, operated at SEMATECH's Mask Blank Development Center (MBDC) in Albany, NY, has a sensitivity to multilayer defects down to 40~45 nm, which is not likely sufficient for mask blank development below the 32 nm half-pitch node. Phase defect printability was simulated to calculate the required defect sensitivity for a next generation blank inspection tool to support reticle development for the sub-32 nm half-pitch technology node. Defect mitigation technology is proposed to take advantage of mask blanks with some defects. This technology will reduce the cost of ownership of EUV mask blanks. This paper will also discuss the kind of infrastructure that will be required for the development and mass production stages.

## 1. INTRODUCTION

Over the past year, the interest of leading edge chip manufacturers has tangibly shifted towards the insertion of extreme ultraviolet lithography (EUVL) into production. This emphasis is increasing the pressure to resolve defect-free blanks, which remains one of the key challenges impeding EUVL insertion into manufacturing. The success of the industry's mask blank defect reduction effort critically depends on the timely availability of inspection tools that can precisely and reliably find ever smaller defects. SEMATECH's Mask Blank Development Center (MBDC) has provided the world's best defect inspection capability starting in 2003 with the Lasertech M1350 tool and continuing with the second generation defect inspection tool, the M7360, in 2006. Both of these tools have deep ultraviolet (DUV) light sources for defect detection: 48 nm wavelength for the M1350 and 266 nm wavelength for the M7360. However, to meet high volume manufacturing (HVM) requirements for sub-32 nm half-pitch (HP) patterning, the industry needs a third generation of defect inspection tools capable of finding defects  $\leq 20$  nm on mask blanks with a high capture rate and high blank throughput. In addition, these tools will also need to support extendibility assessments of low defect deposition technologies and the associated infrastructure development towards meeting 22 nm half-pitch defect specifications. SEMATECH operates an actinic inspection tool (AIT) at Lawrence Berkeley National Lab (LBNL) and a state-of-the-art Lasertec M7360 to support the development of inspection tools and reticle blanks to eventually meet HVM requirements. In this paper, we simulated the required defect sensitivity for the sub-32 nm HP [1-3] and have prepared an EUV mask blank, fabricated in SEMATECH's MBDC, to be inspected using the M7360 in the MBDC and the AIT at LBNL to compare their sensitivity. We prepared mask blanks with real phase defects and then compared detected images using M7360 and AIT to explain why we need an actinic inspection tool for the mass production of EUV mask blanks. Most of the cost of ownership (COO) of EUV masks depends on the defect-free mask blank cost. Consequently, defect mitigation technology using mask blanks with some phase defects should be developed to reduce mask blank cost in the mass production stage. In this paper, we propose what we need for defect mitigation technology. Finally, we will propose a possible defect inspection scheme and gab for EUV pilot line application [4].

## 2. MASK BLANK INSPECTION TOOL IN SEMATECH

A defect inspection tool for EUV mask blanks is the key enabler for may technology development activities, such as defect-free blank fabrication, cleaning, and mask handling. SEMATECH's MBDC has provided the world's best

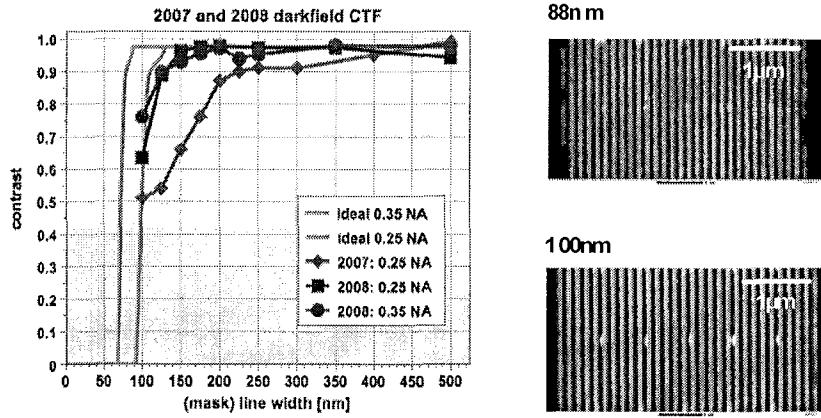

defect inspection capability first with the Lasertech M1350 tool using a 488 nm wavelength in 2003 and then with the second generation inspection tool, the Lasertech M7360, using a 266 nm wavelength. The lower wavelength of the M7360 greatly improves the detection capability of the M7360 compared to the M1350. However, there is a large gap if mask blanks for the 22 nm HP are to be supported. Improved sensitivity for smaller defects could be achieved with higher laser power, a shorter wavelength, and various technologies that can cover multilayer inspection for the 32 nm HP node. However the photon energy absorbed on the multilayer can damage reflectivity at EUV wavelengths, and DUV light sources cannot provide information on phase defects inside multilayer films. Substrate inspection can be supported with a DUV inspection tool based on current mask blank inspection tools. We need an at-wavelength inspection tool for multilayer inspection. SEMATECH has operated the AIT as a defect inspection tool and imaging tool at LBNL. Before 2008, only one zoneplate with a numerical aperture (NA) of 0.00625 on the mask was available for imaging. After upgrading in 2008, five user-selectable zoneplates were implemented, with magnification of 680, 907, and 1000X and NAs of 0.00625, 0.075, and 0.0875 on the mask. These NA emulate a 4X EUV scanner with NAs of 0.25, 0.3, and 0.35. It is now possible to study EUV mask technology down to the 22 nm HP without wafer printing using the upgraded AIT. Figure 1 shows the improvements in contrast and minimum resolution after the 2008 upgrade.

(a) Contrast improvement after the AIT upgrade in 2008

Figure 1. Results following the AIT upgrade

(b) Minimum resolution of AIT

### 3. EXPERIMENTAL

#### 3.1 Phase defect simulation

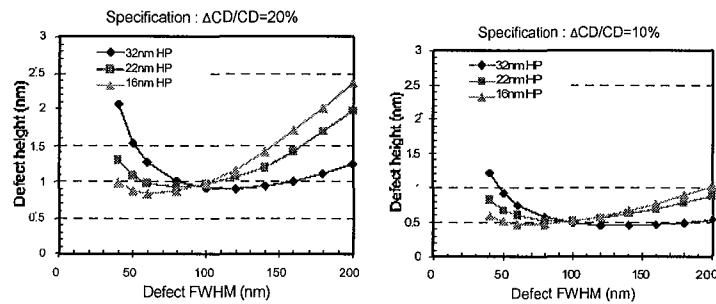

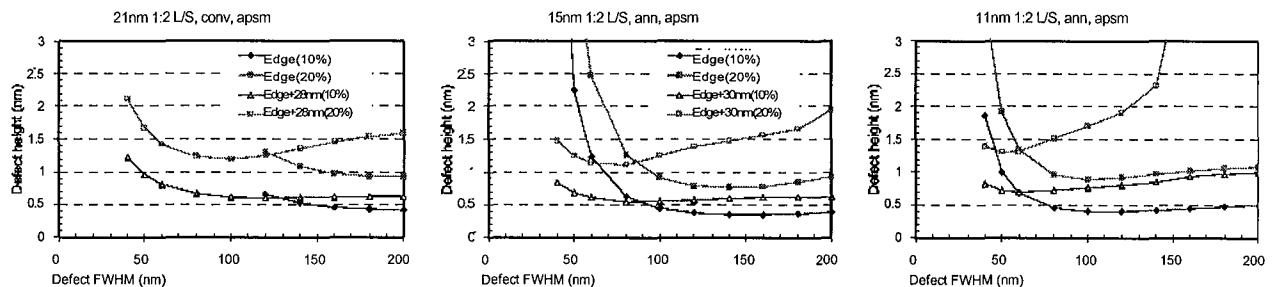

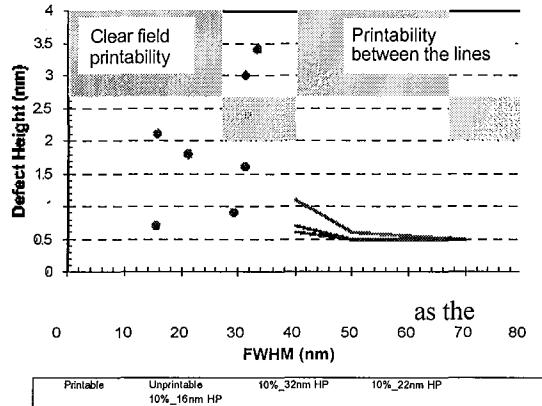

We simulated phase defect printability as a function of defect full width half maximum (FWHM) and height with patterns of 1:1 lines/spaces (L/S) and 1:2 isolated lines for the 32, 22, and 16 nm device nodes [5]. Table 1 shows the simulation conditions used. The simulations cover different mask types (binary mask/phase shift mask) and illumination conditions (conventional and annular). The multilayer profile is assumed to be congruent with the phase defect profile. If smoothing or decorating occurs during multilayer deposition, the simulation results may be different. We used a constant threshold model, and the resist effect was not considered in the simulation. The simulation results of phase defect printability for these 1:1 dense L/S and 1:2 isolated lines is shown in Figure 2. The defect printability criterion is 10% critical dimension (CD) variation in each line CD. The minimum defect FWHM we need to address is  $\sim 40$  nm at a height of  $0.5 \sim 1$  nm; the height of defect has a greater influence on CD variation than width of defect. If the phase defect is away from the main pattern, it also is less printable than when it is adjacent pattern. This means that phase defect specifications should be much more tight for dense patterns than isolated patterns. Inspection tools capable of detecting these types of substrate defects do not yet exist. Table 2

shows the specifications for an inspection tool for phase defects.

Table 1. Simulation conditions for defect printability

| Node                   | 32 nm                         | 22 nm                         | 16 nm                         |

|------------------------|-------------------------------|-------------------------------|-------------------------------|

| NA                     | 0.25                          | 0.35                          | 0.45                          |

| Lines:Spaces           | 32:32/21:42                   | 22:22/15:30                   | 16:16/11:22                   |

| Illumination Condition | Conventional ( $\sigma 0.5$ ) | Conventional ( $\sigma 0.5$ ) | Conventional ( $\sigma 0.5$ ) |

|                        | Annular ( $\sigma 0.3/0.5$ )  | Annular ( $\sigma 0.3/0.5$ )  |                               |

| Mask                   | Binary                        | Binary                        | Binary                        |

|                        |                               | Attenuated PSM                | Attenuated PSM                |

(a) Phase defect simulation for 1:1 L/S

(b) Phase defect simulation for 1:2 isolated line

Figure 2. The simulation of phase defect printability

Table 2. Required sensitivity for phase defect inspection.

| CD variation on wafer | 32 nm HP | 3 ranges of defect width [FWHM] |       |     |      |

|-----------------------|----------|---------------------------------|-------|-----|------|

|                       |          | 40~50                           | 50~70 | >70 |      |

|                       | 22 nm HP | 10%                             | 1.1   | 0.6 | >0.5 |

|                       |          | 20%                             | 1.7   | 1.2 | >0.9 |

|                       | 16 nm HP | 10%                             | 0.7   | 0.5 | >0.5 |

|                       |          | 20%                             | 1.2   | 0.9 | >1   |

|                       | 16 nm HP | 10%                             | 0.6   | 0.5 | >0.5 |

### 3.2 Comparison of the M7360 and AIT

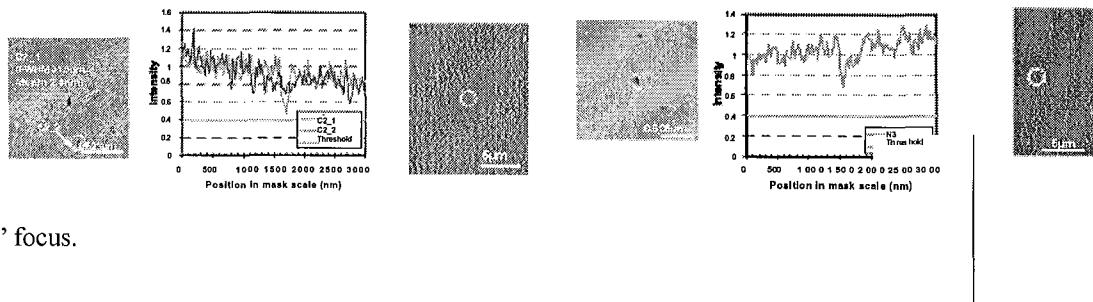

A test multilayer reticle blank was prepared in SEMATECH's MBDC and inspected using the M7360 at its most sensitive inspection condition to capture the smallest defect on the blank. This blank was then inspected with the AIT at LBNL using scanning and imaging mode. The images shown in Figure 3 demonstrate that the AIT can see details of the blank defect that are not detected by the M7360. The AIT shows that the scratch defect is composed of

a series of pit defects. The tool can capture any phase defect less than 1 nm deep. This means that an actinic inspection tool will need to detect this kind of small and shallow defect for pilot line production.

(a) AIT      (b) M7360      (c) AFM

Figure 3. Image comparison using the AIT and M7360

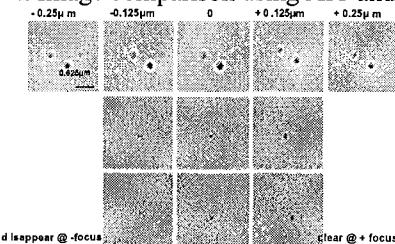

We inspected a total of 16 natural defects on EUV mask blanks using the M7360, AIT, and AFM to study the printability of real defects. Two examples are shown in Figure 4. If the intensity of a phase defect in the AIT is higher than the threshold, it will print on the wafer. We set the printable threshold value at 0.4 using the simulation results (section 2). The shape of the real defect is arbitrary and very different from the PDM and Gaussian profile in the simulations. Defect N3 in Figure 4(a) is 3.0 nm deep. However the aerial image signal is higher than the threshold value, which means that this defect is unprintable if it is on the clear field, not between the lines. Even though the depth of the C2\_1 defect in Figure 4(b) is shallower than N3, its intensity is almost down to the threshold value; therefore, this kind of phase defect will be printed. The AIT can detect the C2\_2, but the M7360 and AFM cannot. This defect will be unprintable in the open field. The depth of focus of phase defect printability in Figure 5 is more than 0.25 ~ 0.5  $\mu$ m, which is greater than the depth of the absorber pattern. The depth of focus of the phase defect will be different from the defect size and profile. Its size on the wafer gets smaller with “-” focus and larger

with “+” focus.

AIT cross sectional aerial image M7360

(a) N3 (FWHM 23.4 nm/depth 3.0 nm)

AIT cross sectional aerial image M7360

(b) C2 (FWHM 31.5 nm/depth 2.4 nm)

Figure 4. Image comparison using AIT and M7360

Figure 5. Defect printability as through focus

## 4. DEFECT MITIGATION TECHNOLOGY

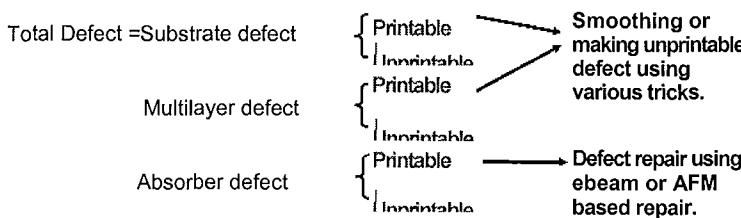

There are various defects in EUV masks such as substrate defects, multilayer defects, and absorber defects, as shown in Figure 6. As we discussed in simulating phase defects, defect printability is a function of not only the defect profile, but also the defect location. We need to categorize which kind of defect is printable using our database, but we need not worry about unprintable defects. In the International Technology Roadmap for Semiconductors (ITRS), the requirement for phase defect in HVM production is  $0.003/\text{cm}^2$ . However it will be very difficult to maintain a high yield with that defect level. This also will increase mask blank cost drastically. We must take advantage of mask blanks with some defects if we can make phase defects unprintable using defect mitigation technology. We can make a printable defect-free mask, not a defect-free mask with defect mitigation technology.

### 4.1 Phase defects under the absorber

A phase defect becomes increasingly more printable as it moves toward the middle of patterns and unprintable if it is under the absorber [6]. Figure 7 shows that the printability of phase defects with 49 nm width and 5.4 nm height. When the defect is on the space of the pattern, there is no depth of focus. However, if defect is under absorber, the depth of focus recovers up to 250 nm.

### 4.2 Phase defects in the clear field

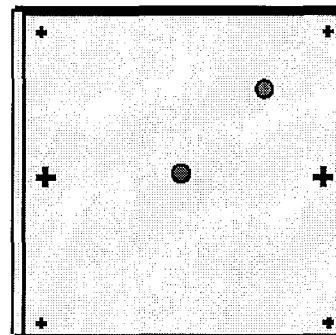

We can get information about 9 phase defects on the clear field using the AIT and AFM. If the location of phase defects is between the lines, the minimum defect FWHM that we need to worry about is  $\sim 40$  nm at a height of  $0.5 \sim 1$  nm with 10% CD variation. On the contrary, clear field printability increases the printable defect size to between 0.7 and 3.5 nm if the defect is far away from pattern. We need more real defect printability data to improve statistics and our understanding. If we can control the defect location, we turn a printable phase defect into unprintable defect using defect mitigation technology.

Figure 6. The species of defect in EUV mask

Figure 7. Phase defect printability position to absorber

Figure 8. Phase defect printability in clear field

Figure 9. Fiducial mark on EUV mask blank

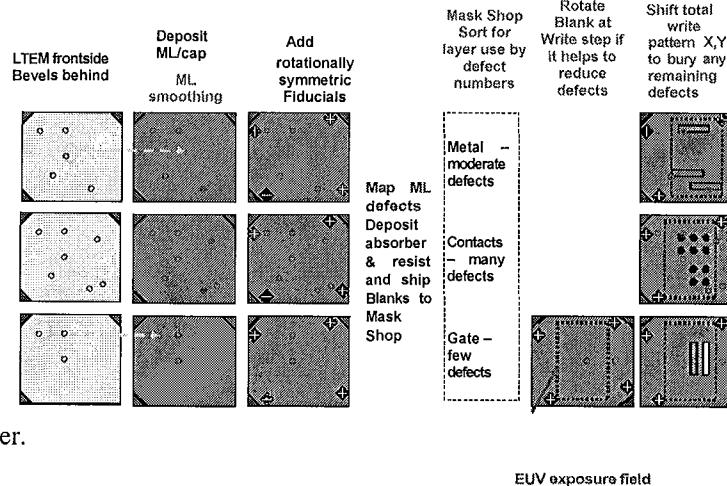

#### 4.3 Fiducial mark on the multilayer

We need complete defect size information and exact coordination for defect mitigation technology. There should be a fiducial mark on the multilayer to extract the relative coordination of each defect. After mask blank inspection, we can get all information about each phase defect. Then we can define which kind of defect is printable or not. Because phase defects under the absorber or in the open field are less printable on wafers, any shift and rotation of the blank with regard to the phase defect before e-beam writing can hide the phase defect on the blank if there are fiducial marks on the blank. Mask shops sort for layer use by defect numbers as in Figure 10. For example, a mask blank with some phase defects can be used for the contact array pattern, moderated defects for the metal layer, and a

few defects for gate layer.

Figure 10. Summary of defect mitigation technology

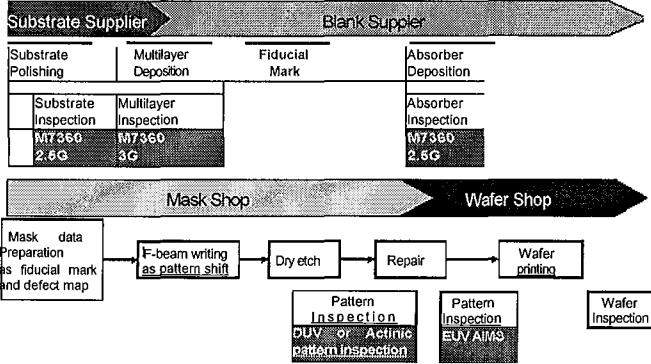

#### 4.4 Mask fabrication process considering fiducial marks

The mask fabrication process using fiducial marks and required inspection tool is shown in Figure 11. We need to develop the next generation substrate inspection tool (2.5G), actinic blank inspection tool (3G), and small field aerial image microscope. SEMATECH is pursuing the following actions to attempt to meet defect metrology requirements. The tool is critical for the industry to stay on the mask blank defect reduction roadmap to meet 22 nm HP targets

- Continued improvement of 2nd generation visible light inspection tools. The Lasertec M7360 should get us to 30-3 5 nm sensitivity for pilot line applications.

- Drive 2.5 generation tool – visible light inspection extension with 20 nm sensitivity.

- Drive 3 generation tool - actinic inspection

Figure 11. Mask fabrication process and required inspection tool.

## 5. CONCLUSION AND FUTURE WORK

Reducing defects on EUV mask blanks is key for mass production using EUV lithography. In this paper, we tested phase defect printability at the 32/22/16 nm half-pitch. Phase defects 0.5 nm high can be printable; we therefore need an inspection tool to detect these kinds of shallow phase defects on EUV mask blanks. Because achieving a high yield in mass production with a defect density of  $0.003/\text{cm}^2$  will be difficult, defect mitigation technology using mask blanks with some phase defects should be developed to maintain a low COO for EUV masks. Fiducial marks need to have exact information about each defect on the EUV mask blank. Actinic mask blank defect inspection and aerial imaging tools are key to enable yielding masks for the 22 nm HP. SEMATECH is making a programmed phase defect mask to study the printability of phase defects using the MET, AIT, and ADT in collaboration with industry.

This work was supported by the Director, Office of Science, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

## REFERENCES

1. K. A. Goldberg, A. Barty, Y. Liu, P. Kearney, Y. Tezuka, T. Terasawa, J. S. Taylor, H. S. Han, and O. R. Wood II., *J. Vac. Sci. & Technol. B* 24 (6), 2824 (2006).

2. K. A. Goldberg, P. P. Naulleau, A. Barty, S. B. Rekawa, C. D. Kemp, R. F. Gunion, F. Salmassi, E. M. Gullikson, E. H. Anderson, H. S. Han, *Proc. SPIE* 6730, 67305E (2007).

3. K. A. Goldberg, S. B. Rekawa, C. D. Kemp, A. Barty, E. H. Anderson, P. Kearney, H. S. Han, *Proc. SPIE* 6921, 69213U (2008).

4. Stefan Wurm, Hakseung Han, Patrick Kearney, Wonil Cho, Chan-Uk Jeon, and Eric Gullikson, *Proc. SPIE* 6607, 66073A, (2007).

5. E. M. Gullikson, C. Cerjan, D. G. Stearns, P. B. Mirkarimi and D. W. Sweeney, *J. Vac. Sci. Technol. B* 20(1), 1071-1023 (2002)

6. Hakseung Han, Wonil Cho, Kenneth A. Goldberg, Eric M. Gullikson, Chan-Uk Jeon, and Stefan Wurm, *Proc. SPIE* 6921, 6921 1Y (2008)