LS-159

D. G. McGhee

September 23, 1990

PULSED POWER SUPPLY FOR PAR INJECTION/EXTRACTION

SEPTUM MAGNET

ABSTRACT

A 22.5  $\mu$ H, 22.5 m $\Omega$  transformer septum magnet must be pulsed at a 60 Hz rate to inject beam from a 450 MeV positron linac into a positron accumulator ring (PAR) and to extract beam from it. Of the 60 pulses per second the first 24 are used for injection and the 30<sup>th</sup> for extraction. The 25<sup>th</sup> through the 29<sup>th</sup> are not used. This pattern is repeated continuously. A design study was performed of the power supply proposed in the APS Title I design. This supply produces a pulse that is approximately a half-sine-wave with a base width of approximately 1/3 ms; its peak current is adjustable from 3.5kA to 4.7kA and is repeatable within  $\pm 0.05\%$ . The septum steel is reset by a half-sine pulse of reverse polarity a few milliseconds after the forward current pulse. No beam is present during reset. The use of the transformer design minimizes the cost of the capacitors used for energy storage.

INTRODUCTION

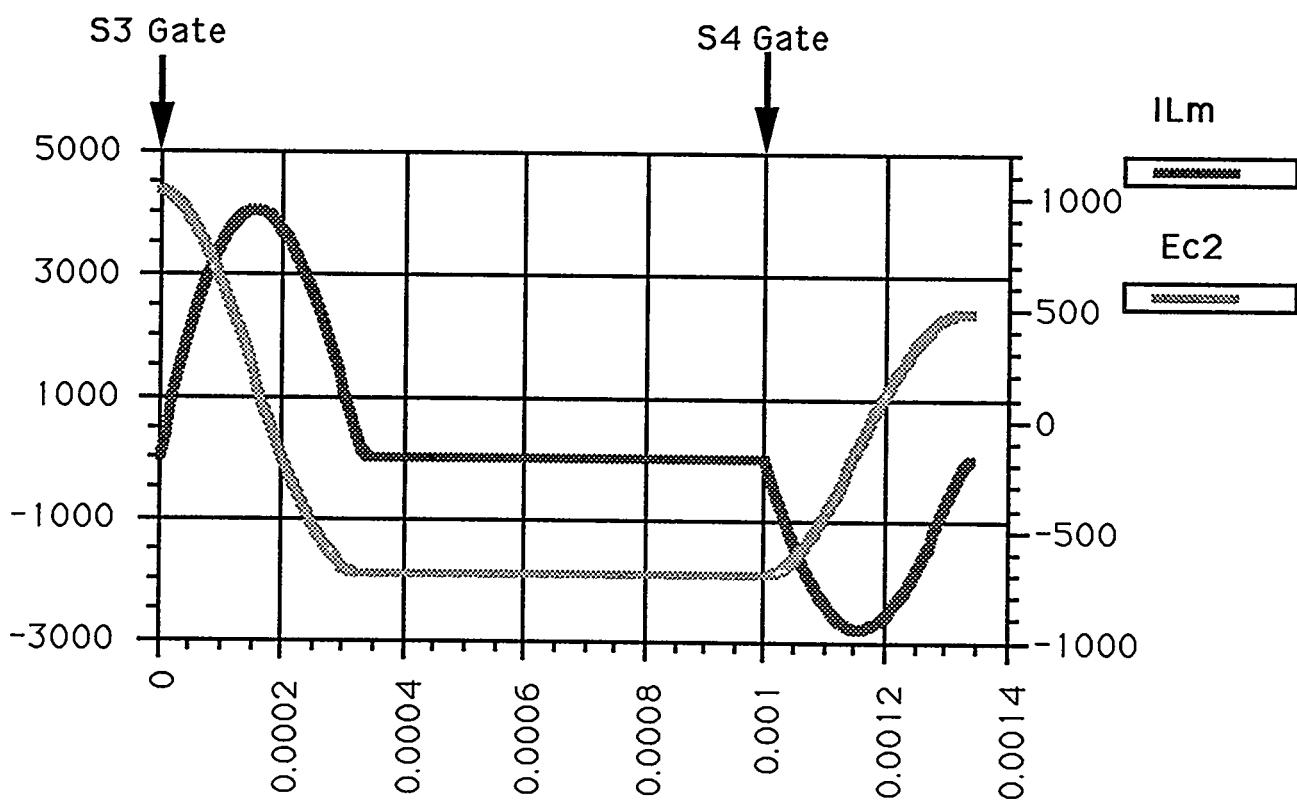

During the injection of the 450 MeV positron beam from the linac into PAR and extraction from PAR, the septum magnet must be pulsed. The combined rise and fall time of the pulse should be  $\leq 1/3$  ms and the flattop time  $> 1 \mu$ s. These requirements can be met with a capacitor discharge circuit that is resonant with the septum magnet at a frequency of approximately 1500 Hz. The peak current should be 4018 A in the transformer primary and 12054 A in the secondary. These requirements can be met with a half sine-wave pulse. This is accomplished by discharging the energy stored in capacitor bank ( $C_2$ ) into the magnet as illustrated by Fig. 1. On triggering the forward thyristor  $S_3$ , the energy stored in  $C_2$  between pulses is discharged into the magnet circuit.  $S_3$  turns off at the end of the first half cycle of the damped oscillation.  $C_2$  is then left

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

MASTEK

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, make any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

Fig. 1

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

with a smaller charge of opposite polarity until the reverse thyristor  $S_4$  is triggered and the second half cycle takes place with current flowing in the opposite direction. The difference between the original and the final charge is furnished by the charging supply between septum pulses.

### Switching Circuits Circuit Equations

When the capacitor  $C_2$  of Fig. 1 is discharged into the load, an oscillatory current will result provided the total resistance in the circuit is sufficiently low.

The resonant frequency of the circuit is:

$$f_r = \beta/2\pi \quad [s^{-1}] \quad (1)$$

where  $\beta = ((1/L_m C_2) - (R_m^2/4L_m^2))^{0.5}$   $[s^{-1}]$

$C_2$  = capacitor bank  $[F]$

$L_m$  = total circuit inductance  $[H]$

$R_m$  = total circuit resistance  $[\Omega]$

The current at any time is:

$$i = (E/\beta L_m) e^{-\alpha t} \sin \beta t \quad [A] \quad (2)$$

where  $t$  = time after discharge starts  $[s]$

$$\alpha = R_m/2 L_m \quad [s^{-1}]$$

The time where the current reaches its first peak is:

$$t_p = 1/\beta \tan^{-1} \beta/\alpha \quad [s] \quad (3)$$

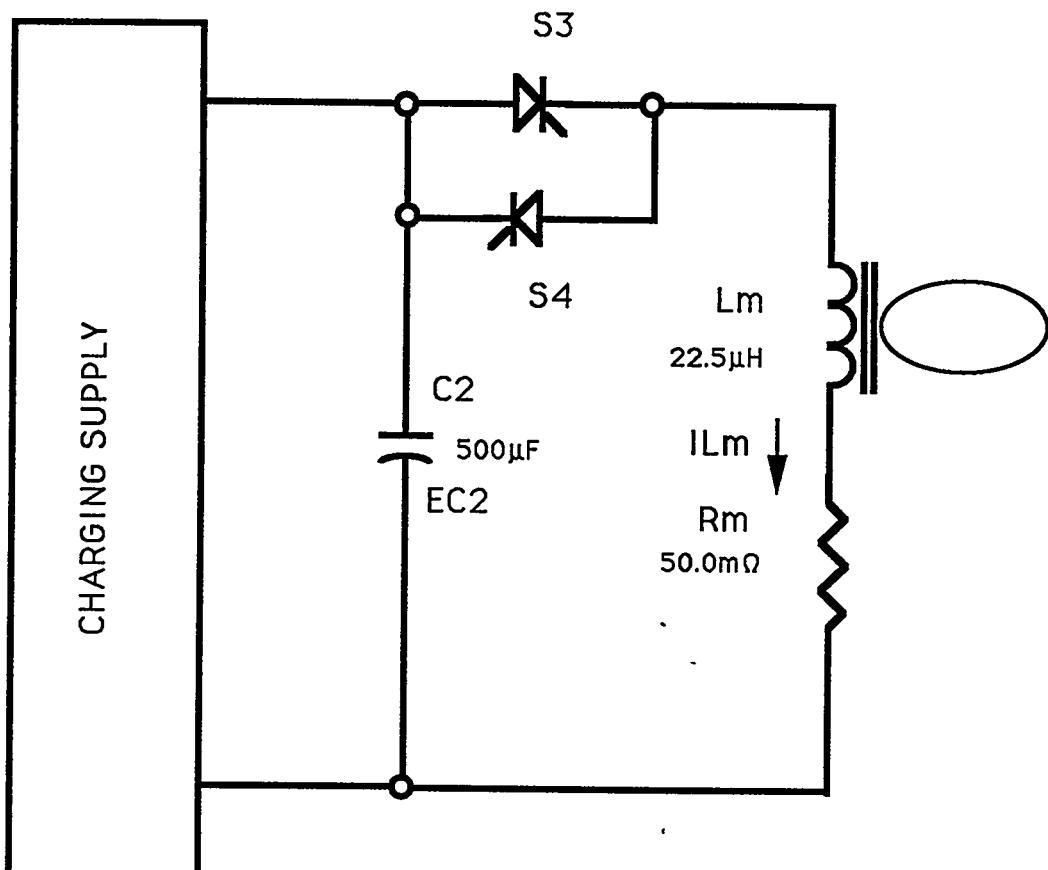

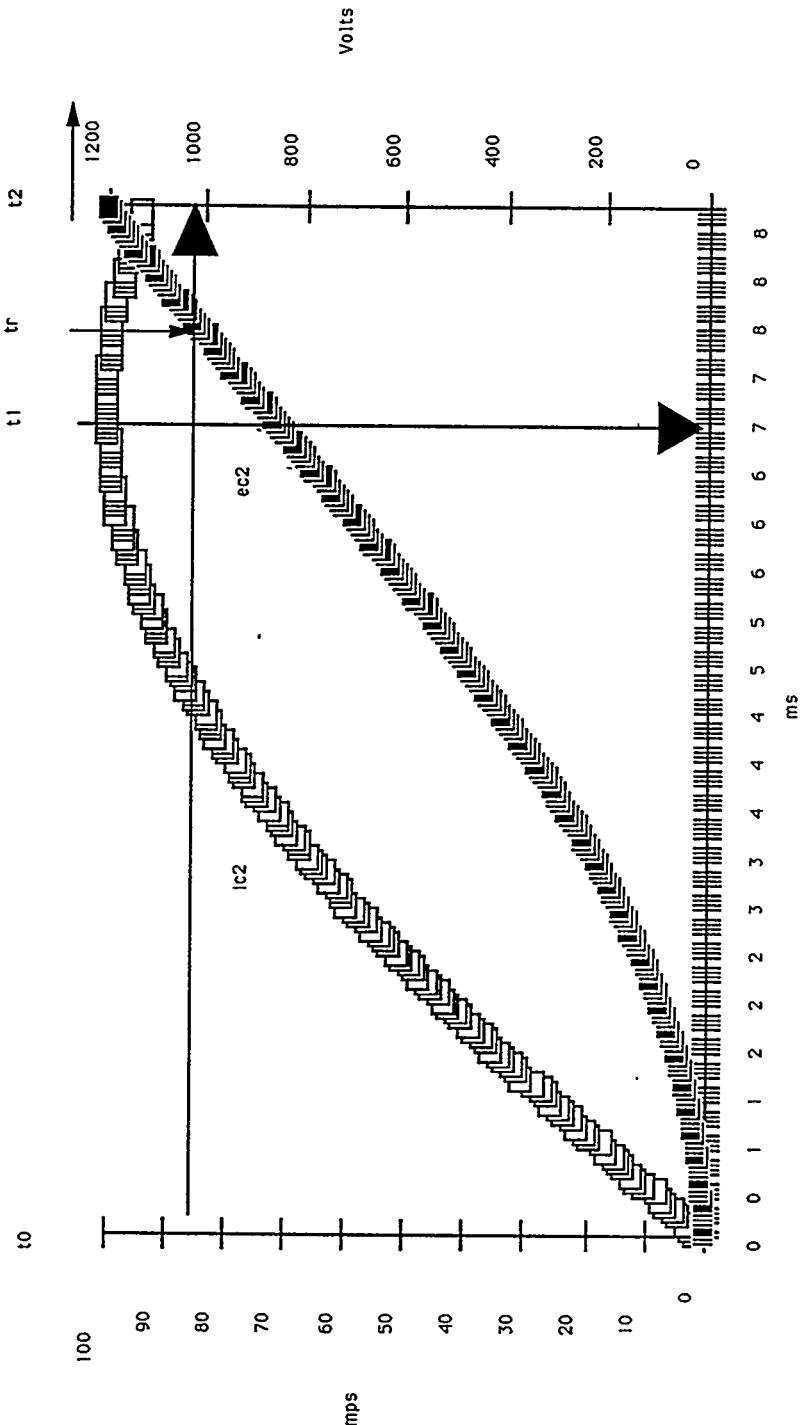

The first current peak does not occur at precisely the first quarter period of the discharge cycle, but at a point in time before. This is shown by the circuit simulation graphed in Fig. 2. The term  $\tan^{-1} \beta/\alpha$

Fig. 2

describes the phase angle at which the peak current occurs.

In this application,  $R_m$  is made appreciably less than the value for critical damping. With  $1/L_m C_2 > R_m^2 / 4L_m^2$  we can write  $\beta = 1/(L_m C_2)^{0.5}$  and the above equations can be simplified to:

$$f_r \approx 1/(2\pi(L_m C_2)^{0.5}) \quad [s^{-1}] \quad (1')$$

$$i \approx E_{C2} (C_2/L_m)^{0.5} e^{-\alpha t} \sin t/(L_m C_2)^{0.5} [A] \quad (2')$$

The peak current is then

$$I_p \approx E_{C2} (C_2/L_m)^{0.5} e^{-((\pi R_m/4)(C_2/L_m)^{0.5})} [A] \quad (2'')$$

and the voltage on the first reversal becomes

$$E_{C2} \approx - E_{C2} e^{-((\pi R_m/2)(C_2/L_m)^{0.5})} [V] \quad (4)$$

Critical damping occurs at a resistance:

$$R_m = 2(L_m/C_2)^{0.5} \quad [\Omega] \quad (5)$$

### Controlled Charging-Choke Circuit

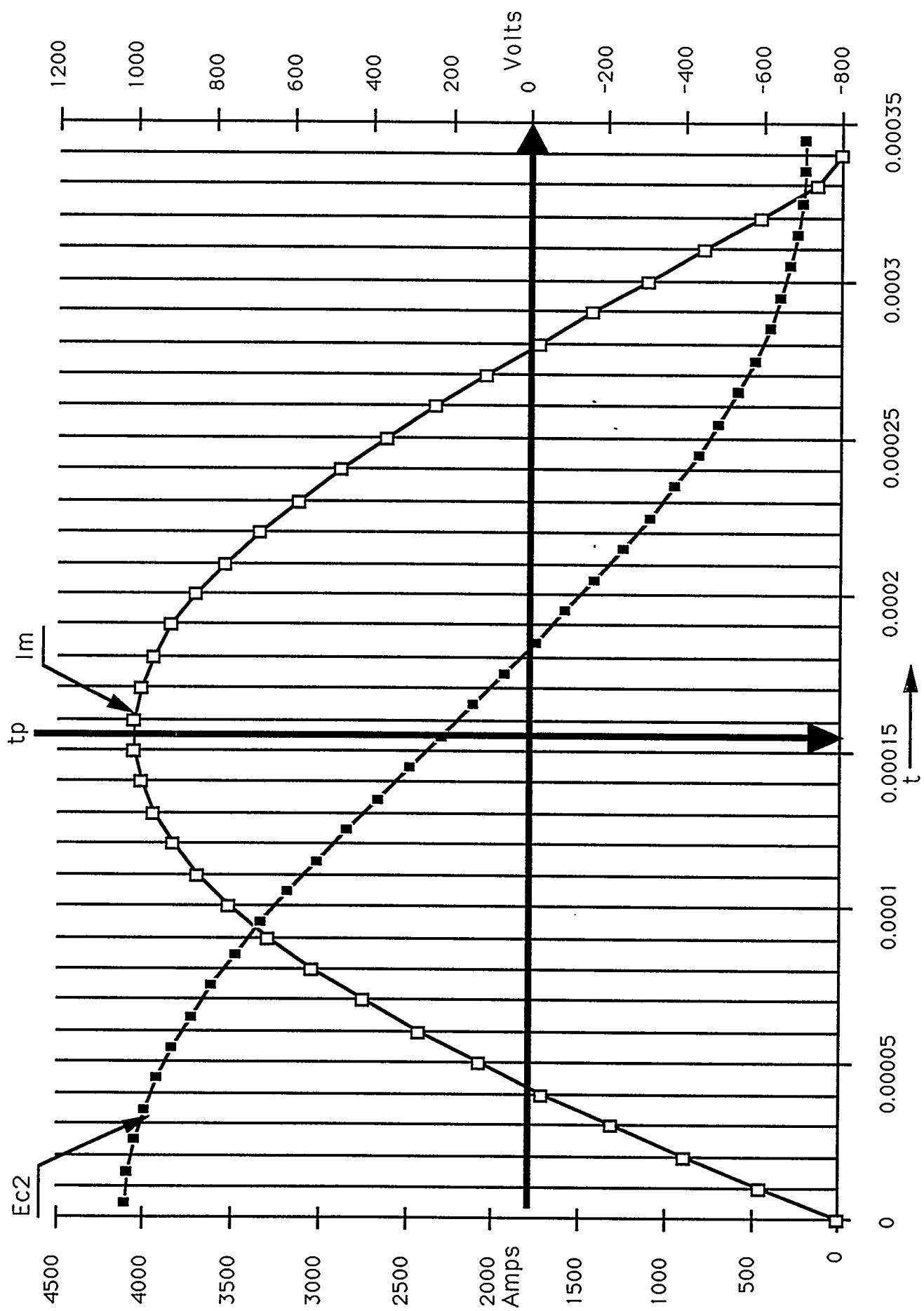

Fig. 3 shows the controlled charging-choke circuit and the capacitor discharge circuit of Fig. 1 combined. The discharge capacitor  $C_2$  is charged and recharged to make up the circuit losses incurred pulsing the magnet. These losses are made up from the unregulated dc power supply comprised of a circuit breaker, contactor, main transformer, diode rectifier assembly and low pass filter. The controlled charging circuit is comprised of  $L_2$ ,  $C_2$ ,  $S_1$  and  $S_2$ . Gating on of  $S_1$  is used to start the charging of  $C_2$  from the dc power supply. At time  $t_0$  the supply voltage  $E$  begins to drive an essentially sinusoidal current through the charging circuit.

$$E = iR_2 + L_2(di/dt) + (1/C_2) \int_0^{t_1} i_{C2} dt \quad (8)$$

KD OPENS 1.5 to 4 s after K1 Closes

6

Fig. 3

At time  $t_1$  the current is at its peak and

$$L_2 \frac{di}{dt} = 0, \quad (9)$$

$$E = iR_2 + (1/C_2) \int_0^{t_1} i_{C2} dt. \quad (10)$$

Between  $t_1$  and  $t_2$  the decaying charging current generates a voltage  $L_2 (di/dt)$  which aids the supply voltage to charge the capacitor  $C_2$  to a voltage larger than  $E$ . In the case where  $R \Rightarrow 0$ , this voltage will be, at time  $t_2$ ,

$$e_{C2} = E + L (di/dt) = 2E.$$

By providing a thyristor across the charging choke as shown in Fig. 3 the charging cycle can be terminated at any instant between times  $t_1$  and  $t_2$ . A fraction of the capacitor voltage  $e_{C2}$  is compared with a reference voltage. At time  $t_r$  when the capacitor voltage is  $\geq$  the supply voltage, a pulse can be generated which turns on  $S_2$ . With  $S_2$  conducting, the driving voltage  $L_2 (di/dt)$  is removed from the circuit and the capacitor voltage  $e_{C2}$  is larger than the power supply voltage  $E$ , thyristor  $S_1$  is back-biased and the charging current  $i_{C2}$  stops. The current  $i_{L2}$  flowing in choke  $L_2$  at time  $t_r$  will decay with a time constant  $L_2/R$ , where  $R$  is the resistance of the choke and thyristor,  $S_2$ , circuit. Thyristor  $S_2$  remains on until the time  $S_1$  is gated on starting the charge cycle again or the choke current decays to 0. The current  $i_{L2}$  flowing in the choke when  $S_2$  is turned off will aid in charging capacitor  $C_2$  (the energy  $0.5 L_2 i_{L2}^2$  is returned to the circuit). This makes the circuit very efficient.

### Warning

It should be noted that the  $Q$  of the discharge circuit in Fig. 1 should be  $< 5$  for this charging circuit to operate properly. As the  $Q$  increases the current flowing in the choke  $L_2$  will decrease. This in turn decreases the operating range of the charging circuit. The  $Q$  of the circuit was decreased from 9.4 to 4.2. This allowed for

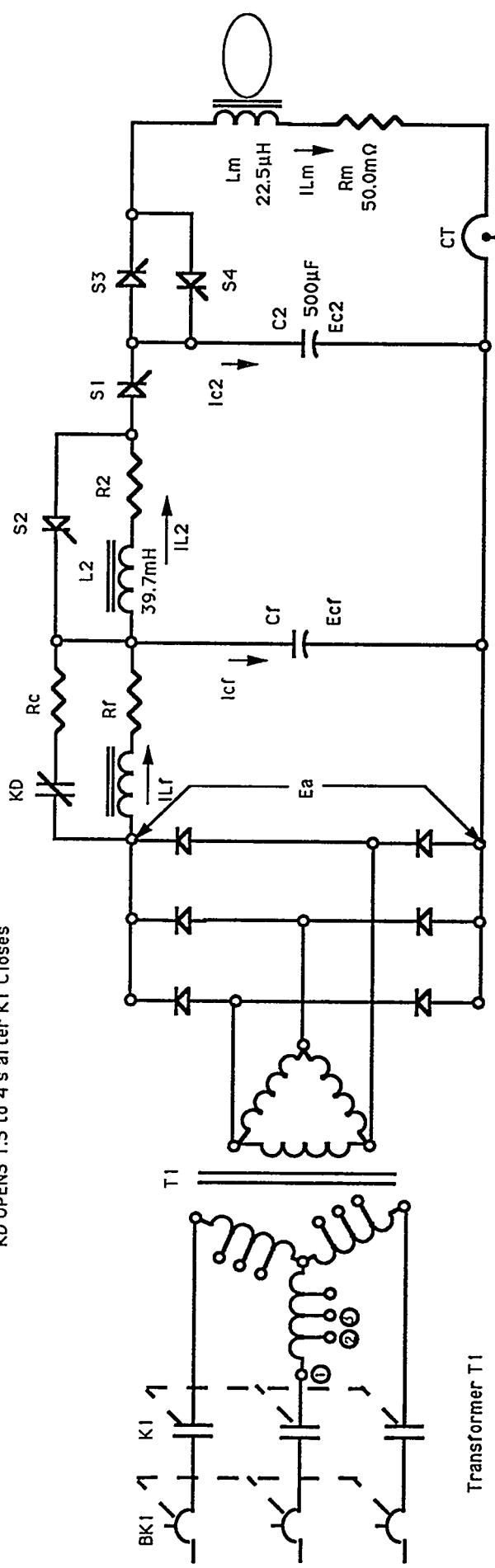

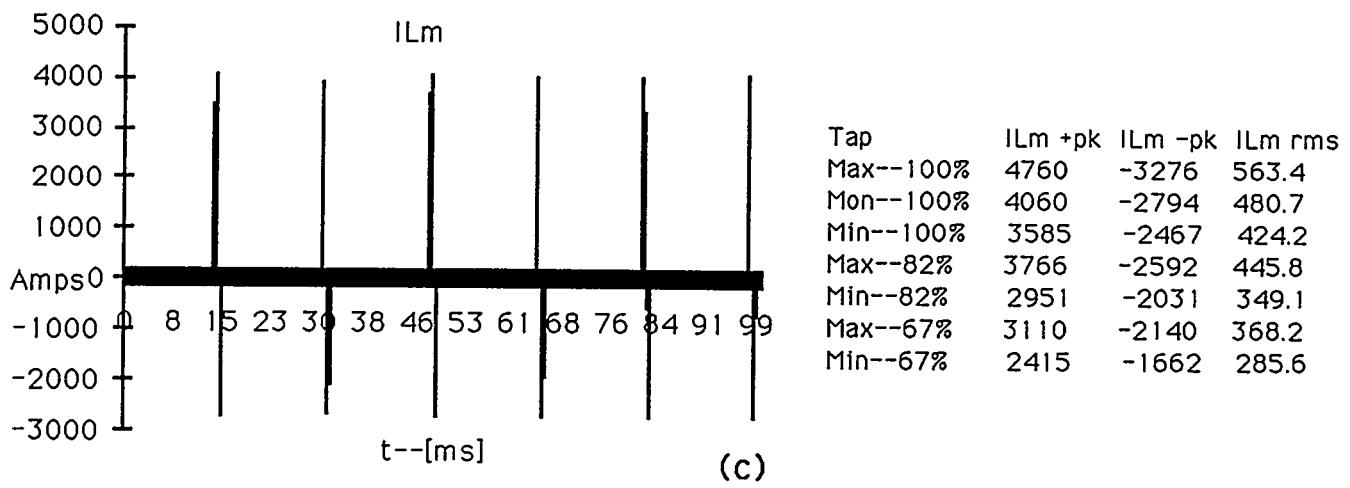

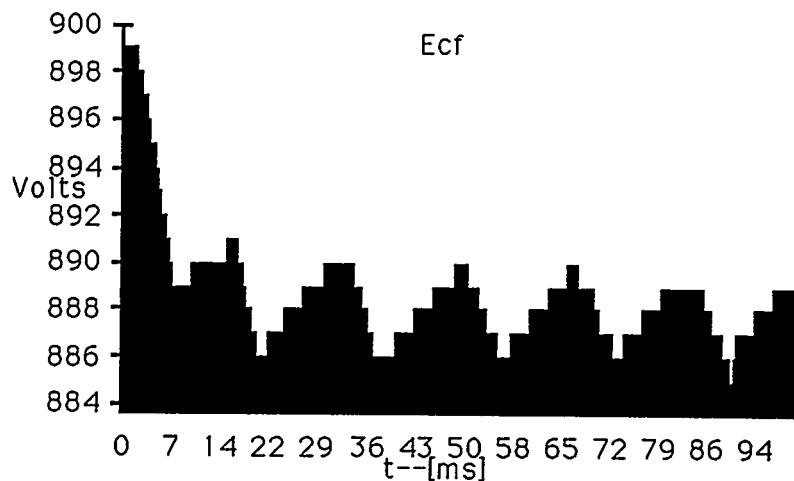

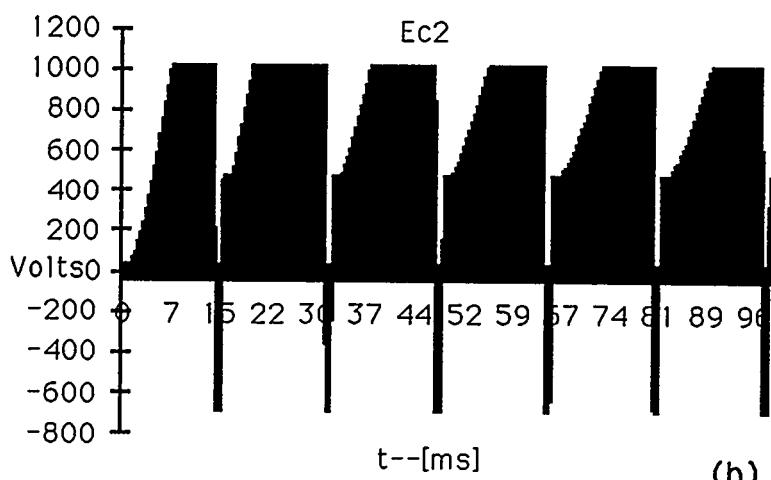

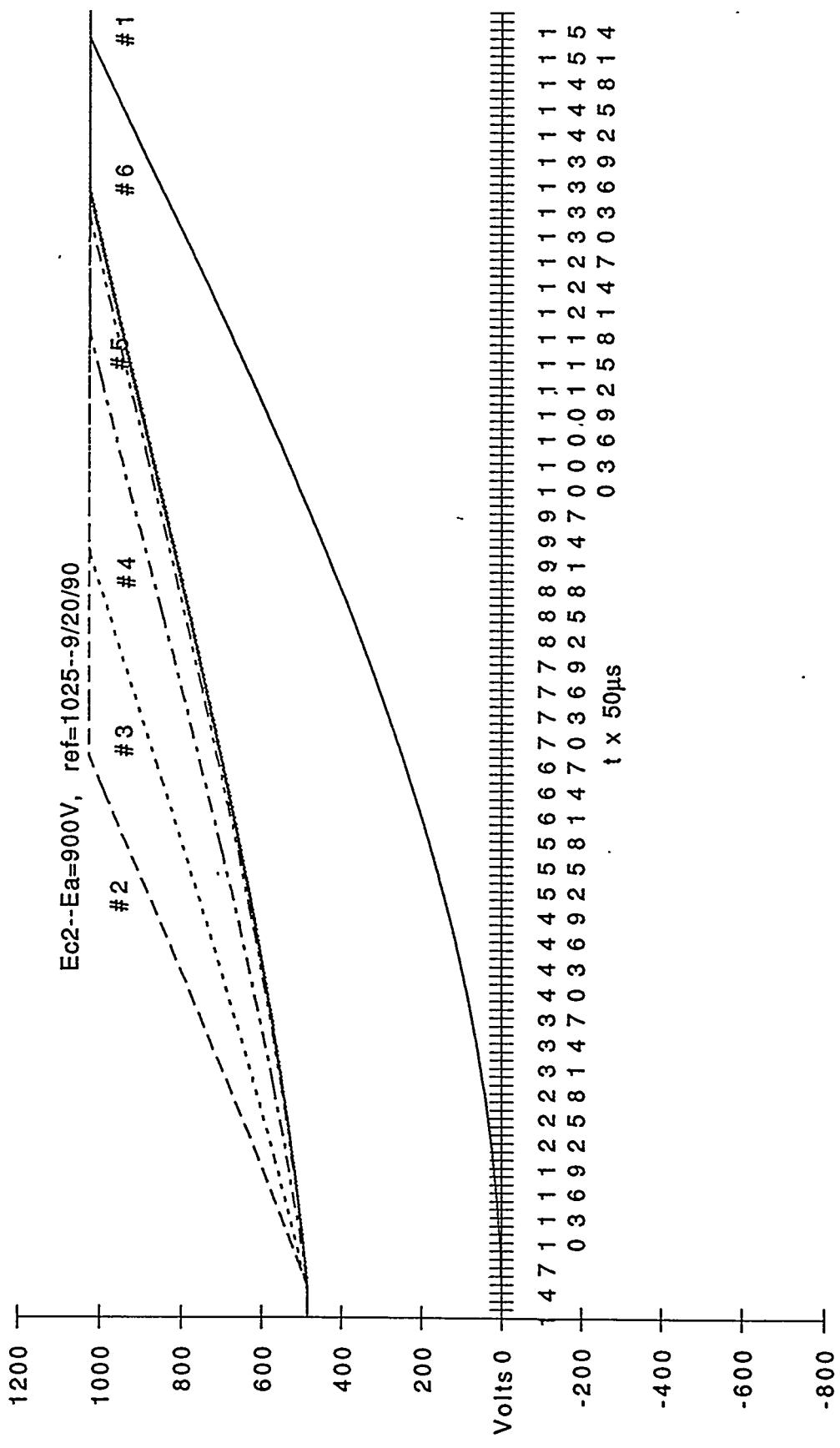

operation with a normal line voltage from 3.5kA to 4.7kA or operation with the normal line fluctuation of  $\pm 5\%$  at 4kA. The circuit was simulated using the logic diagram in Fig. 4, the results are shown in Fig. 5, 6, 7 and 8. Fig. 8 shows the change in time for the first six charge cycles of capacitor C2. It should be noted the first charge cycle is the longest the second is the shortest and the sixth is approaching steady-state.

### Pulsing the Magnet Without Resetting the Core

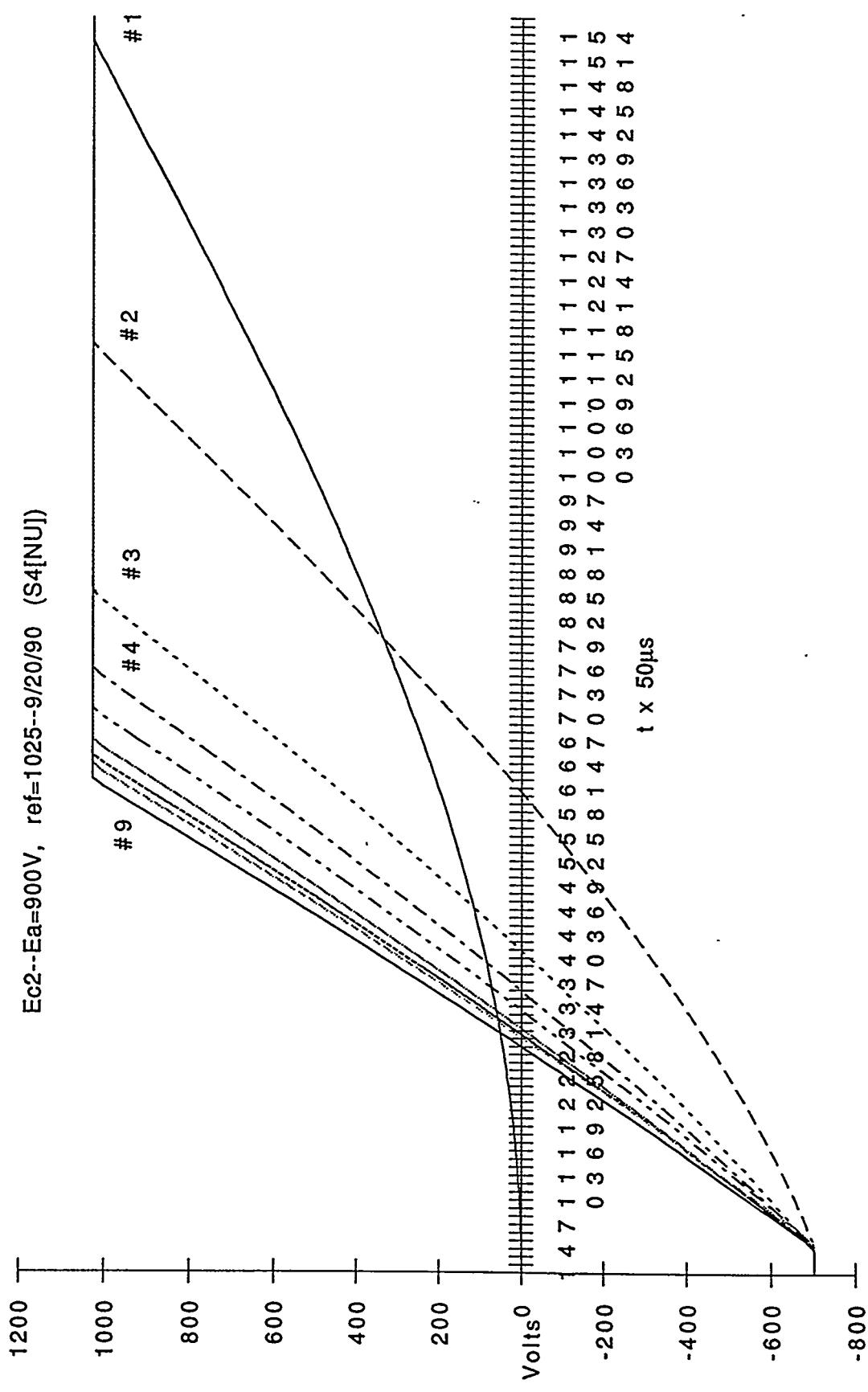

Heat losses in the magnet can be cut approximately 1/3 by not gating S<sub>4</sub> but the magnet core would not be reset. This mode of operation would allow the dc power supply and filter to operate at a lower voltage. Also the circuit Q could be increased increasing the operating efficiency. Fig. 9 shows the change in time for the first nine charge cycles of capacitor C2. It should be noted the first charge cycle is the longest, the second is next longest and the ninth is approaching steady-state.

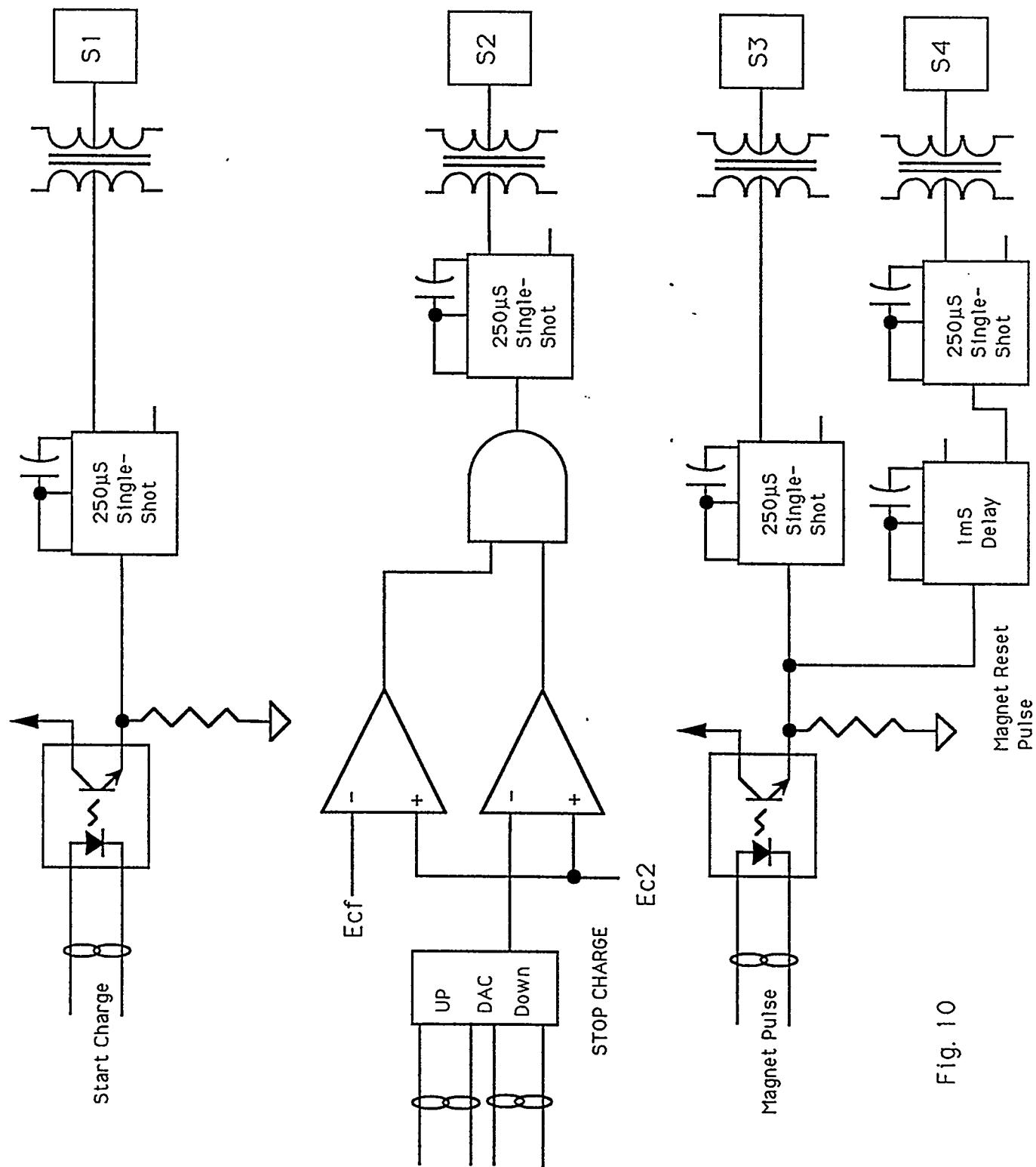

### Control

Control is accomplished with 2 external pulses and a pulse-train, as shown in Fig. 10. One pulse starts the charge cycle for C2 by gating S<sub>1</sub> and the second starts the magnet current pulse by gating S<sub>2</sub>. The pulse train counts the DAC up or down setting the reference voltage that is compared with the capacitor voltage E<sub>c2</sub>. If E<sub>c2</sub> is  $\geq$  the reference voltage and E<sub>c2</sub> > E<sub>rf</sub> the charge cycle is terminated by gating S<sub>2</sub>. The magnet reset current pulse is started by gating S<sub>4</sub> after a fix delay from the start of the magnet current pulse.

### Monitoring and Interlocks

Computer monitoring includes the power supply interlocks, magnet interlocks and two 14 bit analog-to-digital converters (ADC) as listed in attachment 1. One ADC reads the peak capacitor voltage and the other reads the peak magnet current.

In order to operate the power supply the interlocks listed in attachment 1 must be made-up. If they are not made-up or open during operation the contactor, K<sub>1</sub>, shown in Fig. 3 will open and the gating of the thyristors will be inhibited.

Fig. 4

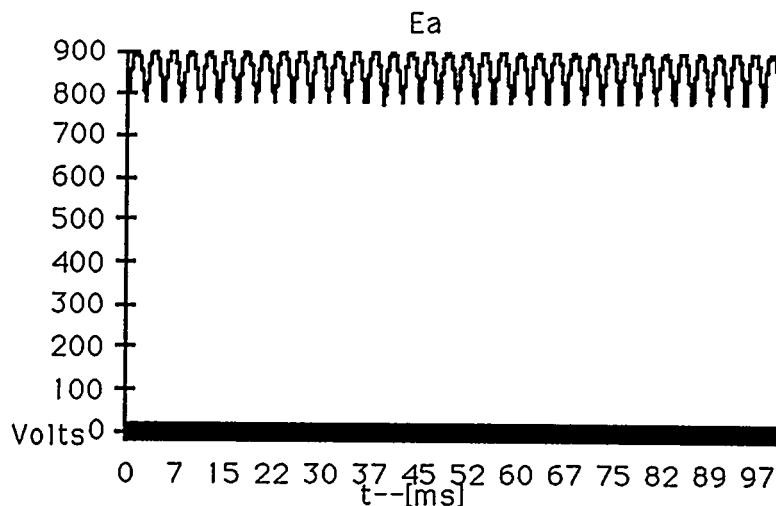

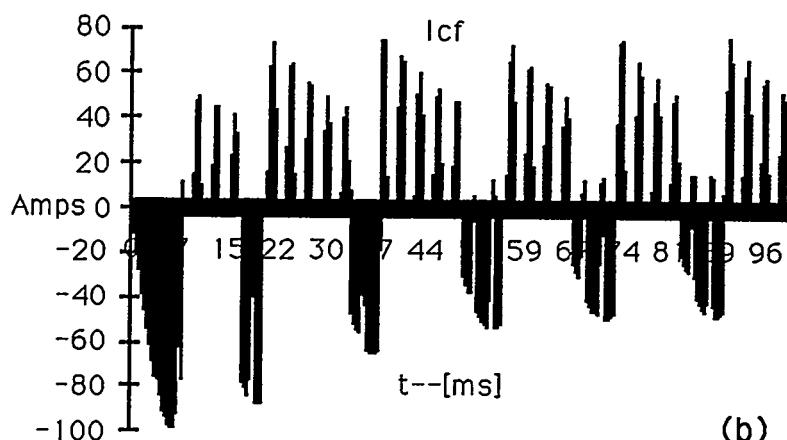

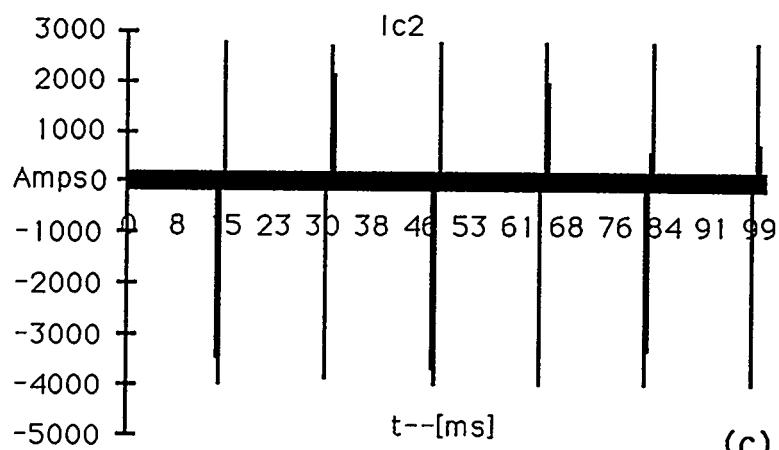

### Responce of Nominal Settings

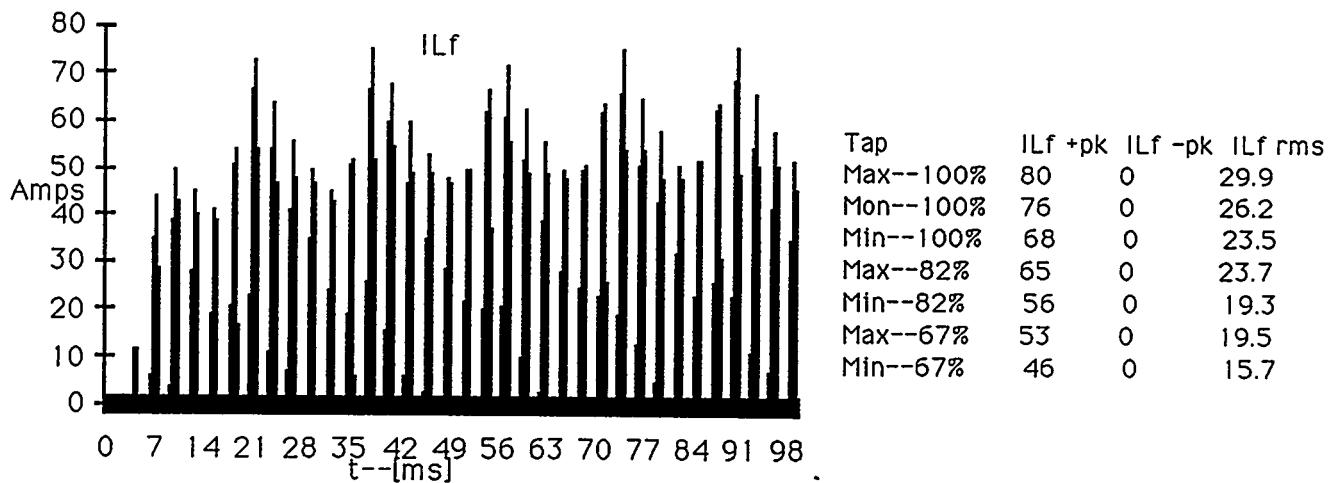

(a)

(b)

(c)

Fig. 5

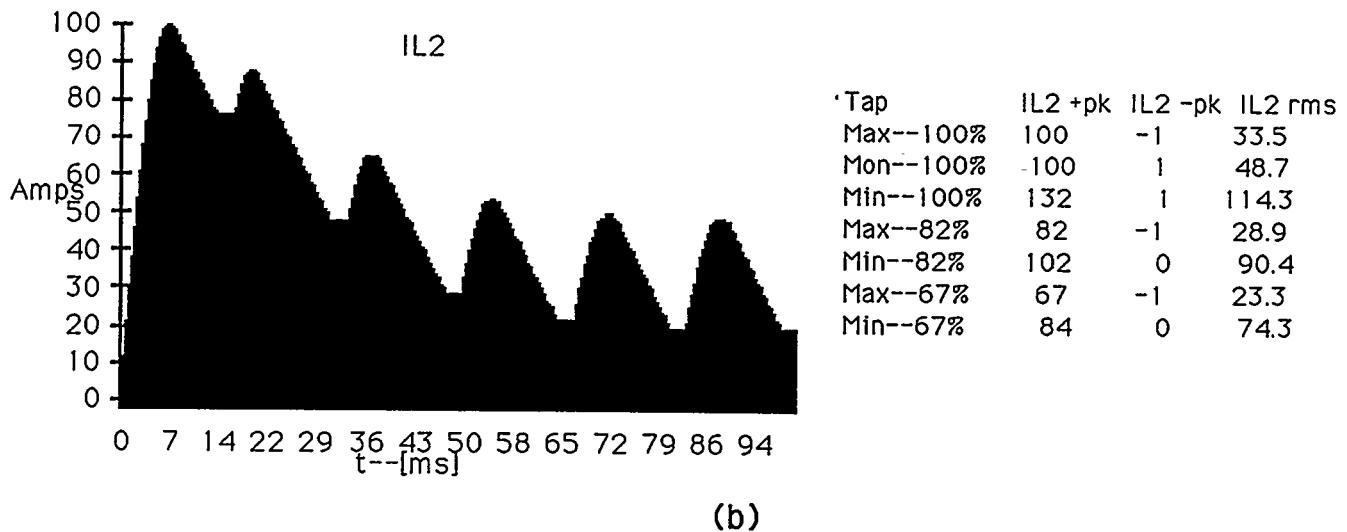

(a)

(b)

Fig. 6

(a)

| Tap       | Ecf +pk | Ecf -pk | Ecf rms |

|-----------|---------|---------|---------|

| Max--100% | 899     | 885     | 887.1   |

| Mon--100% | 899     | 885     | 888.2   |

| Min--100% | 899     | 886     | 888.8   |

| Max--82%  | 737     | 726     | 727.6   |

| Min--82%  | 737     | 726     | 728.9   |

| Max--67%  | 604     | 595     | 596.4   |

| Min--67%  | 604     | 595     | 597.4   |

(b)

| Tap       | Ec2 +pk | Ec2 -pk | Ec2 rms |

|-----------|---------|---------|---------|

| Max--100% | 1200    | -823    | 892.8   |

| Mon--100% | 1025    | -702    | 859.7   |

| Min--100% | 906     | -619    | 810.2   |

| Max--82%  | 950     | -651    | 725.2   |

| Min--82%  | 745     | -509    | 666.1   |

| Max--67%  | 785     | -537    | 595.6   |

| Min--67%  | 610     | -417    | 545.4   |

Fig. 7

Fig. 8

Ec2--(S4[NU])

6

Fig.

Fig. 10

## ATTACHMENT 1

### CONTROL INTERLOCK AND MONITORING OF PAR's AC SEPTUM POWER SUPPLY

DGM WBS 1.2.5.2.6 6/7/90--REV. 10/25/90

#### COMPUTERR CONTROL SIGNALS:

1. "RESET"--OPTICALLY COUPLED PULSE

2. "ON/OFF"--OPTICALLY COUPLED STATE--(HIGH--ON>>>LOW--OFF)

3. "CHARGE"--OPTICALLY COUPLED PULSE

4. "DISCHARGE"--OPTICALLY COUPLED PULSE

5. "DAC--COUNT-UP"-- OPTICALLY COUPLED PULSE

#### COMPUTER MONITORING SIGNALS:

1. "ADC--CAPACITOR-VOLTAGE"--OPTICALLY COUPLED

2. "ADC--PULSE MAGNET CURRENT--PEAK"--OPTICALLY COUPLED

3. "SYSTEM NORMAL/ABNORMAL"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--NORMAL)

- 3.1 "WATER FLOW"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.2 "WINDOW--PEAK MAGNET CURRENT  $\leq$  DAC REFERENCE - FIXED"--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.3 "WINDOW--PEAK MAGNET CURRENT  $\geq$  DAC REFERENCE + FIXED"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.4 "CAPACITOR C2 OVERVOLTAGE"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.5 "AIR OVERTEMPERATURE"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.6 "AC PHASE UNBALANCE"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.7 "DOOR SWITCHES"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.8 "EMERGENCY TRIP SWITCH IS MADE UP" (IN THE TUNNEL)--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.9 "MAGNET INTERLOCKS COMPLETE"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.9.1 "WATER FLOW--SUPPLY SIDE"--OPTICALLY COUPLED STATE--(HIGH--NORMAL>>>LOW--ABNORMAL)

- 3.9.2 "SUPPLY WATER PRESSURE"--ANALOG SIGNAL

- 3.9.3 "RETURRN WATER PRESSURE"--ANALOG SIGNAL

NOTES FOR ITEMS 3.9.1 THROUGH 3.9.4:

- COMPARE THE SUPPLY AND RETURN WATER FLOW IF NOT THE SAME TRIP THE DC POWER SUPPLY.

- COMPARE THE DIFFERENTIAL PRESSURE WITH FLOW, IF INCORRECT ALARM.