R.L. Hogrefe

LS-171

**Magnet Measurement

Interfacing to the G-64 Euro Standard Bus

and Testing G-64 Modules**

**Introduction**

The Magnet Measurement system utilizes various modules with a G-64 Euro (Gespac) Standard Interface. All modules are designed to be software controlled, normally under the constraints of the OS-9 operating system with all data transfers to a host computer accomplished by a serial link.

**G-64 Interfacing**

To simplify system integration and increase acquisition times all software control is performed by the Magnet Measurement computer, an IBM 386 PC/AT. In order to control the Euro (Gespac) Standard modules an IBM I/O (DIO-32) card along with a DIO-32 to G-64 interface are used.

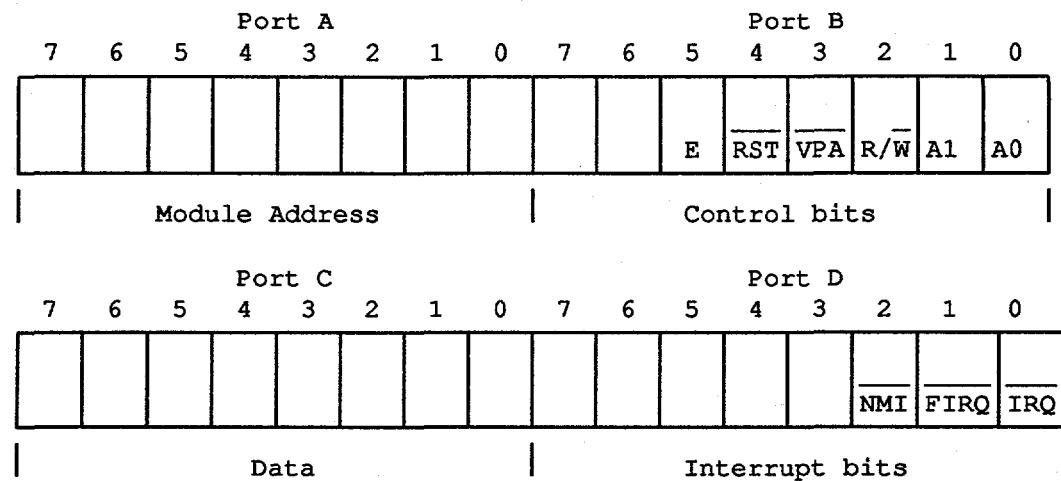

All module functions are accomplished by I/O transfers. Figure 1 details the bit assignments for the 4 I/O ports of the DIO-32. The DIO-32 to G-64 interface routes the port bits to the G-64 backplane. Signal routing for the DIO-32 to G-64 interface is listed in Table 1.

**G-64 Computer Simulator**

A simulator was designed to test/troubleshoot purchased, as well as in-house designed, G-64 modules. The computer simulator mimics the functionality of the IBM DIO-32 board.

**MASTER**

**DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED**

## Operation

The simulator allows the operator to control the module address, control lines and data transfers and receives interrupt requests as if it were the controlling processor to the G-64 bus. While the simulator is enabled the normally active processor must be disconnected. This allows complete testing without computer intervention. The design of the simulator also allows it to be used as a G-64 bus monitor when the simulator is in its disabled (no control) state.

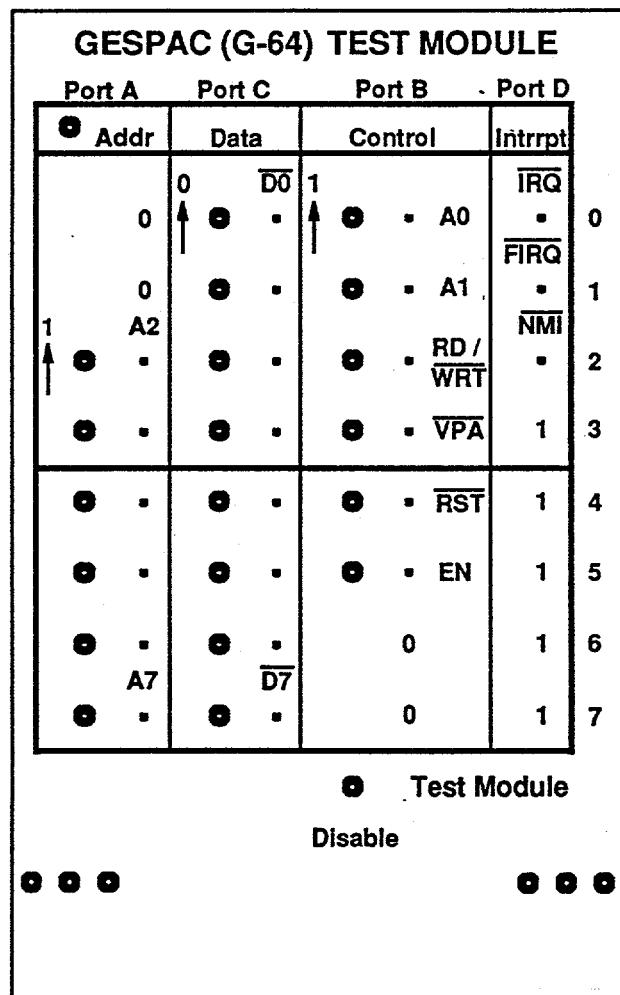

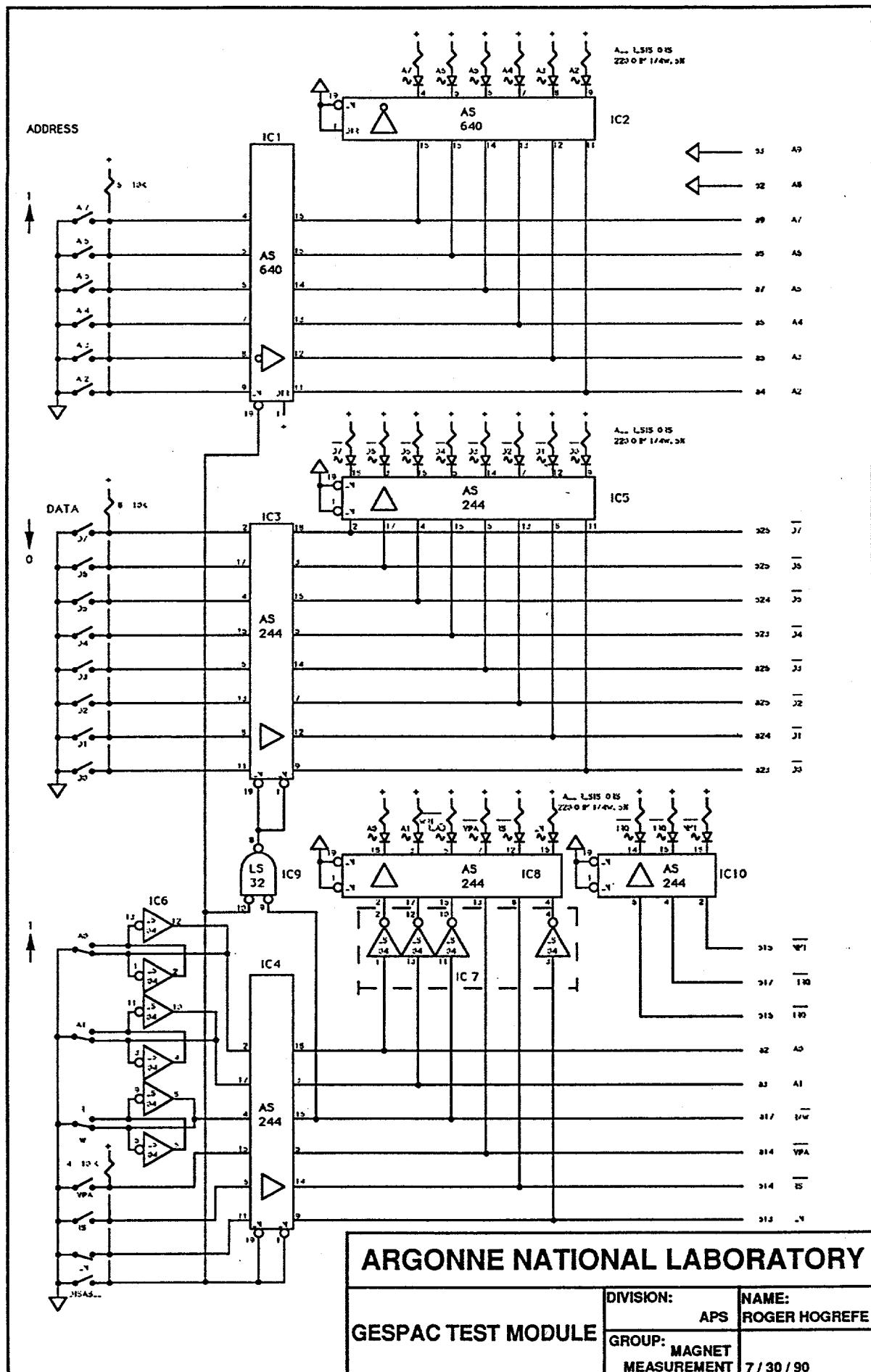

The front panel (see Figure 2) is divided into 4 sections which corresponds to the DIO-32 I/O ports. Switch position and associated logic levels are shown for each port section. The included LEDs will light when a logic bit is active. A bar or line over the bit descriptor implies an active logic level of 0, otherwise the active logic level is a 1. Figure 3 is the schematic of the simulator and is included for additional reference.

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

Figure 1.

Table 1.

DIO-32 to G-64 Interface Pin out

| Function |     | G-64      | AT-DIO    | Function |      | G-64     | AT-DIO    |

|----------|-----|-----------|-----------|----------|------|----------|-----------|

|          |     |           | 37 -----  |          | ---- | D0       | a23       |

|          |     |           | 39        |          |      | D1       | a24       |

|          | A2  | a4        | 38        |          |      | D2       | a25       |

|          | A3  | a5        | 40 Port A | Data     | D3   | a26      | 11 Port C |

| Module   | A4  | a6        | 35        |          |      | D4       | b23       |

| Address  | A5  | a7        | 42        |          |      | D5       | b24       |

|          | A6  | a8        | 36        |          |      | D6       | b25       |

| -----    | A7  | a9        | 41 -----  | ----     | D7   | b26      | 10 -----  |

|          |     |           |           |          |      |          |           |

|          | A0  | a2        | 47 -----  |          | IRQ  | b16      | 4 -----   |

|          | A1  | a3        | 50        |          | FIRQ | b17      | 1         |

| R/W      | a17 | 44        |           |          | NMI  | b15      | 7         |

| VPA      | a14 | 48 Port B |           | D11      | a22  | 3 Port D |           |

| RES      | b14 | 49        |           | D12      | b19  | 2        |           |

| E        | b13 | 43        |           | D13      | b20  | 8        |           |

| A14      | b8  | 46        |           | D14      | b21  | 5        |           |

| A15      | b9  | 45 -----  |           | D15      | b22  | 6 -----  |           |

**Figure 2.**

**G-64 Computer Simulator Front Panel**

**Figure 3. Schematic of the G-64 Computer Simulator**