JAMES D. WELCH

ATTORNEY AT LAW

PROFESSIONAL ENGINEER

INTELLECTUAL PROPERTY

402-391-4448

10328 PINEHURST AVE.

OMAHA, NEBRASKA 68124

May 15, 1995

RE: FEDERAL GRANT NO. DE-FG47-93R701314

COORDINATOR: FRED HART

TO: JAMES D. WELCH, SOLE PROPRIETOR

FROM: U.S. DEPARTMENT OF ENERGY, ENERGY RELATED INVENTIONS.

PROJECT: NOVEL METHOD FOR MAKING SEMICONDUCTOR CHIPS.

SEVENTH QUARTERLY AND FINAL REPORT

INVENTION NO.: 534

OERI NO.: 012693

FOR PERIOD BEGINNING: JANUARY 7, 1995

AND ENDING: MAY 7, 1995

---

FIRST, MATERIAL DISCLOSED HEREIN IS CONFIDENTIAL AND SUBJECT OF PENDING PATENT APPLICATIONS. PLEASE DO NOT RELEASE ANY OF THE INCLUDED INFORMATION.

DOCUMENTATION OF FABRICATION EFFORTS

Directly following in this Seventh Quarterly, and Final Report under the present funding, I have attempted to summarize the progress of the Research in the last two years, provide analysis of how I feel the Schottky Barrier MOSFET devices fabricated operate, and show some additional Results obtained in the last four months.

After serious consideration of what to provide as documentation of work performed and results achieved over the last two years in this Final Report, I have decided to simply include copies of relevant portions of the Six previous Quarterly Reports, as Attachment "A" hereto. After rereading the prior Quarterly Reports, I have concluded that all I would do is rewrite them were I to proceed otherwise, and that would involve leaving data out if anything. I have included as Attachments, said copies of relevant portions of prior Quarterly Reports, a copy of a presently pending Grant Application, and a copy of a presently pending Patent Application which resulted from the Research efforts supported by the DOE.

FOLLOWING THEN IS:

1. HISTORICAL ACCOUNTING OF SUPPORTED RESEARCH EFFORTS;

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

**MASTER**

**DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED**

## **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

2. ANALYSIS OF HOW FABRICATED DEVICES PROBABLY OPERATE WITH ACCOMPANYING VISUAL RESULTS WHICH DEMONSTRATE AND SUPPORT THE THEORETICAL CONSIDERATIONS;

3. ADDITIONAL FABRICATION EFFORT RESULTS ACHIEVED IN LAST FOUR MONTHS.

ATTACHMENTS

"A"---COPIES OF RELEVANT PORTIONS OF THE FIRST SIX QUARTERLY REPORTS SHOWING RESULTS ACHIEVED OVER THE LAST TWO YEARS;

"B"---COPY OF PENDING GRANT APPLICATION TO ALLOW INVESTIGATION OF NONINVERTING AND INVERTING SINGLE DEVICE EQUIVALENTS TO CMOS;

"C"---COPY OF PENDING U.S. PATENT APPLICATION.

HISTORICAL ACCOUNTING OF SUPPORTED RESEARCH EFFORTS

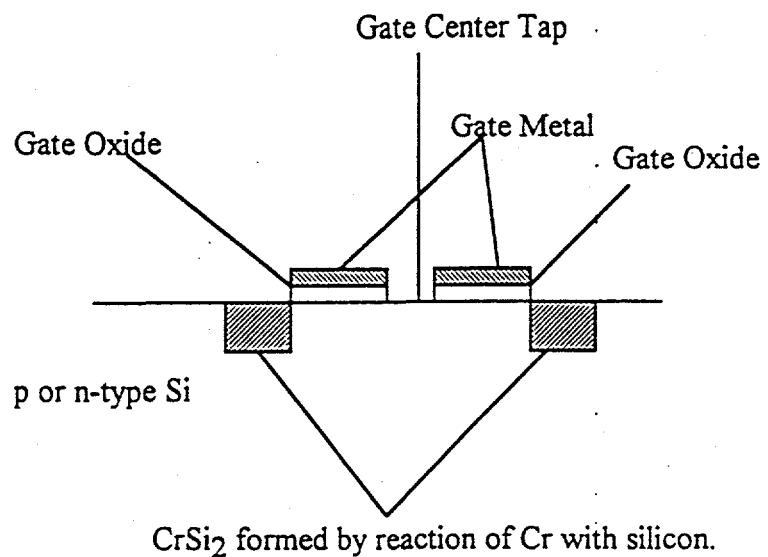

Work under DOE Grant No. DE-FG47-93R701314, to investigate a Novel Process for Fabricating MOSFET Devices, has progressed to a point where feasibility of producing MOSFETS using Chromium Disilicide Schottky barrier junctions at Source and Drain has been shown. Devices fabricated, however, show inconsistent operating characteristics from device to device, and further work is required to overcome the defects. Some fabrication procedures have produced a relatively high, (eg. ninety-five (95%) percent), yield of devices on a substrate which show at least some transistor action, while others have resulted in very low yield, (eg. five (5%) percent). Consistency of results from device to device is less than desired. However, considering that the University of Nebraska at Lincoln (UNL) Electrical Engineering Fabrication Lab is not what industry can provide, it is reasonable to project that essentially one-hundred (99.99+%) percent yield should be achievable in an industrial setting because of the simplicity in the fabrication procedure.

The Grant was initially provided to allow Research into applying the process of Patent No. 4,696,093 to the Principal Investigator Welch, to the end that MOSFET Devices would be fabricated. The goal of the work was to fabricate CMOS from seriesed N and P-Channel devices on a single substrate. While that goal was not achieved, very significant results have been achieved, and the identified goal is, with further funding, within grasp, as are additional goals identified during the work so far completed, (eg. Non-Inverting and Inverting Single Device Equivalents to CMOS, described *supra* herein).

The first Phase of the work involved obtaining supplies and then progressing to show that Chromium deposited onto N and P-type Silicon by a vacuum evaporation process, followed by an

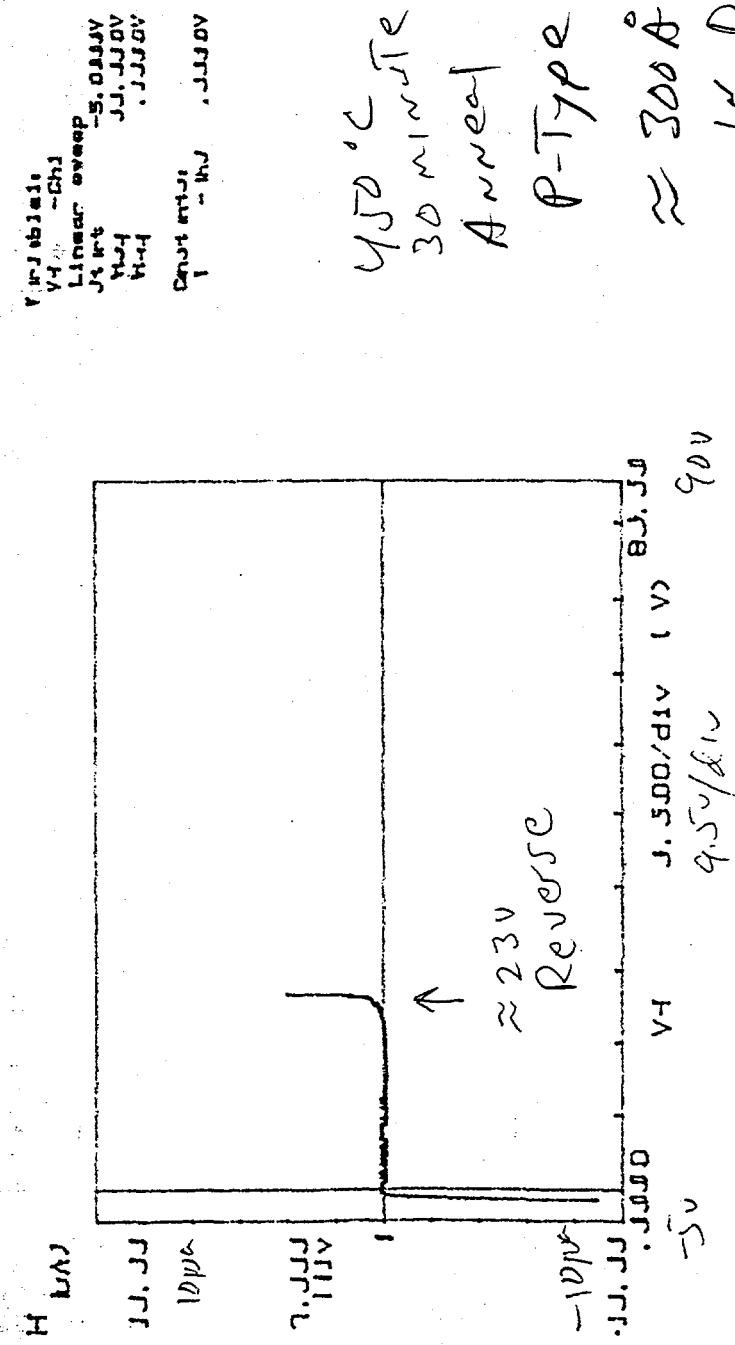

anneal process, produced rectifying junctions on both the N and P-type Silicon. The first attempt at producing said rectifying junctions was successful when Chromium was deposited onto both N and P-Channel Silicon in an electron-beam evaporator, followed by a fifteen minute anneal at 350 Degrees Centigrade. The resulting Rectifying Junctions showed Current-Voltage characteristics with a few tenths of a volt forward conduction knee, and with 20 - 30 volts Reverse breakdown. Further work revealed that if the anneal temperature was raised to above 600 Degrees Centigrade, the Reverse Breakdown Voltage was increased to near 100 volts. This occurred on both the N and P-type Silicon. (Note that this verifies the results the Principal Investigator achieved on N-type Silicon in 1974 during his Masters Research, and extends said results to the case of P-Type Silicon). It was also determined that Rectifying Junctions resulted from the above procedure when as little as eight-hundred (800) Angstroms of Chromium was deposited atop the Silicon Substrates.

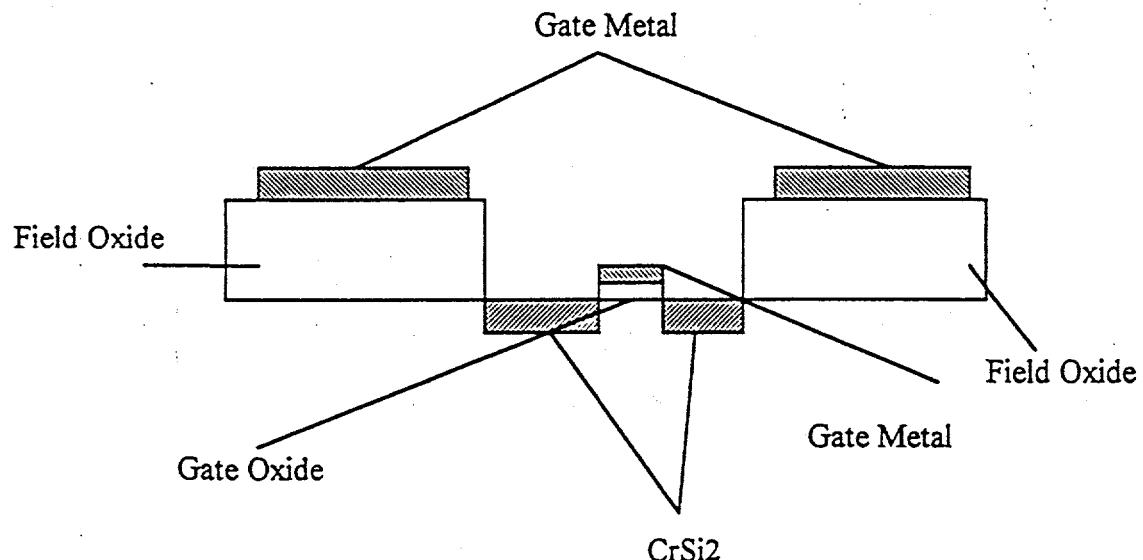

With the above results secured, attention was turned to fabricating MOSFET Devices. Masks were obtained which allowed forming MOSFET Drain-Source separated by a Gate patterns in substrates, by Photolithographic and Etching Techniques.

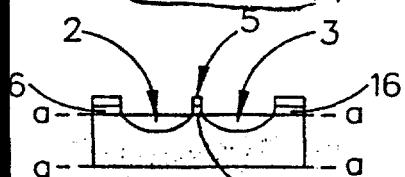

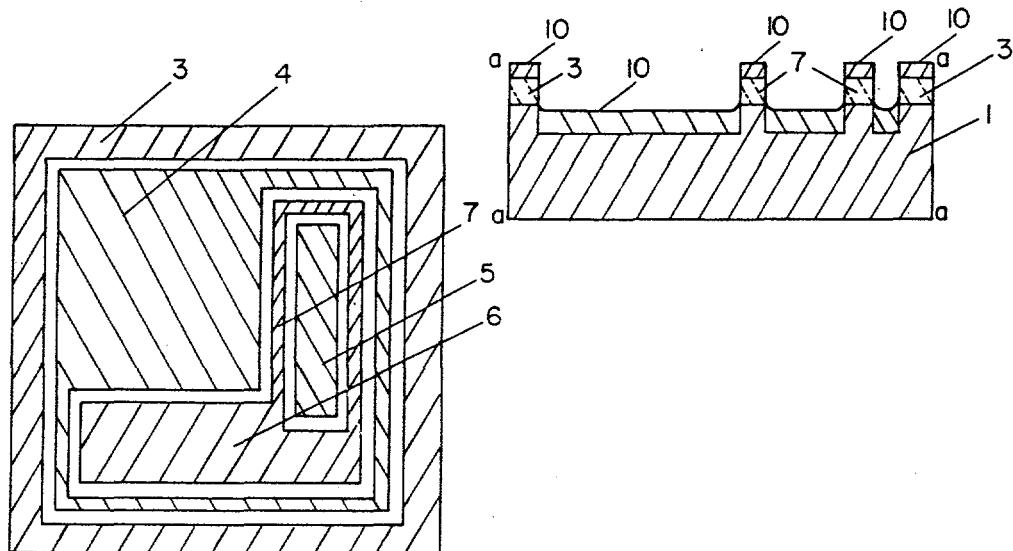

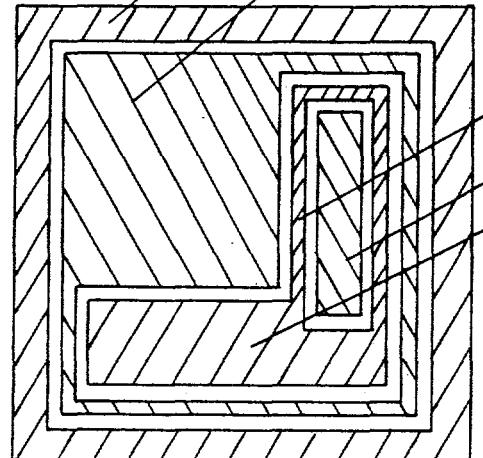

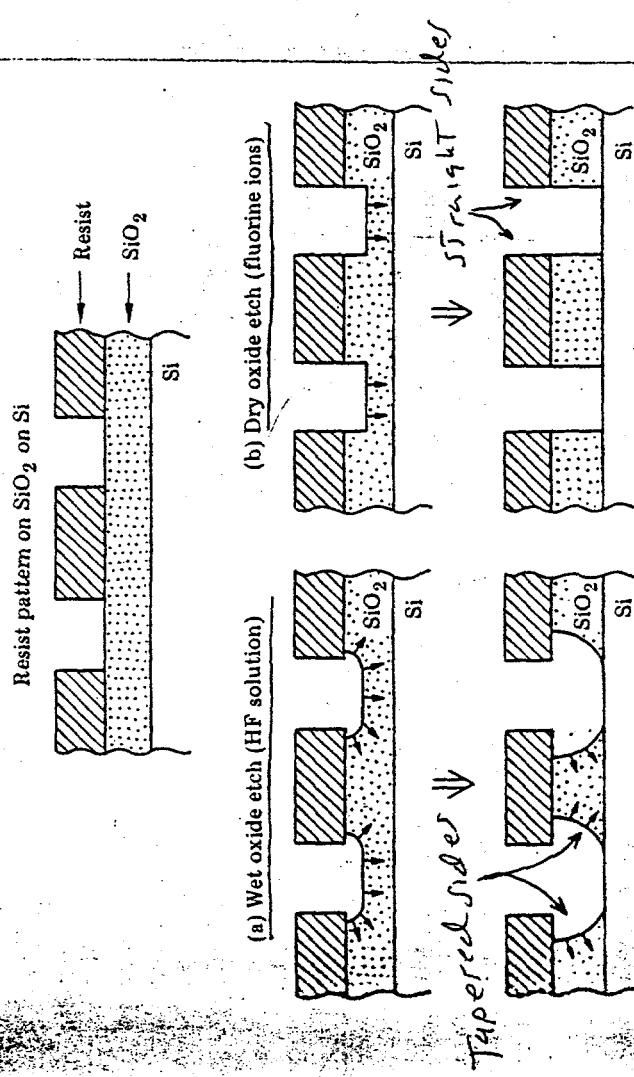

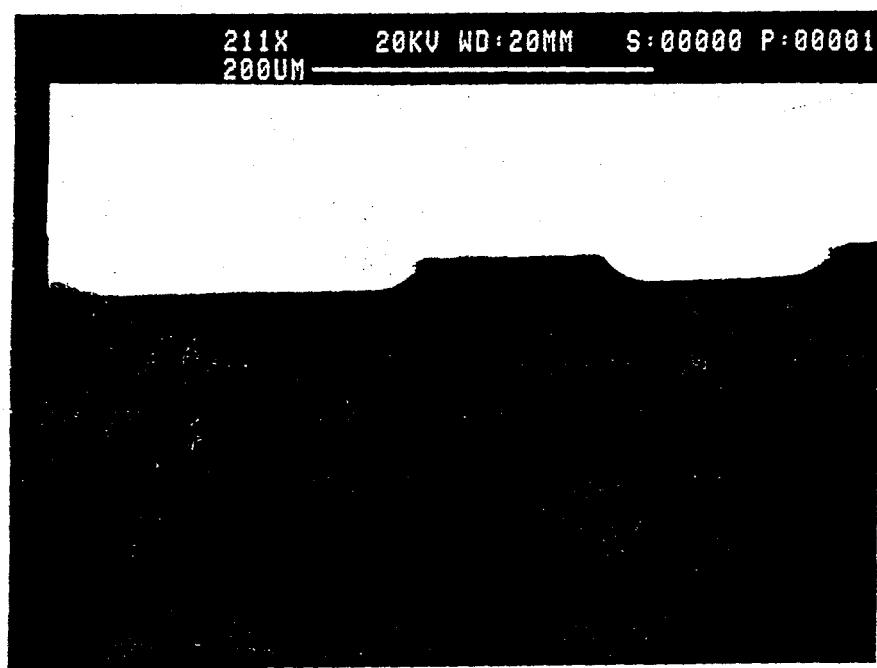

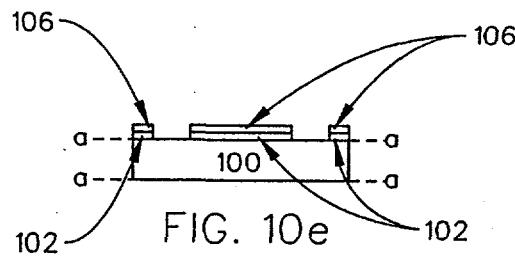

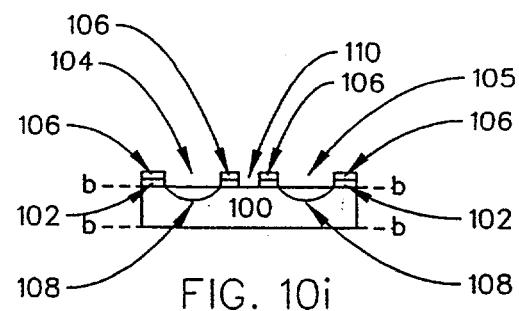

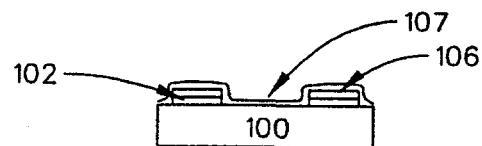

Three Thousand Angstroms of Silicon Dioxide was grown atop N and P-type Silicon substrates at the University of Nebraska at Lincoln, (UNL), in a wet steam atmosphere, and then Source and Drain openings were wet etched using Buffered Hydrofluoric acid to effect Drain and Source holes through the Silicon Dioxide to expose the Silicon. In some devices the Silicon was also etched, to depths of up to two (2) Microns. Note, that Silicon etched by wet acid techniques etches isotropically. That is, the Silicon Dioxide is laterally undercut, with respect to a Silicon Dioxide edge, by the wet acid etch, a distance approximately equal to the depth to which the Silicon is etched. Next, Chromium was deposited over the resulting substrates to a depth of eight-hundred (800) Angstroms. It was hoped that the Chromium would deposit atop the Silicon Dioxide and atop the opened Silicon such that a discontinuity would result therebetween, that the Chromium atop the Silicon would, during an anneal, form Source and Drain Rectifying Junctions, and that atop the Silicon Dioxide would act as Gate Metal. It was expected that this would occur, much as snow on stair-steps forms discontinuous vertical regions between successive steps if the snow is not too deep. It was particularly expected that this result would be achieved where the Silicon Dioxide was undercut laterally by a wet acid etch. That is, it was thought that deposited Chromium would not deposit under the edge of etched Silicon Dioxide. Many attempts at achieving this, however, were unsuccessful. When I ran into the identified problem I approached UNL Professor Ianno and inquired as to our ability to do dry plasma etching at UNL. He responded that he was an expert in the area. The reason for

Etching Silicon Dioxide by Dry Plasma Techniques is that it provides a very vertical anisotropically etched edge, as opposed to a tapered Silicon Dioxide edge result provided by wet acid techniques. The more vertical the etched edge, the more likely we could achieve a Chromium Deposition wherein the Silicon Dioxide edge was free of Chromium. Using the stair-step and snow analogy again, it will be appreciated that is easier to obtain discontinuity between vertically oriented successive steps than along a ramp. What we repeatably found, however, was that deposited Chromium was able to form a short between the Source and Drain. Somehow the deposited Chromium was able to adhere to the edges of the Silicon Dioxide, and even thereunder in laterally etched regions formed by a wet acid Silicon etch. We theorize that our Chromium Deposition technique was not sufficiently "Line-of-sight" to achieve the desired result. Deposited Chromium atoms must have been able to rebound after initial impact with Silicon and come to rest on the edges of the Silicon Dioxide, and even under laterally etched Silicon Dioxide. It is possible that the technique might still be workable, but we were not able to achieve results using it. I am maintaining my 093 Patent to the approach, as a testament to my belief that the technique can still work.

At this juncture I decided to etch the Chromium on the substrates we had produced a bit, in a wet acid etchant. I hoped that the Chromium on the edges of the Silicon Dioxide would be thinner than that atop thereof, and that I'd be able to remove just enough of it to achieve discontinuity between the Source and Drain regions and still have some present atop the Silicon Dioxide to act as a Gate. What occurred however, was that by the time I achieved discontinuity between the Source and Drain, all Gate metalization was etched away. At this point, with really no expectation of success, I decided to probe the resulting structures and apply electrical signals with the UNL Hewlett-Packard Curve-Tracer Test Set. As a bit of insight, the day I did this, (April 27, 1994), I had tickets to the Bob Dylan concert, said concert being scheduled for that day's evening. I had nothing else to do that afternoon, so decided to "play" a bit and kill time until the concert. About 2 P.M. Professor Soukup had come to the Lab to talk to his technician, and when preparing to leave looked over, saw me "playing" and commented with his dry sense of humor, (of which I am not being at all critical as it is actually similar to my own sense of humor!), "I see Jim is over there---that Jim, he has no idea what he's doing". While he was quite correct, I looked up and with a smile said "You're going to eat those words". Dan, the technician, then came over and asked me, "Don't you really know what you're doing?". I smiled and responded "All I know is he gave me an "A" in Solar Cells". With that stage set I went on "playing", and about 20 minutes later, after placing the probes on a device such that the Gate probe simply rested atop the Silicon Dioxide and the Drain and Source probes contacted the Drain and Source regions, pushed the test set button, and "ALA---MOSFET Curves appeared!". I took a plot of them and walked into Professor Soukup's office and just

stood there with the print-out held out in front of me. He looked at them and said "It looks like you have it". I agreed. Then I went and had Chinese food for dinner, then went to the Dylan Concert and then came back to the Lab for a late night repeat of the earlier success. The next day, (April 28, 1994), I "typed" the substrate which had yielded curves, using a standard semiconductor typing "Hot-Point-Probe" technique, and found that the substrate I'd worked with the day before was P-type. I processed an N-type substrate in a similar manner and found similar curves, but they were in the first, rather than third quadrant. This showed we were seeing the effect of substrate type.

(I'll add, possibly inappropriately, that being a long time Bob Dylan fan---perhaps the magic of his being in town provided the atmosphere for the breakthrough. Perhaps not. The Scientific community, at least will never buy that analysis! However, as Scientology, (which I've studied for years), teaches, intangible aesthetics do play an elusive role in success).

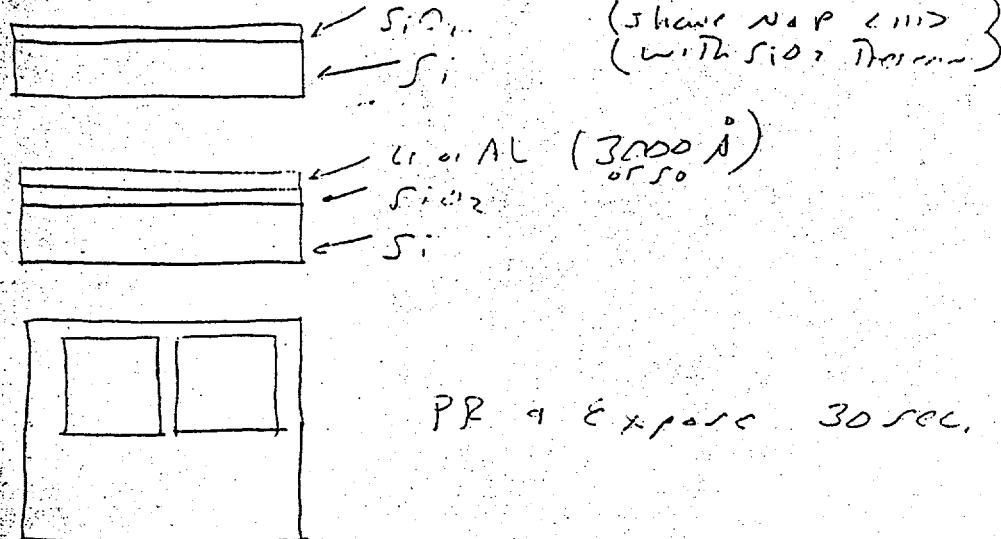

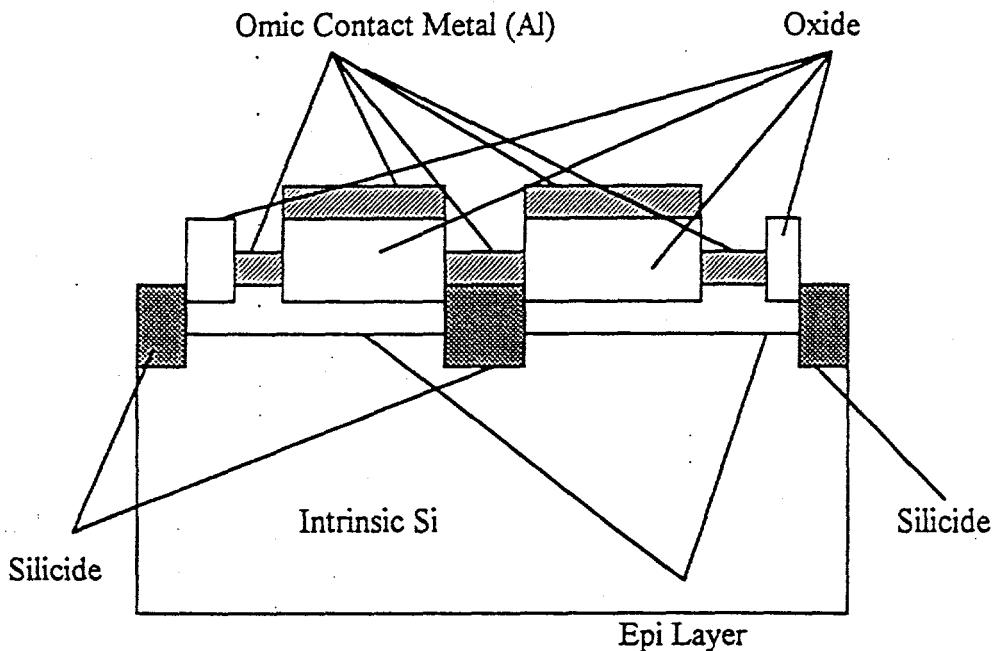

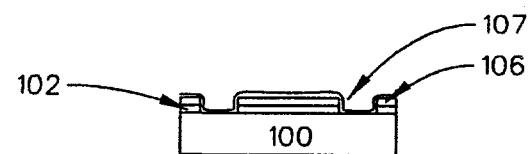

Continuing, while it had become apparent that the concept of using Chromium-DiSilicide as Source and Drain Junction material in MOSFETS was valid, it was obvious that we needed a procedure which would provide devices with a remaining Gate metal. This was so as it was difficult to set the Gate probe to achieve the curves I had stumbled onto, and once achieved, any bump of the probe stand caused them to vanish. As well, any potential industrial usage would require a gate metal be present. In consultation with Professor Ianno, the concept developed that we could add one step to the procedure and achieve the desired result. The added step was a deposition of Aluminum over the Silicon Dioxide prior to etching through the Silicon Dioxide, via the then present Aluminum, to expose the Silicon. We did this and found that we did achieve the desired structure. The reason this worked is that the wet acid etchant for Chromium does not etch Aluminum to any noticeable extent, nor does it etch Chromium Disilicide. Hence our procedure became:

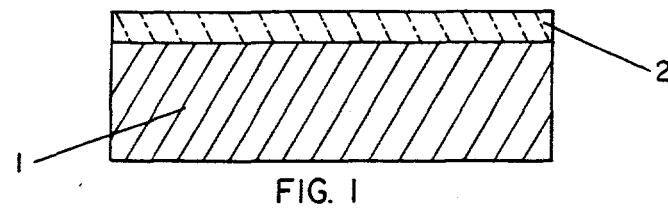

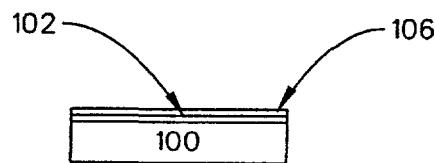

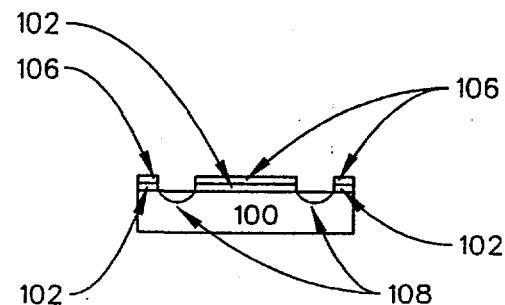

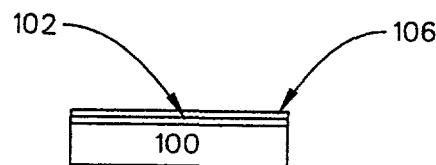

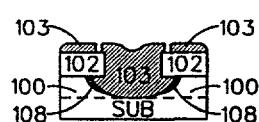

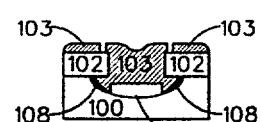

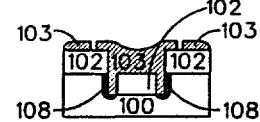

1. Provide an N or P-type Silicon Substrate.

2. Grow Silicon Dioxide atop thereof.

3. Deposit Aluminum atop the Silicon Dioxide.

4. Etch Source and Drain openings to the Silicon, through the Aluminum and Silicon Dioxide.

5. Deposit Chromium over the resulting system.

6. Anneal the System to form Chromium Disilicide in the Source and Drain Regions.

7. Etch remaining Chromium away by a wet acid technique.

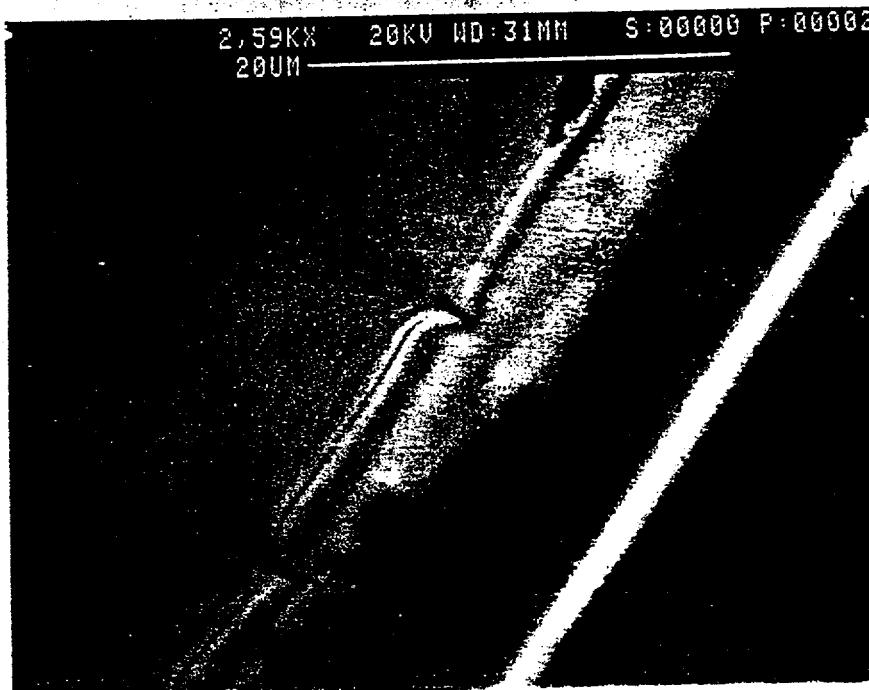

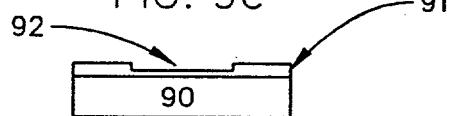

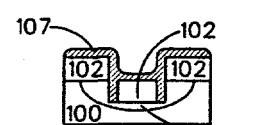

As mentioned, said procedure did provide the structure we desired. That was observable using microscopes, including an

electron-microscope. However, since I had initially stumbled onto the Curves I had achieved, others had used the test set. When I had reconfigured the test set, I could no longer repeat my previous success. This, of course, led me to speculate to myself that the Curves I'd initially achieved were not valid. Perhaps I'd configured the test set wrongly the afternoon I'd first obtained the Curves etc. Finally, approaching anger, I contacted Hewlett-Packard and questioned them as to why what I was experiencing might be occurring. In telephone discussions with a Hewlett-Packard Engineer I learned that small 1 - 2 inch long Interface Adaptors which change three prong connectors on the test set to two prong connectors for interface to the probe stand, must be of the right type to work. That is, there are multiple possible lead interconnections inside an adaptor. What I discovered was that one of the Adaptors present was simply bad. It shorted out voltage applied between its inner terminal and the outer ground braid when the voltage reached 0.7 volts. This was not detectable with an ohm meter. I'd tested it, and the other Adaptors and leads with a ohm meter earlier and did not find the problem. The problem was a true "Gotcha" using the word the Hewlett-Packard Engineer used when clueing me into the scenario. Anyway, with that known, it became apparent that when I'd achieve the Curves I had stumbled onto the afternoon preceding the Dylan Concert, the faulty Adaptor had, by blind luck, been placed upon the Source lead. When present there, shorting problems did not matter as a short is present across said lead inside the Test Set anyway. However, when the Adaptor was placed at the Drain or Gate lead, it prevented voltage from actually appearing at the Devices under test, even though the Test Set showed application thereof.

With the Test Set then working, it was discovered that nearly every substrate upon which we had fabricated devices provided some devices which would demonstrate Curves when tested. The remaining problem, however, was that the reproduceability and consistency of results was not at all under control. This problem remains.

Next, upon achieving the first Curves, I prepared a Patent Application and submitted it to the U.S. Patent Office, for the purpose of obtaining a Patent Search. That Application (Serial No. 08/250,906, filed 05/31/94), served its purpose when a First Office Action provided Patents of which I had not previously been aware. None reported investigation of the use of Chromium in fabrication of MOSFETS, but some did identify the use of Schottky barrier junctions in MOSFETS. After receiving the Office Action I was in Washington D.C. regarding some Patent work for a Medical Doctor Client, and I stopped in and saw the Examiner, (Examiner Loke), for the Application. He provided me with an additional Patent, and I did some Searching myself.

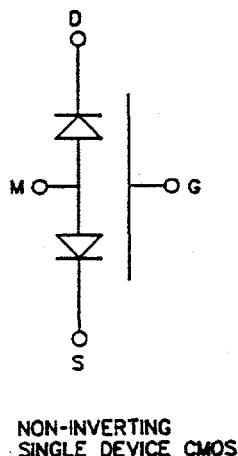

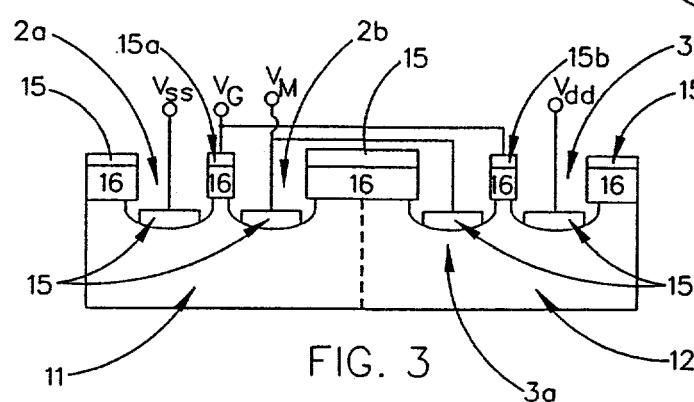

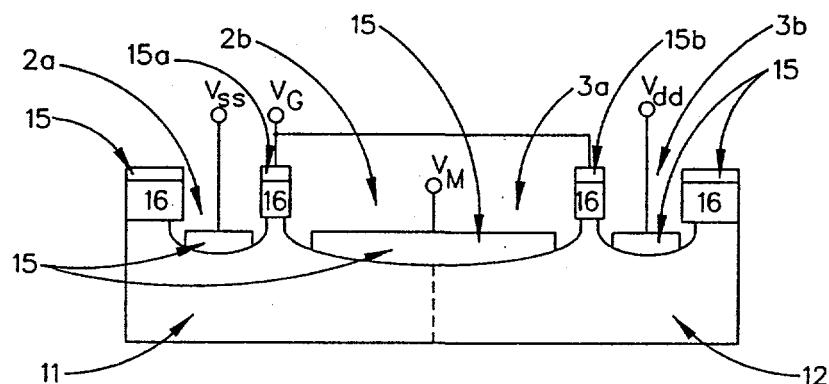

Also, another concept which had been developing in my mind for quite some time, and for which we did some initial fabrication work, has shown promising results. The concept involves production of single devices which have operational characteristics similar to multiple device CMOS systems. I am including, as Attachment "B", a Grant Proposal submitted to the Air Force SBIR Program. A similar, Application has also been submitted to the DOE Energy Related Inventions Program.

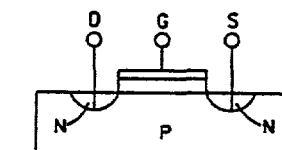

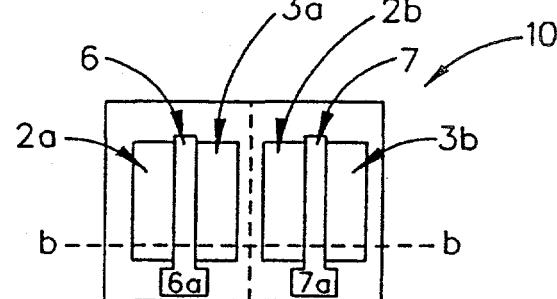

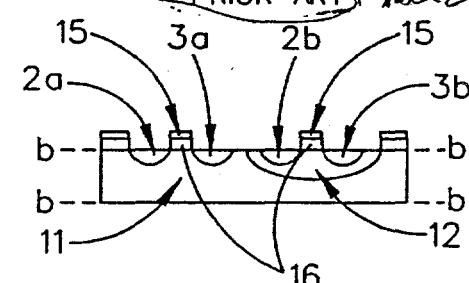

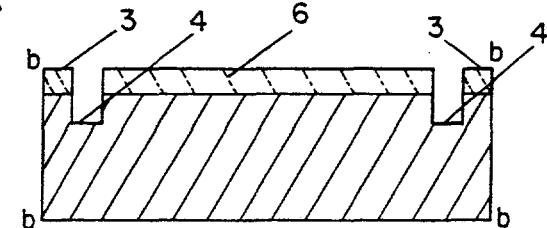

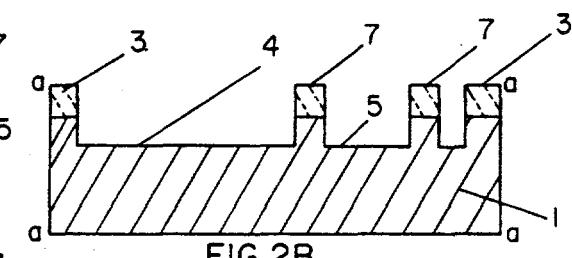

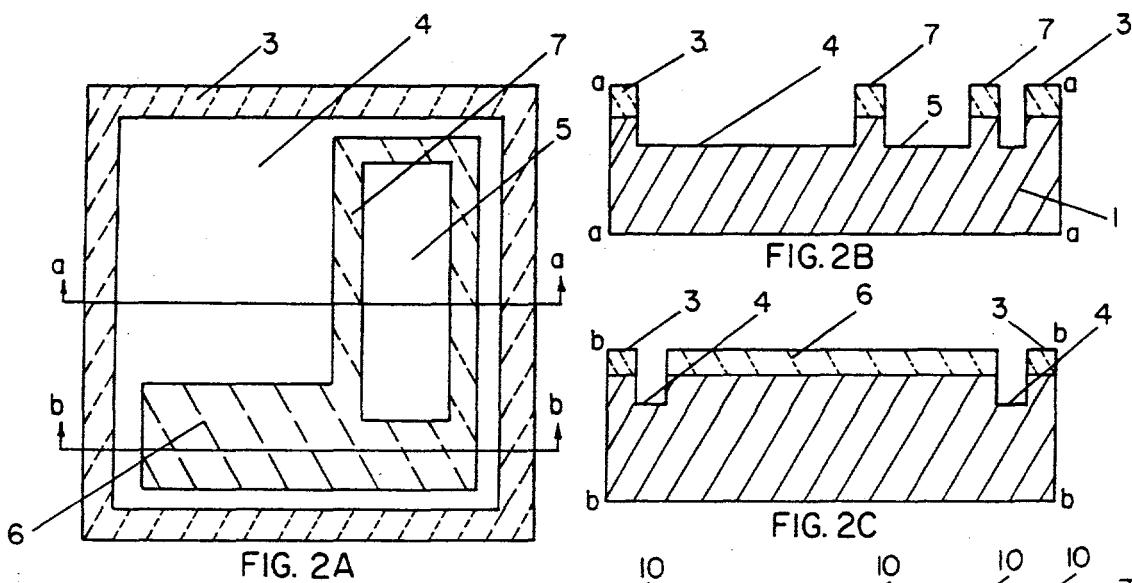

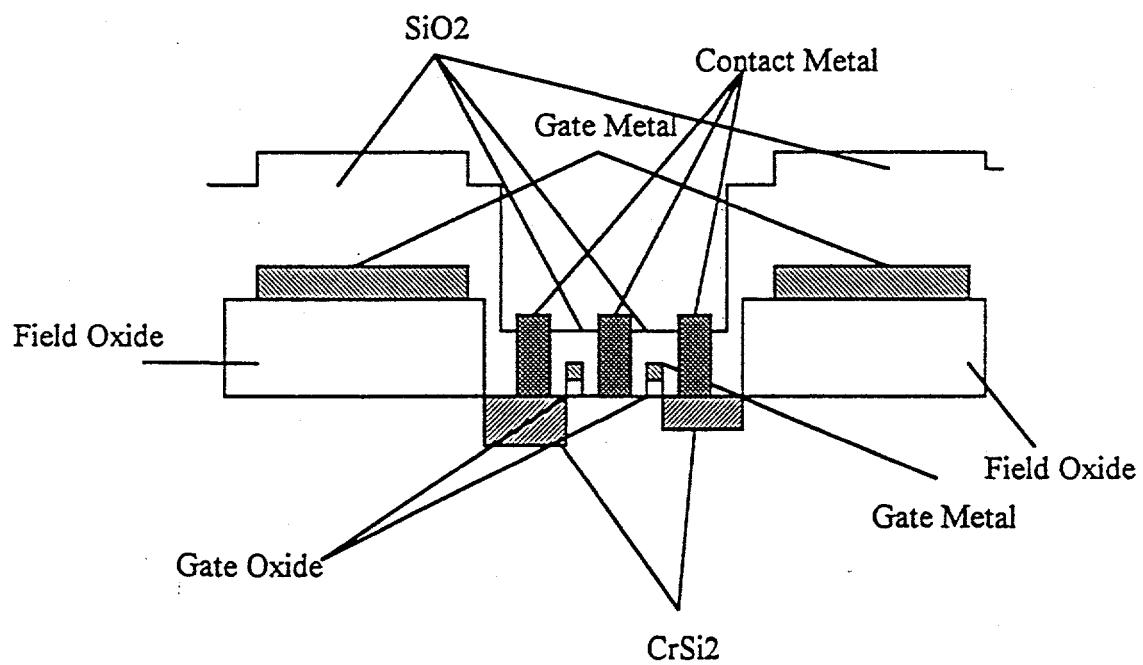

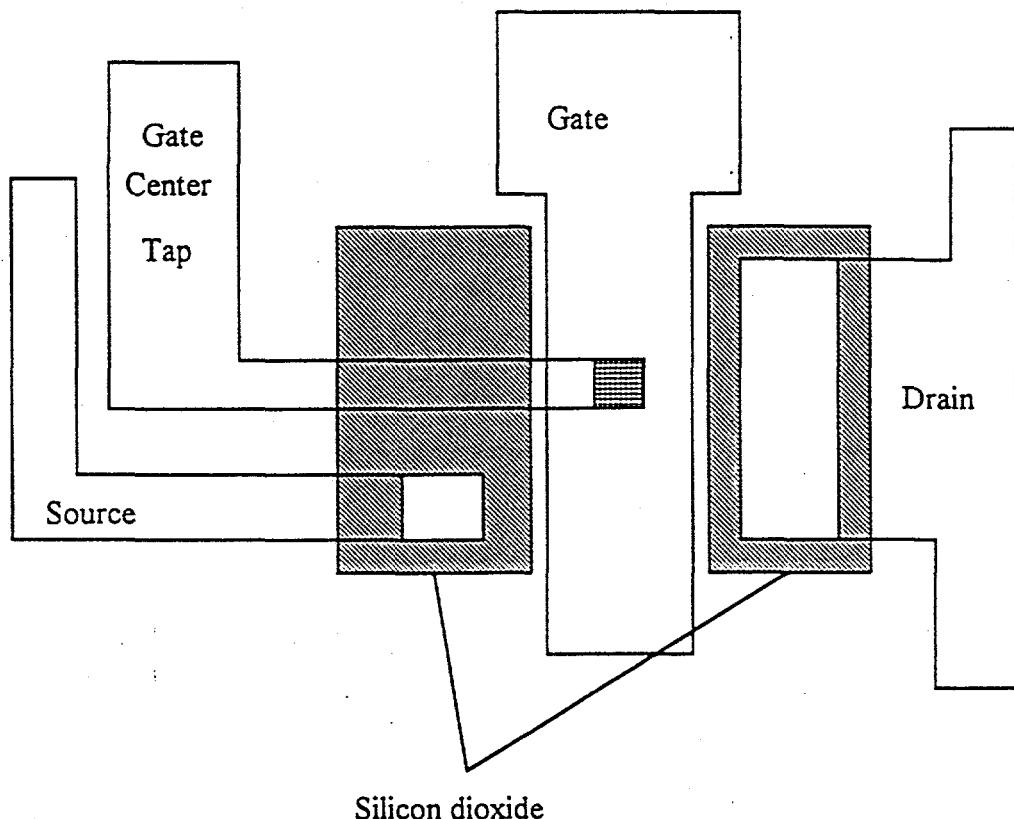

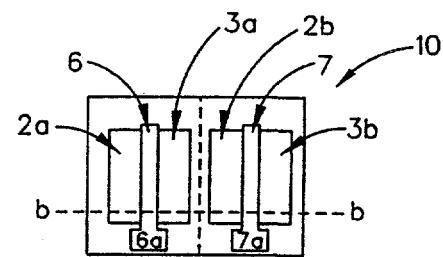

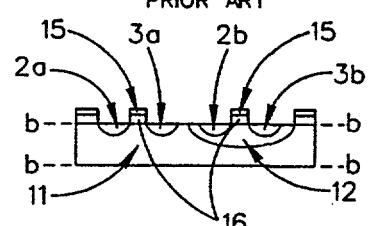

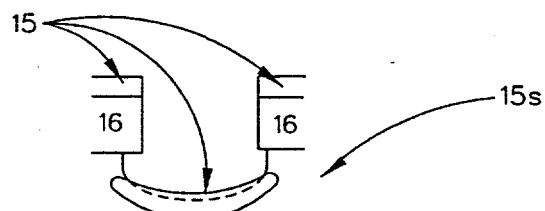

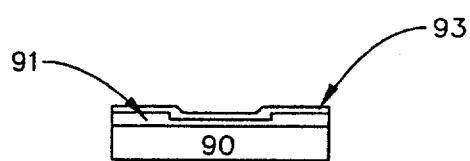

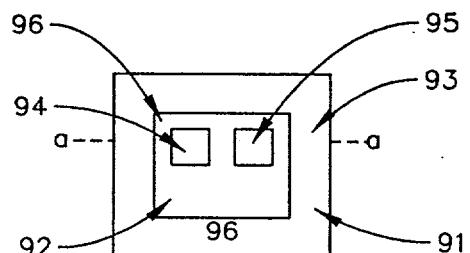

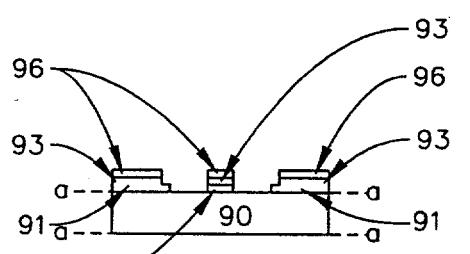

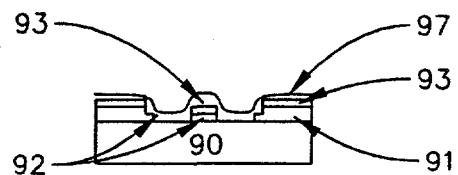

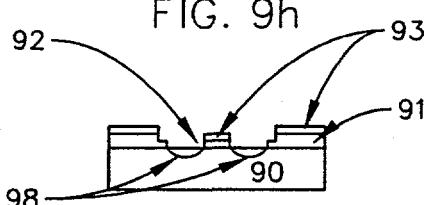

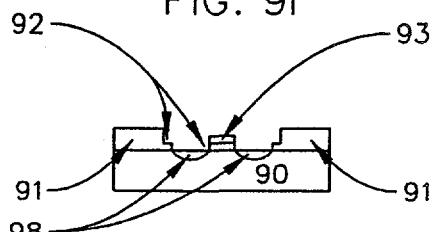

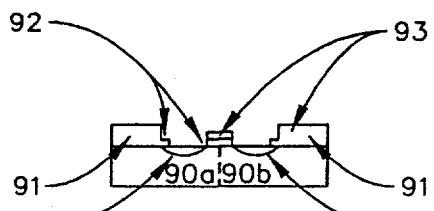

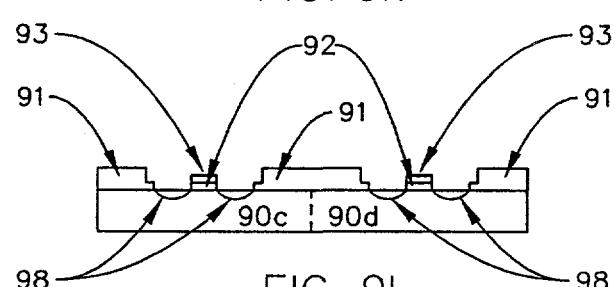

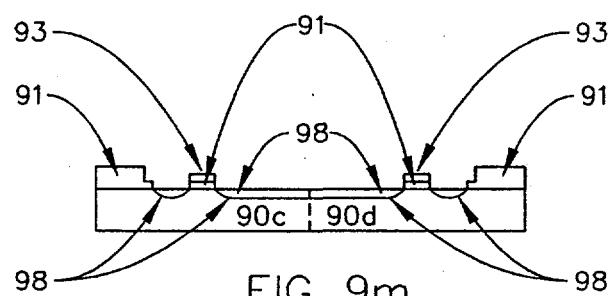

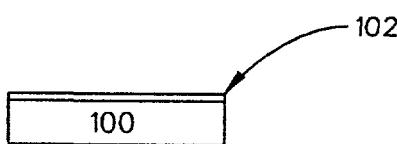

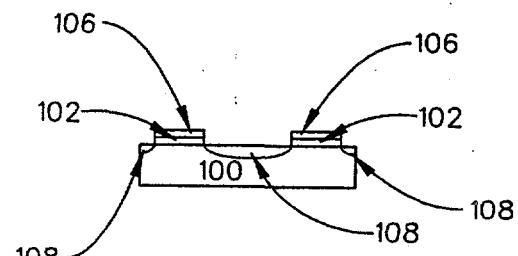

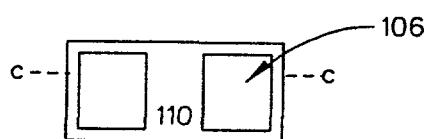

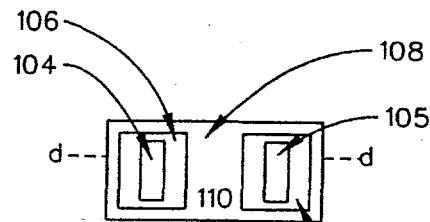

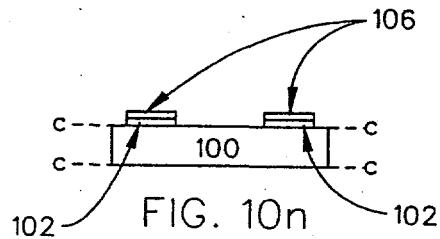

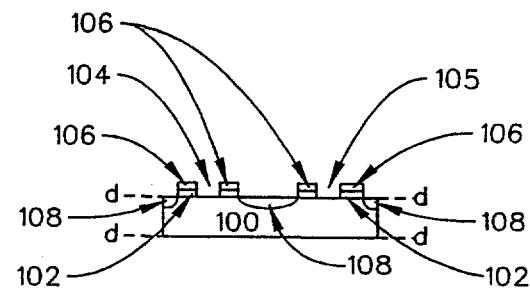

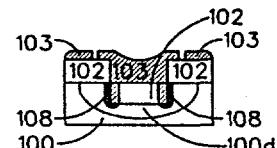

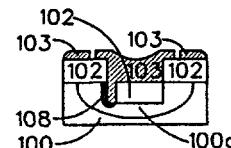

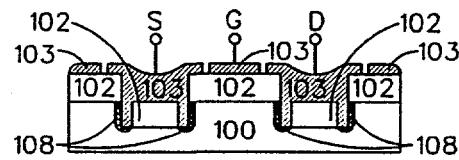

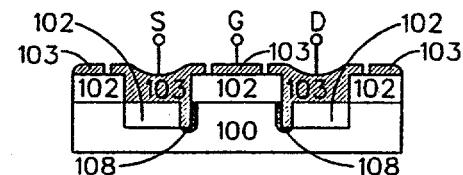

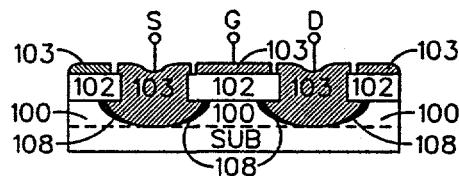

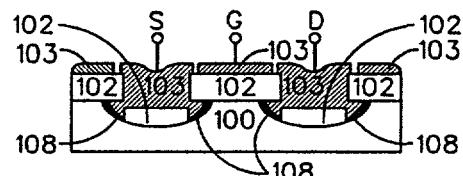

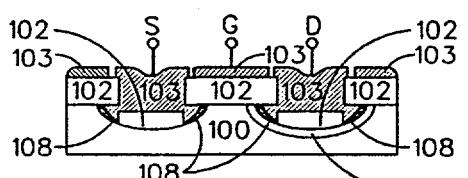

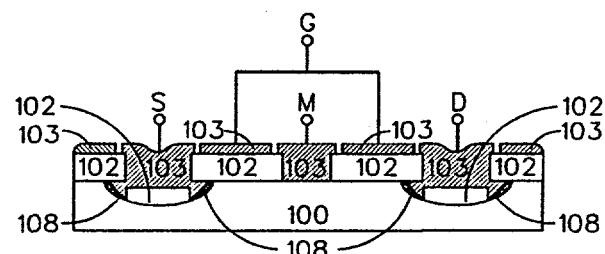

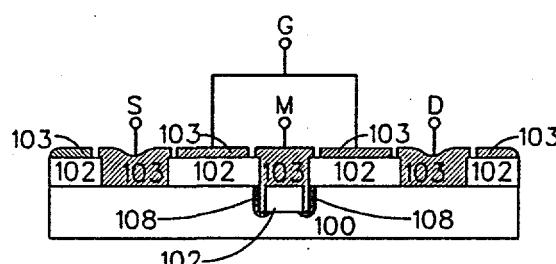

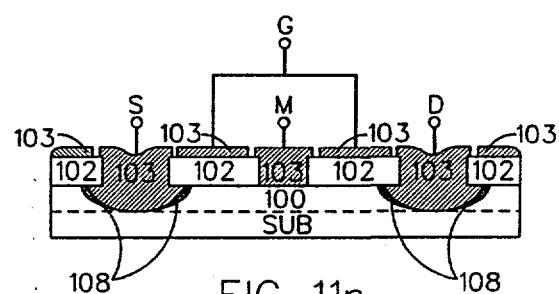

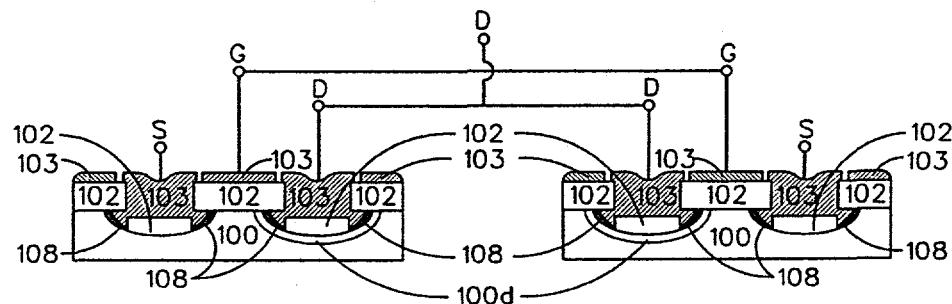

I prepared a new Patent Application which is a CIP of the first, and submitted it. The Serial No. of which is 08/368,149. The focus therein is on the Single Device Equivalents, and on the use of a fabrication technique leading to a low leakage current, limited Schottky barrier cross sectional area geometry. Use of isotropic Silicon etching, and selective Silicon Dioxide growth provides a structure in which the Schottky barriers are present only at the ends of channel regions in MOSFETS, said Schottky barrier junctions being present under Gate Silicon Dioxide. A copy of the Patent Application is included in Attachment "C".

Directly following is an Analysis of how the Fabricated devices are probably operating.

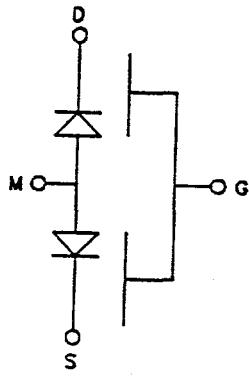

## ANALYSIS OF SCHOTTKY BARRIER MOSFET DEVICES

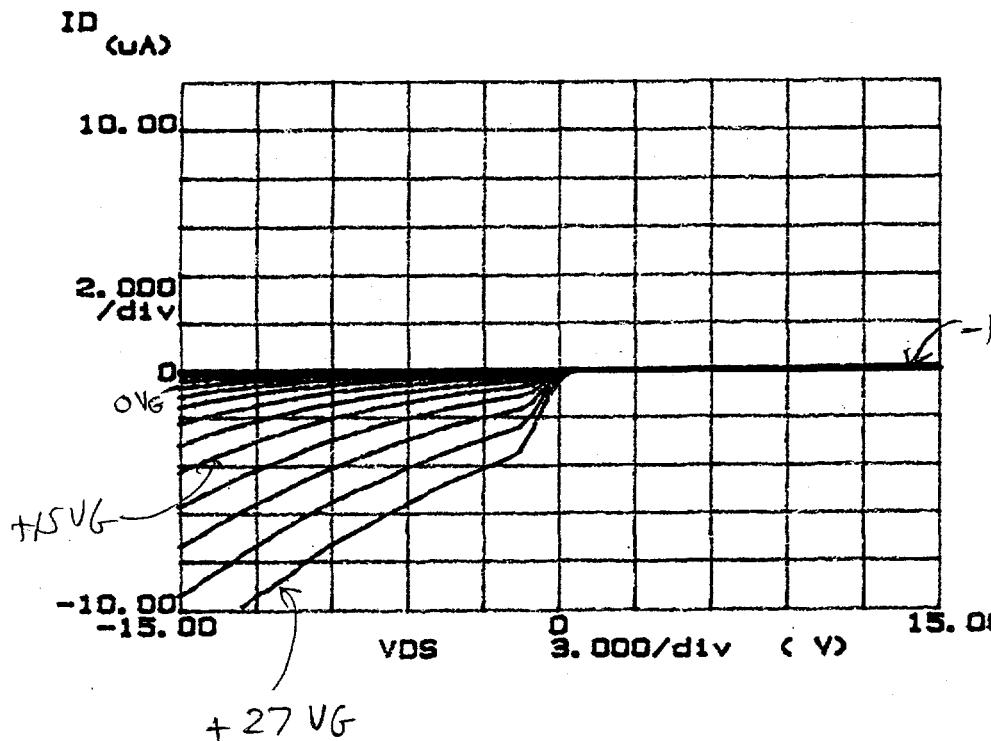

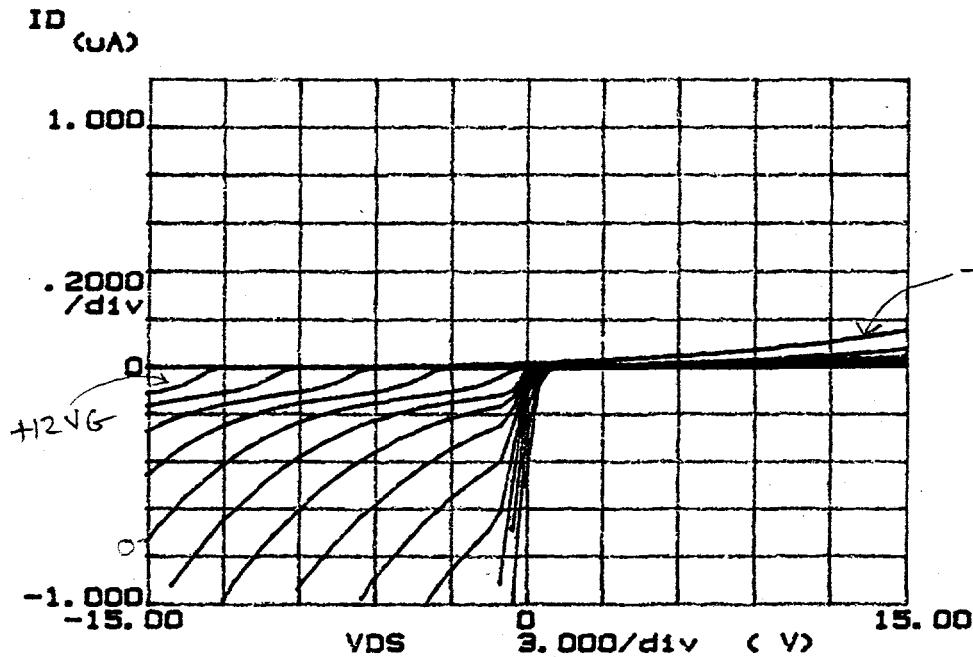

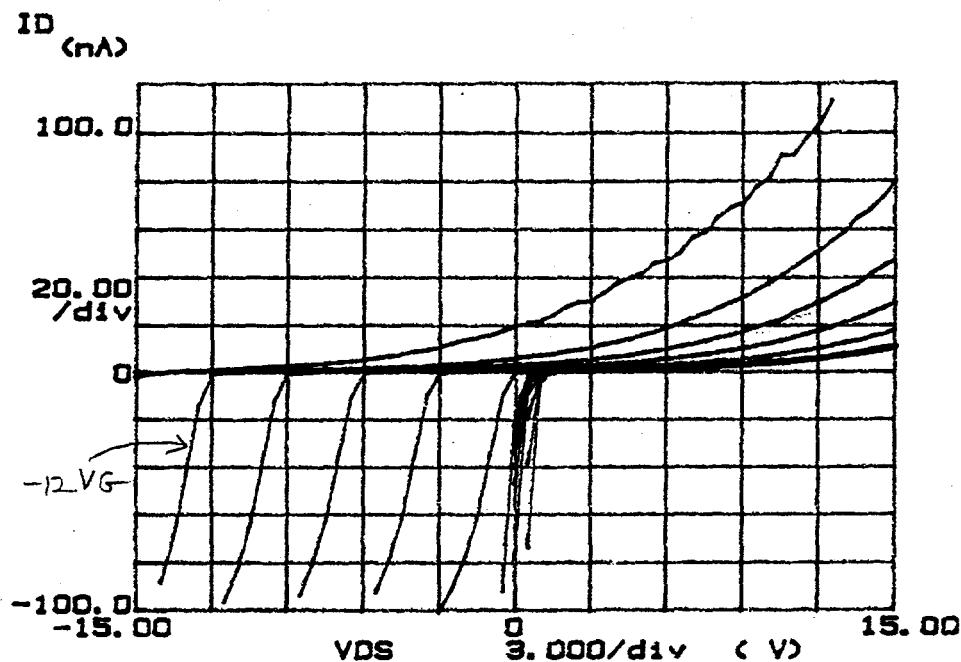

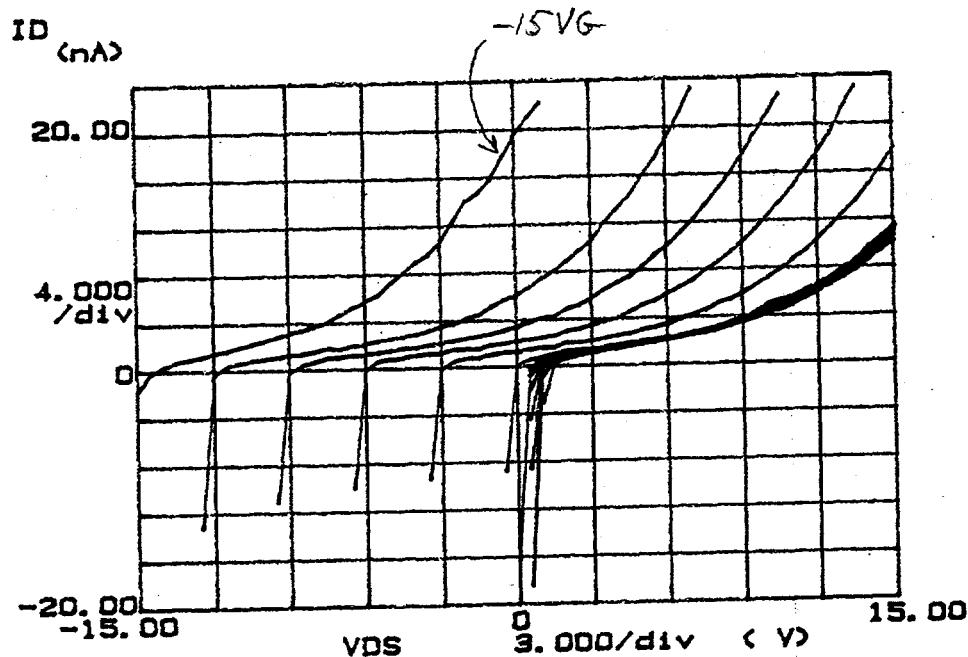

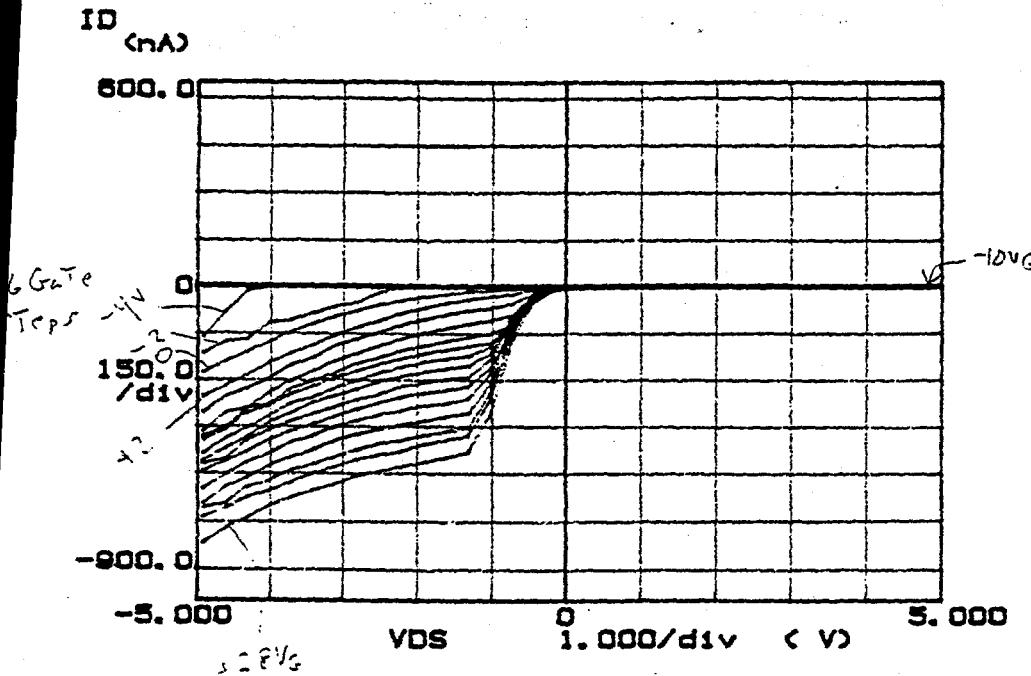

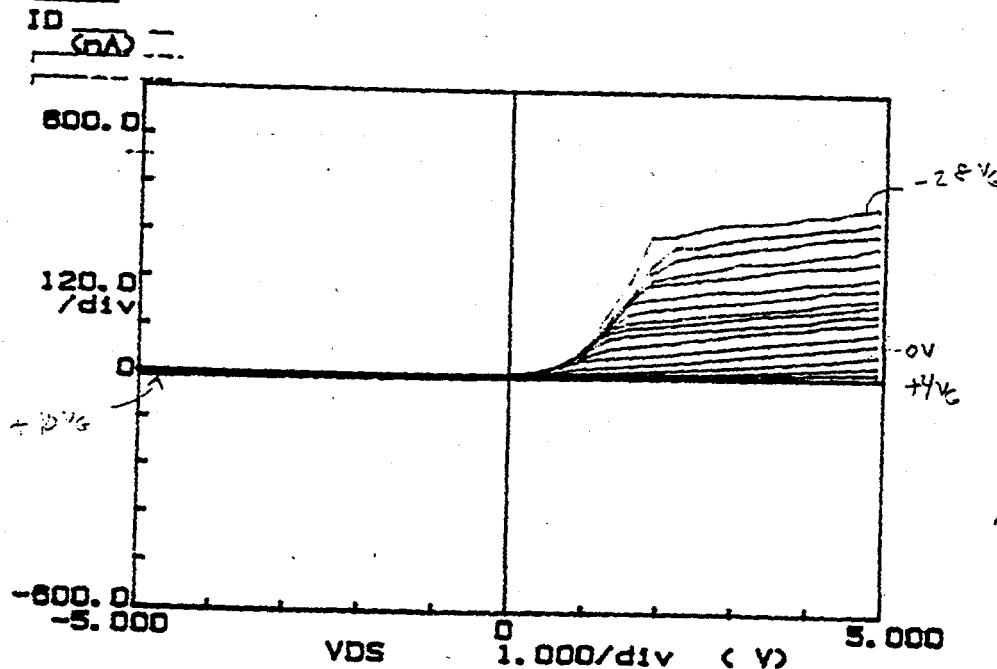

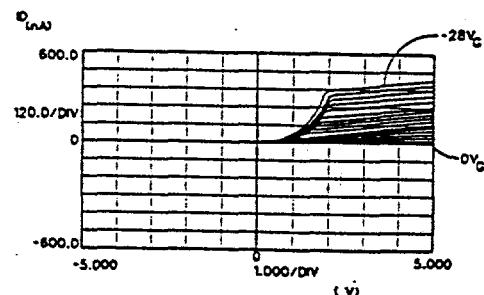

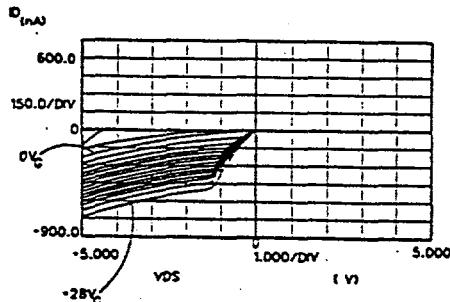

In view of the fact that Schottky barrier MOSFETS fabricated under the DOE support are essentially two Schottky barrier Junction Rectifying Diodes, oppositely directed, in the surface region of a Silicon substrate, which Diode Junctions are separated by a Channel Region, the Effective Doping Level in which can be controlled by application of a Voltage to an associated Gate, it might be predicted that certain Device operating characteristics should be expected. As the Junctions formed are Rectifying on either N or P-Type Silicon, application of a Drain to Source Voltage of either Plus or Minus Polarity to devices fabricated on either N or P-Type Silicon should be expected to cause one of the Diode Junctions to be Forward Biased, and one Reverse Biased on either type Silicon, (whether Metalurgical or Field Induced). Some Reverse Biased Tunneling Current, limited by the Diode which is Reverse Biased, would be expected to flow through the seriesed connection of Diode Junctions, but sufficient applied voltage across said seriesed connection of Diode Junctions should provide essentially symmetrical Reverse Breakdown increased current flow. We do see such in the Devices fabricated on both N and P-Type Silicon, with Tunneling current prior to Reverse breakdown on the order of tens to hundreds of nanoamps, and with Reverse Breakdown typically occurring at between 15 and 30 volts, leading to the flow of microamp and above currents. (Note that the Reverse Breakdown Voltage of a formed Junction seems to be a function of the Temperature at which the Diode Junctions are formed by annealing Chromium to Doped Silicon. The 15 to 30 volt figure corresponds to formation at approximately 450 to 550 Degrees Centigrade, while we have seen Reverse Breakdown occur at approximately 80 to 100 volts where the formation temperature was on the order of 600 to 650 Degrees Centigrade). One might also expect that application of either polarity voltage to the Gate should lead to a result of increased current flowing between the Drain and Source as a result of Field induced Channel Region Effective Silicon Doping Levels, and the effect such has on Reverse Bias Tunneling Currents. That is, the higher the Effective Doping Level of the Channel Region, the more Reverse Tunneling Current should be observed through the Reverse Biased Junction. This is because the Channel Region is simply the Semiconductor portion of a Schottky Barrier Junction, and it is well known that the more highly doped a Semiconductor in a Schottky Barrier Junction, the more Reverse Tunneling Current will flow therethrough at a certain applied Reverse Voltage. This would be expected whether the increased Doping is Metalurgical or Field induced. In fact, at a high enough Schottky barrier Semiconductor Doping Level, the Junction will become essentially "Ohmic". At the practical levels of Gate Voltage investigated, (eg. -15 to +30), we do in fact see a Gate Voltage effect on the current flow when the Gate

Voltage is of a polarity so as to Invert the Channel Region Doping Type and the applied Drain to Source Voltage is of a Polarity so as to effect a reverse Bias at the Drain Junction with respect to the Inverted Channel Region, and a Forward Biased Source Junction. However, we do not see such occur where the Gate Voltage is of a polarity which should accumulate the Channel Region, or where the Drain to Source Voltage is of a polarity so as to cause the Source Junction to Reverse Bias, even where the Channel Region is Inverted. This, to some extent, was not what I expected to find, but it is what we have found in all operational Devices fabricated. As well, we see a fairly large Drain Current flow, (far greater than Reverse Bias Tunneling Current), when zero Gate Voltage is applied and the Drain to Source Voltage Polarity is such as to Reverse Bias the Drain Junction with respect to an inverted Channel Region, but the current flow level is very much less, (on the order of Reverse Bias Tunneling Current), when the Drain to Source Voltage Polarity is reversed. The relatively large Drain Current flow which occurs at zero applied Gate Volts when the Drain to Source Voltage Polarity is such as to Reverse Bias the Drain Junction with respect to an Inverted Channel Region is Decreased by application of a Gate Voltage of a polarity opposite to that required to invert the Channel Region, and is Increased by application of a Gate Voltage of a polarity appropriate to Invert said Channel Region. As plotted against a sweeping Drain to Source Voltage said Decreased Drain Current Curves appear similar to those of a current flowing through a diode-resistor, (ie. the Drain Schottky barrier Junction and the Oxide Resistance), combination beginning where said sweeping Drain to Source Voltage just overcomes an applied Gate Voltage and effects a Forward Bias thereto, as would occur if the Channel Region were not yet Inverted and the Drain Junction were actually Forward Biased for instance; and said Increased Drain Current Curves present with typical MOSFET-like Saturation Drain Current Characteristics. (It is noted that what would be expected is only a relatively small Reverse Bias Tunneling Current flow in either direction with zero Gate volts applied). To understand the outlined empirically achieved results requires a step by step analysis, but reasonable explanations for the observed results are available if we assume operation as a MOSFET. Said explanations are entirely consistent with MOSFET operation, but vary considerably from explanations appropriate to explain Diffused Junction MOSFET operation. Assumption of other modes of operation, (eg. Bipolar Transistor), have not been found appropriate or able to account for what we find by investigation of fabricated devices.

#### STEP BY STEP ANALYSIS OF FABRICATED SCHOTTKY BARRIER MOSFETS

Analysis of the fabricated Chromium-disilicide MOSFETS must be approached in stages depending upon what polarity voltages are

applied to the Drain and Gate with respect to the Source. Also, assumption of a Device Defect, namely the presence of Leaky Silicon Dioxide (Oxide), which is prone to "Breakdown" conduction, is necessary to make sense of the empirically obtained results.

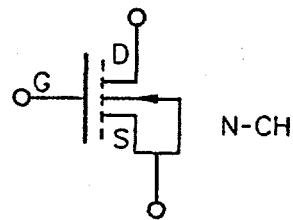

CONSIDER AN N-CHANNEL MOSFET FABRICATED ON P-TYPE SILICON.

(AN ANALOGOUS ANALYSIS APPLIES TO A P-CHANNEL DEVICE WITH THE VOLTAGE POLARITIES APPLIED TO DRAIN AND GATE REVERSED).

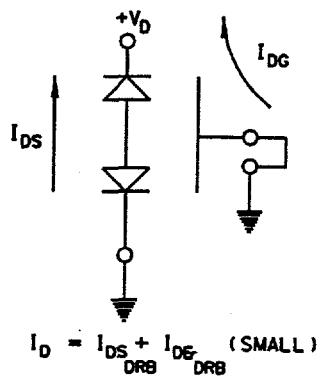

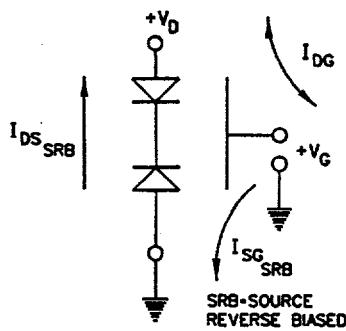

CASE 1. DRAIN TO SOURCE VOLTAGE POSITIVE (+) POLARITY

a. Application of Zero (0) Gate Volts, but gate circuit present. Current can flow through Reverse Biased Drain Junction and through parallel combination of two circuits, namely (1) a Channel Region in series with a Forward biased Source Junction, and (2) a Channel Region in series with a leaky Gate Oxide and Gate Circuit. However, note that the Gate Voltage is less Positive than the applied Drain Voltage and that the Gate sees a P-Type Silicon through a Leaky oxide, thereby effecting a Reverse Bias between the Drain and the Gate.

b. Application of Negative (-) Gate Volts. This will tend to accumulate the Channel Region and thereby effect a lower resistance Channel Region. Such can increase the tunneling current flow through the Reverse Biased Schottky barrier Drain Junction, (of which the Channel Region is the Semiconductor component), and in combination with the reduced Channel resistance increase current flow through the Forward Biased Source Junction. A negative Gate voltage will see a P-Type Silicon through a leaky Oxide, hence, a Reverse Bias situation with respect to the Drain, and Source Junctions, through leaky Oxide. This could serve to increase current flow through said Leaky Oxide and Gate Circuit, from the Drain Junction to a higher value than with Zero Gate Voltage present. The magnitudes of the currents are found to be on the order of relatively small Reverse Bias Tunneling Currents however. Said Currents are orders of magnitude less than those seen when the Drain has a Negative Polarity Voltage applied thereto and the Gate is provided a Positive, Channel Region inverting, Voltage,

BUT REVERSE BIAS DRAIN JUNCTION CAN BREAK DOWN

BEFORE CHANNEL INVERSION

$$V_D > V_G$$

$$I_D = I_{DS_{DRB}} + I_{DG_{DRB}} \text{ (SMALL)}$$

$$V_D < V_G$$

$$I_D = I_{DS_{DRB}} - I_{DG_{DRB}}$$

$I_{DG}$  COULD BE LARGE FORWARD BIAS CURRENT BUT WE DON'T SEE THIS OCCUR AS CHANNEL INVERTS AT LOW  $V_G$

$I_{SG}$  COULD BE LARGE FORWARD BIAS CURRENT IF CHANNEL DOESN'T INVERT

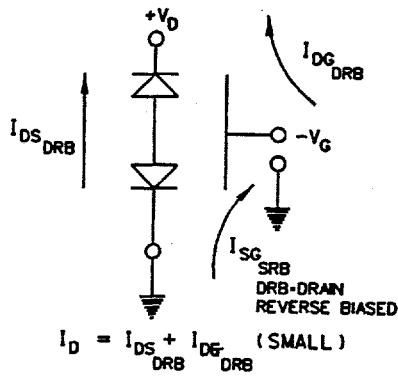

AFTER CHANNEL INVERSION

$$V_D > V_G$$

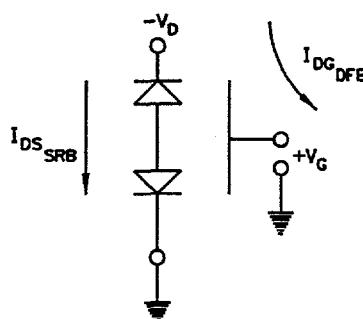

$$I_D = I_{DS_{SRB}} + I_{DG_{DRB}} \text{ (SMALL)}$$

$$V_D < V_G$$

$$I_D = I_{DS_{SRB}} - I_{DG_{DRB}}$$

PINCHOFF LIMITS GATE VOLTAGE MODULATION OF  $I_D$  AT REVERSE BIASED SOURCE

(see supra Case 2c). Apparently, Gate Voltage Modulation of Accumulation Effective Channel Doping has little effect on increasing Reverse Bias Drain Junction Tunneling Current by increasing effective non-Inverted Channel Region Doping Levels. Perhaps Conduction and Valance Energy Band Pinning, (as is known to occur in Schottky barrier Junctions), can not be significantly affected at the actual Schottky barrier Metal-Semiconductor Interface by an applied Gate Voltage in a Metalurigical Junction, whereas it can have a significant effect in Field Induced Schottky barrier Junctions. This interpretation is consistent with the Results we have obtained and I have found it a convenient thought aid to date. It might also be expected that at high Negative Gate Volts and High Positive Drain Volts the Reverse Biased Drain Junction might break down and allow Drain Current to flow. We do see a trend theretoward at times.

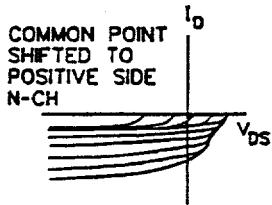

c. Application of Positive (+) Gate Volts. Positive Gate Voltage serves to immediately reduce the Reverse Bias present between the Gate and Drain which results from Applied Positive Drain Voltage, and if the Gate Voltage is increased enough to exceed the Applied Drain Voltage one might think that a Forward bias situation would develop at the Drain Junction, from the Gate through Leaky oxide. This, however, does not occur, as another effect apperantly dominates, that being MOSFET action Channel Region Inversion. This causes the Channel Region to become N-Type. Now, an N-type Channel with a Positive Drain Voltage applied means the Drain Junction will go Forward Biased and the Source Junction will become Reverse Biased as seen from the Drain. The Gate Circuit will see N-type Silicon through a leaky Oxide and could be part of a Forward Biased Drain to Gate Circuit where the Positive Applied Gate Voltage is less Positive than the Applied Positive Drain Voltage. This would be expected to cause a relatively high Forward Bias current flow through the Gate Circuit from the Drain. We do not see this occur however. Likewise one might expect to see a relatively high current flow through a Gate Voltage Modulated Silicon Doping Effect at the then Reverse Biased Source Junction. We do not see this occur either. (Note as will be

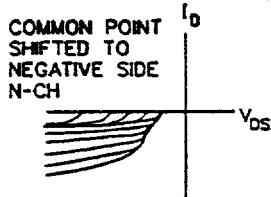

described supra, in Case 2c, when an Inverted Channel Region exists and the Drain Junction is Reverse Biased, that is when applied Gate Voltage is Positive and applied Drain Voltage is Negative, we do see relatively high, applied Gate Voltage Modulated Drain Current flow, which Drain Current vs. Drain to Source Voltage Curves demonstrate "Saturation" Characteristics). What seems to occur when the Applied Drain and Gate Voltages are both Positive is that the Gate and Drain Voltages effect a Channel Region "Pinch-Off" such as that which causes Current Flow Saturation in Diffused Junction MOSFETS, and said "Pinch-Off" Region drops, (ie. "absorbs"), the Applied Drain Voltage. Said "Pinched-Off" Channel Region serves to shelter the Reverse Biased Source Junction so no Tunneling Current Flow Driving Force appears thereacross. This, at least, is a plausible explanation which seems to account for the results we achieved by empirical test of fabricated devices. (Note also that in some devices we see Drain Current Flow starting from a "Common Point" along the Drain to Source abscissa, on the Positive Drain Voltage side of Zero (0) Drain Volts, (eg. at approximately +2 Volts or less). Said Drain Current Flow merges into Saturation Drain Current Flow Characteristics as the applied Drain Voltage sweeps Negative, (see Case 2c supra). I think this occurs where a loss of Channel "Pinch Off" occurs, (as is expected to occur as the Positive Drain Voltage decreases, but which normally occurs at Zero (0) applied Drain to Source Volts), thereby presenting the difference in Voltage Applied to the Gate and that Applied to the Drain across the Oxide, which Oxide then apparently breaks down and allows Current to flow through a Forward biased Drain Junction, atop a Source Junction which remains Reverse Biased prior to Channel Region inversion.

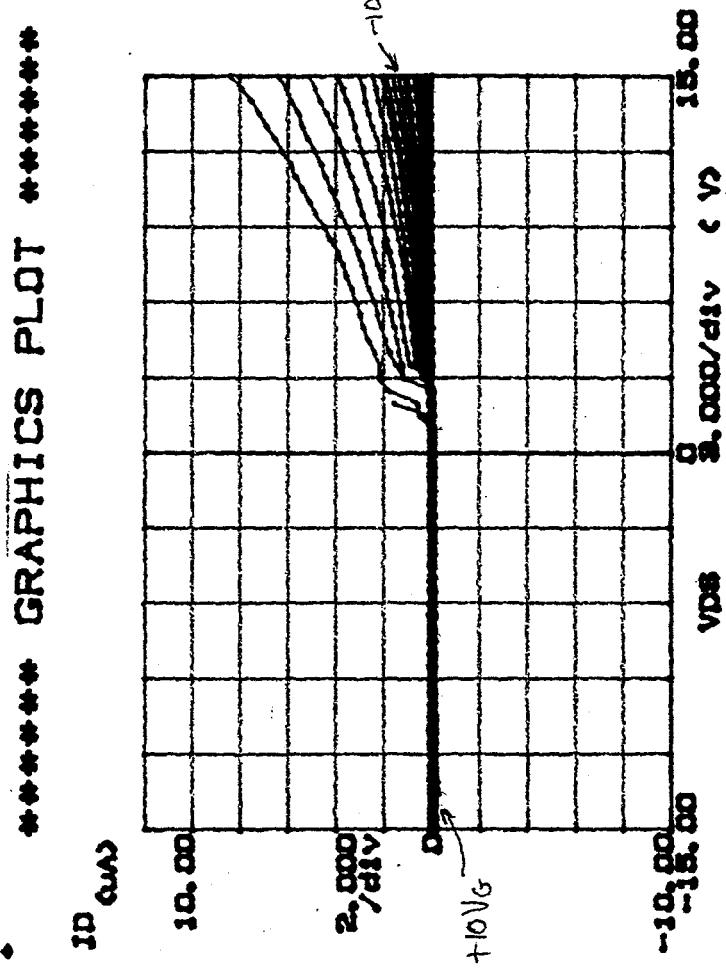

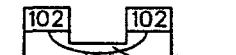

FIG. 20

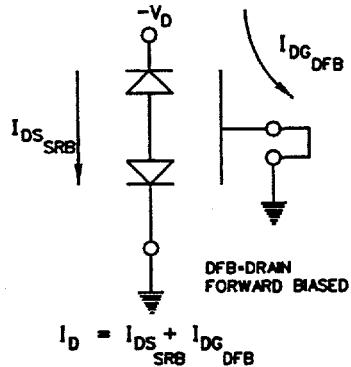

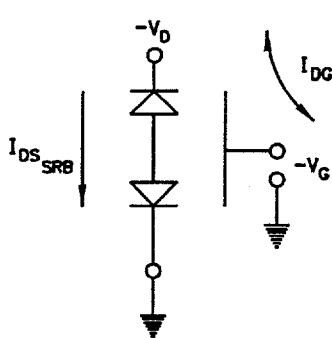

#### CASE 2. DRAIN TO SOURCE VOLTAGE NEGATIVE (-) POLARITY

a. Application of Zero (0) Gate Volts, but Gate Circuit present. Current can flow through a Forward Biased Drain Junction and into a P-Type Channel Region, then through a parallel combination of 1. a Gate Circuit through Leaky Oxide, and 2. a Reverse Biased Source Junction. What we see is a relatively high Drain current flow which originates near the Drain to Source Zero (0) Voltage point and increase as the Drain Voltages is swept more negative. The shape of the Drain Current Curve is like that of a current flowing through a diode and a resistor in series.

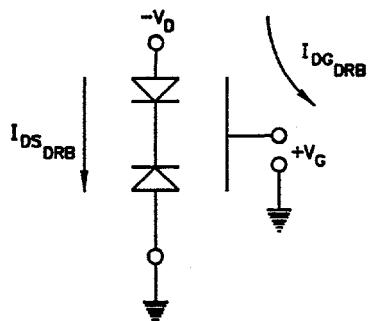

$$V_D > V_G$$

$$I_D = I_{DS_{SRB}} + I_{DG_{DFB}}$$

$$V_D < V_G$$

$$I_D = I_{DS_{SRB}} - I_{DG_{DFB}}$$

b. Application of Negative (-) Gate Volts causes the relatively high Drain Current which flows at Zero (0) applied Gate Volts to decrease, with each applied Negative Gate Voltage being associated with a different origin point at which Drain Current begins to flow. That is, if a Negative 2 Volts is applied to the Gate, the Drain Current flow is relatively low until the Drain to Source Voltage sweeps more negative 2 volts, and then said Drain Current flow increases, with the Curve thereof as the Drain Voltage sweeps being again like that of a diode in series with a resistor. To understand this one must recognize that said Gate Voltage will be applied to a P-Type Silicon through Leaky Oxide. Until the Drain Voltage sweeps more negative than the applied Negative Gate Voltage, the Gate to Drain Circuit will be a Reverse Biased Junction, with only Reverse Bias Tunneling Current flowing therethrough. When the Drain Voltage sweeps more Negative than the Applied Negative Gate Voltage, the Gate to Drain circuit becomes a Forward Biased Drain Junction with Oxide and P-Type Channel Region Silicon providing a seriesed Resistance. In view of this, it is felt that the reduction in Drain Current flowing at Zero (0) Applied Gate Voltage by the application of Negative Gate Voltage is proof that we do have Leaky Oxide, and said Leaky Oxide fully accounts for the Drain Current flow at Zero (0) Applied Gate Volts.

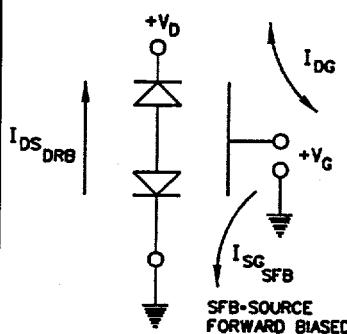

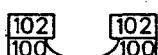

SEE OPERATIONAL

SATURATION

CHARACTERISTIC

DRAIN CURRENT

CURVES

BEFORE CHANNEL INVERSION

$$I_D = I_{DS_{SRB}} + I_{DG_{DFB}}$$

c. Application of Positive (+) Gate Volts provides the Operational Drain Current vs. Drain to Source Voltage Saturation Curves we find empirically. Said Saturation Characteristic Drain Current Curves develop from a Base Current Level corresponding to the Drain Current vs. Drain to Source Voltage Curve achieved at Zero (0) Applied Gate Voltage, and provide increased Drain Current Levels for increased Applied Positive Gate Volts. At low Applied Positive Gate Volts, before Channel Inversion, we see Forward Biased Drain Junction Current Flow through Leaky Oxide. Application of increased Positive Gate Volts, however, causes Inversion of the Channel Region to N-Type Silicon. The Applied Negative Drain Voltage then effects a Reverse Biased Drain Junction and a Forward Biased Source Junction with respect to said Inverted N-Type Channel Region. (Note, As the Polarities of the applied Drain and Gate Voltages are opposite, no "Pinch-Off" effect can develop and Deplete the Channel Region,

AFTER CHANNEL INVERSION

$$I_D = I_{DS} + I_{DC}_{DRB}$$

thereby lowering Channel Region conductivity). Essentially the full Applied Drain to Source Voltage drops across the Reverse Biased Drain Junction through the Forward Biased Source Junction, thereby providing a driving force for the production of a Reverse Bias Tunneling Current through said Reverse Biased Drain Junction. Said Drain Current will flow into said Inverted N-Type Channel Region and through said Forward Biased Source Junction to, in our test situation, ground. (Note the Source Lead could be connected to a Positive Voltage but it was not in our test situation). As the Positive Gate Voltage will see N-Type Silicon in the Channel Region, it sees a Reverse Biased Junction situation with respect to both the Drain Junction and the Source Junction. (Note, Gate Current Flowing has been observed to drop when Channel Inversion occurs). The Drain Junction has a Negative Voltage Applied thereto, and the Source, being at Ground is at a relatively more Positive Voltage. Hence, it is reasonable to assume that the majority of the Drain Current does flow from the Drain through the Inverted N-type Channel and then through the Forward Biased Source Junction. It is noted that the Drain Current Saturation Curves all start essentially at a "Common Point" on the Drain to Source Voltage abscissa, as the Drain Voltage is swept from Positive to negative through Zero (0) Volts. Now, normally we find that the "Common Point" is at Zero (0) Volts Applied to the Drain. However, now and then we find Devices in which the "Common Point" is shifted either Positive, (discussed infra), or Negative along the Drain to Source abscissa. I think this is the result of relatively high Source Contact Resistance, and the effect of forward biased current flowing through the Gate to Source pathway prior to the Inversion of the Channel Region. High Source Contact Resistance shifts the Drain Current Curves to the negative, (by dropping voltage), and Gate leakage Current flow to the positive, (by imposing a positive voltage in the Noninverted Channel, atop a then Forward Biased Source), prior to application of a Drain Current flow forcing Drain to Source Voltage.

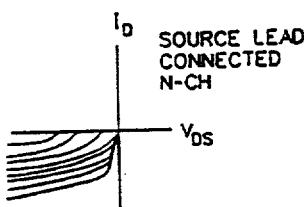

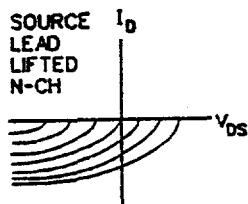

It is also of interest to describe the sort of Curves which appear if we apply Positive Gate Voltages, and sweep the Drain to Source Voltage from Positive to Negative with the Source lead lifted from the Schottky barrier MOSFET Device Source Contact. In this case

the Drain Junction can become Forward Biased, with respect to the Gate, through leaky Oxide. That is the Drain and Gate Voltage Sources will be in a series circuit with the Drain Junction through leaky Oxide. What we see develop are a series of Curves, each similar to those which appear when Voltage is applied across a seriesed Diode and Resistor, (eg. the Leaky Oxide). Curves, one for each applied Gate Voltage, should start at locations along the Drain to Source abscissa, where a swept Drain Voltage just decreases below the then applied Gate Voltage, effecting a Forward Bias on the Drain Junction. If the difference between applied Drain and Gate Voltages becomes large enough, however, Silicon Inversion can occur and the Drain Current Curves become Reverse Bias Tunneling in nature with Current flow through the Oxide.

It is again note that a similar analysis to that presented infra for the N-Channel Schottky barrier MOSFET Devices can be performed for the P-Channel Schottky barrier MOSFET Devices by simply reversing the recited Polarities of applied Gate and Drain Voltages.

Also, in the above analysis Bulk Effects were assumed negligible, which seems to be justified.

Generally, I feel that we must make but a few assumptions, in view of the above, to explain the results we have achieved. First, the Devices do operate in an Inverted Channel MOSFET Mode, but that Drain Current is the result of Tunneling Current through a Reverse Baised Schottky barrier Junction into the Inverted Channel. Second, we have a Leaky Oxide problem which causes Drain Current to flow when Drain Voltage is applied but no Gate Voltage is applied, and which causes Drain current to flow when Gate Voltage is applied and no Drain Voltage is applied. Third, in some devices we have seen evidence of relatively high Contact Resistance and Oxide Breakdown, in that the "Common Point" from which Saturation Drain Current Curves begin, shifts along the Drain to Source abscissa. Forth, the Devices only provide MOSFET Saturation Curves when an Inverted Type Channel Region is effected, and then only when the Drain Junction is Reverse Biased. This is felt to be because Metalurgical Junctions have different characteristics than do Field Induced Junctions, (with the later known to often demonstrate lower Reverse Breakdown Voltages and larger Tunneling Current flows at certain Voltages as compared to Metalurgically effected junctions). Fifth, we must assume that "Pinch-Off" Regions prevent Tunneling current driving force from dropping across a Reverse Biased Source Junction in an Inverted Channel Region Scenario, but have no effect on Voltage Dropped across a Reverse Biased Drain Junction to which the Drain Voltage is Applied directly, rather than through a length of "Pinched-Off" Channel Region.

## ATTEMPT TO EXPLAIN DEVICE OPERATION AS A BIPOLAR TRANSISTOR

As we have seen, the present devices operate with the Drain Junction Reverse Biased and with the Source Junction Forward Biased. With that in mind, one can not help but think of Bipolar Transistors which operate with a Reverse Biased Collector and a Forward Biased Emitter Junction in analogically similar circuit positions to the present Device's Drain and Source. It must, however, be appreciated that the Bias arrangement alluded to is as seen from the Drain or, analogically, the Collector of respective MOSFET or Bipolar devices respectively, with respect to the Source, or analogically the Emitter of the respective devices. When one views from the Gate, or analogically the Base of the respective devices, with respect to the Source, or analogically the Emitter, the analogy to Bipolar devices breaks down. The present Schottky barrier MOSFET devices provide Saturation Drain Current vs. Drain Voltage Curves with the Applied Gate Voltage effecting a Reverse Bias with respect to both Drain and Source Junctions (assuming an Inverted Channel Region is present). If we do not assume an Inverted Channel Region is present the Gate Applied Voltage would effect a Forward Bias with respect to both the Drain and Source Junctions. This is because the Applied Gate Voltage, in the operational region of the present Schottky barrier MOSFET Devices, is of the opposite polarity to that applied to the Drain. (Note that in our test

system the Source is held a ground, hence an applied Positive Gate Voltage is more positive with respect thereto, just as it is more positive with respect to an Applied Negative Drain Voltage. A Bipolar Transistor requires that the Voltage applied to the base be of the same polarity as that applied to the Collector, only of a lesser magnitude with respect to the Emitter thereof, emphasis added. As a result, I conclude that the Operation of the present Devices can not be explained by Bipolar Transistor Theory in view of the Test Set arrangement in which we obtained empirical results, (eg. the presence of a well defined Common Source, (Emitter), Terminal with respect to which the applied Gate and Drain Voltages were applied).

BOTH COLLECTOR AND

BASE SAME POLARITY WHEN

HAVE SATURATION CURVES

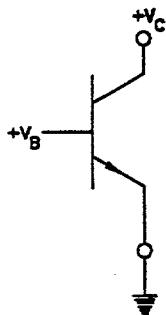

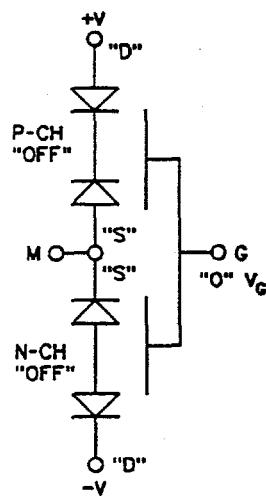

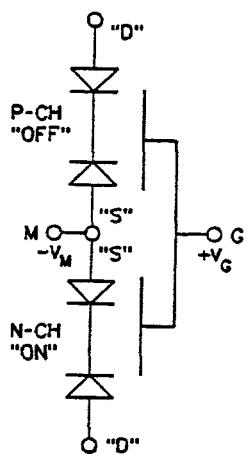

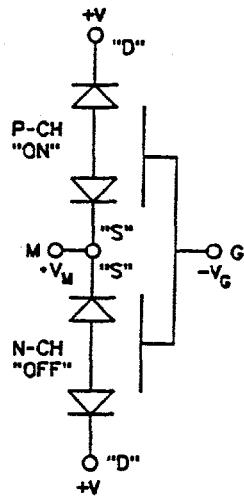

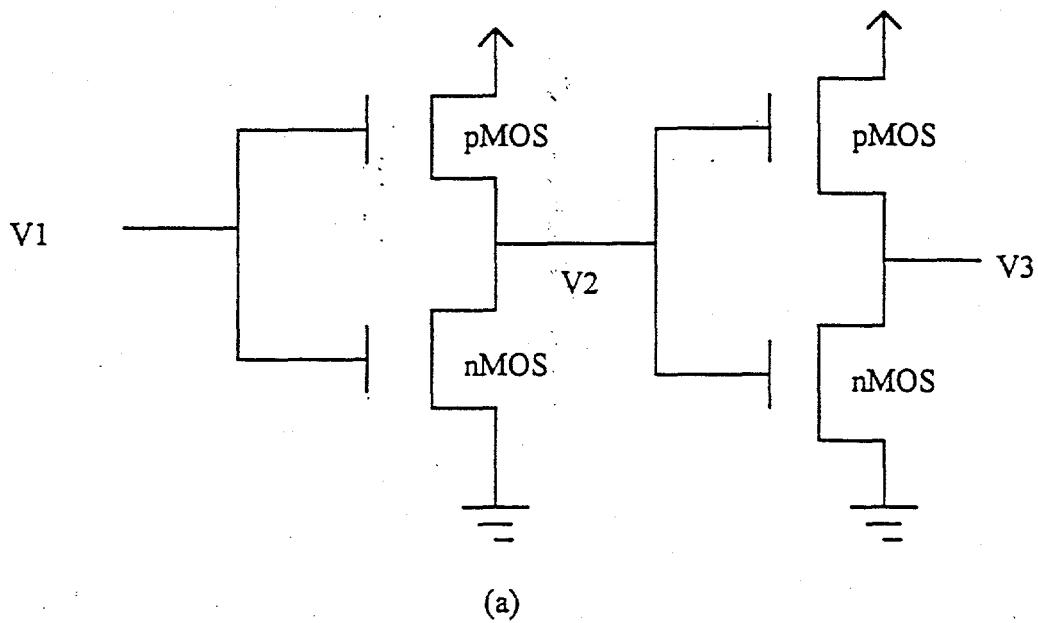

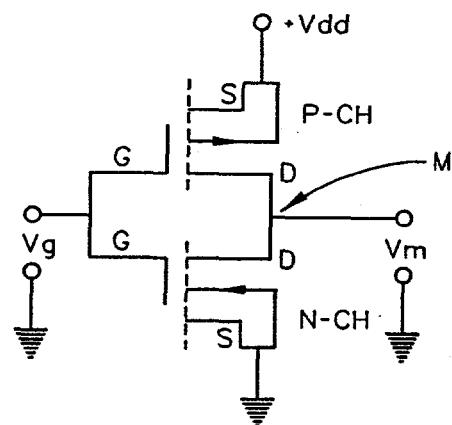

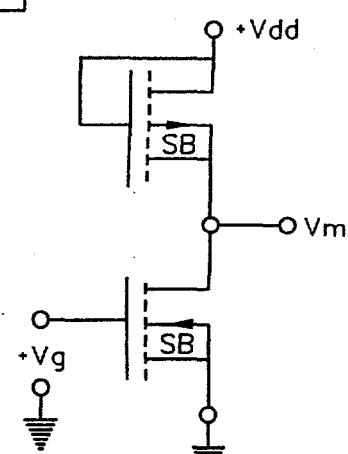

## APPLICATION OF PRESENT DEVICES TO CMOS SYSTEMS

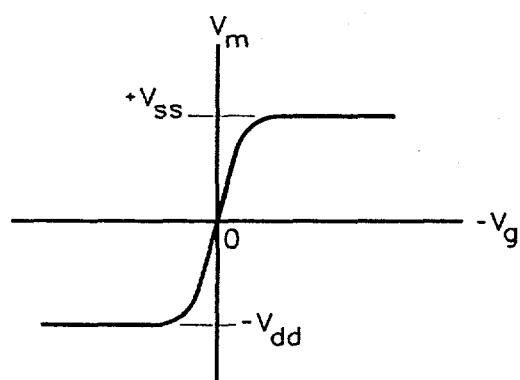

The reader might by now have noted that the present Schottky barrier MOSFETS operate with Drain Current flowing in a direction opposite to that which one finds in Diffused Junction MOSFETS. This is indeed the case. That is, in Conventional Diffused Junction MOSFES the Gate and Drain both have the same Polarity Voltage applied thereto and provide Saturation Drain Current vs. swept Drain to Source Voltage Curves via an Inverted Channel

"Pinch-Off" mechanism, whereas the present Schottky Barrier MOSFETS require Opposite Polaritiy Voltages be applied to the Gate and Drain to effect Saturation MOSFET Drain Current vs. swept Drain to Source Voltage Curves and effect said Curves via the limit of Reverse Bias Leakage Current which can flow through a Reverse Biased Drain Junction as a function of Field Induced Inverted Channel Doping Level. (It will be recalled that the Channel Region constitutes the Semiconductor component of a Schottky Barrier Junction, and that it is well known that a higher Doping Level of the Semiconductor component of a Schottky Barrier Junction is associated with a higher Reverse Bias Tunneling Currents at certian Applied Reverse Bias Voltages thereacross). In view of the above, it becomes a bit difficult to understand how Complimentary Metal Oxide Semiconductor (CMOS) Device Systems can be configured from the present Devices.

First, a conventional Diffused Junction MOSFET comprises Source and Drain Regions of one type of Semiconductor, (ie. N or P-Type), separated by a Channel Region of an opposite Type of Semiconductor. The Channel Regions have associated therewith a Gate, application of a Voltage of a proper polarity to which, can serve to Invert the Type of Semiconductor in the Channel Region, thereby providing an ohmic path between the Drain and Source. That is, no rectifying junction remains between the Drain and Source Contacts.

CONVENTIONAL DIFFUSED JUNCTION CIRCUIT

Conventional Diffused Junction CMOS systems comprise a seriesed combination of P and N-Channel Devices, in which the Drains of the respective devices are interconnected to form a Common Midpoint. If a Voltage is applied between the remaining noninterconnected Sources, and a voltage is applied to interconnected Gates of the P and N-Channel Devices with respect to one of said Sources, the end result is that one device is "On", (eg. conducting), when the other is "Off", (eg. nonconducting), and vice versa. The voltage at the interconnected Drains Midpoint will be an inverted version of the applied Gate voltage. For instance, assume the Source of a P-Channel Diffused Junction MOSFET is provided a Positive Polarity Voltage with

respect to the Source of an N-Channel Diffused Junction MOSFET, which P and N-Channel Diffused Junction MOSFETS are configured in a CMOS configuration by interconnection of the Drains thereof, and by interconnection of the Gates thereof. If a Positive

Voltage, again with respect to the Source, of the N-Channel Diffused Junction MOSFET is applied to the interconnected Gates, the N-Channel Device will form an Inverted conducting Channel Region and be "On". the voltage at the Midpoint interconnection of the Drains will then be at Zero (0) volts. If the Gates are provided a Negative Voltage the P-Channel Device will form an Inverted conducting Channel and will be "On". The voltage at the Midpoint interconnection of the Drains will be at that applied to the Source of the P-Channel Device. In each case, the device not "on" will be "off" as there will not be an Inverted Channel region to ohmically connect the Drain and Source therein. These Inverter Circuit Systems are very energy efficient in use as the only time current flows is at the exact switch point. However, High and Low Voltages can be effected at the interconnected Drains, and remain until applied Gate voltage change effects the switch.

As one might expect the present N and P-Channel Schottky barrier MOSFETS can not simply be substituted for Conventional Diffused Junction N and P-Channel Devices in a CMOS system and the operation thereof in a CMOS configuration thereby understood. This is because the Applied Gate and Drain Voltages are of necessarily of opposite Polarity, as described infra. Also, a true Ohmic connection is not effected between a Drain and Source in the present Devices when they are "On". There are still Rectifying Junctions present with respect to the Channel Region, one of which is Reverse Biased. However, looking into the Drain of a present Device, one will see an effective lower resistance when it is "On" than when it is "Off". This seen to be the case as more current flows through an Applied Gate Voltage effected "On" device than through an "Off" Device at the same Drain to Source Voltage, (ie. Applied Drain Voltage divided by Current Flowing in said Drain provides an effective resistance between Drain and Source Contacts). Now, the Effective Resistance of the Reverse Biased Junction is a function of the Effective Doping of the Semiconductor component of the Schottky barrier Junction, not the amount of Current being force through it by Applied Voltage thereacross.

To understand how the present Schottky barrier MOSFETS can operate in a CMOS configuration it is necessary to understand that physically, the present Devices are symmetrical. That is, the Rectifying Junctions which constitute the Drain and the Source thereof are identical. It is location in a circuit that defines them as Drain or Source, by the function performed thereby. One of the Junctions will be found to be a "Common" terminal to which Applied Drain and the Gate Voltages will refer. It will also be recalled that the present N-Channel Device, (which is fabricated in P-Type Semiconductor) operates, (ie. provides conduction as evidenced by Saturation Characteristic Drain Current vs. Drain to Source Voltage Curves), when the Drain

has a Negative Voltage applied thereto and the Gate has Positive Voltage applied thereto, again, both with respect to the Source thereof. A P-Channel, (which is formed in N-Type Semiconductor), operates (ie. provides conduction as evidenced by Saturation Characteristic Drain Current vs. Drain to Source Voltage Curves), when the Drain has a Positive Voltage applied thereto and the Gate has Negative Voltage applied thereto, both with respect to the Source thereof. In a circuit one must look for Voltage Polarities to define a Drain or Source.

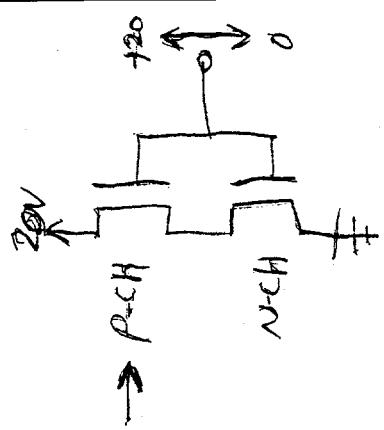

Now, if we configure a present Schottky barrier P-Channel MOSFET and a present Schottky barrier N-Channel MOSFET so that one non-Gate terminal of each are interconnected, and such that the noninterconnected non-Gate Terminal of the P-Channel Device has a Positive Polarity Voltage Applied thereto, and such that the noninterconnected non-Gate Terminal of the N-Channel Device has a Negative Voltage applied thereto, and we interconnect the Gate Terminals, then we have an operable CMOS System wherein the Inverting Midpoint Voltage appears at the interconnected Terminals of the two Devices during use. To understand the operation, assume a Positive Voltage is Applied to the interconnected Gates, (eg. that Positive Voltage applied to the noninterconnected non-Gate Terminal of the P-Channel device). Also understand that the interconnected non-Gate Terminals Midpoint Voltage will be established between the Voltages Applied to the noninterconnected non-Gate Terminals by simple voltage division. Now a Positive Applied Gate Voltage, with respect to a "Source" Terminal is associated with turning "On" an N-Channel Device, the Drain of which is at a Negative Voltage with respect to a "Source" Terminal. If we think of the interconnected non-Gate Midpoint Terminals of the P and N-Channel Devices as the effective "Sources" of the Devices in the present CMOS System, then we see that the N-Channel device will have a Positive Gate Voltage with respect thereto, (eg. this is the result of a voltage drop across the effectively high Reverse Biased Schottky barrier Junction Resistance of the "Off" P-Channel Device), while the Effective "Drain", (ie. the noninterconnected non-Gate Terminal), of the N-Channel Device has a Negative Voltage Applied thereto, again with

respect to the Effective "Source" thereof. In this circuit, the Effective "Sources" must be considered to be at the Midpoint interconnected non-Gate Terminals of the N and P-Channel Devices to understand how the required Voltage Polarities are present to make the circuit work. It will be recalled that when an N-Channel Drain has a Negative Voltage applied thereto, and a Positive Gate Voltage applied thereto, Saturation Drain Current vs. Drain to Source Voltage Curves appear. The appearance of such Curves is associated with an effectively lower Drain to Source Resistance therein. Now, again, it is to be understood that the P-Channel and N-Channel Devices form, in effect, a Voltage Divider Circuit. The Resistance of the P-Channel Device will remain relatively high when the Gate Voltage applied thereto is Positive with respect to the Effective Source thereof. Hence we expect to see a Low Midpoint interconnected non-Gate Terminal voltage. Now the lower the effective Resistance of the N-Channel Device becomes, the lower will be the Midpoint interconnected non-Gate Terminal Voltage by the voltage divider mechanism, hence the more Inverted the N-Channel Channel Region will become if the Gate Voltage is held constant, (which it typical is at that applied to the Effective "Drain" of the P-Channel Device), and the more Inverted the N-Channel Region, the lower will its Resistance become. A regenerative effect occur which serves to progressively turn the N-Channel Device more and more "On"! However, there will come a point where the Tunneling Current Flow Driving Voltage Dropped across the Reverse Biased Effective "Drain" in the N-Channel Device will not be sufficient to sustain Current Flow thereacross, even though the Reverse Biased Junction Resistance thereof will be low. At that point, both the N and P-Channel Devices will serve to limit Current Flow through the Series Chain in the Schottky barrier CMOS System described. As mentioned infra, however, the fact that little current is flowing through the Reverse Biased Effective "Drain" Junction in said N-Channel Schottky barrier MOSFET does not determine the Effective Resistance thereof, and the effect thereof in a Voltage Divider Circuit with the P-Channel Schottky barrier MOSFET Device.

That is, it is the effective Doping of the Inverted Channel Region Semiconductor component of the Schottky barrier Junction which determines the Effective Resistance thereof, and not the current forced therethrough at any point, as is the case with any resistor. (Also note that a "Pinch-Off" Region will add to the "Off" device resistance, thereby enhancing the effect).

A similar analysis applies to the case wherein a Negative Voltage is applied to the Gates of the present Schottky barrier MOSFET System, but the Midpoint Voltage, of course, will be "High" when said Negative Gate Voltage is Applied.

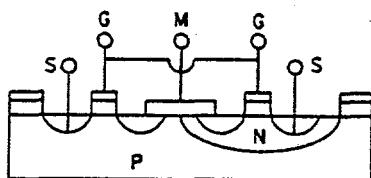

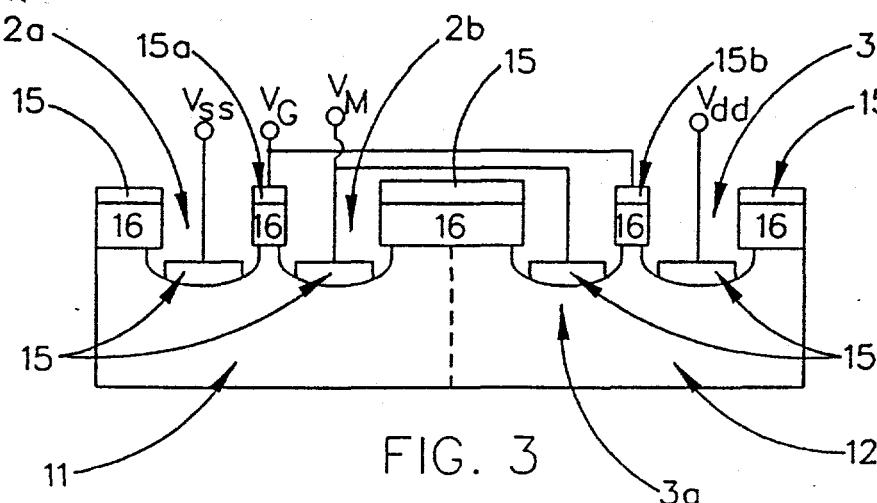

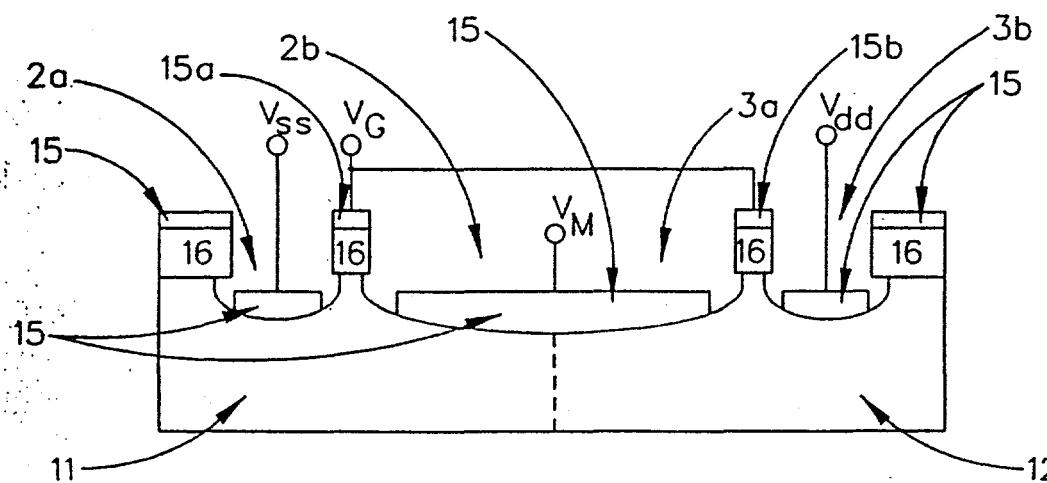

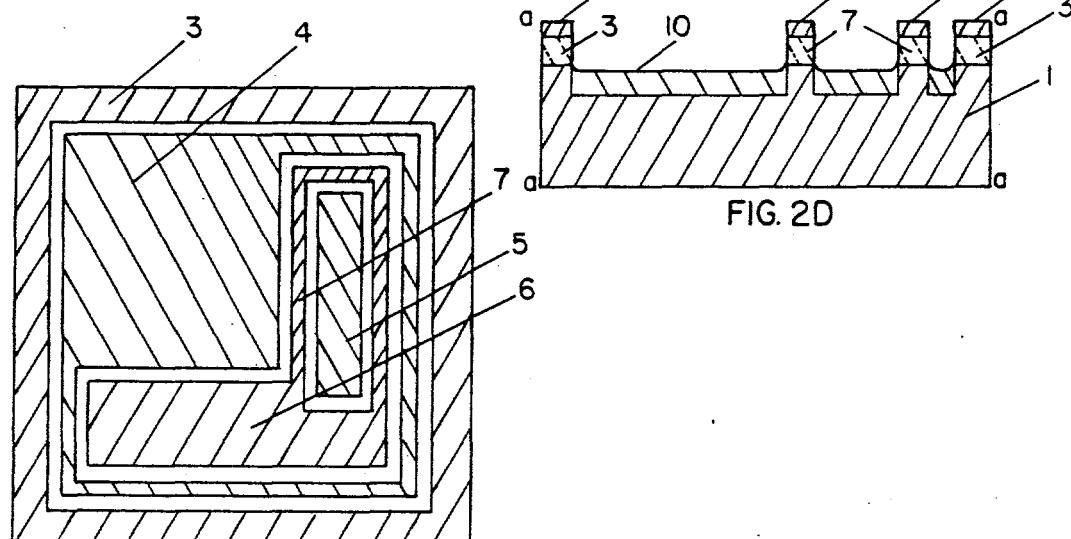

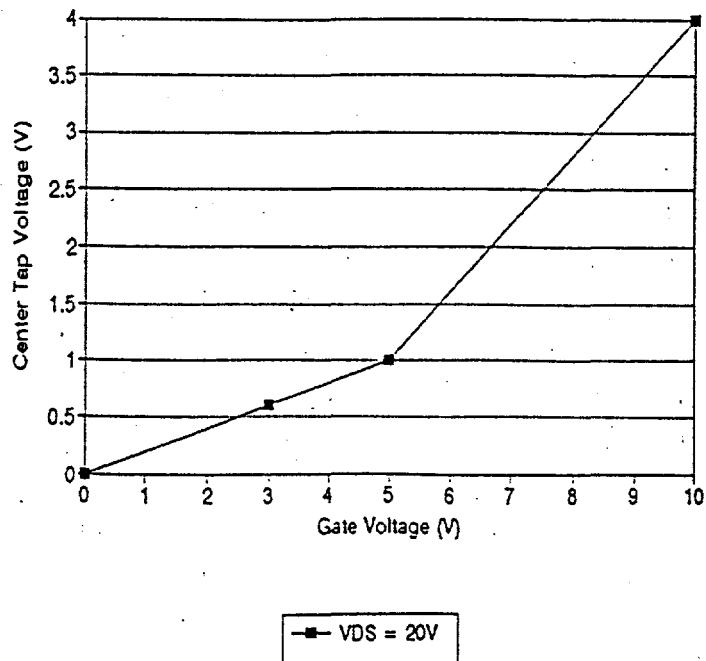

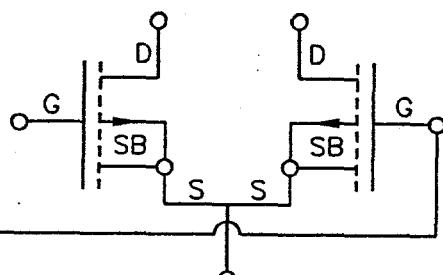

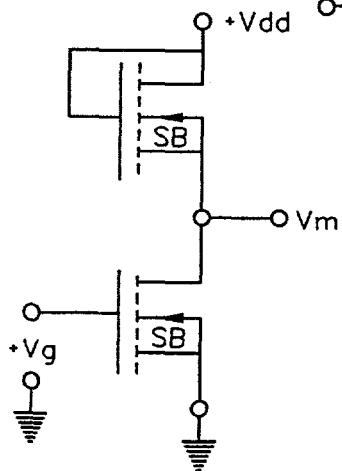

#### SINGLE DEVICE INVERTING AND NONINVERTING EQUIVALENTS TO CMOS

The work under the present support was expanded beyond that originally proposed to show feasibility of producing Schottky barrier Junction based Single Devices which provide Operating Characteristics similar to CMOS Systems, which as demonstrated above, comprise two devices. If successfully developed, such Single Device CMOS Equivalents will allow greatly increased Device Substrate Packing Density, (eg. more devices per area of Semiconductor).

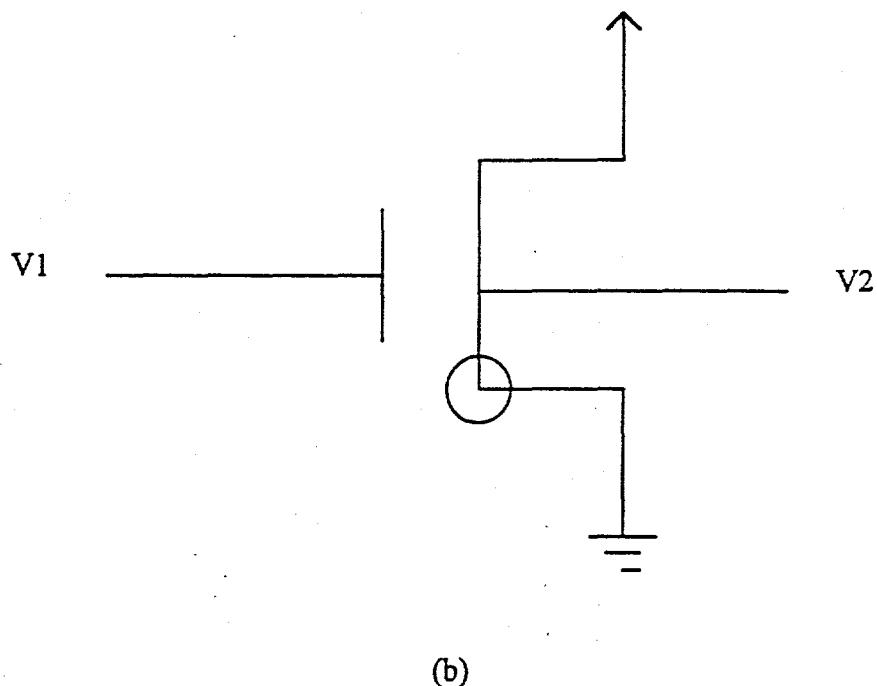

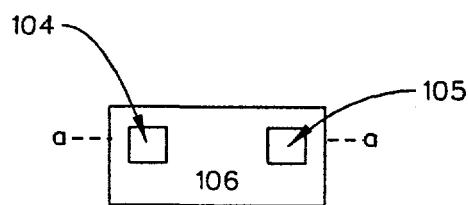

The basic theory behind these Devices is relatively easily grasped. In the case of the Noninverting Single Device CMOS Equivalent, the physical structure is that of a Schottky barrier MOSFET with a Drain and Source separated by a Channel Region. Also present, however, is a Channel Region Contact which can sense Voltage present in the Channel Region under the Gate. Now, if a Voltage is applied across the Drain to Source, then one of the Schottky barrier Junctions, (ie. Drain or Source) is Forward Biased, and the other is Reverse Biased. The Voltage monitored by the Channel Region Contact should be essentially that applied to the Forward Biased Junction, and supported by the Reverse Biased Junction. Application of a Gate Voltage of a proper polarity will Invert the Semiconductor, and that will cause the location of the Forward and Reverse Biased Junctions to reverse. This will cause the Channel Region Contact Voltage to change to that applied to the then Forward Biased Junction. In this Device the direction of change of the Applied Gate Voltage and the direction of change of the Channel Region

Contact Voltage are of the same, thus the Device is "Noninverting". (Note Conventional Diffused Junction CMOS requires four devices to fashion a Noninverting configuration.

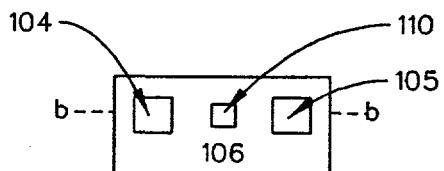

INVERTING

SINGLE DEVICE CMOS

Now, if the geometry of the Device is such that the Schottky barrier Junctions are Centrally located, with Semiconductor leading to an ohmic Source on one side thereof and Semiconductor leading to an ohmic Drain on the other side thereof, then we can achieve an Inverting Single Device Equivalent to CMOS. That is if a Voltage is applied across the Drain to Source, a Midpoint voltage will appear at the Schottky barriers. Now if interconnected Gates are associated with each length of Semiconductor, and a Gate Voltage of a Polarity proper to Invert said lengths of Semiconductor is applied, then we will see the Voltage at the Midpoint Schottky barriers change in a direction opposite to the direction of change of the Applied Gate Voltage.

(Note, these Single Device CMOS Equivalent Devices will probably have to be low Applied Gate Voltage Devices to prevent significant MOSFET Drain Current Flow, where an Inverted Channel Region is formed in use. We will want to achieve just sufficient Channel Region Inversion to shift the location of the Forward and Reverse Biased Junctions, but no more.)

The copy of the Pending Grant Application submitted to the Air Force included herewith, in Attachment "B", and the Patent Application in Attachment "C", better describes the geometry of these devices.

#### CONTINUED WORK

Continued Research is needed to provide better quality Schottky barrier Junction formation, (sputter clean silicon prior to depositing and annealing chromium), and upon obtaining better quality Oxide through which current can not flow. As well, Aluminum pads for mediate contact between Source and Drain Junctions and external testing equipment should be effected. This requires new photolithographic mask sets. Additional work should also investigate the use of other Schottky barrier forming metals, such as Molybdenum and Platinum.

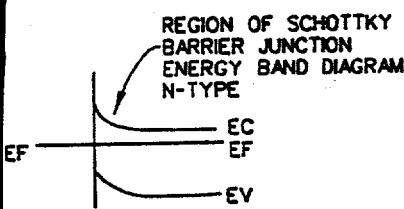

There remains to be developed a Mathematical Model for the present Schottky barrier MOSFET Devices. However it is known that said Model will rely on the use of Reverse Bias Schottky barrier Junction Tunneling Current Equations, the Calculation of

Channel conductivity in both Non-Inverted and Inverted Modes and the effect that Applied Gate Voltage has thereon, as well as the effect that Effective Channel Region Doping Level has on Drain Current Flow via change in the Semiconductor Component of said Schottky barrier Junctions, and how such relates to Conduction, Valence and Fermi Levels in Energy Band Diagrams. Integration of the MOSFET Channel "Pinchoff" effect will be a necessary part of model, and Channel Region Geometry at the lateral edges of the Source and Drain Junctions, and how it affects current flow into and through the Channel should also be investigated.

#### ACTUAL EMPIRICALLY OBTAINED RESULTS

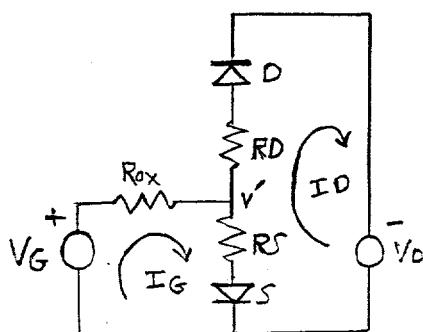

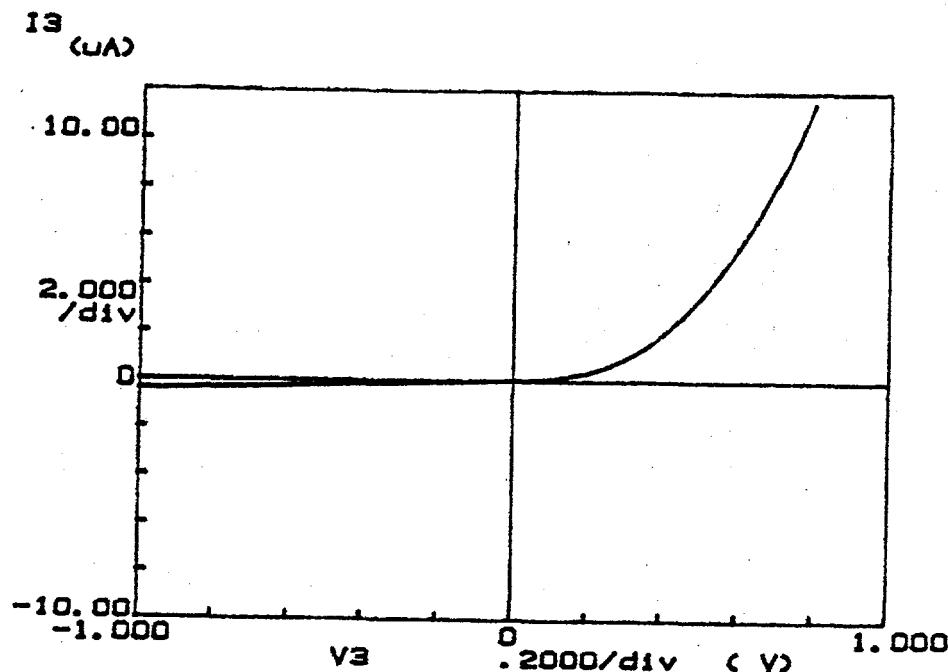

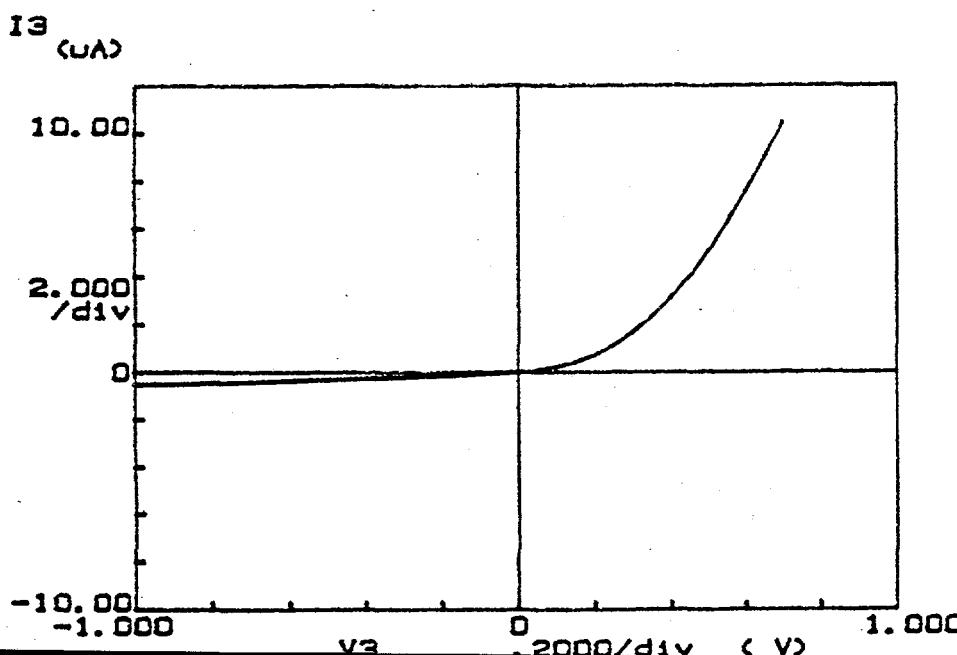

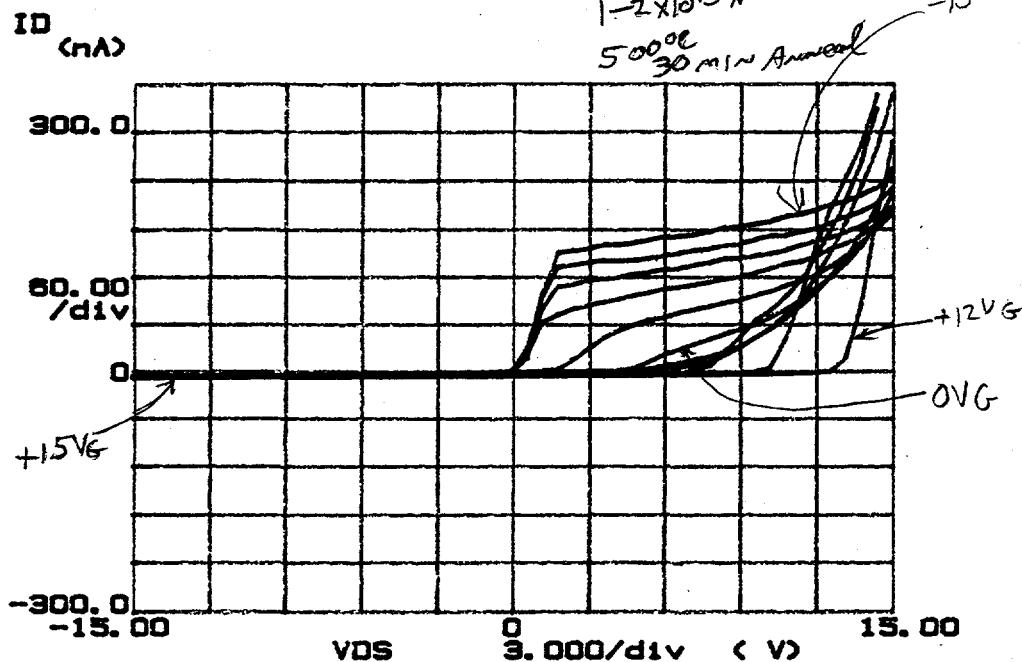

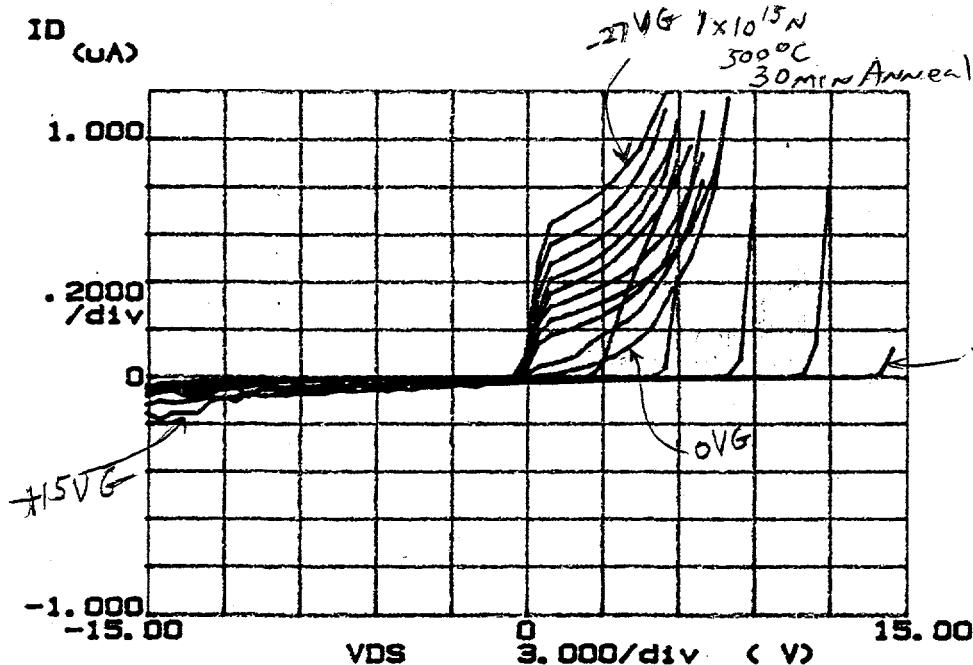

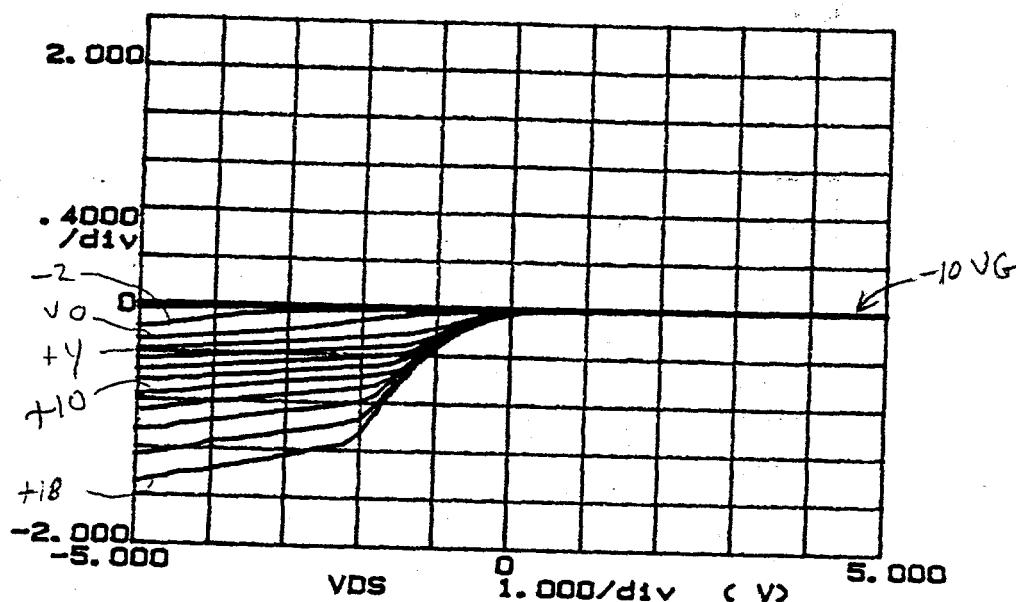

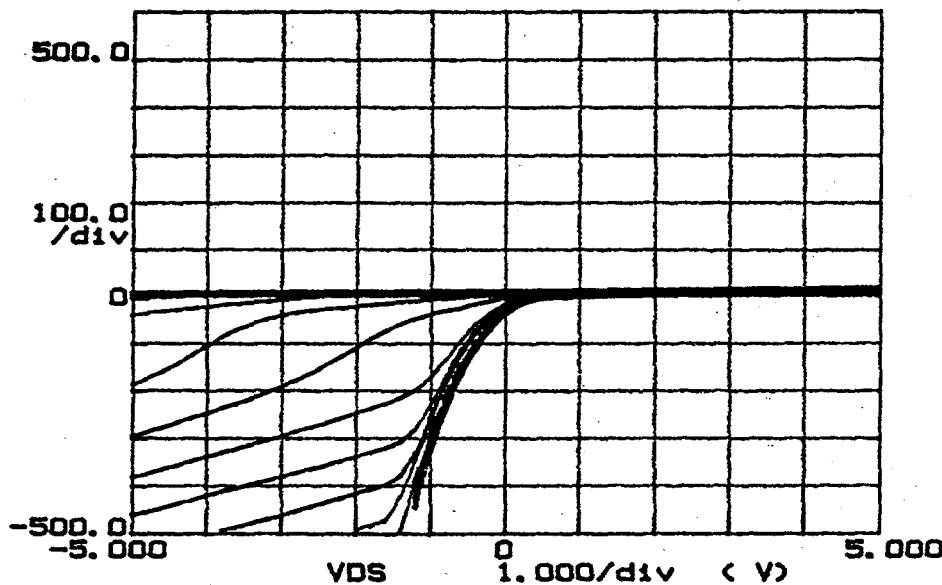

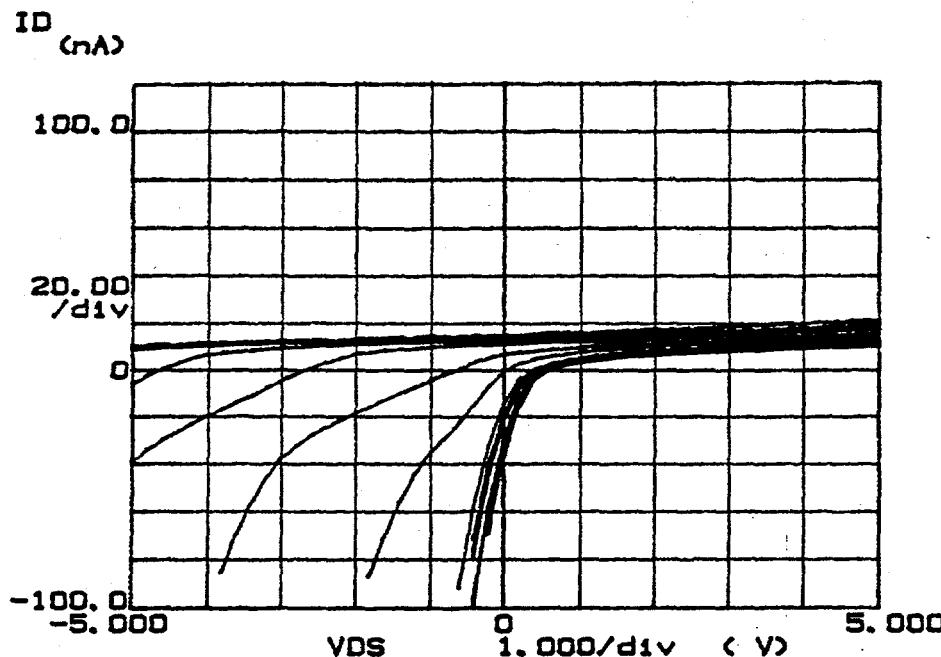

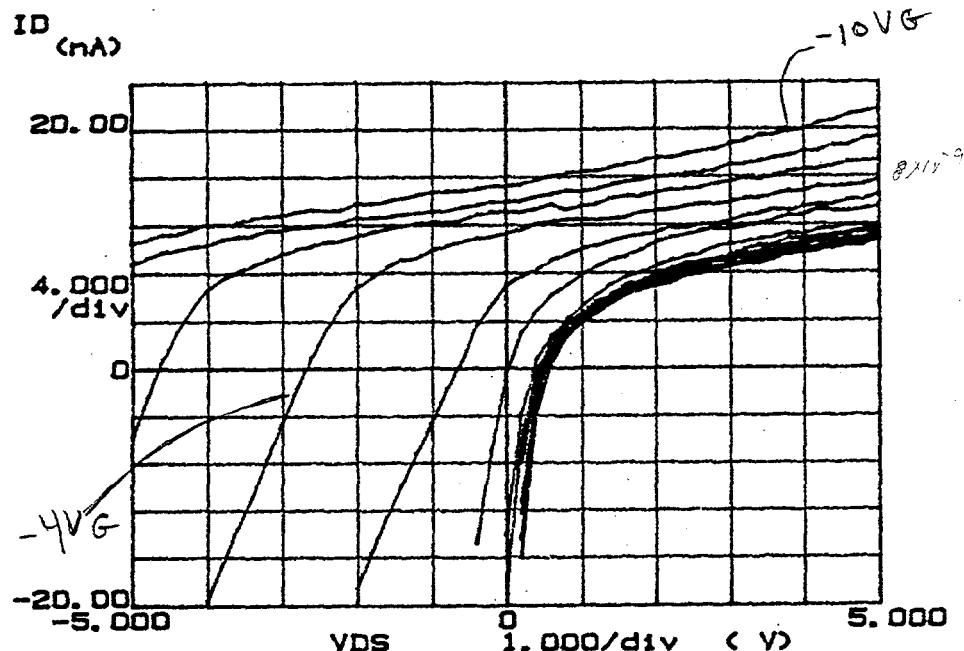

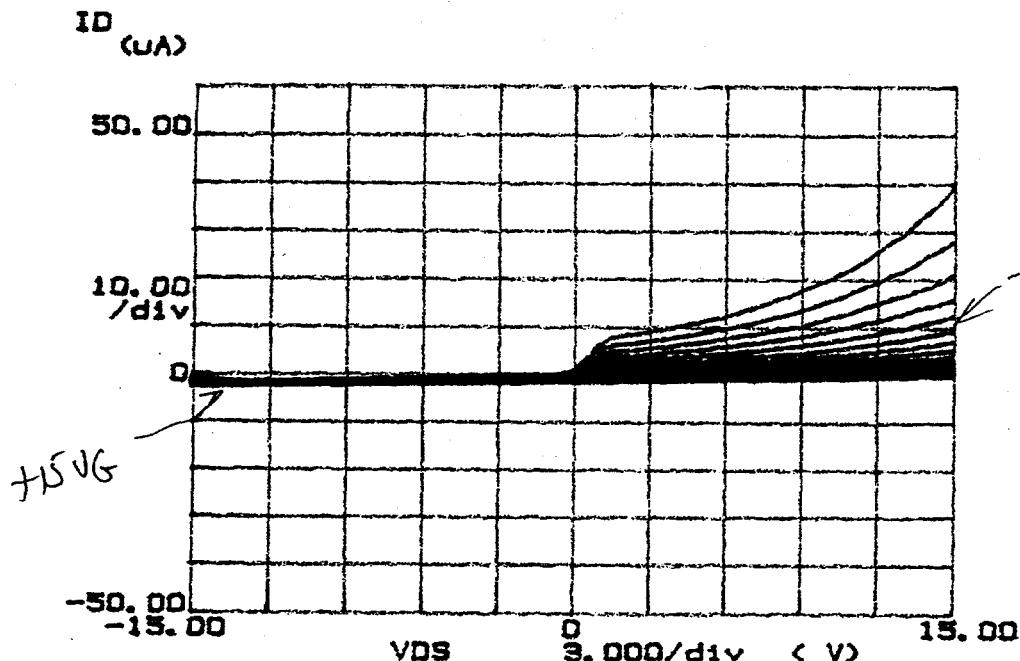

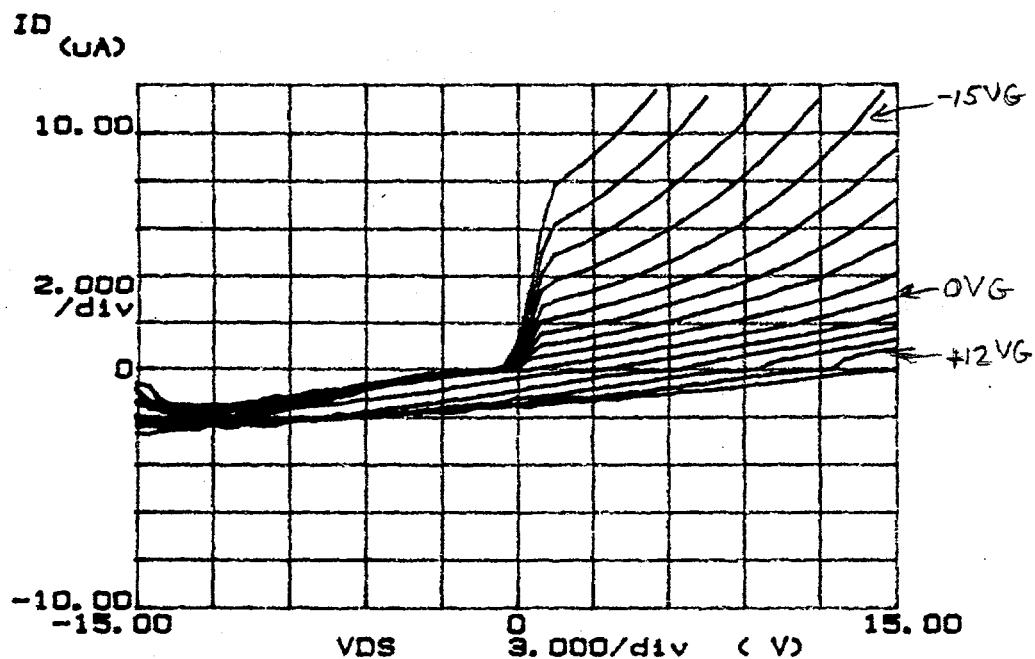

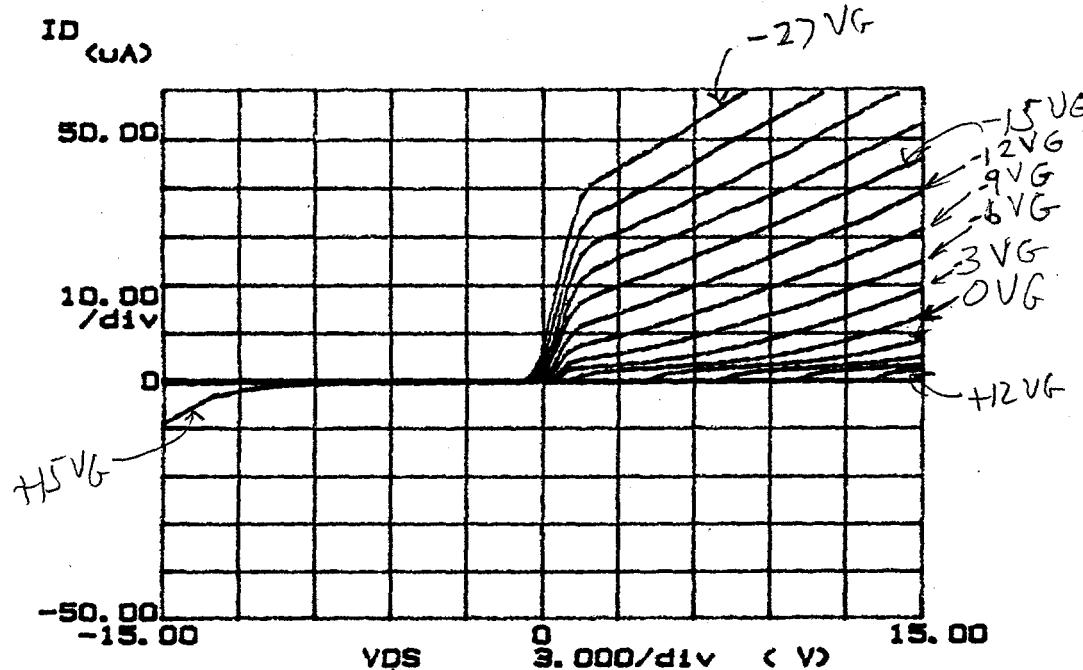

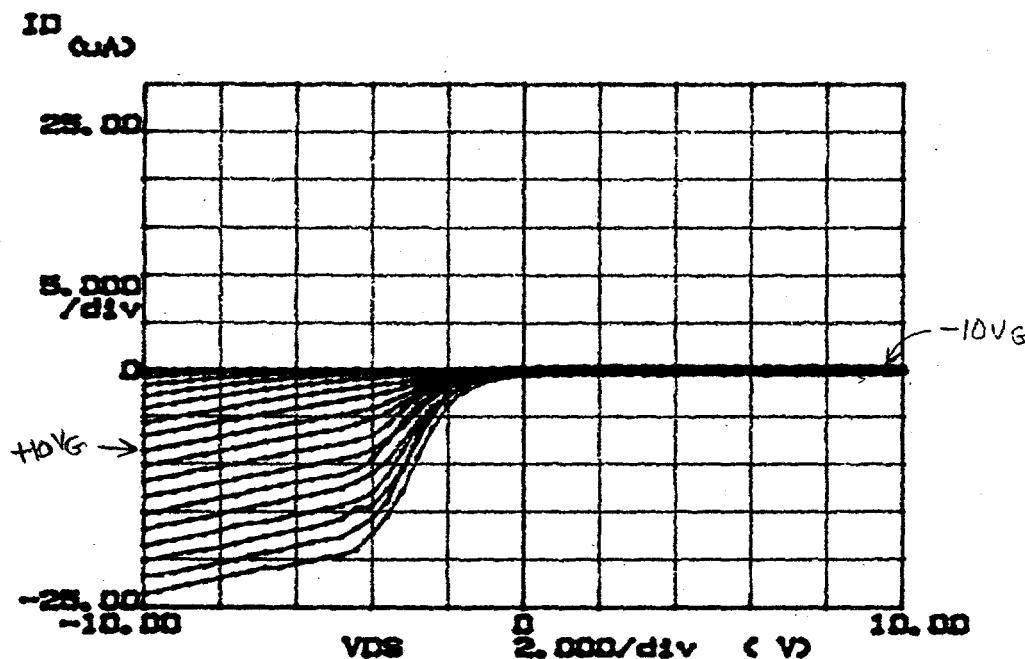

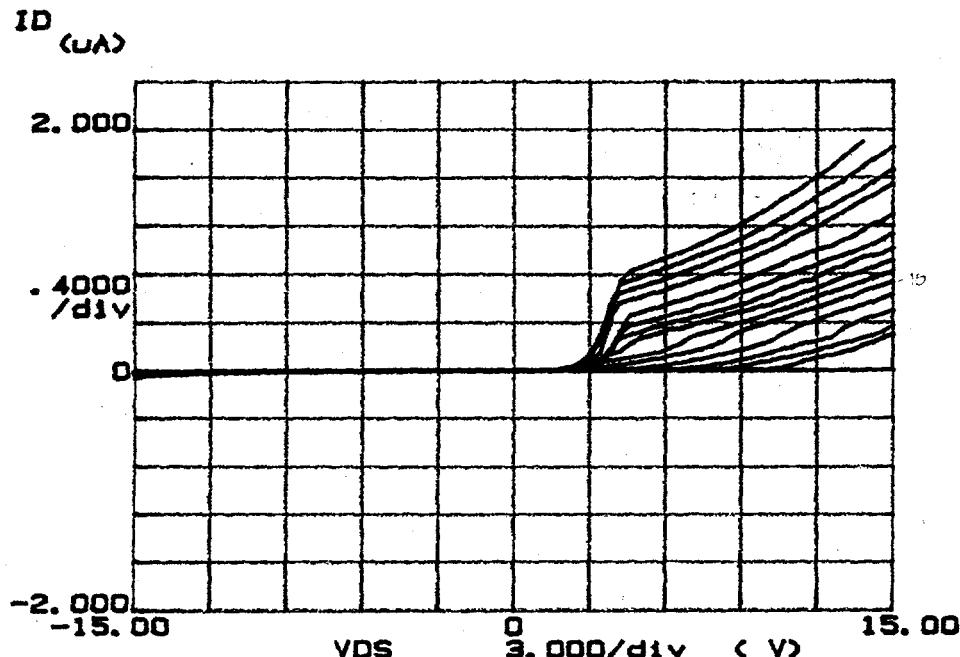

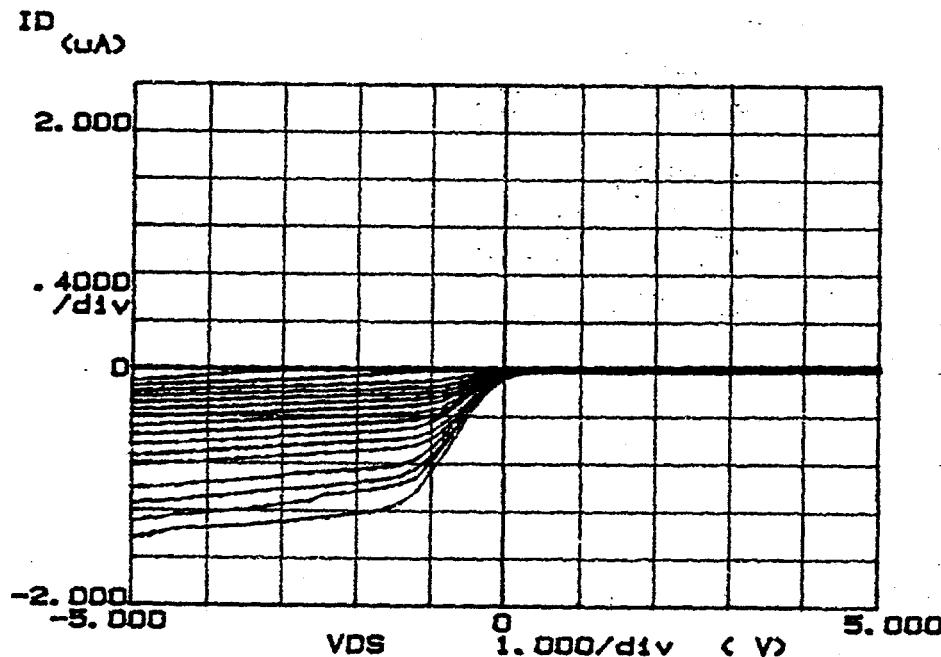

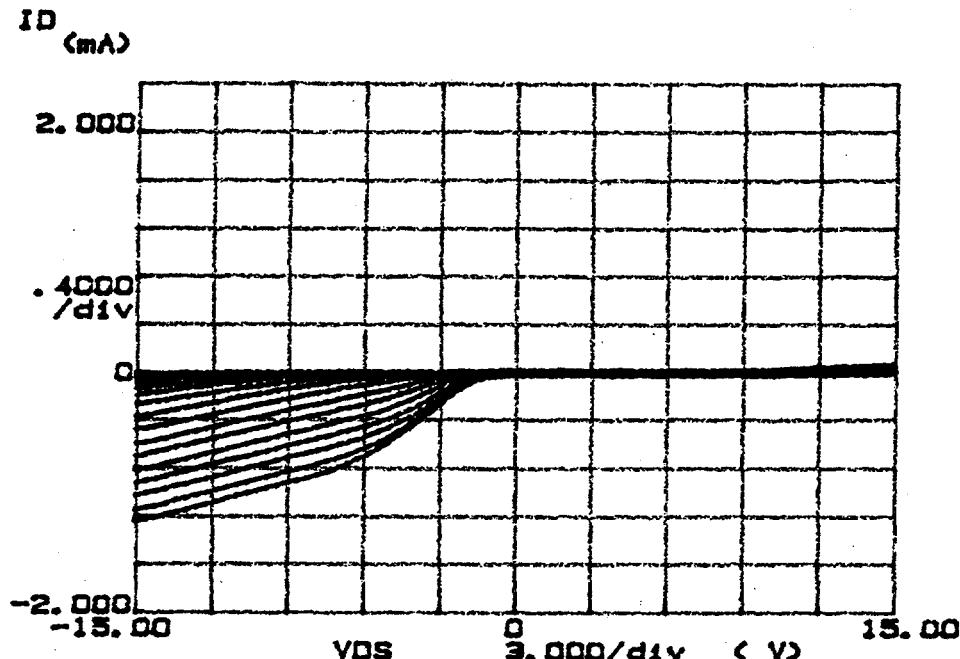

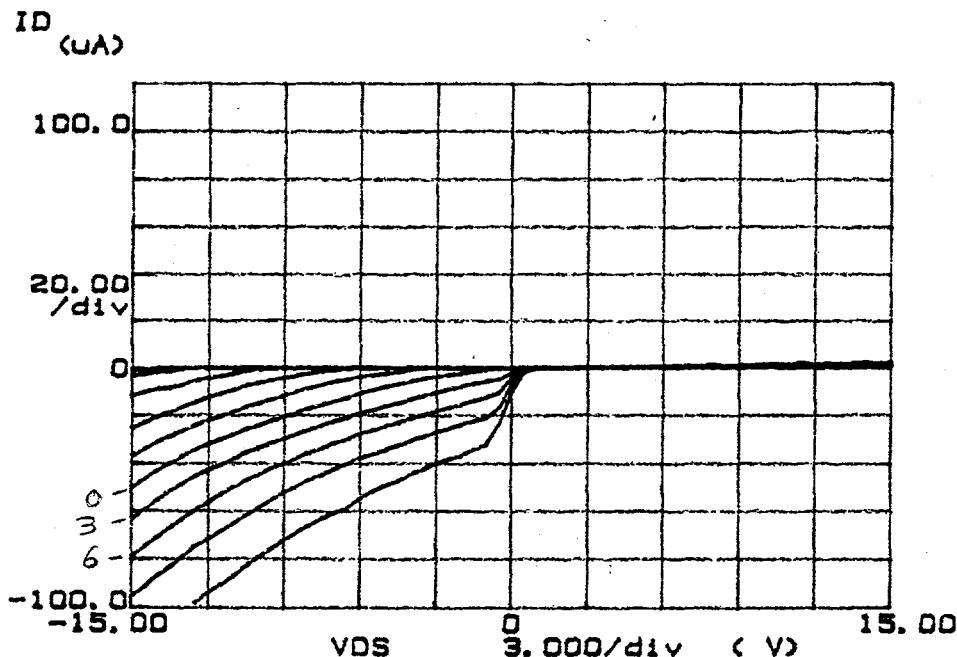

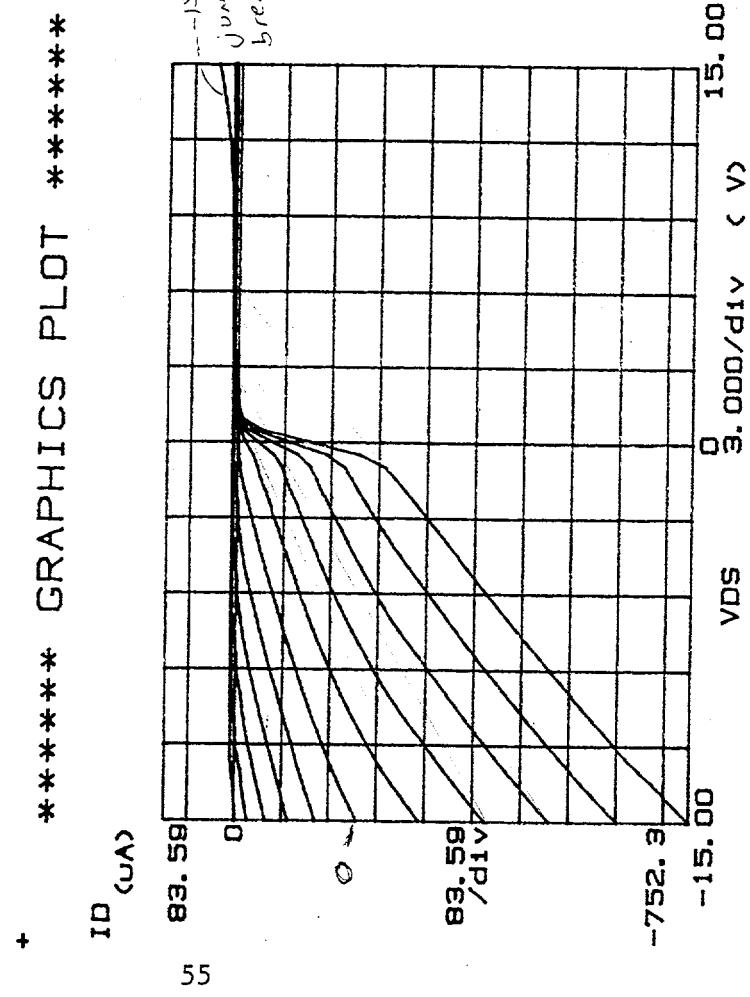

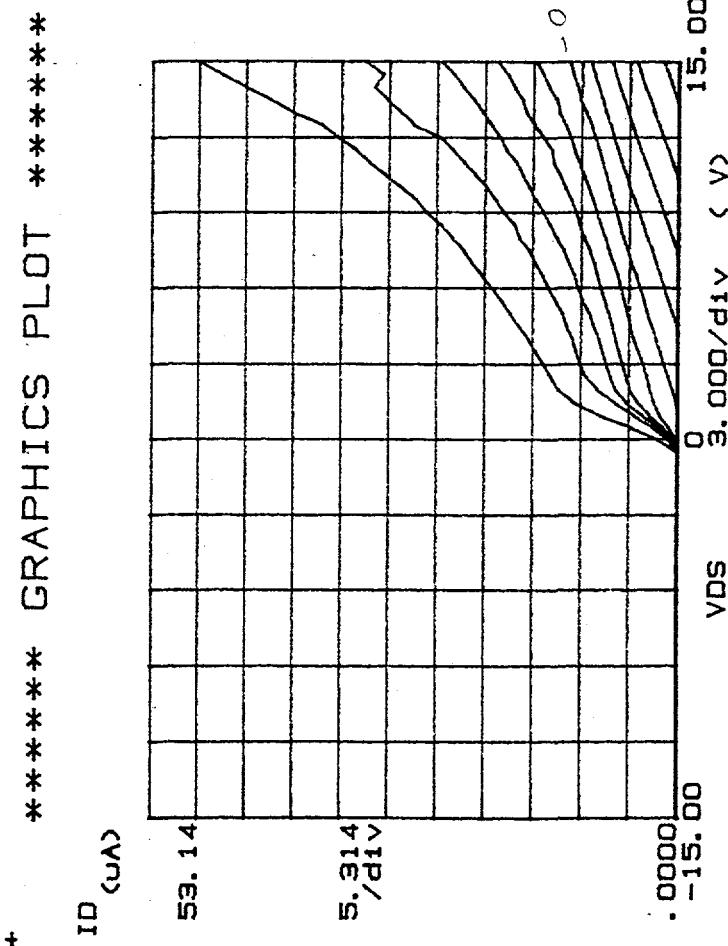

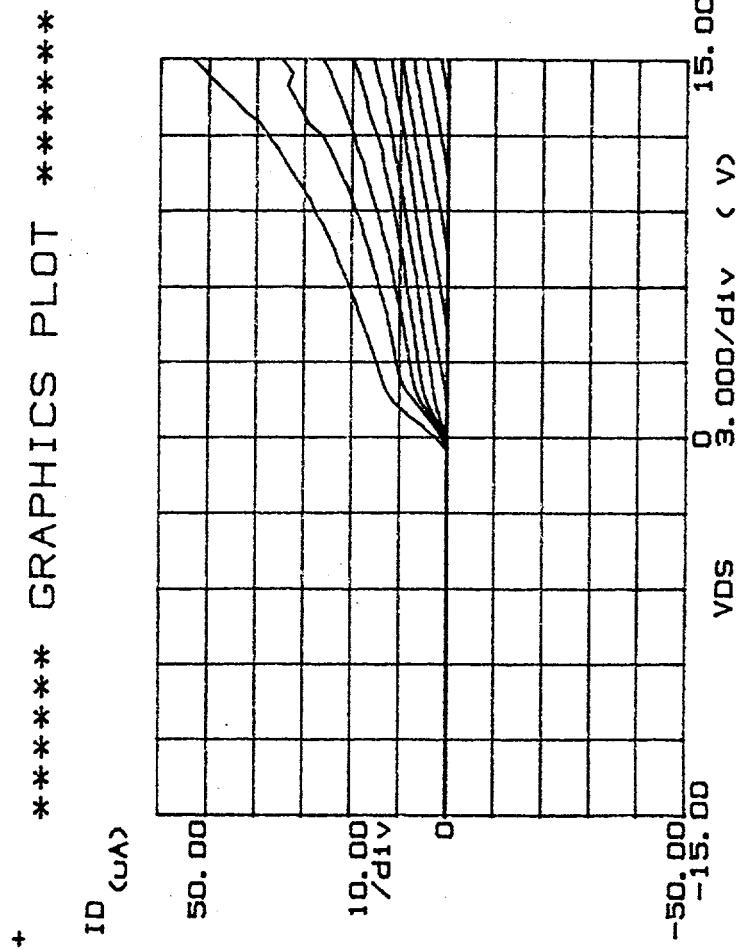

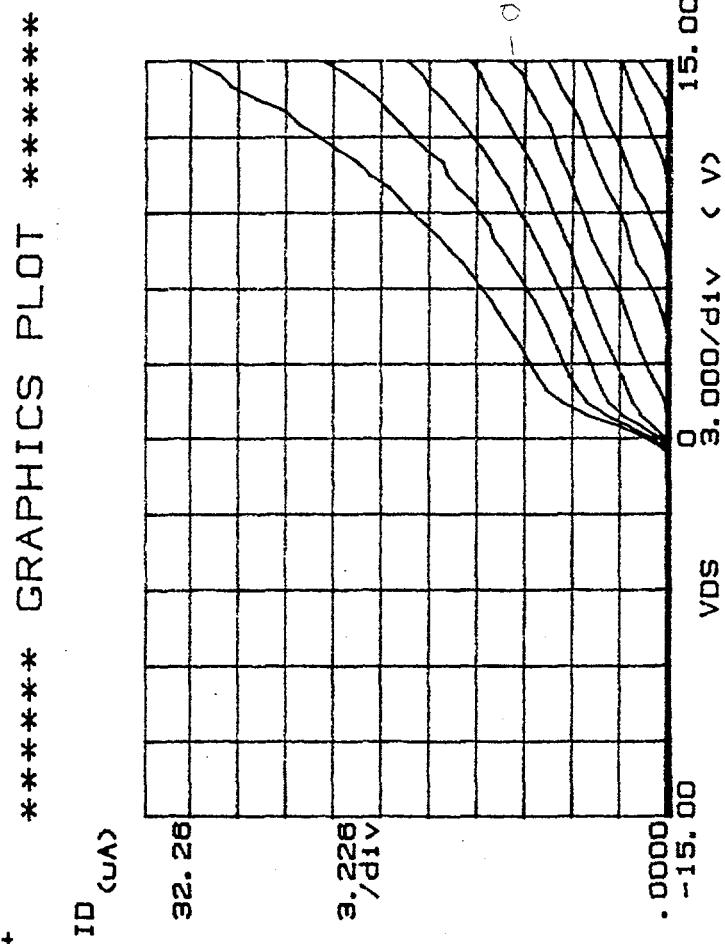

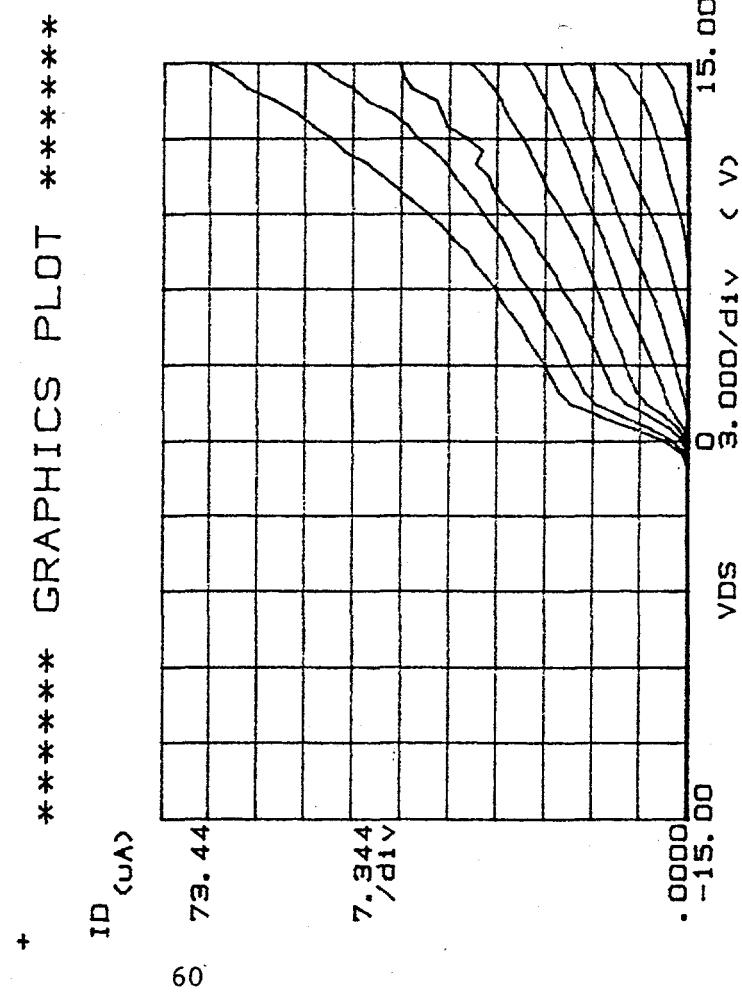

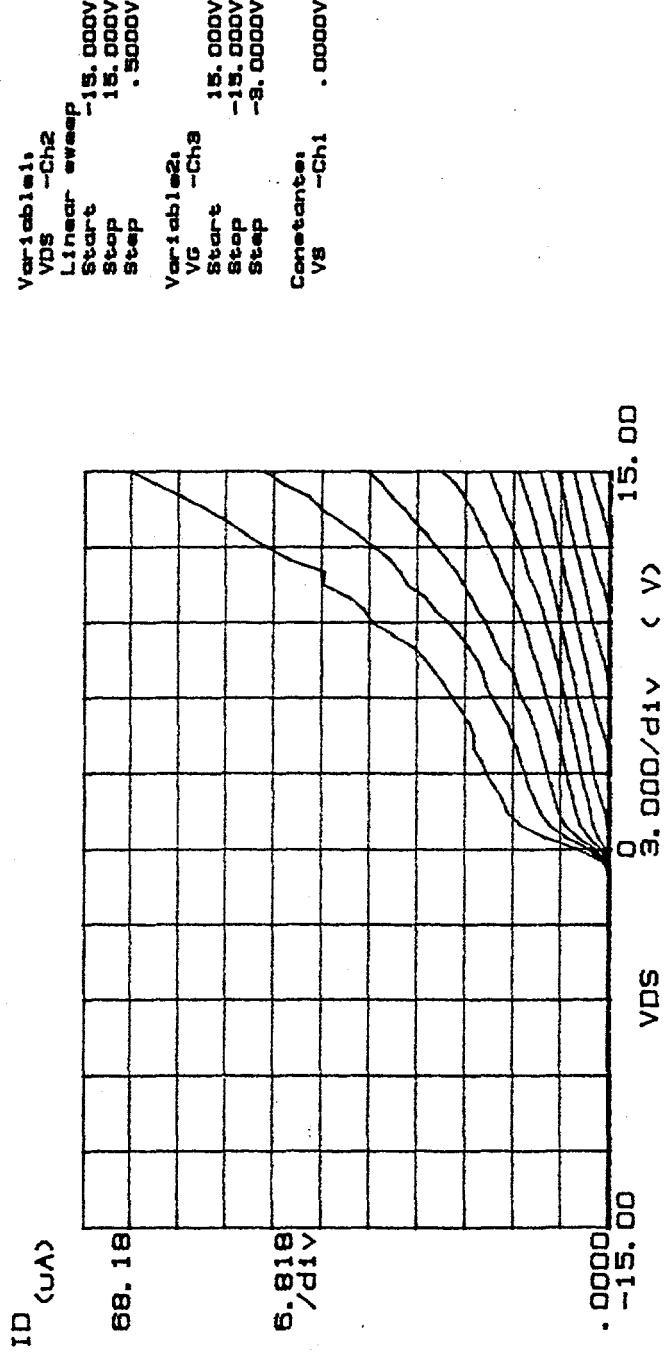

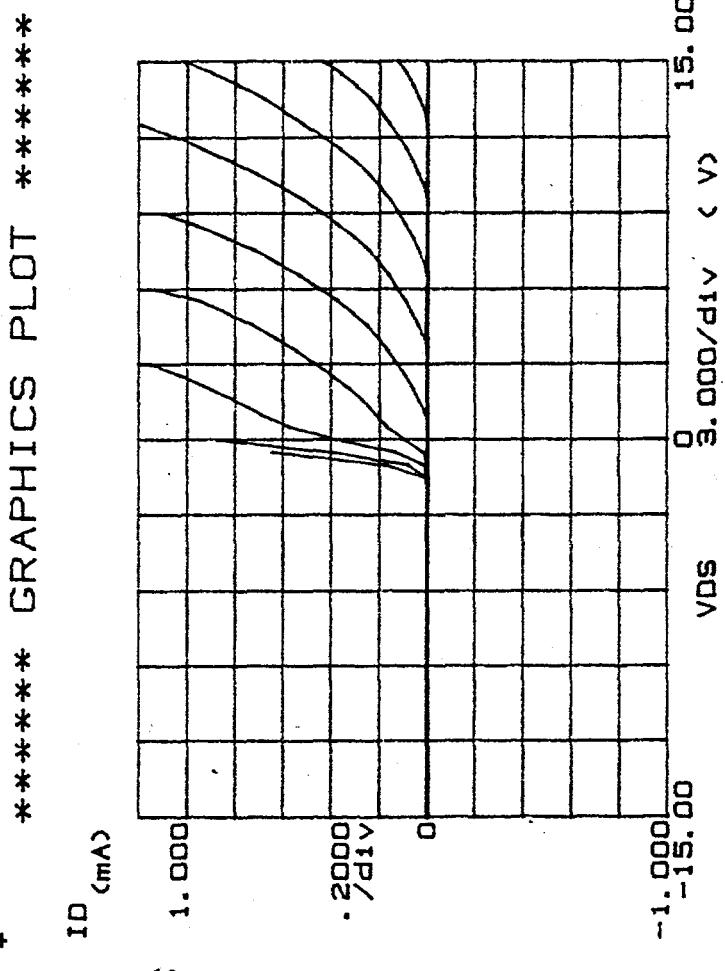

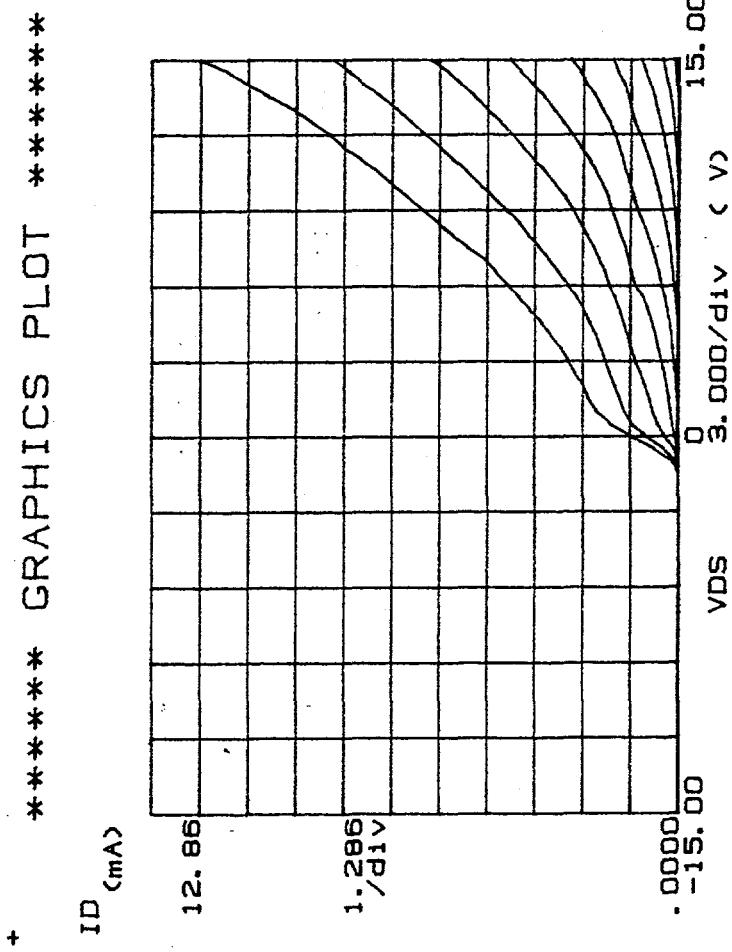

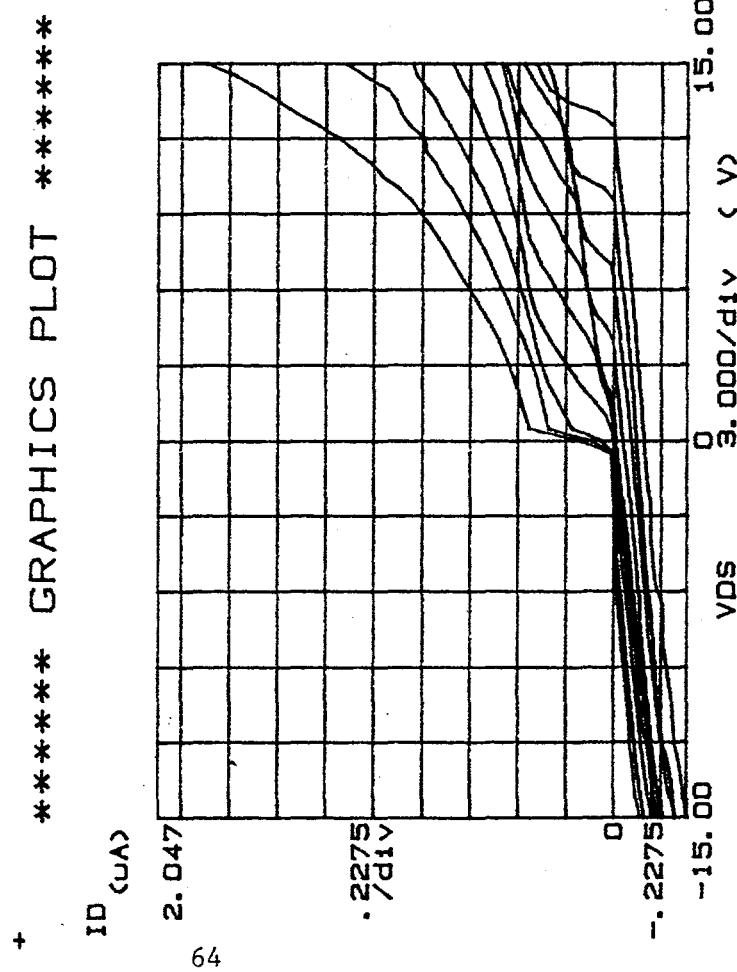

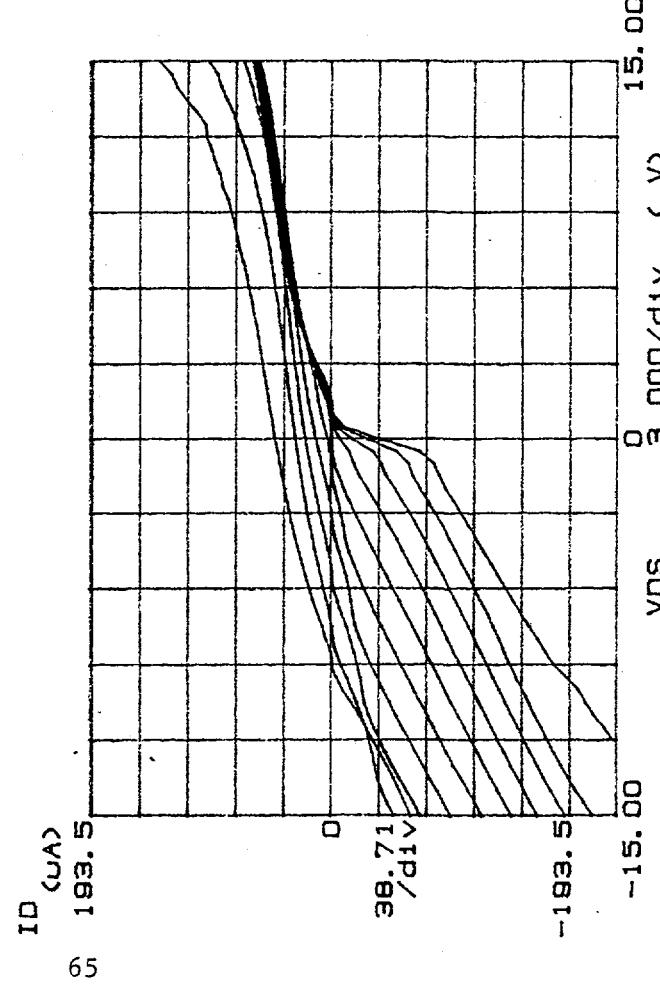

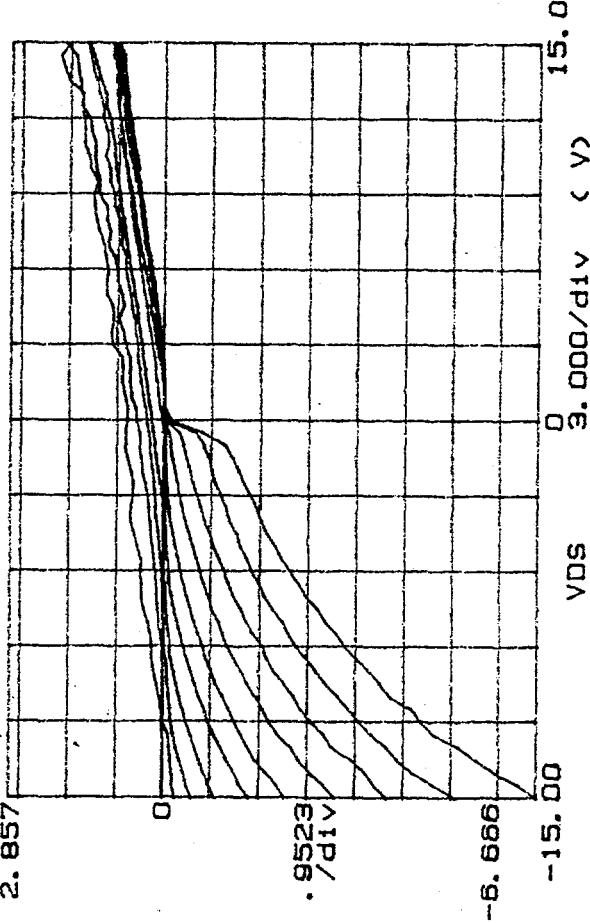

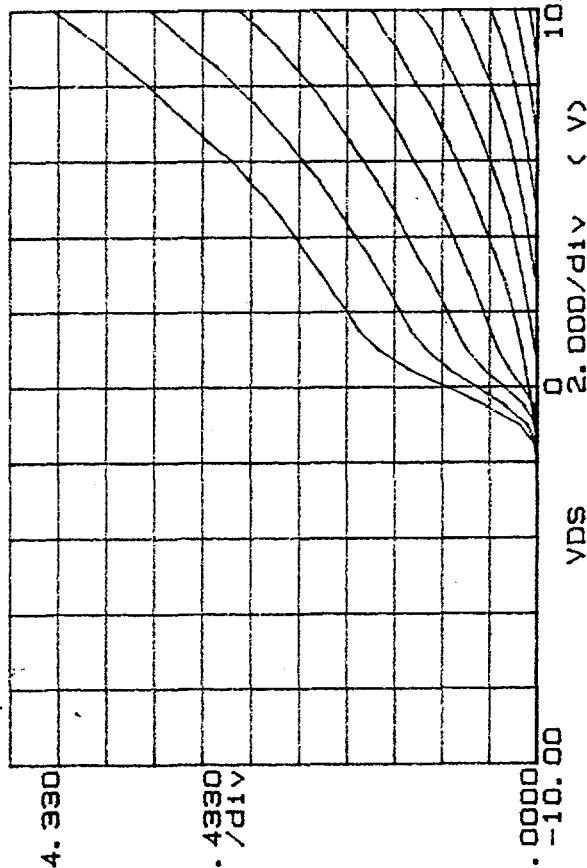

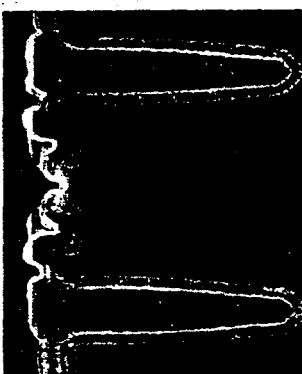

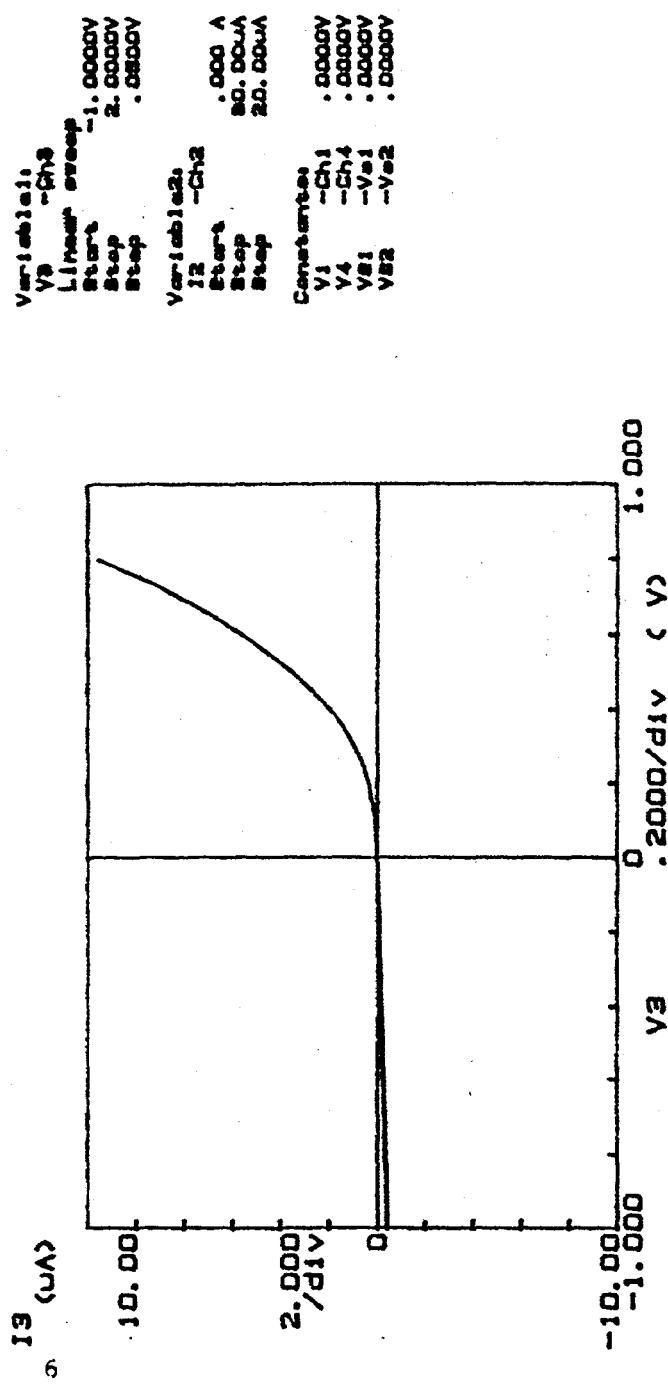

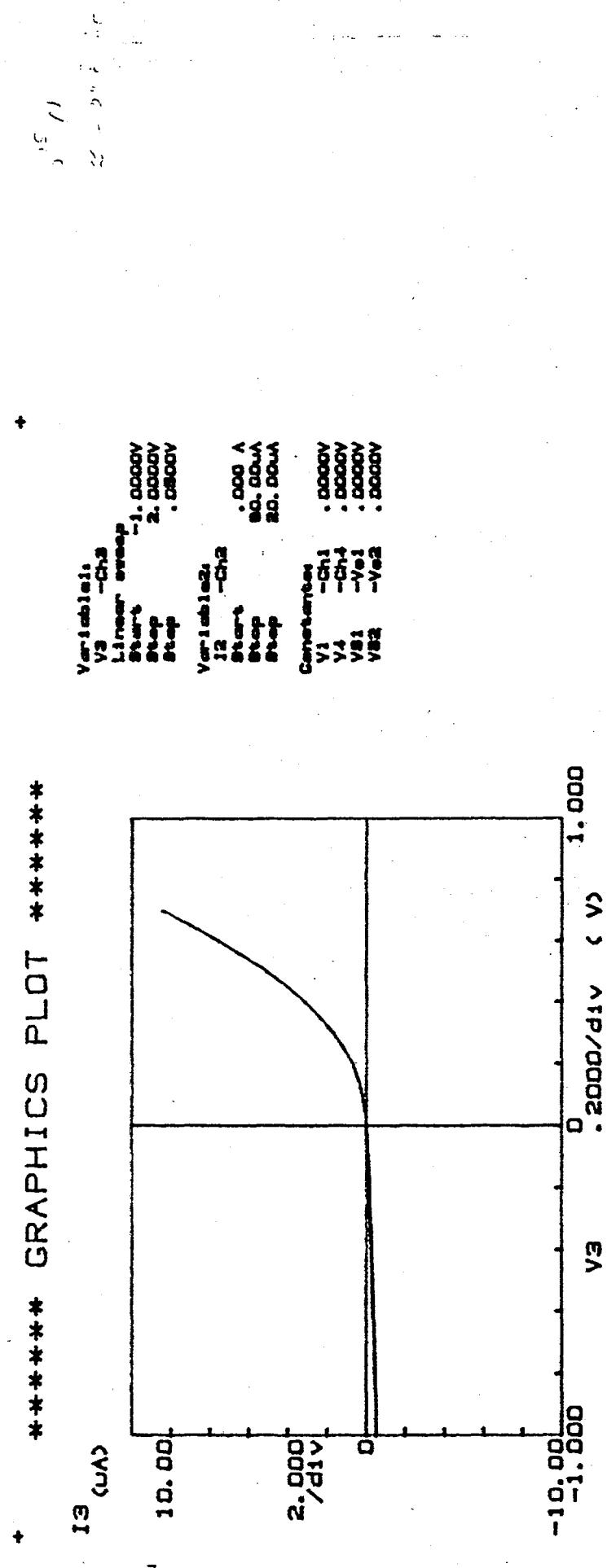

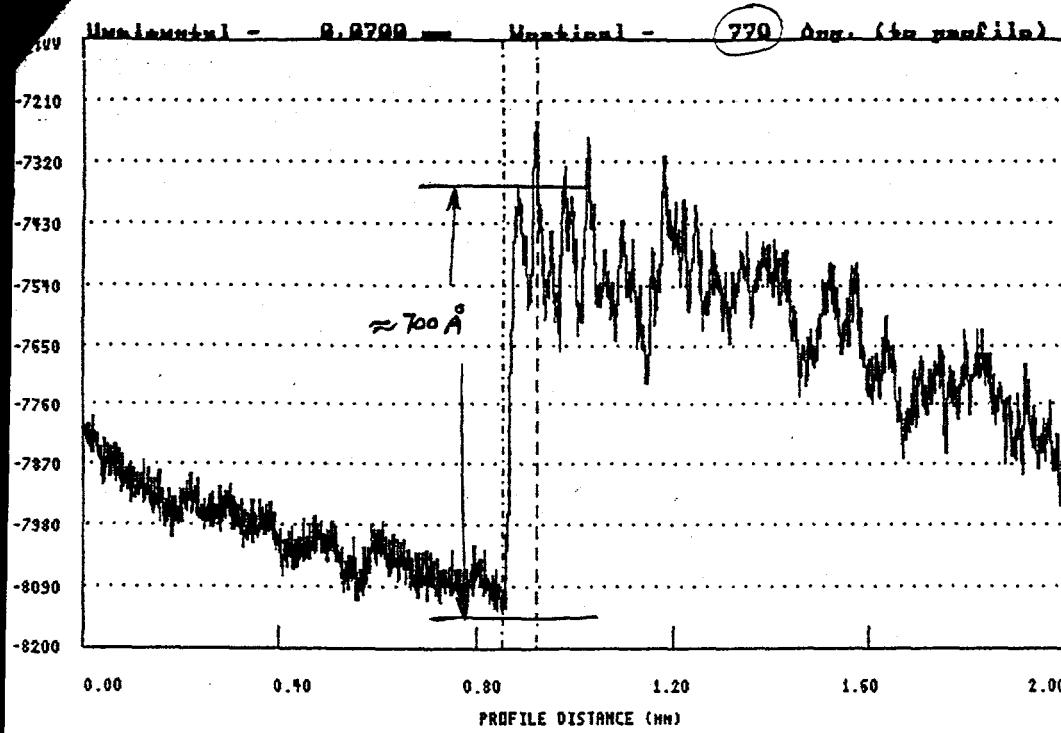

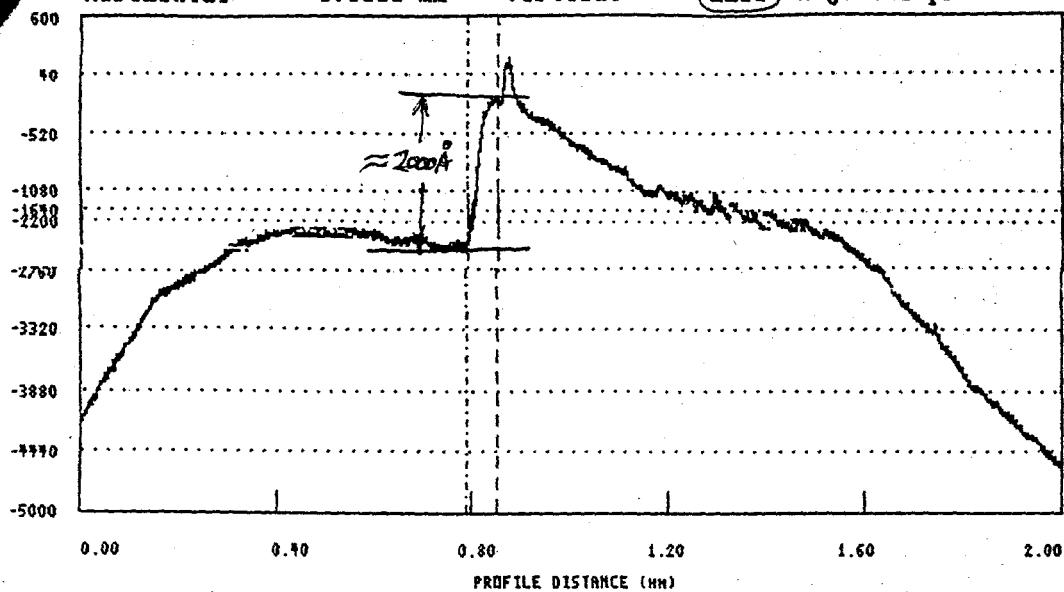

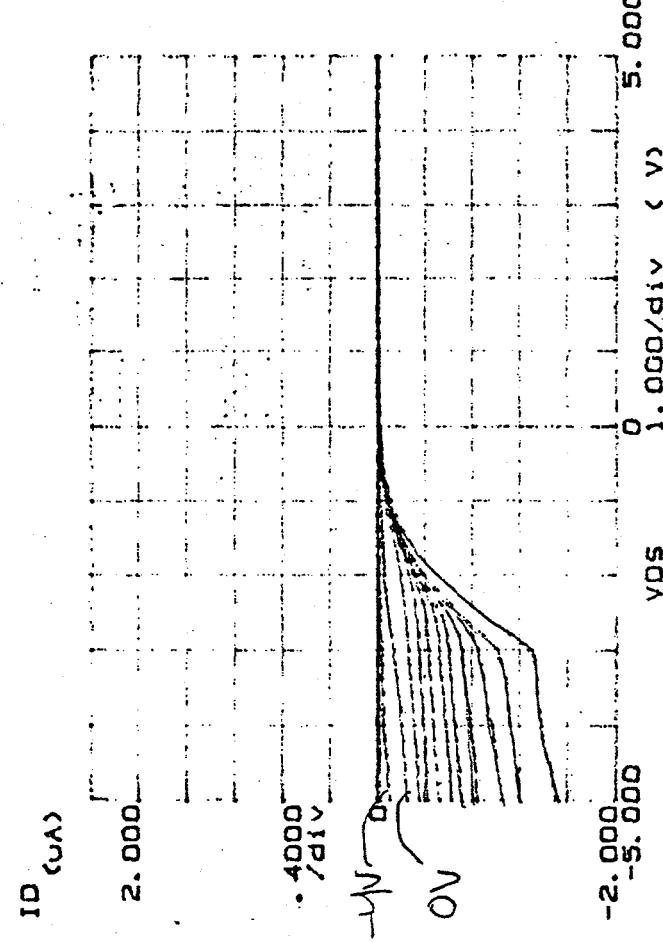

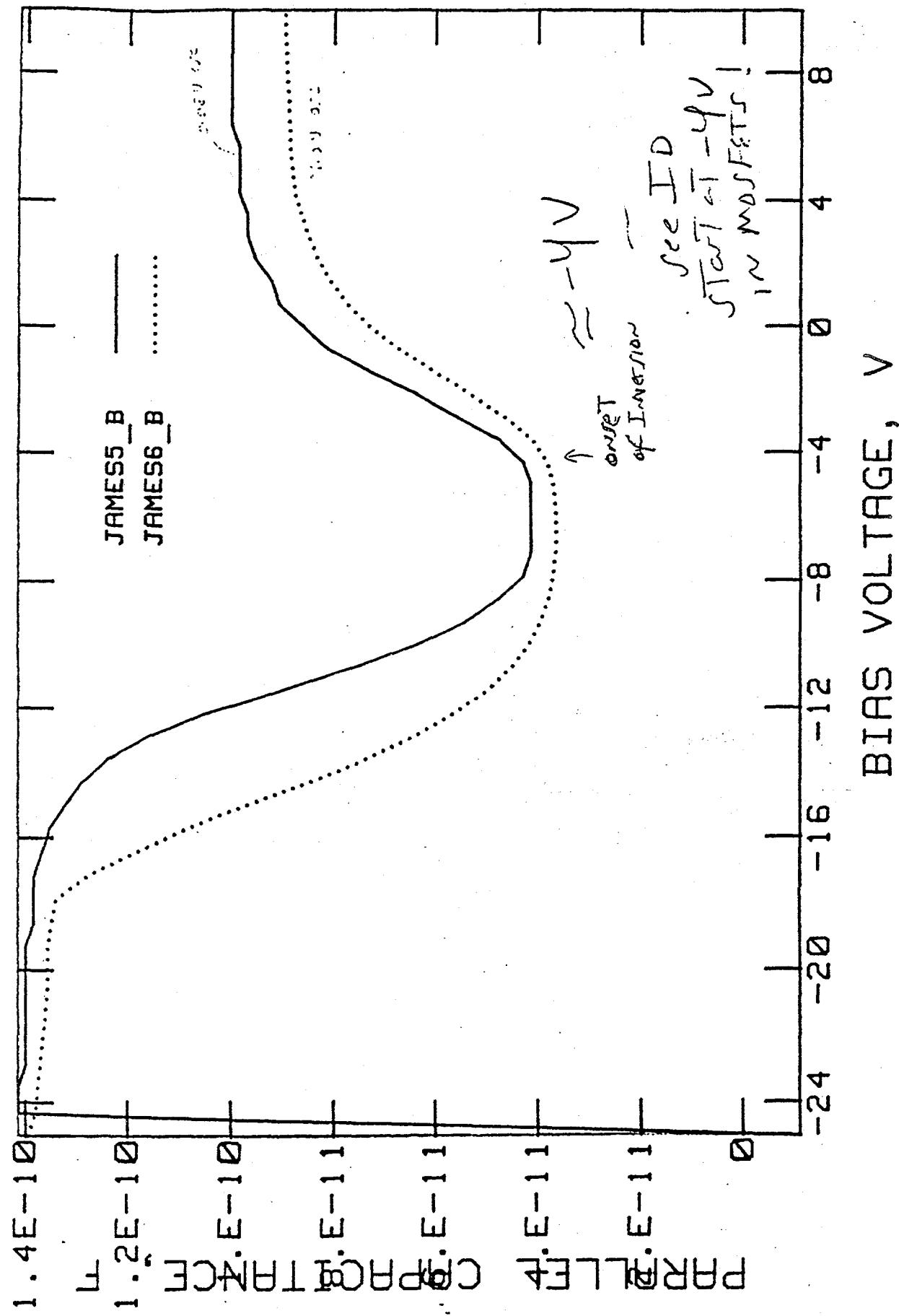

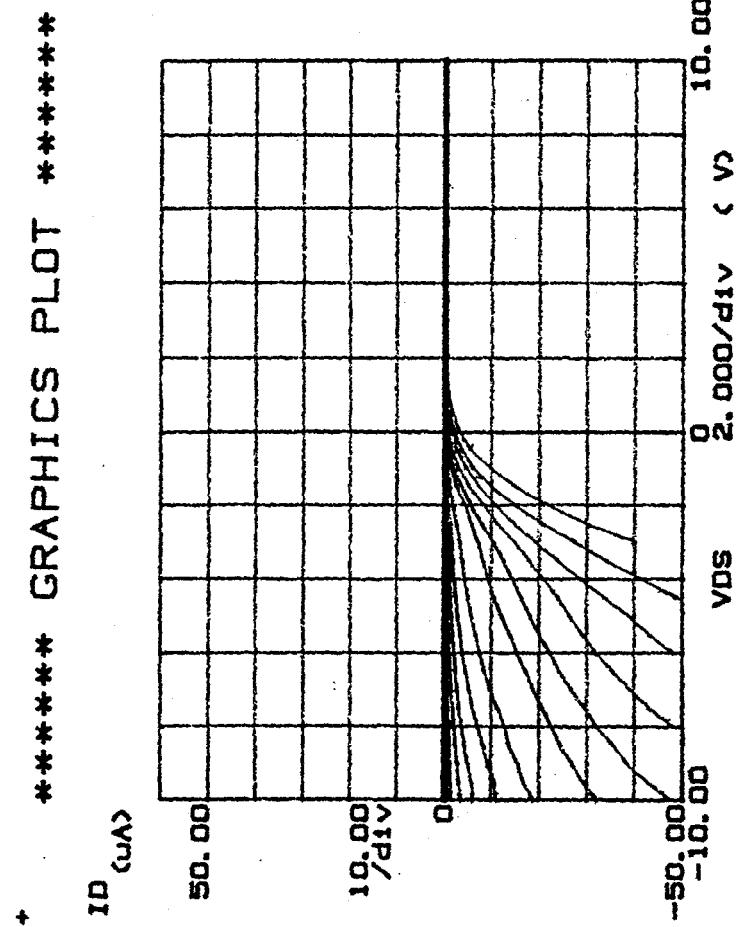

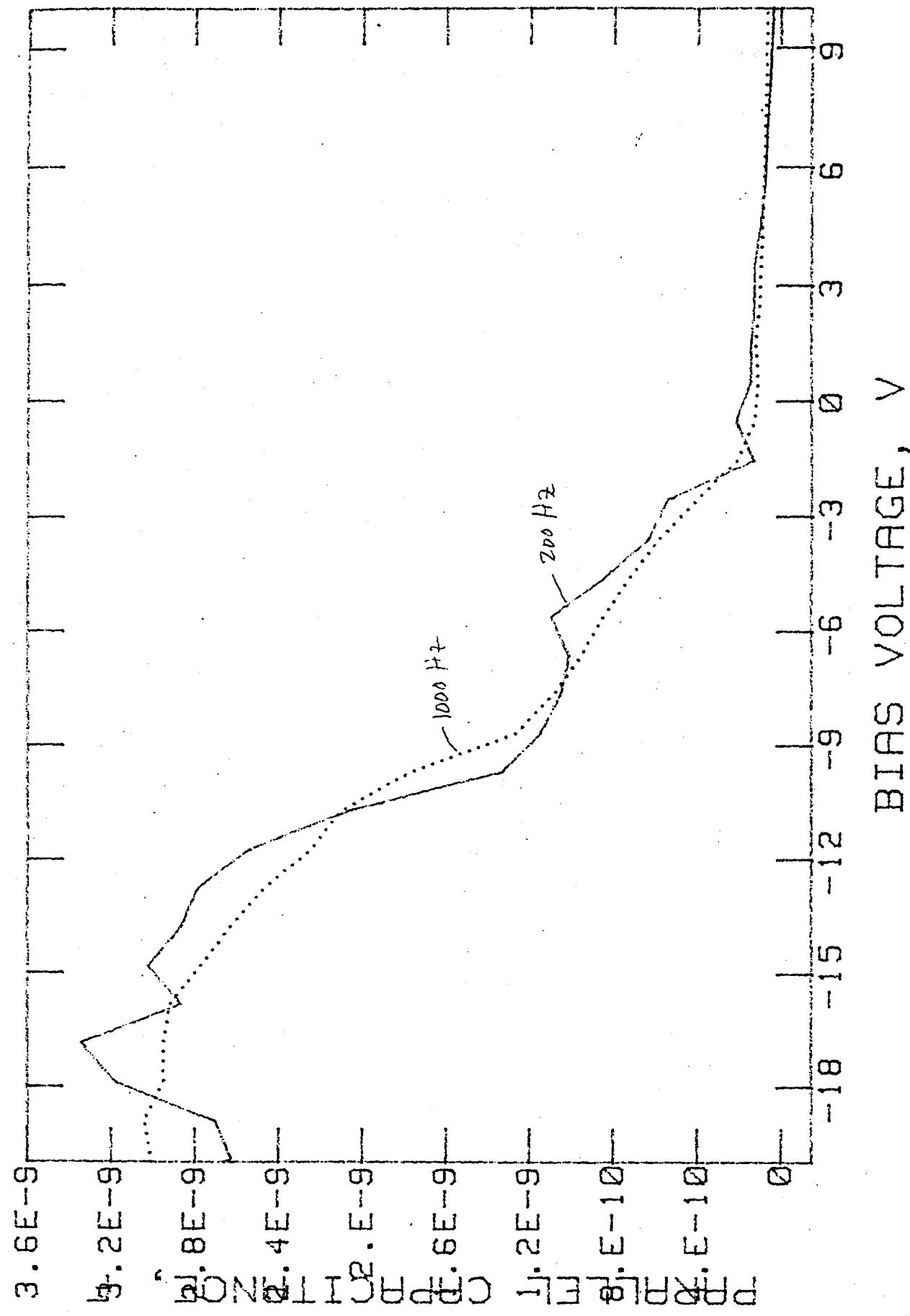

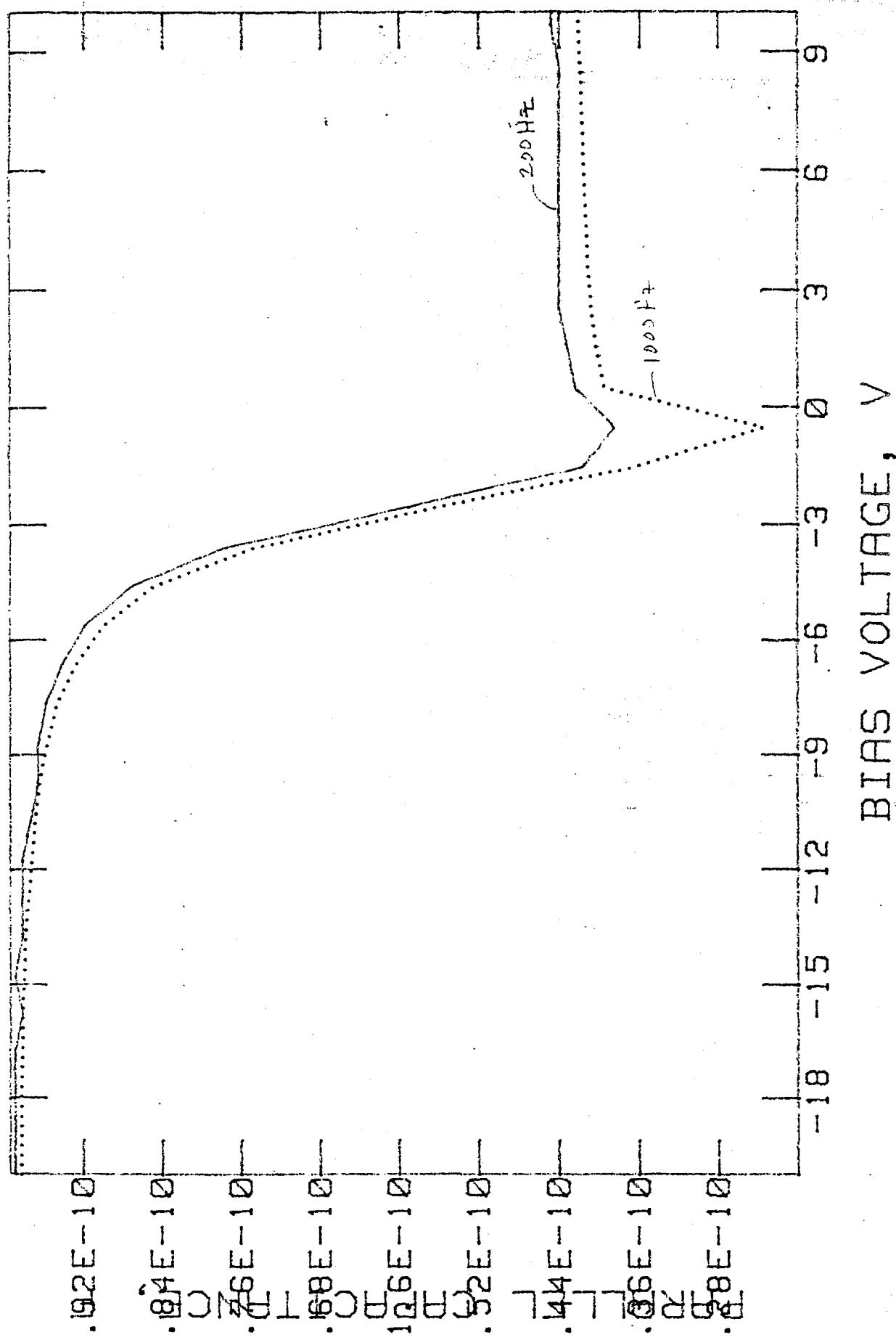

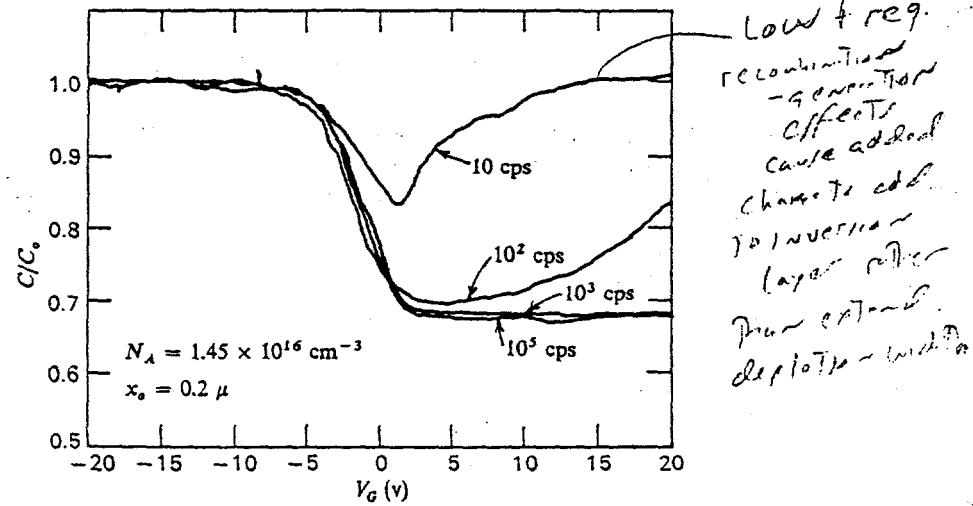

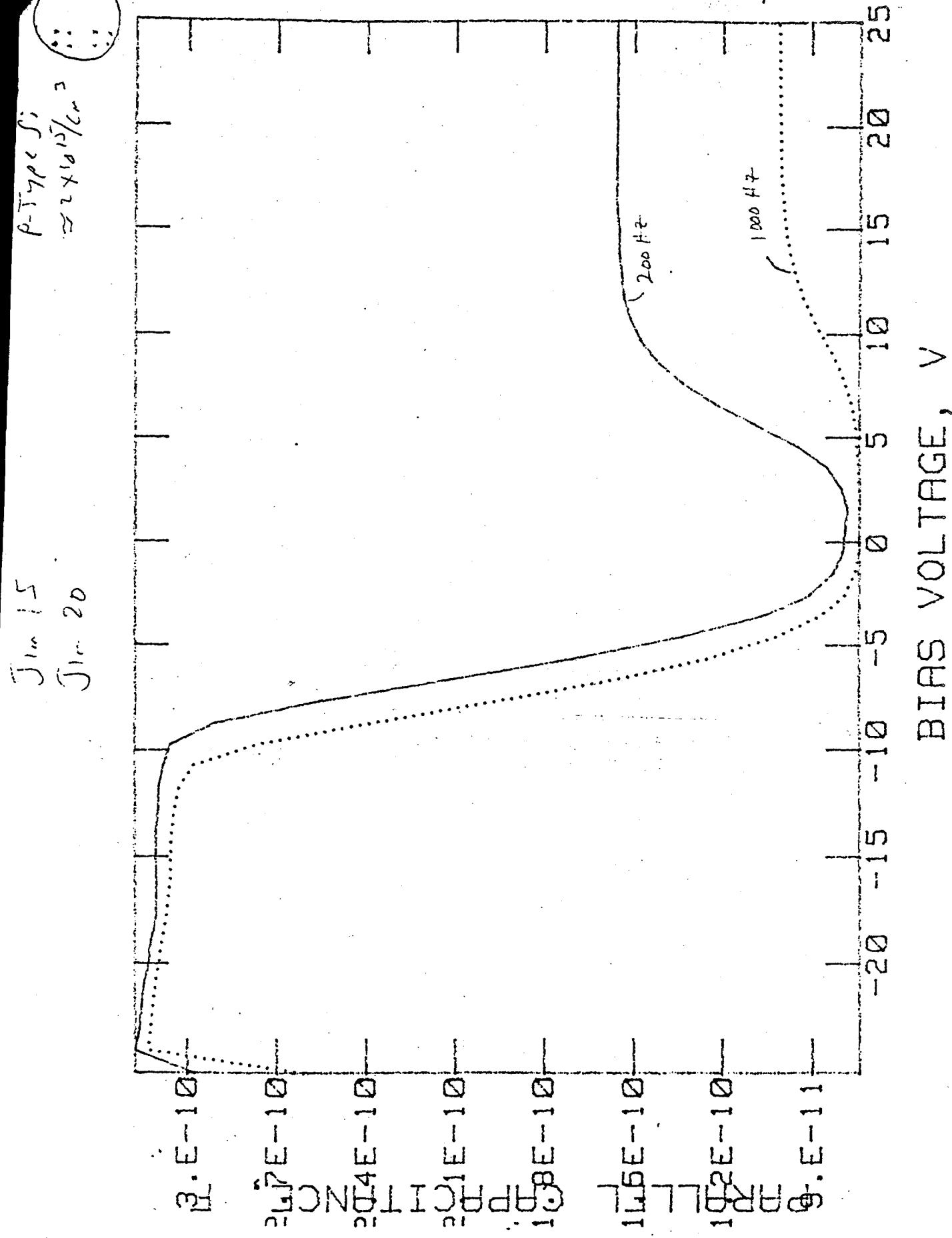

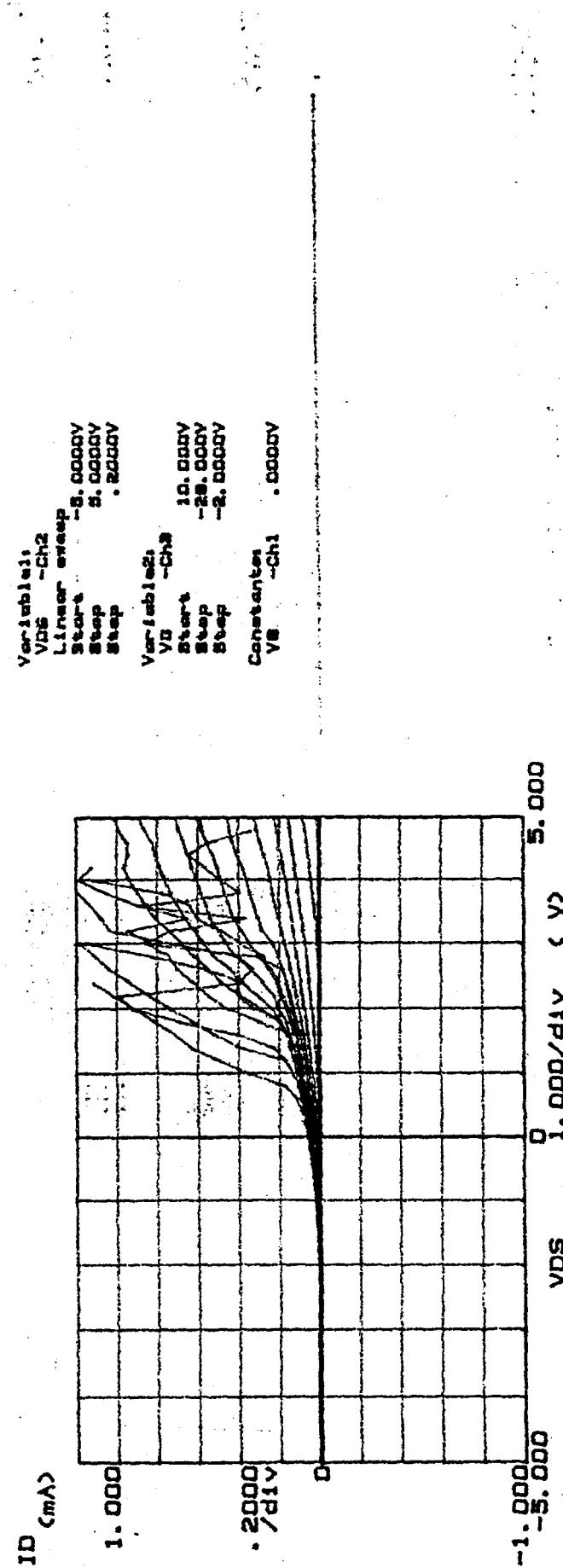

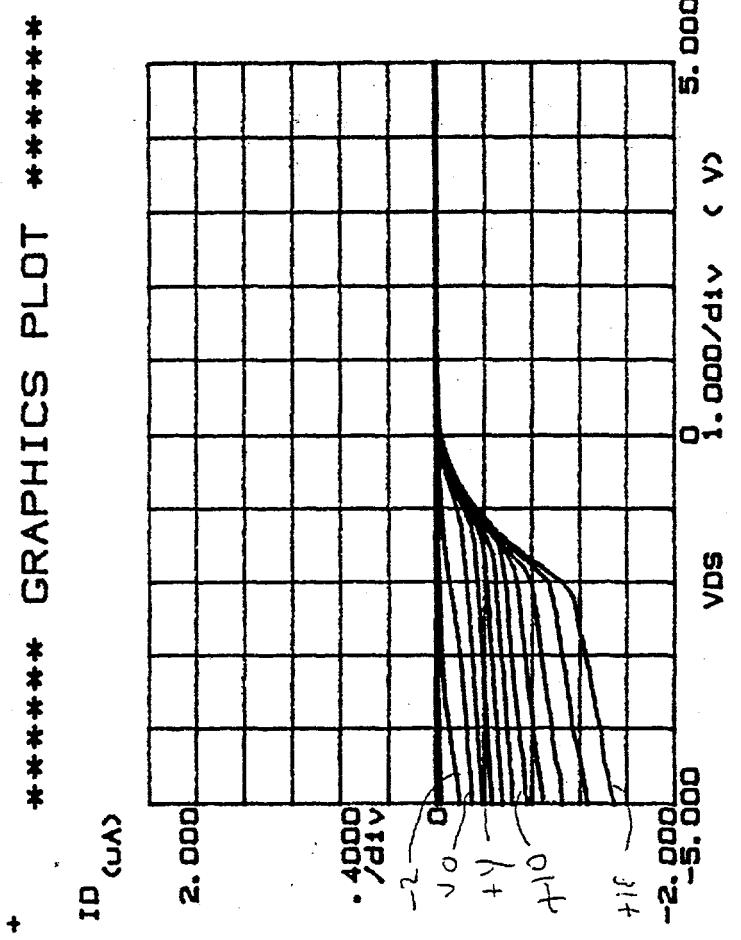

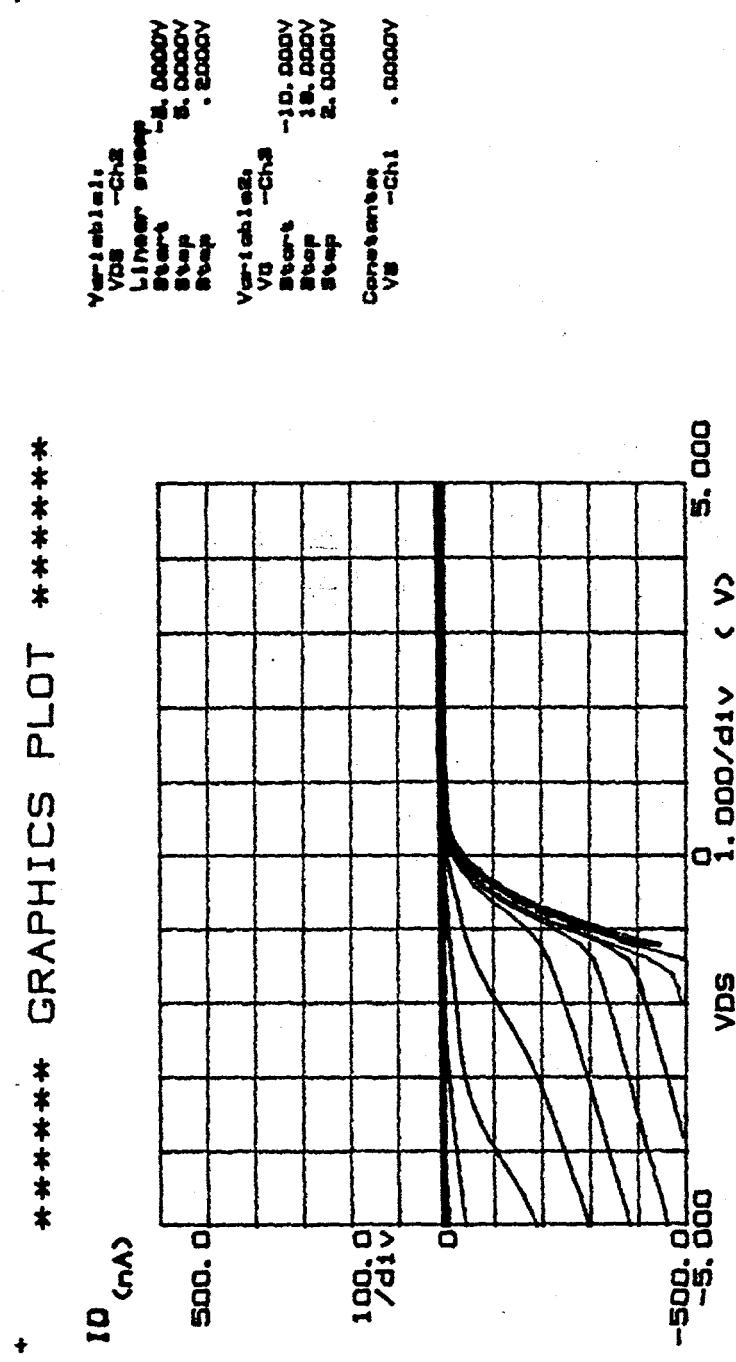

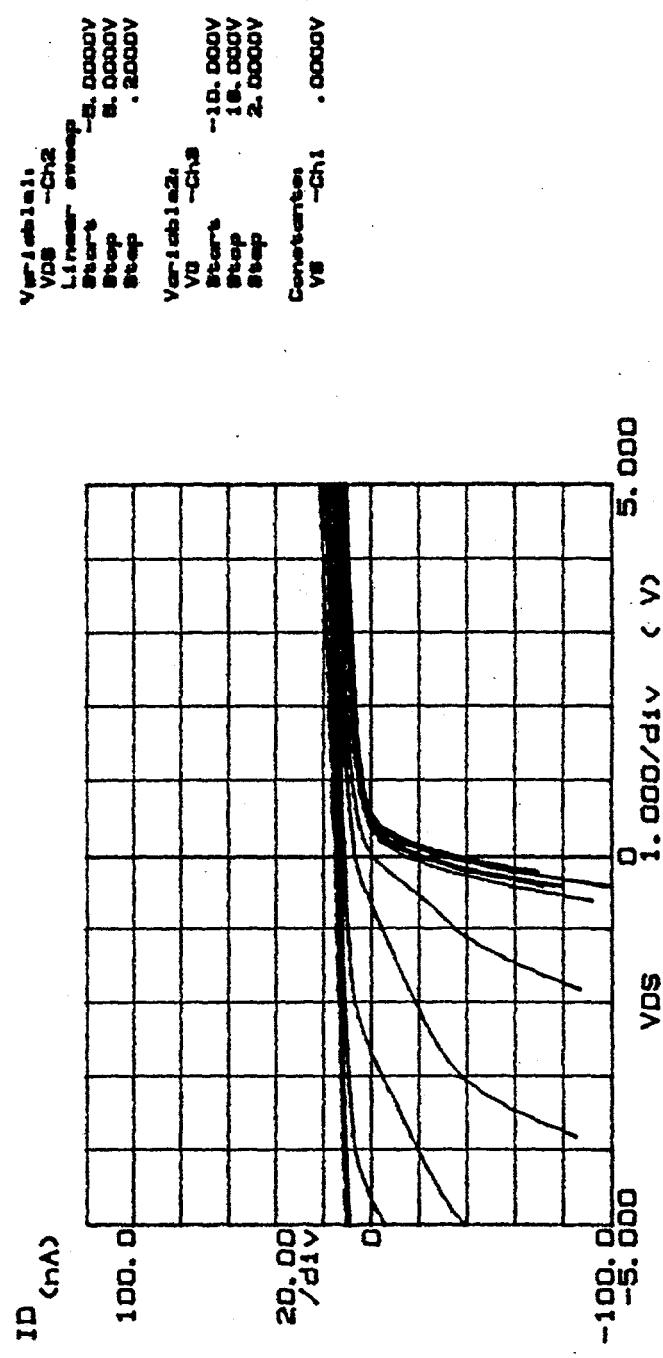

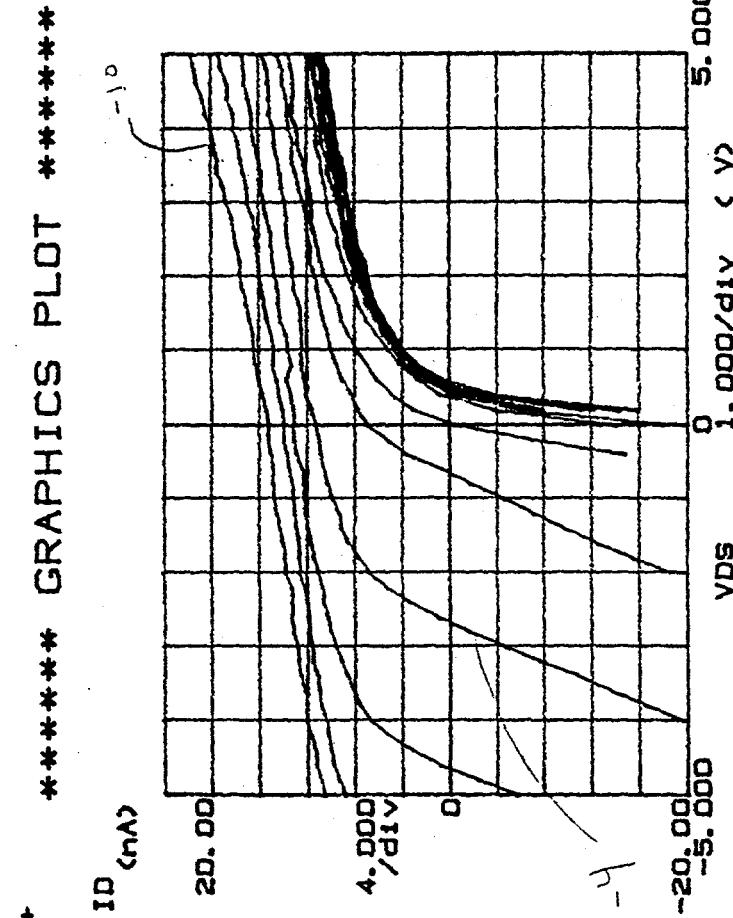

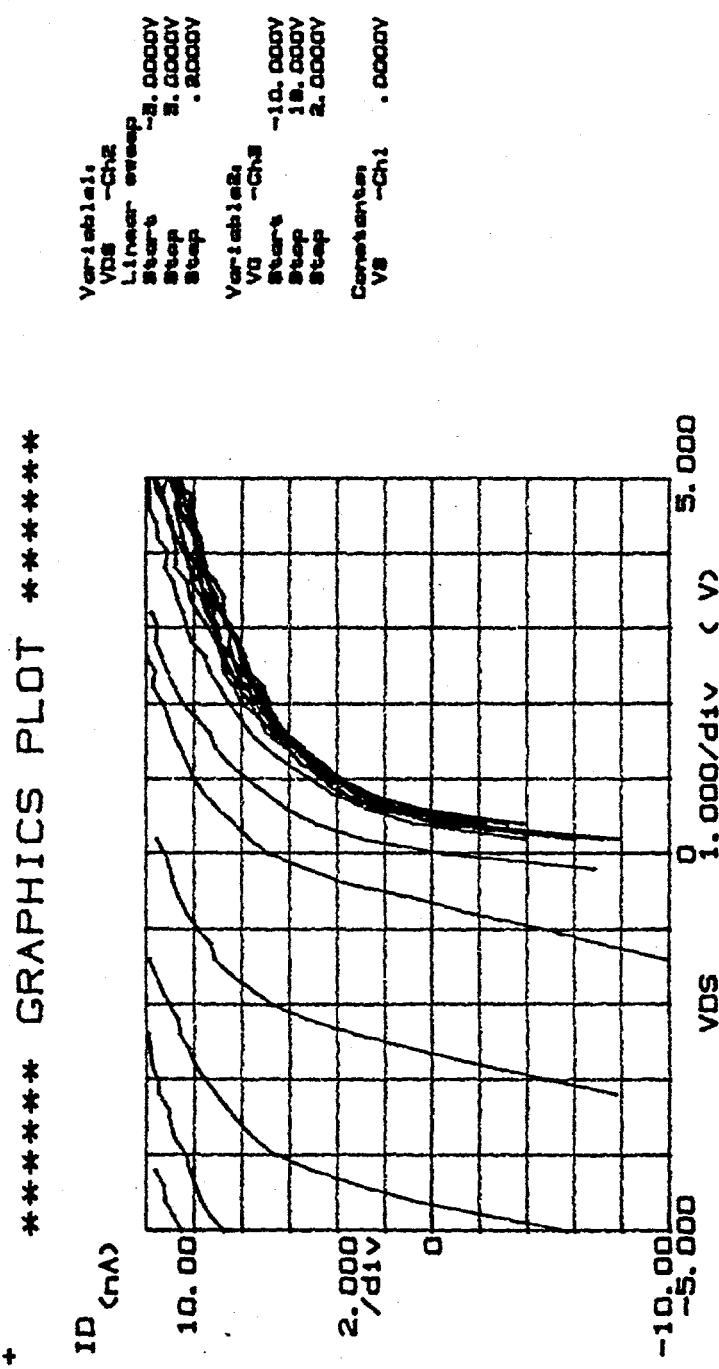

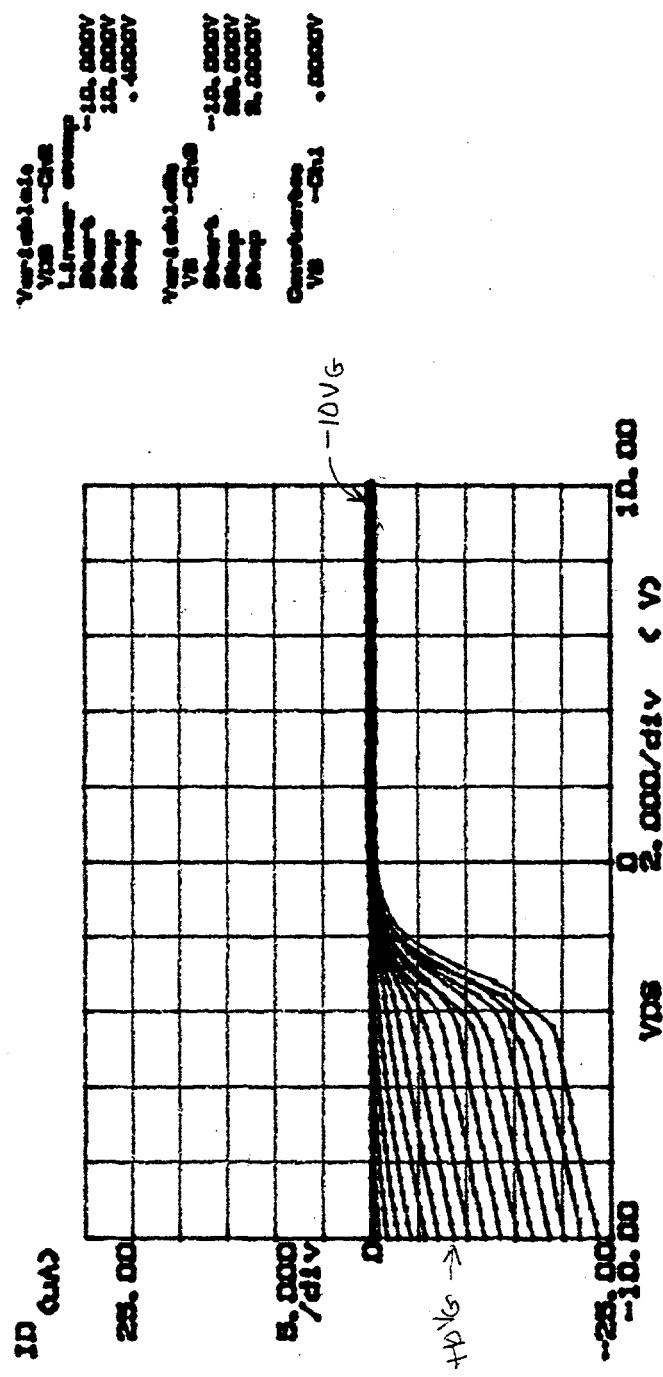

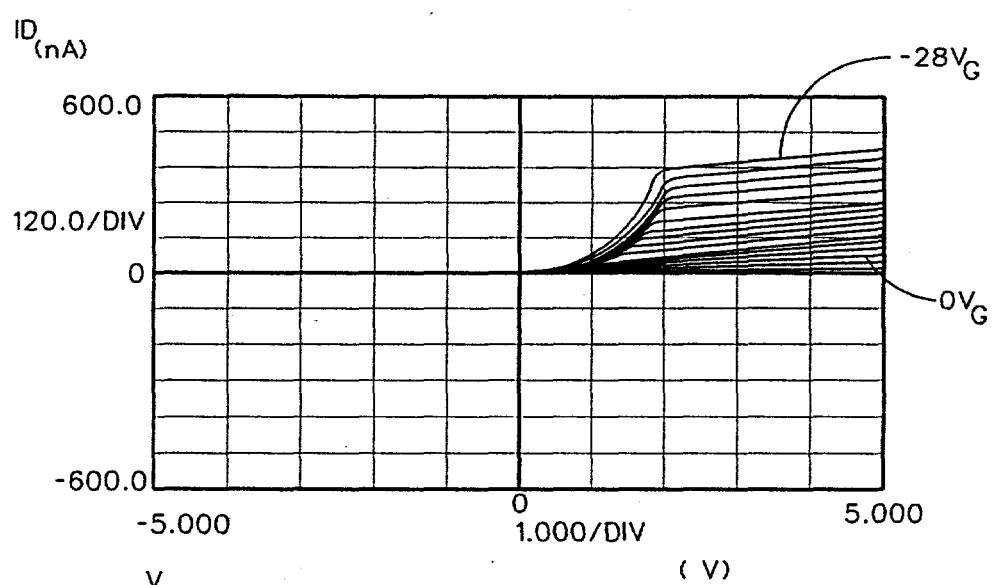

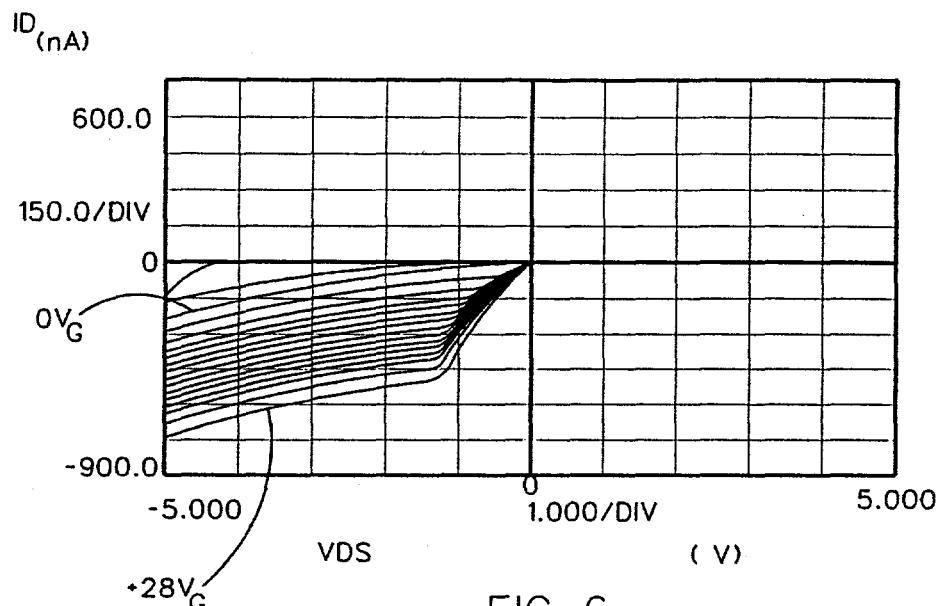

The following Series of Graphs show actual Empirically obtained Data achieved by investigation of Actual Fabricated Devices. Above discussed phenomena are demonstrated thereby.

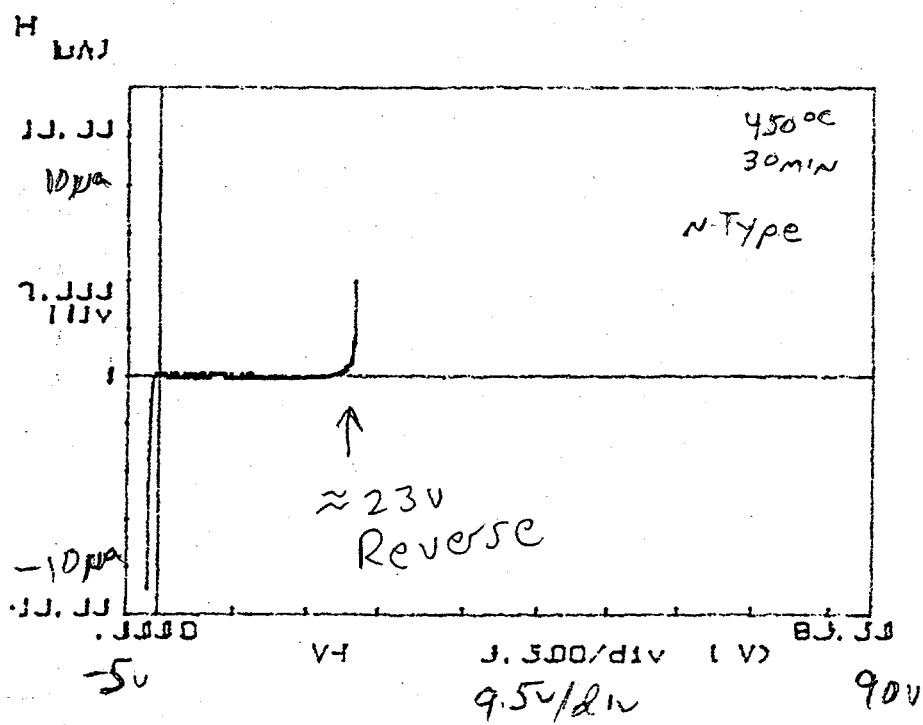

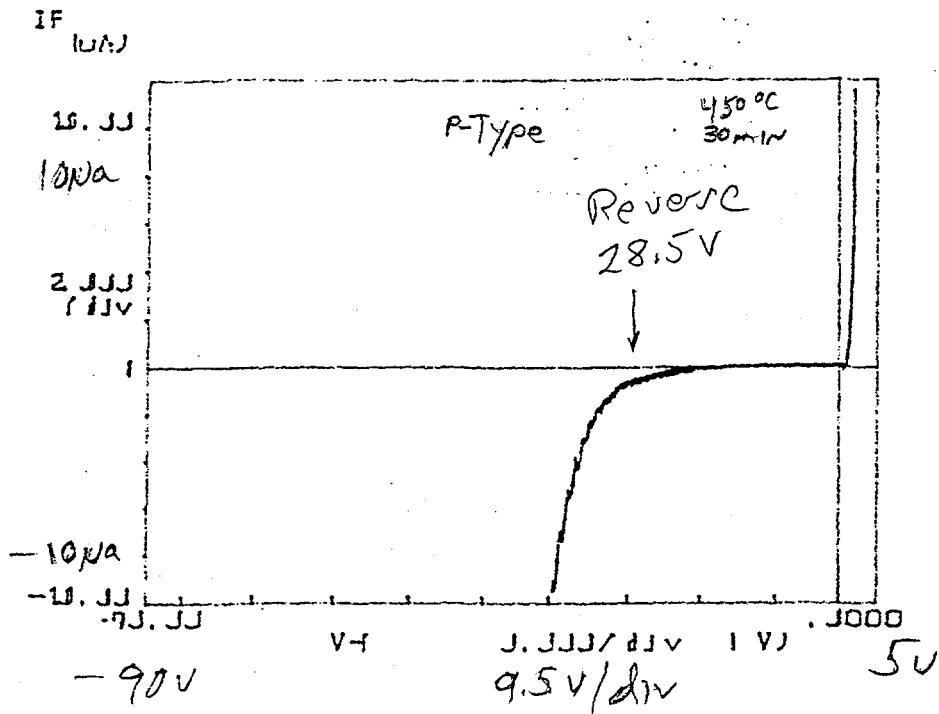

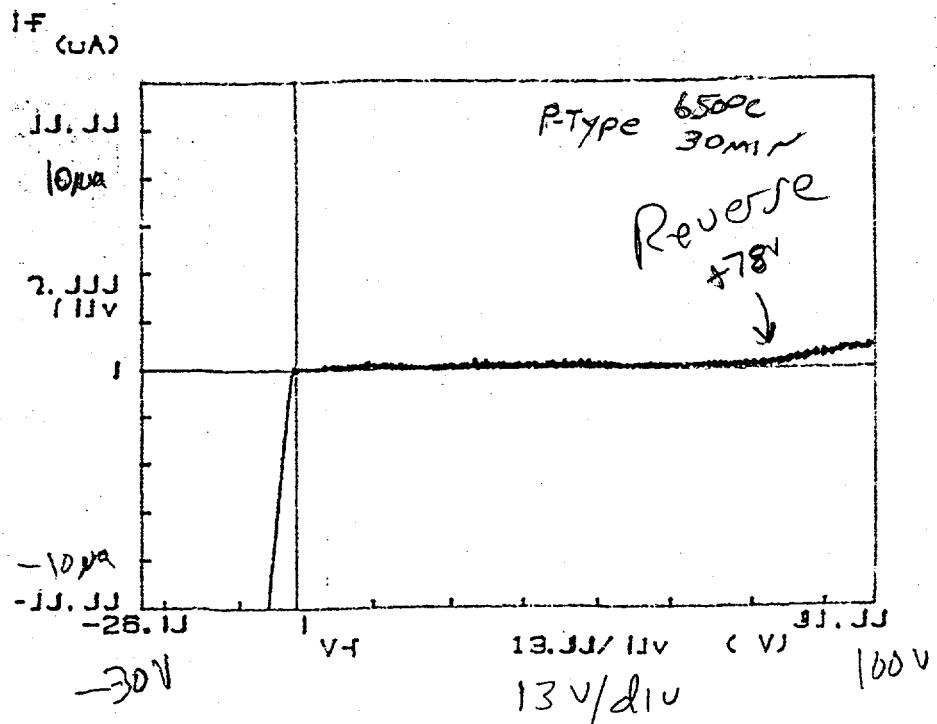

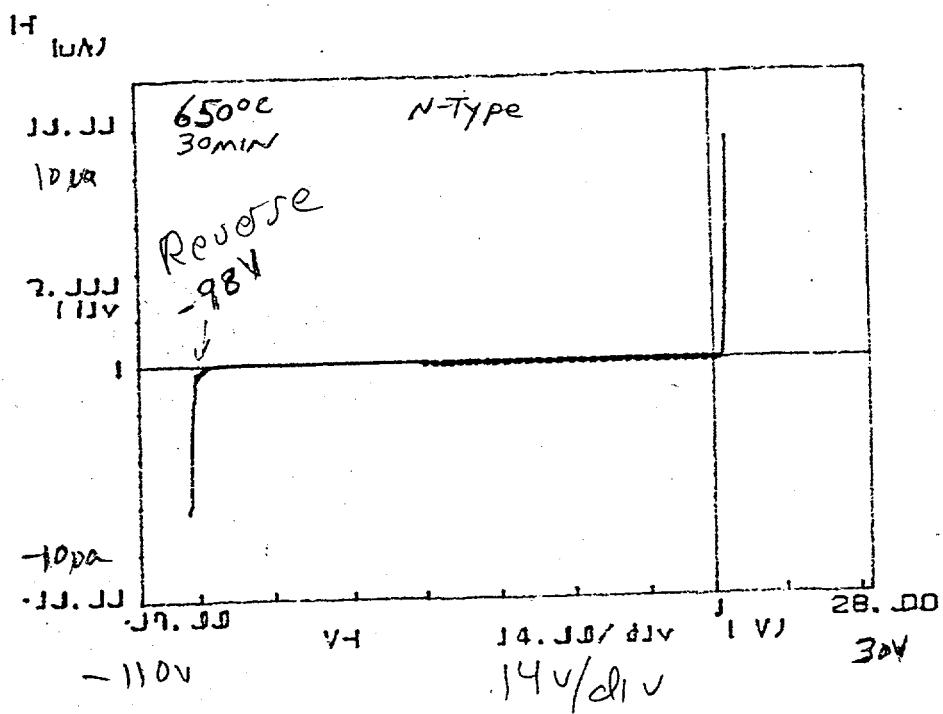

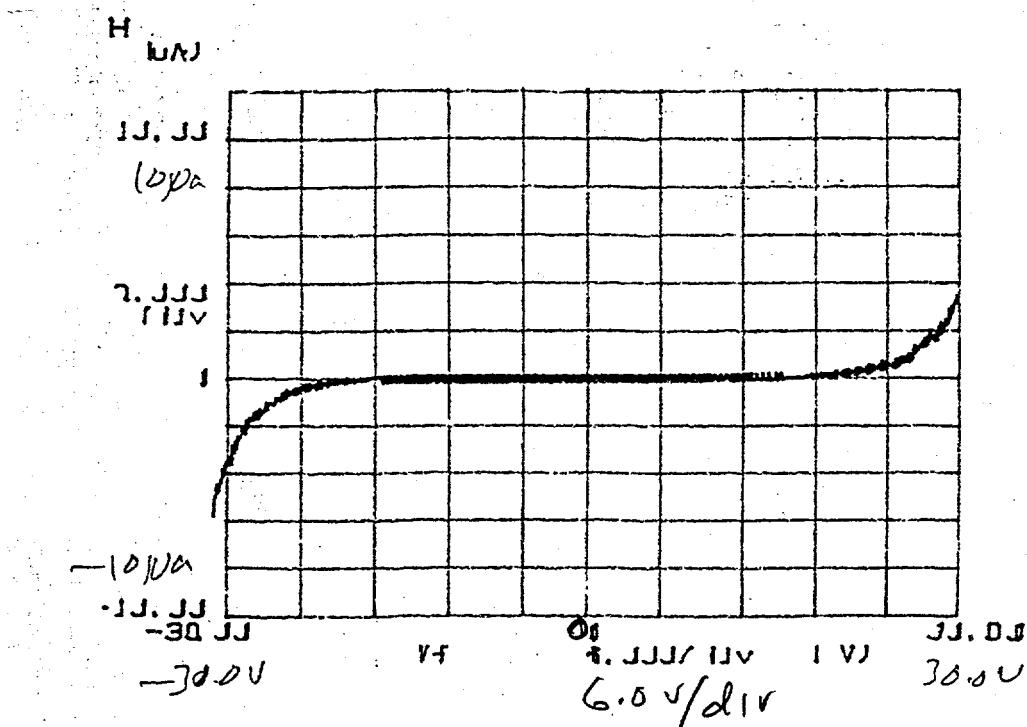

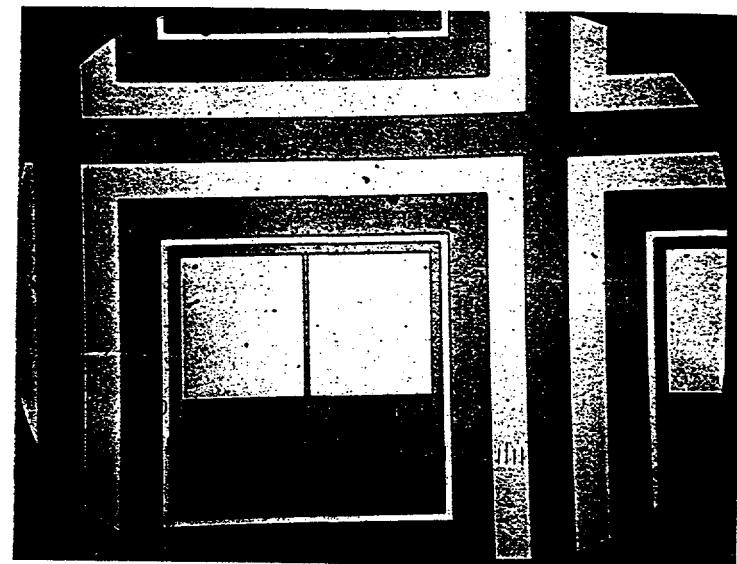

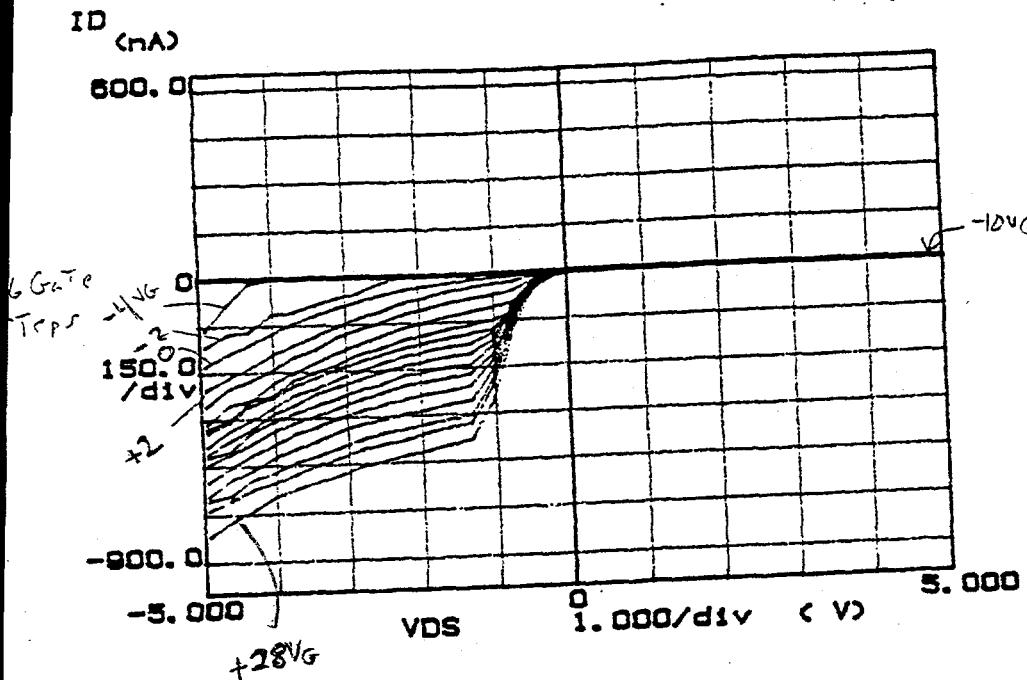

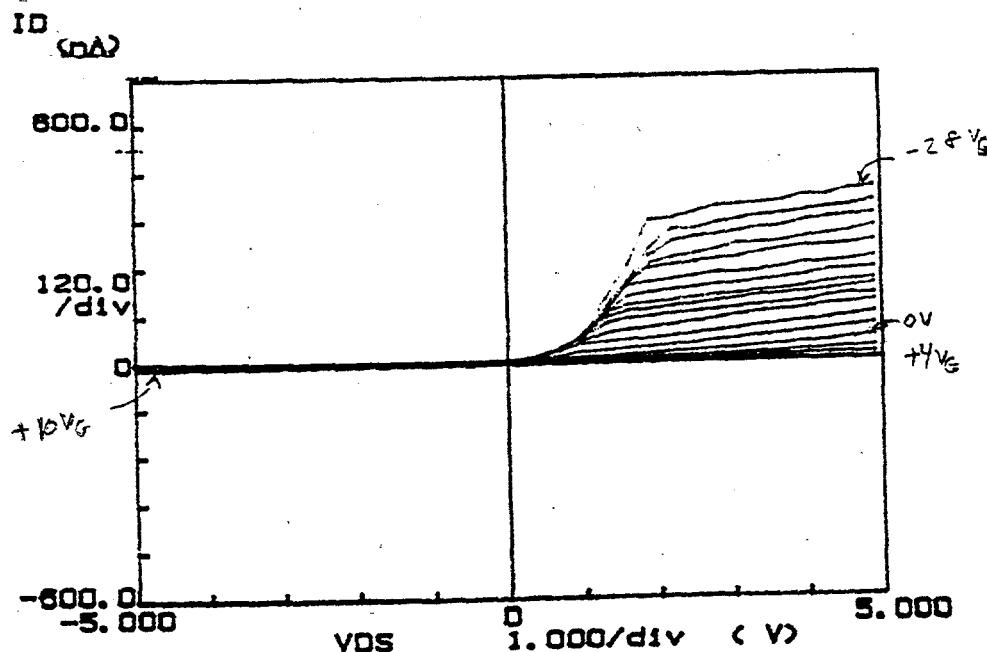

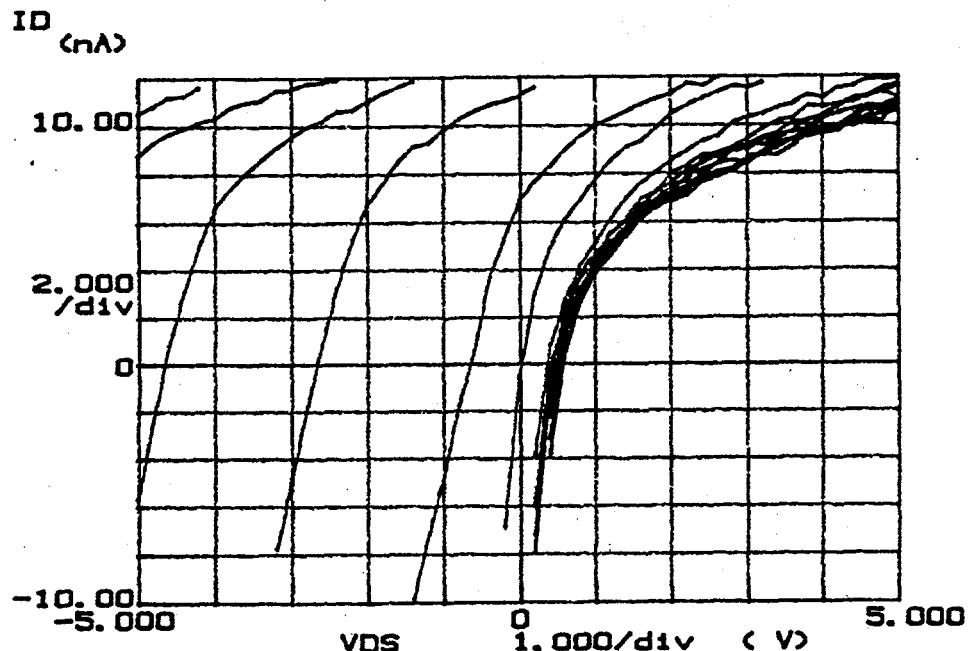

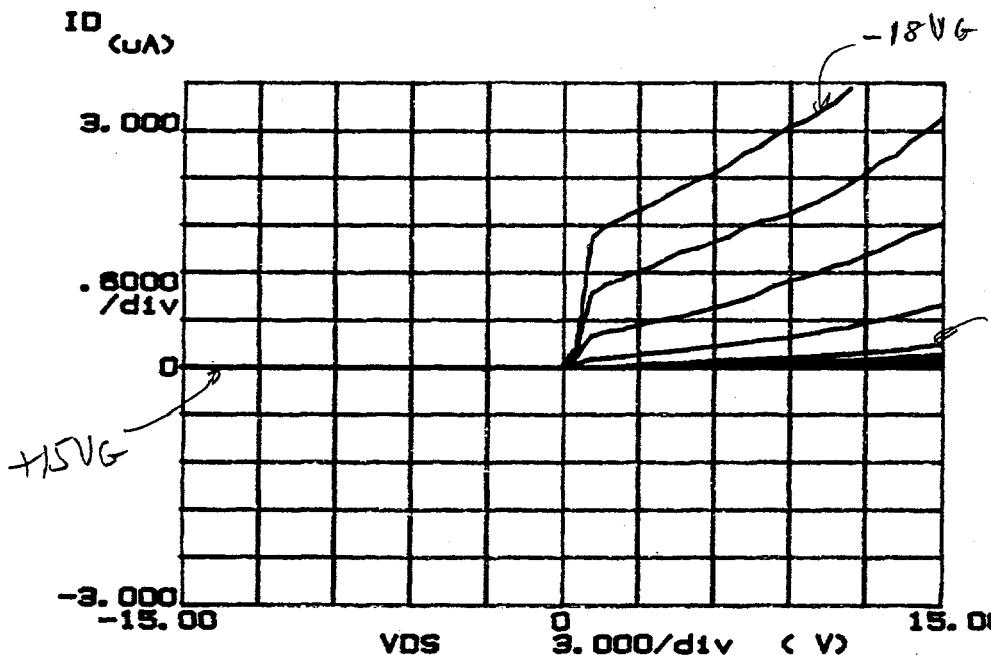

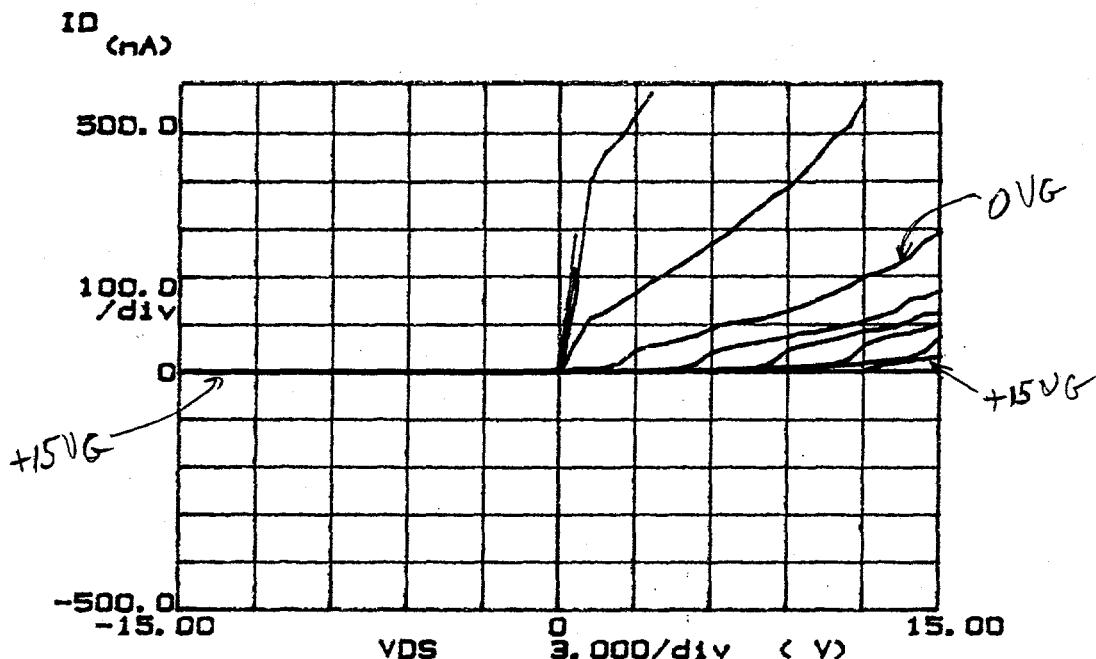

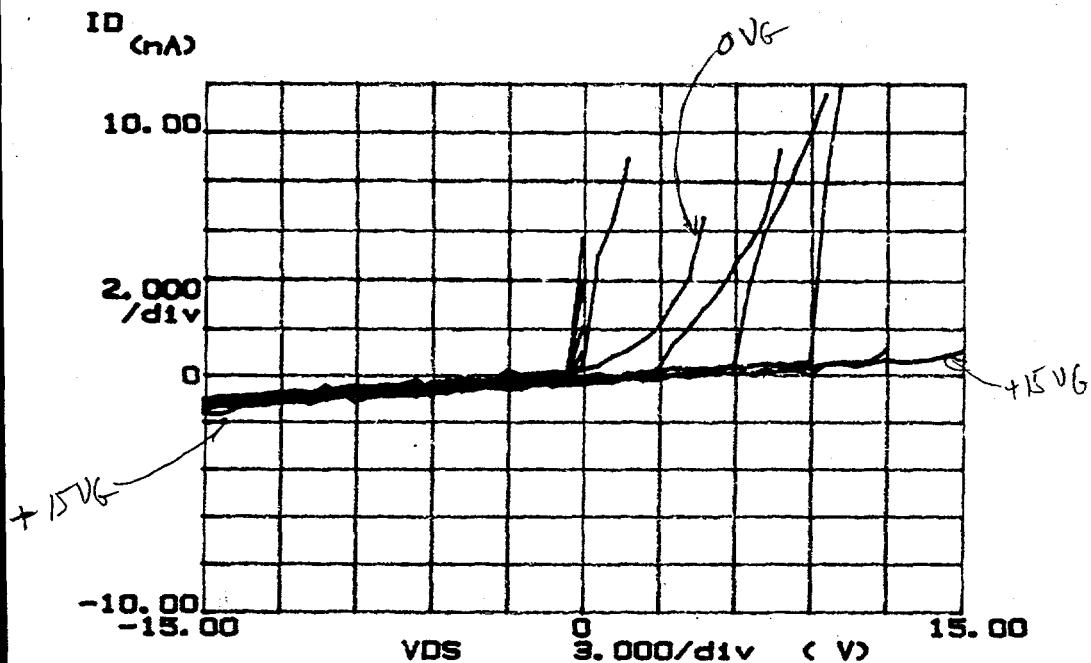

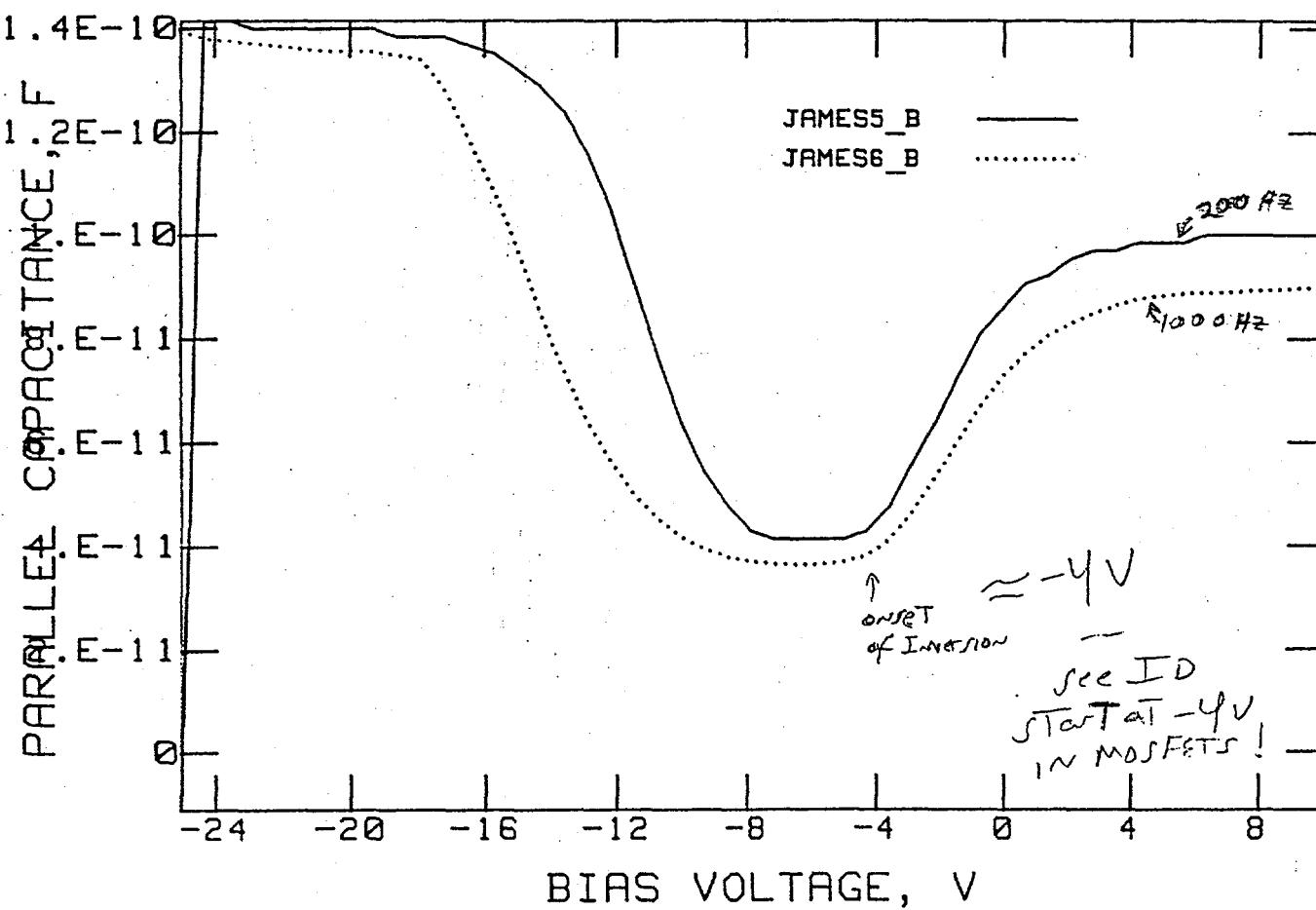

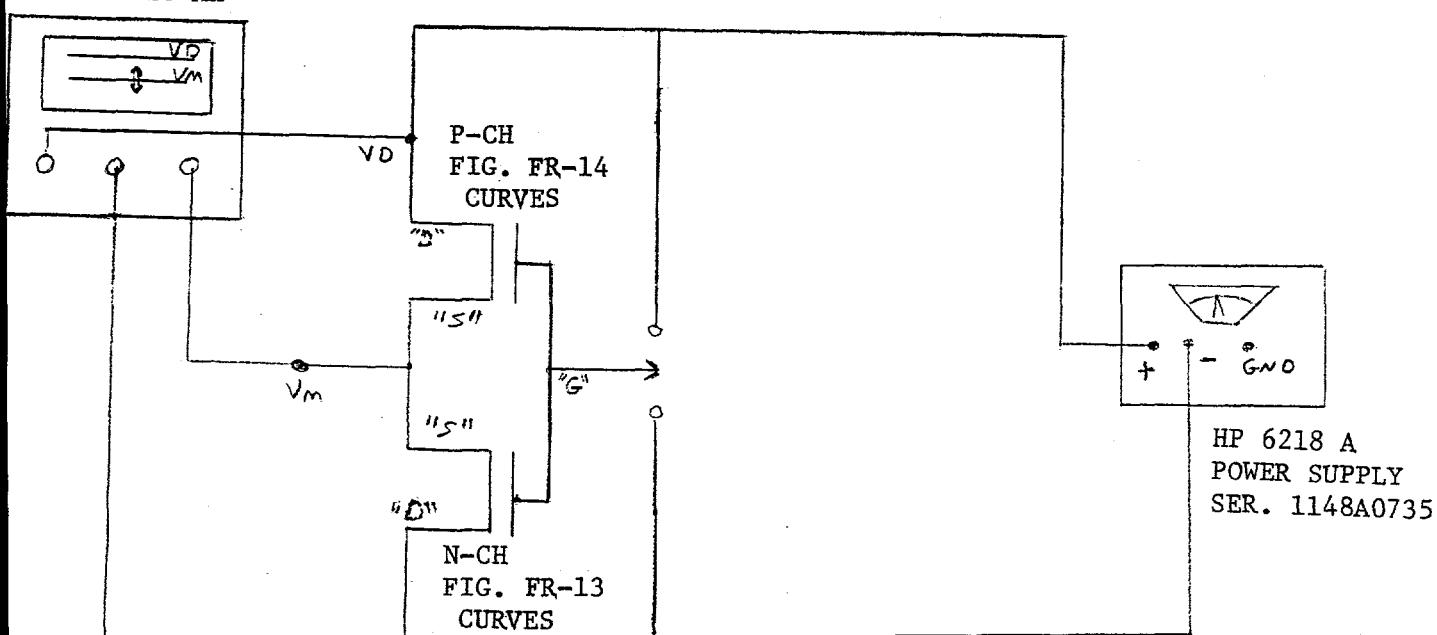

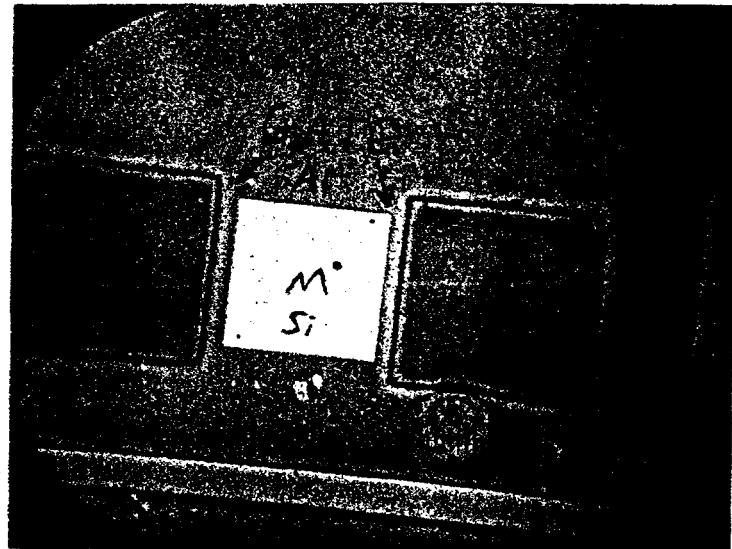

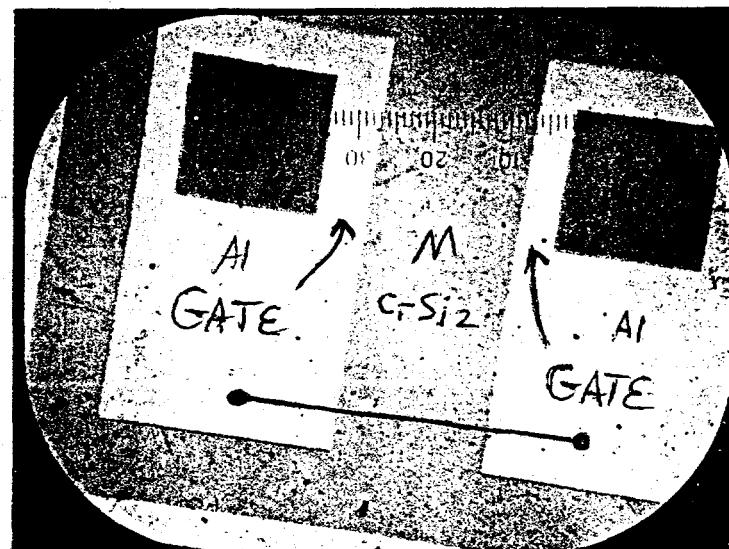

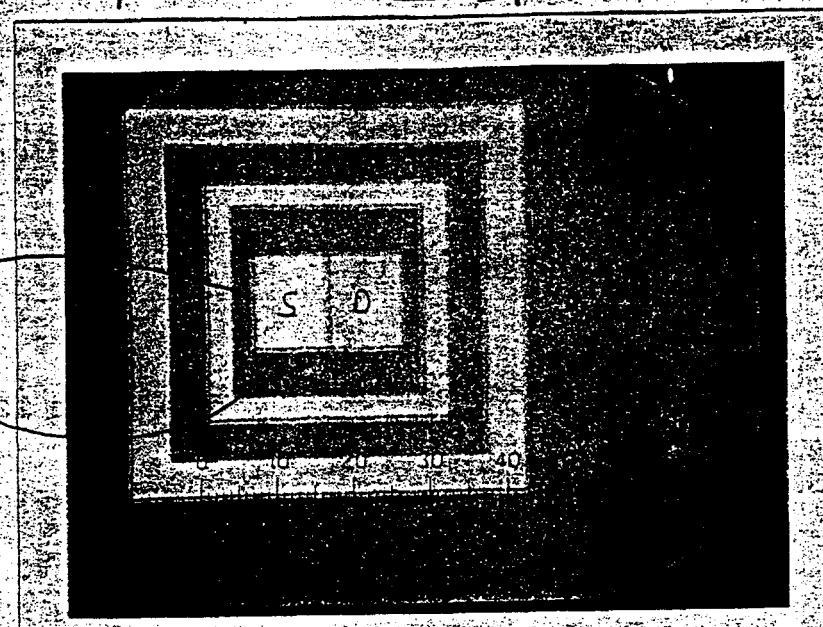

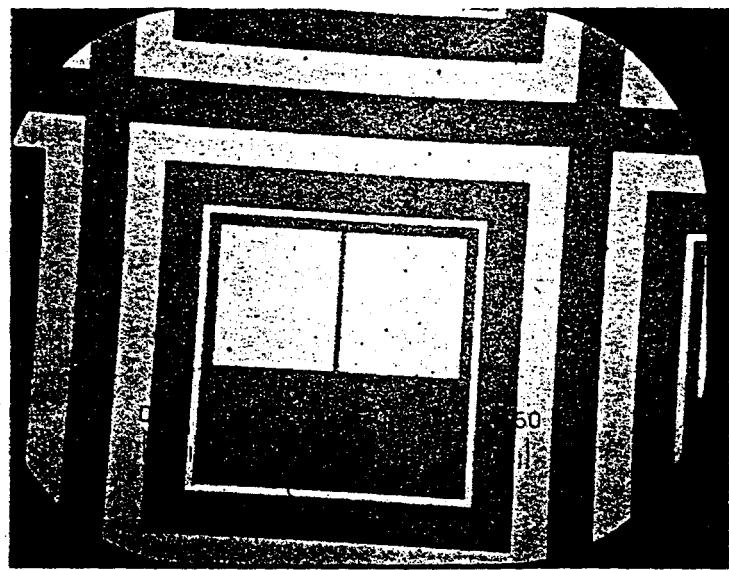

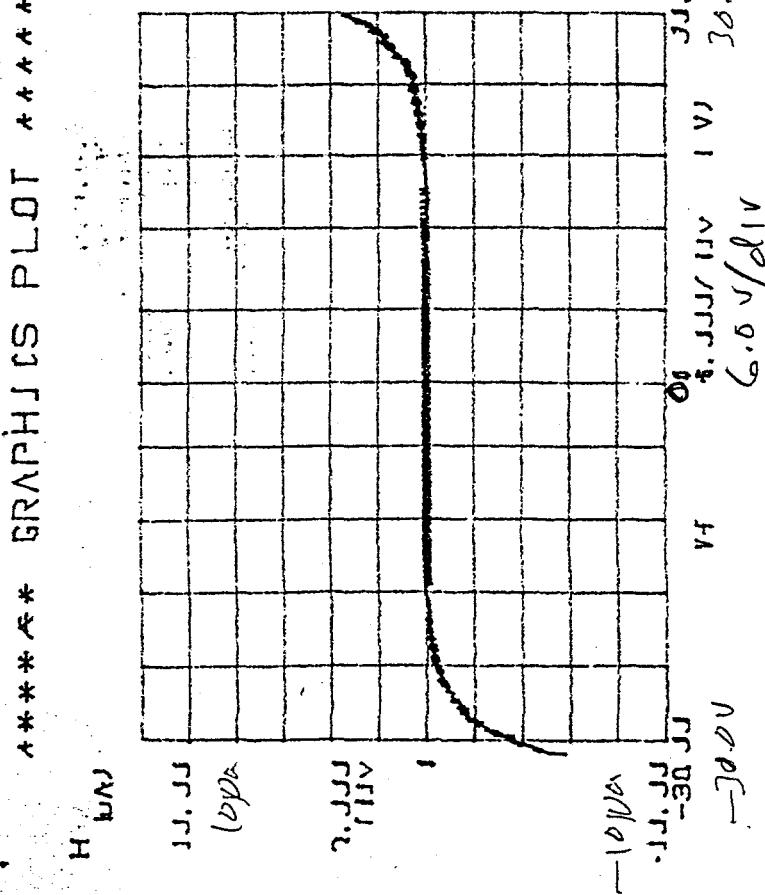

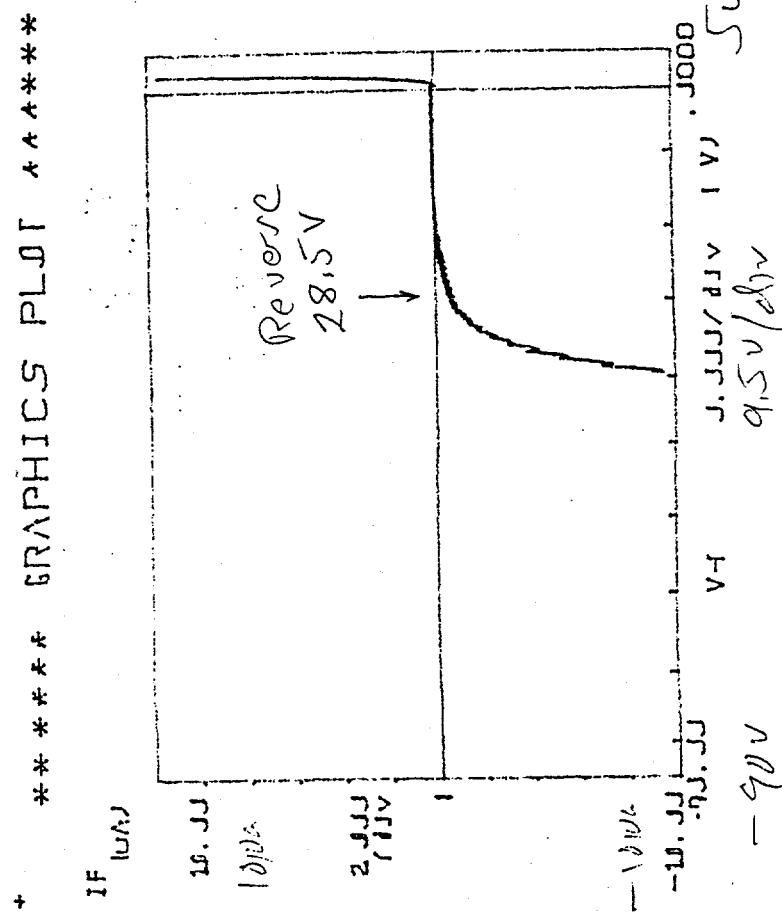

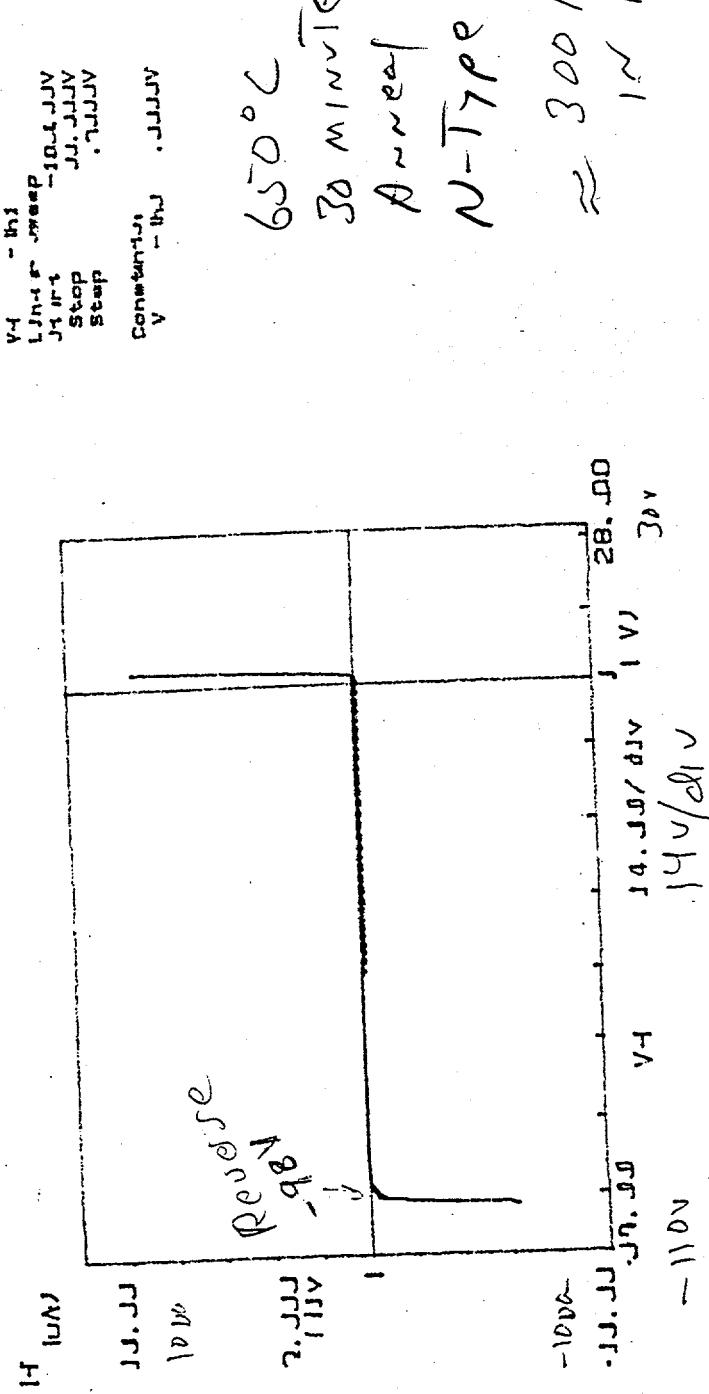

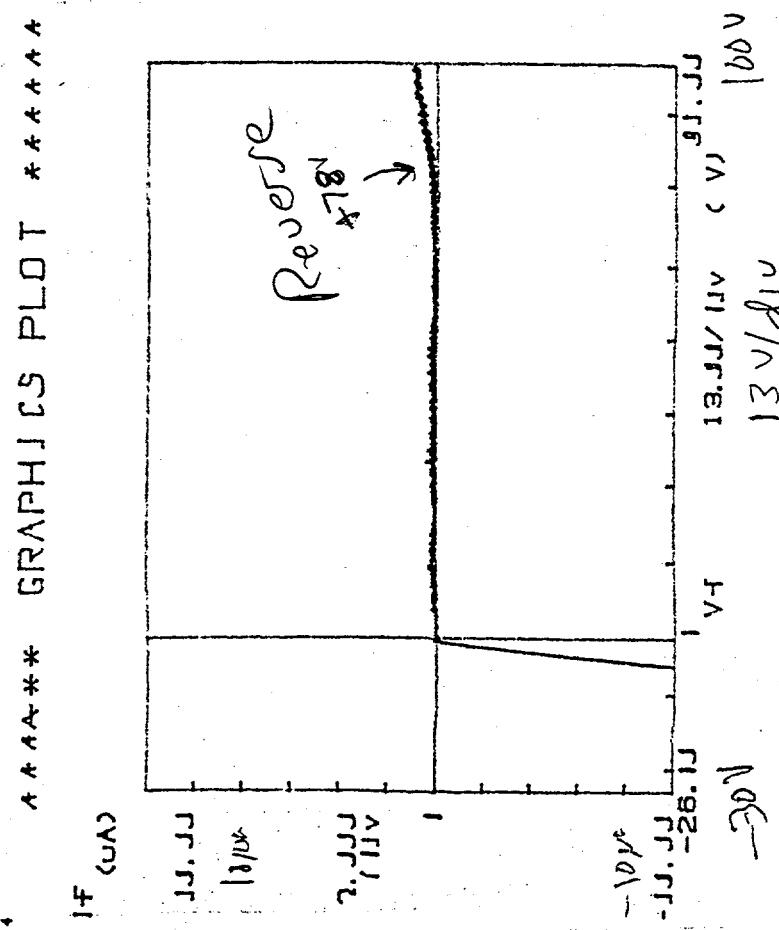

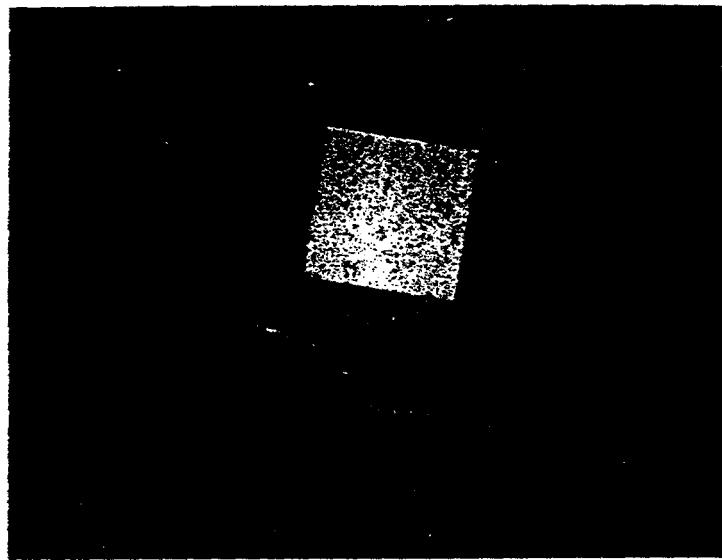

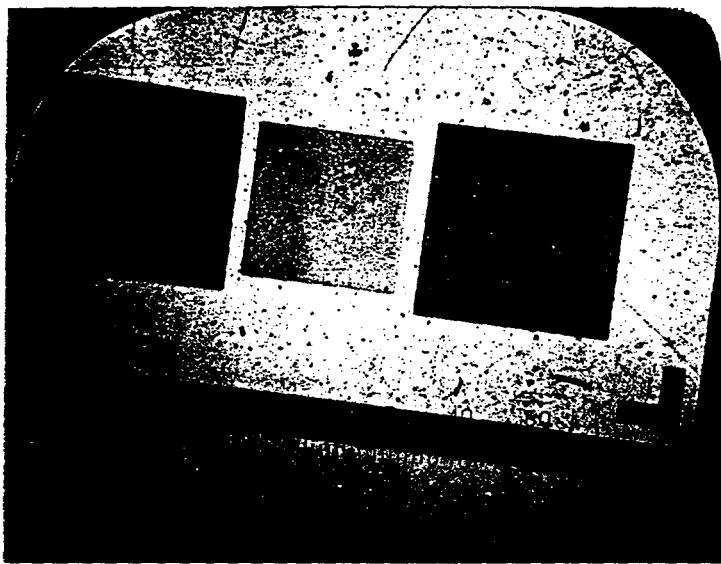

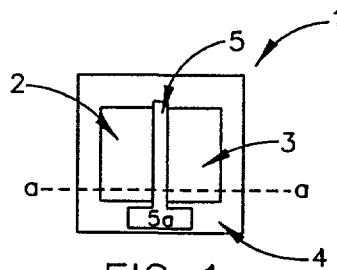

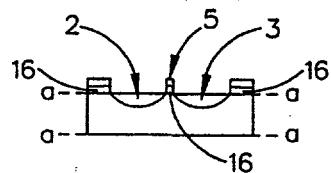

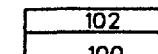

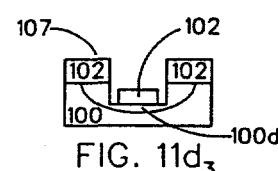

The first Figures show Schottky barrier Junction Current vs. Applied Voltage. Fig. 1 shows said Curves for a P-Type Silicon Substrate and Fig. 2 for an N-Type Silicon Substrate upon which was deposited Chromium. Both Plots are for Schottky barrier Junctions formed by a fifteen minute 350 Degree Centigrade Vacuum Anneal. (Note, the polarities are not opposite on the Fig. 1 and 2 Plots as the monitoring probes were switched around when measuring the Device Curves. I changed this practice after initial efforts. Figs. 3 and 4 show Reverse Breakdown for N-Type and P-Type Silicon Schottky barrier Junctions formed by a 30 minute 450 Degree Centigrade Anneal. Figs. 5 and 6 show Reverse Breakdown for P-Type and n-Type Silicon Schottky Barrier Junctions formed by a 30 minute 650 Degree Centigrade Anneal. Note the Reverse Breakdown Voltage is greatly increased over that shown in Figs. 3 and 4. Fig. 8 shows an Optical Microscope Photograph of a Schottky Barrier MOSFET formed by the present invention procedure. The two Light Square Regions are the Source and Drain, with the thin Dark Region inbetween being the Gate. Fig. 7 shows typical back to back Schottky Barrier Reverse Breakdown Characteristics for Junctions formed by a 400 Degree Centigrade Anneal. Note the Reverse Breakdown is between approximately 15 and 30 Volts. This was a commonly achieved result. Figs. 9 and 10 show the Original N-Channel and P-Channel Curves I achieved on April 27 and 28th, 1994 as described in the Historical Accounting Section of this Report, infra. Note that the N-Channel Curves show Forward biased Junction Currents starting at 0, 2 4 Volts Drain to Source, when the Applied Gate Voltage was approximately 0, 2 and 4 Volts respectively. This is as thought to be explained by Cases 2a and 2b in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra. Figs. 11 and 12 are interesting Plots which were rarely achieved. Obviously they are for P-Channel Devices, formed on N-Type

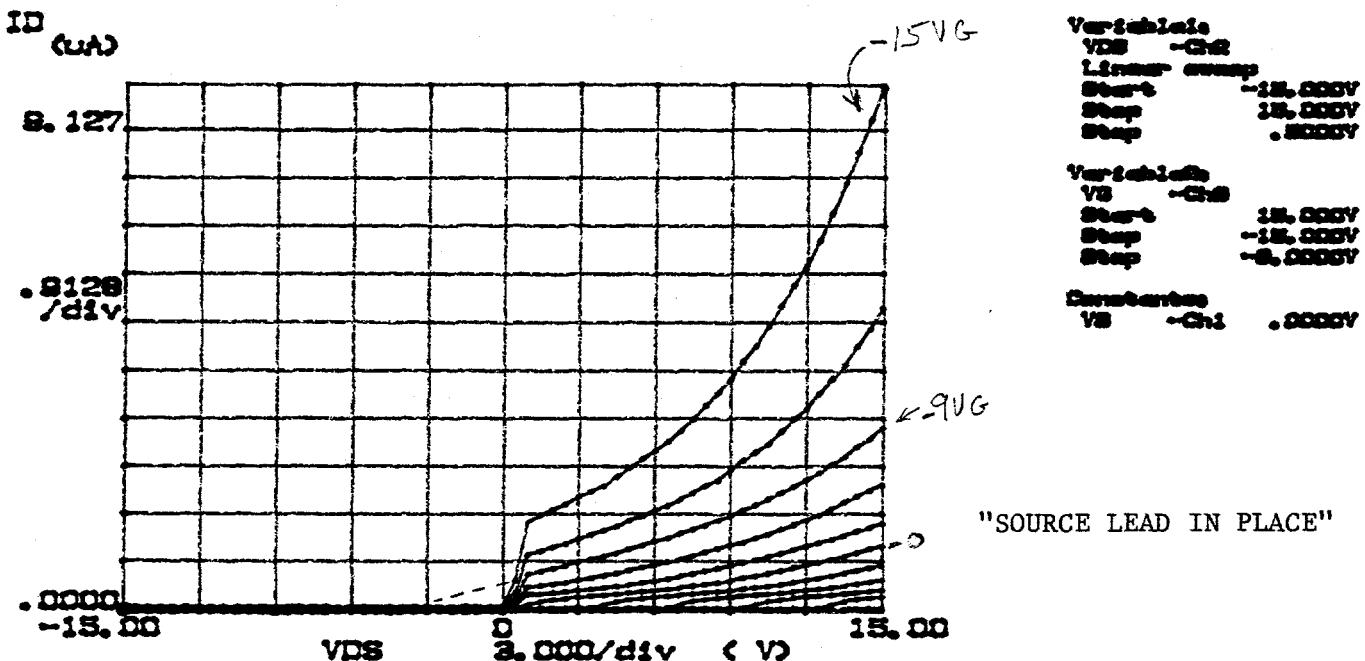

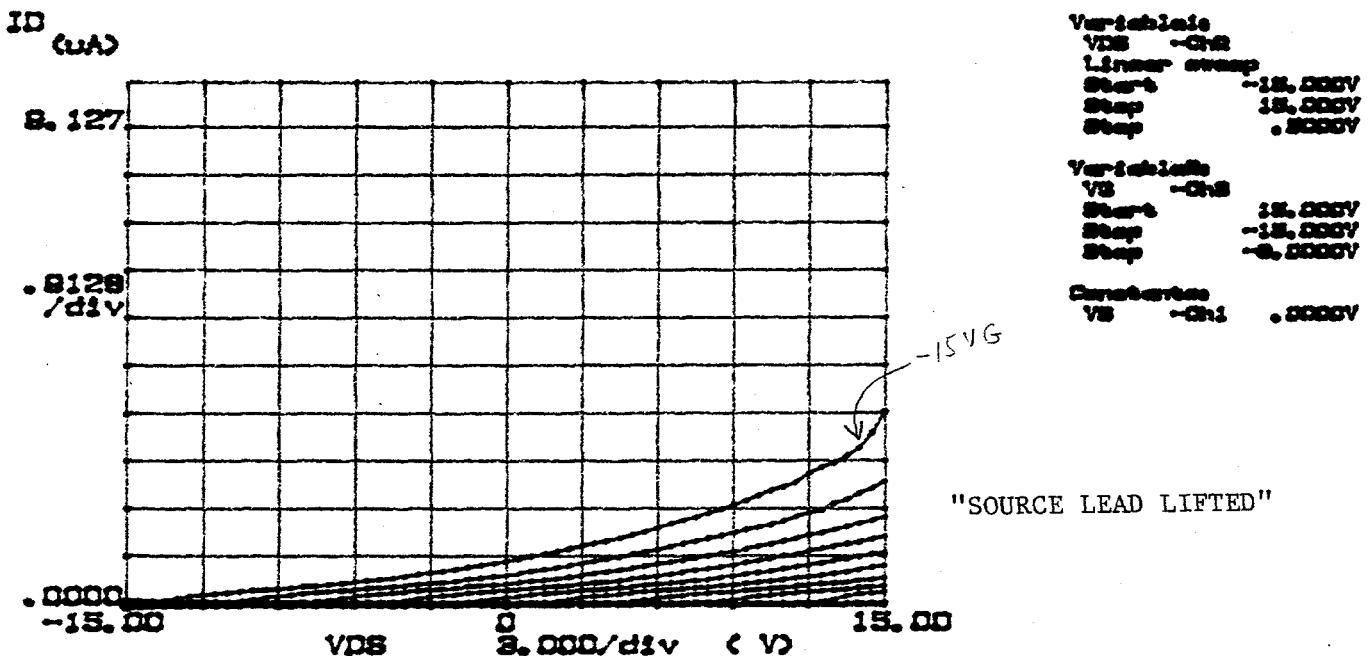

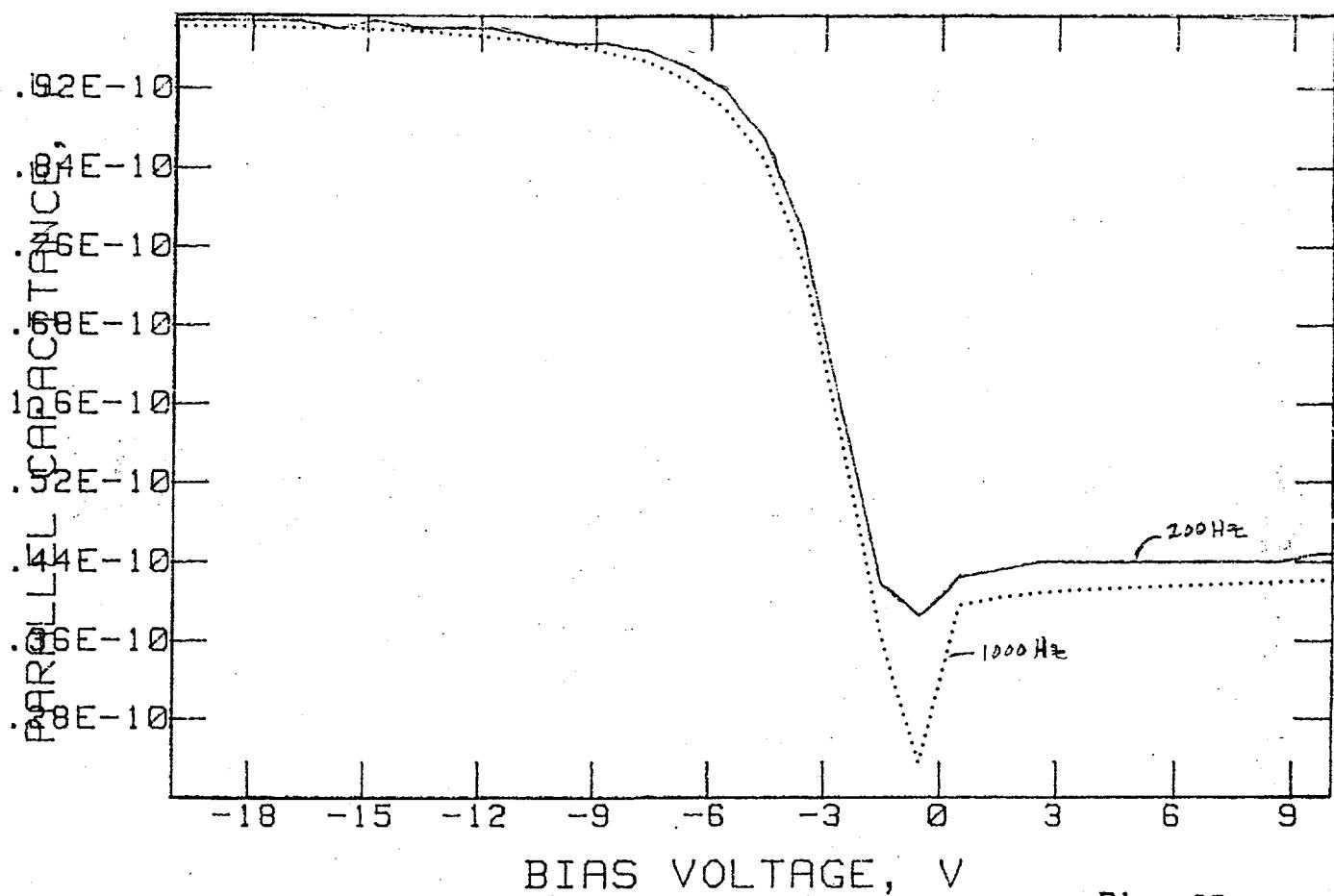

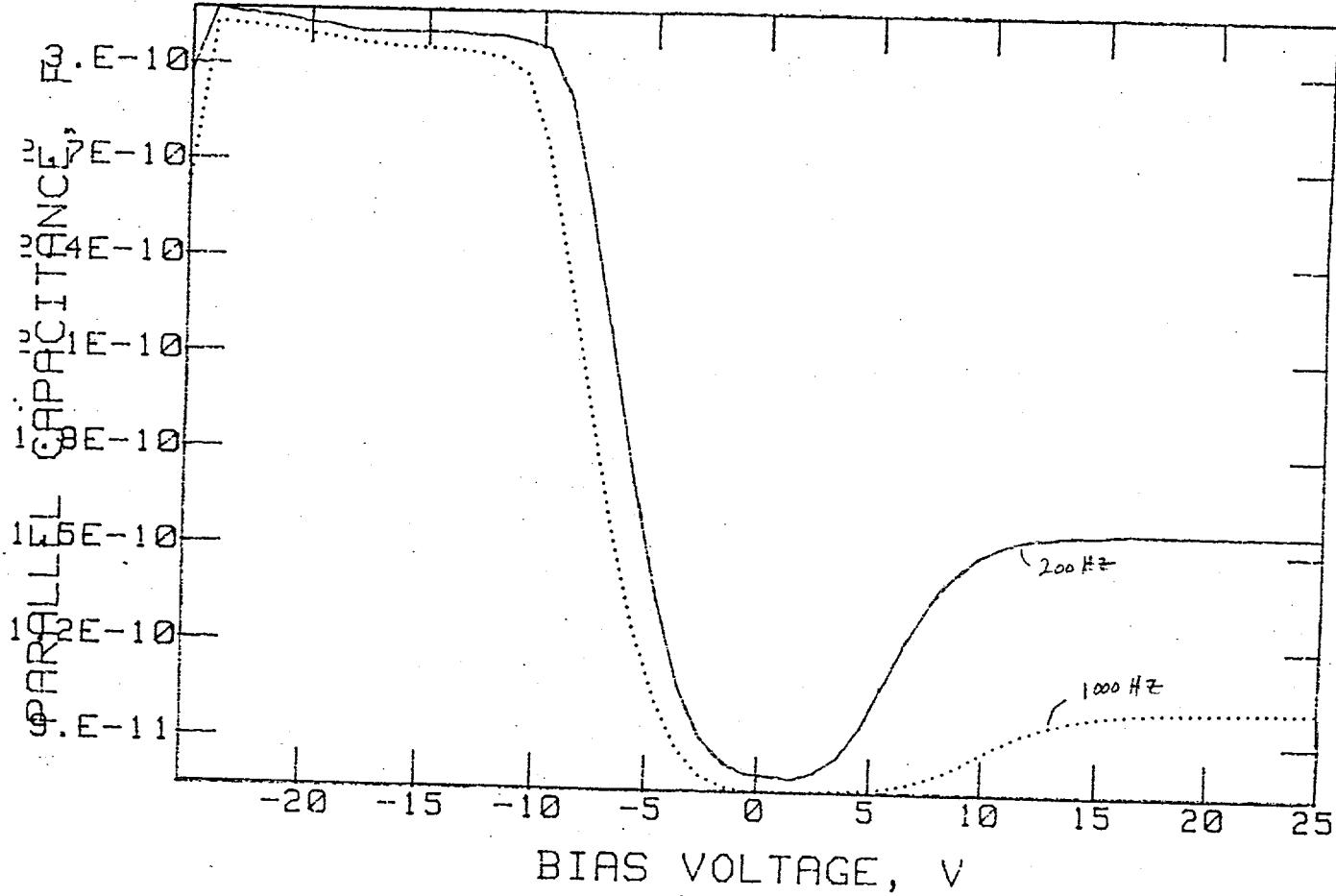

Silicon as the Curves are in the First Quadrant. These Figures seem to show definite transition from the Forward Bias Current Flow through the Drain Junction at Zero and Negative Applied Gate Voltages, to Saturation Current Characteristics at Positive Applied Gate Voltages. The Forward Bias Drain Junction Curves seem to begin at a bit low Drain to Source Voltage in Fig 12, but the general nature of the Curves in both Figs 11 and 12 is thought to be explained by Cases 2a and 2b in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra, (Note said Sections 2a and 2b were written with respect to an N-Channel Device, so the Polarities in Figs. 11 and 12 are opposite to those discussed in said Sections 2a and 2b). Figs. 13 through 17 show Drain Current vs. Drain to Source Voltage for an N-Channel Device formed on P-Type Silicon. The Drain Voltge was swept from -5 to +5 Volts, and the Gate Voltage stepped from -10 Volts to + 18 Volts. Progressively lower Current Scales are applied to the same set of Curves. Again, note that for Gate Voltages of, in this case, Below 0 Volts, we see Drain Current flow as it would through a Forward Biased Drain Junction from the Gate, (eg. at Negative 2 Volts Applied to the Gate we see Drain Current begin at approximately Negative 2 Volts Applied to the Drain). At Positive Applied Gate Volts we see Saturation Drain Current Curves. Note in particular that at a Positive 4 Gate Volts the Current flow when a Positive 5 Volts is applied to the Drain, is approximately  $8 \times 10^{-9}$  Amps, but that when a Positive 4 Gate Volts is applied with a Positive 5 Drain Volts present the Drain Current flow is approximately  $4 \times 10^{-7}$  Amps, which is two orders of magnitude higher. This shows that the Inversion Channel is much more effected by Gate Voltage than is an Accumulated Channel. It is thought this is the result of a basic difference between Metalurgical and Field Induced Junctions as discussed in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra. Figs. 18 through 20 show a similar sequence of Plots, for a P-Channel Device formed on N-Type Silicon. Figs. 21 through 24 show a sequence with the same set of Drain Current Curves obtained from another N-Channel Device, plotted with progressively lower Current Scales. Figs. 22, (and 27), show the Case 1b, (in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra), effect of a trend toward a Reverse Drain Junction Breakdown as the difference between applied Drain Volts and Gate Volts increases. Figs. 25 and 26 show Curves for yet another P-Channel Device. Fig. 26 is plotted on a lower Current Scale, but the Curves are the same as in Fig. 25. Figs. 27 through 32 show additional Drain Current Curves obtained from yet other Fabricated Devices. Note that the P and N-Channel Devices represented by Figs. 29 and 30 respectively are fairly balanced and would probably make a good CMOS pair, were it possible to simultaneously identify, probe and interconnect them. Figs. 33 and 34 show Drain Current Curves obtained from P-Channel and N-Channel Devices which had no Gate Metal present. The Gate Probe was set atop the Oxide and acted as a Gate Metal. The Device which provided the Curves in Fig. 30 had the Silicon

etched approximately 2 microns. Both Figs. 33 and 34 show Drain Current Curves starting from a "Common Point" along the Drain to Source abscissa, but that "Common Point is offset from the Zero Drain to Source Voltage Point. This is thought to be explained by Case 2c in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra, which discusses loss of "Pinch-Off" in an Inverted Channel Region, combined with Oxide Breakdown and accompanying Current flow therethrough. Figs. 35 and 36 show P-Channel device Curves obtained with and without the Source Lead in place, respectively. Note that with the Source lead in place, (Fig. 35 Curves), we find Saturation MOSFET-like Drain Current Curves starting from a "Common Point". Again, Case 2c in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra, discusses why Drain Current Curves are thought to occur. With the Source lead lifted, Fig. 36 shows that a family of Drain Current Curves form, each of which initially appears as a Forward Bias Current flow through a Diode and the Silicon Dioxide. Note that each "Source lifted" Drain Current Curve starts at a point on the Drain Voltage Sweep where the Drain Junction would become Forward Biased, just overcomming a Reverse Bias set by the Applied Gate Voltage. As the difference between Gate and Drain Voltages increases, however, it can occur that the Silicon will invert and the Drain Current Curves will become Reverse Bias Tunneling in nature. Finally, Figs. 37 through 39 show MOS Capacitor Curves. These are included to show that we indeed do Invert silicon by applying Gate Voltage across leaky Oxide.

Another observation is that many of the Saturation Drain Current Curves seem to begin with an almost Forward Biased Diode Form, which then merges into a Saturation Current. It is felt, in view of the Case 2c explanation in the Analysis of Schottky Barrier MOSFETS Section of this Report, infra, that this should be expected where Positive Gate and Negative Drain Voltages are applied, and Drain Current initially flows through the Gate Oxide and a Forward Biased Drain Junction via a Non-Inverted Channel Region, (Figs. 28 & 31 are an exception to this as said Curves appear very MOSFET-like). When the Channel Inverts, the Drain Current Curves change to demonstrate Saturation Characteristics.

Let me add that I think the Gate Voltage supply continuously causes Minority Carrier production through "Avalanche" at the Source Junction, which Minority Carriers form an Inversion Channel Region, which Inversion Channel Region Minority Carriers then serve as the Carriers in Drain to Source Current Flow, under the driving influence of applied Drain to Source voltage. If that is the case one would then expect that limiting the Gate Current Flow to zero (0.0) Amps, would prevent formation of an Inverted Channel Region, and that no MOSFET Drain Current Curves would be effected. Indeed, it was observed that when the Gate Current Flow was limited to zero (0.0) Amps by a "Test Set Compliance" Setting, sweeping the Drain to Source Voltage from Negative to Positive caused no Drain Current to flow, regardless of applied Gate Voltage level. If, however, as little as one-hundred-nano-amps was allowed to flow in the Gate Circuit, in some cases some Drain Current Flow was effected by application of Gate Volts. I think what is occurring is that the Gate Circuit

feeds Source Junction located Gate Voltage controlled Avalanche Minority Carrier production, and the Gate Voltage Supply must be capable of supplying Minority Carriers thereto, for the devices to work. At the outset of the application of Channel Inverting Polarity Voltage to a Device Gate, I think current can flow from the Gate Voltage Supply through the leaky Silicon Dioxide through a Forward Biased Drain Junction and Drain Current can also flow at zero (0.0) applied Gate Volts when Drain Volts are applied. Once Channel Inversion occurs, however, major Gate Voltage Supply-Silicon Dioxide Current Flow ends, as the Gate Voltage Supply then sees a Reverse Biased Drain, (and Source) Junction. Channel Region Inverting Avalanche Minority Carrier production at the Source Junction continues, under the control of the Applied Gate Voltage, and said Minority Carriers are caused to mediate a Drain Current Flow under the influence of applied Drain to Source Voltage. Some Minority Carriers are still lost through the leaky Oxide though, hence the requirement for Gate Current remains.

As stated elsewhere in this Report, we have shown feasibility, but not consistency and repeatability in the work completed. However, hopefully without sounding self serving, let me say that the results achieved, though not perfect, are acutally pretty good in view of how Research often goes, (and without much focused effort would have so gone in the present scenario)\*\*. The results we have achieved are very definitely encouraging. Additional Research funding is definitely justified. The N and P-Channel MOSFETS results should be "Polished" and basic research investigation should be conducted regarding the Single Device Equivalents to CMOS.

---

\*\* For instance, at the outset serious questions existed as to the ability of Chromium to form Rectifying Junctions with both N and P-Type Silicon, when the Chromium is deposited as a thin film and then annealed thereto, and we did not know if a common Anneal Temperature would work for both Silicon Types if the Rectifying Junctions could be so formed. We had, and still have, no reference which teaches the result we achieved. Some references hint that such might occur, (said references provided the insight to initiate the present work), but none directly state that the result does occur. It was a relief when, the first time I tried it, I obtained positive results. We have since found that either Electron beam or Sputtering System can be used to deposit Chromium Thin Films and allow achieving Rectifying Junctions by way of an Anneal at approximately four-Hundred degrees Centigrade.

There was also, at the outset, question as to whether sufficient minority carriers would even be available to form an inverted channel region in both N and P-type Silicon. This point was a serious point of concern in the Second Round NIST Evaluation Report.

Another serious point of concern was whether when the Chromium formed Rectifying Junctions with N and P-Type Silicon,

the Junctions would be of sufficient quality to act as Rectifying Junctions in a MOSFET on both N and P-Type Silicon. That is, would their Reverse Breakdown be sufficiently high on both N and P-Type Silicon. In the same area of concern was the question as to whether when the Junction forming Anneal was carried out the resulting change in Silicon topology would be such to preclude self-delineation of devices. That is, would formed Chromium Disilicide cause an expansion of Silicon in the Source and Drain Regions such that a reasonable Oxide depth would be passed, thereby effecting a hopelessly shorted Source, Gate and Drain. As well, at the outset we had no idea how deep a layer of Chromium would have to be deposited to form usable Rectifying Junctions at a reasonable Anneal Temperature. We now know that the layer can be very thin indeed, (eg. 800 Angstroms), and the Silicide forming Anneal does not cause a Device prohibiting expansion of the Silicon.

In addition, had we, (Professor Ianno and I), not brainstormed and Conceived the added Aluminum Deposition Step to the Original Fabrication Procedure to provide a Gate Metal, when we could not make the initial Procedure work, we would probably never have achieved any Results Consistency with the equipment available to us. And even regarding the Aluminum Deposition, we have, at times, had problems making it succeed. That is, when Aluminum is deposited in the Electron-beam Evaporator, rather than the Sputtering System, and not Annealed, we have seen instances where it does not adhere well. We think that the Sputtering System works better because it doesn't heat the Substrate during a Deposition Process, by Radiation.

We have also found that in some fabrication processes, even though all indications were that we had etched through the Oxide in the Source and Drain Regions, prior to depositing Chromium, we actually had not done so. This means that an Anneal will not form any Chromium Disilicide, hence, Rectifying Source and Drain Junctions, as it is not in contact with the Silicon thereduring. This was discovered when we achieved a particularly low yield of working devices on some processed substrates, but after we had found Operating Curves in prior Devices, (eg. The April 27, 1994 breakthrough). If that problem had occurred early on we would have never known we should be achieving working devices at all, and eventually probably would have concluded that the entire idea was unworkable.

On a completely different note, the Test Set Faulty Interface Adaptor problem I ran into, which is recited in the Historical Accounting Of the Supported Efforts Section of this Report, infra, could have prevented us from knowing that we had achieved any results at all, even though we had.

In view of all the variables that had to "self-align" for me at appropriate times, to find the initial Results I did, it was almost a Mirical that I ever found any results at all. The truth in that statement can not be over emphasised! However, I put forth the effort, had excellent fabrication support from Professor Ianno and others at UNL, and most importantly-----

Luck was with me when I needed it!

## ADDENDUM

After a lot of analysis assuming we have an Inverted Channel Region Scenario, (see infra), it has occurred to me, and I must point out, that there is a way that a family of Drain Current Curves could be achieved without the requirement that MOSFET Channel Inversion occur, if the Silicon Dioxide is leaky. I believe, however, that this case is most likely in Devices in which Drain Current Flow begins offset from the Drain to Source Voltage Zero (0.0) Volts point on a Drain Current vs. Drain to Source Voltage Curves abscissa in a direction representing a Forward Biased Source Junction is effected by Current Flow through Silicon Dioxide by application of Gate Voltage prior to application of Drain Voltage. As is discussed supra herein, this, and a Depleted Channel Region Resistance increase effect are the only causes I see for two-slope "Saturation-type" Drain Curves to develop in a Non-Inverted Channel Scenario.

Proceeding, say we have an N-Channel Device formed on P-Type Silicon, and that it has leaky Silicon Dioxide. When in a test circuit, we will have a Gate Voltage Source looking through said leaky Silicon Dioxide into two Rectifying Junctions, (Source and Drain), the opposite side of which Source is connected to Common, and the opposite side of which Drain is connected to Common through a Drain Voltage Source. Let us look at various Gate and Drain Bias Voltage States again:

If a Negative Gate and Drain Voltages are applied we should expect to see Drain Current flow through the Silicon Dioxide beginning where the Drain Voltage is more negative than the Gate Voltage, thereby Forward Biasing the Drain Junction, just as we do see. This case is no different than that we have analyzed before.

If we apply Negative Gate Voltage and Positive Drain Voltage, both Source and Drain Junctions will be Reverse Biased, as viewed from the Gate Voltage Source. We should expect to see no Drain Current flow, (unless the Drain Junction Breaks down in Reverse Bias), as the Drain Junction will be Reverse Biased looking at it from the Drain Voltage Source. Again this is not different than previously analyzed.

Now, if we apply Positive Gate Voltage and Negative Drain Voltage, (where we see Drain Current Curves), prior to Channel Inversion, we could see Current flow from the Gate Voltage Supply through the Silicon Dioxide and Channel Regions into and through Forward Biased Source and Drain Junctions to Common, with the Current flow through the Forward Biased Drain Junction also flowing through a Drain Voltage Supply. However, the Forward

Biased Source Junction will greatly limit the amount of voltage presented to the Drain Junction in the Channel Region, (which Source Junction appears Reverse Biased to Sufficient Drain Voltage Source, said Drain Voltage being of an opposite Polarity to the Gate Voltage). That is, the Drain Circuit will be comprised of the Drain Voltage Source in series with the Forward Biased Drain Junction, (again assuming the Channel is not inverted), the Channel Region side of which Forward Biased Drain Junction is generally at a Voltage level set by voltage division of the applied Gate Voltage, said applied Channel Region Voltage resulting from a Voltage Division being between the resistance of the Forward Biased Drain Junction plus some Channel Region Resistance, and the Gate Silicon Dioxide Resistance plus some Channel Region Resistance. With Zero (0.0) Drain Voltage applied, however, the Voltage atop the Source Junction in the Channel Region will be at a Forward Biased drop across said Source Junction, perhaps in series with some Voltage drop effected by said Current flowing through the Silicon Dioxide as it flows through some Channel Region Resistance adjacent to said Source Junction. Now, as the applied Gate Voltage is increased, the Positive Voltage appearing atop the Source Junction in the Channel Region can increase by drop across the Channel Resistance between the Silicon Dioxide and the Source Junction. This could lead to increased Drain Current Flow, through the Gate Voltage Source, for a certain applied Drain Voltage as said Voltage is of an opposite Polarity to that applied to Non-Channel side of the Drain Junction. Thus a series of Drain Current Curves could develop as the Gate Voltage is increased. Said Drain Current flowing through the Gate Circuit. However, the "Origin" of said Drain Current Curves will not be a specific "Common Point", emphasis added. The Origin of the Drain Current Curves would shift to a more Positive point as the applied Gate Voltage is made more Positive. The shift will not be a drastic as is the case where the Source is lifted from the Common and the entire applied Gate Voltage appears at the top of the Source Junction, but will be reduced by the effect of the Voltage Division between the Silicon Dioxide, and the Channel Resistance and the Source Junction. (Note that if the Source is lifted from "Common" Forward Bias Drain Current Flow begins at the point where the Drain Voltage Source goes Positive with respect to the Gate Voltage Source, see Figs. 35 & 36). Now, while a Non-Inverted Channel Region family of Drain Current Curves could develop, it is difficult to see how they could occur where the Drain Current Curves all start at a true "Common Point" of zero (0.0) Volts, or thereabouts. That is, where the Source Junction voltage in the Channel does not change significantly with applied Gate Voltage as a result of the above described Voltage Division involving Channel Resistance atop the Source Junction, thereby causing the Drain Current initiation point to move Positive, there is not any added "Driving Force", (ie. increased Channel Region Voltage above the Source Junction as a function of applied Gate Voltage), to effect a Family of Drain Current Curves. If the Channel

Region Voltage above the Source Junction remains essentially the same for any applied Gate Voltage, then sweeping Drain Voltages will cause the same Drain Currents to flow regardless of applied Gate Voltage.