# Project Final Report

## 100kW Energy Transfer Multiplexer Power Converter Prototype Development Project

**DE-FG36-03GO13138**

Submitted by:

Spellman High Voltage Electronics Corporation

475 Wireless Boulevard

Hauppauge, New York 11788 USA

Prepared by:

**dtm Associates**

93 Highland Street

Clinton, Massachusetts 01510 USA

**March 21, 2006**

DOE Contact Person - Keith Bennett

Dept of Energy Golden Field Office

(303) 275-4905

475 Wireless Boulevard • Hauppauge New York 11788. USA • [www.spellmanhv.com](http://www.spellmanhv.com) • T:+1 631.630.3000• F:+1 631.435.1620

USA

EUROPE

JAPAN

MEXICO

## Dedication

This Final Project Report, as well as the entire ETM Converter Project, is dedicated to two men whose vision and drive were responsible for its existence: S. Merrill Skeist (1918-2005), who was the CEO of Spellman High Voltage Electronics Corporation; and Richard H. (Dick) Baker (1928-2006), who was a self-employed Consultant and President of The Baker Company. Both men enjoyed long, active and creative careers in the electronics industry.

At a time in their lives when most of their contemporaries were content primarily with relaxation and pursuits of fancy, these two technical giants among men were constantly seeking the methods and means for the improvement of electronic circuits and system, particularly in the area of power electronics. Their shared interests and technical foresight gave birth to the ETM Converter Topology, among many others. They recognized the benefits that such technology could provide to the renewable energy field, and they were powerful advocates for the adoption of the ETM technology by the Department of Energy and the renewable energy industry. They sought to leave a legacy of high-performance, cost-effective renewable energy conversion to their country and to their society.

We are all collectively better off for having had Merrill and Dick in our midst as colleagues, friends and teachers, and hopefully future generations will be similarly inspired by their ground-breaking spirit and their manifold accomplishments.

## Table of Contents

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| <b>A.) ETM Converter Test Setup.....</b>                                | <b>6</b>  |

| i.) ETM Control Board Debug Test Setup .....                            | 6         |

| ii.) 34kW Prototype ETM Converter Test Setup .....                      | 13        |

| iii.) Test Equipment Used .....                                         | 17        |

| <b>B.) ETM Converter Host GUI Interface Description .....</b>           | <b>20</b> |

| i.) ETM GUI Parameter Discussion.....                                   | 21        |

| ii.) Planned Enhancements to the ETM Converter Host GUI Interface ..... | 26        |

| <b>C.) Summary of Test/Debug Activities.....</b>                        | <b>27</b> |

| i.) Initial Power-Up/Debug Testing (9/1/04 to 10/21/04) .....           | 30        |

| ii.) Performance Testing (12/23/04 to 3/10/05) .....                    | 37        |

| <b>D.) ETM Prototype Test Data Summary.....</b>                         | <b>44</b> |

| i.) IOSF Versus Phase Current Magnitude .....                           | 44        |

| ii.) IOSF Versus Total Output Power .....                               | 47        |

| iii.) IOSF Versus Phase Output Power Factor .....                       | 48        |

| vi.) Tcyc Versus Total Output Power .....                               | 52        |

| vii.) Performance Test Data Set Point #1.....                           | 53        |

| <b>E.) Summary of IGBT Failures Encountered .....</b>                   | <b>57</b> |

| i.) The IGBTs Used and Their Ratings .....                              | 57        |

| ii.) The First IGBT Failure Encountered.....                            | 59        |

| iii.) The Second IGBT Failure .....                                     | 60        |

| iv.) The Third IGBT Failure .....                                       | 60        |

| v.) Fourth (Last) Failure Encountered .....                             | 61        |

| <b>F.) Remaining Tests To Be Performed.....</b>                         | <b>63</b> |

| i.) Test Progress Summary .....                                         | 63        |

| <b>G.) Present Condition of the ETM Converter Prototype.....</b>        | <b>65</b> |

| i.) ETM Prototype Present Condition .....                               | 65        |

| ii.) Hardware Changes and Revisions .....                               | 66        |

| iii.) Software Changes and Revisions .....                              | 67        |

| iv.) The Future of the ETM Converter.....                               | 69        |

| <b>Supplemental Documents.....</b>                                      | <b>71</b> |

## List of Figures

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| Figure A1. <i>ETM Control Board Debug/Programming Test Setup.</i> .....                   | 7  |

| Figure A2. <i>ETM Control Board Debug/Programming Configuration.</i> .....                | 8  |

| Figure A3. <i>ETM Control Board Debug/Programming Configuration.</i> .....                | 8  |

| Figure A4. <i>Low Power ETM Power Train Board w/ETM Control Board.</i> .....              | 9  |

| Figure A5. <i>Test Setup Auxiliary Power Supply.</i> .....                                | 9  |

| Figure A6. <i>ETM Firmware Debug Benchtop Test Setup.</i> .....                           | 10 |

| Figure A7. <i>ETM Firmware Debug Benchtop Test Setup.</i> .....                           | 10 |

| Figure A8. <i>ETM Firmware Debug Support Test Equipment.</i> .....                        | 11 |

| Figure A9. <i>ETM Firmware Debug Test Support Computers.</i> .....                        | 11 |

| Figure A10. <i>ETM Firmware Debug Test In-Progress.</i> .....                             | 12 |

| Figure A11. <i>34kW Prototype ETM Converter Test Setup.</i> .....                         | 13 |

| Figure A12. <i>34kW Prototype ETM Converter GUI Control Interface.</i> .....              | 14 |

| Figure A13. <i>34 kW ETM Converter Prototype Test Setup.</i> .....                        | 15 |

| Figure A14. <i>34 kW ETM Converter Prototype Test Support Equipment.</i> .....            | 15 |

| Figure A15. <i>34 kW ETM Converter Prototype Test Laptop PC Controller.</i> .....         | 16 |

| Figure A16. <i>Three Phase 40kVA Input and Output Variacs.</i> .....                      | 16 |

| Figure A17. <i>34kW ETM Converter Prototype During Performance Test.</i> .....            | 17 |

| Figure A18. <i>Tektronix Model TDS5054B Oscilloscope.</i> .....                           | 18 |

| Figure A19. <i>Tektronix Model AM503 w/A6303 Current Probe.</i> .....                     | 18 |

| Figure A20. <i>Fluke Model 434 Three Phase Power Analyzer.</i> .....                      | 18 |

| Figure A21. <i>Fluke Model 87 Digital Multimeter.</i> .....                               | 19 |

| Figure A22. <i>Compaq Presario 3045US Laptop Computer.</i> .....                          | 19 |

| Figure A23. <i>Test Connections For The Fluke Model 434 Power Analyzer.</i> .....         | 19 |

| Figure B1. <i>ETM Converter Main GUI Control Interface.</i> .....                         | 21 |

| Figure B2. <i>ETM Converter Main GUI Control Interface Functional Descriptions.</i> ..... | 22 |

| Figure B3. <i>ETM Converter DACs Submenu.</i> .....                                       | 25 |

| Figure B4. <i>ETM Converter CommPort Properties Submenu.</i> .....                        | 26 |

| Figure B5. <i>Proposed Improved ETM Converter Host GUI, “Observation”.</i> .....          | 27 |

| Figure B6. <i>Proposed Improved ETM Converter Host GUI, “Generator”.</i> .....            | 28 |

| Figure B7. <i>Proposed Improved ETM Converter Host GUI, “Factory”.</i> .....              | 29 |

| Figure C1. <i>IRZC, IMAG_SIGN and Measured Resonant Current Waveforms.</i> .....          | 31 |

| Figure C2. <i>Nonlinear Resonant Current Pulse.</i> .....                                 | 34 |

| Figure C3. <i>Improved Resonant Inductor.</i> .....                                       | 34 |

| Figure C4. <i>Improved Resonant Inductor Installed In ETM Prototype.</i> .....            | 35 |

| Figure C5. <i>Increased ETM Power Train Resonant Capacitance.</i> .....                   | 36 |

| Figure C6. <i>Increased Resonant Capacitance In The ETM Converter Prototype.</i> .....    | 36 |

## List of Figures (continued)

|                                                                              |    |

|------------------------------------------------------------------------------|----|

| Figure C7. Resonant Signals VRC (green) and IRMAG_SIGN (yellow). ....        | 38 |

| Figure C8. Resonant Signals VRC (green) and IRMAG_SIGN (yellow). ....        | 38 |

| Figure C9. Resonant Signals VRC (green) and IRMAG_SIGN (yellow). ....        | 39 |

| Figure C10. Resonant Signals VRC (green) and IRMAG_SIGN (yellow). ....       | 39 |

| Figure C11. Resonant Signals VRC (green) and IRMAG_SIGN (yellow). ....       | 40 |

| Figure C12. Resonant Signals VRC (green) and IRMAG_SIGN (yellow). ....       | 40 |

| Figure C13. VRC_OV_N Signal Actuation Event. ....                            | 41 |

| Figure D1. IOSF VS Phase Current Magnitude (IOSF vs IO). ....                | 45 |

| Figure D2. IOSF VS Phase Current Magnitude (IOSF vs IO). ....                | 46 |

| Figure D3. IOSF VS Total Converter Output Power (IOSF vs PO). ....           | 47 |

| Figure D6. Tcyc VS Phase Output Power Factor (Tcyc vs PF). ....              | 51 |

| Figure D7. Tcyc VS Total Output Power (Tcyc vs PO). ....                     | 52 |

| Figure D8. Input Voltage VS Phase Output Current (Vin vs IO). ....           | 54 |

| Figure D9. Input Voltage VS Input and Output Power Factors (Vin vs PF). .... | 54 |

| Figure D10. Input Voltage VS Total Output Power, kVA (Vin vs PO). ....       | 55 |

| Figure D11. Input Voltage VS Total Output Power, kW (Vin vs PO). ....        | 55 |

| Figure E1. Dynex DIM200MBS12-A000 Functional Schematic. ....                 | 57 |

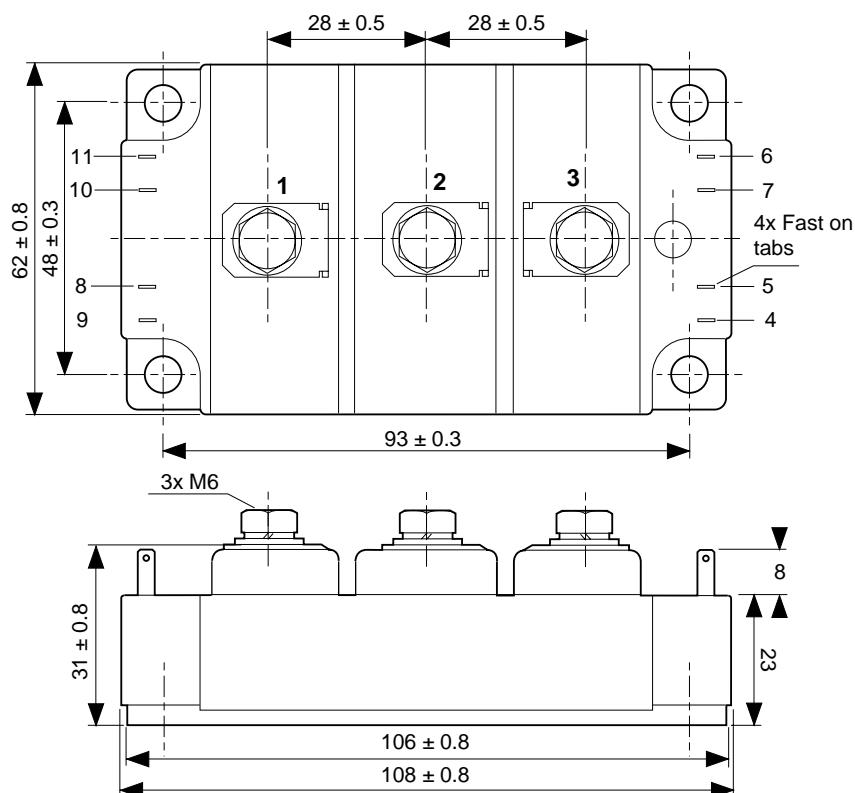

| Figure E2. Dynex DIM200MBS12-A000 Mechanical Dimensions and Pinout. ....     | 58 |

| Figure E3. DIM200MBS12-A000 IGBT With IGBT Driver Board. ....                | 58 |

## List of Tables

|                                                                  |    |

|------------------------------------------------------------------|----|

| Table D1. IOSF VS Phase Current Magnitude (IOSF vs IO). ....     | 44 |

| Table D2. IOSF VS Phase Current Magnitude (IOSF vs IO). ....     | 45 |

| Table D3. IOSF VS Phase Current Magnitude (IOSF vs IO). ....     | 47 |

| Table D6. Tcyc VS Phase Output Power Factor (Tcyc vs PF). ....   | 51 |

| Table D7. Tcyc VS Total Output Power (Tcyc vs PO). ....          | 52 |

| Table D8. ETM Converter Performance Set Point #1 Test Data. .... | 53 |

| Table F1. Revised Performance Test Matrix. ....                  | 64 |

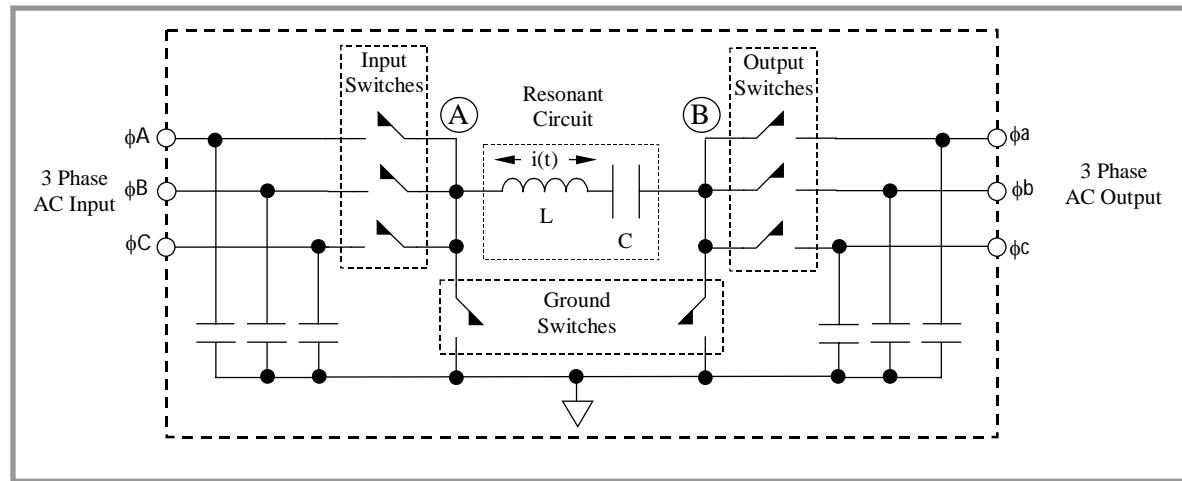

## A.) ETM Converter Test Setup

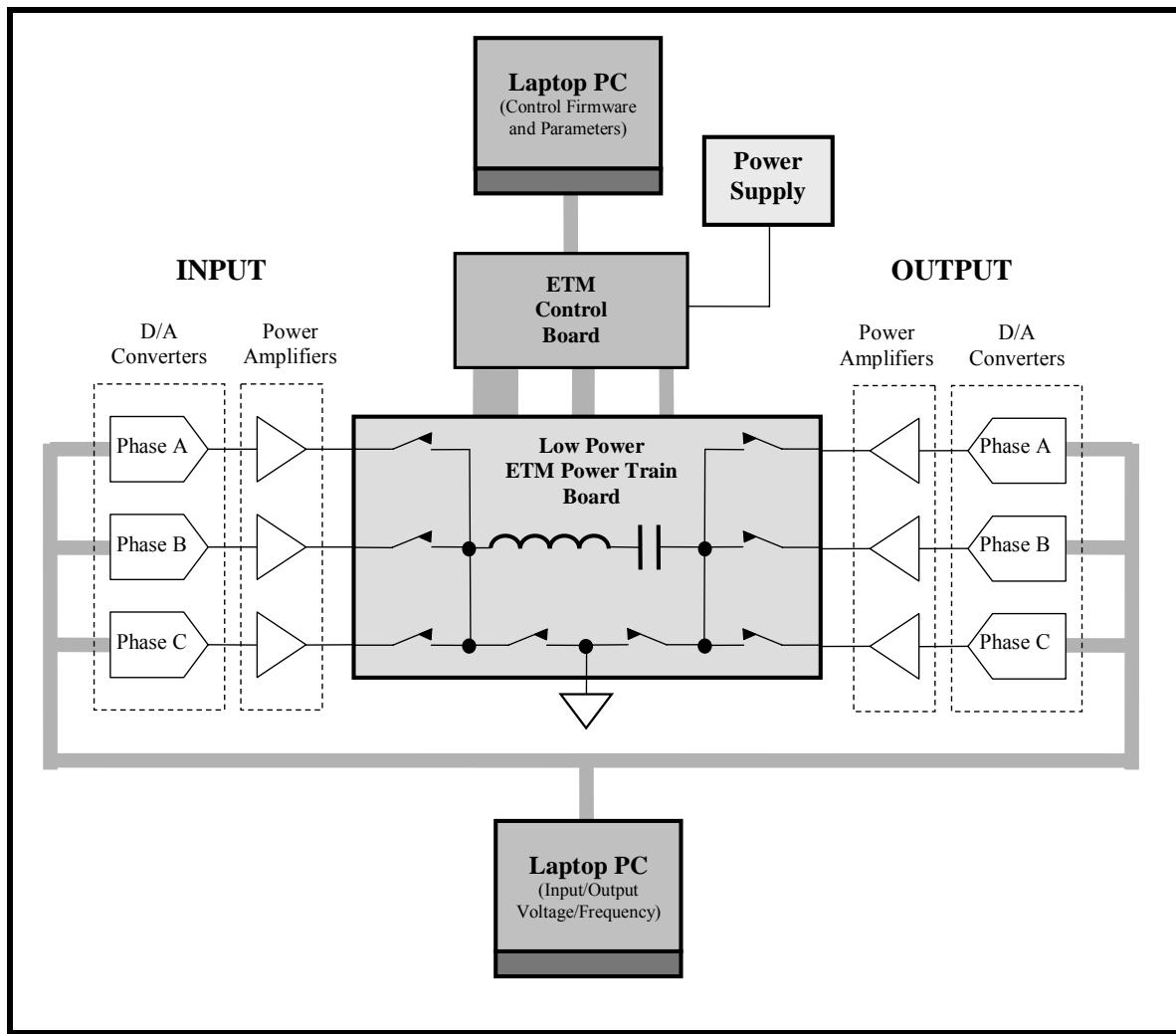

There were two setups used for the ETM Converter prototype. The first was a low power facsimile of the ETM converter power train for the debug and testing of the Control Board assembly. The second was the test lab setup used to observe the parametric and functional performance of the prototype ETM Converter. This two pronged test approach was used to decouple the programming and debug of the Control Board from the Power Train of the prototype so as to avoid damaging the expensive IGBTs and power resonant elements.

### i.) ETM Control Board Debug Test Setup

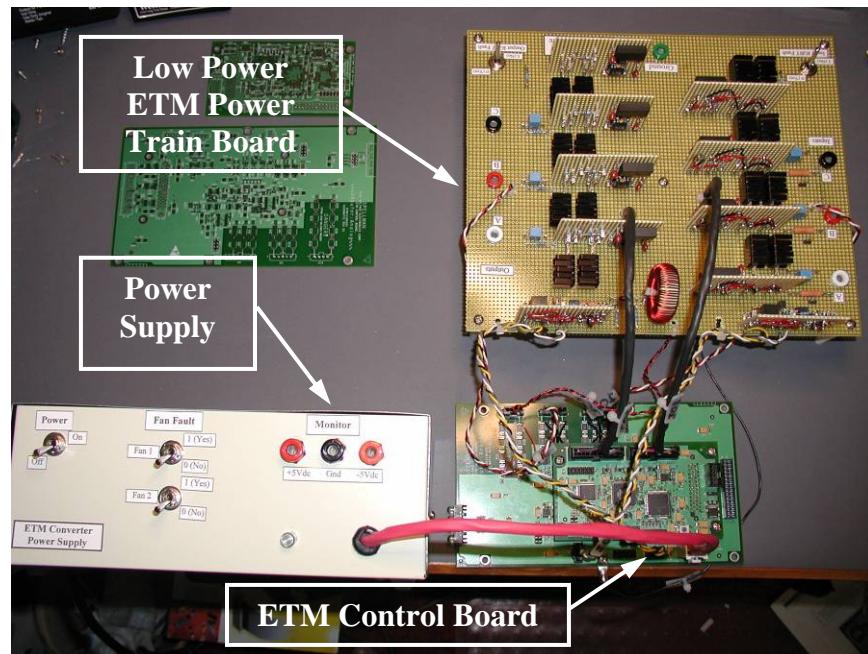

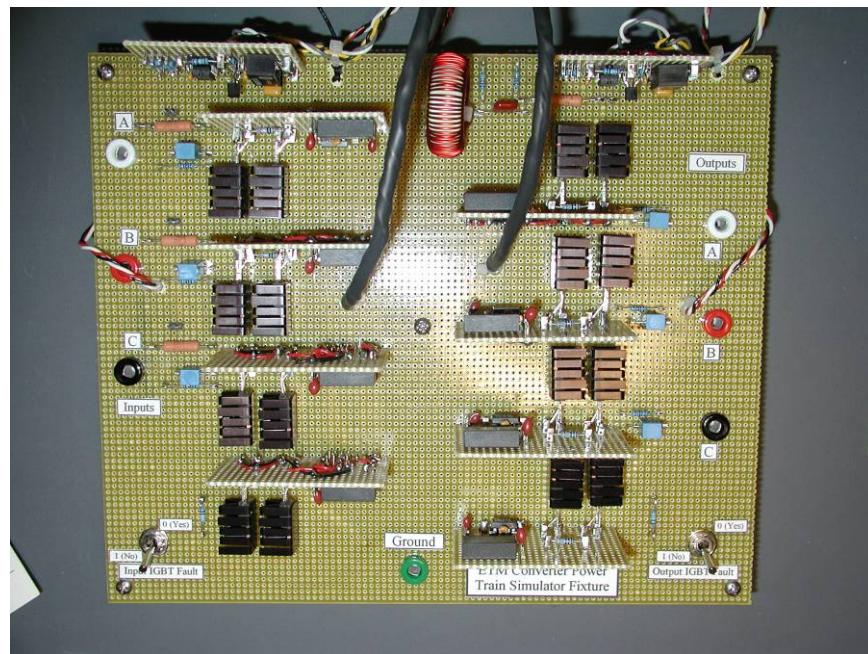

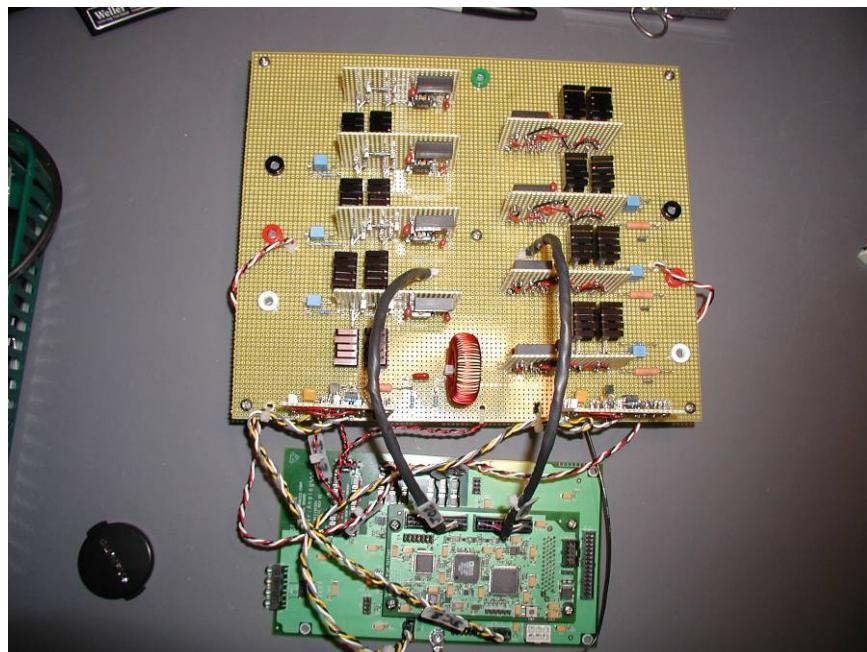

The control board debug test setup was used for two purposes: To debug the firmware for the ETM Control Board (ECB) and to verify the ECB functionality during the testing of the ETM Converter prototype. The Control Board Test setup is shown in Figure A1. Six digital-to-analog converters (along with the power amplifiers) were used to provide variable amplitude, variable frequency input/output phase sources for the ETM Power Train stage. This low power replica of the 34kW prototype power stage was optimized for 20Vp-p input voltages (+/-10V) and a maximum peak current of 200mA. In this way, the operation of the ETM Converter may be achieved without high power/current/voltage to ease and simplify the software/firmware development and debug processes. The low power ETM Power Train Board also included current sensors to measure the resonant current and Phase A input current.

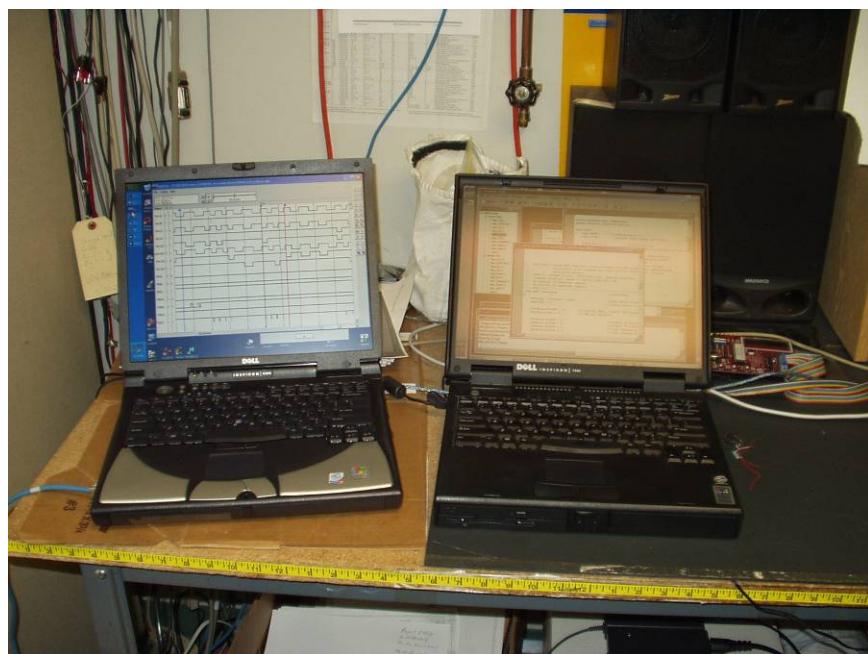

The two laptop computers were employed to: 1.) control the input/output voltage and frequency parameters of the operating ETM Converter; and 2.) to program the firmware on the ETM Control Board and to set the adjustable operating parameters (decision thresholds) of the of the Control Board software algorithm.

During the Control Board debug process and the ETM Converter prototype debug process, the low power facsimile board essentially provided a second prototype and the capability to make changes/modification to the firmware on a concurrent basis with the debug and performance testing of the 34kW ETM Converter prototype. All parameters involved in the operation of the ETM Converter could and were observed using this test

**Figure A1. ETM Control Board Debug/Programming Test Setup.**

setup, and excellent correspondence of operation and values was obtained using this testing methodology.

The low power ETM Converter test boards were constructed by dtm Associates and were located at TechEn, Inc., Milford, Massachusetts (the software/firmware developers) for the duration of the debug test activities.

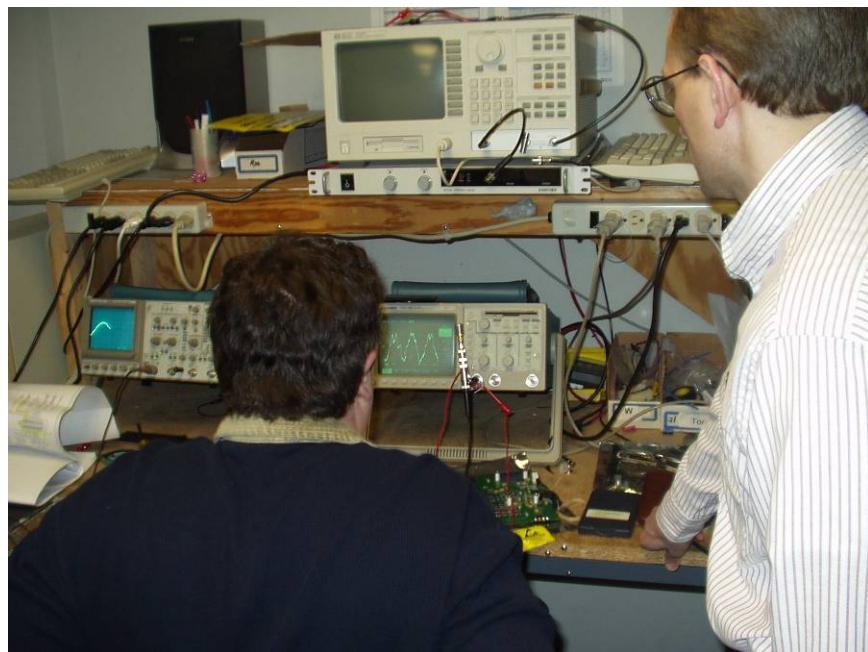

Photographs of the actual low power ETM Converter test setup and the equipment used are shown in Figures A2 through A10, which follow.

**Figure A2.** ETM Control Board Debug/Programming Configuration.**Figure A3.** ETM Control Board Debug/Programming Configuration.

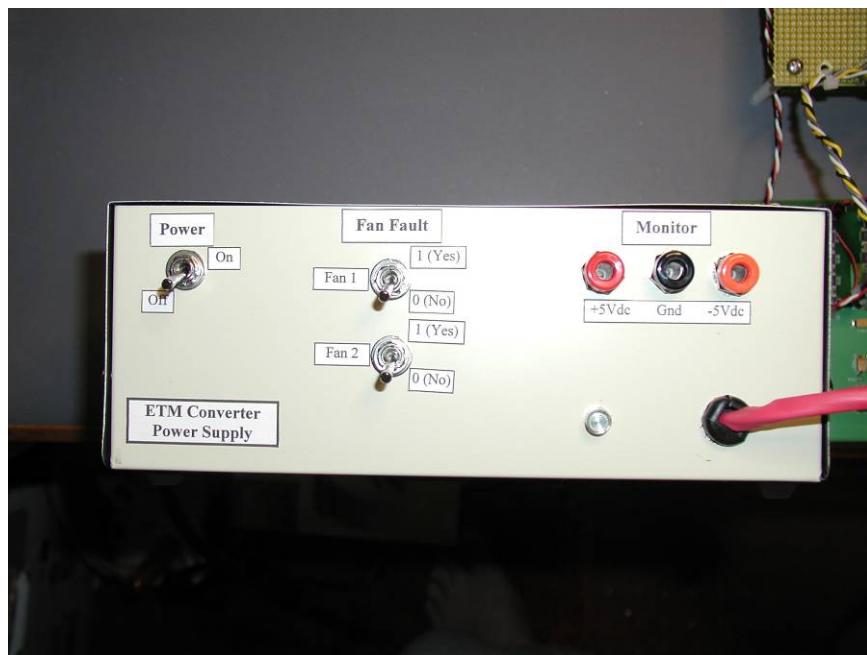

**Figure A4.** Low Power ETM Power Train Board w/ETM Control Board.**Figure A5.** Test Setup Auxiliary Power Supply.

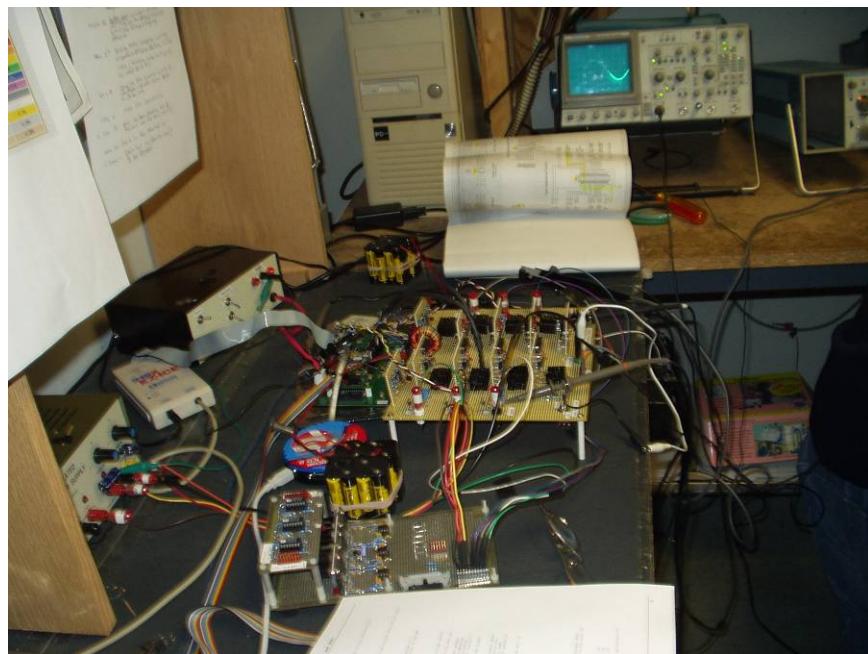

**Figure A6.** ETM Firmware Debug Benchtop Test Setup.

(at TechEn, Inc. Milford, MA)

**Figure A7.** ETM Firmware Debug Benchtop Test Setup.

(at TechEn, Inc. Milford, MA)

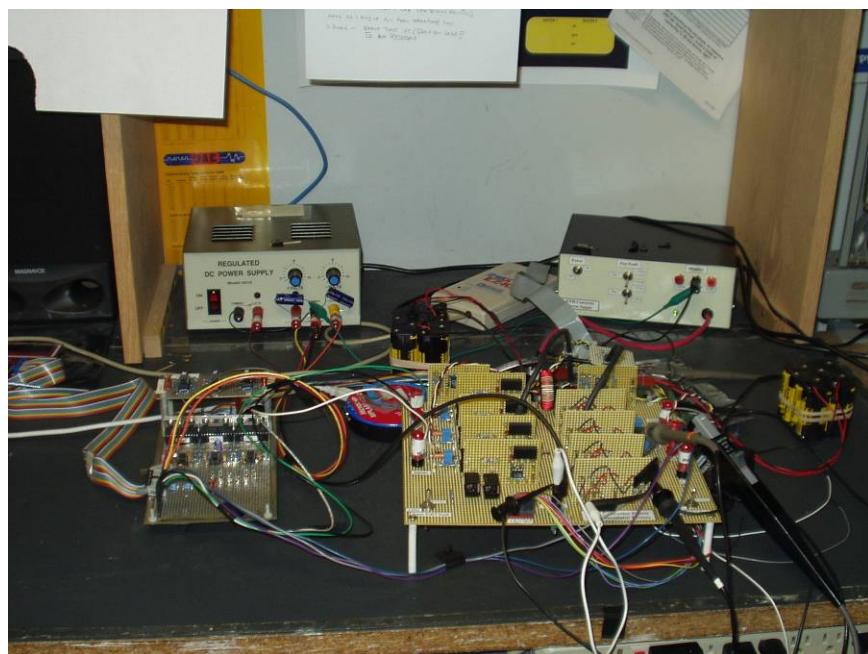

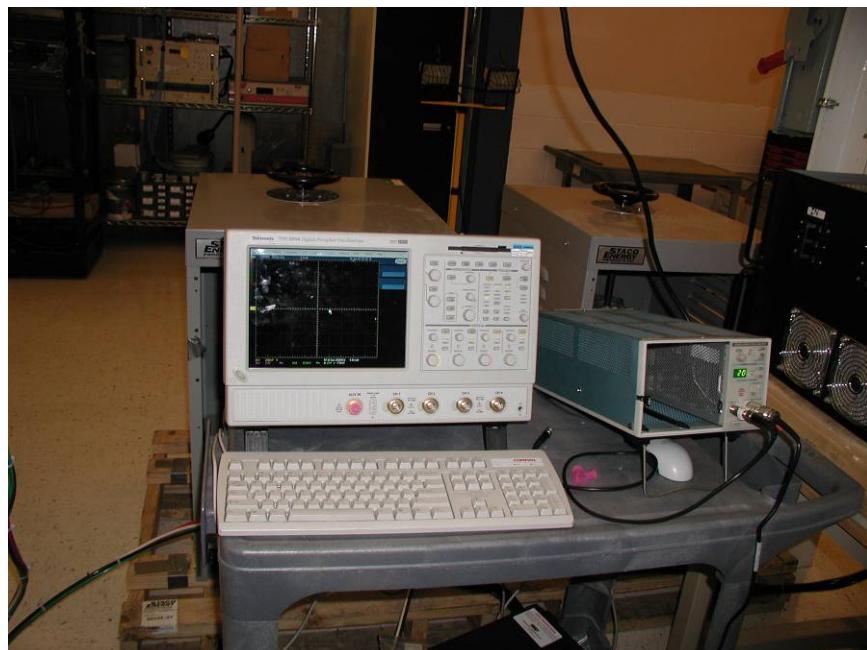

**Figure A8. ETM Firmware Debug Support Test Equipment.**

(at TechEn, Inc. Milford, MA)

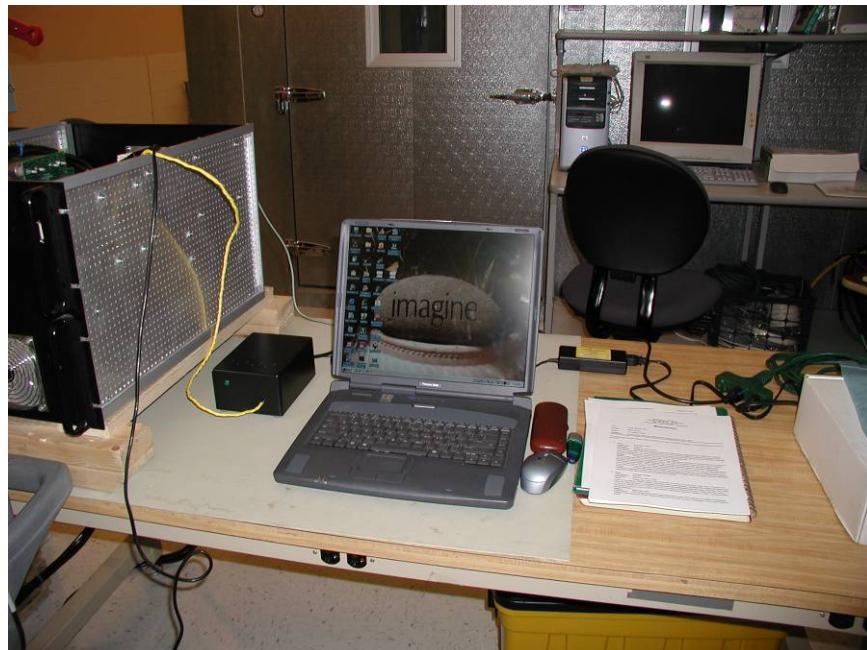

**Figure A9. ETM Firmware Debug Test Support Computers.**

(at TechEn, Inc. Milford, MA)

**Figure A10. ETM Firmware Debug Test In-Progress.**

(at TechEn, Inc. Milford, MA)

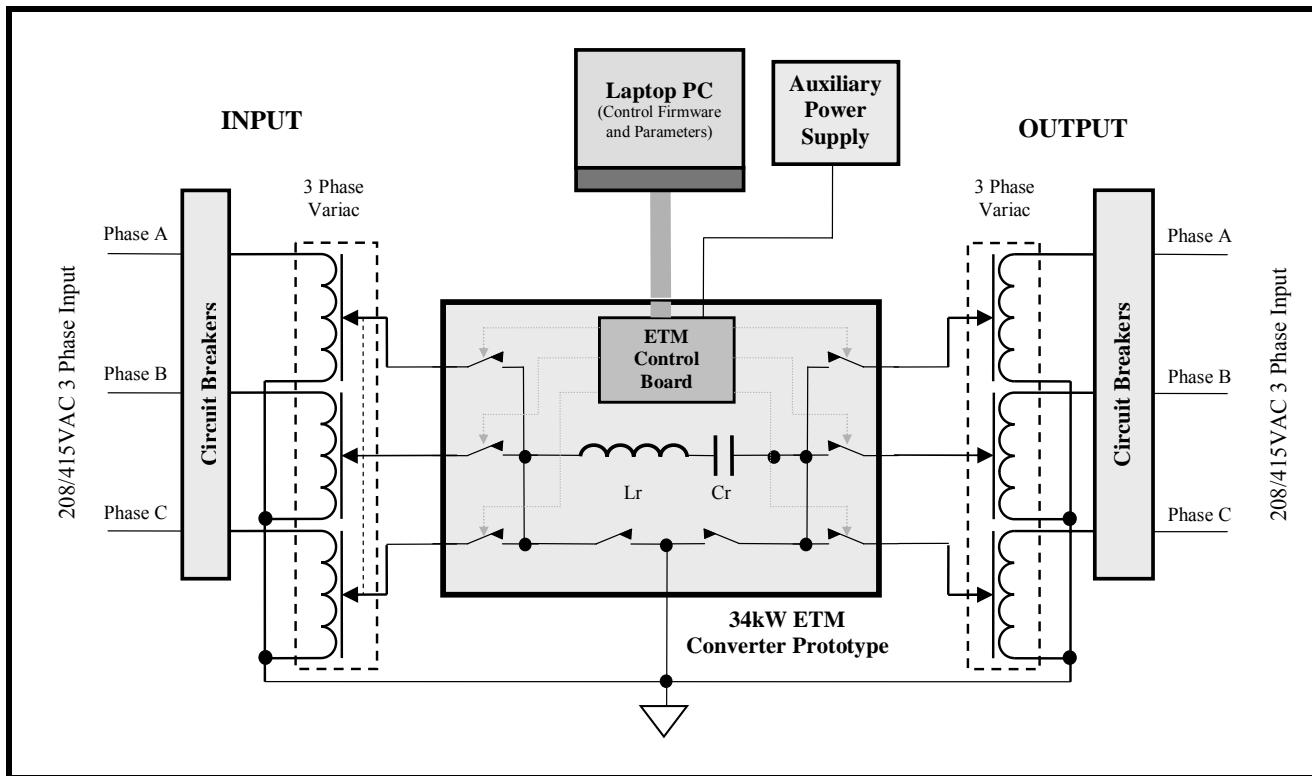

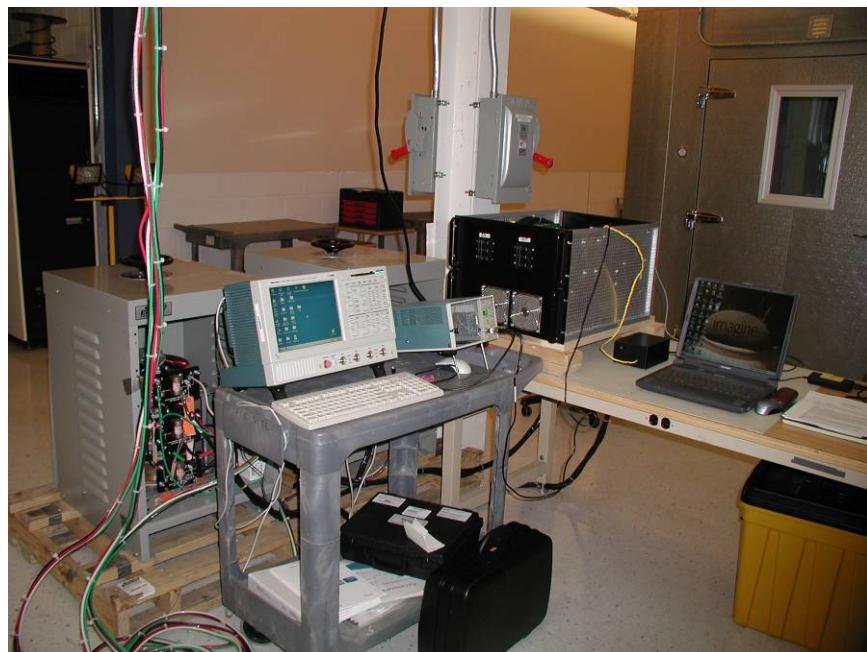

## ii.) 34kW Prototype ETM Converter Test Setup

The ETM Prototype Debug and Performance Tests were performed at IQS LLC/Marlboro Test Labs in Marlborough, MA. This lab had the necessary facilitations to provide the required I/O utility voltage for the ETM Prototype. The test setup consisted of the elements shown schematically in Figure A11.

**Figure A11. 34kW Prototype ETM Converter Test Setup.**

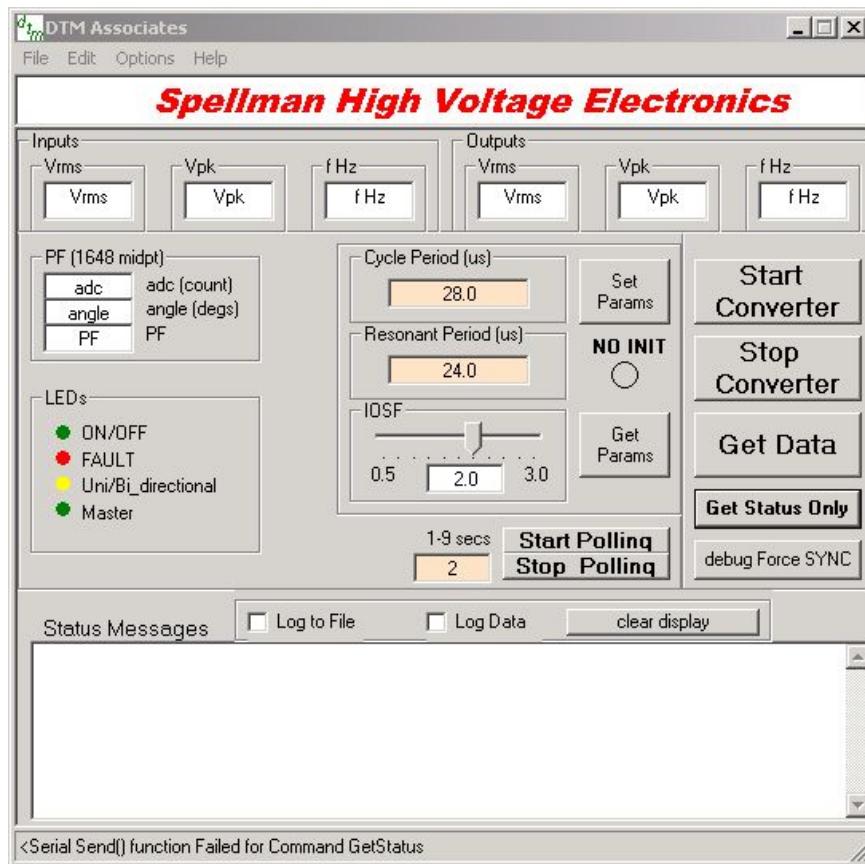

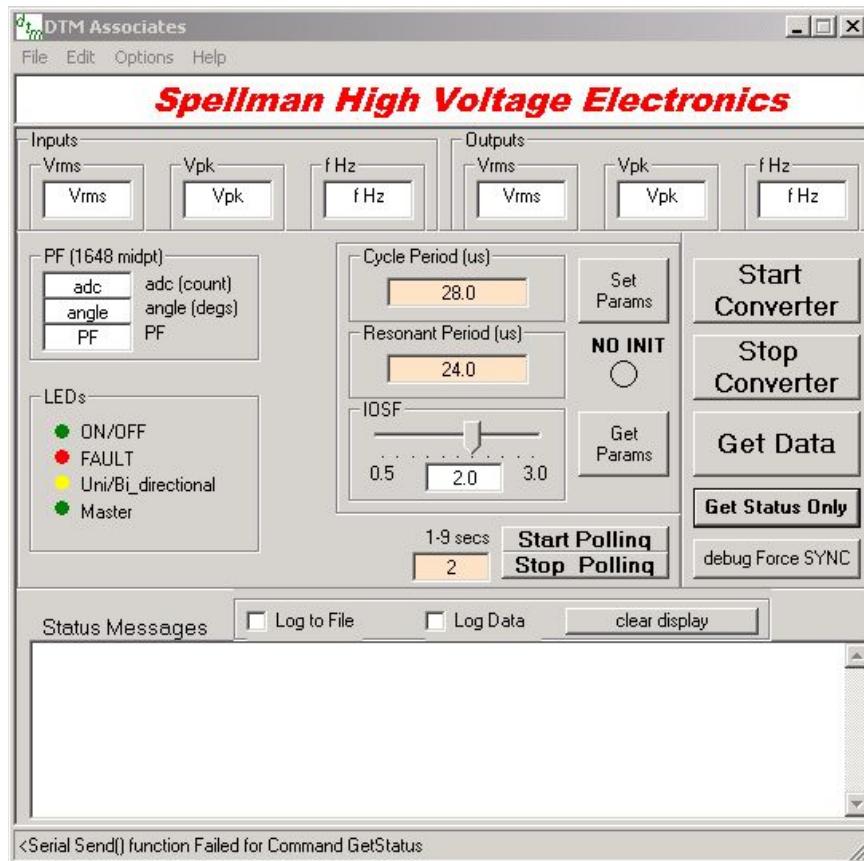

The key elements of this test configuration are the three-phase Variacs used to vary the input and output voltages and the laptop PC computer used to set the operating variables of the ETM Converter. The laptop PC utilized custom GUI software to set the parameters and a screenshot of the software is shown in Figure A12.

**Figure A12.** 34kW Prototype ETM Converter GUI Control Interface.

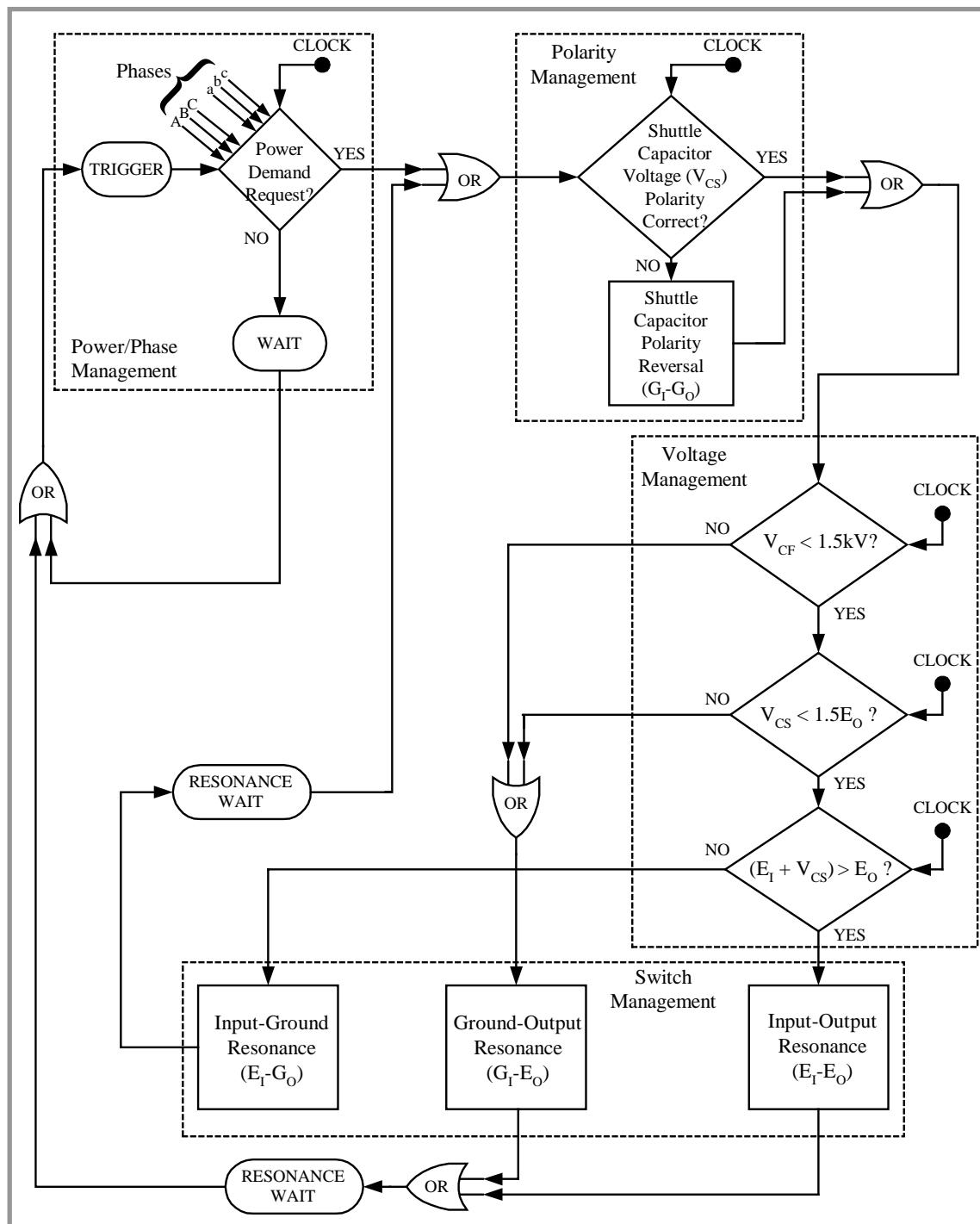

The User Interface on the controller PC allows the setting and retrieval of firmware decision points and ETM Converter operating parameters. The decision point parameters include the Resonant Period time (this should match the measured L-C resonance of the power train), the Cycle Time (which is the Resonant Time plus two microseconds of idle/processing time) and the IOSF parameter (whose value corresponds to the ETM flowchart and sets the final voltage on the resonant capacitor). The operating parameters include the input and output phase voltages and frequencies, the power factor and the LED front panel indicator statuses. Additionally, the operating and fault status of the dsPIC and ADSP microcontrollers can be retrieved for debug information. Thus, during the debug and performance testing of the prototype, the decision point parameters of the ETM converter were varied and the resultant operating performance was observed.

Photographs of the actual low power 34kW ETM Converter test setup and the equipment used are shown in Figures A13 through A17, which follow.

**Figure A13.** 34 kW ETM Converter Prototype Test Setup.

(at MTL/IQS LLC, Marlborough, MA)

**Figure A14.** 34 kW ETM Converter Prototype Test Support Equipment.

(at MTL/IQS LLC, Marlborough, MA)

**Figure A15.** 34 kW ETM Converter Prototype Test Laptop PC Controller.

(at MTL/IQS LLC, Marlborough, MA)

**Figure A16.** Three Phase 40kVA Input and Output Variacs.

(at MTL/IQS LLC, Marlborough, MA)

**Figure A17. 34kW ETM Converter Prototype During Performance Test.**

(at MTL/IQS LLC, Marlborough, MA)

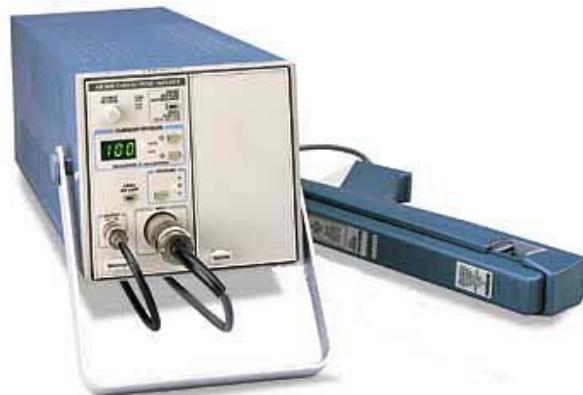

### iii.) Test Equipment Used

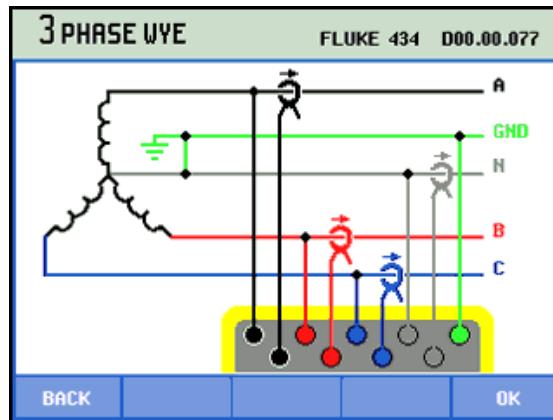

The test equipment used during the Performance Test phase is shown in Figures A18 through A22. The majority of the waveform data captures were made directly on the ETM Control Board via the test point stake pins. The remainder of the performance measurements (AC voltage, AC current, Power Factor, etc.) were made on the external connections utility connections to the ETM Prototype, using the Fluke Model 434 Power Analyzer, as shown in Figure A23.

**Figure A18.** *Tektronix Model TDS5054B Oscilloscope.*

**Figure A19.** *Tektronix Model AM503 w/A6303 Current Probe.*

**Figure A20.** *Fluke Model 434 Three Phase Power Analyzer.*

**Figure A21.** Fluke Model 87 Digital Multimeter.

**Figure A22.** Compaq Presario 3045US Laptop Computer.

**Figure A23.** Test Connections For The Fluke Model 434 Power Analyzer.

## B.) ETM Converter Host GUI Interface Description

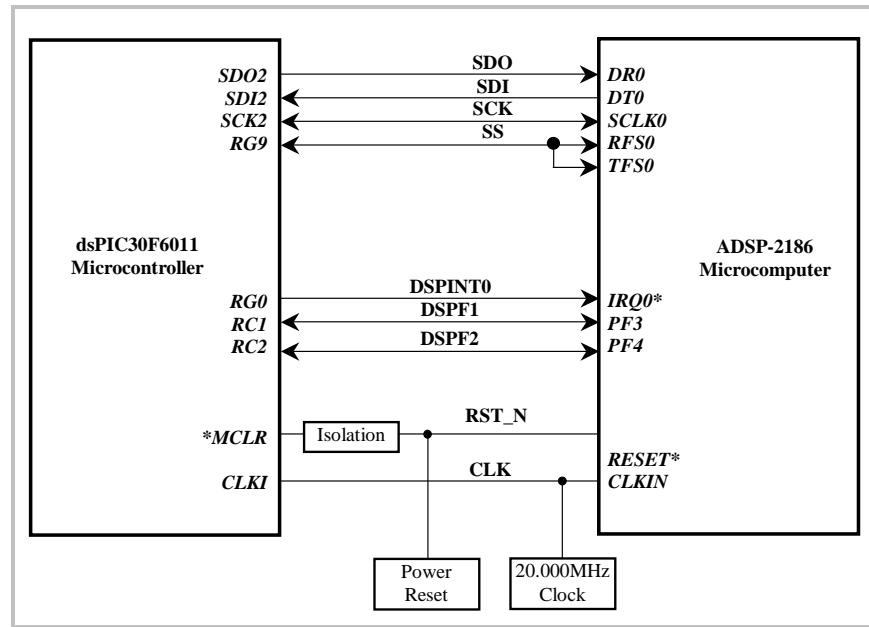

The ETM Converter Host GUI Interface resides on a host PC used to set the operational parameters of the ETM Converter. The GUI Interface is necessary because the ETM Converter is a totally microprocessor/DSP-controlled power system. It does not have a hardware-based set point for operation or an inherent hardware-based mode of operation. The operation of the Converter is controlled by firmware code, downloaded to the Converter via the host PC and natively resident in non-volatile memory in each of the DSP microcontrollers used. The GUI Interface is used to set the variable parameters within the firmware code, which determine the operating points of the Converter in its application. Within the framework of the fixed firmware code utilized by the Converter, the GUI parameters can be thought of as “personalizing” the Converter. Because of this functionality, the ETM Converter may truly be considered a “Power Computer”!

The ETM Converter Host GUI is written in Visual Basic, and it communicates a set of data parameters via an external RS-232 serial data link between the host PC (the laptop) and the ETM Converter Control Board within the Converter (ultimately communicating with the dsPIC30F6011 DSP microcontroller device). The GUI allows for the bidirectional exchange of data between the host and the Converter. Data parameters (Tres, Tcyc and IOSF values) controlling the Converter pass from the host PC to the ETM Converter and operating parameters (I/O frequencies, I/O voltages, the firmware-resident values of the previously-described data parameters, microcontroller status information and general Converter fault/status information) are passed from the ETM Converter to the host PC. The GUI Interface also allows for data logging and capture while the ETM Converter is operating.

Finally, the GUI Interface acts as the ON/OFF “softkeys” for the ETM Converter, as the ONLY way to turn the converter on and off is via the host GUI software; there are no mechanical ON/OFF switches on the ETM Converter housing. This is done to make the ETM Converter as autonomous as possible – once personalized for the particular application, the converter is started (turned ON) and left to operate until grid conditions or an internal fault cause the converter to shut down (i.e. go “off line”). This means the ETM Converter may be controlled or personalized from a physically remote location.

### i.) ETM GUI Parameter Discussion

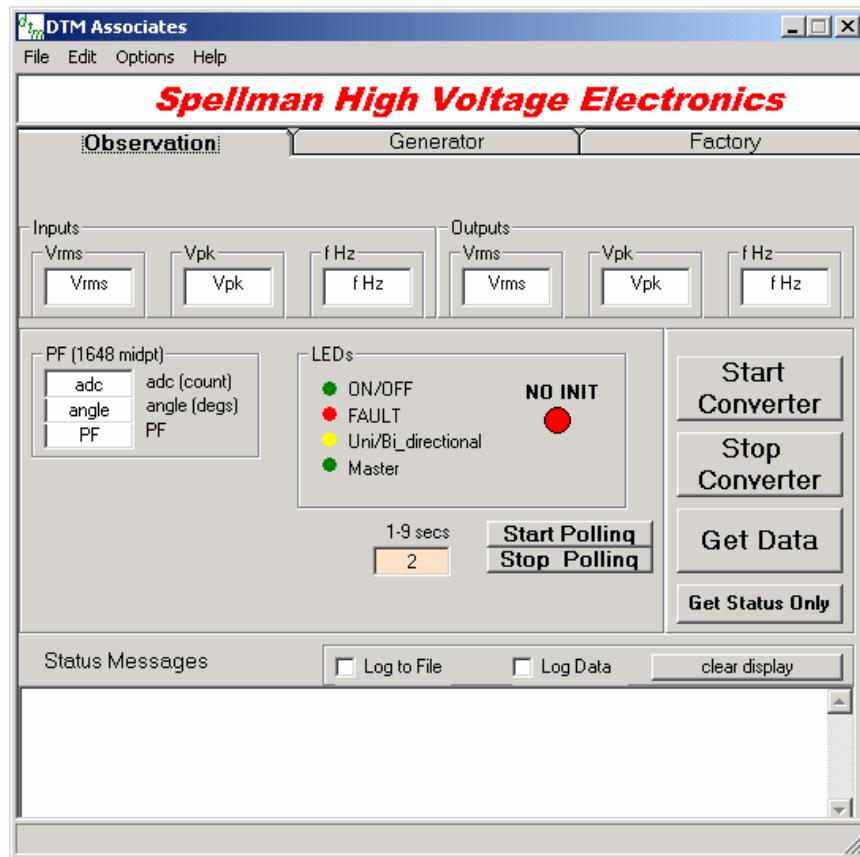

A screens shot of the main GUI Interface screen is shown in Figure B1.

**Figure B1.** ETM Converter Main GUI Control Interface.

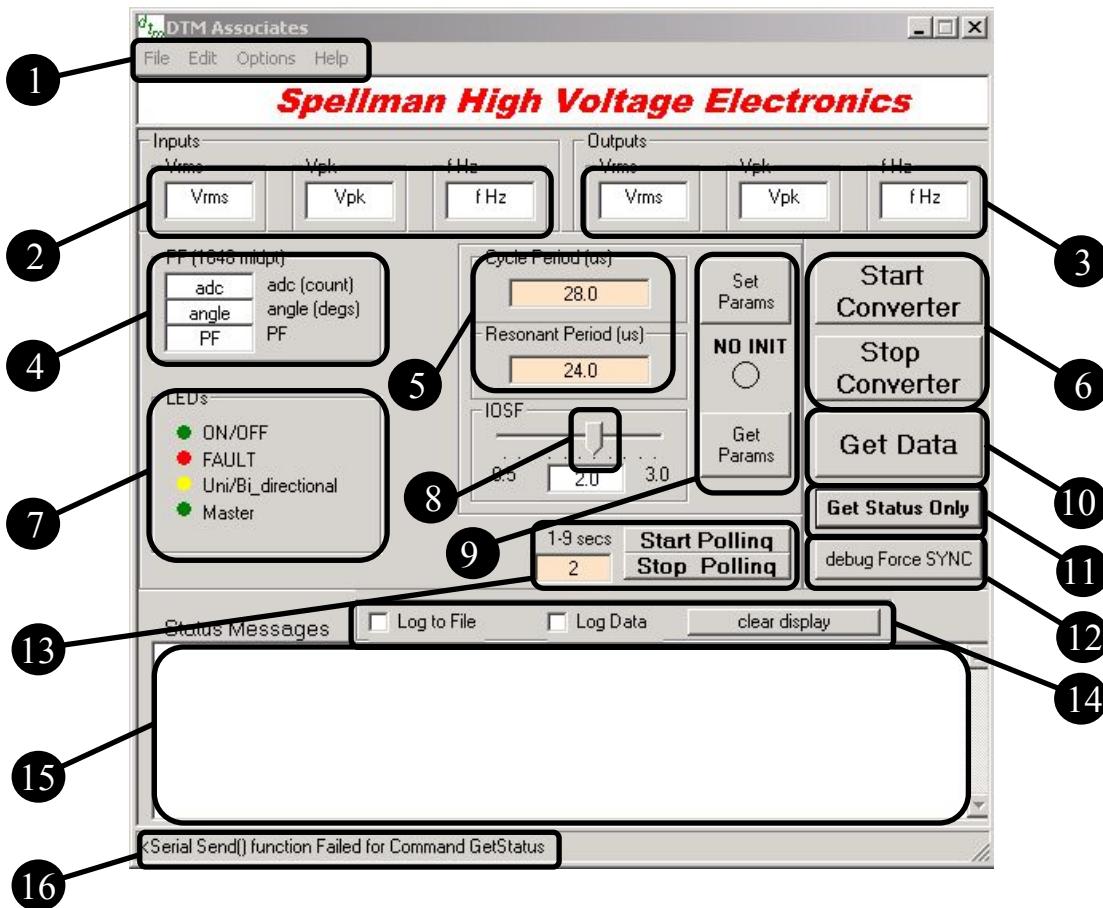

This interface is the main data entry and retrieval location for the host PC. The various functionalities of this Interface window are shown in Figure B2.

**Figure B2. ETM Converter Main GUI Control Interface Functional Descriptions.**

The operation of the individual numbered function blocks is detailed as follows.

1. **Submenu Action Menu:** This menu allows for the selection of the various submenus available for parameter setting and debugging.

- a. *File:* Allows the User to dismiss/shut-down the GUI.

- b. *Edit:* Allows the User to set the values of the IRZC (current zero-crossing detector) upper and lower limit DACs and clear their values.

- c. *Options:* Allows the User to set the properties of the RS-232 Comm Port on the Host PC.

- d. *Help:* Unused at present.

2. **Input Parameter Display:** Allows the User to view the actual operating ETM Converter input voltage and frequency. In future revisions, input current is planned to join this list.

3. **Output Parameter Display:** Allows the User to view the actual operating ETM Converter output voltage and frequency. In future revisions, output current is planned to join this list.

4. **Power Factor (PF) Parameter Display:** Allows the User to monitor the input power factor and phase angle of the Phase A input (which is representative of all three phase inputs).

5. **Resonant and Cycle Time Parameter Input Areas:** Allows the User to enter the desired Resonance Time (Tres) and Cycle Time (Tcyc) into the input boxes.

6. **Start/Stop Converter “Softkeys”:** These are the only means for the User to start and stop the ETM Converter. Once the Converter is started, it can only be stopped via the “Stop Converter” softkey.

7. **Front Panel LED Status Indicators:** This display area allows the User to view the status of the operating ETM Converter.

8. **IOSF Parameter Value-Setting Slider Bar:** This slider bar may be set by the User to select the optimum IOSF parameter value during the debug phase. This control is not planned to be included in production ETM GUI displays, as this value will be hard-coded into the firmware.

9. **Set Params/Get Params Softkeys and NO INIT Indicator:** At the initial Converter start-up/turn-on, the NO INIT indicator flashes RED to indicate to the User that the values displayed in the Cycle Period and Resonant Period input boxes on the GUI may not agree with the values stored in the non-volatile memory (NVM) in the ETM Converter. The ETM Converter may not be started by the User while this indicator flashing persists – the Start Converter softkey is disabled. The indicator is extinguished by the User by placing the desired values into the Cycle and Resonant Period input boxes and then clicking the Set Params softkey. This action stores the values entered on the host GUI to be saved in the NVM of the ETM Converter. Once the Tres and Tcyc values have been set via the Set Params softkey, they may be retrieved from the Converter NVM by the User at any time in the future using the Get Params softkey. Once the Set Params softkey has been clicked, the converter may be started using the Start Converter softkey.

10. **Get Data Softkey:** Allows the User to retrieve real-time data from the ETM Converter. This data is the I/O voltage and frequency, which are displayed in the data boxes shown in 1. and 2., as previously described.

11. **Get Status Only:** Allows the User to retrieve the status of the dsPIC and ADSP microcontrollers in the ETM Converter. This status information is displayed in the Status Message Window Area as shown in 15 in Figure B2 and described in 15., following.

12. **debug Force SYNC:** Allows the User to manually force the GUI-to-ETM Converter serial interface communications to synchronize. This is used only in those debug testing situations where the serial communications are observed to be disrupted.

13. **Start Polling/Stop Polling Softkeys and Value Display Area:** Allows the User to continuously monitor the I/O parameters shown in 1 and 2 and the Status Messages as shown in 15 of Figure B2. This is a useful feature for debug activities and remote troubleshooting.

14. **Log to File/Log Data Action Check Boxes and Clear Data Softkeys:** Allows the User to capture and save the ETM Converter debug or operating data to a Log File (i.e. “logfile.txt) or to continuously log data to the Status Messages area as shown in 15 of Figure B2. The Clear Data Softkey allows the User to clear the Status Messages area of all data and status messages.

15. **Status Messages Display Area:** Allows the User to view the real-time status messages received from the dsPIC and ADSP microcontrollers in the ETM Converter, or to view the real-time data retrieved from the Log Data function of the GUI as described in 14., previously.

16. **Command Line Display:** allows the User to view the last command executed by the GUI as well as the direction of the information exchange. A “<” character preceding the command indicates that it was executed from the ETM Converter to the GUI, and a “>” preceding the command indicates that it was executed from the GUI to the ETM Converter.

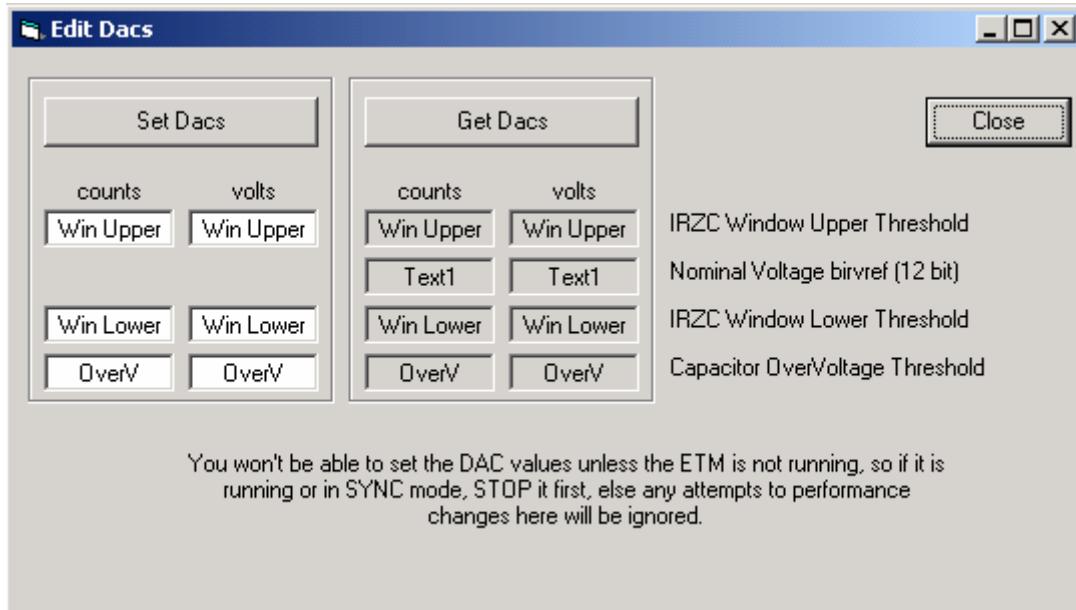

When the Edit Submenu is selected and the DACs option is chosen, the display box shown in Figure B3 is displayed:

**Figure B3. ETM Converter DACs Submenu.**

The operation of the individual functions for the Edit DACs window is detailed as follows:

1. **Set DACs:** This softkey allows the User to enter the DAC threshold information contained in either the “counts” or “volts” data boxes for the threshold point descriptions shown on the right side of the window. The upper two data boxes set the upper and lower IRZC thresholds for the zero crossing window detectors. The lower data box sets the threshold for the resonant capacitor over voltage threshold. These values may only be set if the ETM Converter is stopped.

2. **Get DACs:** This softkey allows the User to retrieve the information stored in the NVM of the ETM Converter. The values retrieved are displayed in the data boxes just beneath this softkey. It is always recommended to perform a “Get DACs” command after a “Set DACs” command is executed.

When the Options Submenu is selected and the CommPort Properties option is chosen, the display box shown in Figure B4 is displayed:

**Figure B4. ETM Converter CommPort Properties Submenu.**

This submenu allows the user to choose the serial Com Port for communications with the ETM Converter. The remaining parameters are “greyed-out” at the default conditions that are compatible with the internal RS-232 interface of the ETM Converter.

## ii.) Planned Enhancements to the ETM Converter Host GUI Interface

The host GUI interface was envisioned to undergo a sweeping change to make it more amenable to setting up the Converter for operation in an intended end-application. As such, there would be two distinct modes of operation for the GUI: the first would be to enable a User to perform cursory debugging and threshold set point functions; and the second is to perform the “personalization” of the Converter – setting voltage and frequency operating ranges and allowing for the input of the parameters as described in the “ETM Converter Programmers Guide”. Thus the GUI would have two natures, making it more user-friendly and intuitive in its functionality.

A screenshot of the improved GUI is shown in Figure B5.

**Figure B5. Proposed Improved ETM Converter Host GUI, “Observation”.**

This screen, tabbed “Observation”, will provide the means for monitoring the performance of the operating ETM Converter.

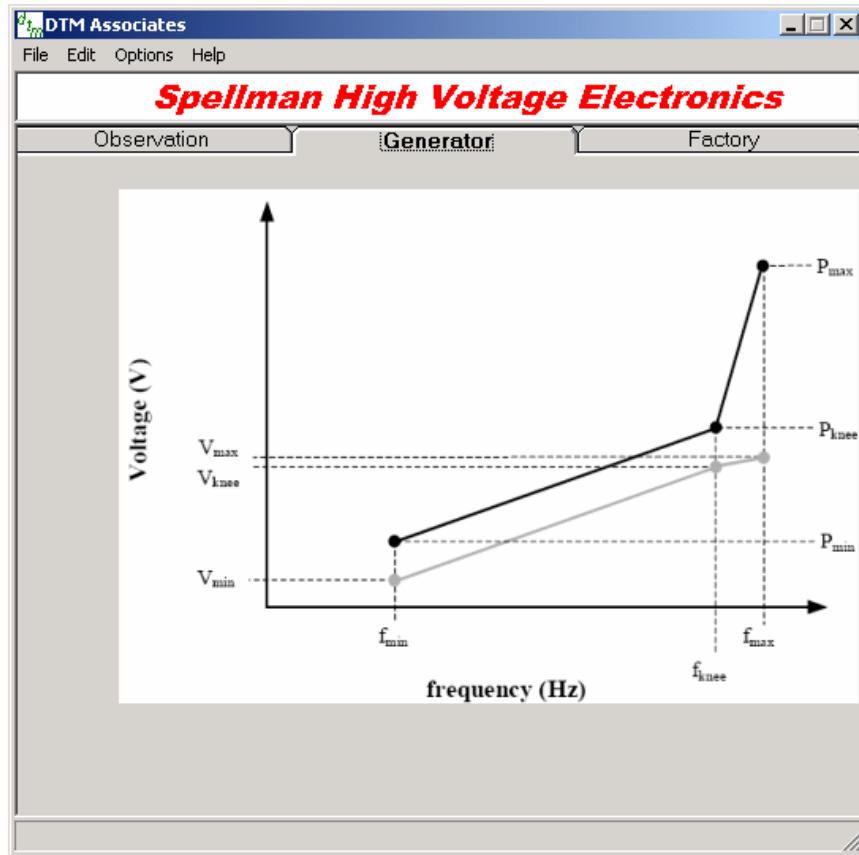

**Figure B6. Proposed Improved ETM Converter Host GUI, “Generator”.**

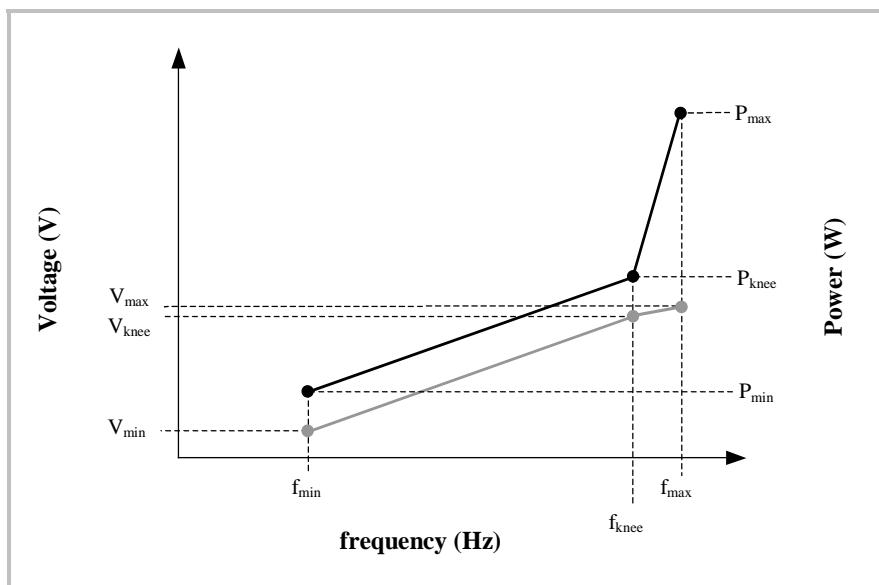

This screen, tabbed “Generator”, will provide the means for the User to personalize the ETM Converter to the wind turbine generator in the end-application.

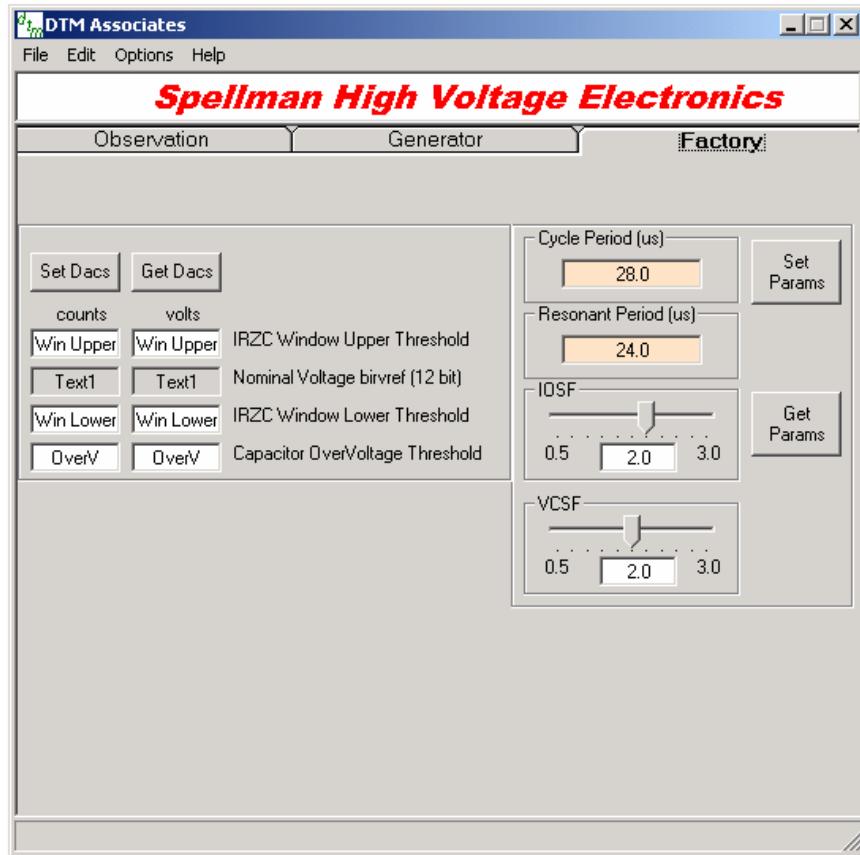

**Figure B7. Proposed Improved ETM Converter Host GUI, “Factory”.**

This screen, tabbed “Factory”, will provide the means for the Spellman HV to set the operating parameter of the ETM Converter, matching the firmware to the actual hardware performance. This tab will probably be password-protected as once these values are set at the factory, there is never the need by the User to reset or change them in the future.

## C.) Summary of Test/Debug Activities

The system-level debug and test activities for the 34kW ETM Converter prototype took place from September 1, 2004 until March 20, 2005. This time coincides with the successful power-on of the ETM prototype and continued until the funding for the project ran out.

### i.) Initial Power-Up/Debug Testing (9/1/04 to 10/21/04)

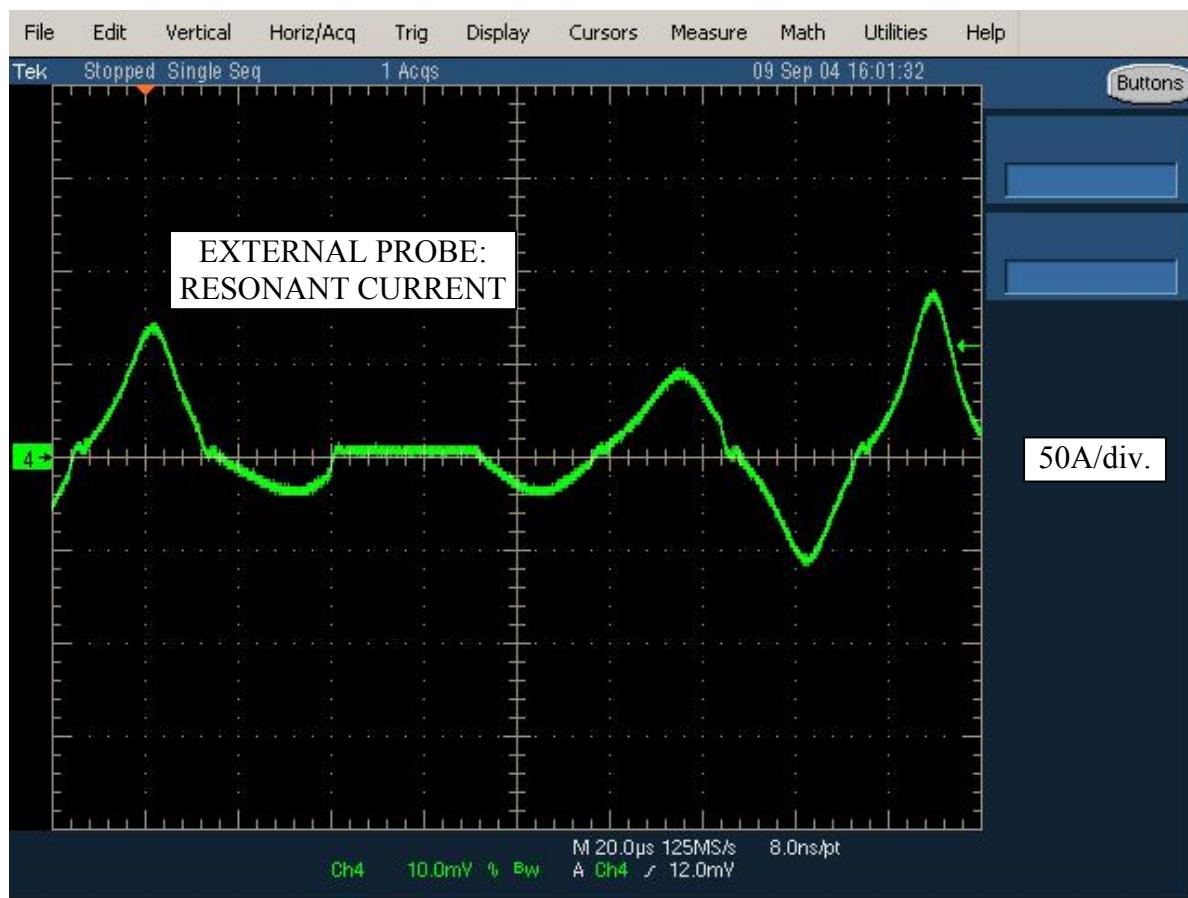

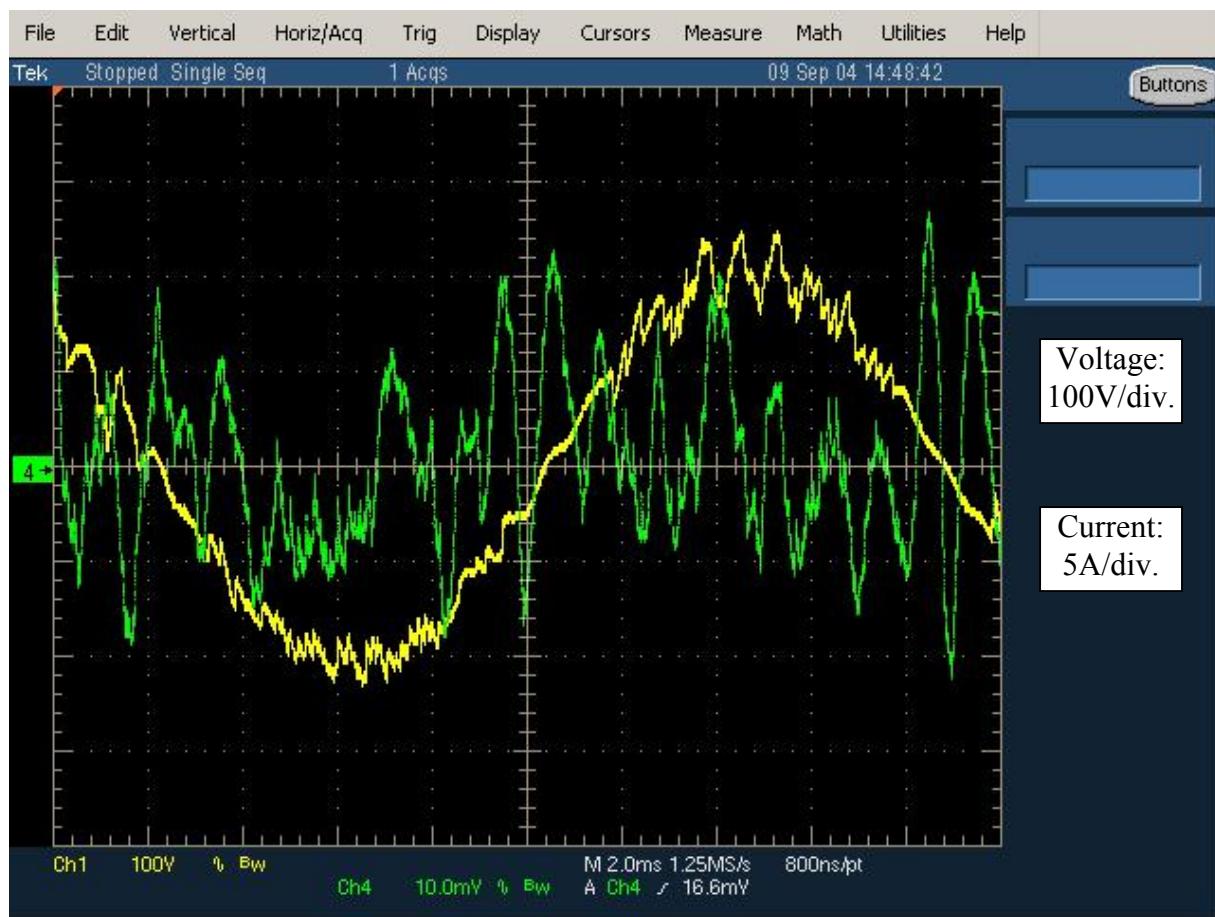

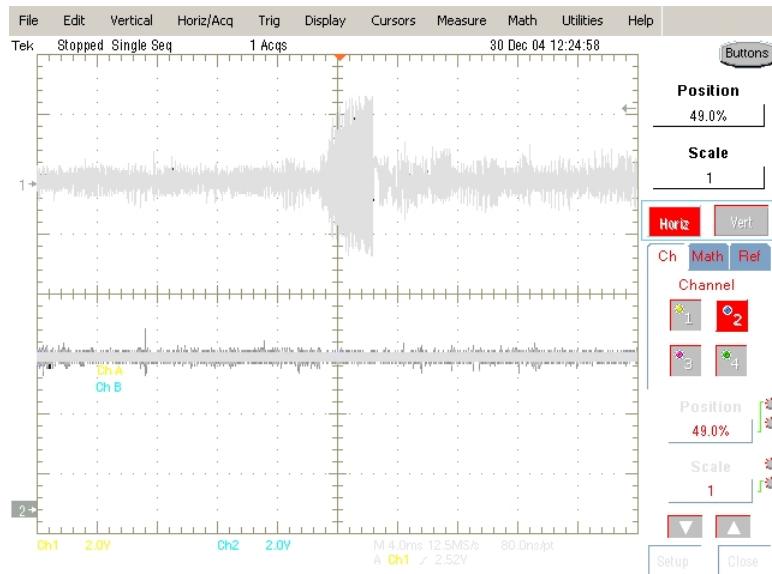

The initial power-up/debug testing commenced on September 1, 2004. These activities included the instrumentation of and then the powering-up of the ETM prototype at a greatly reduced input/output voltage level in order to observe and verify the key operating voltage and current waveforms in the circuit, and functional operation according to the “ETM Converter Programmers Guide”.

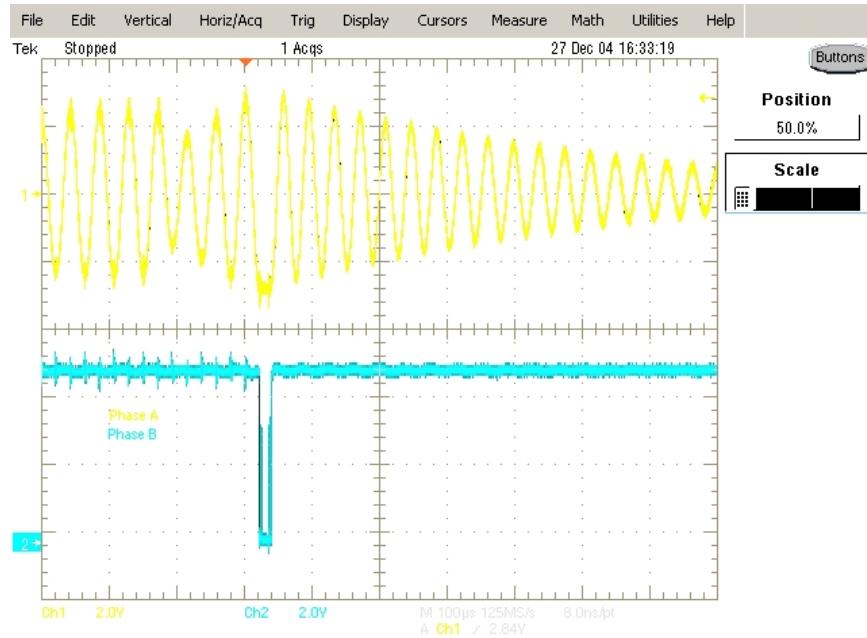

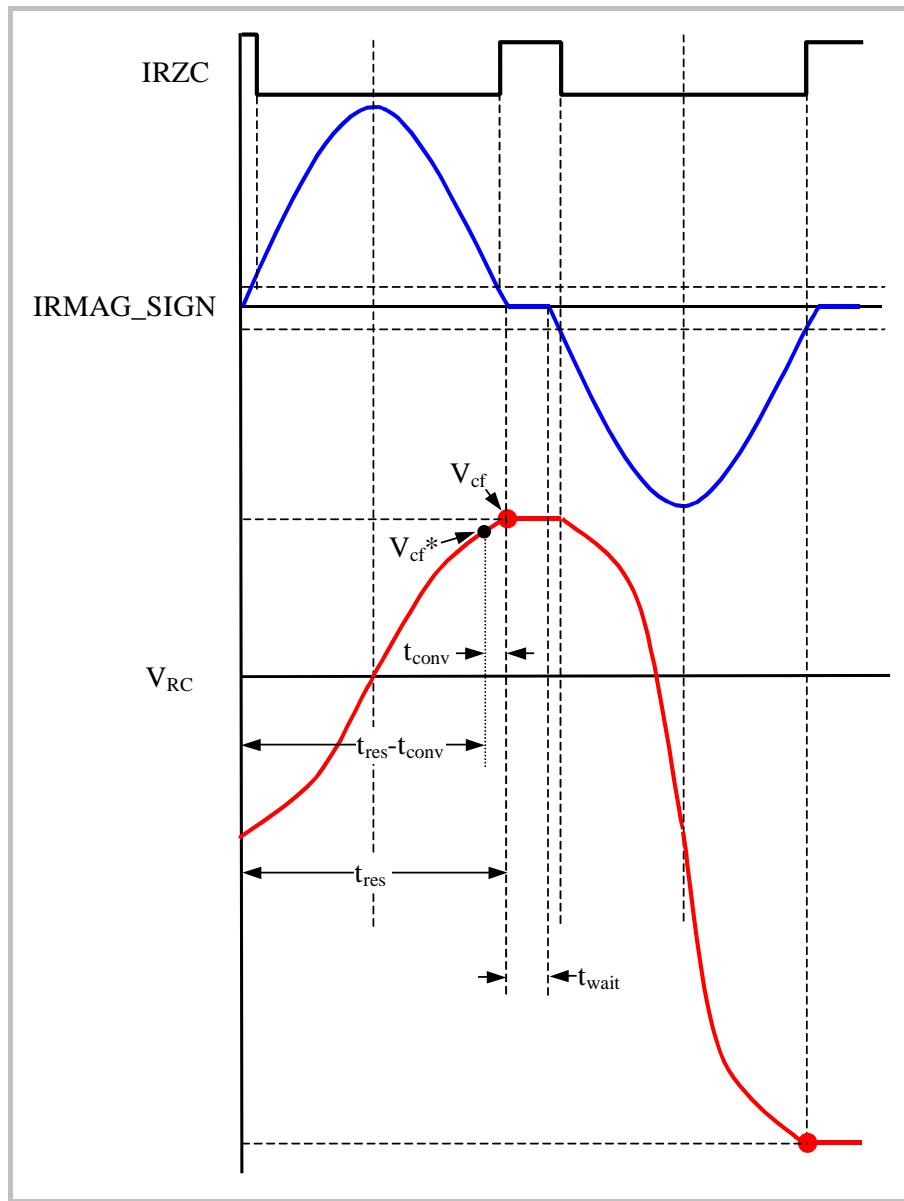

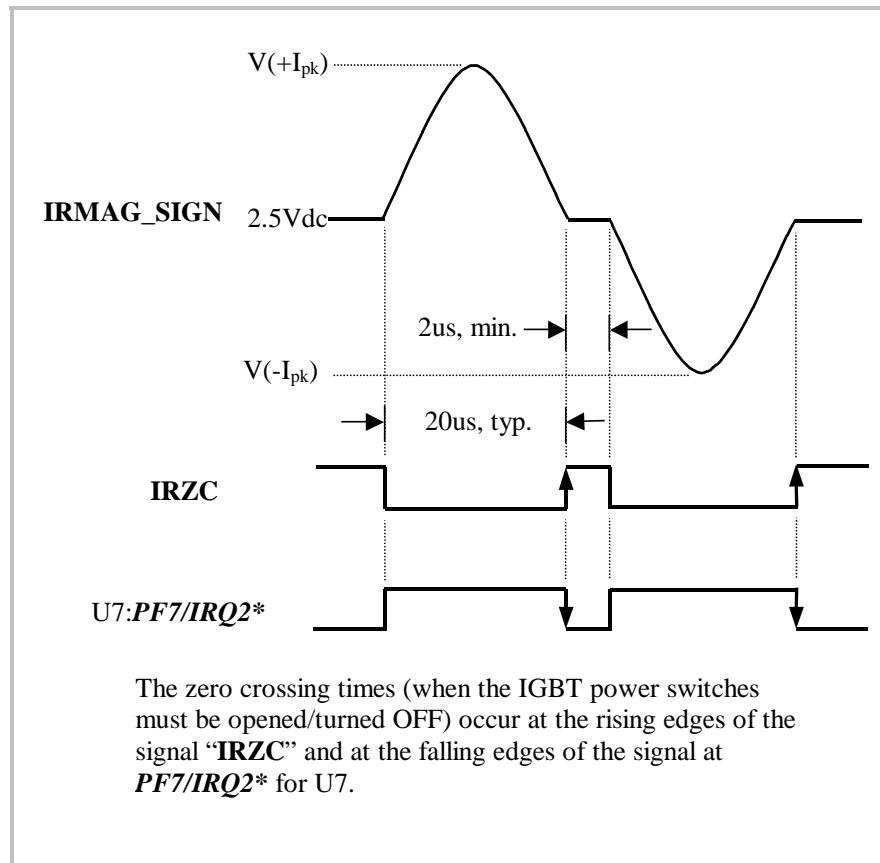

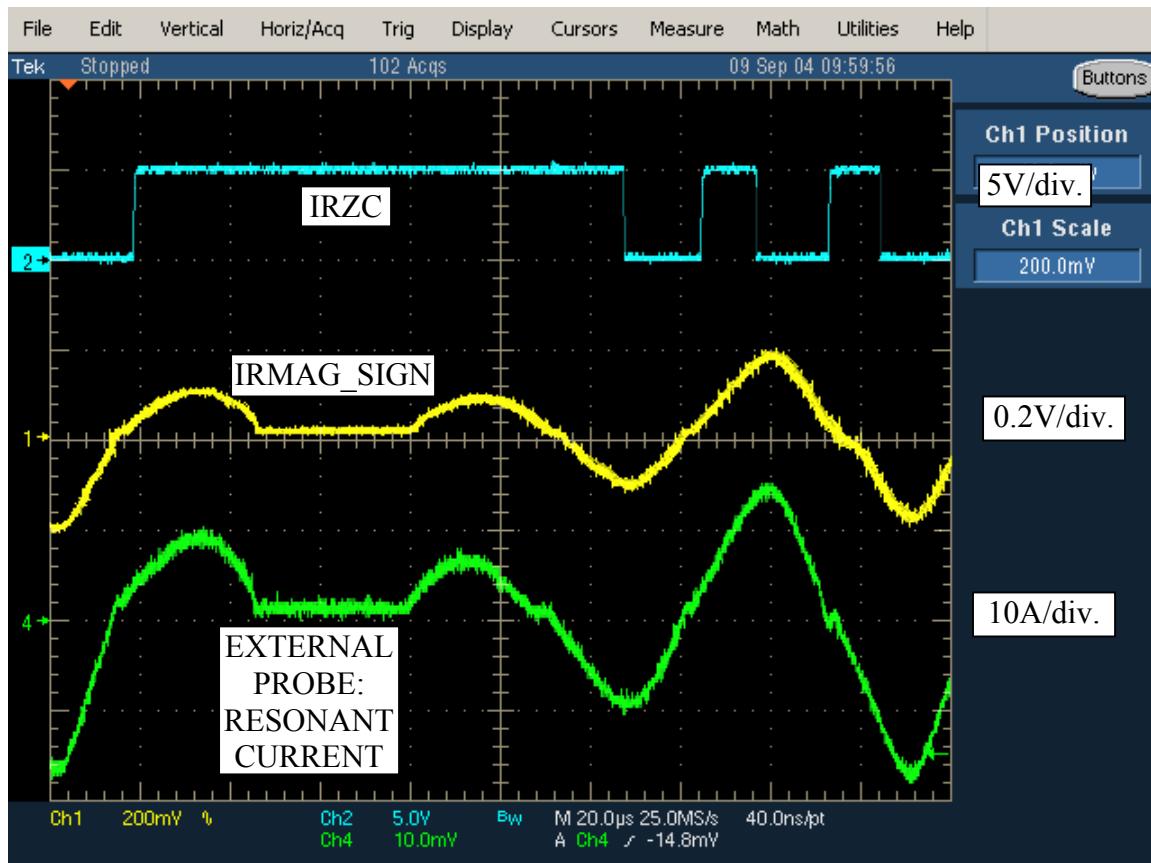

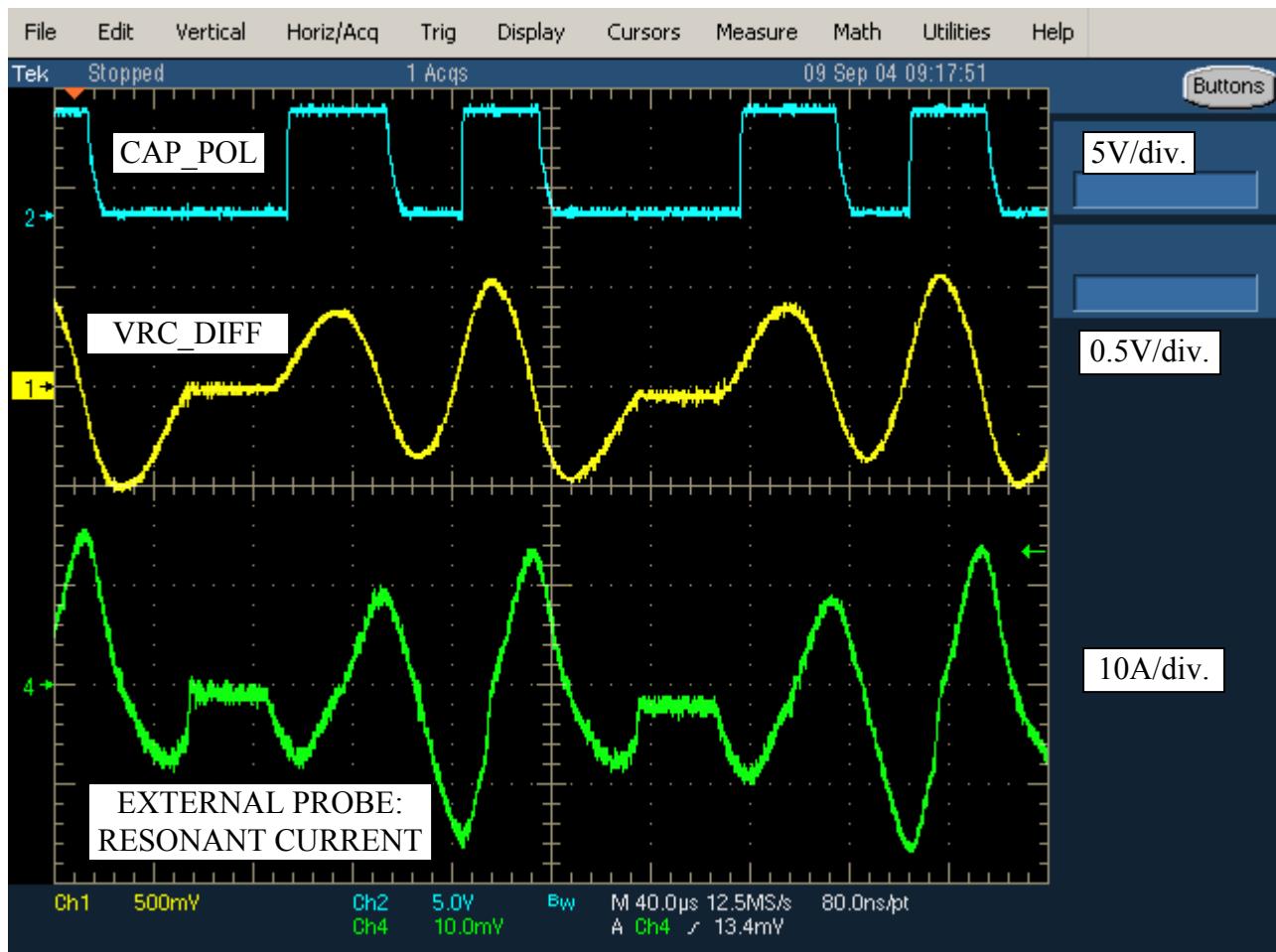

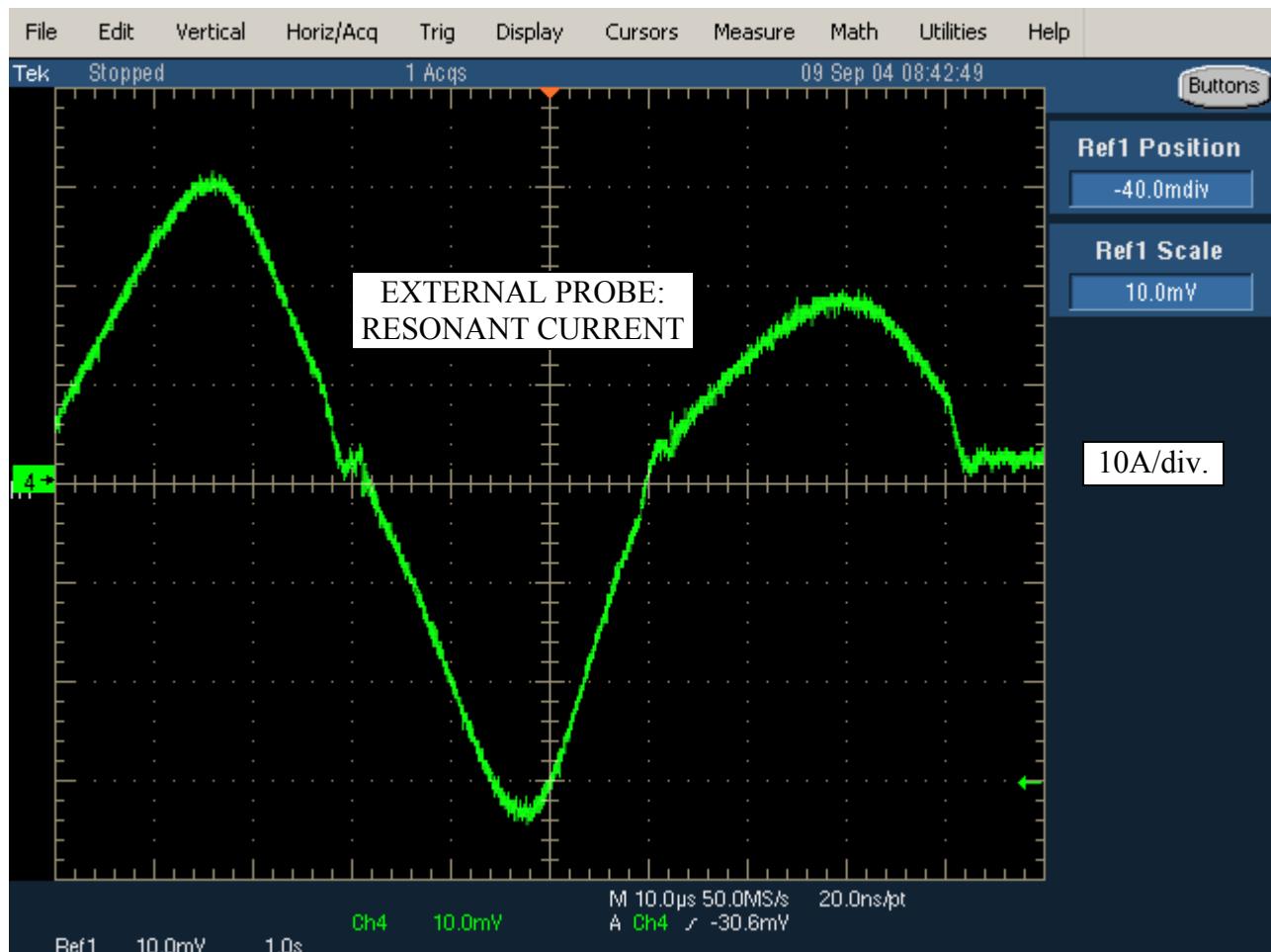

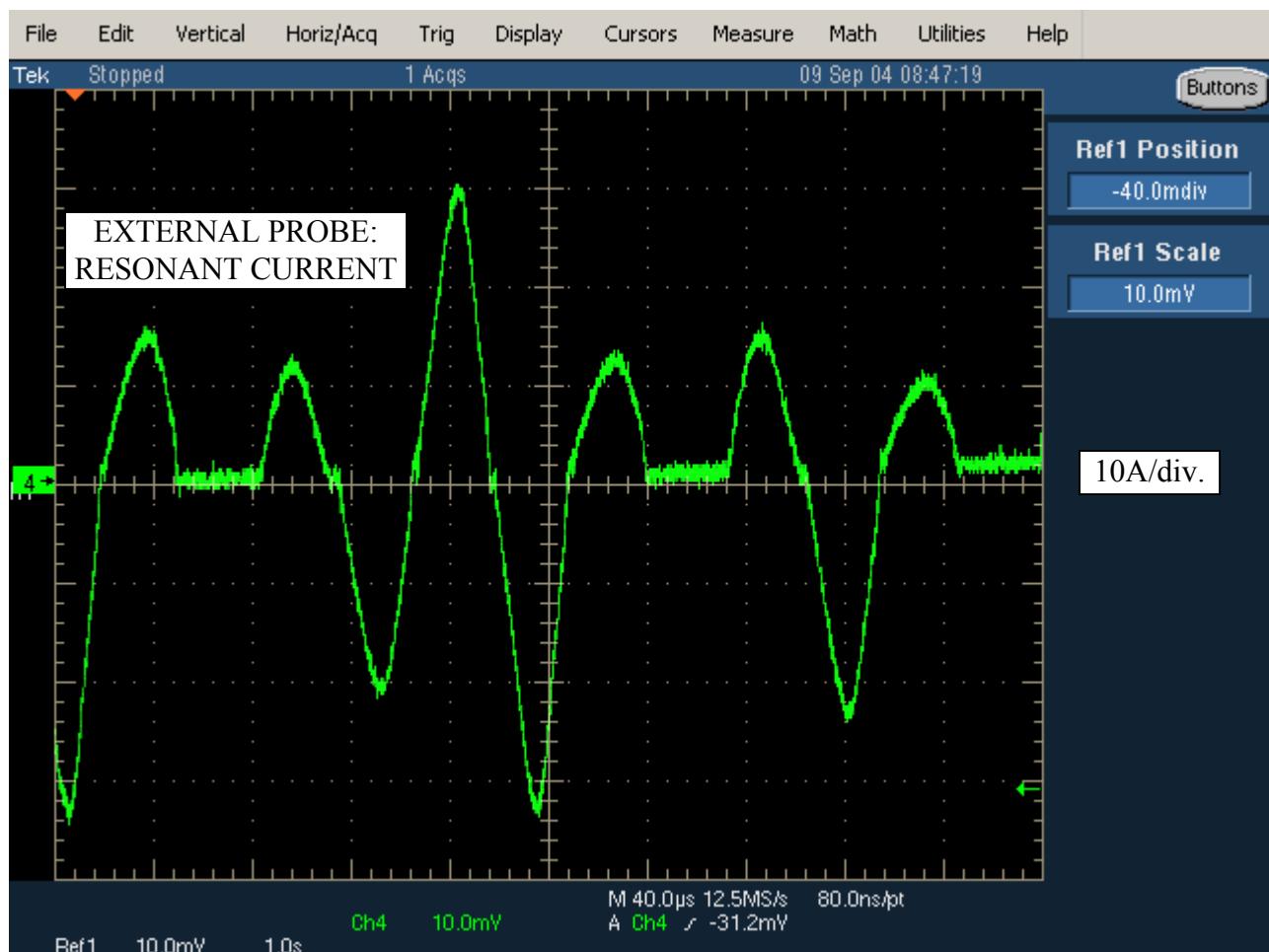

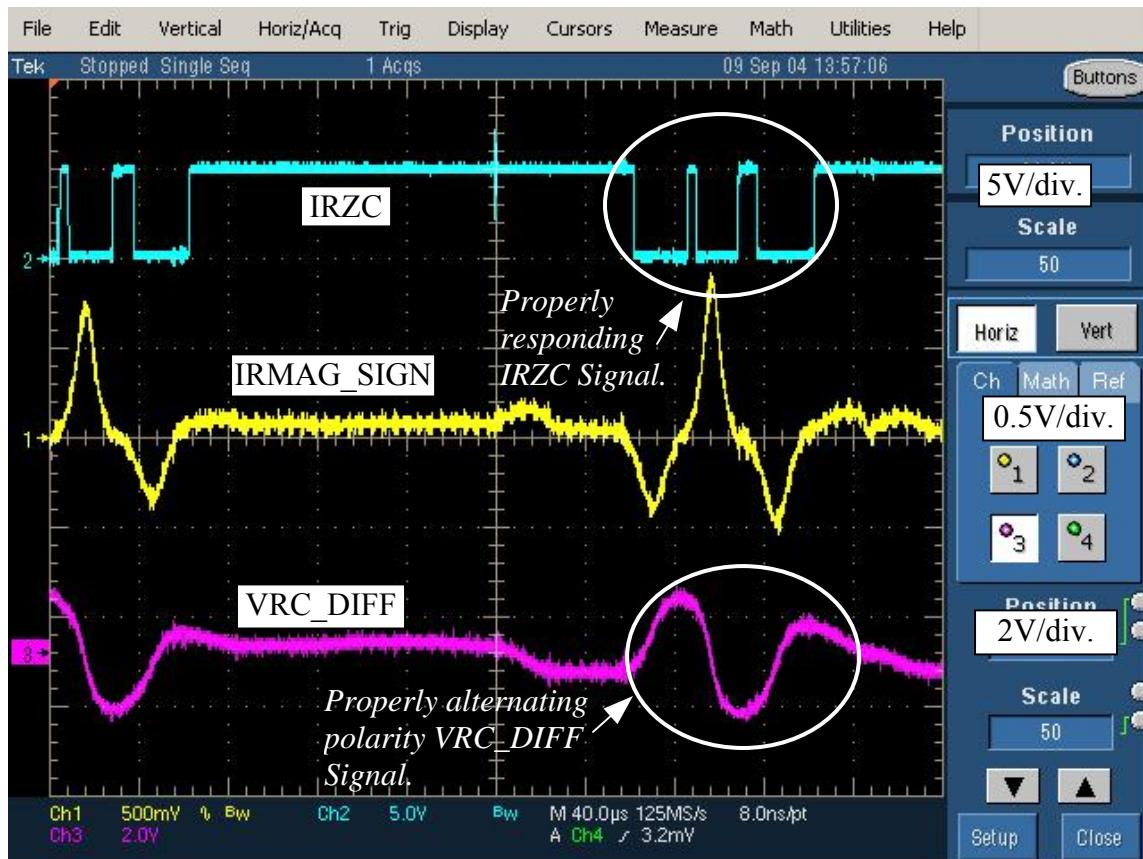

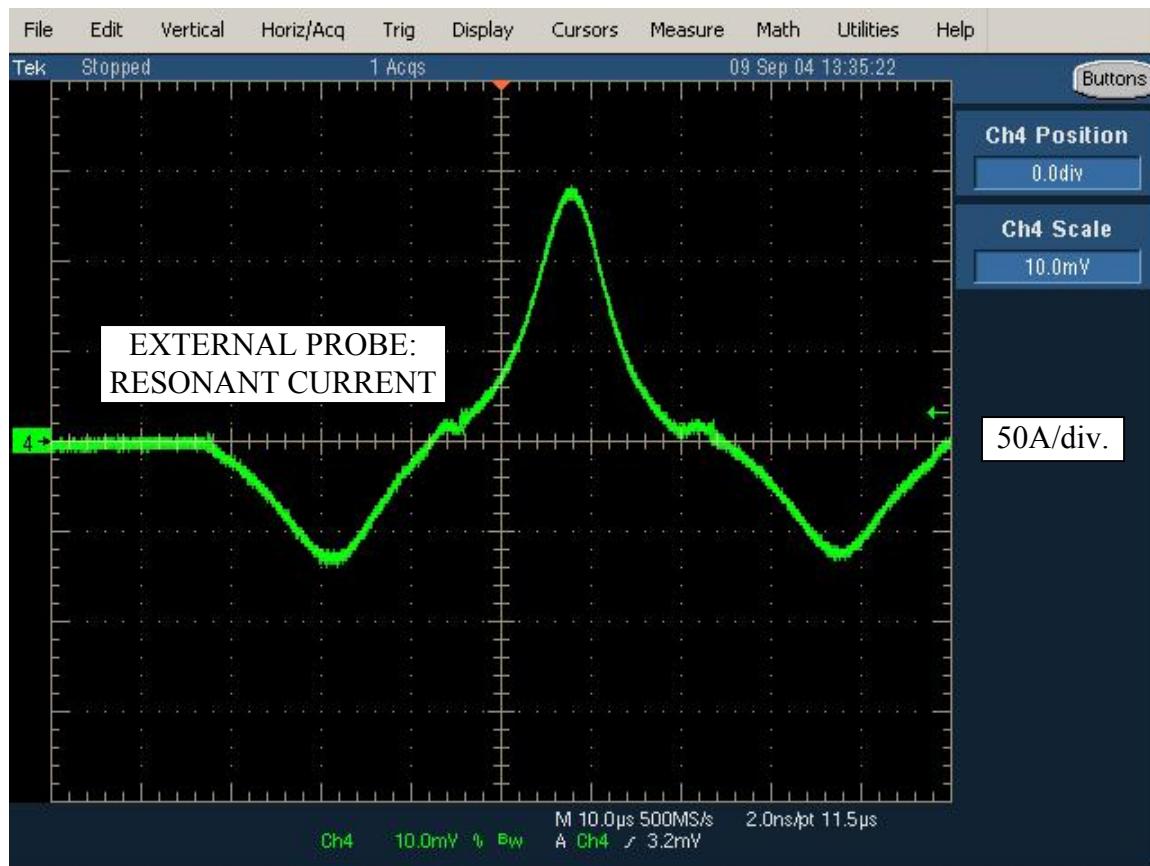

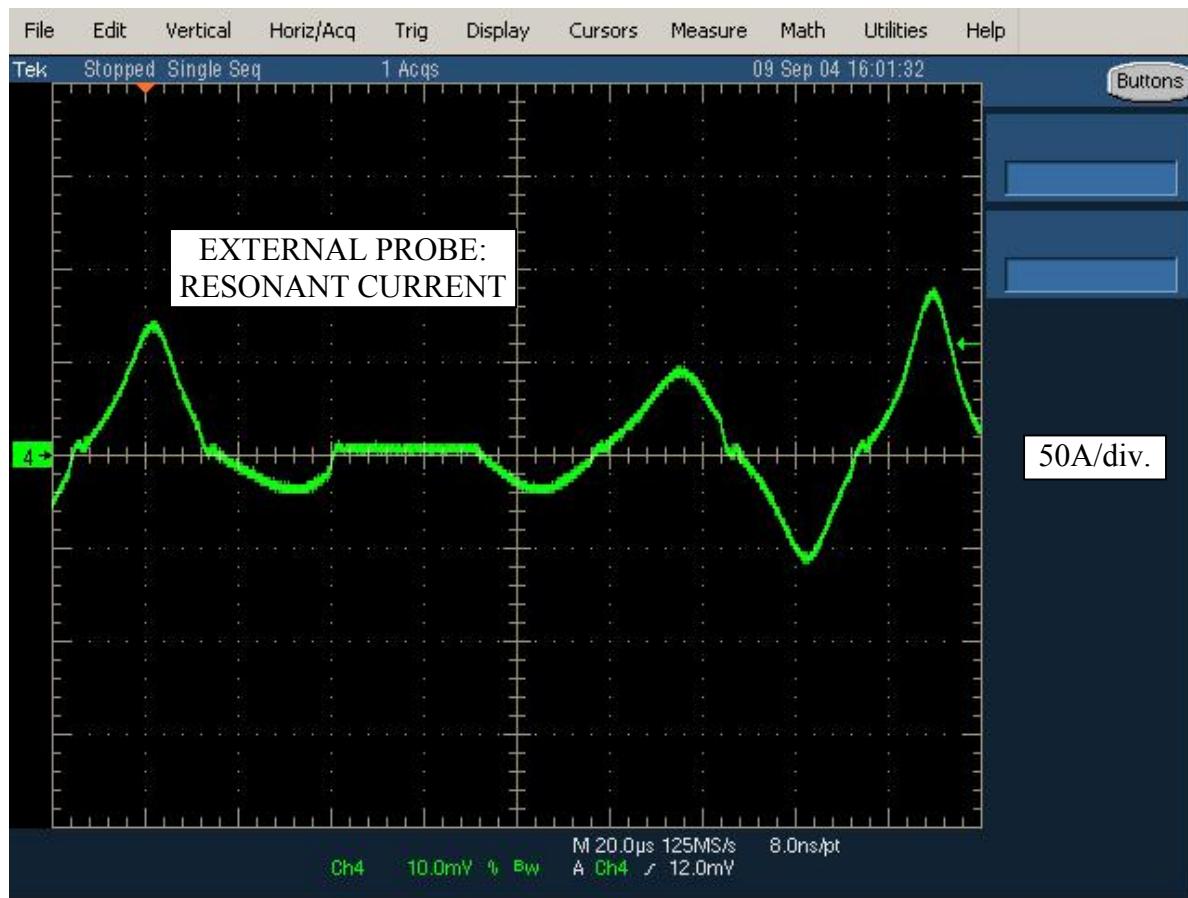

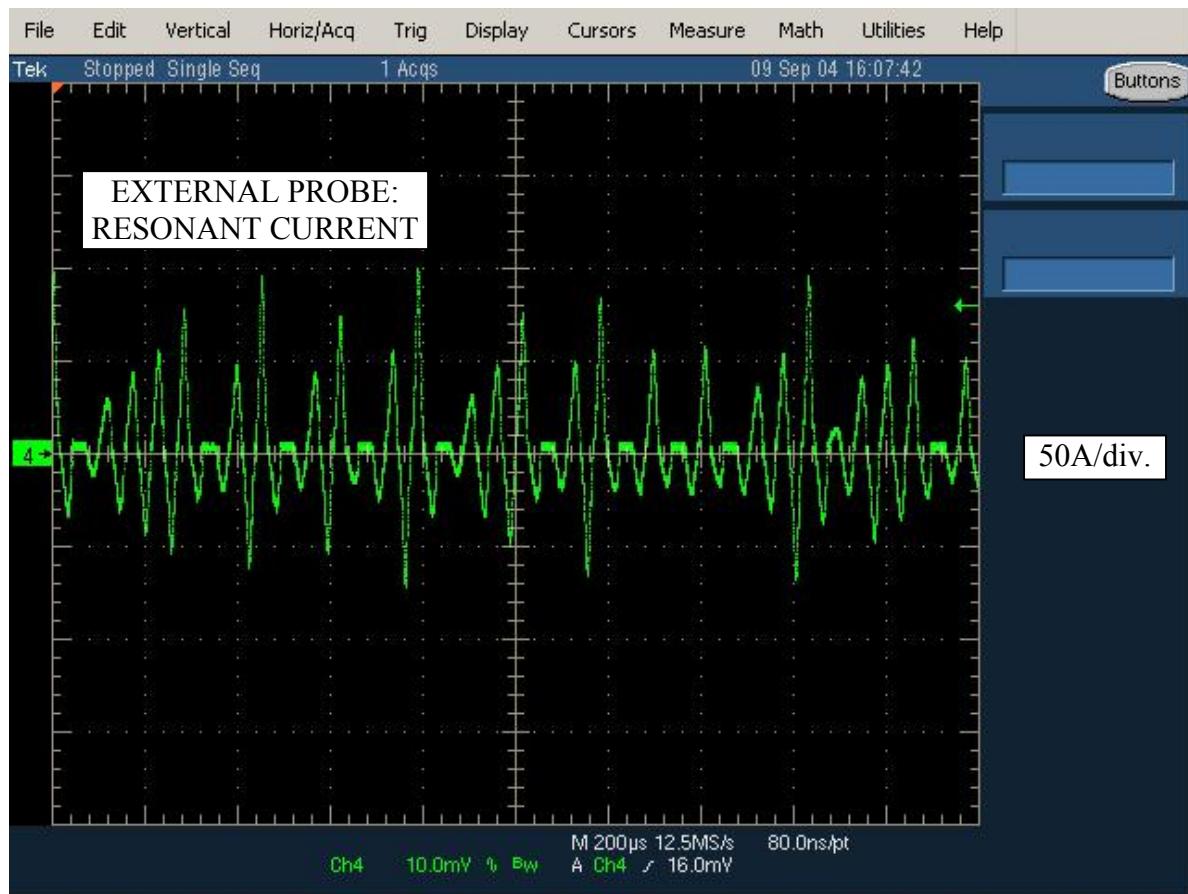

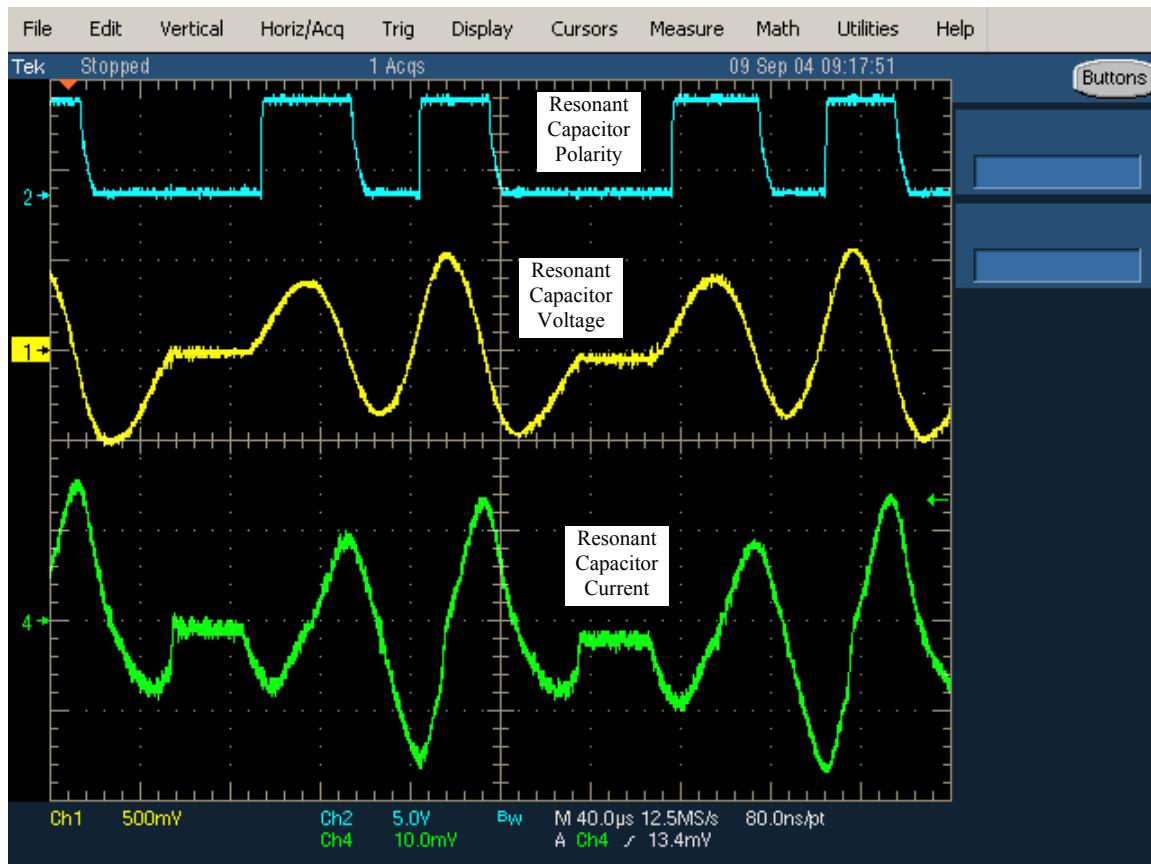

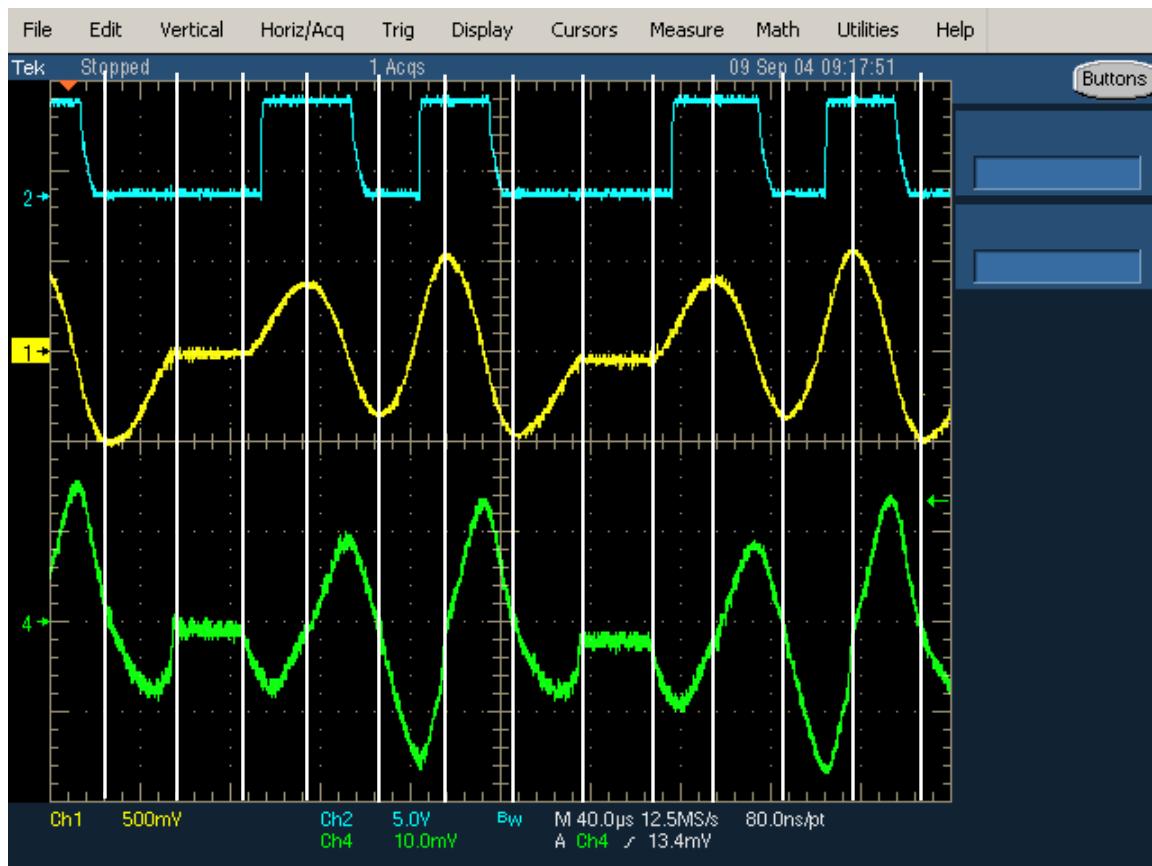

For the initial power-up, the input and output voltages were set at  $75V_{L-N}$  ( $130V_{L-L}$ ). The test points for the resonant current (IRMAG\_SIGN), the resonant crossing zero crossing (IRZC) and the resonant capacitor voltage (VRC) on the ETM Control Board as well as the direct measurement of the resonant current by current probe were monitored with a four channel oscilloscope. These points were initially monitored for any activity and close-too-normal operational waveforms, as well as for any abnormal, unexpected or transient behavior. A typical set of waveforms captured during this initial testing is shown in Figure C1.

This testing revealed that an excellent replica of the resonant current was obtained from the current transducer in the ETM Converter and this signal was further faithfully transmitted to the analog portion of the ETM Control Board. Figure C1 does demonstrate one of the debug issues encountered with the prototype at initial power-up: the fact that sense threshold of the current zero crossing signal was set too high (it can be seen that the first three low amplitude current zero crossings were “missed” by the IRZC detection comparator) and that the thresholds would need to be adjusted lower with a firmware change.

Data was collected to observe the typical operation of the converter in comparison with the expected operation, for example these reports: “Report #1”, “Report #2” and

**Figure C1. IRZC, IMAG\_SIGN and Measured Resonant Current Waveforms.**

“Report #3”, and this information was shared with the software/firmware programmers for their analysis and input. Additionally, if any abnormal or unexpected operating behavior was observed, then this data was captured in a report and analyzed for the root cause. Typical of this activity is the report titled “Four Cycle Hiccup Mode”, which details an unexpected resonant transfer event during the observed ETM prototype operation. Again, this data was shared with the software programmers for review analysis and action.

After minor revisions were made to the ETM Control firmware to correct the observed problems, the input/output (I/O) voltages were increased to 100V<sub>L-N</sub> and then to 150V<sub>L-N</sub>. At both these I/O points, the circuit was observed to be operating normally. It was at the 150V<sub>L-N</sub> operating point that an IGBT failure in the output switch matrix occurred. The ETM Converter prototype had operated more than five cumulative hours when the failure occurred. This failure, suspected to have been a random failure in a single IGBT, had the effect of damaging all four IGBTs in the output switch matrix (the three phase output and the ground switch devices), requiring their replacement for continuance of the testing. [Luckily there were four spares of the IGBTs and driver

boards remaining/available from the ETM Converter prototype build for the necessary repairs to be accomplished!]

With the repairs accomplished, the prototype Converter was again subjected to the  $75V_{L-N}$  I/O voltage test value in order to test the efficacy of the repairs. Unfortunately, after approximately 30 seconds of operation, the prototype Converter experienced another IGBT failure both the input and output stages. It was determined that a total of four (4) IGBTs were destroyed before the internal circuit breaker tripped. These failures necessitated the ordering of replacement IGBTs (in a quantity sufficient to support the remaining testing) and incurred a ten week lead time before their receipt.

Although replacement IGBTs had been ordered, after significant searching activities it was determined that four IGBTs that were of a similar device type were found in the UK, these devices were obtained, the driver boards were repaired and the ETM prototype was ready for test once again.

Once again, with the repairs accomplished, the prototype Converter was again subjected to the  $75V_{L-N}$  I/O voltage test value in order to test the efficacy of the repairs. This time, the Resonance Period time was set to 26.5 microseconds (the actual resonance time was determined to be 26us from previous measurements, see Figure C1) and the Cycle Period time was set to 28us. This action was performed to bring the firmware timing in line with the actual circuit performance. If this action were not done, there would be significant current flowing in the IGBTs when turning OFF depending upon the mismatch of the firmware resonance time and the hardware resonance time. It should be noted that the ETM Converter is by-design a zero current switching power converter, and to avoid excessive switching stresses and safe operating area (SOA) excursions the switches must open at or very near zero current.

Figure B1 demonstrated that the current zero crossing detector had a “dead spot” for lower magnitude resonant currents (measured to be less than 15A), so that it was critical that the firmware possess an accurate cycle time in light of the missing IRZC (zero crossing) signal. It was determined that the software allowed for a condition whereby a fixed resonance time IGBT switching event could not be guaranteed in the absence of the IRZC signal, and this condition existed during testing after the first failure

repair. It is believed that this software bug relating to resonance timing and switching caused the second failure observed during the debug testing.

However, at the power-up of the repaired ETM prototype, the internal circuit breaker tripped and it was determined that all four IGBTs in the input switching matrix were damaged. It was determined that this failure was caused by the fact that although a change in the Cycle Time or Resonance Time may have been accomplished via the GUI, there was no confirmation or update of the GUI parameters. Additionally, it was determined that there was no guarantee that the parameter data was properly exchanged between the host laptop and the dsPIC/ADSP microcontrollers in the ETM Converter after a change was initiated. The reason the particular failure occurred was that a value of 15us was somehow entered as the value of the Cycle Time,  $T_{cyc}$ . With this value, the IGBT switches would have been forced to open while carrying their maximum resonant current. This action subjected the switched IGBT to stresses exceeding their maximum ratings. This is a grievous flaw, and was immediately corrected with a revision to the GUI software and the microcontroller firmware to signal (as an indicator on the GUI) that matching values did not exist in microcontroller memory and in the GUI value registers.

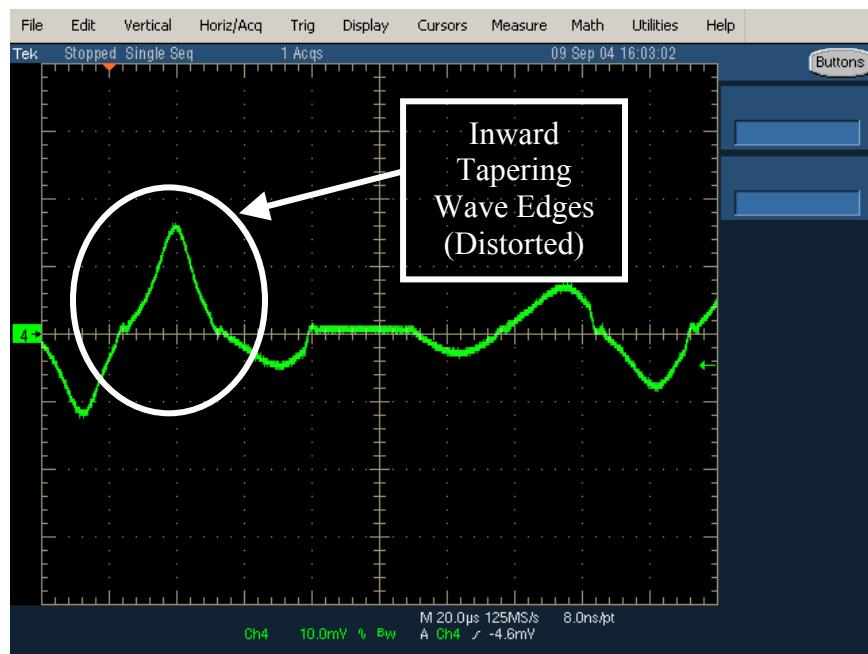

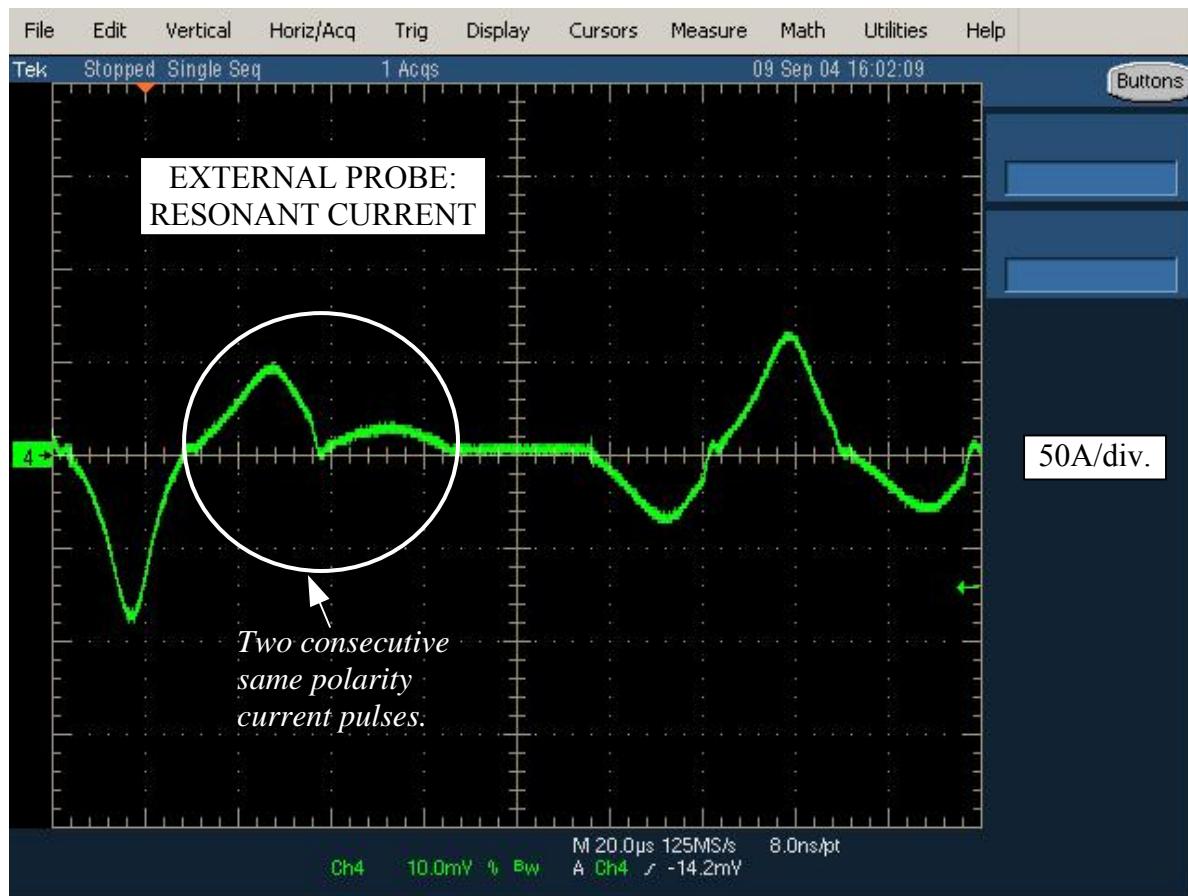

The last failure encountered guaranteed that there would be a ten to twelve week hiatus in testing while waiting for the replacement IGBTs to arrive. It was decided to use this time as an opportunity to re-design and replace the resonant inductor in the ETM prototype. Observation of individual high current resonant pulses indicates that the shape of the pulse is not a true sinusoid, as expected. Rather, the actual pulses exhibited inward-tapering edges. This waveshape indicated nonlinearity in the magnetic material used, or an inadequate core size (see Figure C2). A new inductor was specified, procured and installed in the ETM prototype prior to the receipt of the IGBTs. The improved inductor is shown in Figure B3 and installed in the ETM prototype in Figure C4.

**Figure C2.** Nonlinear Resonant Current Pulse.**Figure C3.** Improved Resonant Inductor.

**Figure C4. Improved Resonant Inductor Installed In ETM Prototype.**

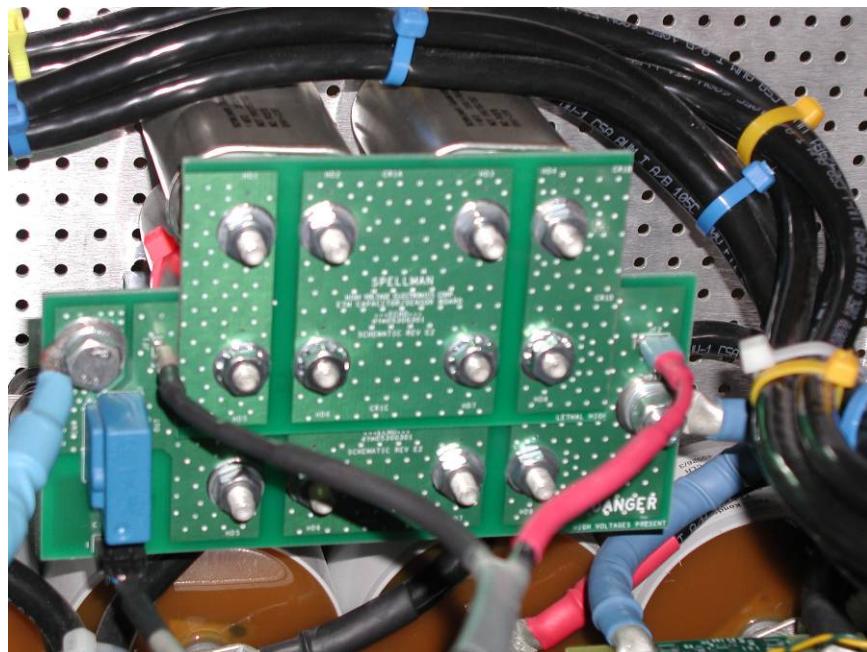

Before any further testing commenced after the IGBT failure repairs, it was decided to lower the power train resonance from the observed 26 microseconds to the design goal of 20 microseconds by connecting an additional 1uF resonant capacitor in parallel to the existing capacitors to increase the overall value (see Figures B5 and B6). With the new inductor ( $L_r = 36.2\mu H$ , measured) and the modified capacitor ( $C_r = 1.49\mu F$ , measured), the power train resonance was calculated to be 23.1 microseconds.

Finally, during the initial debug test period, there were numerous minor changes made to the values of components on the Analog and Digital ETM Control Boards in order to fine tune performance (e.g. filter breakpoints), improve performance (higher slew rate amplifiers) or add additional power supply bypassing, as observed during the debug test cycle. Coinciding with the hardware changes were several firmware changes to optimize the conversion algorithm and switch-state sequence table, as well as a makeover of the GUI interface to add adjustability for the parameter IOSF and improvements in the data gathering and subsequent display of the phase voltage/frequency operating parameters.

**Figure C5.** Increased ETM Power Train Resonant Capacitance.**Figure C6.** Increased Resonant Capacitance In The ETM Converter Prototype.

## ii.) Performance Testing (12/23/04 to 3/10/05)

After the repairs to the IGBTs and the revisions to the ETM Control Board from the last set of hardware failures, it was determined that the hardware and firmware were robust enough in operation to support the commencement of performance testing. The test philosophy adopted was to start the performance testing at low I/O voltages ( $75V_{L-N}$ ) and then increase the amplitude(s) in 50V steps until the design value of  $230V_{L-N}$  ( $400V_{L-L}$ ) is achieved. The actual resonance time was measured and found to be 21.5us (as opposed to the calculated 23.1us), and the GUI control parameters were set accordingly.

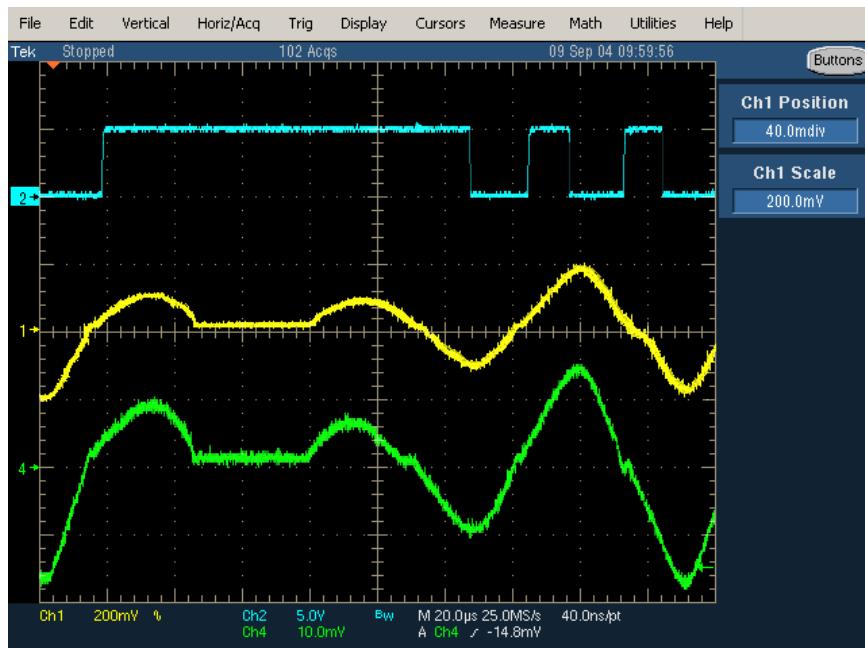

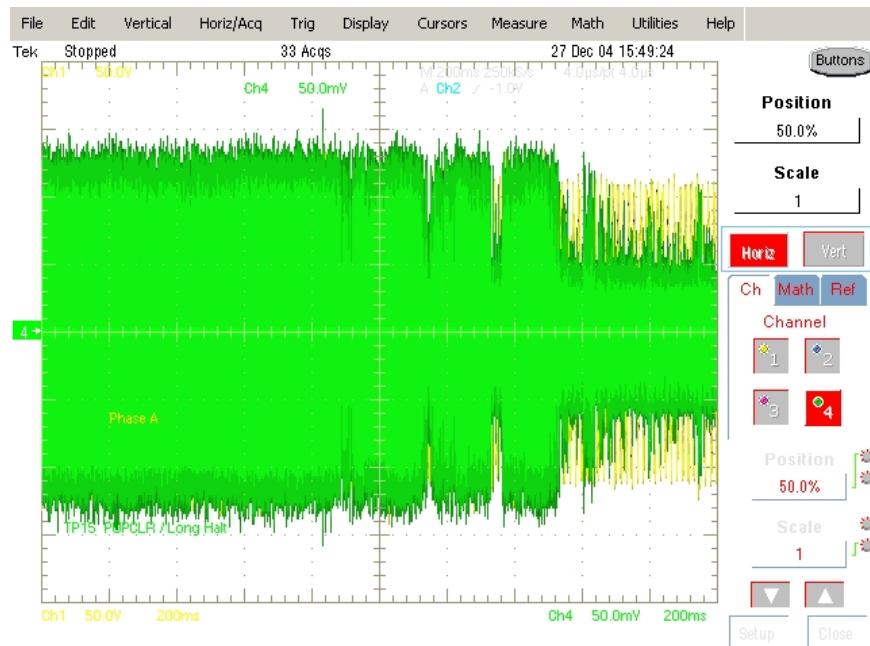

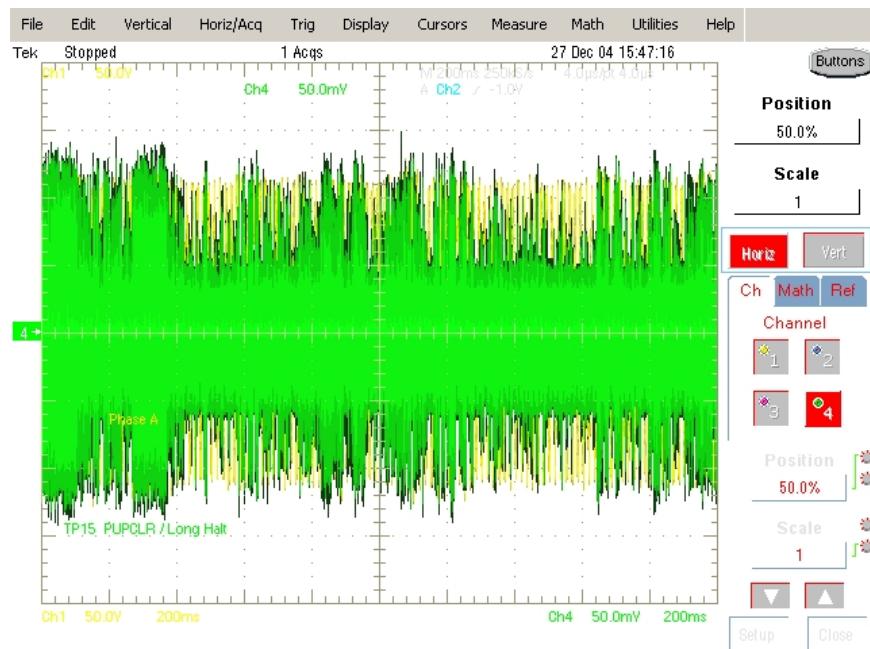

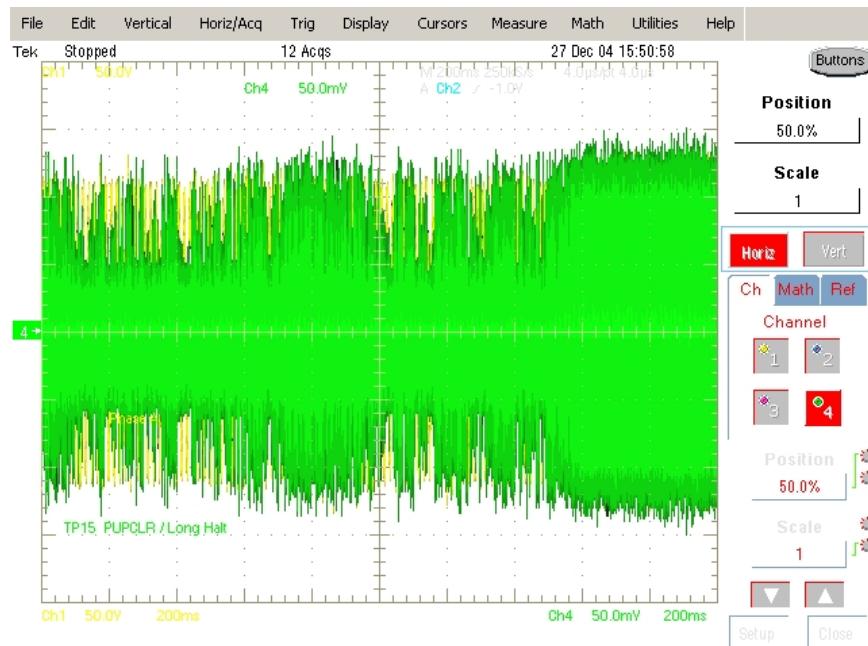

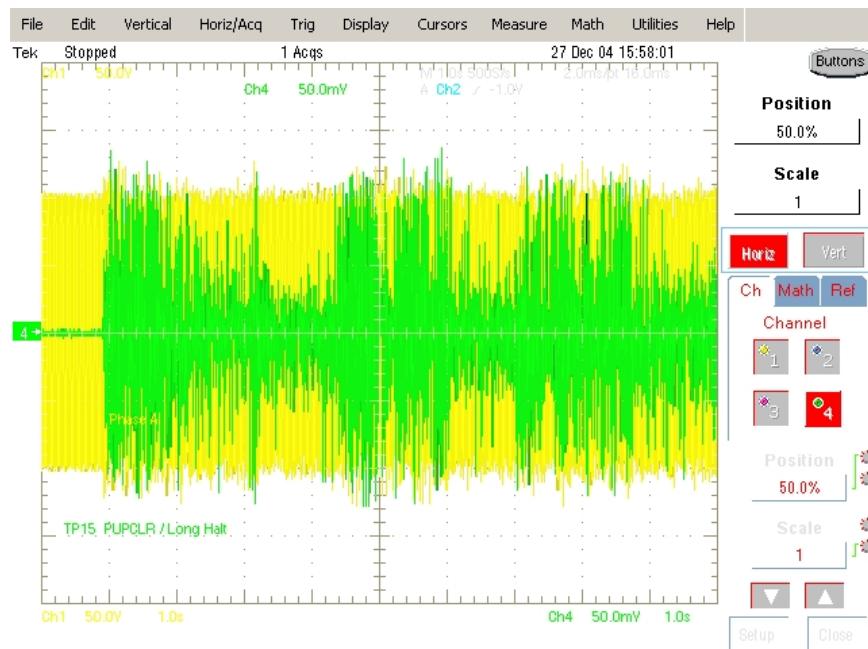

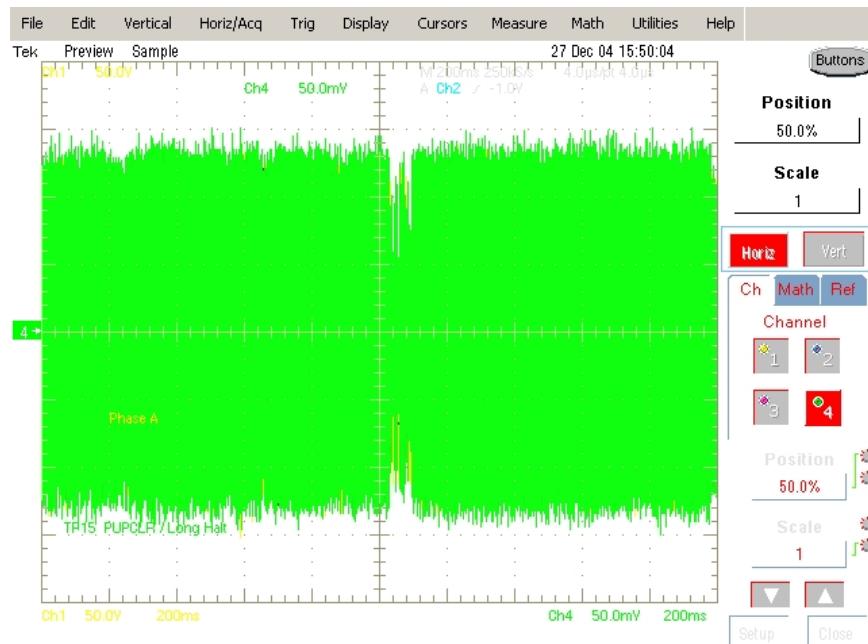

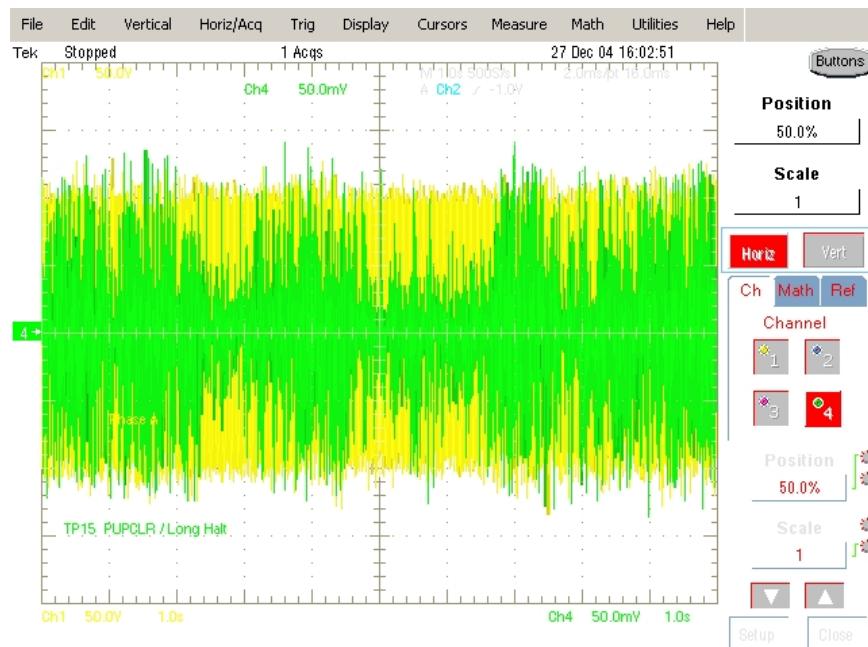

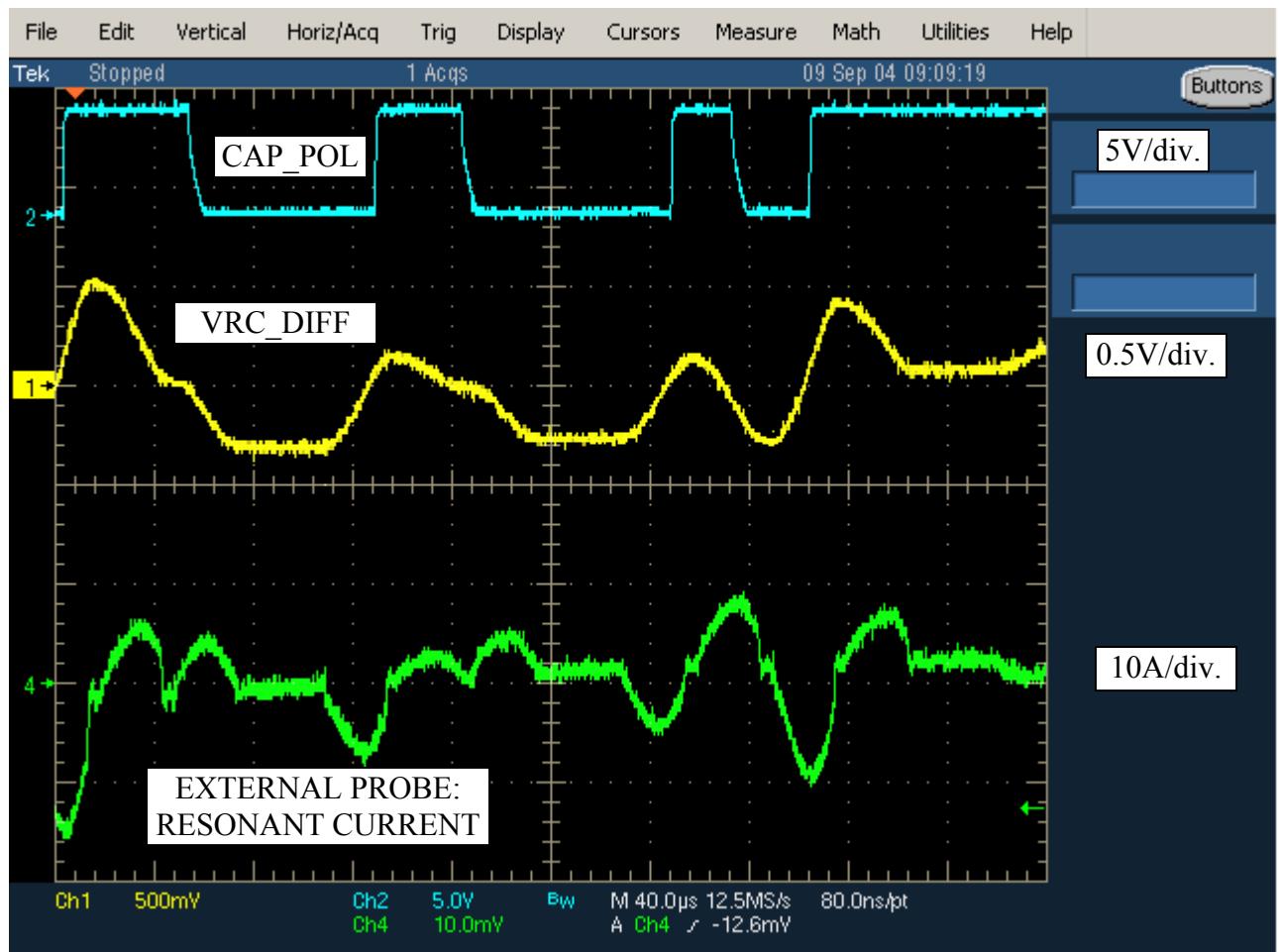

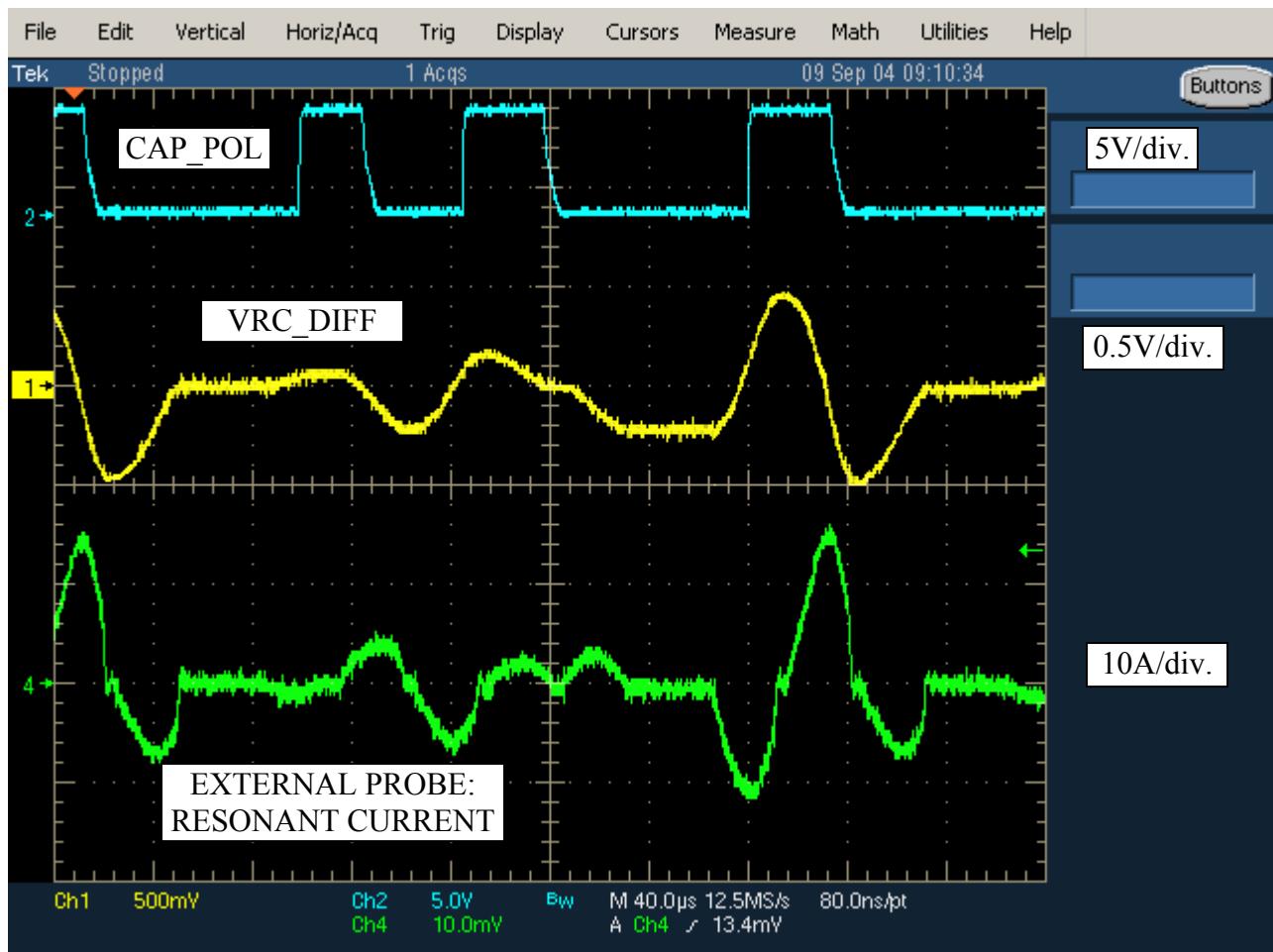

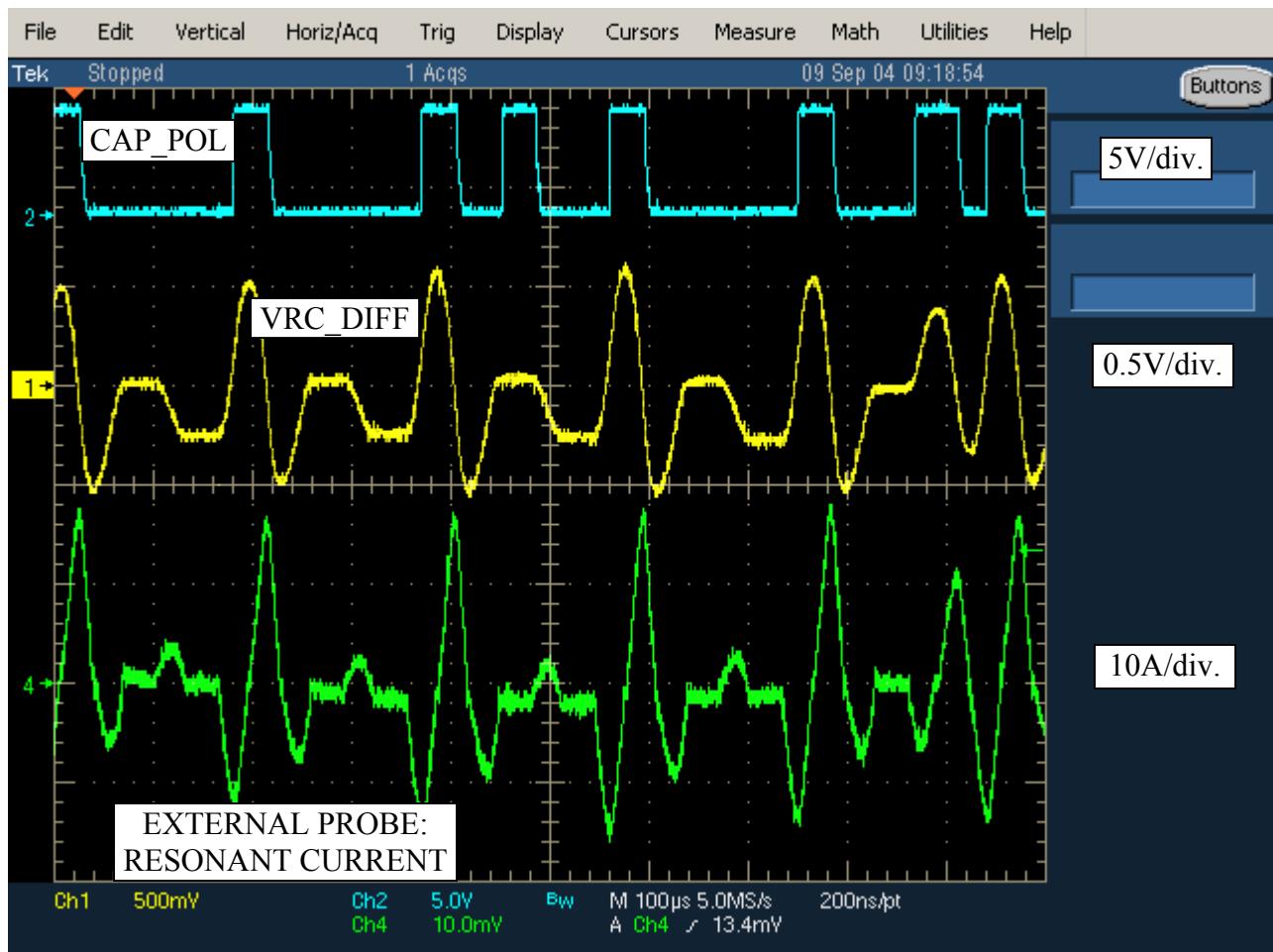

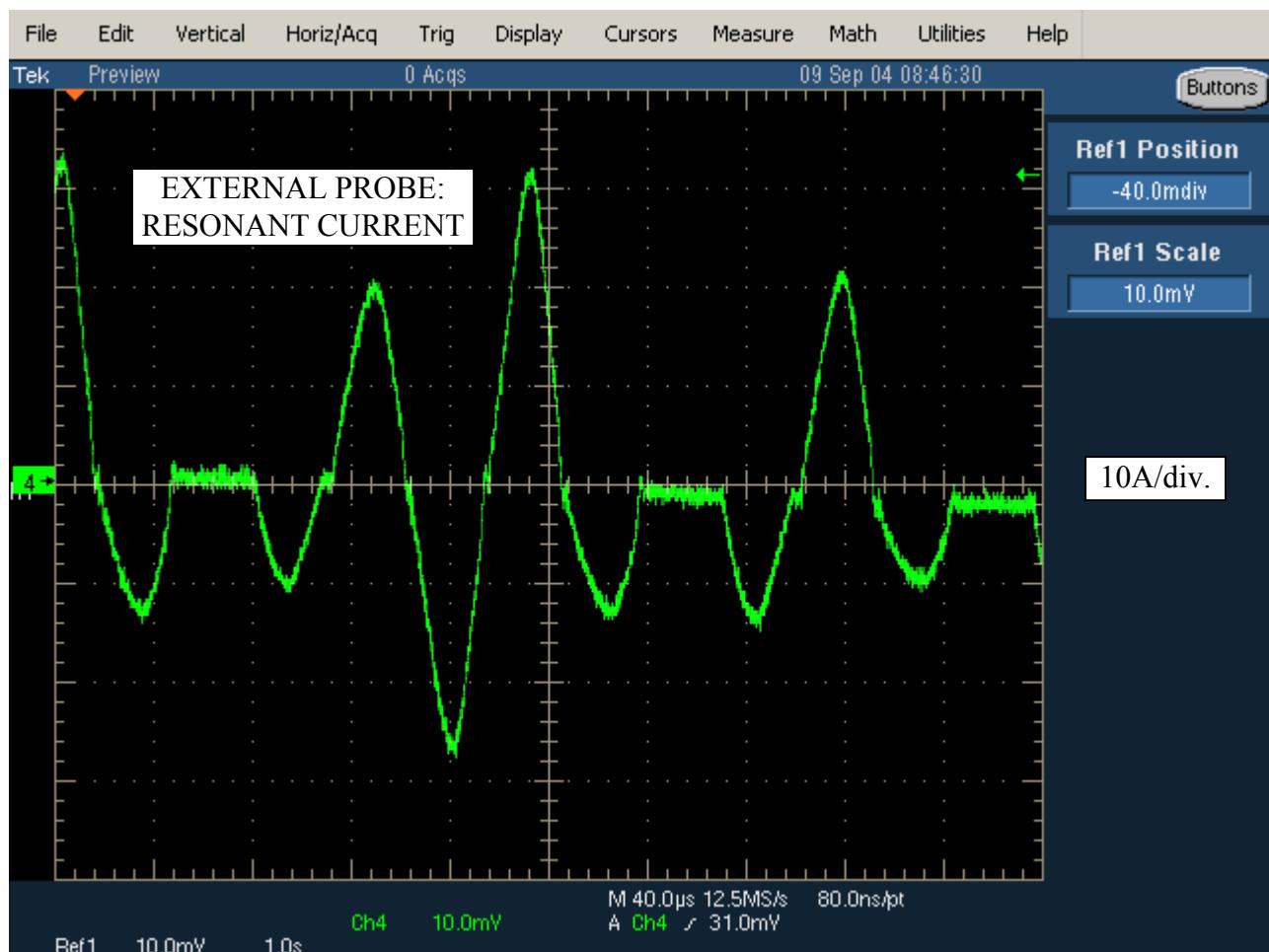

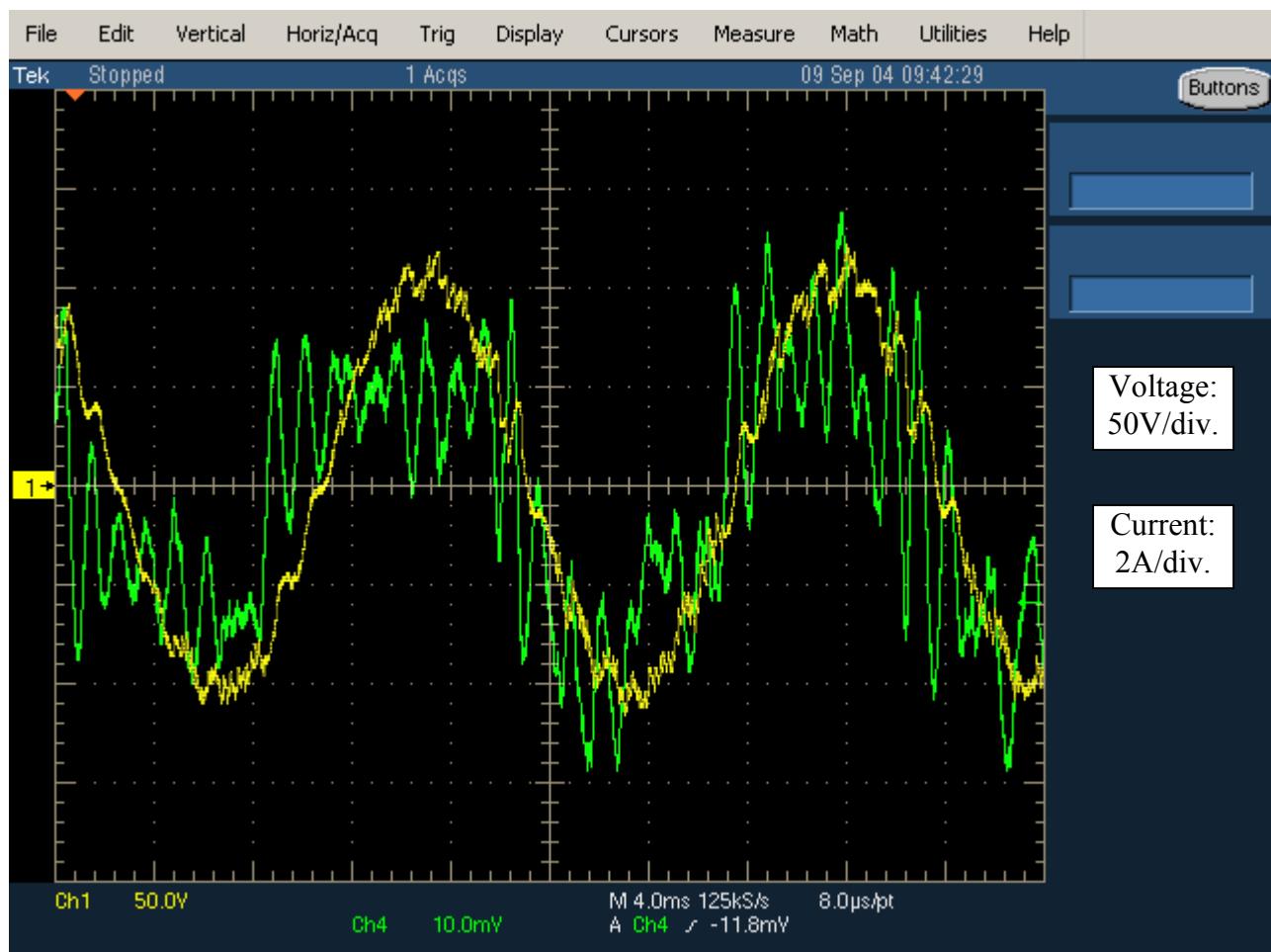

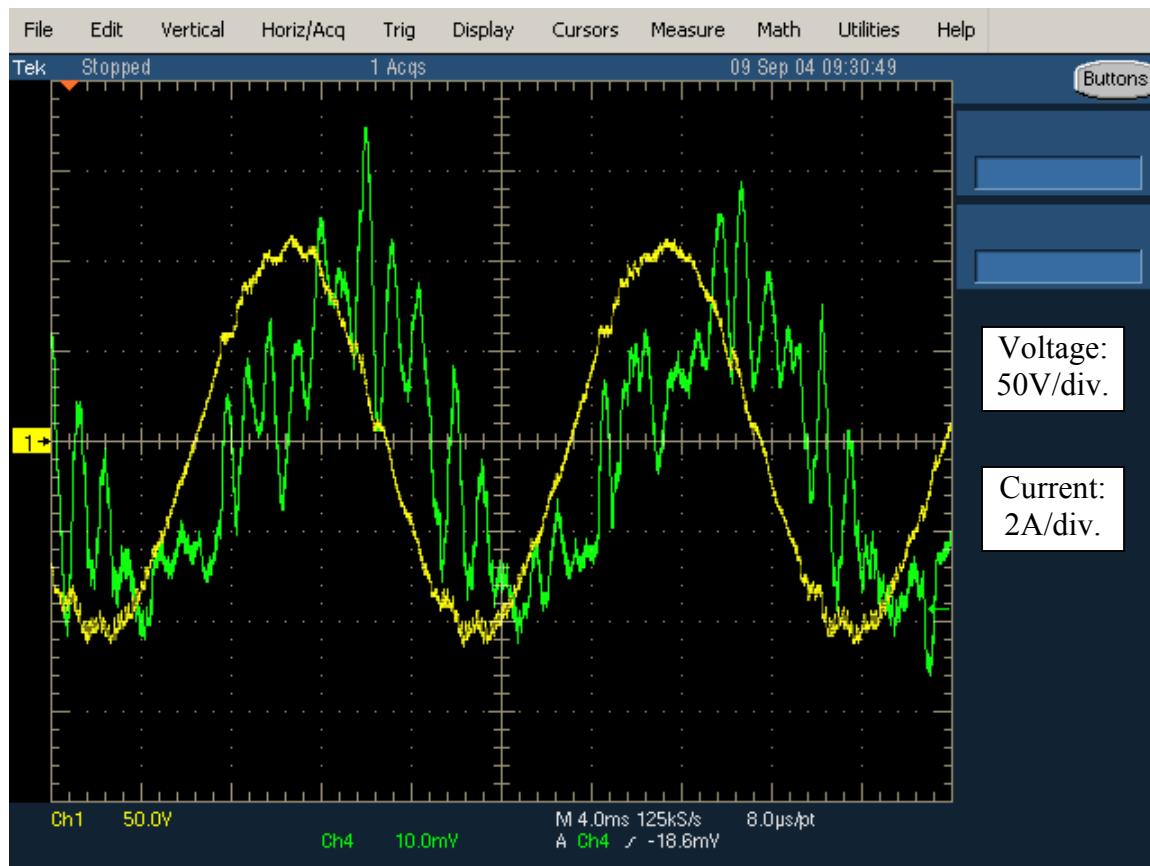

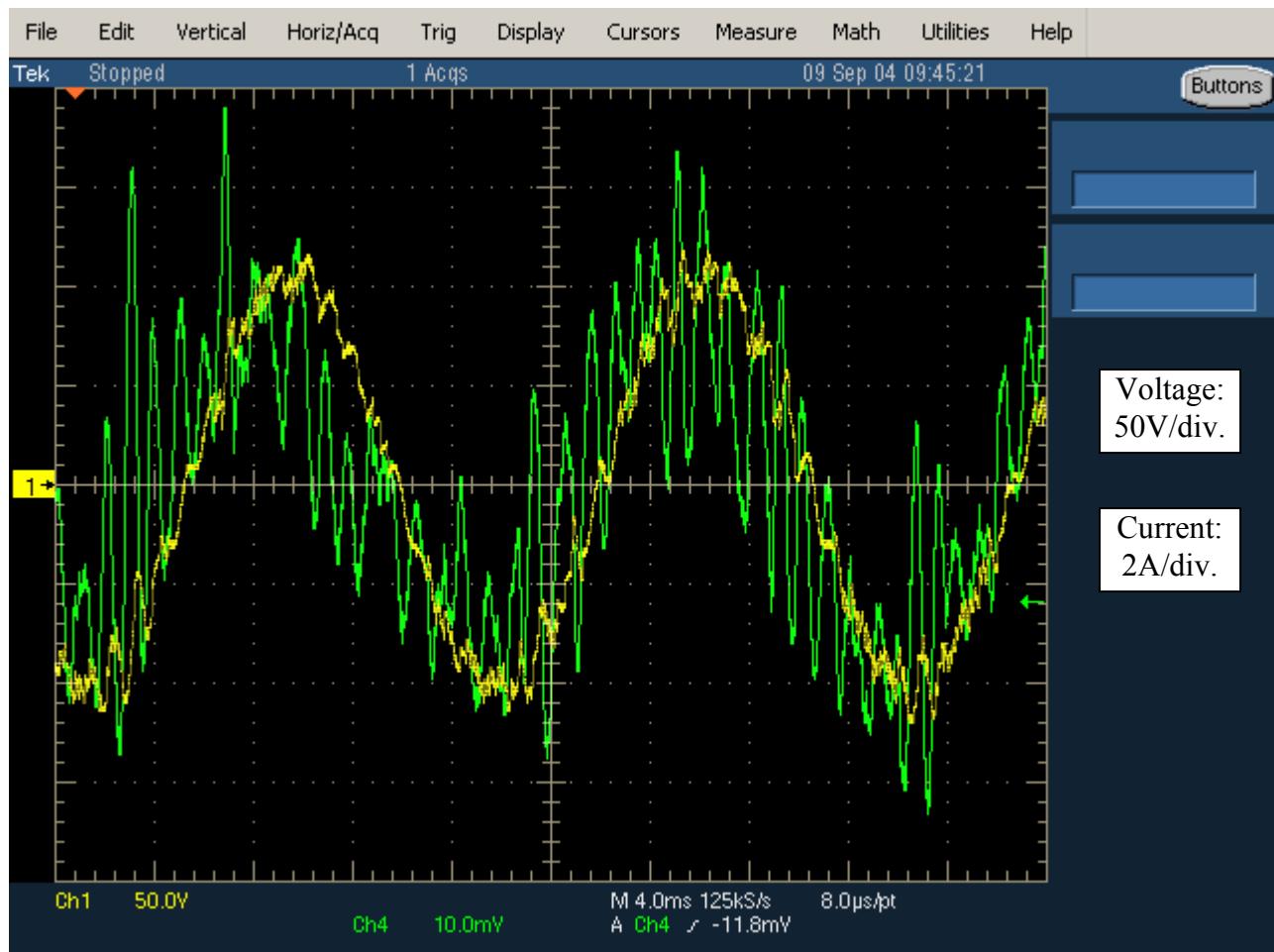

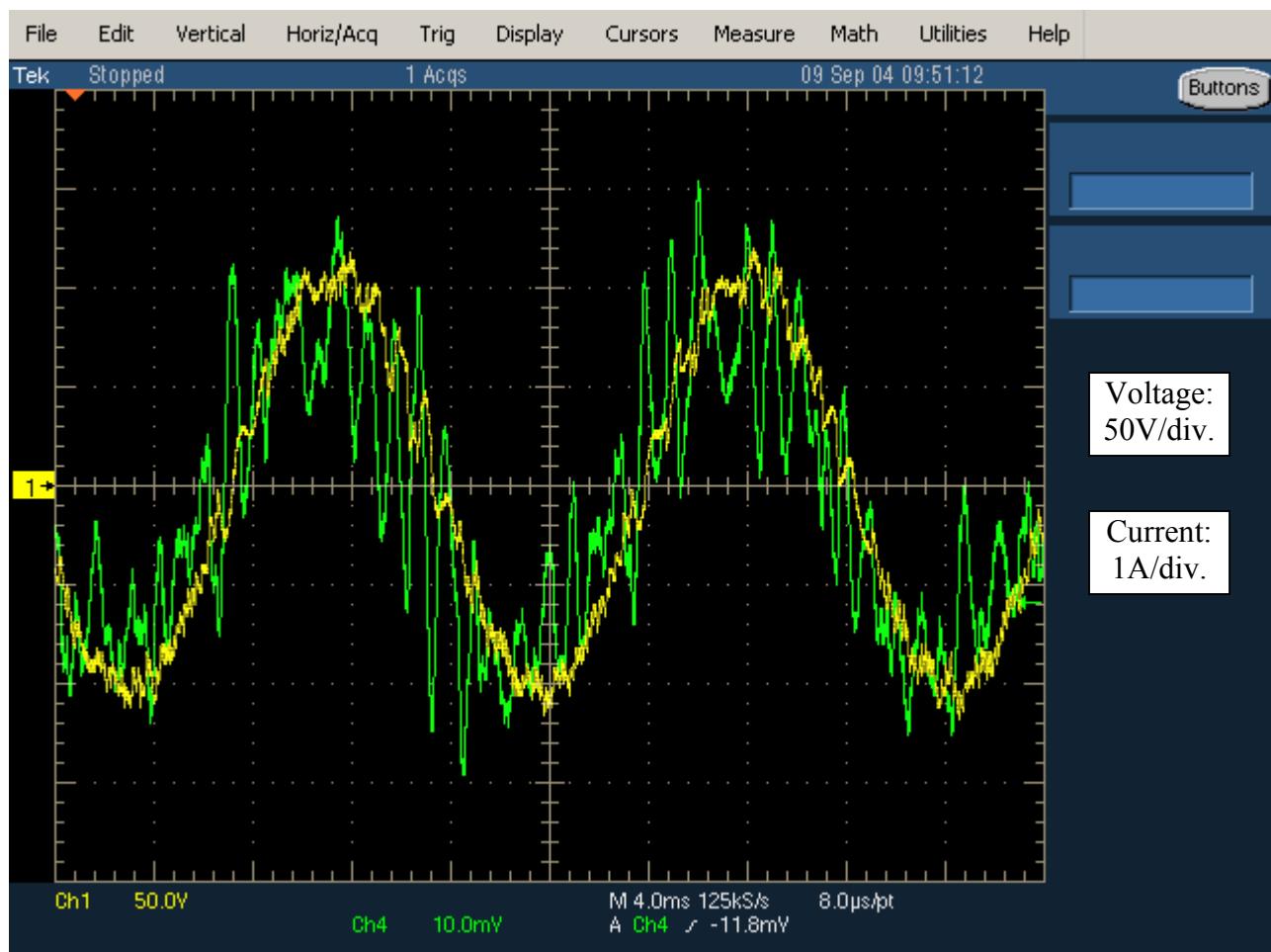

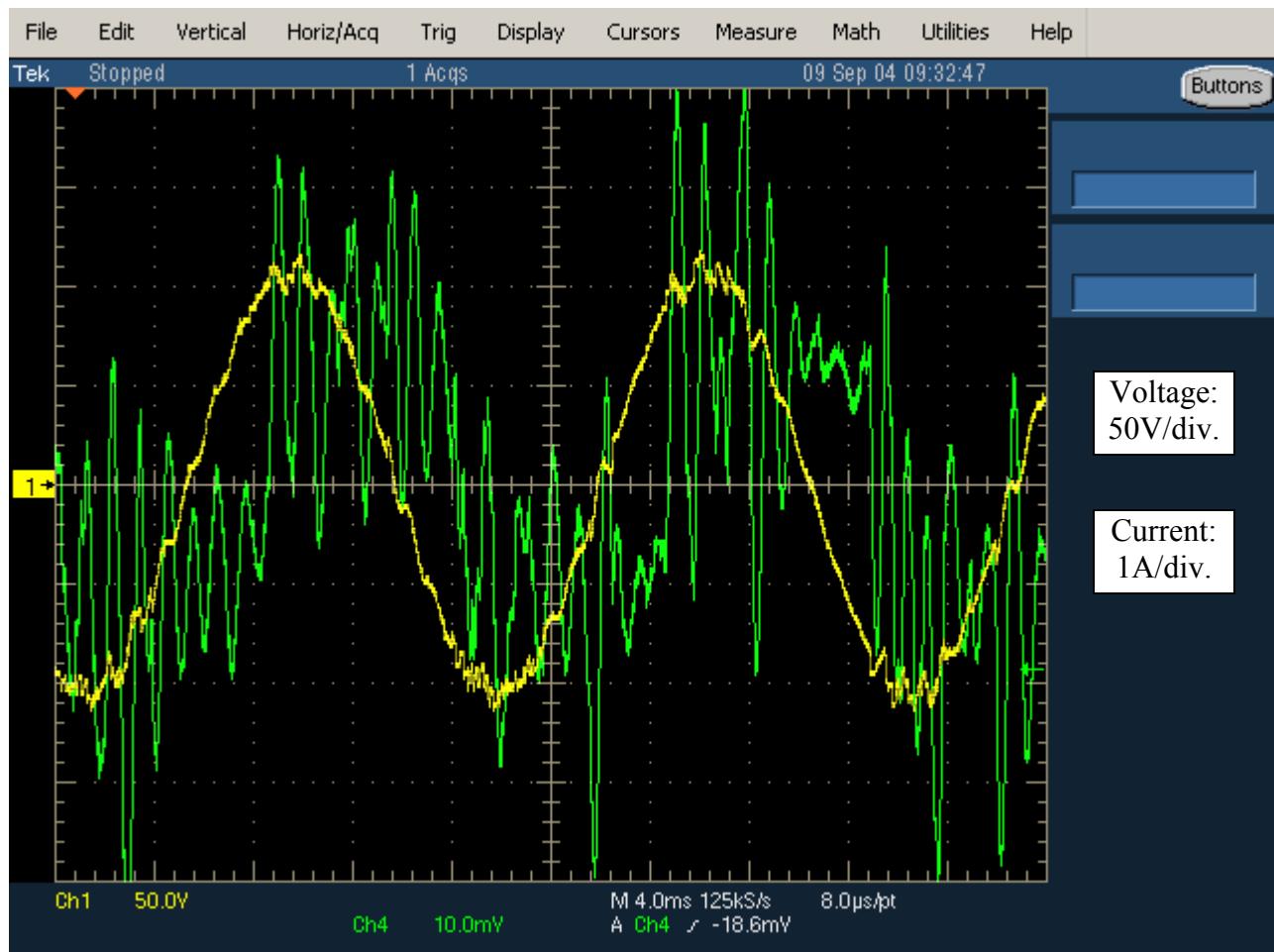

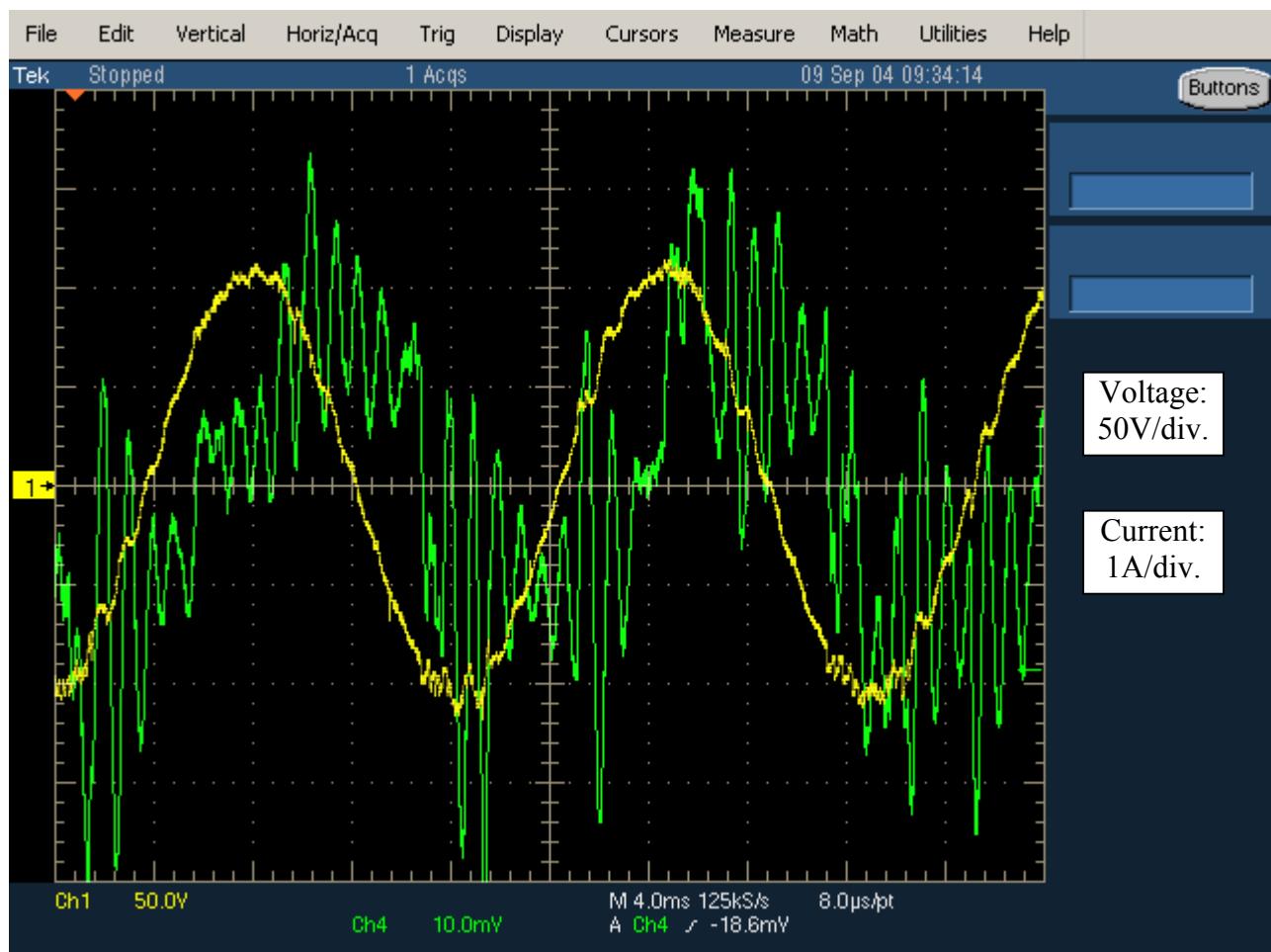

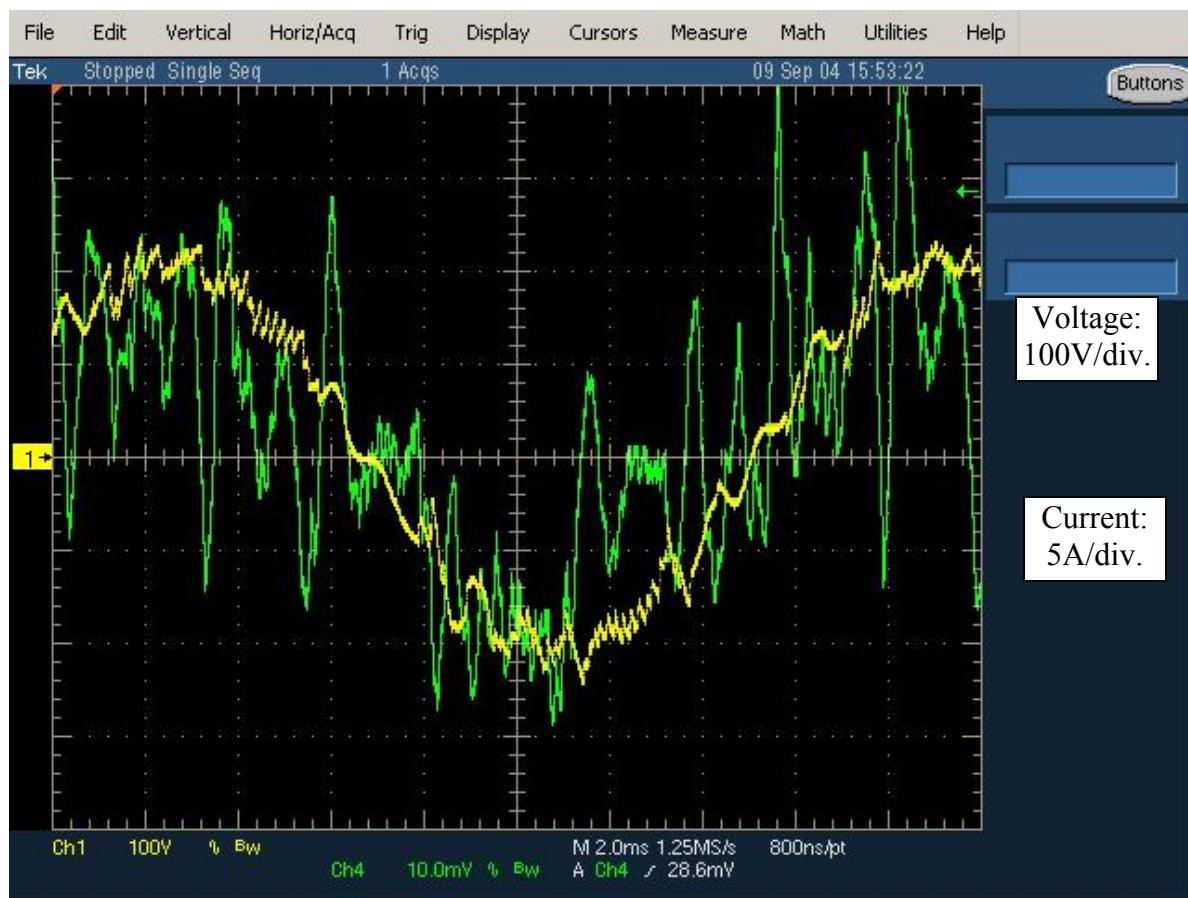

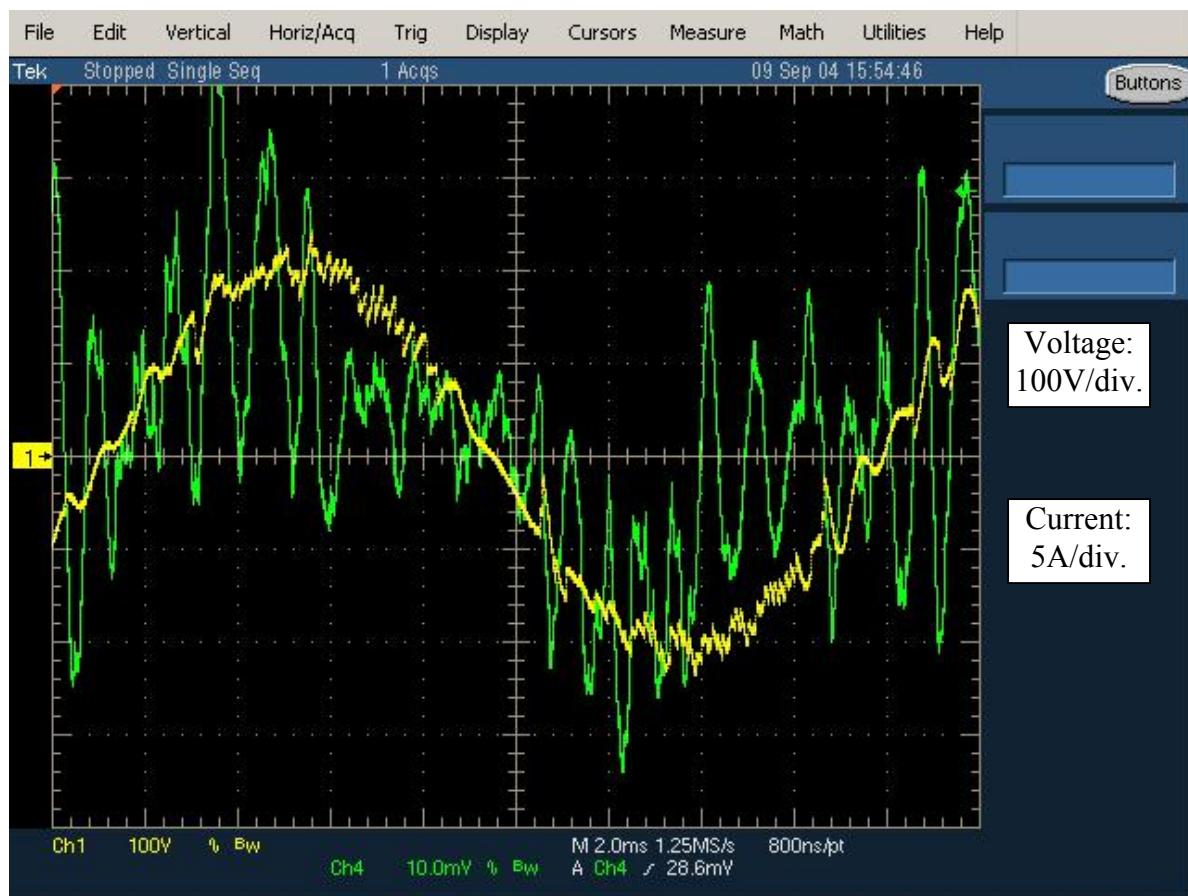

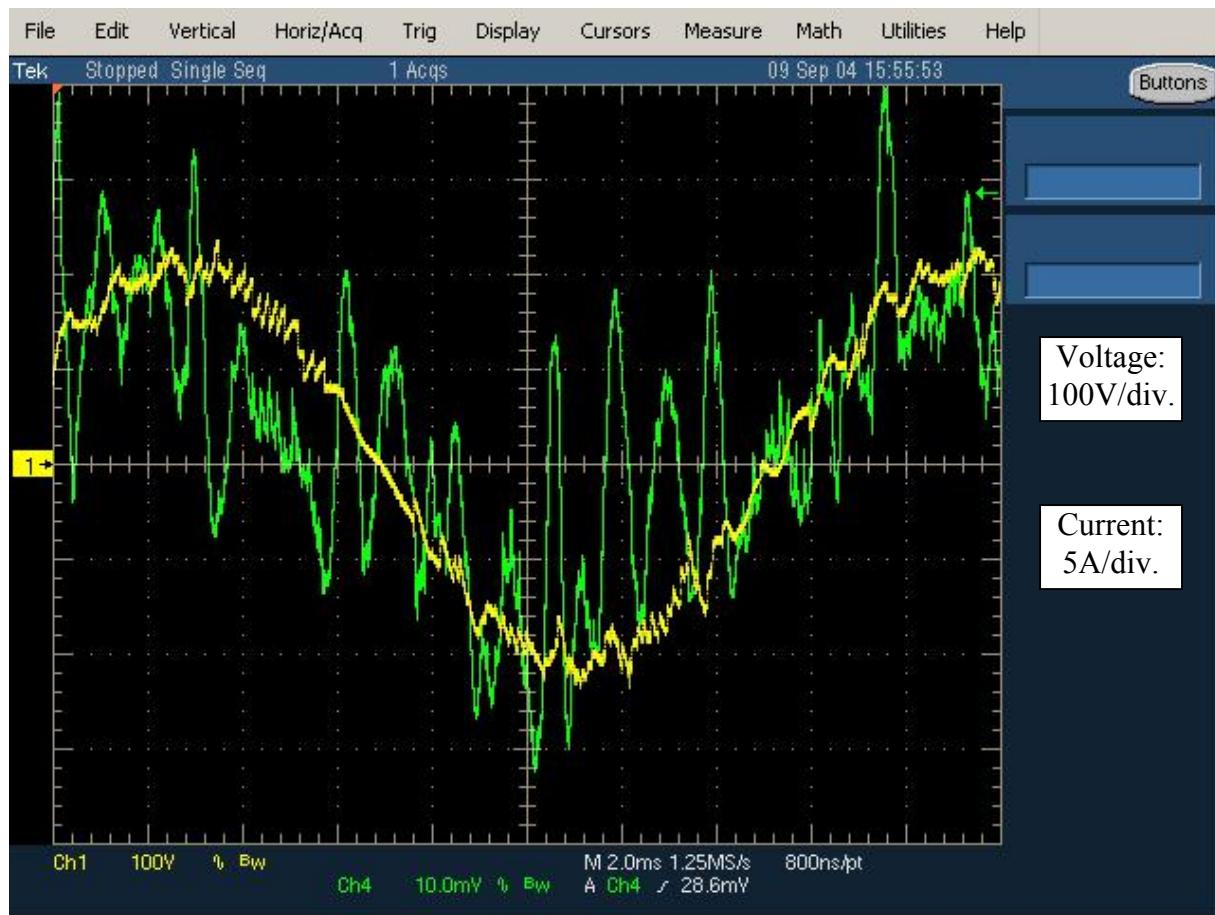

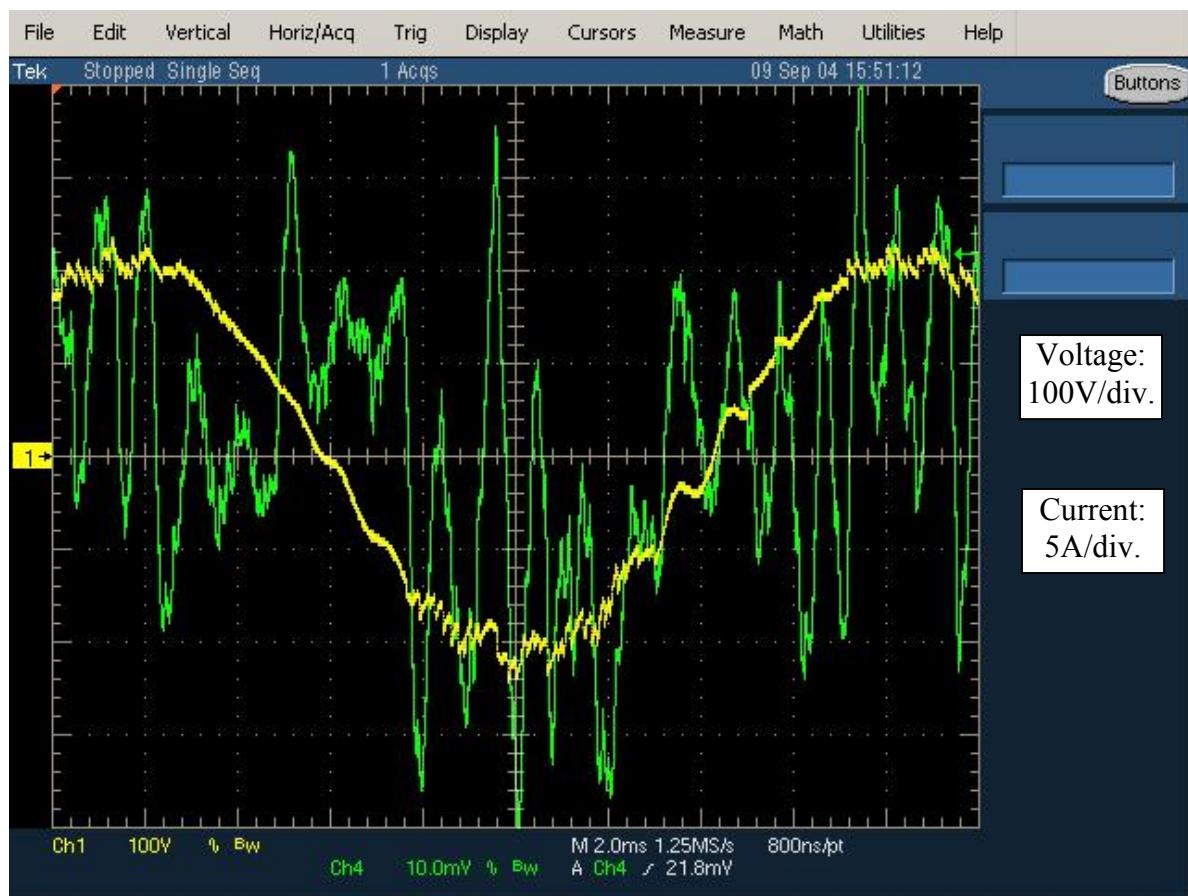

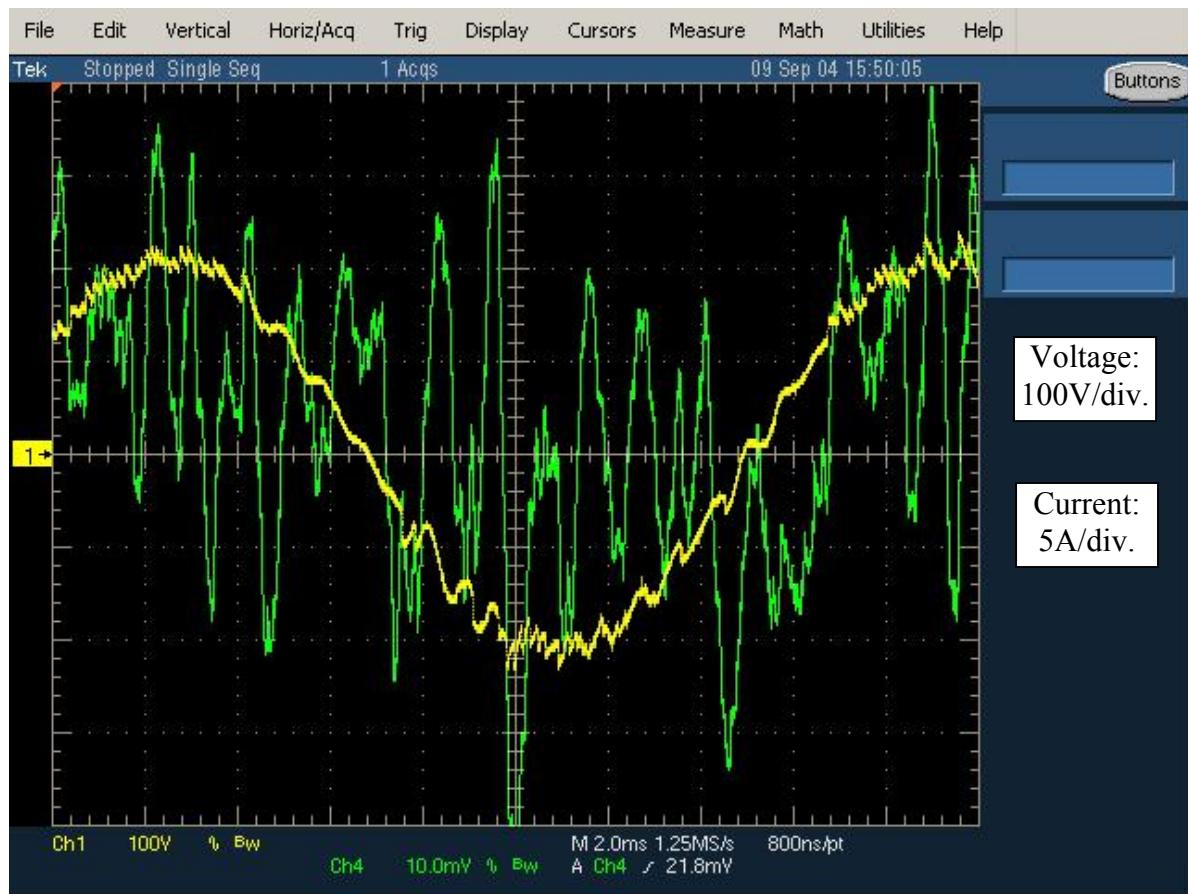

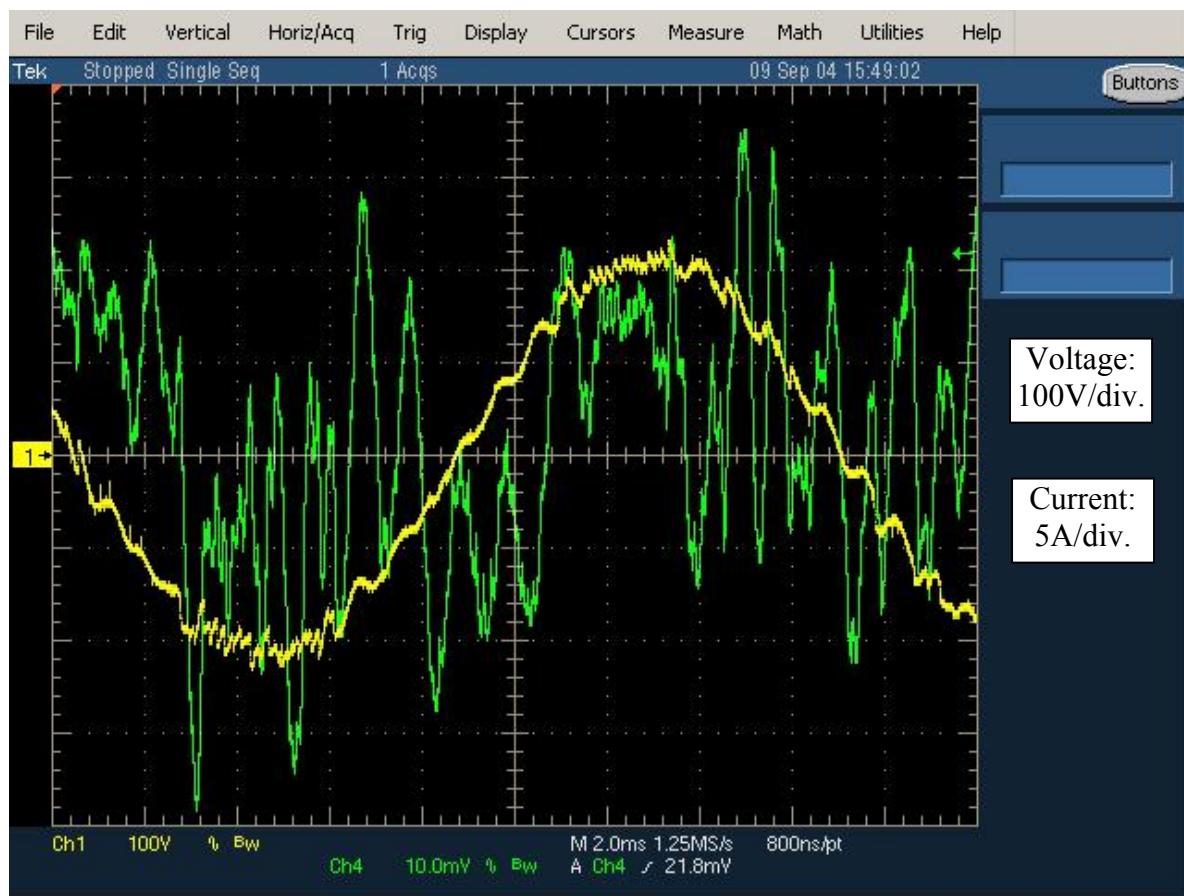

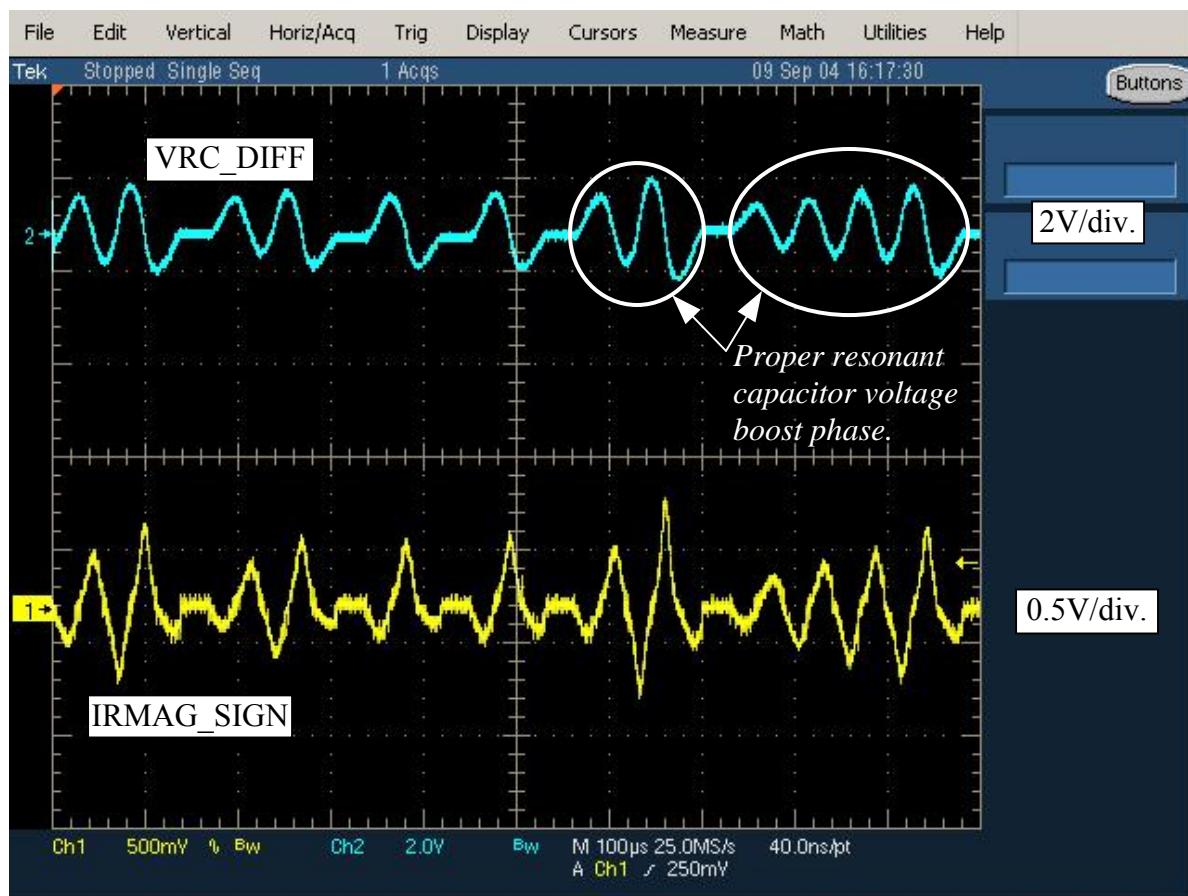

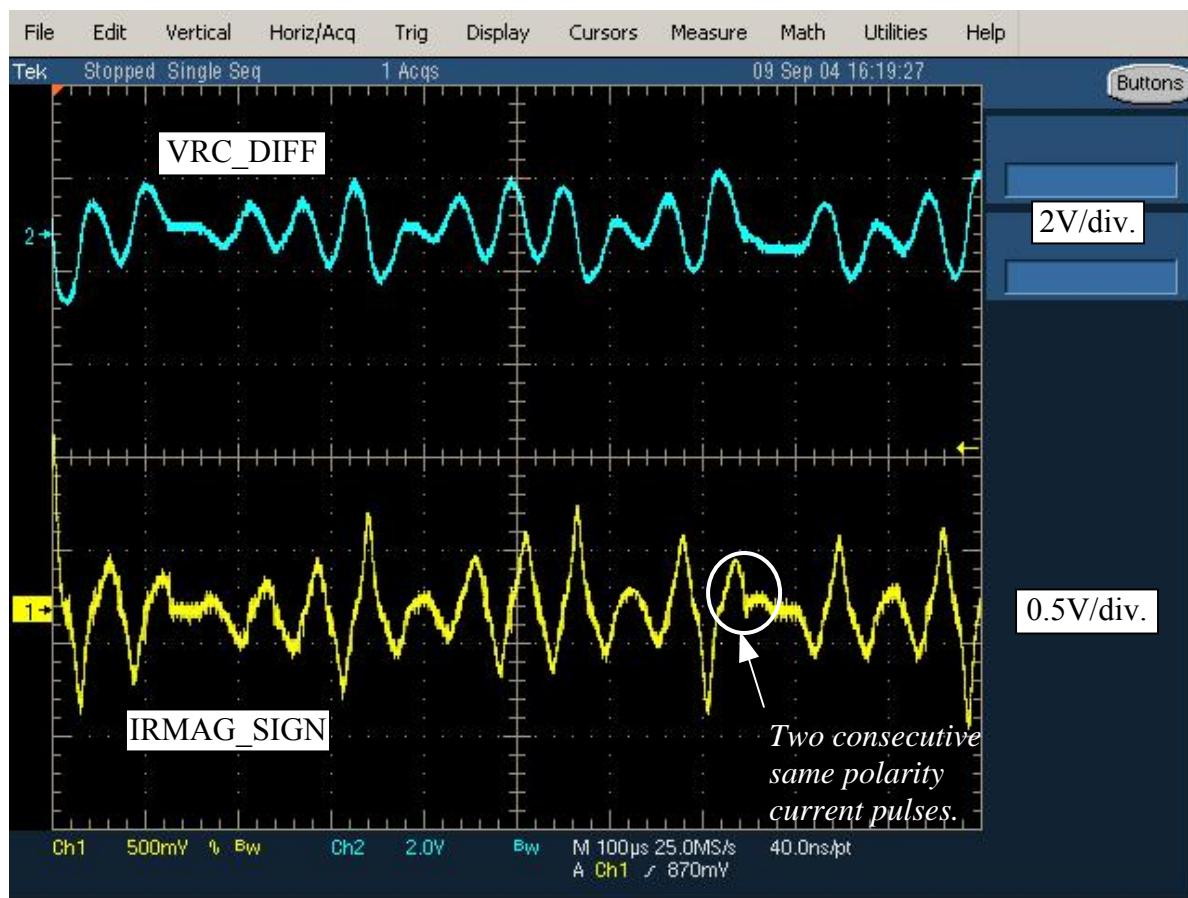

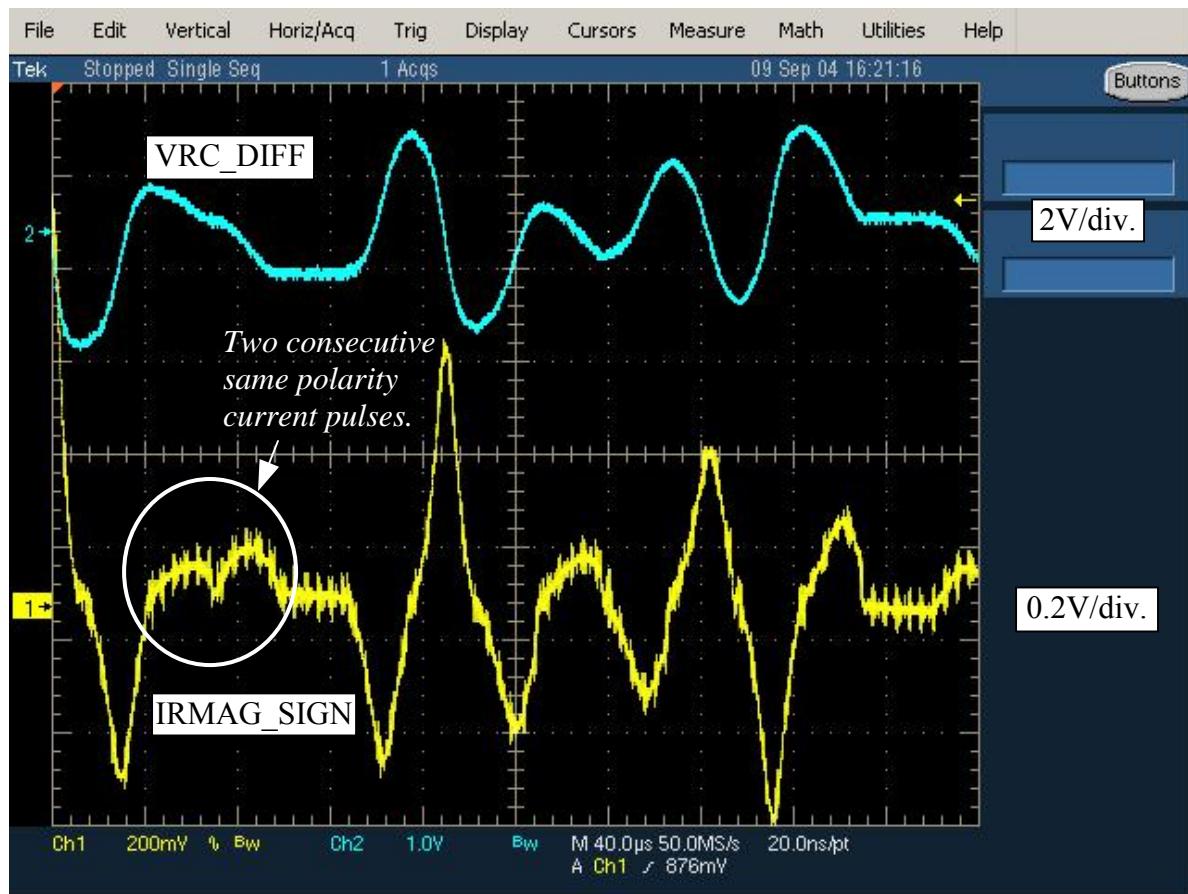

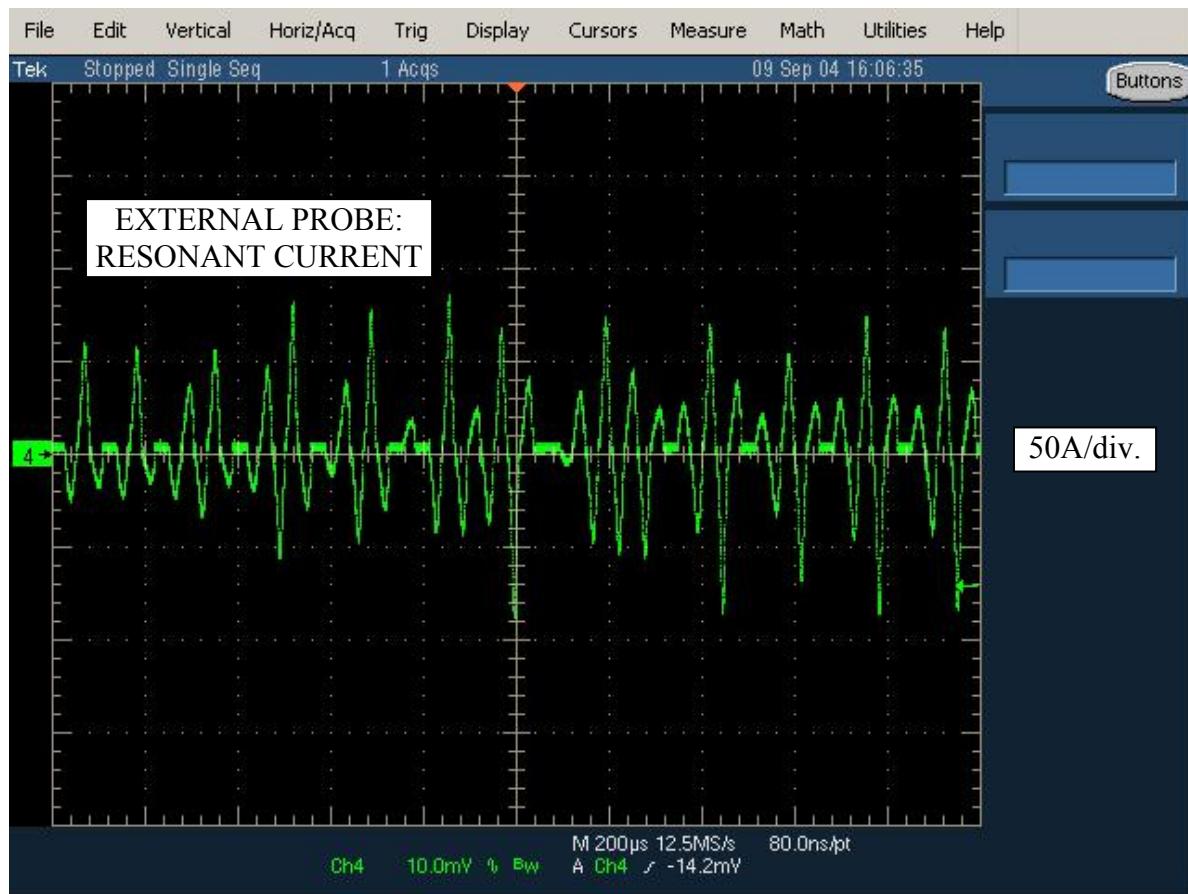

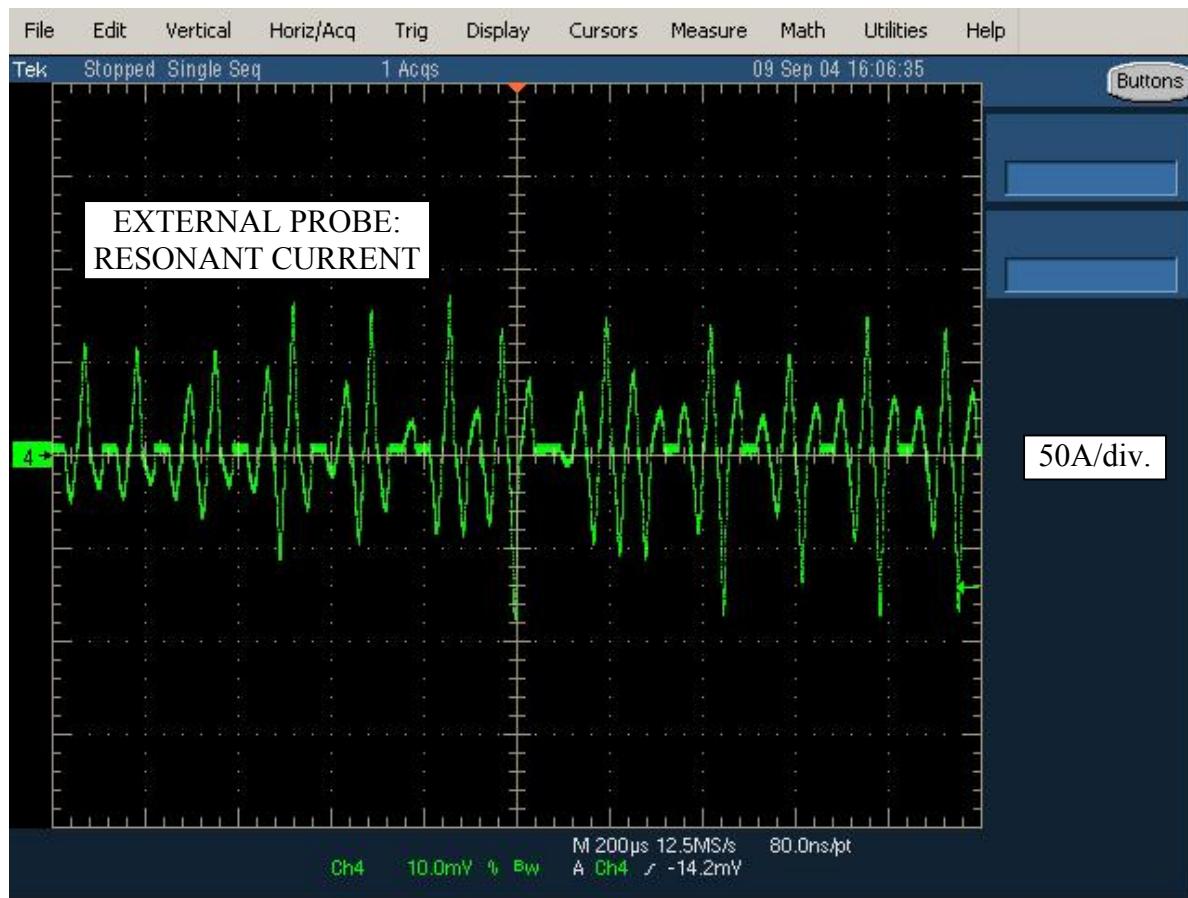

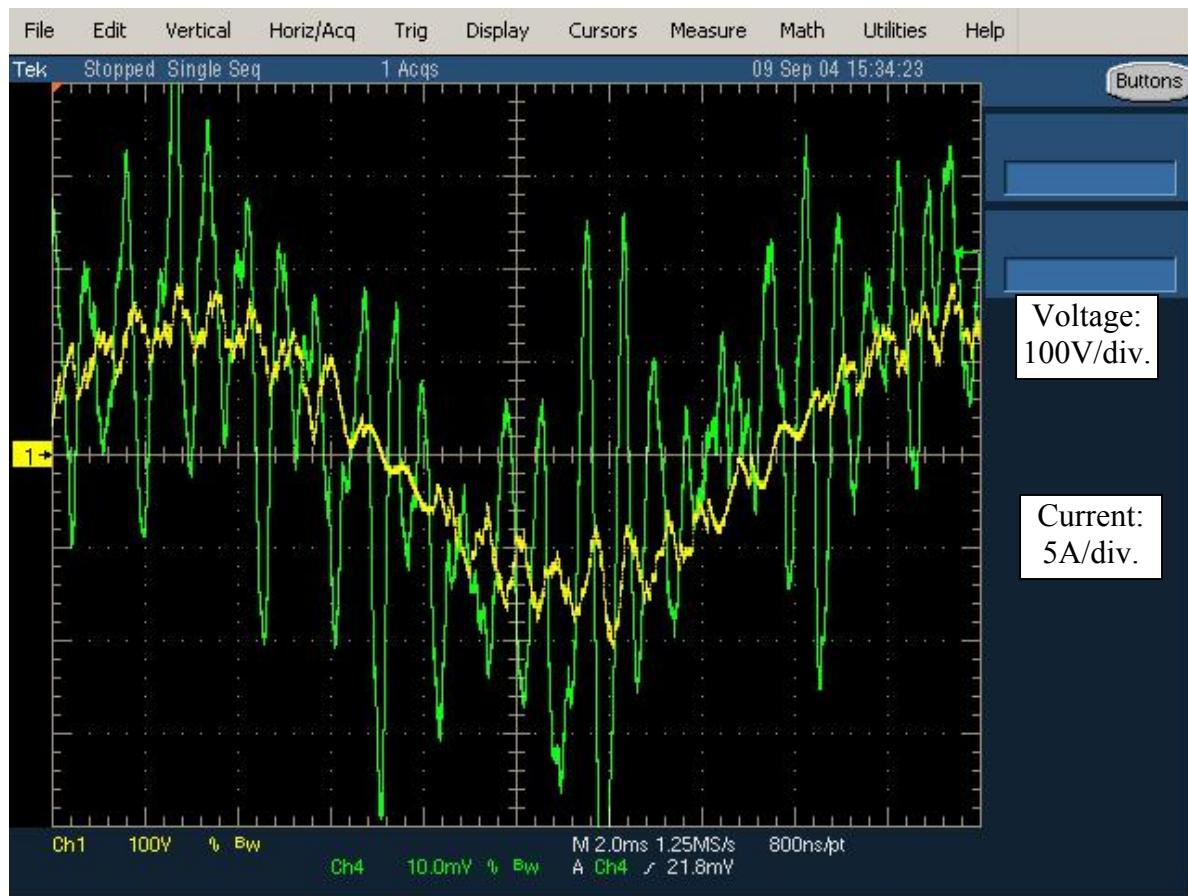

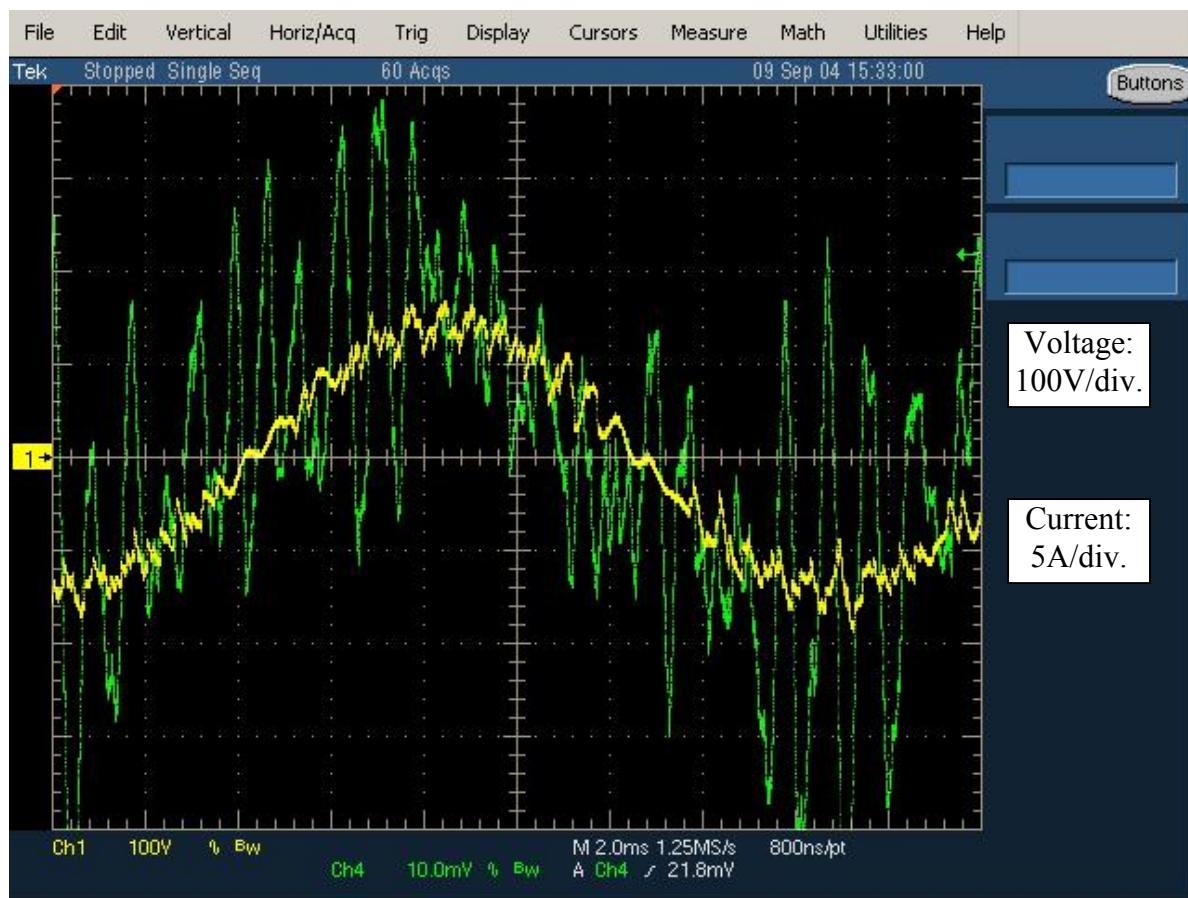

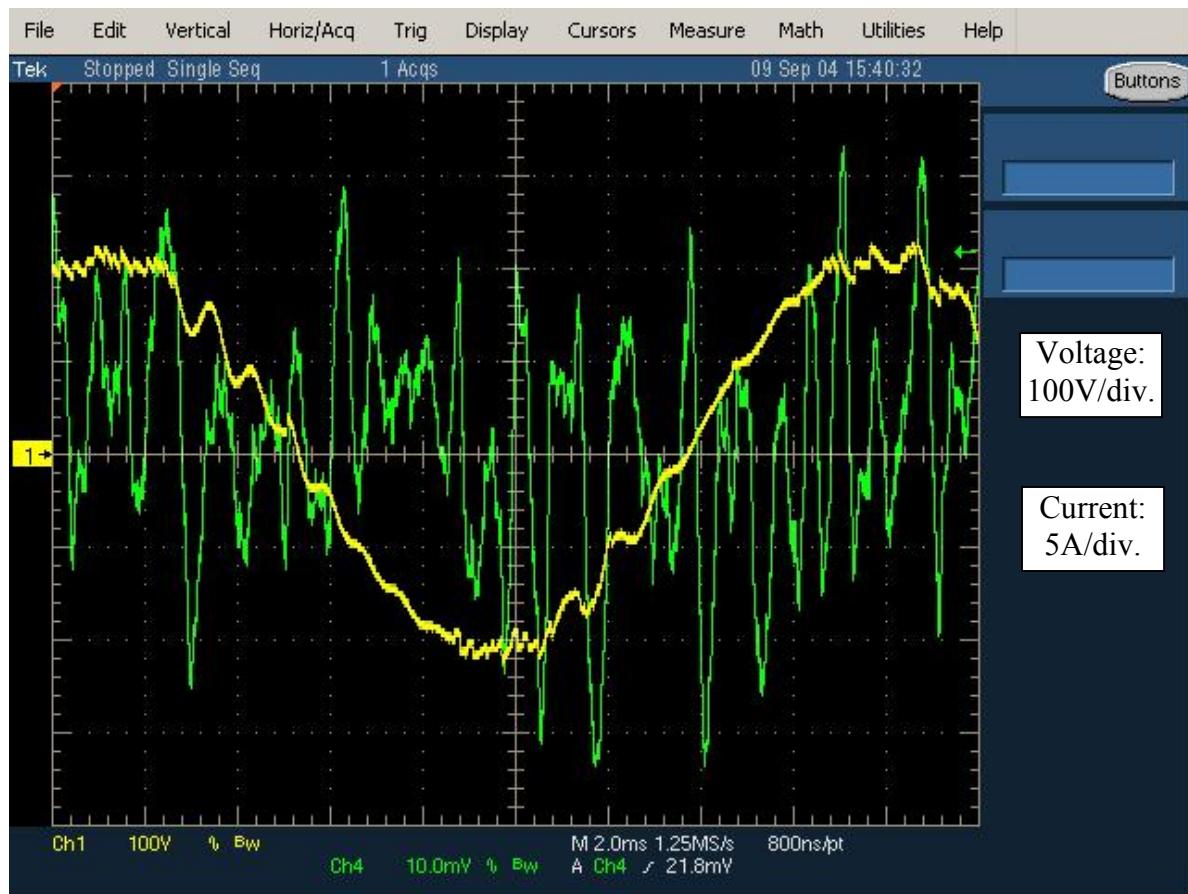

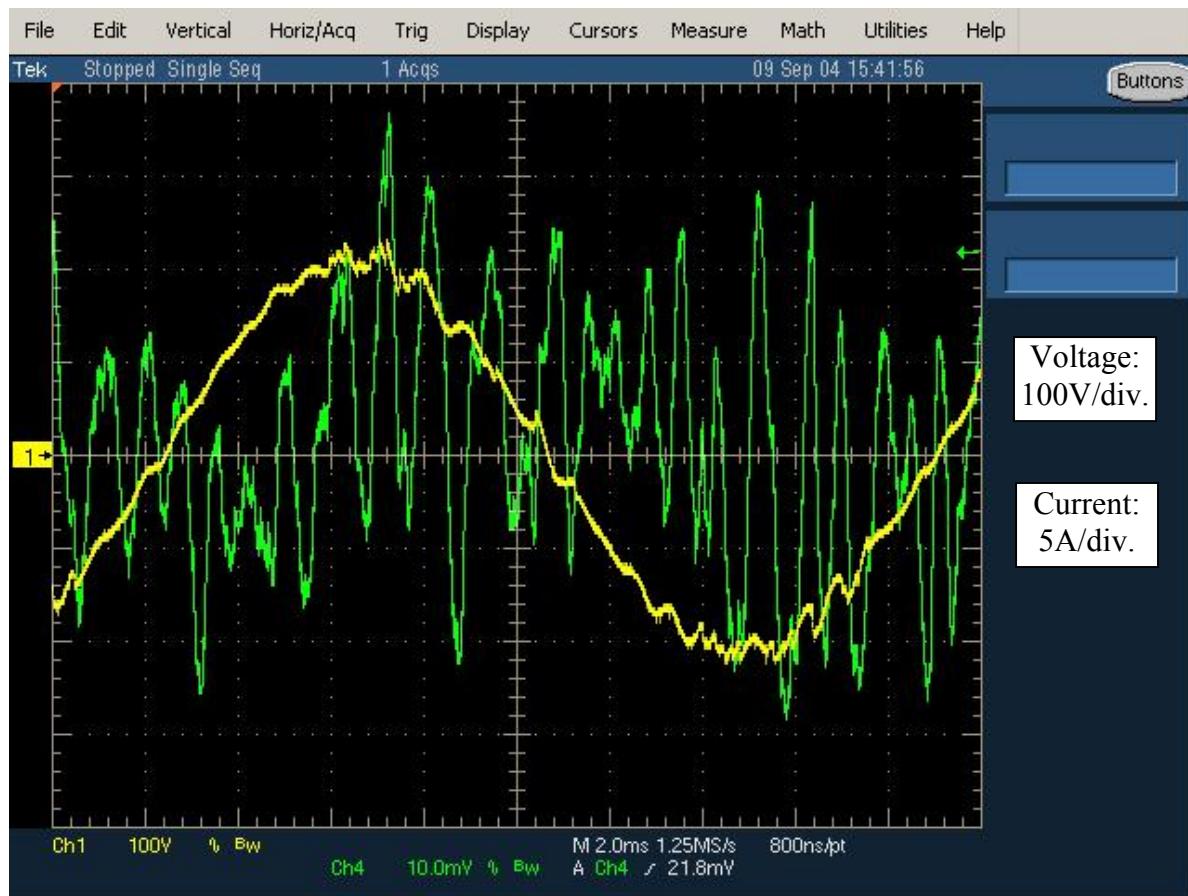

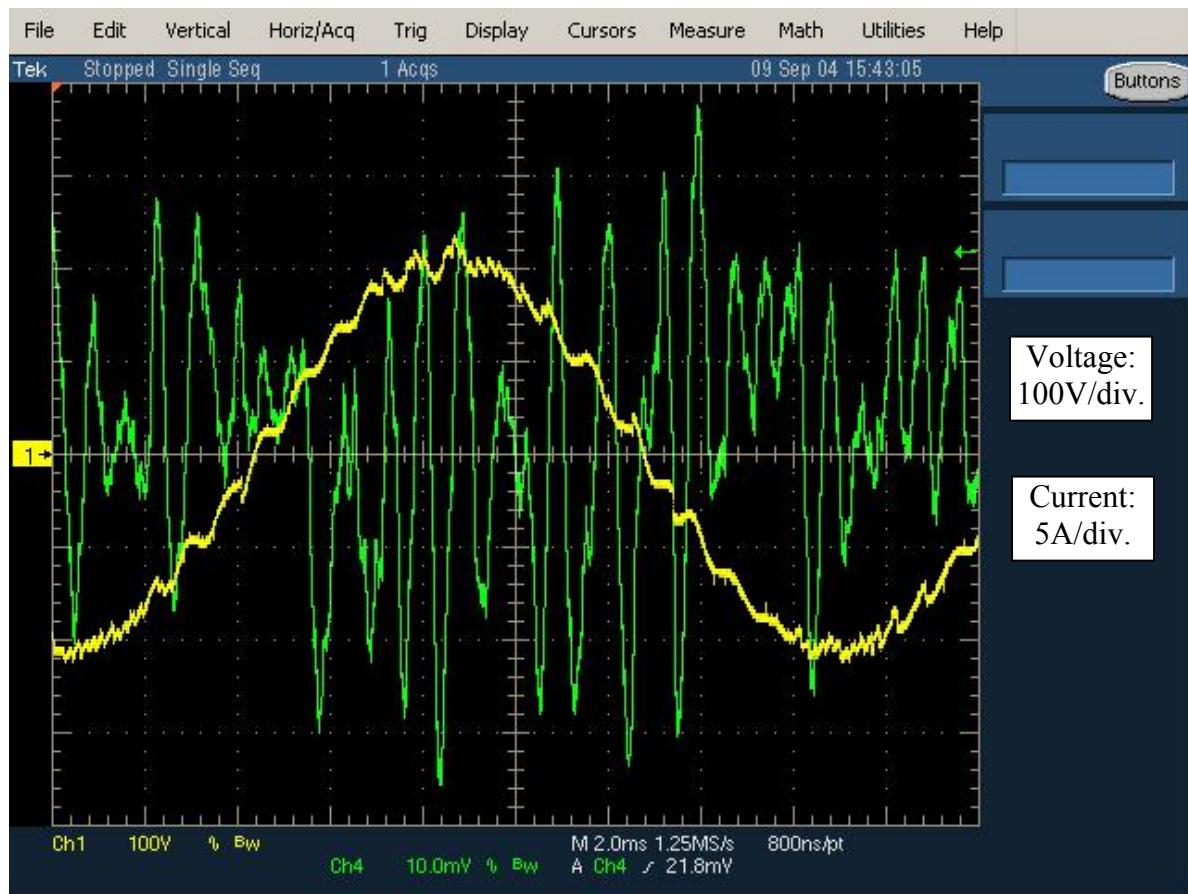

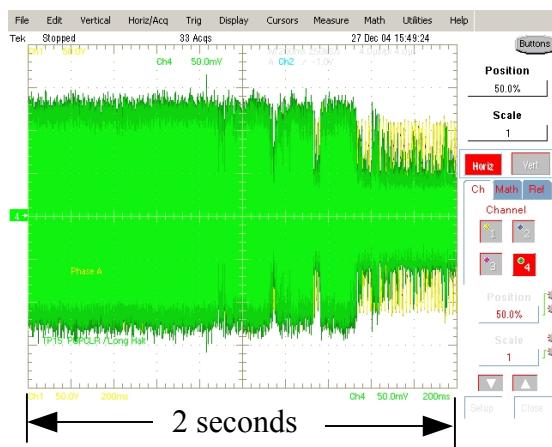

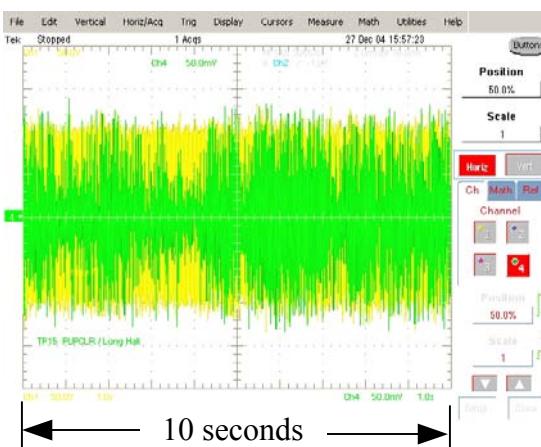

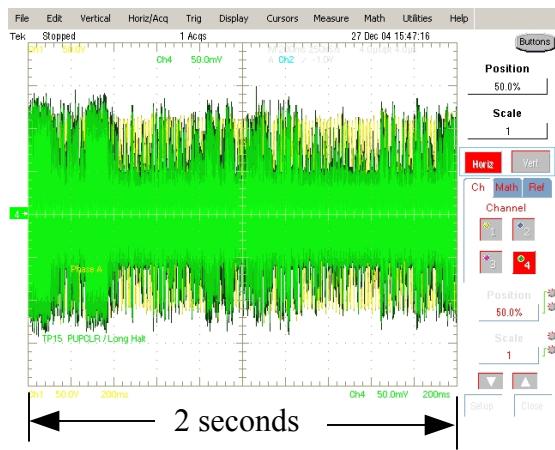

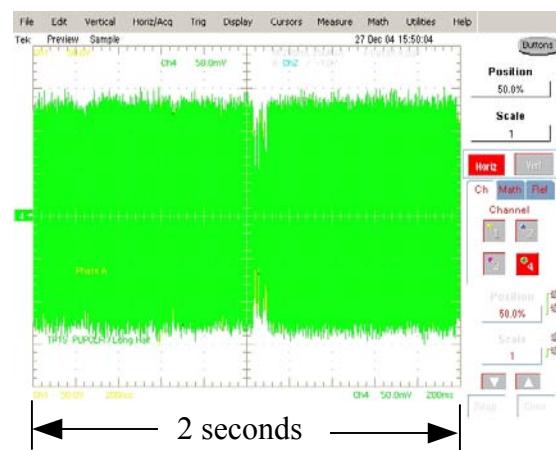

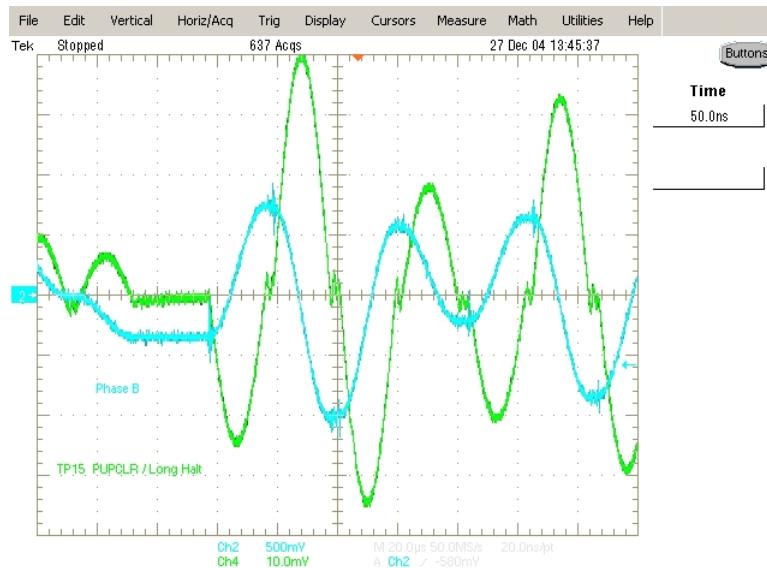

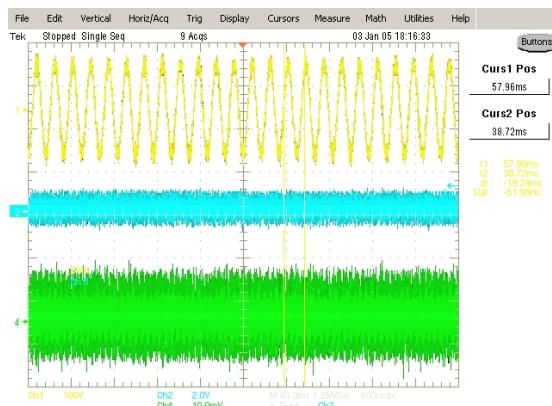

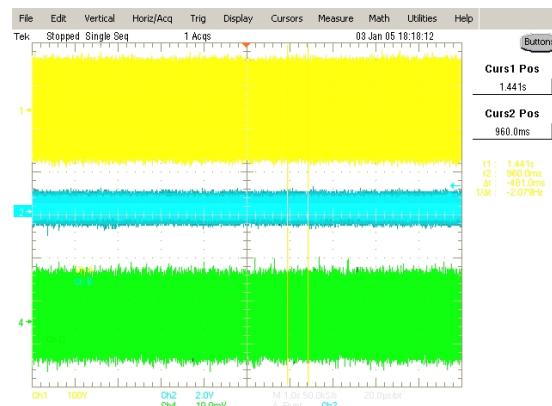

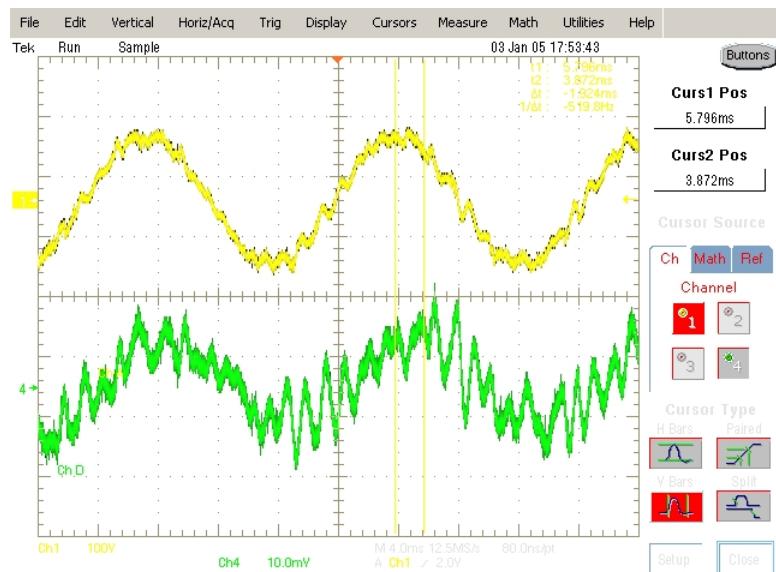

The testing was commenced and it was immediately noticed that there was a higher level of audible noise from the resonant inductor, as well as the fact that the ETM prototype would shut down at random after operating at random intervals from 60 seconds to 10 minutes. Once shut down, the prototype would remain latched off. This behavior was radically different from that noted before the repairs and revisions were accomplished. There are several events that can shut down the converter, not the least of which is an over voltage event on the resonant capacitor. This is the primary hardware event (that was not disabled for debug/test purposes) and as a result the differential capacitor signal VRC was monitored along with the resonant current signal IRMAG\_SIGN on the ETM Control Board. Typical waveforms observed on the VRC and IRMAG\_SIGN signals are shown in Figures C7 through C12.

**Figure C7.** Resonant Signals VRC (green) and IRMAG\_SIGN (yellow).**Figure C8.** Resonant Signals VRC (green) and IRMAG\_SIGN (yellow).

**Figure C9.** Resonant Signals VRC (green) and IRMAG\_SIGN (yellow).**Figure C10.** Resonant Signals VRC (green) and IRMAG\_SIGN (yellow).

**Figure C11.** Resonant Signals VRC (green) and IRMAG\_SIGN (yellow).**Figure C12.** Resonant Signals VRC (green) and IRMAG\_SIGN (yellow).

The one common characteristic of all these traces, taken at random times, are that they are inconsistent. During normal ETM Converter operation, one would expect to see a capacitor voltage and an inductor current that were reasonably stable in amplitude (in the

time scale shown of one second per division) with few random positive or negative amplitude fluctuations. This is obviously not the case! Figures C7 through C12 embody the behavior dubbed “breathing”, whereby the resonant capacitor voltage and resonant current took on a random, amplitude modulated appearance with time. It was this breathing phenomenon that was responsible for the very much increased audio noise from the resonant inductor. After considerable troubleshooting, the breathing phenomenon could not be attributed to a hardware bug or issue.

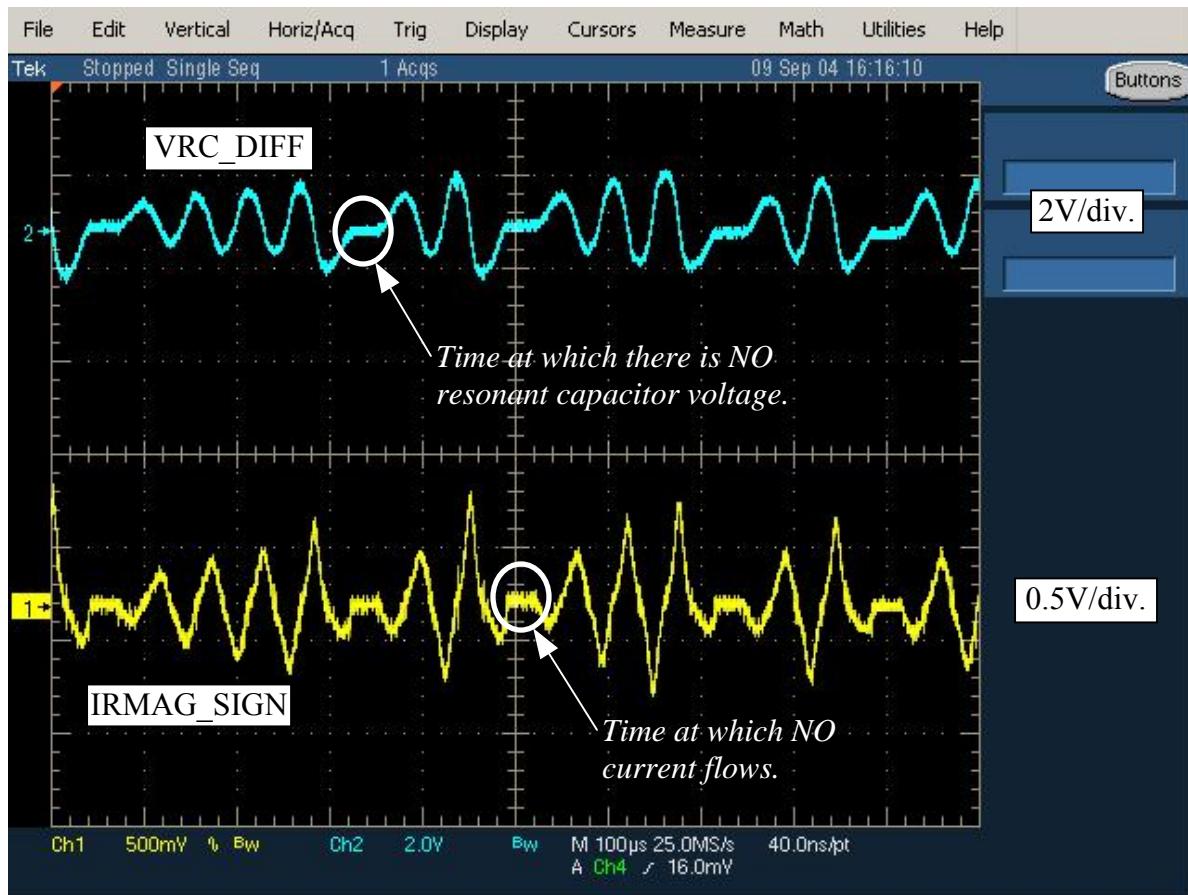

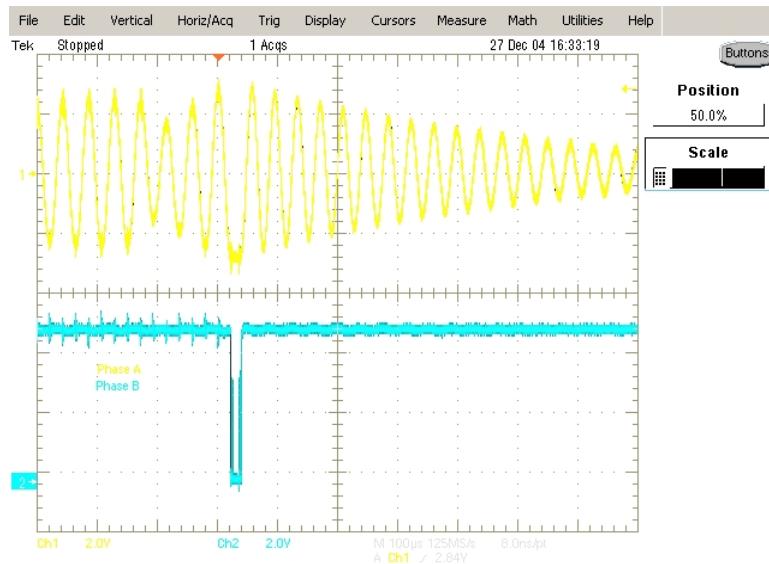

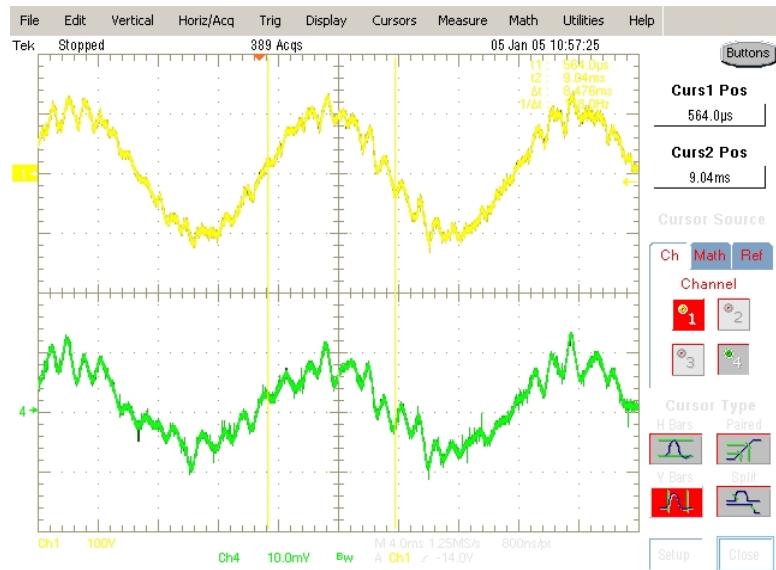

Furthermore, the latch off problem was highly inconsistent and very annoying. To determine where this behavior was originating, the signal VRC\_OV\_N (a negative-going signal indicating that the resonant capacitor has exceeded the firmware-set voltage threshold value of  $|1500V|$ ) was monitored. The waveform, shown in Figure C13, shows that this level had indeed been exceeded by the presence of the negative-going pulse on this signal.

**Figure C13. VRC\_OV\_N Signal Actuation Event.**

In Figure C13, the yellow trace is the differential resonant capacitor voltage signal VRC and the blue signal is the resonant capacitor over voltage fault signal VRC\_OV\_N.

This condition (VRC\_OV\_N pulse) should have never existed by virtue of the operating algorithm – the converter will (should) ignore (i.e. “pass on”) current transfer opportunities that would result in a final capacitor voltage of greater than |1500V|. The detection circuitry and signal were included solely as a fail-safe mechanism for the detection of a hardware failure or fault that existed in the ETM Converter, and quickly shut it down before damage may be propagated.

After two days of intensive troubleshooting and data analysis with the software developer (TechEn, Inc.), it was finally determined that the ADSP microcontroller was out of “real time” – that is that the required time to execute the software exceeded the Cycle Time (set at 23.5us) required for the ETM Prototype. The reason why this problem came to light after the last repair of the Prototype due to the fact that the resonance time was set to 21.5 microseconds (23.5us by calculation). With the 2us dead time added to this value, the Cycle Time became 23.5us. The difference of 4.5 microseconds between the original Cycle Time setting of 28us and the new value of 23.5us was enough to consume any real time software execution time buffer that may have existed. The reason that the breathing and the random resonant capacitor over voltage events existed was the fact that for certain code executions, times greater than the cycle time were required and were thus prematurely truncated without proper software flow and resolution. The result was random, unpredictable operation with the observed fluctuations in resonant capacitor and resonant current amplitudes. The ETM Converter simply will not work properly if there is not sufficient time for the microcontrollers to execute the software code and “think”.

There were two solutions to this problem; an expedient solution that would allow testing to continue, and a longer-term solution that involved optimizing the software/firmware in the ADSP microcontroller to reduce the execution time to below 20 microseconds (to allow for a code execution safety margin). The expedient problem solution was determined experimentally – the Cycle Time was increased until the ETM Prototype began to function as was expected. This time was increased in 0.2 microsecond steps from the 23.5us value until no breathing or shutdown phenomena were encountered. This occurred at 24.2us – so the Cycle Time was set to 25us to add a safety margin for the remainder of the testing. This action is not without consequence; as the maximum power

available from the ETM Prototype will drop from 34kW to approximately 31kW. But this decrease in power would only temporarily exist until the software code was optimized to reduce the execution time to below 20us by converting time-consuming C code routines into corresponding functionality ADSP native assembly code.

For a more detailed description of this problem and the eventual solution, please refer to the document “34kW ETM Converter Prototype Project Status”.

So, with the Cycle Time set to 25us, the performance testing was restarted. Data was gathered for the operating ETM Prototype at several different I/O operating voltages, including: Phase Input power factor, voltage, current, and power; Phase Output power factor, voltage, current and power; and the effects of the variation of the parameters Tres, Tcyc and IOSF. During this testing process, there were several minor changes made to the GUI control software and the ADSP firmware to improve the ETM Prototype operating characteristics and its controllability from the GUI interface.

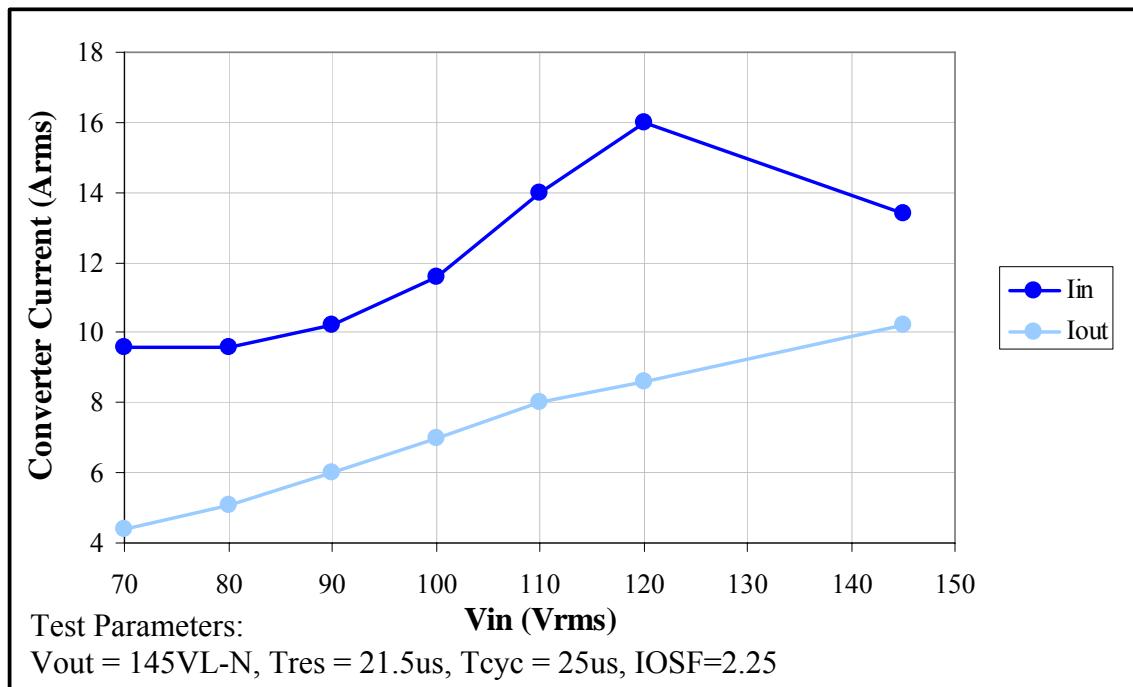

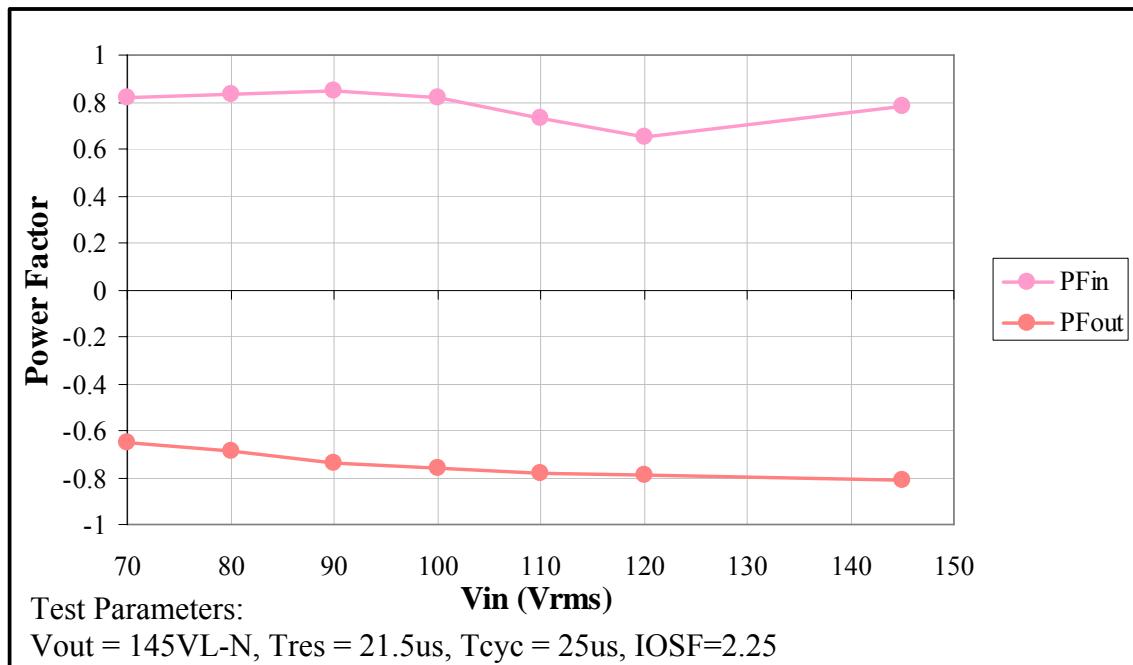

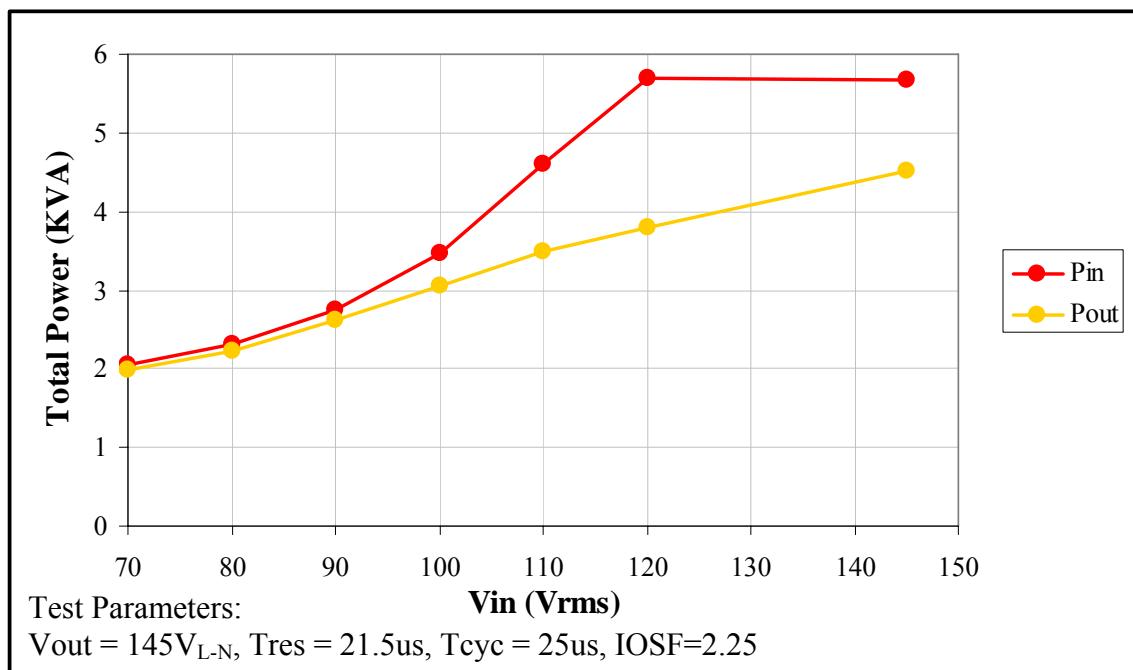

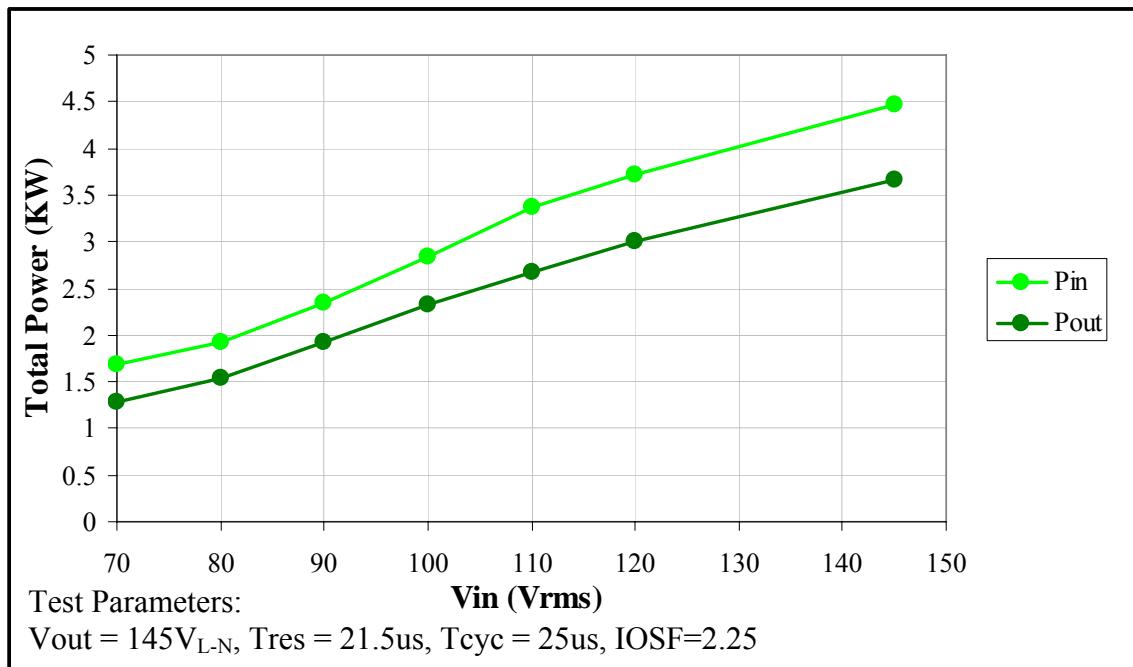

In particular, the output voltage was set to  $145V_{L-N}$  ( $250V_{L-L}$ ) and the input voltage was set to 70/80/90/100/110/120/145 $V_{L-N}$ , with the aforementioned parameters recorded at each input voltage step. Additionally, at each input voltage step, Tcyc was varied from 25 to 55us and the parameter IOSF was varied from 1.0 to 3.0 to observe their effects on the operation of the converter. The data obtained for this range of I/O voltages is summarized in a following section.

Unfortunately, when the input and output voltages were increased to  $200V_{L-N}$  ( $\sim 350V_{L-L}$ ) and the power was turned on, the circuit breakers immediately tripped, indicating an internal fault. Upon troubleshooting the ETM Prototype, it was determined that all the IGBTs in the power train were damaged, along with their associated IGBT driver boards. Due to a number of different factors, the testing was halted at this point, and this was the state of the Prototype when the testing was terminated.

## D.) ETM Prototype Test Data Summary

The ETM Converter Prototype test data collected during the Performance Test phase over the time period of 12/22/04 to 3/10/05, and is summarized in the following discussion.

### i.) IOSF Versus Phase Current Magnitude

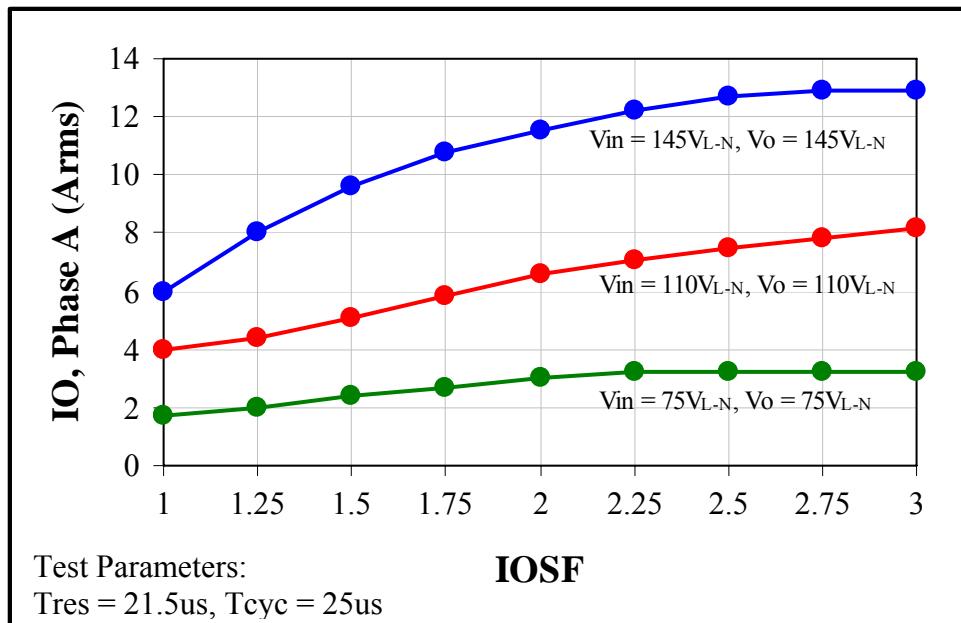

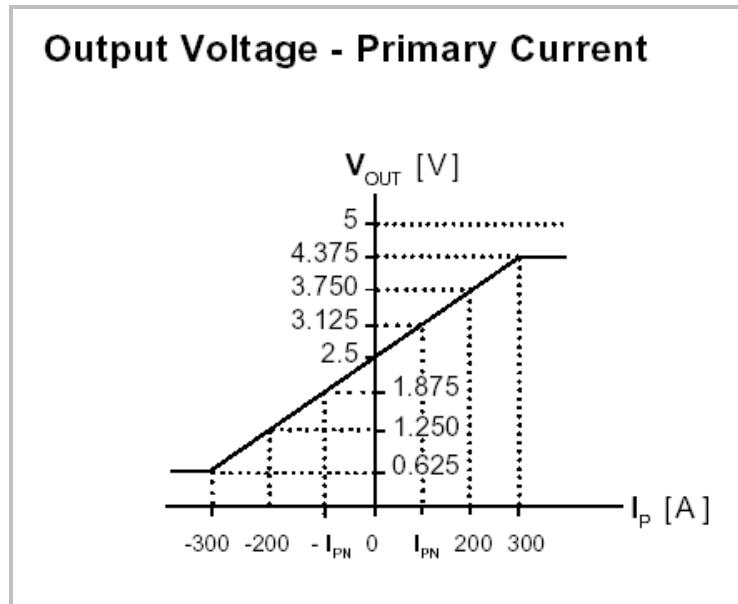

The parameter IOSF was varied over the range of 1 to 3 in 0.25 unit increments while observing the Phase Output Current. This was done to determine the transfer characteristic of the parameter IOSF in relationship to the I/O characteristics of the ETM Converter. It should be noted that this parameter directly controls a variable placed in the ETM Converter operational flowchart for the decision point " $E_I + V_{cs} > E_o$ ", which ultimately controls the window of resonant capacitor voltages which may be allowed to initiate a resonant current transfer from input-to-output. The IOSF range is an arbitrary analog of the multiplicand " $1 * E_o$ " in the previous equation. This value of 1 was capable of being varied over a 3-to-1 range by varying IOSF from 1 to 3. This data is shown in Tables D1 and D2 and Figures D1 and D2.

**Table D1.** *IOSF VS Phase Current Magnitude (IOSF vs IO).*

| IOSF | IO, Phase A (Arms) | IO, Phase A (Arms) | IO, Phase A (Arms) |

|------|--------------------|--------------------|--------------------|

| 1    | 1.7                | 4                  | 6                  |

| 1.25 | 2                  | 4.4                | 8                  |

| 1.5  | 2.4                | 5.1                | 9.6                |

| 1.75 | 2.7                | 5.8                | 10.8               |

| 2    | 3                  | 6.6                | 11.5               |

| 2.25 | 3.2                | 7.1                | 12.2               |

| 2.5  | 3.2                | 7.5                | 12.7               |

| 2.75 | 3.2                | 7.8                | 12.9               |

| 3    | 3.2                | 8.2                | 12.9               |

**Figure D1.** *IOSF VS Phase Current Magnitude (IOSF vs IO).***Table D2.** *IOSF VS Phase Current Magnitude (IOSF vs IO).*

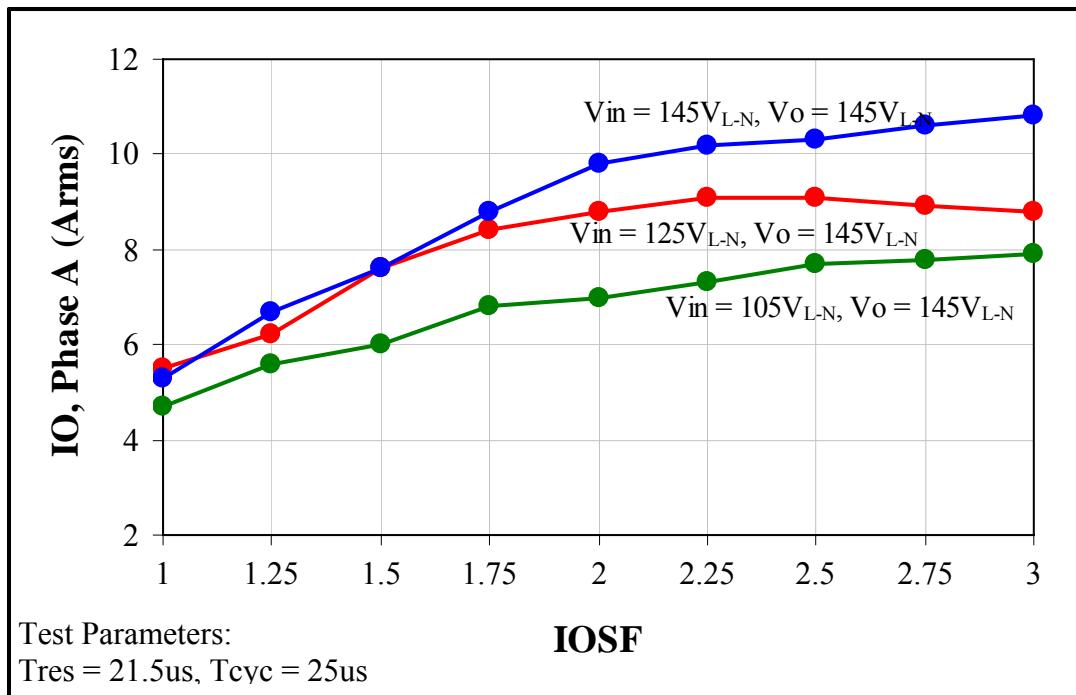

| IOSF | Vout = 145V <sub>L-N</sub> |                           |                           |

|------|----------------------------|---------------------------|---------------------------|

|      | Vin = 105V <sub>L-N</sub>  | Vin = 125V <sub>L-N</sub> | Vin = 145V <sub>L-N</sub> |

|      | IO, Phase A (Arms)         | IO, Phase A (Arms)        | IO, Phase A (Arms)        |

| 1    | 4.7                        | 5.5                       | 5.3                       |

| 1.25 | 5.6                        | 6.2                       | 6.7                       |

| 1.5  | 6                          | 7.6                       | 7.6                       |

| 1.75 | 6.8                        | 8.4                       | 8.8                       |

| 2    | 7                          | 8.8                       | 9.8                       |

| 2.25 | 7.3                        | 9.1                       | 10.2                      |

| 2.5  | 7.7                        | 9.1                       | 10.3                      |

| 2.75 | 7.8                        | 8.9                       | 10.6                      |

| 3    | 7.9                        | 8.8                       | 10.8                      |

**Figure D2. IOSF VS Phase Current Magnitude (IOSF vs IO).**

From the data gathered, it can be seen that there is a plateau level for the phase output current, for each setting of input voltage, at an IOSF value of 2.25. This makes sense, as the output current is expected to decrease as IOSF is decreased, because the ETM control loop will reject resonant current transfer events as the parameter is lowered.

## ii.) IOSF Versus Total Output Power

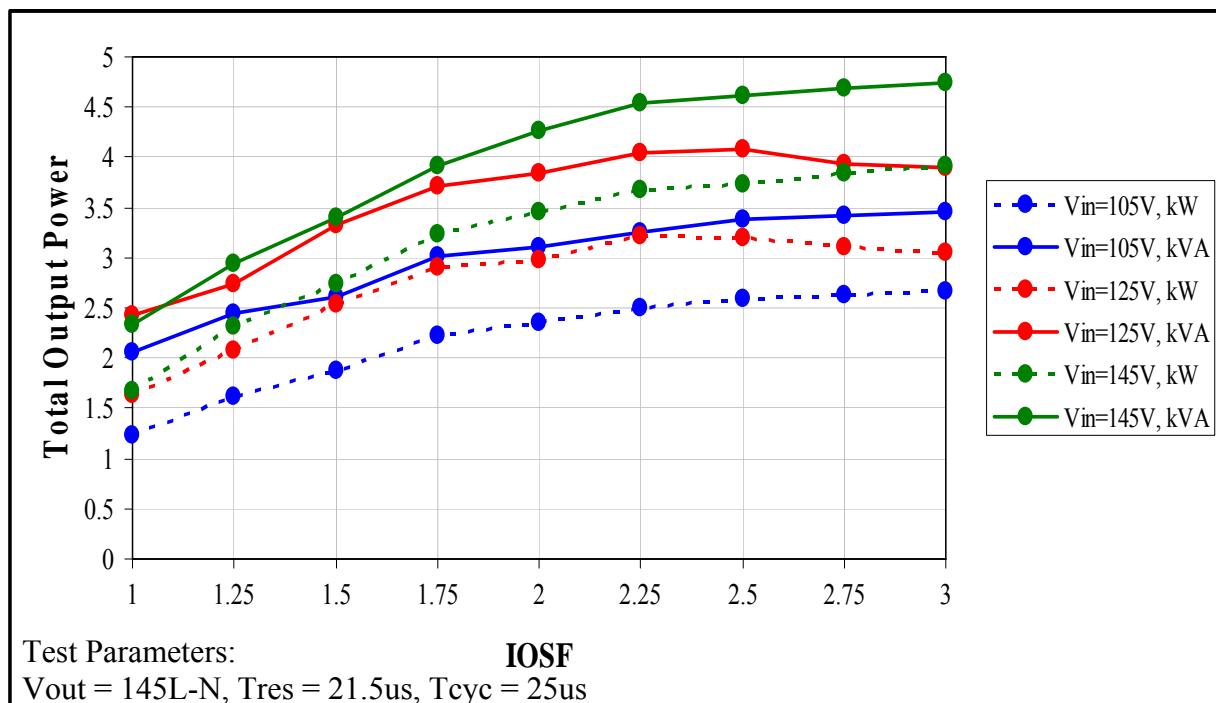

The Total Output Power was monitored via a three-phase power analyzer while the parameter IOSF was varied. The results are shown in Table D3 and Figure D3, following:

**Table D3. IOSF VS Phase Current Magnitude (IOSF vs IO).**

| IOSF | Vin = 105V <sub>L-N</sub> , Vout = 145V <sub>L-N</sub> |                          | Vin = 125V <sub>L-N</sub> , Vout = 145V <sub>L-N</sub> |                          | Vin = 145V <sub>L-N</sub> , Vout = 145V <sub>L-N</sub> |                          |

|------|--------------------------------------------------------|--------------------------|--------------------------------------------------------|--------------------------|--------------------------------------------------------|--------------------------|

|      | Total Output Power (kW)                                | Total Output Power (kVA) | Total Output Power (kW)                                | Total Output Power (kVA) | Total Output Power (kW)                                | Total Output Power (kVA) |

| 1    | 1.24                                                   | 2.06                     | 1.64                                                   | 2.43                     | 1.68                                                   | 2.34                     |

| 1.25 | 1.62                                                   | 2.45                     | 2.07                                                   | 2.74                     | 2.32                                                   | 2.95                     |

| 1.5  | 1.87                                                   | 2.61                     | 2.53                                                   | 3.32                     | 2.74                                                   | 3.4                      |

| 1.75 | 2.22                                                   | 3.02                     | 2.9                                                    | 3.72                     | 3.23                                                   | 3.92                     |

| 2    | 2.36                                                   | 3.11                     | 2.97                                                   | 3.85                     | 3.45                                                   | 4.27                     |

| 2.25 | 2.5                                                    | 3.25                     | 3.22                                                   | 4.04                     | 3.67                                                   | 4.54                     |

| 2.5  | 2.6                                                    | 3.39                     | 3.2                                                    | 4.08                     | 3.74                                                   | 4.62                     |

| 2.75 | 2.63                                                   | 3.41                     | 3.1                                                    | 3.93                     | 3.85                                                   | 4.68                     |

| 3    | 2.66                                                   | 3.46                     | 3.06                                                   | 3.9                      | 3.92                                                   | 4.74                     |

**Figure D3. IOSF VS Total Converter Output Power (IOSF vs PO).**

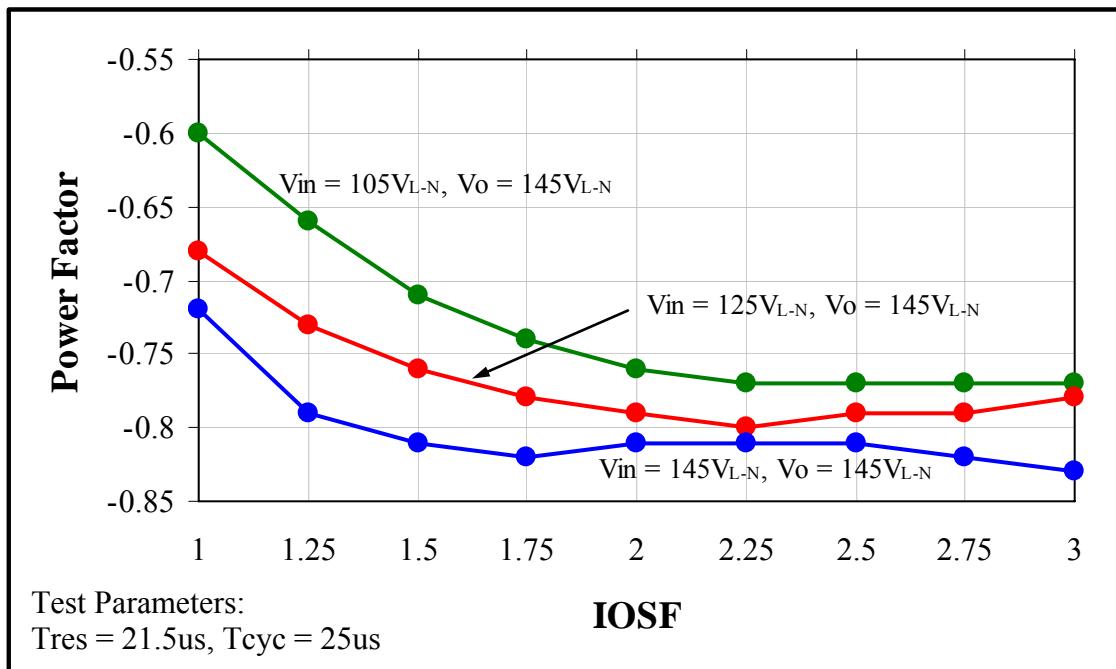

### iii.) IOSF Versus Phase Output Power Factor

The Phase Output Power Factor was monitored via a three-phase power analyzer while the parameter IOSF was varied. The results are shown in Table D4 and Figure D4, following:

**Table D4.** *IOSF VS Total Phase Output Power Factor (IOSF vs PF).*

| IOSF | Vout = 145V <sub>L-N</sub> |                           |                           |

|------|----------------------------|---------------------------|---------------------------|

|      | Vin = 105V <sub>L-N</sub>  | Vin = 125V <sub>L-N</sub> | Vin = 145V <sub>L-N</sub> |

|      | Output Power Factor        | Output Power Factor       | Output Power Factor       |

| 1    | -0.6                       | -0.68                     | -0.72                     |

| 1.25 | -0.66                      | -0.73                     | -0.79                     |

| 1.5  | -0.71                      | -0.76                     | -0.81                     |

| 1.75 | -0.74                      | -0.78                     | -0.82                     |

| 2    | -0.76                      | -0.79                     | -0.81                     |

| 2.25 | -0.77                      | -0.8                      | -0.81                     |

| 2.5  | -0.77                      | -0.79                     | -0.81                     |

| 2.75 | -0.77                      | -0.79                     | -0.82                     |

| 3    | -0.77                      | -0.78                     | -0.83                     |

**Figure D4.** *IOSF VS Total Phase Output Power Factor (IOSF vs PF).*

It should be noted that the firmware version used during the Performance Testing did not have provisions for the ETM control loop to adjust or correct the I/O power factor. The resultant power factor resulted solely from the execution of the native ETM Converter operational algorithm. The observed power factors at low values of IOSF make sense in regards to operation of the ETM control loop – as resonant current transfers are excluded at low IOSF values, there is less “fill in” of the resultant output current and a higher harmonic distortion with an attendant power factor.

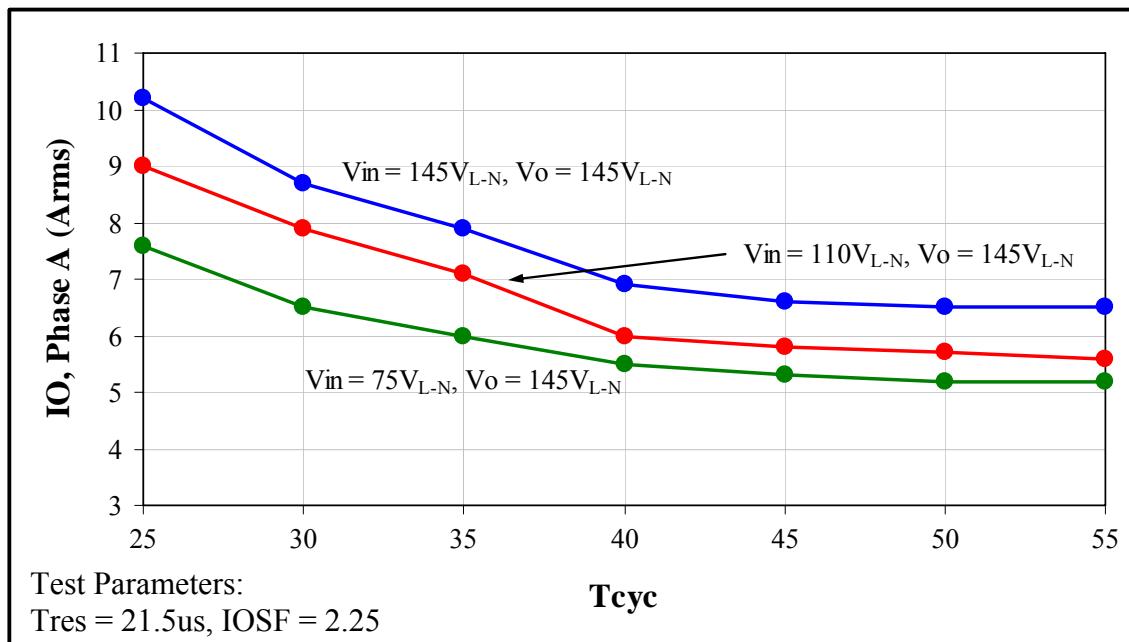

#### iv.) Tcyc Versus Phase Output Current

The Phase Output Current was monitored via a three-phase power analyzer while the parameter Tcyc was varied. The results are shown in Table D5 and Figure D5, following:

**Table D5.** *Tcyc VS Phase Output Current (Tcyc vs IO).*

| Tcyc<br>(us) | Vout = 145V <sub>L-N</sub> |                           |                           |

|--------------|----------------------------|---------------------------|---------------------------|

|              | Vin = 105V <sub>L-N</sub>  | Vin = 125V <sub>L-N</sub> | Vin = 145V <sub>L-N</sub> |

| 25           | 7.6                        | 9                         | 10.2                      |

| 30           | 6.5                        | 7.9                       | 8.7                       |

| 35           | 6                          | 7.1                       | 7.9                       |

| 40           | 5.5                        | 6                         | 6.9                       |

| 45           | 5.3                        | 5.8                       | 6.6                       |

| 50           | 5.2                        | 5.7                       | 6.5                       |

| 55           | 5.2                        | 5.6                       | 6.5                       |

**Figure D5.** *Tcyc VS Phase Output Current (Tcyc vs IO).*

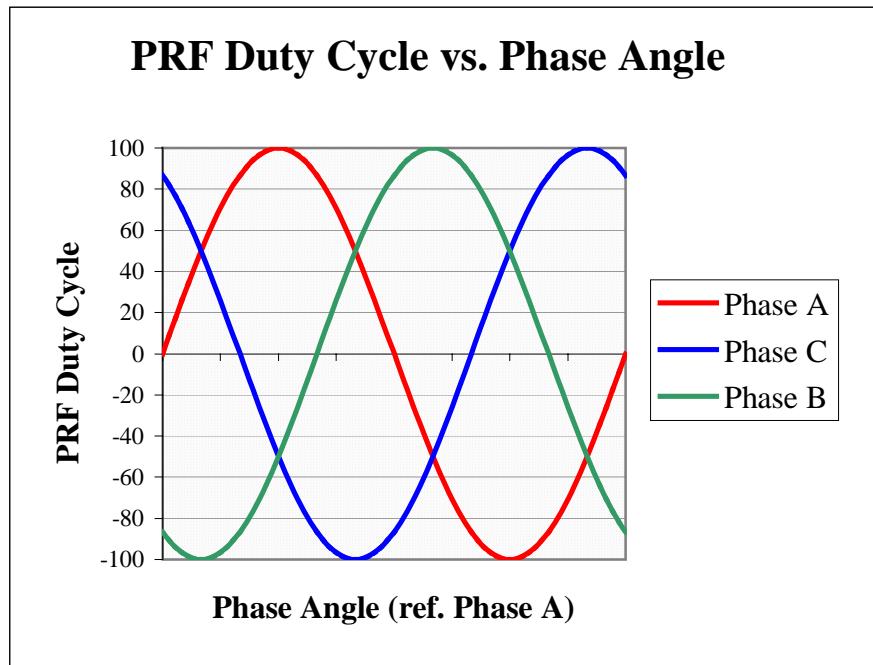

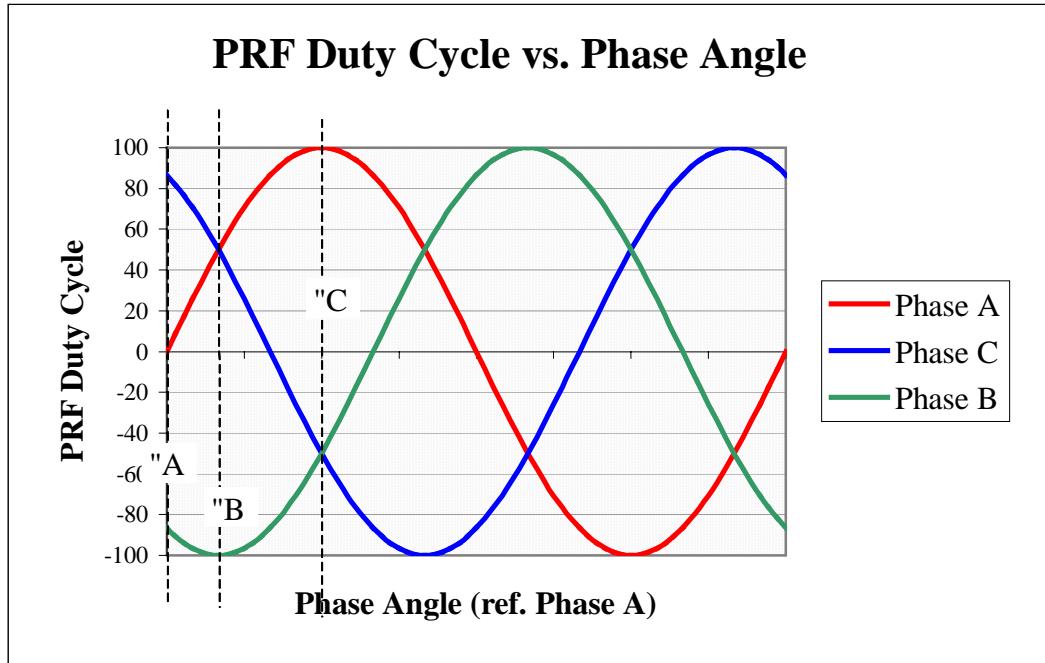

It is expected that as the parameter Tcyc is increased that the output current should decrease, due to the fact that an increasing Tcyc with a Tres amounts to a lower pulse repetition rate. A lengthened cycle time can be thought of as a lower resonant current transfer event duty cycle. There is another plateau of results that is observed as the Cycle Time is increased, beginning at approximately 40us. This is not an expected behavior and requires further investigation for an explanation.

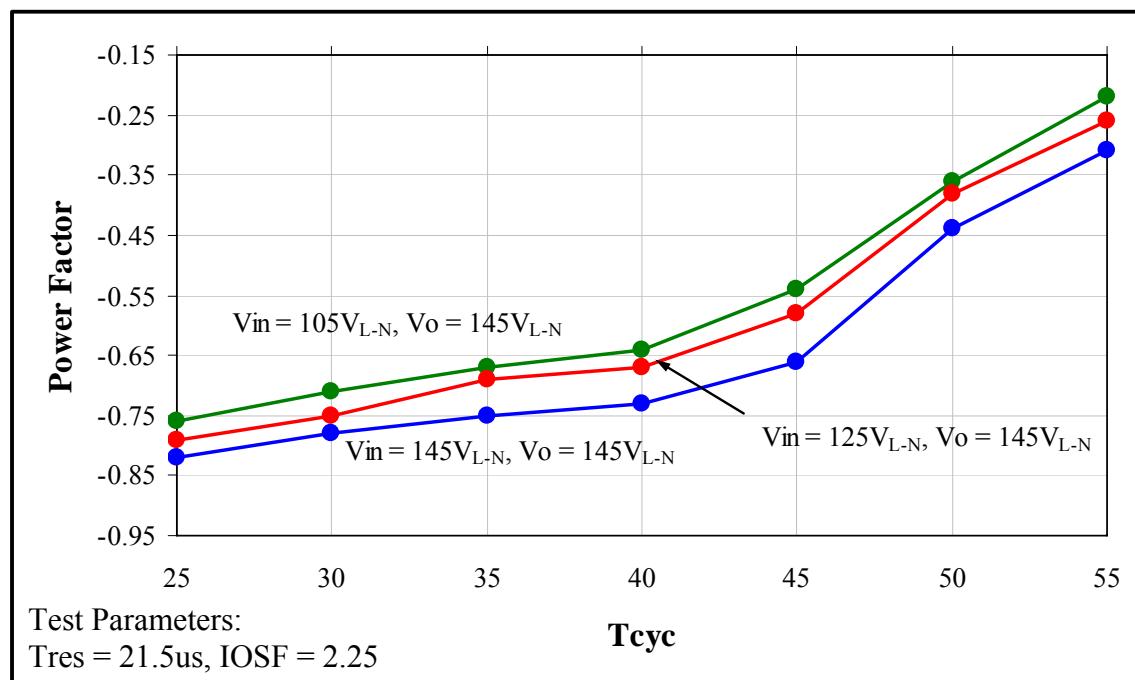

### v.) Tcyc Versus Phase Output Power Factor

The Phase Output Power Factor was monitored via a three-phase power analyzer while the parameter Tcyc was varied. The results are shown in Table D6 and Figure D6, following:

**Table D6.** *Tcyc VS Phase Output Power Factor (Tcyc vs PF).*

| Tcyc<br>(us) | Vout = 145V <sub>L-N</sub> |                           |                           |

|--------------|----------------------------|---------------------------|---------------------------|

|              | Vin = 105V <sub>L-N</sub>  | Vin = 125V <sub>L-N</sub> | Vin = 145V <sub>L-N</sub> |

| 25           | -0.76                      | -0.79                     | -0.82                     |

| 30           | -0.71                      | -0.75                     | -0.78                     |

| 35           | -0.67                      | -0.69                     | -0.75                     |

| 40           | -0.64                      | -0.67                     | -0.73                     |

| 45           | -0.54                      | -0.58                     | -0.66                     |

| 50           | -0.36                      | -0.38                     | -0.44                     |

| 55           | -0.22                      | -0.26                     | -0.31                     |

**Figure D6.** *Tcyc VS Phase Output Power Factor (Tcyc vs PF).*

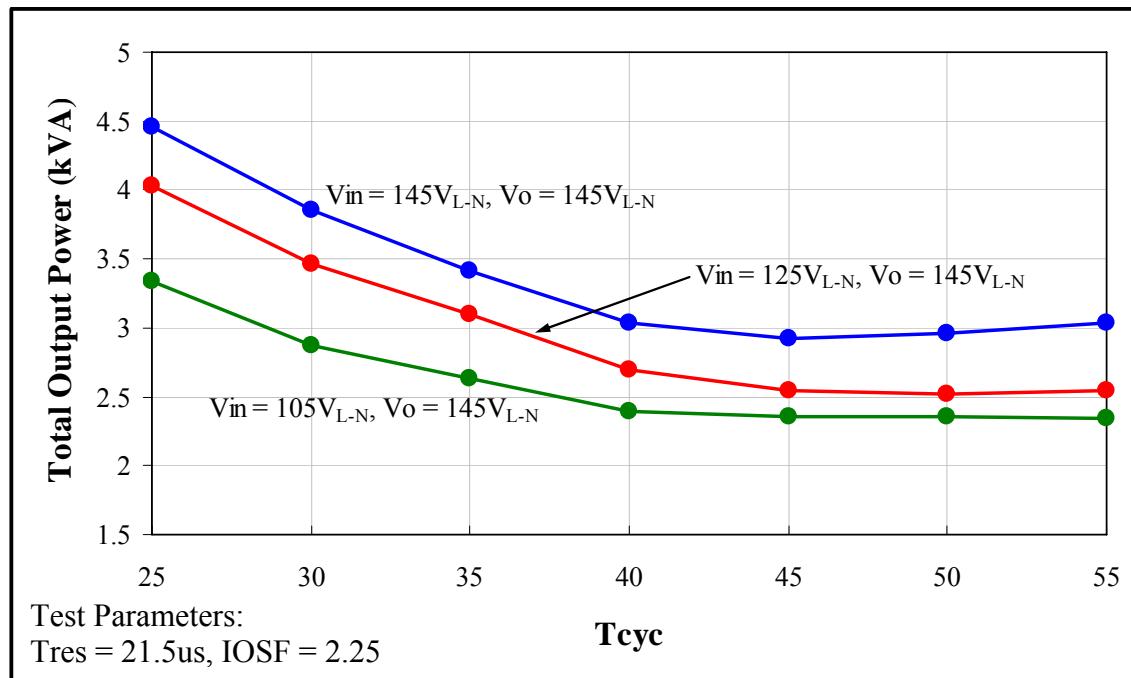

## vi.) Tcyc Versus Total Output Power

The Total Output Power was monitored via a three-phase power analyzer while the parameter Tcyc was varied. The results are shown in Table D7 and Figure D7, following:

**Table D7.** *Tcyc VS Total Output Power (Tcyc vs PO).*

| Tcyc<br>(us) | Vout = 145V <sub>L-N</sub> |                           |                           |

|--------------|----------------------------|---------------------------|---------------------------|

|              | Vin = 105V <sub>L-N</sub>  | Vin = 125V <sub>L-N</sub> | Vin = 145V <sub>L-N</sub> |

|              | Total Output Power (kVA)   | Total Output Power (kVA)  | Total Output Power (kVA)  |

| 25           | 3.34                       | 4.03                      | 4.46                      |

| 30           | 2.87                       | 3.47                      | 3.85                      |

| 35           | 2.63                       | 3.1                       | 3.41                      |

| 40           | 2.4                        | 2.7                       | 3.03                      |

| 45           | 2.35                       | 2.55                      | 2.92                      |

| 50           | 2.35                       | 2.52                      | 2.96                      |

| 55           | 2.34                       | 2.55                      | 3.03                      |

**Figure D7.** *Tcyc VS Total Output Power (Tcyc vs PO).*

As was the case of the Power Factor, the Output Power exhibits the same plateau behavior (as it should) for Cycle Times greater than 40us. This behavior is unexplained and requires further investigation.

### vii.) Performance Test Data Set Point #1

The Performance Testing for the ETM Converter Prototype was planned to be a series of data gatherings at set points ranging from 145V<sub>L-N</sub> output voltages to the maximum design value of 240V<sub>L-N</sub> (corresponding to ~408V<sub>L-L</sub>). The data set points would be increased in 20V increments from the minimum value to the maximum value. Performance data was collected for the input and the output at data set point #1, with the following fixed parameters: Tcyc = 25us, Tres = 21.5us, Vout = 145V<sub>L-N</sub> and IOSF = 2.25, and is shown in Table D8 and Figures D8 through D12:

**Table D8. ETM Converter Performance Set Point #1 Test Data.**

| <b>Vin</b> | <b>Iin</b> | <b>KVA</b> | <b>KW</b> | <b>PF</b> | <b>Vout</b> | <b>Io</b> | <b>KVA</b> | <b>KW</b> | <b>PF</b> |

|------------|------------|------------|-----------|-----------|-------------|-----------|------------|-----------|-----------|

| 70         | 9.6        | 2.05       | 1.68      | 0.82      | 145         | 4.4       | 1.98       | 1.29      | -0.65     |

| 80         | 9.6        | 2.31       | 1.92      | 0.83      | 145         | 5.1       | 2.23       | 1.54      | -0.69     |

| 90         | 10.2       | 2.76       | 2.35      | 0.85      | 145         | 6         | 2.62       | 1.93      | -0.74     |

| 100        | 11.6       | 3.47       | 2.84      | 0.82      | 145         | 7         | 3.06       | 2.33      | -0.76     |

| 110        | 14         | 4.61       | 3.37      | 0.73      | 145         | 8         | 3.5        | 2.68      | -0.78     |

| 120        | 16         | 5.69       | 3.72      | 0.65      | 145         | 8.6       | 3.8        | 3         | -0.79     |

| 145        | 13.4       | 5.67       | 4.47      | 0.78      | 145         | 10.2      | 4.52       | 3.67      | -0.81     |

**Figure D8.** Input Voltage VS Phase Output Current ( $V_{in}$  vs  $I_{IO}$ ).**Figure D9.** Input Voltage VS Input and Output Power Factors ( $V_{in}$  vs  $PF$ ).

**Figure D10.** *Input Voltage VS Total Output Power, kVA (Vin vs PO).***Figure D11.** *Input Voltage VS Total Output Power, kW (Vin vs PO).*

During the Data Set Pont #1 Performance Testing, there was anomalous behavior noted in the input current, power factor and total power (kVA) for input voltages between 100V and 145V. It is interesting, however that the total power in kW demonstrated the expected straight line variation as expected! This behavior is most likely due to the fact that the I/O power factors are uncontrolled by the ETM control loop with the revision level of the firmware used, so the resultant power factors during operation were “what they were”.

## E.) Summary of IGBT Failures Encountered

### i.) The IGBTs Used and Their Ratings

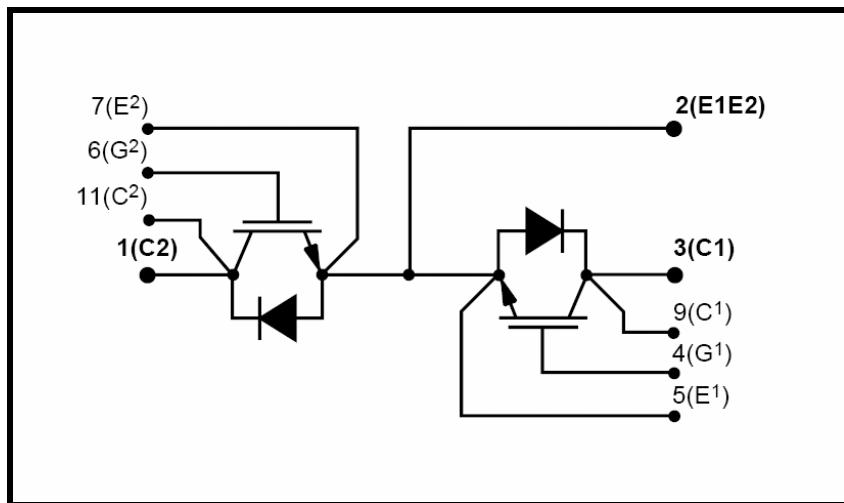

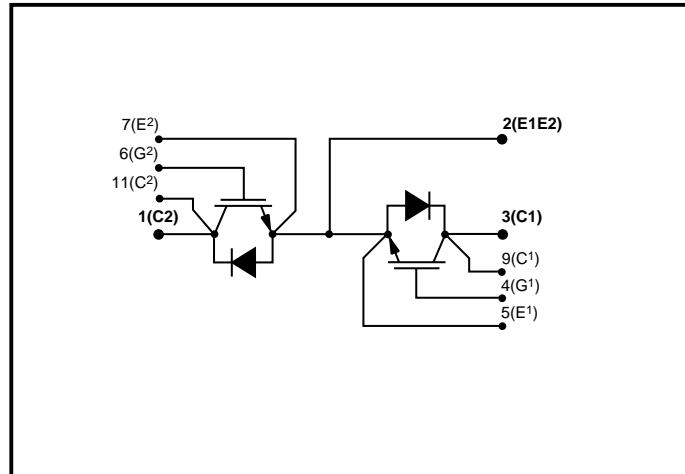

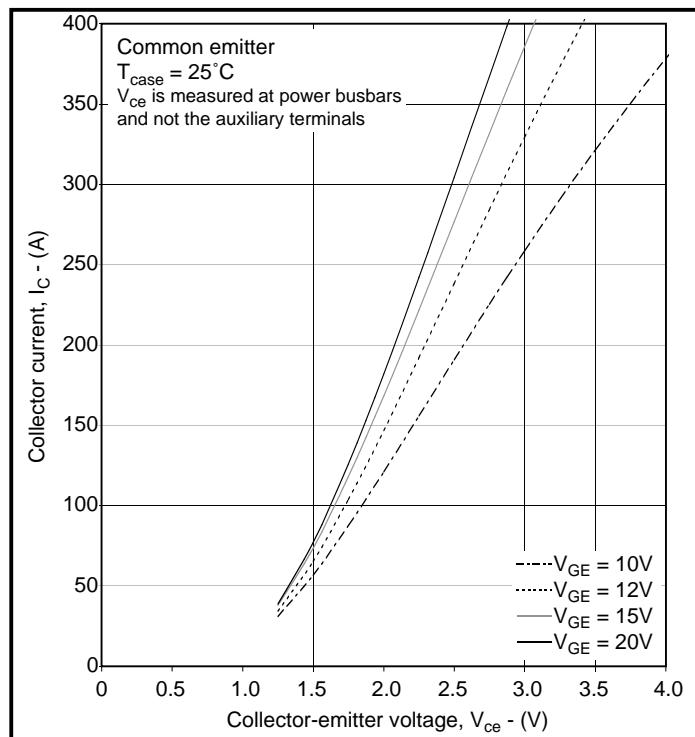

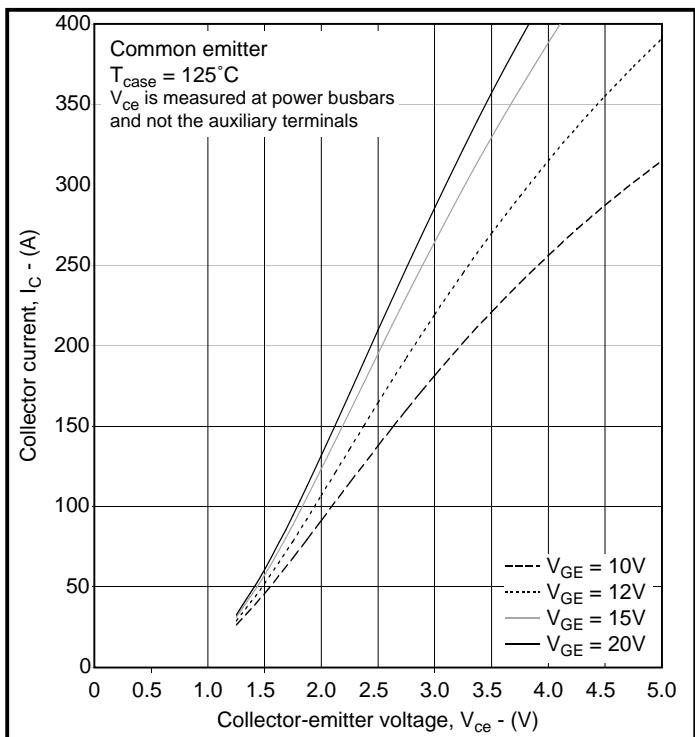

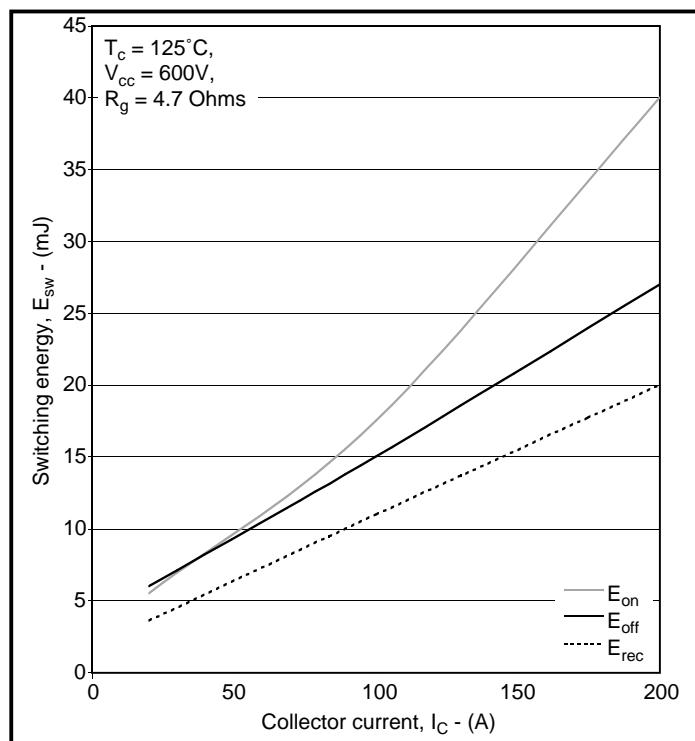

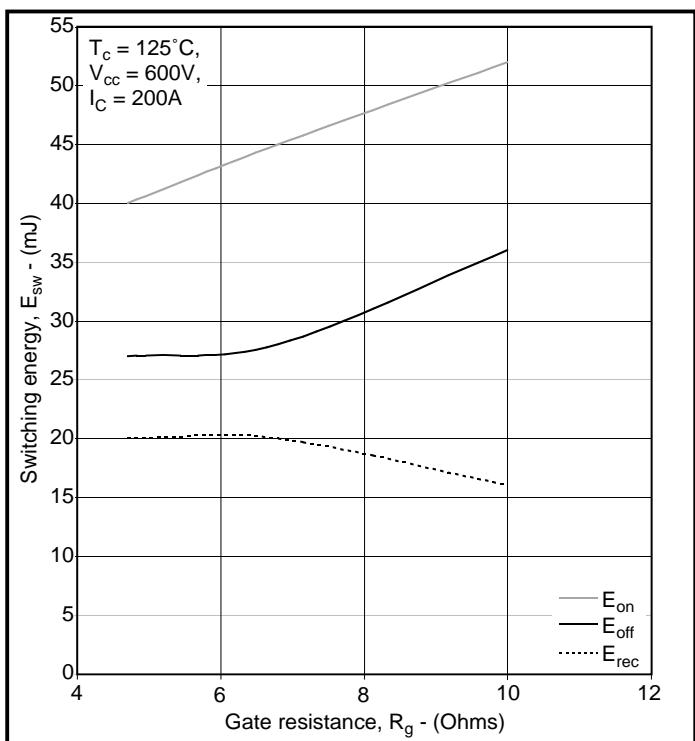

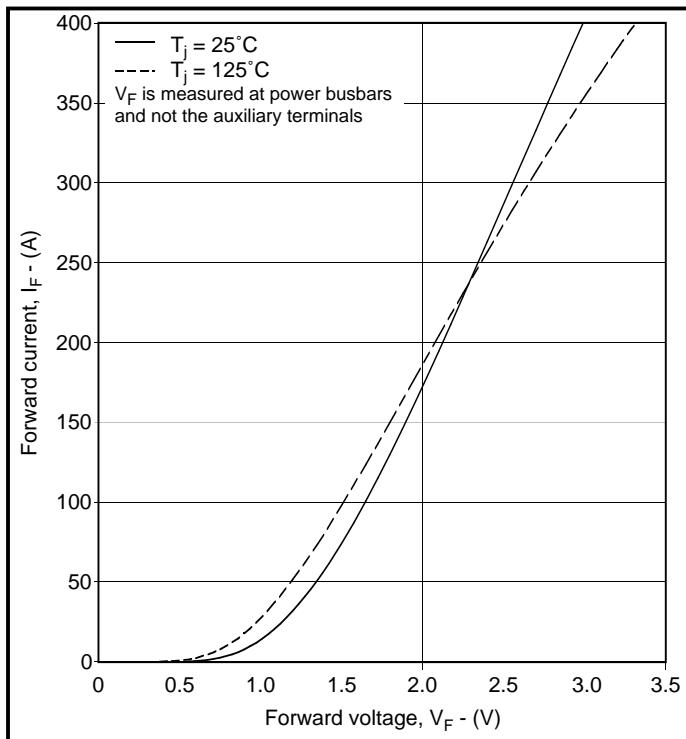

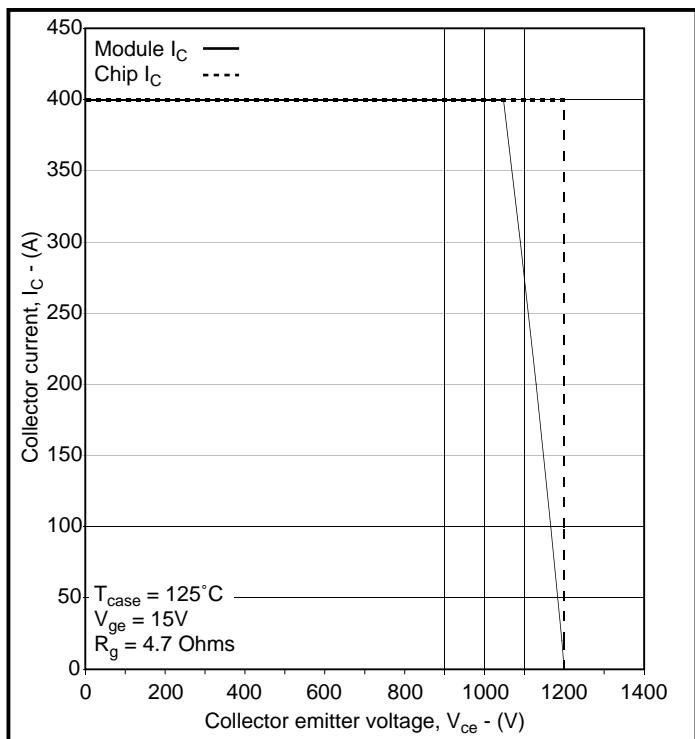

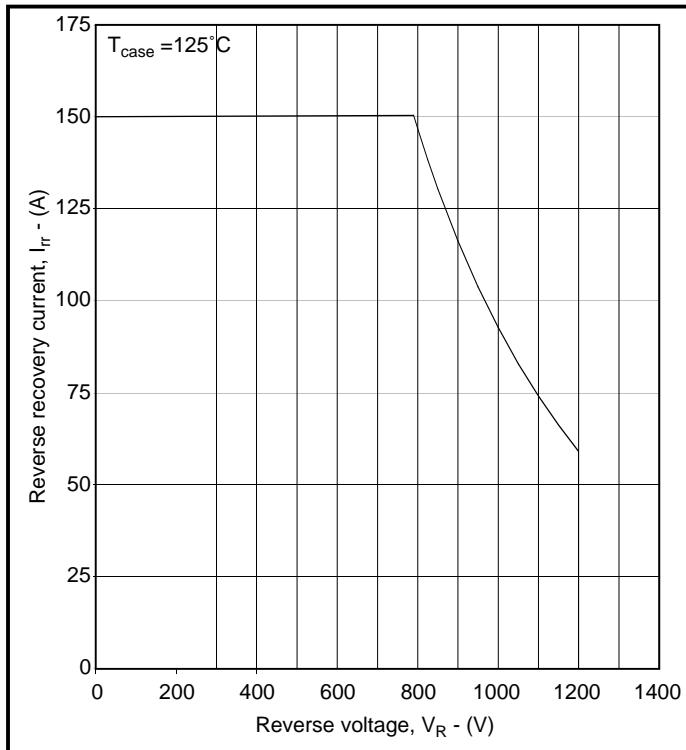

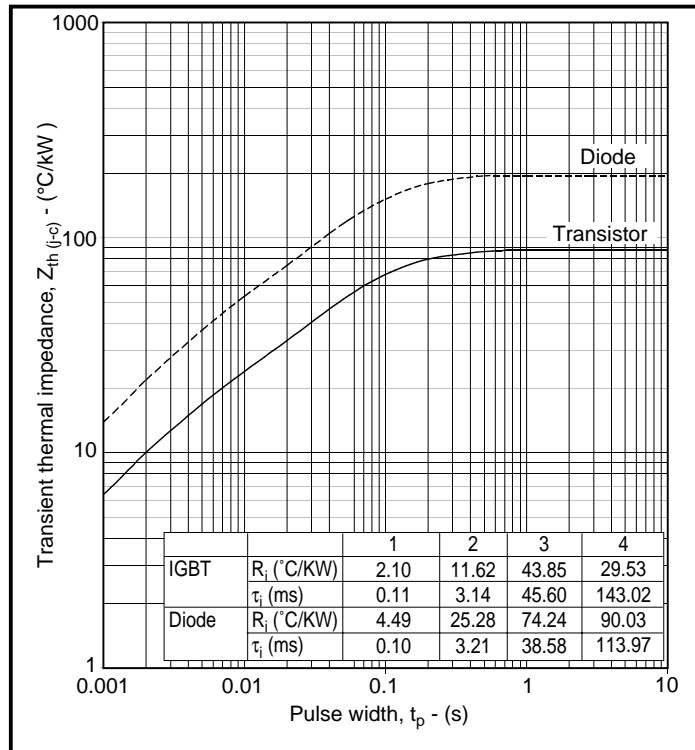

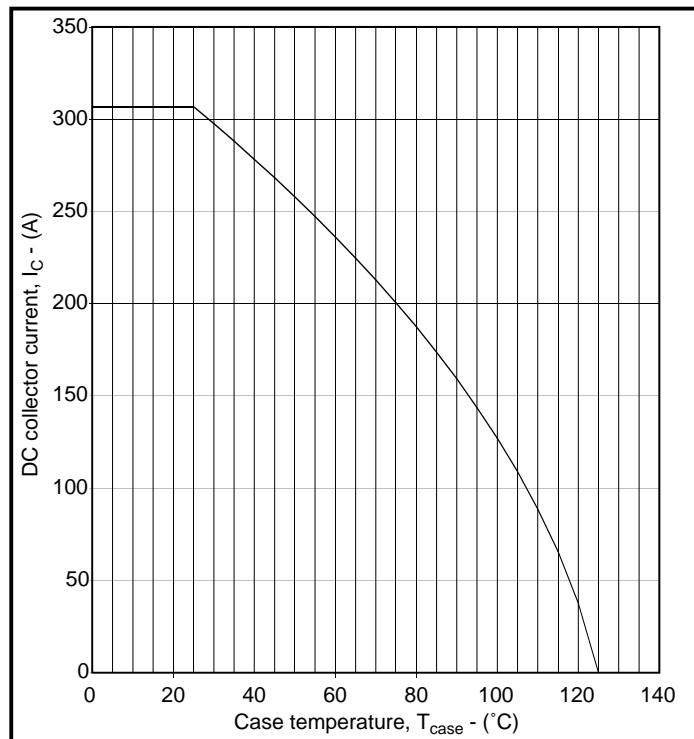

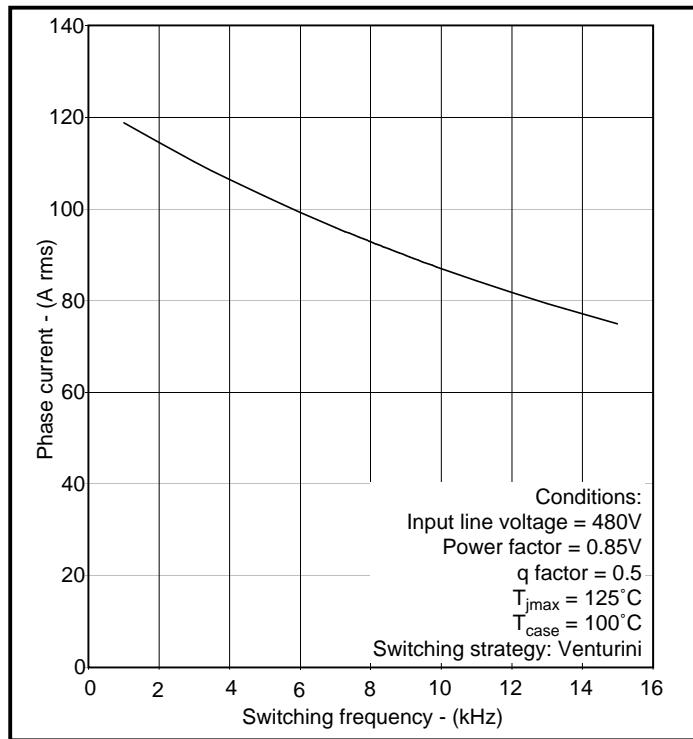

The IGBTs used in the ETM Converter are manufactured by Dynex Semiconductor, their part number DIM200MBS12-A000. These components are rated for  $\pm 1200V$  and have an average current rating of 200A (400Apk for 1ms). This device is an AC switch composed of two series connected IGBTs (each with an anti-parallel silicon rectifier) with common emitters, as shown in Figure E1:

**Figure E1.** Dynex DIM200MBS12-A000 Functional Schematic.

These devices were selected for their 1200V breakdown voltage and their 200A current carrying rating, as well as for their very fast switching times. The data sheet of their electrical characteristics may be found here: [DIM200MBS12-A000](#).

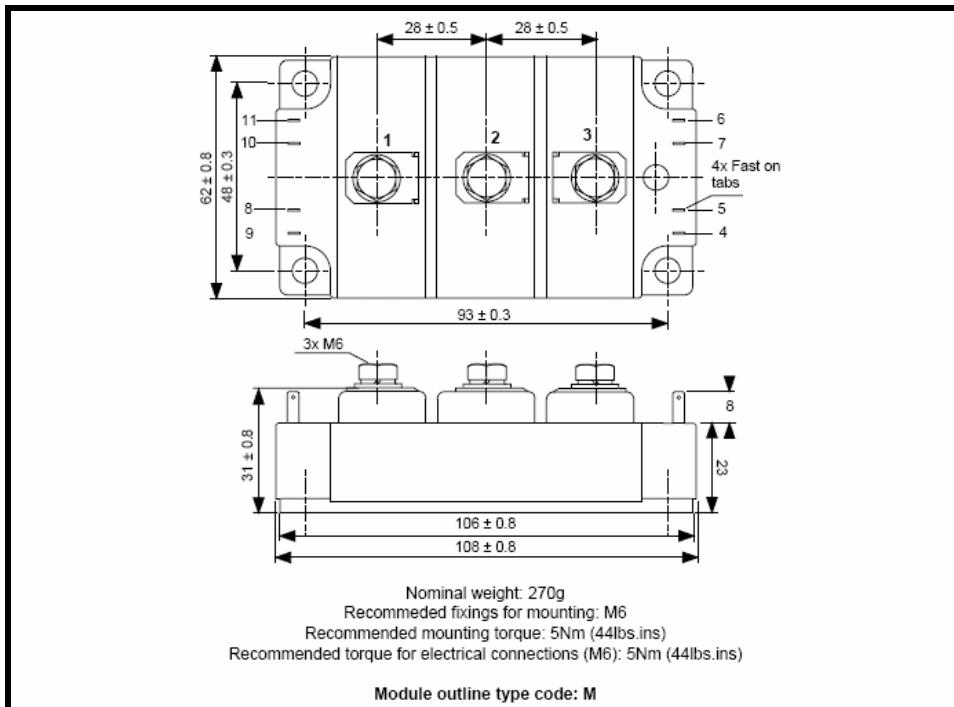

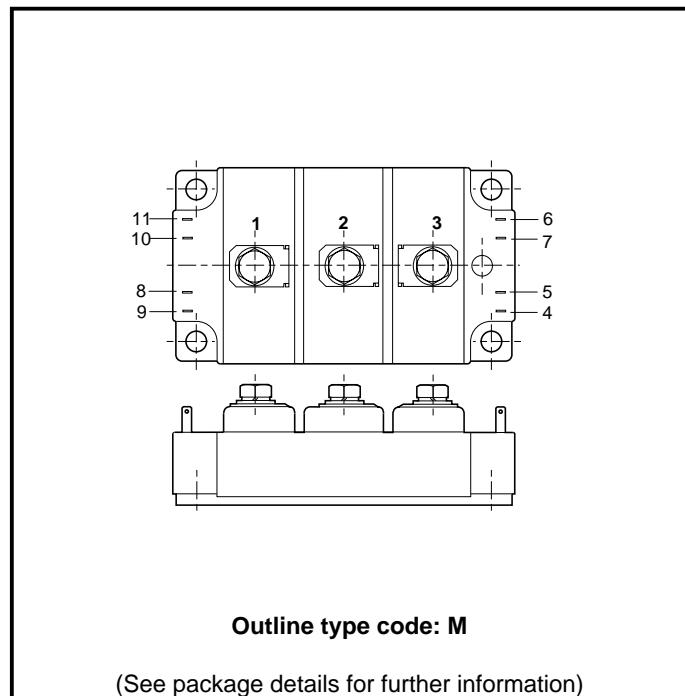

This device is housed in an M-6 modular package whose dimensions and electrical connections are shown in Figure E2.

**Figure E2.** *Dynex DIM200MBS12-A000 Mechanical Dimensions and Pinout.*

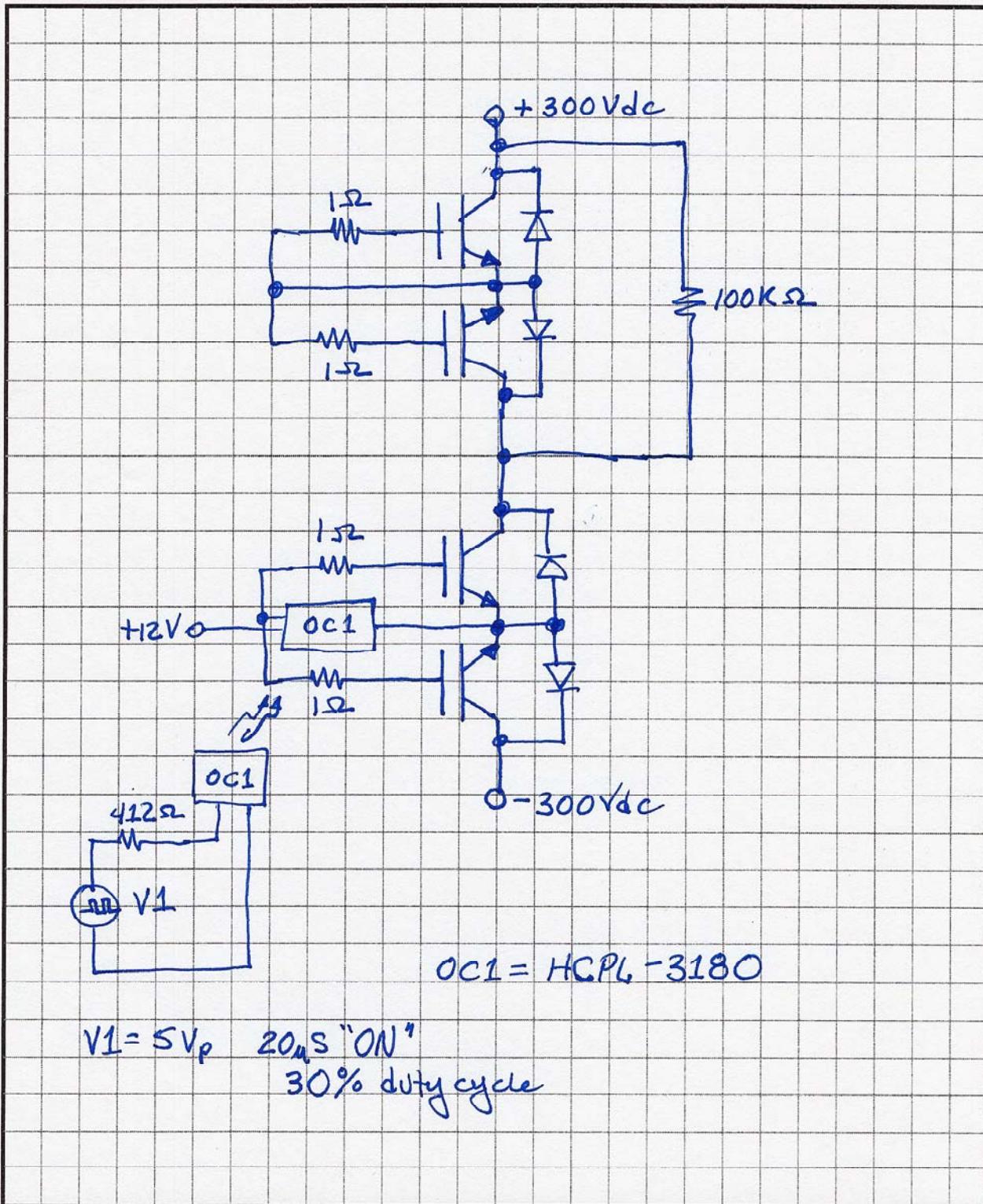

In the ETM Converter circuit application, each of the eight power train IGBTs had an isolated IGBT Driver Board integrated onto the package, as shown in Figure E3. This board consisted of a DC-DC converter, protection circuitry and an optically-isolated IGBT gate driver IC.

**Figure E3. DIM200MBS12-A000 IGBT With IGBT Driver Board.**

## ii.) The First IGBT Failure Encountered

Since the initial power the ETM Converter Prototype had operated more than five cumulative hours when the first failure occurred. This failure manifested itself in the tripping of the internal circuit breakers of the ETM Prototype. Upon closer inspection, it was determined that all four in a single IGBT, had the effect of damaging/destroying all four IGBTs in the output switch matrix (the three phase output and the ground switch devices). It was at the  $150V_{L-N}$  operating point that this IGBT failure occurred.

Upon closer inspection, it was observed that each IGBT failure consisted of a gate-emitter (G-E) shoot-through, whereby the G-E junction was short-circuited (with a resultant resistance less than  $1\Omega$ ). Additionally, the IGBT Driver Board for each device was damaged and was observed to be non-functional – this is a result of the very high fault current that flows from the gate at the time of failure. A shoot-through failure is indicative of a safe operating area (SOA) overstress, where the semiconductor was forced to handle too much energy during a switching event, or from an over-breakdown voltage stress. Since the Prototype was operating at such a low I/O voltage level, the voltage overstress failure option was discounted. The low operating voltage also helped to discount the SOA overstress; so as a result, this failure was suspected to have been a random device failure. This failure will be further discussed in a following section.

The reason all four devices in the output switching matrix were destroyed is a direct result of the ETM Converter architecture. Upon failure of a single device in a short-circuit mode, it serves to permanently (actually temporarily until the protection circuit breaker trips!!) connect the central point of the matrix to a fixed bias point. This fixed bias point destroys each IGBT in turn (each successively failed and shorted IGBT adds to this situation) until all the IGBTs are destroyed. The destruction of all the devices in the switching matrix occurs because the ON cycle time of the resonance pulse (and consequently of any IGBT) is 20us; a time much shorter than the response time of the circuit breaker. After a time period of approximately 100us, all four IGBTs will be destroyed and shortly thereafter, the circuit breaker will trip.

### iii.) The Second IGBT Failure

After the repair of the first failure, the converter was restarted for further debug activities. Unfortunately, after approximately 30 seconds of operation, the Prototype Converter experienced another IGBT failure in the output stage. It was determined that a total of four (4) IGBTs were destroyed before the internal circuit breaker tripped. This was a similar failure result as the first failure encountered. Like the first failure encountered, the I/O voltages were set to  $75V_{L-N}$ , and these failures were also observed to be G-E shoot-through failures for the IGBTs.

Again, since there was no reasonable explanation for this shoot-through event to have occurred, this failure was also assumed to be a random device failure.

### iv.) The Third IGBT Failure

At power-up of the repaired ETM prototype, the internal circuit breaker immediately tripped and it was determined that all four IGBTs in the input switching matrix were damaged/destroyed once again. As was the case for the last failure, this test was conducted at  $75V_{L-N}$  I/O voltages and the IGBT failures were all shoot-throughs.

After this exasperating failure, extensive debug activities were undertaken to determine the root cause of the IGBT failures. As a result, it was revealed that this failure was caused by the fact that although a reasonable value was entered in the data box for the Cycle Time or the Resonance Time (or even that a change may have been made to these two variables) on the GUI, there was no hardware confirmation or update of the parameters in the non-volatile memory (NVM) in the ETM Converter. Additionally, it was determined that there was no guarantee that the parameter data was consistently exchanged properly between the host laptop and the dsPIC/ADSP microcontrollers in the ETM Converter after a change was initiated. And, to make matters worse, there were instances observed where extraneous, random data was loaded into the NVM in the ETM Converter. It was determined that the root cause reason the third failure occurring was that a value of 15us was somehow entered in the NVM as the value of the Resonance Time, Tres. With this time value (approximately 50% of the actual resonant time), the IGBT switches would have been forced to open while carrying their maximum or very

close to their maximum resonant current. This switching situation subjected the IGBTs to stresses exceeding their maximum ratings, in particular their reverse SOA.

In light of the failure mode that accounted for the first two sets of failures observed, this newly-identified failure mode had made sense as the root cause. Rather than just random failures, the previous failures could be accounted for by the NVM random data problem. Although this theory could not be directly verified, it made sense as a reasonable explanation, as the only difference in the failures was the time span that had elapsed before a failure had occurred.

It should be noted that after the NVM-related problem was resolved, the converter was started and stopped more than 100 times and had successfully run at load levels up to **8kW**, having logged an operating time of greater than 40 hours. It was during this time that the lion's share of the performance testing and data collection was achieved.

#### **v.) Fourth (Last) Failure Encountered**

Unfortunately, the fourth and final Prototype failure occurred when the input and output voltages were increased to  $200V_{L-N}$  ( $\sim 350V_{L-L}$ ) and the power was turned on. The circuit breakers tripped within five seconds of power application, indicating an internal fault. Upon cursory troubleshooting the ETM Prototype, it was determined that all the IGBTs in the power train were damaged, along with their associated IGBT Driver Boards. In fact, the IGBT Driver Boards were damaged beyond repair in six of the eight cases (all except for the ground-references switches in the I/O switching matrix). Due to a number of different factors, the testing was halted at this point, and this was the state of the Prototype when the testing was terminated.

The remainder of the failure analysis is speculation based on this very limited troubleshooting and failure analysis, but due to the nature of the damage it was most likely that this failure was caused by  $dV/dt$ -induced turn-on of one or more the off-state IGBTs in the I/O switching matrix. It had been suspected that voltage rate-related problems might exist for the IGBTs at or above the maximum rated I/O voltage of  $235V_{L-N}$  ( $408V_{L-L}$ ), due to the gate drive levels that were utilized. So, it was not entirely surprising that failures occurred at this lower level. It had been a planned task activity that the IGBT Driver Boards were to be redesigned re-spun to incorporate a negative off-state gate bias of at

least 5V in order to improved the predicted dV/dT immunity to greater than 15,000V/us. Several steps were taken to improve the DV/dt immunity of the present hardware (optimizing the gate resistance value and the implementation of an improved gate driver IC), but in the absence of a negative gate bias potential, there was only a limited rate immunity improvement available.

At the operating point at which the failure had occurred, the calculated maximum rate of change was approximately 9,000V/us (dV at the switching common switching node = 1000V and the rise time, dt, for an IGBT = 120ns), which was uncomfortably close to the actual predicted value for the Prototype hardware of 12,000V/us (a number reached using numerous assumptions). For this performance parameter in particular, due to the variability in IGBT characteristics (junction capacitances and switching characteristics), a 2-to-1 (200%) tolerance in threshold sensitivity is desired to absolutely guarantee immunity to the effects, and one that should be measured and treated as a “datasheet” parameter. Due to budget, manpower and schedule constraints, this could not be achieved with the present design. It was *hoped* that unchanged/unimproved hardware would suffice (with adequate dV/dt margin) to enable the Prototype ETM to successfully complete the Performance Testing. This obviously was not the case.

At the time the project was terminated, the next step in the troubleshooting process was to construct a test jig/fixture and to measure/determine the dV/dt turn-on threshold of the actual hardware (IGBT and Driver Board). [The test jig had been constructed but no testing had commenced as of the time of project cancellation.] Additionally, a voltage rate-induced failure mode had been suspected (actually one of a longer list of suspects) as the root cause of the first three failures observed, but the operating level at which the failures occurred was too low to have absolutely been suspected as the root cause. Thus rate-induced failures were almost immediately ruled out in those cases. However, at that time, a new design for the IGBT Driver Board was accomplished – one that included a negative 5V off-state bias to improve that would dV/dt immunity to 15,000V/us. And, after the NVM issue was resolved, the Prototype Converter worked reliably for a long period of time, so the new design was “shelved” for future implementation. But, the change in operating condition caused the ultimate failure of the prototype, and until future work is done to reveal the actual, all the previous words are conjecture and speculation.

## F.) Remaining Tests To Be Performed

The ETM Converter Test Matrix that was planned from early on in the ETM Converter development project was fairly ambitious. It covered the range of tests required, including: Debug, Functional, Performance, Safety/Compliance and System Integration Tests. These represented the tests required to fully characterize the ETM Converter Prototype in order to guarantee its fitness as a potential product, and to reveal any flaws in the design or the topology. This testing was also intended as a gateway to have prepared the Prototype for future testing at Sandia Labs, or another similarly-equipped DOE laboratory.

The test matrix that was planned for Sandia Labs was intended to perform those demanding tests that could not be performed at other lab sites available to the ETM Converter Prototype; most importantly those tests that involved providing variable frequency, variable amplitude input power to the Converter. The Sandia Labs Test Matrix emphasized the variable input tests, and the ability of the ETM Converter to process power from such inputs. It also strived to reveal the durability of the Converter in transient operating condition sweeps for the input of the Converter; these tests had sought to mimic the performance of a permanent magnet generator for a variety of output situations.

Finally, the Revised Performance Test Matrix, as shown in Table G1, was developed as a less aggressive, compromise testing regime to accommodate for the test deficiencies at the Marlboro Test Labs facility – particularly the inability to vary the input operating frequency. This testing was seen as the lead in to the ETM Converter Test Matrix; to have enabled the Prototype to have been thoroughly debugged and still have yielded test results pertaining to Performance test criteria.

### i.) Test Progress Summary

It is clear that the testing that had been performed had only scratched the surface of even the most compromising test plan (Figure F1). This was due to the fact that the four sets of IGBT failures were unexpected, and the unavailability of replacement spares for the third failure set had quite negatively affected the test schedule. Even if adequate

spares had been available, the pauses in the test schedule to repair the Prototype Converter were a distraction and a drain of the very limited manpower available to the project. In the end, the need to make repairs consumed the available schedule and budget and made it impossible to complete the required testing.

**Table F1. Revised Performance Test Matrix.**

| Test                                                                                                           | Purpose                                                                                                                                                                                                                                                                                                                                                      |