# Evaluating the Effects of Aging on Electronic Instrument and Control Circuit Boards and Components in Nuclear Power Plants

*Technical Report*

---

# **Evaluating the Effects of Aging on Electronic Instrument and Control Circuit Boards and Components in Nuclear Power Plants**

**1011709**

Final Report, May 2005

U.S. Department of Energy

1000 Independence Avenue

Washington, DC

EPRI Project Manager

J. Naser

## **DISCLAIMER OF WARRANTIES AND LIMITATION OF LIABILITIES**

THIS DOCUMENT WAS PREPARED BY THE ORGANIZATION(S) NAMED BELOW AS AN ACCOUNT OF WORK SPONSORED OR COSPONSORED BY THE ELECTRIC POWER RESEARCH INSTITUTE, INC. (EPRI). NEITHER EPRI, ANY MEMBER OF EPRI, ANY COSPONSOR, THE ORGANIZATION(S) BELOW, NOR ANY PERSON ACTING ON BEHALF OF ANY OF THEM:

(A) MAKES ANY WARRANTY OR REPRESENTATION WHATSOEVER, EXPRESS OR IMPLIED, (I) WITH RESPECT TO THE USE OF ANY INFORMATION, APPARATUS, METHOD, PROCESS, OR SIMILAR ITEM DISCLOSED IN THIS DOCUMENT, INCLUDING MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, OR (II) THAT SUCH USE DOES NOT INFRINGE ON OR INTERFERE WITH PRIVATELY OWNED RIGHTS, INCLUDING ANY PARTY'S INTELLECTUAL PROPERTY, OR (III) THAT THIS DOCUMENT IS SUITABLE TO ANY PARTICULAR USER'S CIRCUMSTANCE; OR

(B) ASSUMES RESPONSIBILITY FOR ANY DAMAGES OR OTHER LIABILITY WHATSOEVER (INCLUDING ANY CONSEQUENTIAL DAMAGES, EVEN IF EPRI OR ANY EPRI REPRESENTATIVE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES) RESULTING FROM YOUR SELECTION OR USE OF THIS DOCUMENT OR ANY INFORMATION, APPARATUS, METHOD, PROCESS, OR SIMILAR ITEM DISCLOSED IN THIS DOCUMENT.

ORGANIZATION(S) THAT PREPARED THIS DOCUMENT

**Science Applications International Corporation**

## **ORDERING INFORMATION**

Requests for copies of this report should be directed to EPRI Orders and Conferences, 1355 Willow Way, Suite 278, Concord, CA 94520, (800) 313-3774, press 2 or internally x5379, (925) 609-9169, (925) 609-1310 (fax).

Electric Power Research Institute and EPRI are registered service marks of the Electric Power Research Institute, Inc.

Copyright © 2005 Electric Power Research Institute, Inc. All rights reserved.

## CITATIONS

---

This report was prepared by

Science Applications International Corporation

20201 Century Blvd.

Germantown, MD 20841

Principal Investigators

G. William Hannaman

C. Dan Wilkinson

This report describes research sponsored by the Electric Power Research Institute (EPRI) and the U.S. Department of Energy (Award No. DE-FC07-03ID14536, Task #6).

The report is a corporate document that should be cited in the literature in the following manner:

*Evaluating the Effects of Aging on Electronic Instrument and Control Circuit Boards and Components in Nuclear Power Plants.* EPRI, Palo Alto, CA, and U.S. Department of Energy, Washington, DC: 2005. 1011709.

# REPORT SUMMARY

---

Circuit boards used in the electronic instrument and control (I&C) systems of nuclear power plants may suffer from aging failures that can cause a plant trip or unavailability of plant systems. The overall objective of this study was to determine how precursors of failures in I&C circuit boards can be measured and how these measures can be used to estimate the probability of failure during the next operational period within a statistical confidence level. The study provides a framework for the identification of techniques that can be used to monitor circuit board component aging failure modes that could lead to a failure of the circuit.

## Background

The nuclear power industry is currently facing increasing obsolescence issues with original equipment installed for instrumentation, control, and safety system applications. These systems, frequently more than thirty years old, are experiencing aging-induced failures in electronic boards and components. These failures can cause plant trips and reduce the reliability and availability of systems. Most plants take a policy of running to failure and/or periodic replacement—frequently without a good technical basis. Both of these approaches can be very costly. The industry needs a better understanding of the aging mechanisms and observable precursors to failure along with more cost-effective aging inspection, mitigation, and other aging management technologies.

## Objectives

- To classify the failures of electronic boards and components used in I&C systems according to the type of measurable failure mode conditions

- To apply reliability criteria to the components to understand the likelihood of failure using existing data sources

- To propose potential measurement tools and models of failure for input into a condition monitoring and operational assessment process for predicting I&C board failures.

## Approach

The project team reviewed the failure modes identified in EPRI reports 1003568 “Collected Field Data on Electronic Part Failures and Aging in Nuclear Power Plant I&C Systems” and 1008166 “Guidelines for the Monitoring of I&C Electronic Components,” as supplemented by technical papers, IEEE reliability meetings, and contacts with utility people. The team used data on failure modes from Military Handbook 217F to define the likelihood of failure for I&C electronic components. The team defined monitoring methods and techniques based on currently used methods and methods that have been used in laboratories for circuit board testing, for computer hardware testing, software verification and database integrity assurance.

## **Results**

The report describes potentially useful techniques for monitoring the aging of I&C boards. The techniques have been grouped into six methods: periodic testing, reliability modeling, resistance measures, signal comparison, external (passive) measures, and internal (active) measures, each representing distinct theoretical approaches to detection and evaluation. Each technique has significant advantages and disadvantages. The design of hardware and software monitoring systems increases in complexity as the methods become more precise in their ability to measure aging factors, but the technical tools that can be applied to monitoring within the methods have also clearly improved within the last few years as computers and networks have been enhanced to rapidly process large amounts of data.

The report provides a decision process for selecting those circuits and components that could benefit from an upgraded approach for monitoring the effects of aging and highlights areas where future R&D is needed to establish firm recommendations for I&C systems. The report also assesses the relative costs and technical benefits of upgrading circuit-monitoring systems.

## **EPRI Perspective**

As the nuclear power industry is facing increasing aging and obsolescence issues, one area that needs attention is the aging of electronic boards and components used in I&C systems. Existing methods of functional testing of I&C systems typically detect circuit failures after they occur whereas the new monitoring techniques provide indications of failure while the circuit is still functional. This information will make it possible to maximize the operating life of components without suffering circuit failure.

This report presents a number of specific techniques for improving the ability to monitor aging induced changes in circuits and board components that could lead to board failure. Some promising techniques are discussed that have been used in applications outside of electronic circuit board monitoring. Additional R&D efforts are needed to test, confirm, and demonstrate the viability of circuit board monitoring techniques for use as a predictive tool to detect aging induced changes that can lead to circuit failure. Additional engineering studies need to be completed to better quantify the implementation and operational costs and benefits of the viable techniques and to provide sufficient justification for their implementation.

## **Keywords**

Instrumentation and control systems

Electronic boards and components

Electronic board aging

Electronic components aging

Circuit boards

Aging management

Reliability

Predictive maintenance

# ABSTRACT

---

This report addresses understanding the effects of aging on electronic instrument and control (I&C) circuit boards in nuclear power plants. The issue is that circuit boards used in I&C systems may suffer from aging failures that can cause a plant trip or unavailability of plant systems. The overall objective is to determine how precursors of failures in I&C circuit boards can be measured, and how these measures can be used to estimate the probability of failure during the next operational period within a statistical confidence level. This initial study provides a framework for identification of techniques that can be used to monitor circuit board component aging failure modes that could lead to a failure of the circuit. This study has three tasks:

1. Provide (1) a review of information on circuit board aging failure descriptions, and (2) an identification of reliability data for I&C component failures.

2. Propose and review six uniquely different methods and associated techniques that could be applied to measure and predict the effects of aging within I&C boards and circuits.

3. Provide a systematic framework for deciding how to select circuit boards as well as methods for improving the process for monitoring aging effects of circuit boards in nuclear power plants - the framework includes a relative cost benefit assessment for each technique.

Many causes of I&C circuit board failure progress slowly. This opens the possibility for measuring the impacts of aging progression prior to complete failure. Measures of changes in electrical characteristics provide a basis for estimating the probability of failure during the next operational period. Simulation of the aging process can be used to produce a statistical confidence in the probability estimate. Such information can be used to support optimized maintenance planning and decisions.

The ideal result of this project is to define a framework for selecting techniques for aging management that can be applied to any circuit. The techniques should be easy to use and account for various modes of circuit component aging. This is an initial study to examine a wide range of issues and approaches for aging management in electronic systems. The existing state of the I&C systems is that most nuclear power plants were designed using analog control circuits and relay controlled safety circuits. Hardwired electric relays have become obsolete, as electronic circuits rely on integrated circuits and software controls to accomplish the same functions. Current technology permits software logic to replace relay logic and analog controls to activate safety and control circuits. Therefore, circuit boards can become obsolete in less than a decade and as this older equipment fails, the spare parts inventories become depleted and failures can't be easily repaired. Then there is an increasing need for older technology I&C systems to be upgraded or replaced. Even new solid state, integrated circuits and systems can become obsolete in a few years. Older nuclear power plants are in various stages of identifying

---

obsolescence, upgrading and replacing I&C systems. As a result the key control and protection systems in nuclear plants use a range of technologies in different plants, and even within the same plant. Thus, the state of I&C technology within plants may be considered as fragmented with respect to replacement components and the amount of digital versus analog I&C systems.

In an absolute sense the rate of failure and replacement for electronic circuit boards may not be considered high. However, from a regulatory point of view, and also relative to other major plant systems, the I&C system repair and replacement rates are relatively high. For example, individual circuit boards are typically repaired or replaced several times during the life of a plant. Therefore, this higher rate of circuit board replacements makes them of low concern as an aging issue in plant license extension, whereas, insulation on the wires connecting the I&C systems is a required aging issue that must be addressed in license extension applications.

Reviewing the descriptions of aging failures in circuit boards provides some very valuable insights. For example, a conclusion from review of information from EPRI (EPRI 2002, EPRI 2003 and EPRI 2004) is that the failure end state of most electronic components is either an open or short circuit. These findings help simplify the design of potential measurement systems by permitting the monitoring of each board circuit to be treated as an equivalent circuit with measurable electronic parameters such as voltage, impedance, resistance, current, and ground resistance. Changes in these parameters become precursor indications of degradation that could lead to a complete failure.

Aging induced failures (due to temperature, operating stress, quality of components, corrosion, and environment) are slow and many intermediate states of partial failure exist. Changes in the electrical parameter signals from the circuit can be measured before an inoperable condition is reached. In the case of a rapid shock induced failure (e.g., high voltage spikes, rapid corrosion or high temperature effects from fire, etc.) the time between the triggering condition and the component failure would be too short for corrective action to be taken before a failure.

A variety of technology and software methods can be used to develop improved monitoring, including continuous circuit monitoring, and active as well as passive testing approaches.

1. The EPRI reports developed by EdF (EPRI 2002 and EPRI 2004) show the impact of component failures involving capacitance and inductance that are sensitive to frequency variation tests.

2. Simple voltage tests could easily identify circuits that are drifting toward shorts or open circuits.

Replacement of an aging component with a spare board may not always be possible, because of obsolescence. If this is the case, then the ability to locate the failed component supports the process of replacing individual components on a board when replacement circuit boards are not available. This circuit board reconditioning can be enhanced by early identification of precursor failures.

---

Considerable failure data are available for electronic components. These data are complied as failures per unit time for like components. The grouping process reduces the details of the failure modes in MIL-HBK-217F (i.e., descriptions of the failure modes typically found in event data and root cause analysis are subsumed into the term “failure” so that the detail is lost). The MIL-HBK-217F data can be assigned with some judgment to the individual board components. Since a board or circuit contains a combination of many components, board failure rates can be approximated by a sum of failure rates for the components following the recommended methodology in MIL-HDBK-217F.

It should be noted that information about aging failures of individual components of circuit boards has been presented previously, and therefore is not repeated in this report. References such as EPRI 2002 and EPRI 2004 identified the families of components that are of greatest concern for aging and failure, described component technologies typically found in nuclear plant circuit boards, and presented field data from a number of plants. These field data included failure analysis reports and visual inspections of boards and components. Root causes of failures are also presented, along with photos in many cases, to provide examples of various failure types. Furthermore, the reports describe postulated aging mechanisms and identify early aging indicators, which may be measured in a simple manner. Therefore, any reader who wishes to review detailed examples of various types of board and component failures should refer to these prior reports.

Potentially useful techniques for monitoring the aging of I&C boards are presented in Section 4. The techniques have been grouped into six methods of periodic testing, reliability modeling, resistance measures, signal comparison, external (passive) measures, and internal (active) measures, representing unique theoretical approaches for detection and evaluation. The technical tools that can be applied to monitoring within the methods have clearly improved within the last few years as computers and networks have been enhanced to rapidly process large amounts of data. Each technique has significant advantages and disadvantages. Human inspections can detect a surprisingly large group of aging issues, but unfortunately, most likely after the failure occurs. As the methods become more precise in their ability to measure aging factors, the design of the hardware and software monitoring system increases in complexity.

Section 5 provides a decision process for selecting those circuits and components that could benefit from an upgraded approach for monitoring the effects of aging. This investigation of providing a systematic decision process has highlighted areas where responses to the decision element questions are not yet precise enough to establish firm recommendations for systems. Rather, technical questions that should be answered have been identified for future R&D. To develop a cost effective program for upgrading the circuit monitoring systems, the relative costs and technical benefits are assessed to help refine the recommendations for the next steps. These are provided in Section 6.

I&C maintenance personnel and managers can benefit from this report. The business objective for developing I&C board monitoring systems includes identification of circuit board aging degradation before board failure, which could cause an unplanned outage or power reduction.

---

The value of upgrading the existing functional testing process, with techniques for monitoring the aging effects of components within the circuit, is expected to become a higher priority with increasing circuit failures due to aging. The existing methods typically detect circuit failures after they occur whereas the new monitoring techniques provide indications of failure while the circuit is still functional. This will give operators information upon which to maximize the operating life of components without suffering circuit failure.

Most monitoring techniques have been applied to mechanical equipment or to a process, but not to circuits that control the mechanical equipment or process. Thus, a need exists for integrating the hardware and software components necessary to monitor aging of components within various circuit types according to the use of a specific technique.

Once the system operation of a circuit monitoring technique(s) is developed and demonstrated it will find wide applications in power plants for circuits that are classified as important to plant operation.

## ACRONYMS

---

A/D—Analog to Digital

AC— Alternating Current

ANS—American Nuclear Society

ANSI—American National Standards Institute

ASME—American Society of Mechanical Engineers

CFR— Code of Federal Regulations

D/A —Digital to Analog

DC— Direct Current

DOD— Department of Defense

EdF— Electricite de France

EOPs —Emergency Operating Procedures

EPRI—Electric Power Research Institute

EPROM—Electronic Programmable Read Only Memory

ESFAS—Engineered Safety Features Actuation System

ETM— Electronic Temperature Monitor

FET—Field Effect Transistor

HRA— Human Reliability Assessment

I&C—Instrumentation and Controls

IAEA —International Atomic Energy Agency

IC—Integrated Circuit

IEEE—Institute of Electrical and Electronic Engineers

INPO —Institute for Nuclear Power Operations

JFET—Junction Field Effect Transistor

LCDs —Liquid Crystal Display

LCO— Limiting Condition of Operation

LEDs —Light-Emitting Diodes

MIL-HDBK —Military Handbook

MOS— Metal Oxide Semiconductor

MTBF— Mean time between failures

NEI — Nuclear Energy Institute

NRC – Nuclear Regulatory Commission

OpAmp—Operational Amplifier

PCB—Printed Circuit Board

PC—Printed Circuit

---

PM—Preventive Maintenance

POF—Physics of failure

PSAs— Probabilistic Safety Assessments

PTH —Pin through Hole (PTH) solder joints

R&D —Research and Development

RAM —Random Access Memory

ROM —Read-Only Memory

RTD—Resistance Temperature Detectors

SCSI —Small Computer System Interface

SMT — Simultaneous Multi Threading (SMT) solder joints

SRAM —Static RAM

SSCs— Structures Systems or Components

SSR—Solid-State Relay

US —United States

# CONTENTS

---

|                                                             |            |

|-------------------------------------------------------------|------------|

| <b>1 INTRODUCTION .....</b>                                 | <b>1-1</b> |

| Bathtub Curve .....                                         | 1-1        |

| Foundations for Addressing Aging .....                      | 1-2        |

| Application of a Periodic Test Interval .....               | 1-3        |

| Reliability Modeling.....                                   | 1-3        |

| Condition Monitoring and Operational Assessment .....       | 1-4        |

| Continuous Monitoring.....                                  | 1-4        |

| Framework for Improved Aging Monitoring .....               | 1-5        |

| <b>2 CIRCUIT BOARD AGING FAILURES .....</b>                 | <b>2-1</b> |

| Component Listing .....                                     | 2-1        |

| Aging Failure Modes .....                                   | 2-2        |

| <b>3 RELIABILITY DATA.....</b>                              | <b>3-1</b> |

| Component Specific Failure Data.....                        | 3-1        |

| Event Data Sources .....                                    | 3-2        |

| Failure Rate Equations.....                                 | 3-2        |

| <b>4 METHODS FOR DETECTING I&amp;C BOARD FAILURES .....</b> | <b>4-1</b> |

| Circuit Board Failure Detection and Prediction Methods..... | 4-2        |

| Method 1 Periodic Inspections .....                         | 4-2        |

| Functional Testing .....                                    | 4-2        |

| Visual Inspections .....                                    | 4-2        |

| Advantages.....                                             | 4-3        |

| Disadvantages: .....                                        | 4-3        |

| Method 2 Reliability Modeling.....                          | 4-4        |

| Advantages.....                                             | 4-4        |

| Disadvantages .....                                         | 4-5        |

---

|                                                                      |            |

|----------------------------------------------------------------------|------------|

| Example Application .....                                            | 4-5        |

| Method 3 Measures of Resistance .....                                | 4-13       |

| Ground Resistance Testing .....                                      | 4-13       |

| Leakage Current Testing .....                                        | 4-13       |

| Advantages: .....                                                    | 4-14       |

| Disadvantages: .....                                                 | 4-14       |

| Method 4 Signal Comparison Measures .....                            | 4-15       |

| Advantages: .....                                                    | 4-15       |

| Disadvantages: .....                                                 | 4-15       |

| Method 5 Passive Measurement Systems .....                           | 4-16       |

| Circuit Parameter Measures .....                                     | 4-16       |

| Environmental Parameter Measures .....                               | 4-17       |

| Advantages: .....                                                    | 4-17       |

| Disadvantages: .....                                                 | 4-17       |

| Method 6 Active Measurement System .....                             | 4-18       |

| Current or Voltage Change .....                                      | 4-18       |

| Signature Analysis .....                                             | 4-19       |

| Pattern Recognition .....                                            | 4-19       |

| Frequency Analysis .....                                             | 4-19       |

| Advantages .....                                                     | 4-20       |

| Disadvantages .....                                                  | 4-20       |

| Review of Methods and Techniques .....                               | 4-21       |

| <b>5 SELECTING A METHOD FOR MONITORING CIRCUIT BOARD AGING .....</b> | <b>5-1</b> |

| Considerations for Addressing Electronic Component Aging .....       | 5-2        |

| Existing Approach to Managing Aging .....                            | 5-2        |

| Evaluating Circuit Board Failure Probabilities .....                 | 5-2        |

| Decision Process Elements .....                                      | 5-3        |

| Decision Element 1: Importance .....                                 | 5-3        |

| Classification With Maintenance Rule .....                           | 5-3        |

| Classification Following AP-913 .....                                | 5-4        |

| Critical Circuits .....                                              | 5-4        |

| Run-to-Failure Circuits .....                                        | 5-5        |

| Non-Critical Circuits .....                                          | 5-5        |

| Decision Element 2: Observability .....                              | 5-6        |

---

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| Control Circuits .....                                                 | 5-6        |

| Protection Circuits.....                                               | 5-8        |

| Decision Element 3: Detectability .....                                | 5-10       |

| Detection Methods.....                                                 | 5-11       |

| Monitoring Approaches.....                                             | 5-11       |

| Decision Element 4: Predictability .....                               | 5-11       |

| Reliability and Physics of Failure Models.....                         | 5-12       |

| Statistical Correlations .....                                         | 5-12       |

| Synopsis .....                                                         | 5-12       |

| Decision Element 5: Repairability.....                                 | 5-13       |

| Existing Repair or Replacement Process .....                           | 5-13       |

| Improved Repair or Replacement Process .....                           | 5-13       |

| Decision Mapping Logic .....                                           | 5-14       |

| Summary of Decision Process Considerations for Utilities.....          | 5-15       |

| Importance.....                                                        | 5-15       |

| Observability .....                                                    | 5-16       |

| Detectability .....                                                    | 5-16       |

| Predictability .....                                                   | 5-17       |

| Repairability .....                                                    | 5-17       |

| Illustration of Decision Process .....                                 | 5-17       |

| Resistance Components.....                                             | 5-17       |

| Capacitor Components .....                                             | 5-18       |

| Integrated Circuits.....                                               | 5-18       |

| <b>6 QUALITATIVE COST BENEFIT OF AGING MONITORING TECHNIQUES .....</b> | <b>6-1</b> |

| Purpose.....                                                           | 6-1        |

| Relative Technical Benefit.....                                        | 6-1        |

| Relative Cost.....                                                     | 6-3        |

| Cost Benefit Comparison .....                                          | 6-5        |

| Reliability Modeling.....                                              | 6-6        |

| Visual Inspections.....                                                | 6-6        |

| Environmental Parameter Testing .....                                  | 6-6        |

| Functional Testing .....                                               | 6-6        |

| Leakage Current and Resistance Testing .....                           | 6-6        |

| Passive Parameter Monitoring .....                                     | 6-7        |

---

|                                                          |            |

|----------------------------------------------------------|------------|

| Signal Change Testing .....                              | 6-7        |

| Signal Comparison Measures .....                         | 6-7        |

| Signature Analysis Testing .....                         | 6-7        |

| Pattern Recognition and Frequency Analysis Testing ..... | 6-7        |

| <b>7 FINDINGS.....</b>                                   | <b>7-1</b> |

| Summary .....                                            | 7-1        |

| Recommendations .....                                    | 7-2        |

| <b>8 REFERENCES .....</b>                                | <b>8-1</b> |

| <b>A APPLICATION OF AGING THEORY .....</b>               | <b>A-1</b> |

| Purpose of MIL-HDBK-217.....                             | A-1        |

| Failure Rate Equations.....                              | A-1        |

| Application of Arrhenius Equation in Aging .....         | A-2        |

| Accuracy of MIL-HDBK-217F Predictions .....              | A-3        |

| References .....                                         | A-3        |

| <b>B DEFINITIONS OF COMPONENTS.....</b>                  | <b>B-1</b> |

| Components Found on Circuit Boards .....                 | B-1        |

## LIST OF FIGURES

---

|                                                                                                                      |      |

|----------------------------------------------------------------------------------------------------------------------|------|

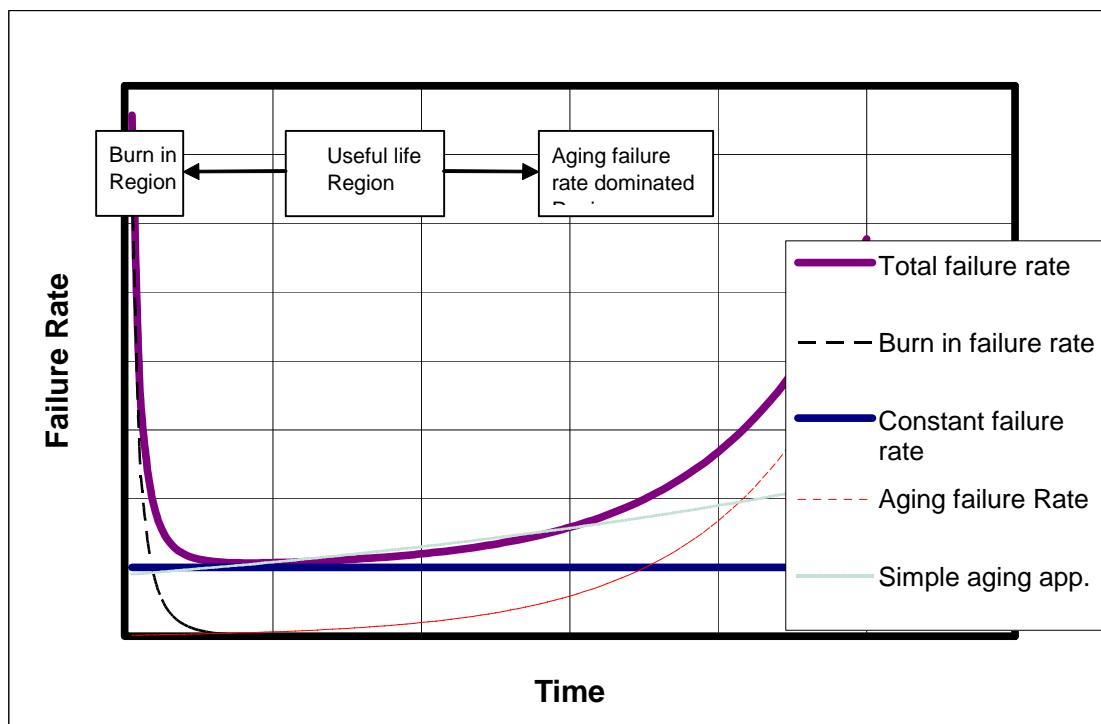

| Figure 1-1 Example Bathtub Failure Rate Curve .....                                                                  | 1-1  |

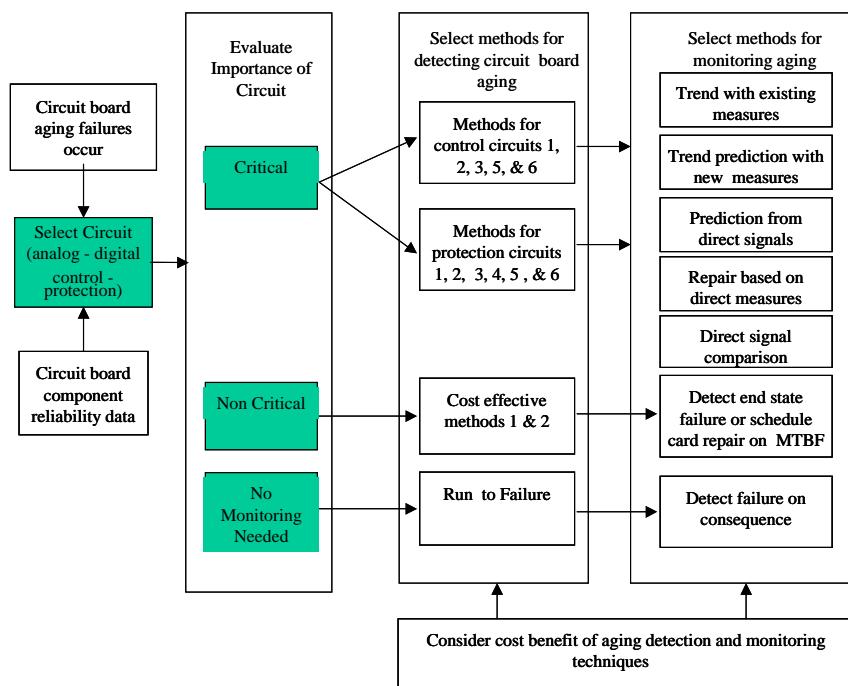

| Figure 1-2 Framework for Considering Improved Circuit Board Monitoring for Aging .....                               | 1-5  |

| Figure 4-1 Example of a Circuit Board With Various Components .....                                                  | 4-5  |

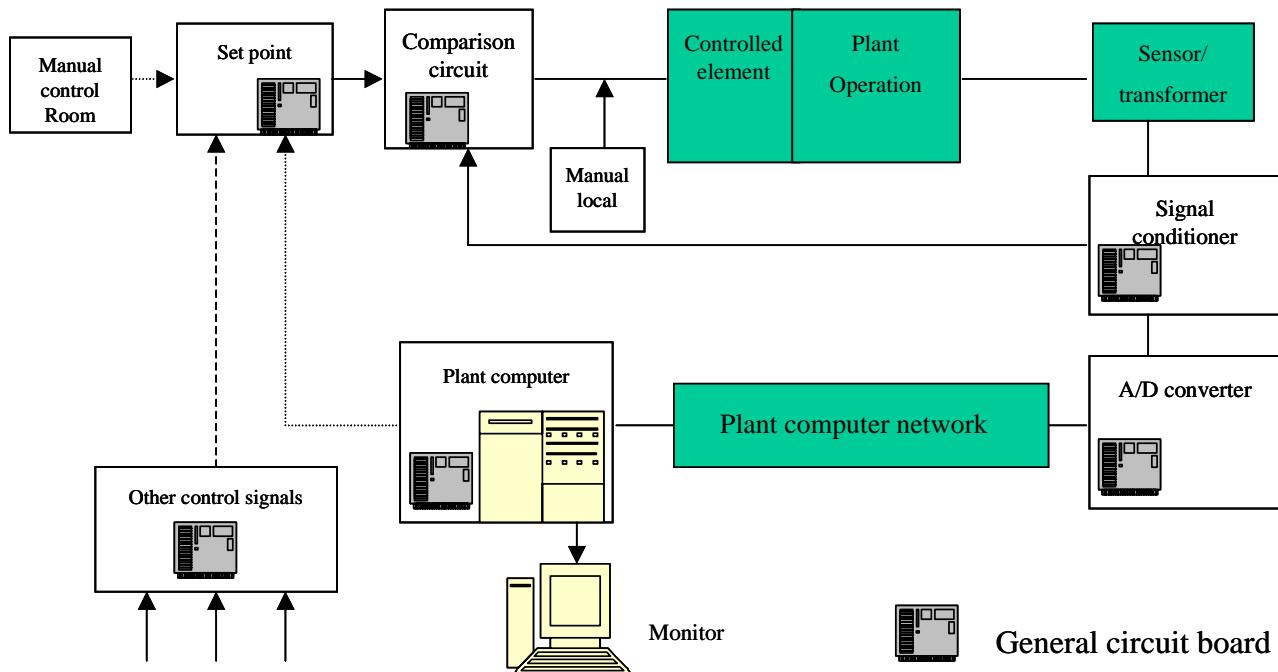

| Figure 5-1 Example Analog Control Circuit With Circuit Boards .....                                                  | 5-7  |

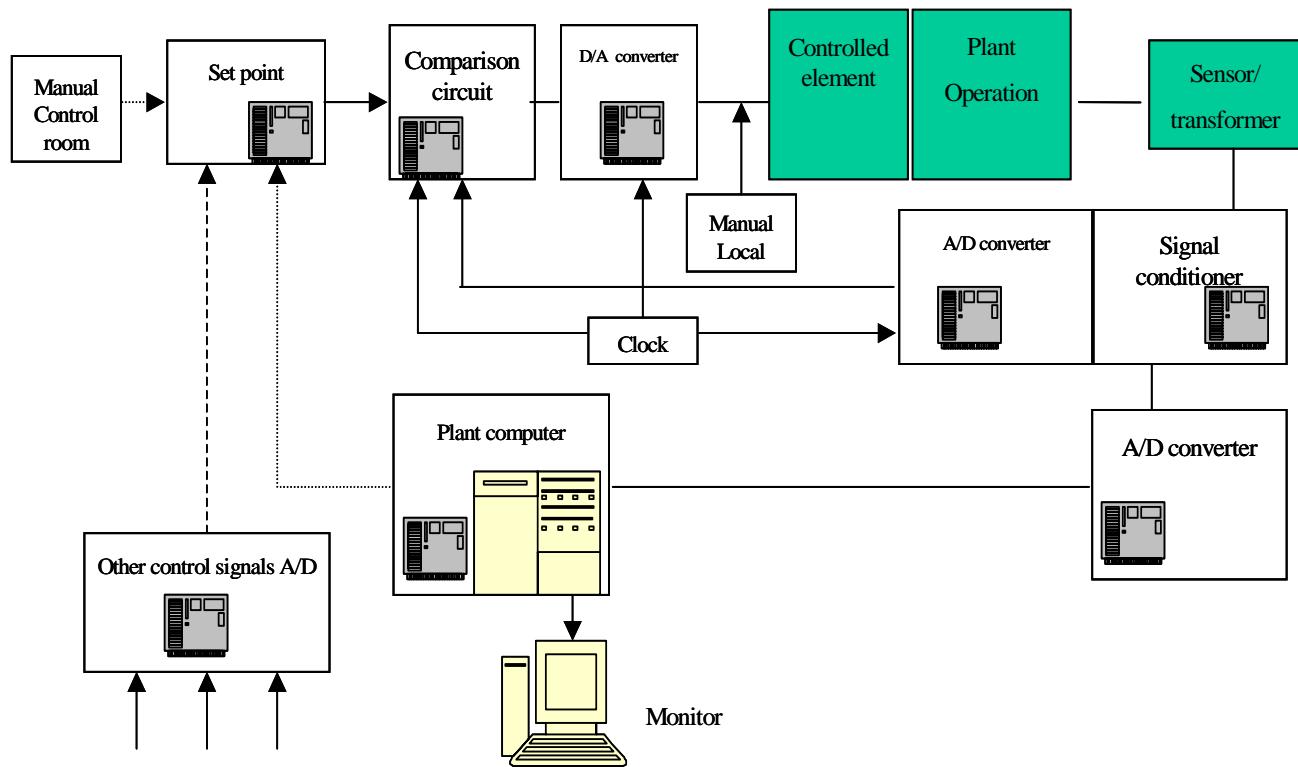

| Figure 5-2 Example Digital Upgrade Control Circuit .....                                                             | 5-8  |

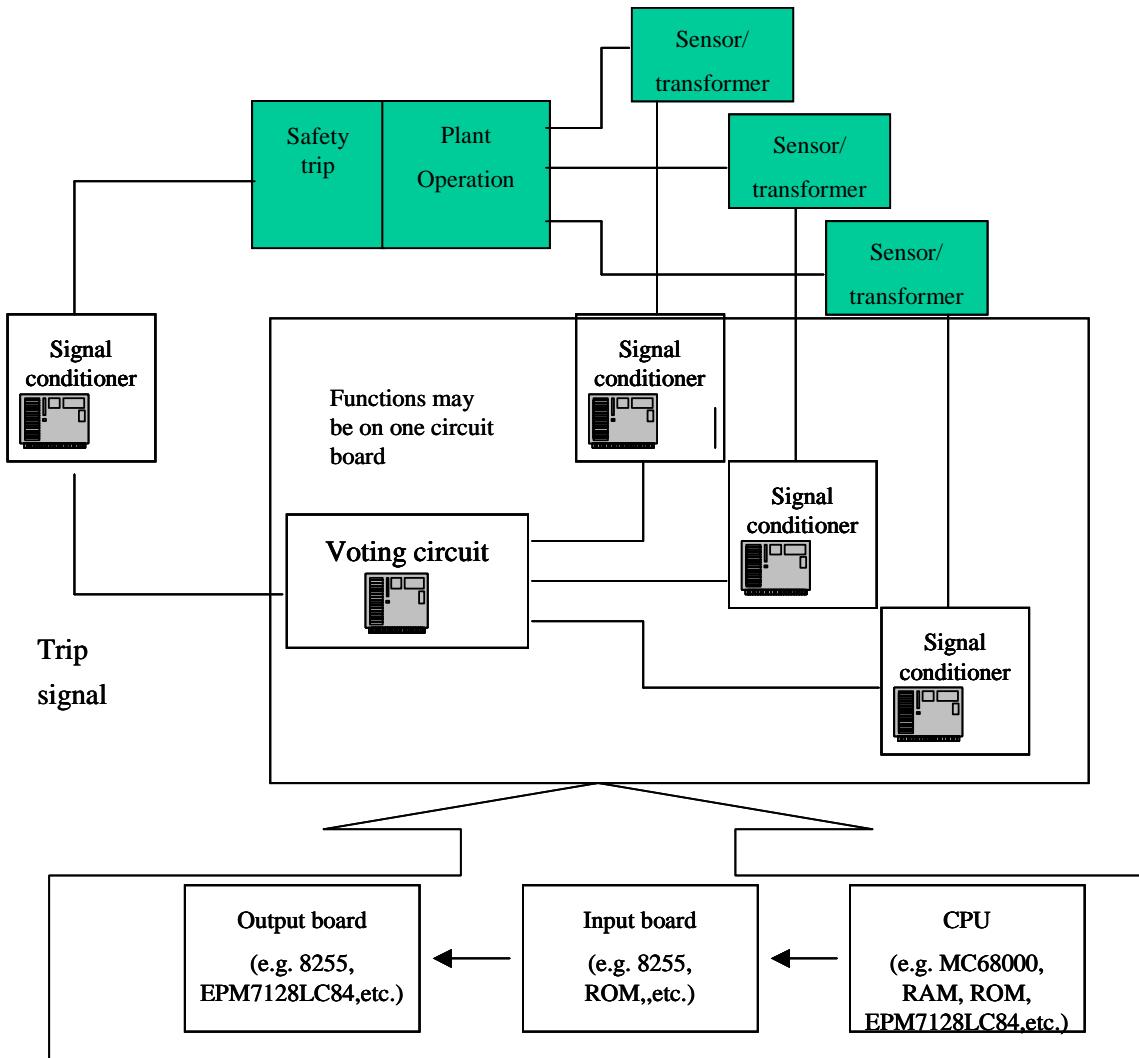

| Figure 5-3 Example Plant Protection Logic Circuit With Train Components .....                                        | 5-9  |

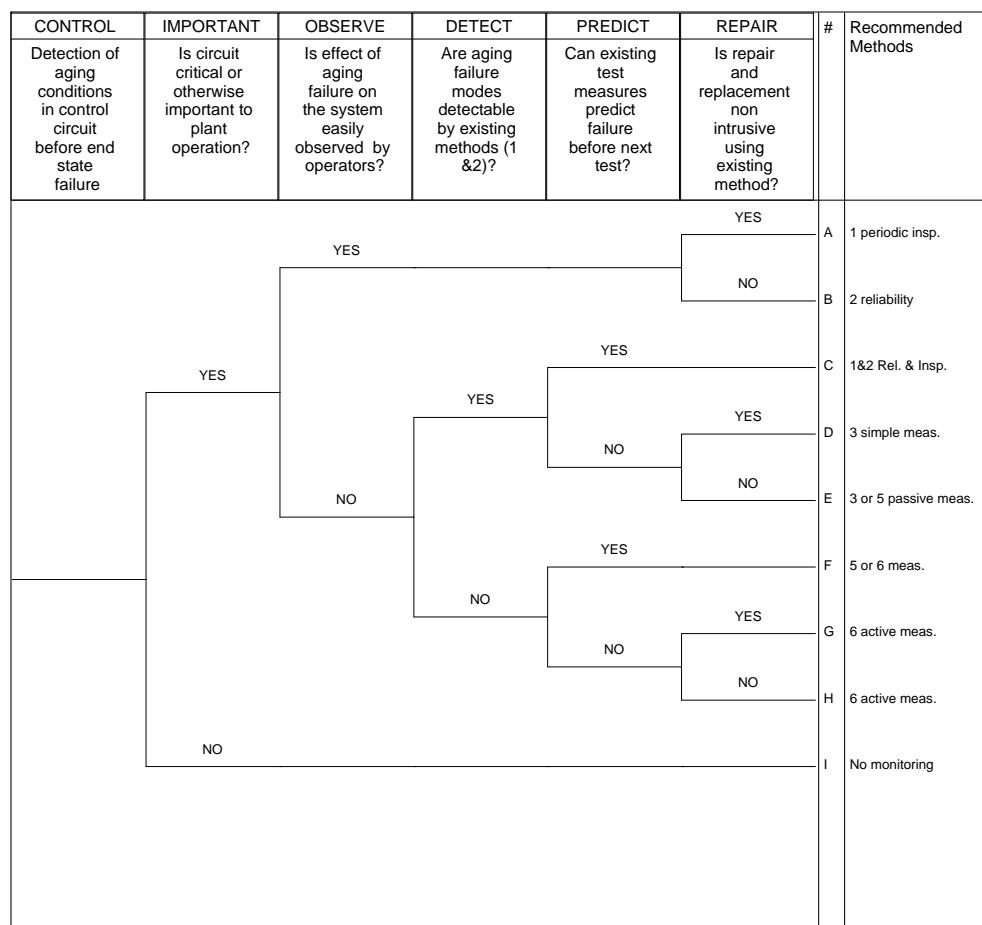

| Figure 5-4 Control Circuits' Progressive Aging Decision Tree .....                                                   | 5-14 |

| Figure 5-5 Protection Circuits' Progressive Aging Decision Tree .....                                                | 5-15 |

| Figure 6-1 Comparison of Relative Cost Benefit Inferred for Each Technique as Applied<br>to a Selected Circuit ..... | 6-8  |

## LIST OF TABLES

---

|                                                                                                                                 |      |

|---------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2-1 Listing of Components Typically Found on Circuit Boards .....                                                         | 2-1  |

| Table 2-2 General Effects of Aging on Resistors, Capacitors, Transformers and Other Components on I&C Electronic Boards.....    | 2-3  |

| Table 2-3 General Effects of Aging on Integrated Circuits on Chips on I&C Electronic Boards.....                                | 2-3  |

| Table 2-4 General Effects of Aging on Printed Circuit Electronic Boards .....                                                   | 2-4  |

| Table 3-1 Assigning Failure Rate Data for Electronic Components in MIL HBK 217F to EdF Components in Table 2-1 .....            | 3-3  |

| Table 4-1 Summary of Methods for Detecting and Monitoring Aging in Circuit Boards .....                                         | 4-1  |

| Table 4-2 I&C Board Materials, Part Descriptions, and Failure Rate Estimate.....                                                | 4-6  |

| Table 4-3 Review of the Potential for Techniques to Identify Precursors of Aging Failure in Electronic Components .....         | 4-22 |

| Table 4-4 Review of the Potential for Techniques to Identify Precursors of Aging Failure in Integrated Circuits and Chips ..... | 4-23 |

| Table 4-5 Review of the Potential for Techniques to Identify Precursors of Aging Failure on Circuit Boards.....                 | 4-24 |

| Table 5-1 Techniques for Detecting Precursors and Progression of Aging Failures in Circuits .....                               | 5-1  |

| Table 5-2 Maintenance Rule Questions to Assess Circuit Importance.....                                                          | 5-4  |

| Table 5-3 Classification of Circuit Types Following AP 913 (INPO 2003) Elements.....                                            | 5-5  |

| Table 5-4 Relationship Between the Detection Method, Technique and Monitoring Category.....                                     | 5-10 |

| Table 6-1 Qualitative Review for Detecting Aging Degradation With Technique .....                                               | 6-2  |

| Table 6-2 Qualitative Review of Cost for a Technique to Detect Aging Degradation.....                                           | 6-4  |

| Table A-1 First Order Activation Energies .....                                                                                 | A-2  |

# 1

## INTRODUCTION

---

An important metric commonly used to measure and specify the lifetime of electronic components and circuit boards is the mean time between failures (MTBF). This is the mean time until the group of devices will fail. The MTBF is a function of the failure rate of the circuit board and the components on it.

### Bathtub Curve

The failure rate for most modern electronic components has a distinctive "bathtub" curve that represents their failure characteristics (Kumamoto and Henley 1996, Wowk 1991, and Ireson and Coombs 1988). The bathtub curve in Figure 1-1 provides a means for discussion of the characteristics of the statistical failure rate during three phases of the component life burn in, useful life, and aging dominated

**Figure 1-1**

**Example Bathtub Failure Rate Curve**

As shown in Figure 1-1 during the early life of the component (referred to as the burn-in phase), it's more likely to fail due to the initial manufacturing defects and introduction of damage during assembly and testing. The initial testing of electronic components uses high temperatures to act as a time accelerator to verify limits of failure conditions and eliminate obvious defects in the subsequent manufactured devices.

Once this initial burn in phase is over, through factory tests and initial testing at the site, a device's overall failure rate typically remains quite low for a number of years. This MTBF or useful life is expected to last more than ten years for electronic devices built in the 1980s, and operated within specified limits for the entire time period.

The useful life ends when the failure rate increases due to age related failures. Examples of age related failures include insulation breakdown, increases in current leakage, loss of resistance and loss of capacitance. Aging is impacted by long term stress from voltage differential, voltage cycles on specific components, and other factors.

For the purposes of this document it is assumed that the burn in failure period has passed, and components on the circuit boards are either in the constant failure rate period or transitioning from the useful lifetime into a period of increasing failure rate due to aging. The impact of failures during these periods is that circuits controlling the operation of equipment in the plant can fail in ways that can cause normally operating equipment to operate spuriously and then, for example, could cause controlled equipment such as a turbine generator to reduce power or go off line without advanced notice. In the case of safety systems the actuation signal might become unavailable due to aging failures on the electronic boards or operate spuriously. Such spurious actions can result in significant costs to the plant in lost revenue from generation, or extended down times for trouble shooting the cause of the failure. With these assumptions in mind the next step is to establish rationale foundations for addressing aging circuit boards that could lead to the identification of improved methods for limiting the impact of failures on the safety and operation of plants.

## **Foundations for Addressing Aging**

Utilities operating power plants are well aware of the aging issues and have adopted a variety of rationales for protecting the plant from unexpected circuit failures that go beyond the simple procedure of running the circuits until failure occurs. In general the proactive rationales can be characterized in four groups. The groups are (1) application of technical specifications to perform periodic testing, (2) replacement of a circuit board based on an estimated MTBF using statistical component reliability methods<sup>1</sup>, (3) use of condition monitoring and operational assessment models<sup>2</sup> to predict the need for replacement, and (4) continuous monitoring to warn of precursors of failure.

---

<sup>1</sup> DiSandro and Torok 2005 state that "There is no accepted methodology to quantify the failure probabilities of a control operation operating within a multitasking operating system environment."

<sup>2</sup> Condition monitoring assessments use past performance to evaluate likelihood of failure. Operational assessments define the failure probability over next operating cycle and may include statistical uncertainty bands.

### ***Application of a Periodic Test Interval***

Plant protection systems are subject to periodic surveillance that detects failed modules. This application currently involves periodically testing the plant protection circuits during outages or by testing one of the redundant circuits during operation. When a circuit is found to be out of specification for its intended use, an action is taken such as recalibrating or replacing the controlling circuit boards (if not obsolete). If replaced from stock, the failed printed circuit board (PCB) is typically repaired and returned to stock (EPRI 2003). This rationale is known as wait until a failure is discovered, and then restore the circuit, which is also called "run to failure." In some cases an aging failure can progress to a complete failure between the test intervals. The test interval is usually found in the technical specifications. Because of long life of many circuit boards the test interval in the technical specifications is on the order of 18 to 24 months to coincide with the refueling interval. Hence, if there is no pre-warning time of failure, the only question becomes, "Is the circuit operable as tested or is it failed?" Using this rationale, circuit components that pass a functionality test with significant aging degradation can be placed back into service with no understanding of the degree of degradation.

### ***Reliability Modeling***

A second rationale for aging management of circuit boards is to use either the manufacturers recommended replacement schedule or calculate board specific MTBFs to establish a generic replacement schedule. Use of a replacement schedule defined by the circuit board MTBF relies on failure rate data from a population of similar boards. Determination of an MTBF then relies on generic information that might not apply to the actual operational conditions for the circuit board components in the plant. Thus, a large uncertainty must be applied to the MTBF and, if a 90% confidence level is used, a board with a nominal MTBF of 15 years might be replaced at 3 or 4 years. This can cause the cost of maintenance for aging failures to be more than actually needed.

Reliability models for electronics, including MIL-HDBK 217F data and models, can be used to predict the life of many electronic systems, such as computers and consumer goods, which may have a short life, typically two to five years, and critical applications, such as in the case of power plants, where life may be 15 years or more (EPRI 2003). However, when using this rationale, there is no warning time for a specific component failure on a specific board, and failures during the next test interval can trigger unplanned plant outages.

In typical reliability models component failures are assumed to be "random", i.e. exponentially distributed. A model such as this has no "infant mortality" or "wear out" region. Physics of failure (POF) approaches can describe the "life" of electronic products where life is limited by predictable physical mechanisms (Ireson and Coombs 1988). These models work well, e.g., for the case of solder joint fatigue by thermal cycling. However, POF approaches are not adequate for large systems, with disparate part types, where the environmental conditions are benign (i.e., there is no failure forcing stress on the component).

In power plant applications, circuit boards are typically operated in a control room with carefully controlled environmental conditions. So, EPRI (EPRI 2002 and EPRI 2004) conducted a large measurement program on samples of aged control circuit boards to determine what components

age, and by how much, over 20 years or more. The results, in concert with additional analysis, can be used to establish maintenance strategies for control systems using similar components, which exhibit the same failure mode and rate characteristics.

### **Condition Monitoring and Operational Assessment**

A third foundational rationale for board replacement begins with the initial recommendation for replacement, and based on an evaluation of measures of a specific circuit condition and on use of the information in models that predict the probability of board failure adjusts the replacement interval. This type of proactive maintenance is normally practiced for mechanical components, but no references to such proactive methods have been found in the technical literature for electronic systems (Loman et. al. 2003).

Condition monitoring relies on measurable test information given from a circuit to develop inputs into a model for calculating the probability of circuit failure. In the case of condition monitoring and evaluation of the probability that the circuit failure would have occurred over the last cycle can be calculated. In the case of operational assessment the probability of failure during the next cycle can be estimated. Given this information the board could be left in place or replaced proactively.

This rationale requires measures upon which to predict the likelihood of failure in the next operating cycle. The predictions rely on statistical models, which may be derived from reliability models, but are adapted to a specific circuit through a correlation between the measured information and inputs to the failure probability quantification. An important question is then how much warning time is given between the measurement of an aging failure condition and loss of the circuit function? Improved circuit availability is possible, if the warning time for circuit replacement is short relative to the test interval based on refueling outages<sup>3</sup>. The improved warning time based on anomalous indications is a basis for replacement before failure.

### **Continuous Monitoring**

A fourth rationale for determining the board replacement interval is to provide a means for continuous monitoring so that the results of the condition monitoring calculation and the operational assessment are the same. This occurs when the time interval between measurements approaches zero. If rapid changes in current flow are observed, and these changes are interpreted as precursor indications by trending, then this indicates that the maximum life of a component on a specific board is approaching or has been reached.

This rationale for board replacement has not been applied by utilities, but represents a more idealized approach that could be established. It provides a warning of the aging impact long before the failure would occur. It is compatible with a philosophy of replacement just in time and yet allows the operators to maximize the useful circuit board life. It would require specialized monitoring equipment, and may be cost effective when applied to key circuits.

---

<sup>3</sup> Typical refueling intervals are in the range of 18 to 24 months in US nuclear power plants.

Use of continuous monitoring could be one reason to select industrial grade boards in the important circuits. This would replace savings in one area with the increased cost of constant monitoring. In NEI, 2001b, the cost of a board that meets nuclear standards is about five times the cost of an industrial grade board that can perform the same function for which it is intended. The industrial-grade electrical circuit board could be purchased for \$1,160, or \$5,700 for the same circuit board under nuclear standards. “The main difference in cost is the extent of the process used to verify the component’s performance capability. Commercial industrial standards are entirely satisfactory for many applications with low safety-significance in nuclear power plants. In fact, they already are widely used in these facilities. Their use could be expanded substantially, and it simply makes sense to do so” (NEI 2001b).

## Framework for Improved Aging Monitoring

A framework for integrating the issues related to upgrading circuit board functional testing to include aging monitoring is needed. Figure 1-2 provides a framework for considering how new techniques can be considered for application in existing plants and what type of monitoring might be associated with the technique. It also includes deciding if it is necessary to upgrade the aging detection process.

**Figure 1-2**

**Framework for Considering Improved Circuit Board Monitoring for Aging**

---

*Introduction*

In general after choosing a specific circuit, its importance is assessed in the next column, and then from the potential methods factors such as observability and detectability of failure modes are considered. Finally, in the process monitoring column factors such as predicting failure and the timing of restoring, repairing, or replacing are considered.

The following sections address these elements in more detail leading to example decision trees and a relative cost benefit review. The next section reviews aging component failure modes on circuit boards and the use of various methods for monitoring failure modes recognized in electronic components by examination of used circuit boards (EPRI 2002 and EPRI 2004).

# 2

## CIRCUIT BOARD AGING FAILURES

---

This section provides an important input to the framework. It begins with a listing of the components that are found on circuit boards and are subject to aging failures. This section also provides progressive failure mode descriptions for categories of component types.

### Component Listing

The components analyzed in EPRI 2002 and EPRI 2004 are shown in Table 2-1. These were identified as important by a survey of nuclear power plant I&C personnel. Definitions for these components are provided in Appendix B. It is necessary to understand the details of each component in order to assess how a method or technique for monitoring aging could be applied.

**Table 2-1**

**Listing of Components Typically Found on Circuit Boards<sup>4</sup>**

|    |                                                      |

|----|------------------------------------------------------|

| 1  | Capacitors                                           |

| 2  | Relays                                               |

| 3  | Potentiometers                                       |

| 4  | Edge board connectors                                |

| 5  | Power diodes and transistors                         |

| 6  | Transformers and inductive devices                   |

| 7  | Thyristors                                           |

| 8  | Integrated circuits                                  |

| 9  | Printed circuits                                     |

| 10 | Signal diodes and transistors                        |

| 11 | Regulators & other analog circuits                   |

| 12 | Optocouplers                                         |

| 13 | On board connectors                                  |

| 14 | Fixed resistors                                      |

| 15 | LED                                                  |

| 16 | PTH solder joints Pin through Hole (PTH)             |

| 17 | DC/DC converters                                     |

| 18 | SMT solder joints Simultaneous Multi Threading (SMT) |

| 19 | LCD                                                  |

| 20 | Switches and keyboards                               |

| 21 | Quartz                                               |

---

<sup>4</sup> Analyzed in EPRI reports (EPRI, 2002 and EPRI 2004)

The next step was to identify detailed descriptions of effects of failure, root causes and failure modes from EPRI reports and other sources for the components in Table 2-1.

## **Aging Failure Modes**

A failure mode is the effect by which a failure is observed; whereas, a failure mechanism is the chemical, physical, or material process that led to the component failure (EPRI 2003). For electronic components, there are basically two general aging progressive failure modes and two end state aging failure modes:

Progressive failures

- Degraded performance

- Functional failures

End states

- Short circuit

- Open circuit

Transistors, diodes, and certain types of capacitors typically fail short circuit, although resistors and optoelectronic devices fail in a functional mode by having an output signal that is different from what is expected. Failure mechanism can typically be corrosion, wire-bond fatigue, oxide breakdown, electromigration, bond liftoff, and many others. The area of failure mechanism is truly a fertile frontier for understanding the contributors to equipment failure and then being able to first design the mechanisms out of components or at least understand the onset of failures and be able to detect them and take preventive measures to combat them (EPRI 2003).

The following precursor and progressive failure descriptions for circuit board components were obtained directly from EPRI 2002 and EPRI 2004. The failure modes and aging progression issues identified for the components in Table 2-1 are listed in Tables 2-2, 2-3 and 2-4 for components, integrated circuits and circuit boards, respectively. The tables focus on the effects of aging degradation, which generically can be addressed for all components as leading to an open or shorted circuit end state. The differences in component types and functions can result in unique progressions of intermediate degradation failure states that are precursors of failure. These unique progression states, if measured, provide a way of pin pointing the component on the board that is aging.

Tables 2-2, 2-3 and 2-4 provide a generic mapping of precursor effects in time groupings for generic components. These tables show that the aging mechanisms for these components can be observed both externally and internally from changes in circuit characteristics. Furthermore, most aging mechanisms that occur after the “burn in period” proceed slowly, therefore trends of aging can be observed before the circuit becomes fully open or shorted. Thus, if the aging effect can be measured and related to a failure condition, then trending the measures of aging mechanisms can provide a basis for quantifying the probability of failure over a time interval. This provides a rationale for reviewing the potential for detecting the aging with a particular method or technique.

The next section provides a review of the failure data that are available for the components listed in Table 2-1.

**Table 2-2****General Effects of Aging on Resistors, Capacitors, Transformers and Other Components on I&C Electronic Boards**

| Precursor Condition                                                                     | Progressive Conditions                                                 | Inoperable State                 |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|

| Electrical parameters (resistance, impedance, voltage or current) are out of spec,      | Intermittent short circuit or open circuit,                            | Permanent short or open circuit, |

| Drift                                                                                   | Out of spec transfers                                                  | Loss of output voltage           |

| High leakage current to ground.                                                         | Temperature increases                                                  | Short circuit                    |

| Input voltage is out of spec.                                                           | Out put voltage out of spec.                                           | Loss of output voltage           |

| Loss of heat sink (thermal resistance increase, thermal dissipation problems may occur) | Long term reliability is affected (thyristors do not trigger properly) | Loss of output voltage           |

| Short circuits between all leads                                                        | Cathode can turn around itself                                         | Anode to cathode short circuit   |

| Contact problems                                                                        | Temperature increases                                                  | Permanent short or open circuit  |

**Table 2-3****General Effects of Aging on Integrated Circuits on Chips on I&C Electronic Boards**

| Precursor condition                                         | Progressive conditions                     | Inoperable state                                          |

|-------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------|

| Weak supply current,                                        | Unstable supply pin loss of memory @ FF... | Open circuit inside the integrated circuit                |

| Supply current is too high,                                 | Memory cannot be reburned                  | Short circuit between the an output pin and circuit board |

| Leakage current of an output transistor is out of spec.     | Checksum is does not agree with standard   | Loss of program instruction                               |

| High temperature operation                                  | Gates have unstable output                 | Partial destruction of the wire bond component            |

| Corrosion induced intermetallic layers growth at interfaces | Output voltage of a gate oscillates        | Failure open or short circuit                             |

**Table 2-4**

**General Effects of Aging on Printed Circuit Electronic Boards**

| Precursor condition                    | Progressive conditions degradation of parameters              | Inoperable state                              |

|----------------------------------------|---------------------------------------------------------------|-----------------------------------------------|

| Due to cracks                          | Resistance increase                                           | Open circuits on the printed circuit board    |

| Due to corrosion                       | Resistance change                                             | Short or open circuit                         |

|                                        | Resistance fluctuation                                        | Short circuit due to tracking                 |

| Junction breakdown -due to temperature | Leakage current between base and collector is out of spec     | Open circuits                                 |

| Due to vibration                       | Inverse leakage current is out of spec ( $> 10 \mu\text{A}$ ) | Short or open circuit                         |

| Due to corrosion                       | Shift in wave form input -output                              | Short or open circuit                         |

| Due to moisture                        | Increase in resistance (increase in need to restart)          | No longer functions                           |

| Due to Insulation aging                | Operation limited to one position                             | Discover upon testing                         |

|                                        | Output is not regulated for input change                      | No change on output                           |

|                                        | Voltage drift high leakage current                            | Out of spec conditions                        |

|                                        | Frequency progressively shifts                                | Voltage control problems through out circuits |

# 3

## RELIABILITY DATA

---

An element of the framework is to apply reliability modeling. Thus, the next step is to establish a reliability database that can be used for failure predictions on typical instrument and control (I&C) boards. In Table 3-1 the collected circuit board failure rates from grouped data sources are compared with the list of components in Table 2-1. The failure rates discussed in this section generally apply to the useful life period as previously illustrated in the bathtub curve of Figure 1-1.

### Component Specific Failure Data

The data sources for the nuclear power plant electronic components listed in Table 3-1 come from EPRI 2002 and EPRI 2004. They describe failure modes and root causes that have been observed in I&C boards and electronic components. In order to bridge between the list of components in Section 2 and component failure rate data, a clear description and function for each component is needed. Expanded component definitions are provided in Appendix B. The reliability data follow the data collected for military applications and other applications that have been collected and presented in the literature.

The estimates of electronic equipment failure rates can be obtained from the reliability data in Table 3-1. These data represent the results of accelerated aging tests that use high temperatures, excessive voltage stress, and many voltage, vibration and impact cycles to represent long term aging.

The recommended environmental values for each type of component assume the following conditions for power plant applications.

- The quality of the components is best commercial (quality)

- The operation is in a clean filtered air, fixed ground location (environment) with low mechanical vibration.

- The components have been proven under use for at least two years in other applications before installation (learning).

- The voltage is never more than 70% of the rated value (stress), for example for a fifty volt rating the operating voltage never exceeds 35 volts. In many circuit board operations the basic source voltage is 3 or less volts.

- The operating temperature is less than or equal to 40°C (temperature).

The failure rate data must be adjusted for conditions that differ from the above assumptions. The weakness in these data is that neither the impact of the failure nor the root cause is described in detail. The data typically describe only the failure rate or number of failures per time period.

## Event Data Sources

Other sources of data describing I&C board failures were reviewed for applicability to aging component evaluations. In addition to the MIL-HDBK-217 data, event data can be found for other facility operations. Event databases developed to support weapons processing facilities usually describe the impact of a circuit board failure following a root cause analysis. They are generally limited to only a few events, often use technology that is newer than that found in nuclear power plants (and therefore are of limited value in assessing failures in older technology circuit boards), and deal with the system level issues rather than the component level aging issues, which are the focus of this document. Additionally, there is concern about authorizing the use of database information from weapons processing facilities. Therefore, only the MIL-HDBK-217 type data are presented in Table 3-1.

## Failure Rate Equations

The general failure rate model for a part in MIL-HDBK-217 is of the form:

$$\lambda_p = \lambda_b \bullet \pi_Q \bullet \pi_E \bullet \pi_A \bullet \bullet \bullet$$

Where:  $\lambda_b$  = the base failure rate, is described by the Arrhenius equation, and  $\pi_Q \pi_E \pi_A \dots$  = factors related to component quality, environment, and application stress.

The Arrhenius equation illustrates the relationship between insulation breakdown rate and temperature for components. This application has been derived from the observed dependence of chemical reactions on temperature changes.

$$R(t) = A e^{-\frac{E}{\kappa \cdot T}}$$

Where:  $R(T)$  = process rate (e.g., rate of discharge increase)

$E$  = activation energy for the process

$\kappa$  = Boltzmann's constant

$T$  = absolute temperature

$A$  = a constant

Additional details involving the application of the Arrhenius equation are provided in Appendix A. A review of the information in Table 3-1 shows that the failure rates apply to complete failure and are not effective in identifying aging failure modes. Thus, the failure data can be used to estimate a circuit board MTBF during the operational period, and must be adjusted to account for aging with environmental factors. The reliability of a circuit is a strong function of its environment and operating temperature. Such measurements are typically not available, and it is not clear that collecting such data would be the most effective way of monitoring circuit board aging effects.

**Table 3-1**

**Assigning Failure Rate Data for Electronic Components in MIL HBK 217F to EdF**

**Components in Table 2-1**

| EdF Field Data From Analyses & Inspections | MIL-Handbook 217F Electronic Component Generic Names   | MH217F Comp.λ x1. E-9 Per Hr | TQ Quality | TIL Learning | TIE Environ. | Adj. Comp. λ x1. E-9 Per Hr |

|--------------------------------------------|--------------------------------------------------------|------------------------------|------------|--------------|--------------|-----------------------------|

| Capacitors                                 | Capacitors, Discrete, Fixed, Alum, Axial Lead, <400uF  | 24                           | 1          | 2            | 2            | 96                          |

| Capacitors                                 | Capacitors, Discrete, Fixed, Ceramic                   | 3.6                          | 1          | 2            | 2            | 14                          |

| Capacitors                                 | Capacitors, Discrete, Fixed, Tantalum, Solid, Hermetic | 1.5                          | 1          | 2            | 2            | 6                           |

| Relays                                     | Relay General purpose                                  | 130                          | 1          | 2            | 2            | 520                         |

| Relays                                     | Relay Meter movement                                   | 880                          | 1          | 2            | 2            | 3520                        |

| Relays                                     | Relay Time delay                                       | 500                          | 1          | 2            | 2            | 2000                        |

| Relays                                     | Relay Contactor, high current                          | 430                          | 1          | 2            | 2            | 1720                        |

| Relays                                     | Relay Solid State                                      | 400                          | 1          | 2            | 2            | 1600                        |

| Relays                                     | Relay thermal bi-metal                                 | 290                          | 1          | 2            | 2            | 1160                        |

| Relays                                     | Relay latching                                         | 130                          | 1          | 2            | 2            | 520                         |

| Relays                                     | Relay reed                                             | 110                          | 1          | 2            | 2            | 440                         |

| Potentiometers                             | Motor                                                  | 1600                         | 1          | 2            | 2            | 6400                        |

| Potentiometers                             | Switch Thumbwheel                                      | 560                          | 1          | 2            | 2            | 2240                        |

| Potentiometers                             | ETM-Inverter Driver                                    | 15000                        | 1          | 2            | 2            | 60000                       |

| Potentiometers                             | ETM-AC                                                 | 10000                        | 1          | 2            | 2            | 40000                       |

| Edge board connectors                      | Conn IC socket                                         | 5.4                          | 1          | 2            | 2            | 22                          |

| Edge board connectors                      | Conn Clip terminators                                  | 0.12                         | 1          | 2            | 2            | 0                           |

| Edge board connectors                      | Conn comp                                              | 0.26                         | 1          | 2            | 2            | 1                           |

| Power diodes & transistors                 | DIODES Power Rectifier                                 | 3                            | 0.7        | 2            | 2            | 8                           |

| Power diodes & transistors                 | DIODES General Purpose Analog                          | 3.8                          | 0.7        | 2            | 2            | 11                          |

**Table 3-1 (continued)**

**Assigning Failure Rate Data for Electronic Components in MIL HBK 217F to EdF Components in Table 2-1**

| EdF Field Data From Analyses & Inspections | MIL-Handbook 217F Electronic Component Generic Names | MH217F Comp.λ x1. E-9 Per Hr | TQ Quality | TIL Learning | TIE Environ. | Adj. Comp. λ x1. E-9 Per Hr |

|--------------------------------------------|------------------------------------------------------|------------------------------|------------|--------------|--------------|-----------------------------|

| Power diodes & transistors                 | DIODES Transient Suppressor/Varistor                 | 3.1                          | 0.7        | 2            | 2            | 9                           |

| Power diodes & transistors                 | DIODES Fast Recovery Power Rectifier                 | 69                           | 0.7        | 2            | 2            | 193                         |

| Power diodes & transistors                 | DIODES Gunn/Bulk Effect                              | 180                          | 0.7        | 2            | 2            | 504                         |

| Power diodes & transistors                 | DIODES Schottky Barrier and Point Contact            | 27                           | 0.7        | 2            | 2            | 76                          |

| Power diodes & transistors                 | DIODES Si Impatt                                     | 220                          | 0.7        | 2            | 2            | 616                         |

| Transformers & inductive devices           | XFMR RF                                              | 28                           | 1          | 2            | 2            | 112                         |

| Transformers & inductive devices           | Synchro                                              | 70                           | 1          | 2            | 2            | 280                         |

| Transformers & inductive devices           | XFMR High power pulse and power filter               | 23                           | 1          | 2            | 2            | 92                          |

| Transformers & inductive devices           | XFMR Audio                                           | 7.1                          | 1          | 2            | 2            | 28                          |

| Transformers & inductive devices           | XFMR Low power pulsed                                | 3.5                          | 1          | 2            | 2            | 14                          |

| Transformers & inductive devices           | XFMR RF coils variable                               | 3.3                          | 1          | 2            | 2            | 13                          |

| Transformers & inductive devices           | XFMR RF coils fixed or molded                        | 1.7                          | 1          | 2            | 2            | 7                           |

| Thyristors                                 | DIODES Thyristor/SCR                                 | 2.2                          | 0.7        | 2            | 2            | 6                           |

| Integrated circuits                        | MOS MicroProc 32 Bit                                 | 190                          | 1          | 2            | 2            | 760                         |

| Integrated circuits                        | MOS DLA 60000 Gates                                  | 130                          | 1          | 2            | 2            | 520                         |

| Integrated circuits                        | Bipolar MicroProc 32 Bit                             | 110                          | 1          | 2            | 2            | 440                         |

| Integrated circuits                        | Resolver                                             | 110                          | 1          | 2            | 2            | 440                         |

| Integrated circuits                        | MOS MicroProc 16 Bit                                 | 93                           | 1          | 2            | 2            | 372                         |

| Integrated circuits                        | MOS DLA 30000 Gates                                  | 84                           | 1          | 2            | 2            | 336                         |

| Integrated circuits                        | Bipolar DLA 60000 Gates                              | 75                           | 1          | 2            | 2            | 300                         |

**Table 3-1 (continued)**

**Assigning Failure Rate Data for Electronic Components in MIL HBK 217F to EdF Components in Table 2-1**

| EdF Field Data From Analyses & Inspections | MIL-Handbook 217F Electronic Component Generic Names | MH217F Comp.λ x1. E-9 Per Hr | IIQ Quality | TIL Learning | TTE Environ. | Adj. Comp. λ x1. E-9 Per Hr |

|--------------------------------------------|------------------------------------------------------|------------------------------|-------------|--------------|--------------|-----------------------------|

| Integrated circuits                        | Bipolar DLA 30000 Gates                              | 52                           | 1           | 2            | 2            | 208                         |

| Integrated circuits                        | Bipolar MicroProc 16 Bit                             | 52                           | 1           | 2            | 2            | 208                         |

| Integrated circuits                        | Bipolar LinearLA 10000 Trans                         | 50                           | 1           | 2            | 2            | 200                         |

| Integrated circuits                        | MOS LinearLA 10000 Trans                             | 50                           | 1           | 2            | 2            | 200                         |

| Integrated circuits                        | MOS DLA 10000 Gates                                  | 49                           | 1           | 2            | 2            | 196                         |

| Integrated circuits                        | MOS MicroProc 8 Bit                                  | 48                           | 1           | 2            | 2            | 192                         |

| Integrated circuits                        | MOS SRAM 1MB                                         | 43                           | 1           | 2            | 2            | 172                         |

| Integrated circuits                        | Bipolar DLA 10000 Gates                              | 33                           | 1           | 2            | 2            | 132                         |

| Integrated circuits                        | Bipolar LinearLA 1000 Trans                          | 33                           | 1           | 2            | 2            | 132                         |

| Integrated circuits                        | Bipolar SRAM 1MB                                     | 33                           | 1           | 2            | 2            | 132                         |

| Integrated circuits                        | MOS LinearLA 1000 Trans                              | 33                           | 1           | 2            | 2            | 132                         |

| Integrated circuits                        | Bipolar MicroProc 8 Bit                              | 28                           | 1           | 2            | 2            | 112                         |

| Integrated circuits                        | MOS SRAM 256K                                        | 23                           | 1           | 2            | 2            | 92                          |

| Integrated circuits                        | Bipolar PLA 5000 Gates                               | 22                           | 1           | 2            | 2            | 88                          |

| Integrated circuits                        | MOS DLA 3000 Gates                                   | 19                           | 1           | 2            | 2            | 76                          |

| Integrated circuits                        | Bipolar SRAM 256K                                    | 18                           | 1           | 2            | 2            | 72                          |

| Integrated circuits                        | Bipolar LinearLA 300 Trans                           | 17                           | 1           | 2            | 2            | 68                          |

| Integrated circuits                        | MOS LinearLA 300 Trans                               | 17                           | 1           | 2            | 2            | 68                          |

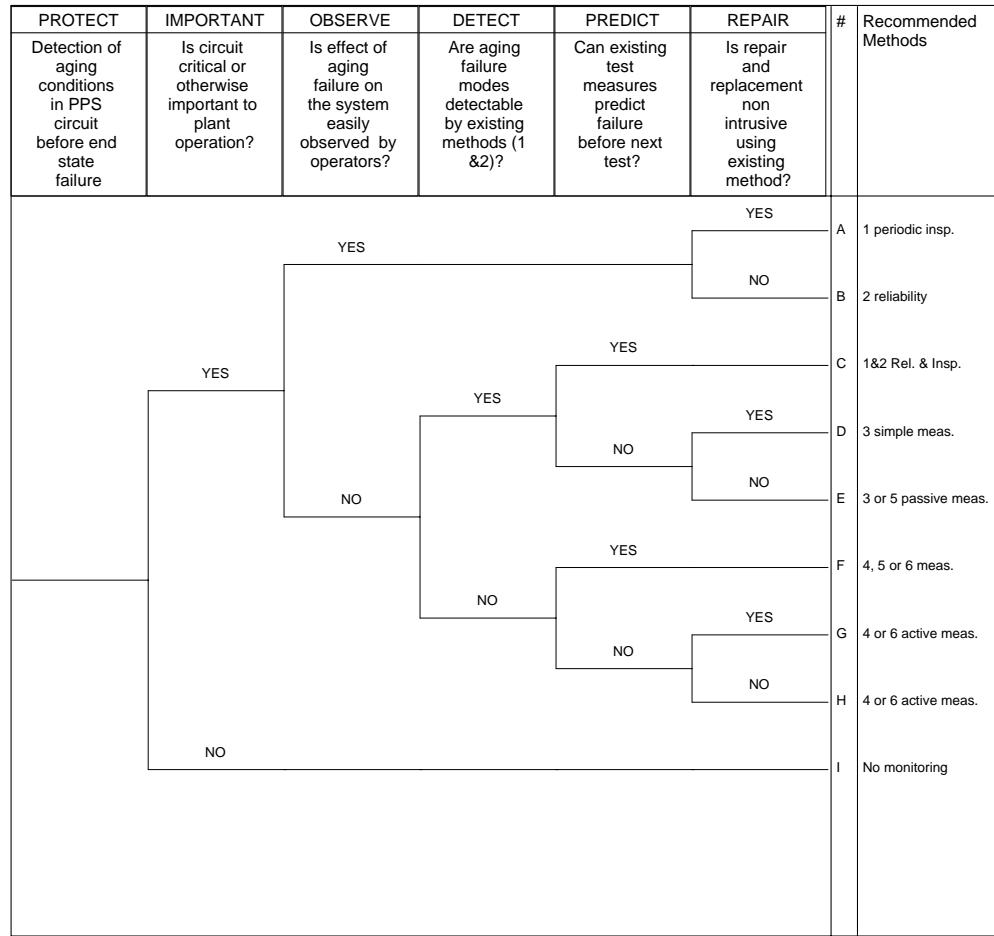

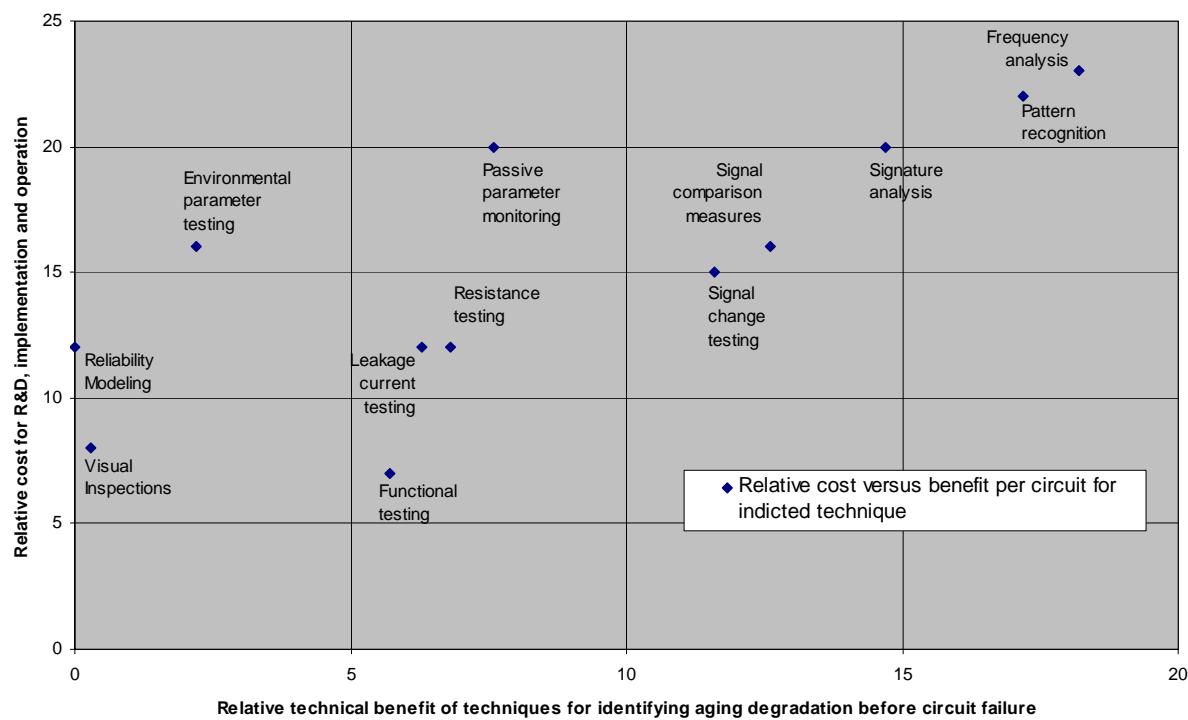

| Integrated circuits                        | MOS SRAM 64K                                         | 14                           | 1           | 2            | 2            | 56                          |