172/27/26

172/27/26

593

605

**LA-6456-MS**

Informal Report

UC-32

Issued: December 1976

## **CRAY-1 Evaluation**

### **Final Report**

by

**T. W. Keller**

**los alamos**

**scientific laboratory**

of the University of California

LOS ALAMOS, NEW MEXICO 87545

An Affirmative Action/Equal Opportunity Employer

MASTER

UNITED STATES

ENERGY RESEARCH AND DEVELOPMENT ADMINISTRATION

CONTRACT W-7405-ENG. 36

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

---

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

Publication of this report does not imply endorsement of the products described herein.

Printed in the United States of America. Available from

National Technical Information Service

U.S. Department of Commerce

5285 Port Royal Road

Springfield, VA 22161

Price: Printed Copy \$5.50 Microfiche \$3.00

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Energy Research and Development Administration, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights.

TABLE OF

CONTENTS

**NOTICE**

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Energy Research and Development Administration, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

|       |                                          |    |

|-------|------------------------------------------|----|

| I.    | EXECUTIVE SUMMARY.....                   | 1  |

| II.   | INTRODUCTION .....                       | 6  |

|       | Context of Evaluation.....               | 6  |

|       | Qualification Criteria.....              | 7  |

| III.  | SCALAR PERFORMANCE.....                  | 9  |

|       | Introduction and Approach.....           | 9  |

|       | Preliminary Scalar Performance Test..... | 12 |

|       | Workload Determination.....              | 14 |

|       | Execution and Monitoring.....            | 20 |

|       | Kernel Selection.....                    | 21 |

|       | Kernel Implementation.....               | 24 |

|       | Timing Results.....                      | 26 |

|       | Impact of Hardware Features.....         | 28 |

|       | Conclusions .....                        | 29 |

| IV.   | VECTOR PERFORMANCE.....                  | 31 |

| V.    | RELIABILITY.....                         | 34 |

|       | Approach .....                           | 34 |

|       | The EXERCISER Program.....               | 35 |

|       | Results and Conclusions.....             | 36 |

| VI.   | INPUT/OUTPUT PERFORMANCE.....            | 43 |

|       | Disk Performance Tests.....              | 43 |

|       | Computation and I/O Interference.....    | 47 |

| VII.  | INFORMAL ESTIMATES.....                  | 52 |

| VIII. | CONCLUSIONS.....                         | 54 |

|       | Scalar Performance.....                  | 54 |

|       | Vector Performance.....                  | 54 |

|       | Reliability .....                        | 54 |

|       | Input/Output Studies.....                | 55 |

|       | Conclusion .....                         | 56 |

|       | APPENDIX A.....                          | 57 |

|       | Configuration Being Evaluated.....       | 57 |

|       | Summary of CRAY-1 Characteristics.....   | 58 |

|       | Evaluation Plan.....                     | 66 |

|       | Statistics Addendum.....                 | 79 |

|       | I/O Studies.....                         | 83 |

|       | Vectorization Criteria.....              | 84 |

|       | Decision Rule.....                       | 86 |

|       | Evaluation Plan Figures.....             | 86 |

|       | APPENDIX B FIGURES.....                  | 87 |

SIGNATURES

Ronald S. Schwartz, Director

Office of ADP Management

Energy Research and Development Administration

Ronald Bartell, Deputy Assistant Director for

Program Analysis and Budget

Division of Military Application

Energy Research and Development Administration

Fred W. Dorr, Division Leader

Computer Science and Services Division

Los Alamos Scientific Laboratory

SECTION IEXECUTIVE

SUMMARY

The performance evaluation of the CRAY-1 computer was structured to determine if the CRAY-1 meets the minimum performance standards set forth by the Los Alamos Scientific Laboratory (LASL) and the Energy Research and Development Administration (ERDA) to qualify the machine for further consideration for procurement.

The performance standards are divided into specific qualification criteria in three main areas: scalar performance, vector performance and reliability. The qualification criteria are summarized in Table I-1. The final Evaluation Plan, including precise definitions of the qualification criteria, is presented in Appendix A of this document.

It was impossible to convert large segments of the LASL computing workload to the CRAY-1 because programs to be run on the machine would require assembly language coding. Thus, for the scalar test, a sampling scheme was adopted that selected small computational kernels to be run on both the CDC 7600 and the CRAY-1. Kernels were drawn from a program by a method that weighted the probability of drawing a specific kernel by its contribution to the total execution time of the program. The sampling process was defined to a level of detail that eliminated the chances of biasing the selection toward either machine. By statistical methods it was possible to establish a test of the hypothesis that the CRAY-1 (in scalar mode) is greater than two times faster than the CDC 7600 with 90 percent confidence for any sampled program. To assure that the code kernels were representative of the potential LASL workload for the CRAY-1, the code kernels were drawn from the actual programs expected to comprise the eventual Class VI workload. Only programs consuming greater than one CDC 7600 hour per run and requiring more than one run per week were considered as potential workload candidates.

A second workload for the CRAY-1 was established from a sample that included frequently run codes not expected to be included in the immediate LASL workload for the machine. This was done as an attempt to establish a performance index of the machine based upon a more general workload, and one that might be more representative of computing throughout ERDA.

In order to eliminate the impact of compiler efficiency, kernels were coded as efficiently as was feasible in both CRAY-1 assembly language and CDC 7600 assembly language.

It was not possible to rigorously establish "representative" kernels for testing the vector performance of the CRAY-1. This was because none of the existing codes comprising the workload had been converted for vector operations, and such conversion efforts were outside the evaluation's time frame.

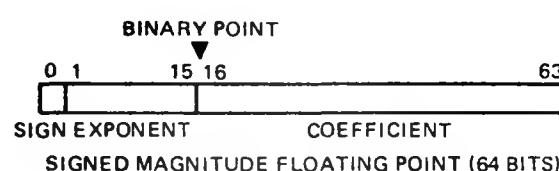

At the risk of oversimplifying, the vector computational speed of the CRAY-1 relative to the CDC 7600 is a function of both vector length and complexity of the vectorized arithmetic function. Relative performance of the CRAY-1 increases with vector length and complexity of operation. Performance criteria using vector lengths of 20, 100 and 500 were established, and the complexity of vector operations remained to be chosen. The simplest expressions, such as  $R = A + B$ , result in the lowest relative performance. Relative performance increases with greater numbers of different operators and operands (increasing complexity), as this allows increased overlap of functional units and chaining to occur. Chaining refers to an increase in parallelism resulting from the ability of the machine to store the result of a computation in a vector register while the result is re-entered as an operand to another vector computation in the same clock period. Thus, two or more primitive vector operations may be "chained" together. The more complex the evaluated expression, the greater the likelihood that chaining can occur. The Applications Support and Research Group of the Computer Science and Services Division at LASL was asked to furnish vector kernels that, in their judgement, represented common vector operations that user codes would perform on the CRAY-1. Five expressions of medium complexity, such as  $R = A * B + C$ , were chosen to evaluate the machine's vector performance as a function of vector length. The average of the five performance ratios was chosen to compare against the qualification criteria. Each vector kernel was coded as efficiently as was feasible in assembly language for each machine. In particular, the CDC 7600 kernels were coded as "in-stack" loops--a scheme that pushes the CDC 7600 toward its theoretical maximum performance for these algorithms.

The reliability of the CRAY-1 was evaluated by establishing a reliability test code to run on the

machine for long periods of time. This "exerciser" was designed to utilize as many different hardware units of the machine as possible, at as rapid a rate as possible, for extended periods. The exerciser underwent several evolutionary stages toward this goal. The latest version of the exerciser accesses the machine's memory at a sustained rate several times greater than that plausible for a production workload. The reliability figures were determined for contiguous 20-workday periods in order to "smooth" short-term fluctuations in reliability.

In addition to the tests against the qualification criteria outlined above, the evaluation also investigated the CRAY-1 disk system performance and made other miscellaneous studies. For sake of brevity these studies will not be discussed in the Executive Summary.

Clearly, many aspects of the CRAY-1's performance were evaluated, some in considerable detail. An impartial study was accomplished despite the constraints of a primitive CRAY-1 operating system, the absence of a Fortran compiler, the relatively short evaluation period, and the necessity of agreement by LASL, ERDA, and the Federal Computer Performance Evaluation and Simulation Center (FEDSIM) upon an evaluation plan. Rigorously defensible results were obtained by adopting methods of known accuracy wherever possible. Although the constraints confined the scope of the evaluation, they did not hinder the objectivity nor accuracy of its results.

## Results

A brief summary of the evaluation results is presented in Table I-1.

Scalar. Timing results for the scalar kernels are summarized in Table III-6 of Section III. On the basis of these results the hypothesis that the CRAY-1 is at least two times faster than the CDC 7600 for scalar kernels was satisfied in all tests.

Vector. Results of the vector kernel timings are summarized in Table I-1. The machine met the vector performance qualification criteria for the three vector lengths.

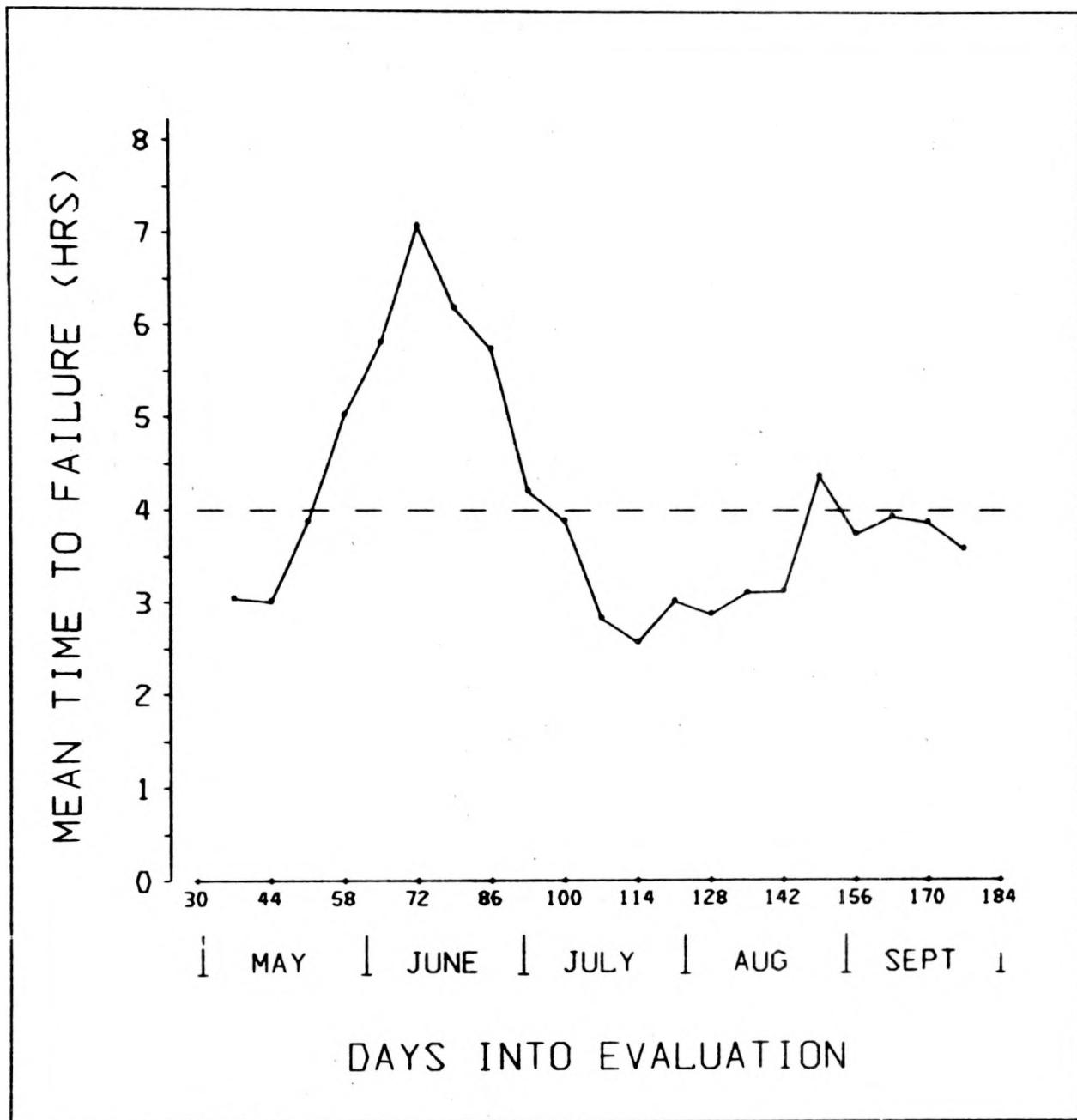

Reliability. The machine met the reliability criteria for many reported 20-day periods. The Mean-Time-To-Failure (MTTF) fluctuated from a low of approximately 2.5 hours to a high of

approximately 7.5 hours during the six-month period. No trend was observed.

Approximately 89 percent of all machine failures during the evaluation were memory parity errors. If one assumes that all memory errors were correctable single-bit errors, then installation of single-bit memory error correction would have resulted in an increase in MTTF by a factor of nine. Such an increase would result in extremely good reliability for a machine of this complexity.

The conclusion of the evaluation is that the CRAY-1 satisfies the threshold performance criteria in all categories. FEDSIM, in a separate report to be issued, concurs in this conclusion.

Table I-1. Summary of Qualification Criteria

and Evaluation Results.

A. Qualification Criteria

Scalar Performance.

Scalar operations  $\geq 2 \times$  CDC 7600 in speed

Vector Performance.

|                          |                                   |

|--------------------------|-----------------------------------|

| Short vector operations  | $\geq 3 \times$ CDC 7600 in speed |

| Medium vector operations | $\geq 4 \times$ CDC 7600 in speed |

| Long vector operations   | $\geq 5 \times$ CDC 7600 in speed |

Reliability.

|                      |               |

|----------------------|---------------|

| Mean-Time-To-Failure | $\geq 4$ hrs. |

| Mean-Time-To-Repair  | $\leq 1$ hr.  |

| System availability  | $\geq 0.8$    |

B. Results

Scalar.

The hypothesis that the CRAY-1 is  $\geq 2 \times$  the CDC 7600 in speed tests as true for each of the three codes comprising the LASL "applications" workload. The hypothesis tests as true for a more general workload consisting of five codes.

Vector.

Average CRAY-1/CDC 7600 speed ratio of five vector functions by vector length:

|                            |      |

|----------------------------|------|

| Vector length 20 (short)   | 3.30 |

| Vector length 100 (medium) | 4.50 |

| Vector length 500 (long)   | 5.12 |

Reliability.

For the period 5-14-76 to 6-11-76:

|                      |           |

|----------------------|-----------|

| Mean-Time-To-Failure | 7.08 hrs. |

| Mean-Time-To-Repair  | 0.38 hr.  |

| System Availability  | 0.950     |

SECTION IIINTRODUCTION

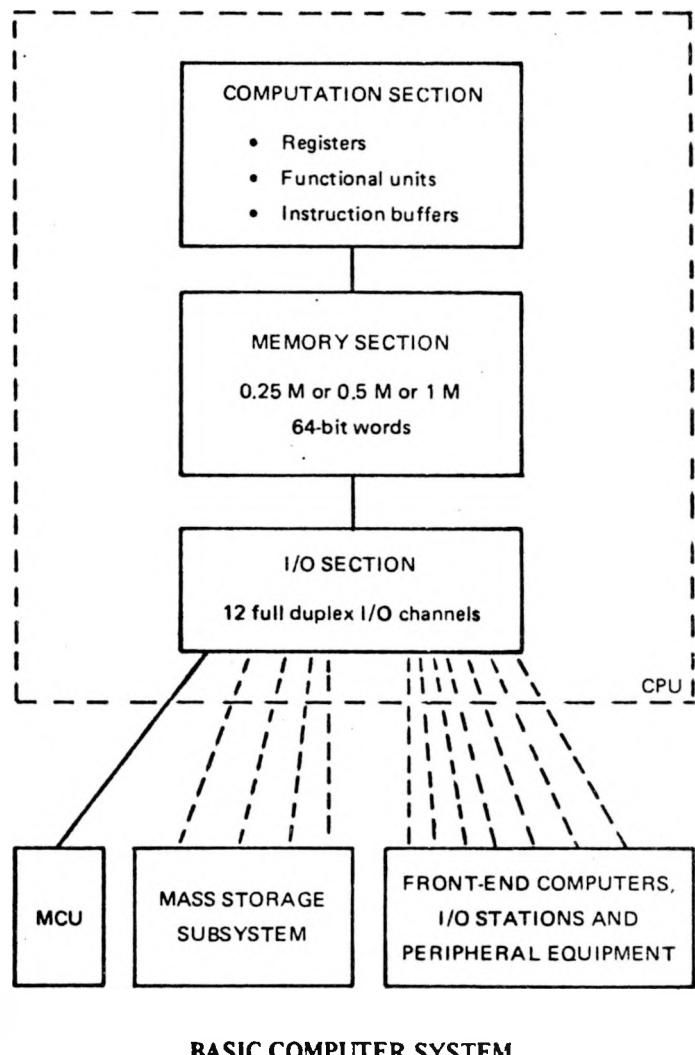

The growing complexity of the programmatic efforts at the Los Alamos Scientific Laboratory (LASL) in weapons design, laser fusion and isotope separation, magnetic fusion energy research, reactor safety, and other basic and exploratory research requires calculations that are beyond the capability of the fastest computer currently installed in the LASL Central Computing Facility--the CDC 7600. Thus, LASL needs a computer that can meet the growing requirements for computational speed. For this reason, LASL, in conjunction with the Energy Research and Development Administration (ERDA) and the Federal Computer Performance Evaluation and Simulation Center (FEDSIM), undertook to evaluate a new class of scientific computer system. This class has been identified by ERDA as "Class VI"--one that is capable of executing 20 to 60 million floating point operations per second.

## Context of Evaluation

Because computers of this class are necessarily pushing the state of the art of both computer architecture and electronic technology, there have been worries expressed in ERDA and Congress that the usual procurement procedures did not afford adequate protection to the Government against failure of these machines to fulfill their specifications for reliability and performance. The basic reason for this is that Class VI computers are very complex, and considerable time is required to convert previous application programs so that an adequate evaluation of the product can be assured. By the time reliability and performance evaluations can be conducted, the usual protections for the Government have elapsed.

To avoid a repetition of previous ERDA experiences with similar computers, a plan was designed that offered vendors an equal opportunity to compete and yet provided a large measure of protection for the Government.

The plan to implement these desired policies of competition and protection consisted of the following steps.

a. Offer all potential vendors an opportunity to have their computers evaluated with respect to stated performance criteria within approximately a

six-month time scale. A letter was sent on 2-26-76 by ERDA to a number of vendors.

b. Determine the set of computers to be evaluated. In the words of the letter to the vendors, "....a demonstration and evaluation of machine capabilities must precede a decision to acquire a new class of computers." Thus, all vendors were given an opportunity to have their products evaluated; however, only those with a product available for immediate evaluation which met the minimum evaluation criteria would qualify to provide the equipment for later acquisition at LASL.

Responses were received from two vendors--Control Data Corporation (CDC) and Cray Research, Incorporated (CRI). The CDC response did not offer a computer for immediate evaluation; the proposed product was not scheduled for availability until about eighteen months after the beginning of the evaluation period. Thus, the policy of "evaluation before acquisition" could not be implemented with respect to the CDC proposal, and the CDC proposal was judged non-responsive to LASL's requirements.

c. Evaluate the products proposed. The proposal by CRI was consistent with the specified criteria and that computer was evaluated, beginning April 1, 1976. The evaluation was a cooperative effort between LASL, ERDA and FEDSIM and conformed to the performance criteria specified to vendors.

d. On the basis of evaluation results (c), determine whether to pursue a procurement action.

In summary, a plan was implemented that offered vendors an equal opportunity to compete, yet afforded the Government extra protection in an area of high technological risk.

Qualification

Criteria

The performance standards necessary to qualify a computer for procurement were established in the ERDA letter to vendors. Qualification criteria for the CRAY-1, incorporating these standards, are formalized in the Evaluation Plan (Appendix A of this document). An informal description of the criteria follows. The criteria are divided into three general areas: scalar operations, vector operations and reliability.

The scalar operations criterion is that by methods discussed in Section III and formalized in the Evaluation Plan, the hypothesis that the CRAY-1

is at least two times faster than the CDC 7600 for two specified workloads must be satisfied.

The vector operations criteria are defined for three vector lengths. The criteria are that the CRAY-1 be capable of executing vector operations at a rate at least 3, 4 and 5 times that at which the CDC 7600 can perform the equivalent functions for vectors of lengths 20, 100 and 500, respectively.

Reliability is determined by three metrics: System Availability (SA), Mean-Time-to-Failure (MTTF) and Mean-Time-to-Repair (MTTR). Informally, SA is the fraction of time the system is available for use, MTTF is the expected time to system failure, and MTTR is the expected "down-time" interval. The reliability criteria are that MTTF be at least 4 hours, MTTR be at most 1 hour, and SA be at least 0.8. Furthermore, the three criteria must collectively be met during any contiguous 20-workday period.

These criteria are summarized in Table I-1 of the Executive Summary (Section I) of this report.

It now appears that there is an existing computer system that meets LASL Class VI computing requirements -- the Cray Research, CRAY-1. The CRAY-1 was installed at LASL for six months for evaluation against the threshold performance criteria specified by LASL and ERDA to qualify the machine for procurement. The purpose of this document is to describe the approach taken by LASL, ERDA and FEDSIM in evaluating the CRAY-1 and the results of the evaluation. This document was preceded by a preliminary version of this report ("Interim Report of the CRAY-1 Evaluation") issued July 1, which consisted of the CRAY-1 Evaluation Plan and gave results of the evaluation to that date.

SECTION IIISCALAR

PERFORMANCEIntroduction

and

Approach

The scalar operations performance criterion is that the CRAY-1 must perform scalar operations at a rate at least twice that of the CDC 7600 for each of two workloads. The approach to testing the machine against this criterion is specified in detail in the Evaluation Plan (Appendix A). Some of the constraints and requirements which shaped this approach are described here.

Since no compiler was available on the CRAY-1, any code implemented on the machine was written in assembly language. The decision was made to implement "optimal" code on both machines, instead of attempting to emulate compiler-generated code. The fundamental reason for this approach was that the CRAY-1 and CDC 7600 have different architectures. For example, the B and T programmer-controlled register caches on the CRAY-1 have no equivalent on the CDC 7600. Attempts to emulate compilers would raise such questions as: "How well will a (hypothetical) CRAY-1 compiler take advantage of this cache for the storage of temporaries?" It soon became obvious that no satisfactory solution to the problem of functional differences existed where the problem was compounded by questions of compiler "intelligence" and convention.

Another reason that code optimization was undertaken was because "optimal" is a yardstick for comparison. For very short modules it is reasonable to expect that careful coding, cross-checking by other programmers, the use of software tools that test efficiencies, etc., will result in nearly optimal code. The metric for optimality is simple. If two approaches are considered, the approach resulting in the least execution time is more optimal. When emulating compiler-generated code, any question of approach becomes a debate between compiler implementation philosophies.

The next decision to be made was whether Input/Output operations (I/O) should be included in the analysis or whether computational kernels should be compared alone. A complete analysis would require inclusion of the properties of CPU/I/O

overlap. This would necessitate a complete analysis of the program's CPU burst, I/O burst profile. Unfortunately, tools did not exist for such complete analysis, nor could they be constructed within the time frame of the evaluation. Furthermore, at the time the evaluation was started, the complete operating characteristics of the eventual CRAY-1 I/O subsystem were not well-determined. The only manner in which to gather such statistics would be extensive modifications in the running codes and operating system. This approach was not considered tractable. A modeling approach was suggested, but since only a trivial I/O system was available, it was not thought that models could be validated with the necessary rigor. Thus the decision was made to limit the comparison to the machines' mainframe hardware. An analysis of the CRAY-1 I/O subsystem was formulated to determine if any pathologies existed in the subsystem.

The next decisions facing the evaluation design committee were 1) what codes would be analyzed and 2) how would kernels be selected from these codes to run on the machine? A workload determination was considered essential for selecting "representative" codes. Since the workload of the Class VI computer would consist of long-running codes, the manner of the selection of criteria defining the potential workload for the machine was relatively straightforward. These criteria are put forth in the Evaluation Plan. A more ticklish question was how to draw "representative" kernels from the codes. Since kernels would have to be written in assembly language for both machines and "optimized", the amount of code that could be implemented was obviously small. The general question of "representativeness" is still a very active area of research in computer performance prediction. Many opinions were put forth by the evaluation design committee. The constraint that blocked most approaches was the desire to attain rigorously defensible estimates. There is no metric of "representativeness" that can be applied. Error bounds for performance estimates for workloads attainable from kernels are usually impossible to attain. Thus a new approach was considered necessary.

It was decided to adopt a sampling scheme to which proven statistical methods could be applied in order to attain error bounds for the performance estimates. The sequential sampling scheme that was formulated is described in the Statistics Addendum. Informally, the approach assumes that any code can

be partitioned into small, nonoverlapping code segments. If we ignore I/O, then the total execution time for any code will be the sum of the total execution times for the segments. What we desire to estimate is the ratio of the CDC 7600 execution time to CRAY-1 execution time for the code. If this speed ratio is at least two then the CRAY-1 meets the scalar qualification criterion for that code. The sampling scheme draws a number of these segments from the code. These computational kernels are then implemented in assembly language on each machine and timed. The speed ratios of these kernels are thus related to the actual speed ratio for the code. The larger the sample size from a particular code, the more confident we are that the sampled speed ratio is close to the code's actual speed ratio.

Unfortunately, it became apparent that the sample size necessary to estimate a code's speed ratio with adequate confidence was too large to be tractable. However, the hypothesis that the CRAY-1 is greater than twice as fast as the CDC 7600 (the qualification criterion) can be tested with a tractable sample size. A procedure can be constructed so that the number of kernels drawn is not fixed, but is a function of the fraction of kernels that have speed ratios in excess of two. The hypothesis is tested each time the sample size is increased by one. The number of samples drawn must be at least six if we wish the probabilities of accepting the hypothesis when it is false or rejecting it when it is true to each be less than 0.1. The practical significance of this scheme is that no more kernels than necessary need be programmed, thus avoiding the wasted effort of unnecessarily large sample sizes. Again, the reader is referred to Appendix A for a more thorough explanation of the scheme.

An estimate can be made of the actual speed ratio for a code, although the small sample size precludes determining the error bounds on the estimate. Such estimates are included in the Informal Estimates Section of this report.

A final complication for the workload determination was the concern that the LASL workload would not be "representative" of the broader ERDA-wide workload for the machine. LASL, of course, was primarily interested in the performance of a small set of codes that, for programmatic reasons, would be candidates for conversion to the Class VI computer. Thus a second set of codes, including the LASL set, was also tested. The first set was designated the Class VI

applications workload, while the extended set was labeled the Class VI workload. It was decided to test the hypothesis for each of the applications codes and to test the hypothesis for the Class VI workload as a whole. At that time the problem of determining a rule attaching a weighting to the importance of each code in the applications workload became apparent. It was decided to use a decision rule that is applied against the results of the hypothesis test for each applications code and which determines whether or not CRAY-1 performance over the entire workload is satisfactory. The decision rule was formulated by LASL and approved by the ERDA Division of Military Application before the testing was initiated. The rule adopted was that the hypothesis must test as true for one or more of the three applications codes in order for the CRAY-1 to meet the applications workload threshold criterion. An indeterminate test result was to be considered a negative result when applying the decision rule.

Preliminary

Scalar Performance

Test

A preliminary test of the CRAY-1 scalar performance was desired in order to estimate if the CRAY-1 might meet the scalar performance criteria prior to beginning the extensive sampling procedure outlined above. Since the kernels selected by the sampling method would by necessity be very small, on the order of three to ten Fortran statements, a preliminary test program an order of magnitude larger was desired in order to provide a rough check on the sensitivity to kernel size of the CRAY-1/CDC 7600 speed ratio when determined by the sampling method.

The test routine chosen is a kernel of the Equation of State (EOS) algorithm. EOS is common to many LASL production codes. The algorithm consumes approximately 3.4% and 1.2%, respectively, of the CPU time for representative runs of two of the production codes comprising the Class VI workload.

The kernel TLU extracted from EOS is given in Figure B-1 and consists of over 70 lines of Fortran code. The kernel was hand translated into CDC 7600 assembly language and CRAY-1 assembly language as efficiently as was feasible for each machine. The assembly language code is available in a separate document. In order to factor out the impact of possible differences in efficiency between the CRAY-1 and CDC 7600 library versions of the functions ALOG and EXP, the functions were re-defined as  $\text{ALOG}(x) = x$  and  $\text{EXP}(x) = x$ .

Naturally, the CRAY-1 version of TLU consisted of purely scalar calculations. It can be noted from Figure B-1 that the test routine is characterized by much address computation, numerous tests and branches, and a moderate amount of floating-point arithmetic.

For each machine, the test routine was timed for 5400 calls with a different parameter set for each call in order to fully exploit all paths in the routine. This was accomplished by using a driver. A Fortran listing of the CDC 7600 driver is given in Figure B-2. The equivalent CRAY-1 driver was written in PASCAL and CRAY-1 assembly language.

Results of these timings are given in Table III-1. The timing ratio of 2.55, greater than the criterion of 2.0, indicated that the more extensive sampling procedure was worthwhile.

---

Table III-1. Scalar Test Routine Timings.

---

|                            |            |

|----------------------------|------------|

| A. CDC 7600 Execution Time | .0877 sec. |

| B. CRAY-1 Execution Time   | .0344 sec. |

| C. Ratio A/B               | 2.55       |

---

## Workload

## Determination

For a code to be included in the Class VI workload, the following criteria were established:

1. The code consumes enough CDC 7600 CPU time to merit conversion to a Class VI computer.

2. The code will continue to be used at current or increased levels.

3. Support for the code's conversion to a Class VI computer exists within the user group.

A measure of at least one run per week greater than one hour on the CDC 7600 was chosen as the level of significance to merit conversion (Criterion 1). To accomplish this, a detailed analysis of LASL's production workload was undertaken utilizing historical accounting data provided by LASL's computer operations group.

Statistics are collected and maintained on the two CDC 7600 operating systems utilized for production work: CROS and LTSS. CROS is a batch operating system suited to a production environment, while LTSS is a timesharing operating system suited to an interactive environment. Both systems run on the CDC 7600. Accounting methodologies between these two systems differ. Statistics on the CROS system are detailed and flexible enough to summarize and tabulate requested data to the level of a single run. LTSS statistics, however, are logged by account number, the accounting philosophy being that an account number is associated with a "family" of codes programmatically related. Thus, many codes may charge to a single account and the charged time cannot be easily apportioned among individual codes, as in the CROS system.

A summary of compiled results is presented in Tables III-2 and III-3. The CROS data is straightforward. The criterion of "greater than one hour" could not be as easily applied to the LTSS workload because of the previously discussed accounting methodology. The approach taken on LTSS was to determine usage by account number. The codes associated with an account number were then determined by interviewing the holder of the account. Since it was not possible to break down the run times by code, short runs within a "family" are lumped together with production runs. Thus, the method of ascertaining the production workload on LTSS was to conduct a user survey to discover the account numbers and associated codes active during the production shifts. Fortunately, LTSS production codes are few in number and highly visible, since they were only recently transferred from CROS to LTSS.

The total LTSS charged time, by family of codes, is presented in Table III-3 for three months of usage. The reader will note that the values of charged time are low when compared to the CROS figures, especially when one considers that the CPU time includes all runs charged to an account, not merely runs of one-hour duration or more. This is explained by 1) at that time, there was only one CDC 7600 running LTSS in a production environment while three CDC 7600s were running CROS, and 2) LTSS currently has a smaller population of production codes.

The complete set of codes enumerated in Tables III-2 and III-3 comprise the potential Class VI workload. The significance criterion (Criterion 1) determines that a code must have more than 12 one-hour or greater runs in three months to be considered in the Class VI workload. On the basis of Criterion 1 all codes consuming less than 12 hours of CDC 7600 time in greater than one-hour runs were eliminated from consideration.

Additionally, programmatic requirements dictated that certain codes would receive little or no support for conversion to the CRAY-1. A user review process eliminated many codes from consideration on the basis of Criterion 2; namely, ZORK, TD4TWOD, TIGER, and the MAGEE and MCN families. MCRAD, EOTOTO, GUANO, TORUS-M and SIMMER were left to comprise the Class VI workload.

Of these five codes, MCRAD, GUANO, and EOTOTO were selected to comprise the Class VI applications workload. Table III-4 tabulates the final results of the workload study.

Table III-2.

Potential Class VI Workload from CROS.

System: CROS

Period Evaluated: 1/1/76 to 3/31/76

Source of Data: CROS HISTORICAL DAYFILE DATABASE

| Code     | User Supplied Description                                      | Total CPU Time used (hrs.) | % of Total CPU time for for Jobs >1 hr. Jobs >1 hr. |

|----------|----------------------------------------------------------------|----------------------------|-----------------------------------------------------|

| GUANO    | 2-D Lagrangian explosion code                                  | 271.28                     | 31.06                                               |

| ZORK     | 1-D explosion code                                             | 92.75                      | 10.62                                               |

| EOTOTO   | 2D Monte Carlo particle-in-cell code                           | 79.27                      | 9.08                                                |

| TD4TWOD  | Controller for Magee family of codes                           | 72.98                      | 8.36                                                |

| TIGER    | 2-D particle-in-cell S/N code                                  | 64.57                      | 7.40                                                |

| TORUS-M  | 3-D toroidal geometry fluid code; magnetic fusion research     | 48.58                      | 5.56                                                |

| SIMMER   | Hydrodynamic-neutronics-equation of state code; reactor safety | 39.00                      | 4.47                                                |

| MAGEE    | 2-D hydrodynamic code                                          | 36.51                      | 4.18                                                |

| MCNGACE  | 3-D Monte Carlo neutron and gamma transport code               | 17.05                      | 1.95                                                |

| MCNG     | 3-D Monte Carlo neutron and gamma transport code               | 10.03                      | 1.15                                                |

| MCRAD    | Monte Carlo radiation output code                              | 11.02                      | 1.15                                                |

| DITTO    | 1-D Lagrangian explosion code                                  | 8.67                       | 0.99                                                |

| MCMD     | Monte Carlo molecular dynamics for hard spheres and hard disks | 7.59                       | 0.87                                                |

| MOOP     | Weapons diagnostics                                            | 6.81                       | 0.78                                                |

| DYNSTAR  | Weapons diagnostics                                            | 5.89                       | 0.68                                                |

| LONGWALK | Weapons diagnostics                                            | 4.47                       | 0.51                                                |

|                   |                                                                               |        |        |

|-------------------|-------------------------------------------------------------------------------|--------|--------|

| SPECTOR           | 2-D radiation transfer code;<br>astrophysics research                         | 3.31   | 0.38   |

| YAZM              | 2-D radiation transfer code                                                   | 3.04   | 0.35   |

| UNDETER-<br>MINED | No identification--unable to<br>infer from other dayfile<br>data the code ID. | 91.22  | 10.45  |

| TOTAL             |                                                                               | 873.04 | 100.00 |

Table III-3. Potential Class VI Workload from LTSS.

System: LTSS

Period Evaluated: 1/1/76 to 3/31/76

Source Data: Account Number Data Base and User Survey

| Code   | User Supplied Description                                              | Total Time (hrs.) Charged for all Runs | Percent |

|--------|------------------------------------------------------------------------|----------------------------------------|---------|

| MCRAD  | Monte Carlo radiation output code                                      | 463                                    | 85.42   |

| MAGCON | Controller for MAGEE family of codes                                   | 49                                     | 9.04    |

| LASNIX | 2-D hydrodynamic code for laser fusion pellet design                   | 14                                     | 2.58    |

| WAVE   | 2-D electrodynamic relativistic particle simulation code; laser fusion | 11                                     | 2.03    |

| SIMMER | Hydrodynamic-neutronics-equation of state code; reactor safety         | 5                                      | 0.92    |

| TOTAL  |                                                                        | 542                                    | 99.99   |

Table III-4. LASL Class VI Workload and

Class VI Applications Workload.

## Class VI Workload

| Code ID | User Supplied Description                                            |

|---------|----------------------------------------------------------------------|

| MCRAD   | Monte Carlo radiation output code                                    |

| GUANO   | 2-D Lagrangian explosion code                                        |

| EOTOTO  | 2-D Monte Carlo particle-in-cell code                                |

| TORUS-M | 3-D toroidal geometry fluid code;<br>magnetic fusion energy research |

| SIMMER  | Hydrodynamic-neutronics-equation of state code;<br>reactor safety    |

## Class VI Applications Workload

| Code ID | User Supplied Description              |

|---------|----------------------------------------|

| MCRAD   | Monte Carlo radiation output code      |

| GUANO   | 2-D Lagrangian explosion code          |

| EOTOTO  | 2-D Monte Carlo particle-in-cell code. |

## Execution and Monitoring

After the LASL Class VI workload and its subset, the Class VI applications workload, had been determined, each user of a selected code was asked to provide files of the code's Fortran source and all data and control card files necessary for a typical execution of the program. The source code and associated data files were copied in order to insulate the "evaluation" code from the normal evolutionary changes of a production environment. Isolation was desired in order that monitoring results be reproducible during the entire evaluation period.

Monitoring proceeded utilizing the LASL-written software monitor STAT. For a given code, the entire field length of a particular overlay and its suboverlays was divided into non-overlapping address ranges labeled "buckets." STAT samples the program address counter and determines which bucket encompasses the address. STAT then increments a count for that bucket and subsequently summarizes these results into a cumulative distribution that gives the fraction of time spent by the sampled overlay in execution in or below the address range for each bucket. Implementation does not allow the generation of a cumulative distribution over more than one overlay. Additionally, the bucket size was chosen to be 16 words--a size large enough to encompass a meaningful Fortran segment yet small enough to result in assembly language segments of tractable size.

The subject codes were run and monitored over a sufficiently long period to exercise the normally used features of each code--typically five to fifteen minutes of CDC 7600 time. Monitoring was done on those overlays that encompassed the main iterative loop. The five to fifteen minutes includes pre- and post-processing which were ignored because this processing consumes insignificant portions of a code's production execution time.

Kernel

Selection

In order to achieve a single cumulative distribution for an entire code execution, a separate program was written to integrate STAT-generated overlay cumulative distributions. This integration is accomplished by weighting the individual overlay distributions by the percent of time spent in each overlay. From this data a single cumulative distribution can be inferred.

The same program then generates a random number, evenly distributed from 0 to 1, utilizing the Fortran library function RANF. The generated random number is applied to the cutoff points of the cumulative distribution associated with each overlay. For example, assume three overlays (A, B and C) were sampled by STAT and consumed 10 sec., 20 sec., and 35 sec., respectively, of run time. The fraction of the total time spent by each overlay would be 10/65, 20/65 and 35/65, respectively. This would imply cutoff points of 10/65 and 30/65 for overlays A and B, respectively. Thus, if the random number .31417 was obtained, it would be associated with overlay B. Furthermore, the bucket associated with .31417 would be associated with the B overlay cumulative distribution value .31417 - 10/65.

An initial sample size of six from each of the three Class VI applications workload codes was drawn for the Class VI applications workload sample. This is because the minimum sample size for testing the speed ratio hypothesis is six (see the Statistics Addendum). Ten kernels were drawn for the test of the Class VI workload, two from each of the five codes comprising the workload. The initial sample size of ten allows each code to be equally weighted in the test. The random number which determined the location of each kernel (the "bucket") in the code and the overlay block in which the kernel resides is presented in Table III-5. Each kernel is identified by a unique label. Kernel labels begin with the first letter of the code from which they were drawn, and are numbered in the order in which they were drawn. Kernels drawn for the Class VI workload test are specified by an "H" in their label.

In this initial drawing of 28 kernels, four were duplicates, namely G2/G3, E3/E6, M2/MH1 and SH1/SH2. Duplication occurs when two random numbers are so close in value that they "fall" into the same bucket.

Table III-5.

Random Numbers Associated with Kernels.

| Code Name | Kernel ID | Random Number | Overlay Block |

|-----------|-----------|---------------|---------------|

| EOTOTO    | E1        | .0678473      | (1,3)         |

|           | E2        | .3986746      | (2,2)         |

|           | E3        | .9058777      | (2,2)         |

|           | E4        | .1780081      | (2,2)         |

|           | E5        | .8107489      | (2,2)         |

|           | E6        | .8764135      | (2,2)         |

|           | EH1       | .6488114      | (2,2)         |

|           | EH2       | .6430924      | (2,2)         |

| GUANO     | G1        | .0063286      | (2,0)         |

|           | G2        | .8719697      | (7,0)         |

|           | G3        | .9059678      | (7,0)         |

|           | G4        | .9562930      | (8,0)         |

|           | G5        | .3848960      | (2,0)         |

|           | G6        | .2780379      | (2,0)         |

|           | GH1       | .2046974      | (2,0)         |

|           | GH2       | .4215584      | (2,0)         |

| MCRAD     | M1        | .3130292      | (2,0)         |

|           | M2        | .0574623      | (0,0)         |

|           | M3        | .0409673      | (0,0)         |

|           | M4        | .6274798      | (2,1)         |

|           | M5        | .6945399      | (2,1)         |

|           | M6        | .7010670      | (2,1)         |

|           | MH1       | .0706280      | (0,0)         |

|           | MH2       | .6218473      | (2,1)         |

| TORUS-M   | TH1       | .2906896      | (0,0)         |

|           | TH2       | .5704439      | (0,0)         |

| SIMMER    | SH1       | .1115372      | (3,5)         |

|           | SH2       | .2733280      | (3,5)         |

A portion of the segment of Fortran statements associated with the bucket was selected as the Fortran kernel. This was accomplished according to the following procedure.

- a. If the address boundaries of the bucket resulted in incomplete Fortran statements, the segment was expanded to include entire statements.

- b. Starting at the selected address one went "backward in execution" to either the segment boundary or a labeled statement actively accessed from outside the segment. "Active" execution paths are those taken during execution of the code. Whether an execution path was active or inactive was inferred from the STAT histogram of execution within the segment. The selected statement formed the first statement of the Fortran kernel.

- c. From the first statement of the Fortran kernel one went "forward in execution" to either the segment boundary or an active jump outside the segment. The subsegment encountered in this action comprises the Fortran kernel.

If at any time in this selection process additional knowledge of program flow was required, STAT was rerun over the kernel in question with a one-word bucket size. It should be noted that seldom were two possible program flow paths active in the same segment. Thus steps b and c usually consisted of merely identifying the active portion of the segment. The active portion then comprised the kernel.

In summary, kernel selection was accomplished in a straightforward and unbiased manner. The methodology yielded representative samples weighted by frequency of execution in a code.

**Kernel

Implementation**

The code selection yielded an initial 28 kernels to be coded both in COMPASS (CDC 7600 assembly language) and in CAL (CRAY-1 assembly language). A careful examination of the segments, from which each kernel was selected, established coding assumptions for each kernel. Some examples of coding assumptions follow. By examining the section of code from which the kernel was extracted one could determine variables local to the kernel. These variables were left in registers after calculation but not stored to memory. If a variable was a DO loop index, it was assumed to be in a register and not fetched from memory every time it was used. On the CRAY-1, B and T registers were used for temporary storage whenever feasible. Both the Fortran statements and the coding assumptions were incorporated as comments at the beginning of each kernel.

The evaluation team was assigned two full-time programmers and the services of two data analysts. One programmer was the primary author of the majority of the COMPASS kernels, while the other was the primary author of the CAL kernels. The data analysts took the handwritten code, punched the decks, and assembled and executed the kernels. They corrected some assembly errors and kept a file of all the decks and listings. This technique let the programmers concentrate their efforts on writing correct and efficient kernels. The success of this technique is indicated by the fact that it took only five weeks to completely write, assemble, and make the first debug pass over 52 assembly language kernels--26 COMPASS and 26 CAL. Two of the 28 kernels were nothing more than a block transfer of data from Large Core Memory (LCM) to Small Core Memory (SCM) on the CDC 7600. Since no such transfer is necessary on the CRAY-1, the kernels "exceeded" the speed ratio criterion and no coding was necessary.

Following the programming of the kernels the programmers spent four weeks debugging the kernels, "tuning" the code for efficiency, and verifying that the kernels satisfied the execution assumptions. Both programmers verified all kernels for accuracy and efficiency. The CAL and COMPASS versions of each kernel were checked against each other, instruction by instruction, by both programmers to verify their functional equivalence. The data analysts continued making all changes, executing the kernels, and updating the files.

A further pass over all the kernels was made by other experienced assembly language programmers.

These people looked for errors in the documentation and the coding and checked to see if any improvement could be made in the efficiency of the kernels. This pass revealed few substantial errors. Most corrections were aimed toward improvement in documentation. Once this process was complete the suggested changes were incorporated, and the kernels sent to FEDSIM for final review. Changes suggested by FEDSIM were then incorporated to produce the finished kernels.

The following steps were taken to guarantee that the implemented kernels are efficient and accurate.

1. The authors of the kernels were chosen for their experience in efficient coding. They were extremely knowledgeable about the architecture of the two machines that were programmed.

2. REGREF, a LASL-developed software tool that statically analyzes COMPASS code for efficiency, was used as an aid in optimizing the COMPASS kernels.

3. Both the two-man checkout and the cross-checking by other programmers were done to correct inefficiencies and to minimize any differences in efficiency attributable to individual programmers.

The assembly language listings of the kernels, timing information and driver programs comprise about 350 pages of output. In addition, from one to ten pages of Fortran text were extracted for each kernel in order to define the kernel and establish the coding assumptions relevant to the kernel. The STAT-generated output used to locate and define the kernels is approximately 500 pages long for the five monitored codes. Source listings of the monitored codes were so lengthy that they were tractable only in microfiche format.

Because of the length of this material, no listings can be reproduced in this report. However, listings of kernel E1 are presented as an example in Figure B-3.

Timing

Results

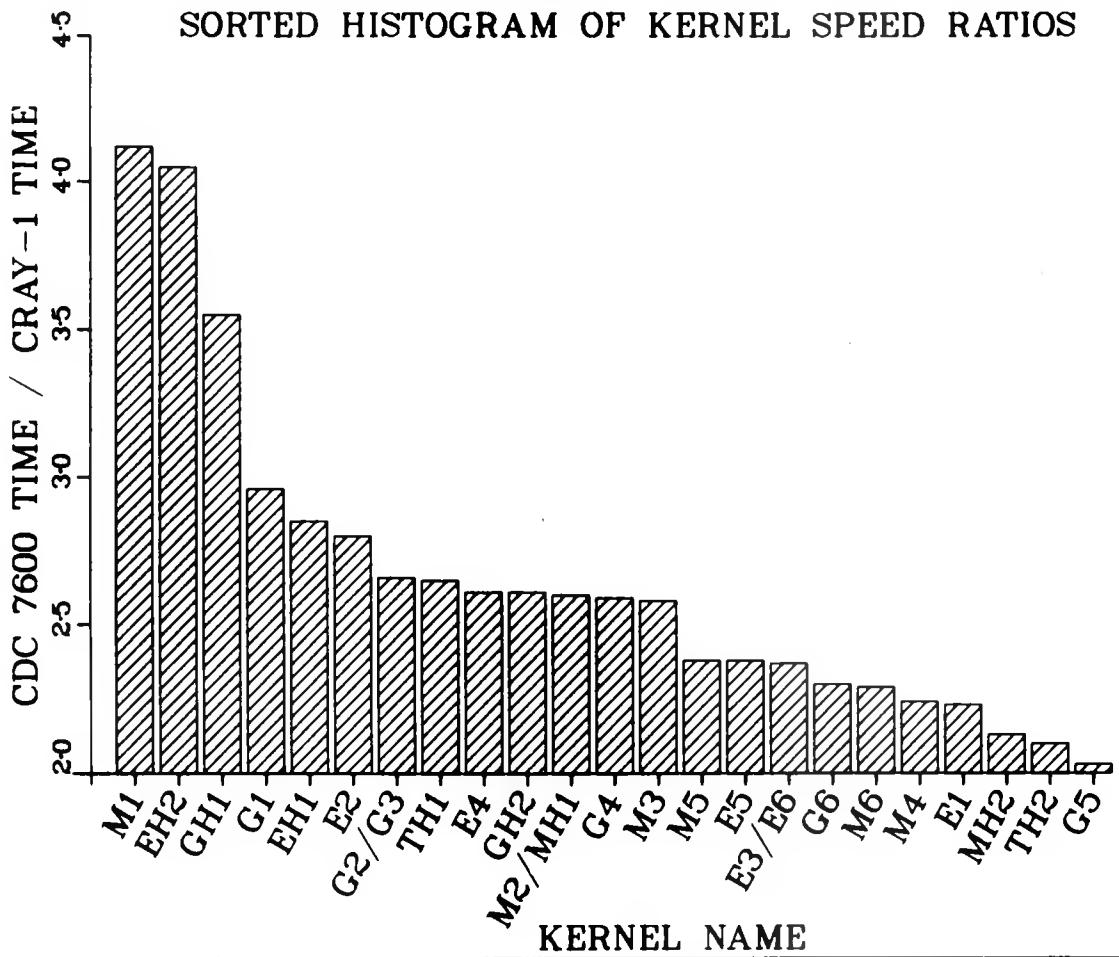

Results of the kernel timings are displayed in Table III-6. A sorted histogram of the kernel speed ratios is displayed in Figure III-1.

Table III-6. Timing Results.

| Code<br>Name | Kernel<br>ID | Subprogram<br>Name | Absolute<br>Address<br>Octal | CRAY-1<br>Cycles | CDC 7600<br>Cycles | CDC 7600<br>Time/<br>CRAY-1 Time |

|--------------|--------------|--------------------|------------------------------|------------------|--------------------|----------------------------------|

| EOTOTO       | E1           | HYDRO              | 130020-130040                | 80               | 81                 | 2.23                             |

|              | E2           | FLYPART            | 112760-113000                | 92               | 117                | 2.80                             |

|              | E3           | ALNLOG             | 134120-134140                | 93               | 100                | 2.37                             |

|              | E4           | FLYPART            | 110140-110160                | 75               | 89                 | 2.61                             |

|              | E5           | ACECASE            | 131660-131700                | 100              | 108                | 2.38                             |

|              | E6           | ALNLOG             | 134120-134140                | 93               | 100                | 2.37                             |

|              | EH1          | ACETOTN            | 127070-127100                | 64               | 83                 | 2.85                             |

|              | EH2          | ACETOTN            | 127020-127040                | 51               | 94                 | 4.05                             |

| GUANO        | G1           | EOSE               | 61200-61220                  | 121              | 163                | 2.96                             |

|              | G2           | NSOLV              | 123220-123240                | 130              | 157                | 2.66                             |

|              | G3           | NSOLV              | 123220-123240                | 130              | 157                | 2.66                             |

|              | G4           | UDDER              | 101020-101040                | 117              | 138                | 2.59                             |

|              | G5           | CSOLV              | 115440-115460                | 117              | 108                | 2.03                             |

|              | G6           | CSOLV              | 115320-115340                | 44               | 46                 | 2.30                             |

|              | GH1          | VEPQT              | 107760-110000                | 121              | 195                | 3.55                             |

|              | GH2          | CSOLV              | 115460-115500                | 70               | 83                 | 2.61                             |

| MCRAD        | M1           | RADSWP             | 71640-71660                  | 47               | 88                 | 4.12                             |

|              | M2           | TEXP               | 44463-44512                  | 49               | 58                 | 2.60                             |

|              | M3           | TLOG               | 44463-44512                  | 46               | 54                 | 2.58                             |

|              | M4           | H2200              | 103620-103640                | 51               | 52                 | 2.24                             |

|              | M5           | H2200              | 105120-105160                | 72               | 78                 | 2.38                             |

|              | M6           | H2200              | 105200-105220                | 72               | 75                 | 2.29                             |

|              | MH1          | TEXP               | 44463-44512                  | 49               | 58                 | 2.60                             |

|              | MH2          | H2100              | 103600-103620                | 67               | 65                 | 2.13                             |

| TORUS-M      | TH1          | BAAL               | 31460-31500                  | 64               | 77                 | 2.65                             |

|              | TH2          | BAAL3              | 44660-44700                  | 111              | 106                | 2.10                             |

| SIMMER       | SH1*         | ECSRW              | 15520-15540                  | --               | --                 | --                               |

|              | SH2*         | ECSRW              | 15520-15540                  | --               | --                 | --                               |

\*These two kernels perform large core memory/small core memory transfers on the CDC 7600. No such transfers are necessary on the CRAY-1. Hence, these kernels "exceed" the speed ratio criterion and did not require implementation.

FIGURE III-1.

SORTED HISTOGRAM OF KERNEL SPEED RATIOS

All kernels drawn displayed a speed ratio that was in excess of 2.0. Thus it was not necessary to draw more than six kernels per test (with the exception of the Class VI workload test in which two kernels from each of the five codes were chosen). This result was unexpected because of the following simple analysis. The ratio of CPU cycle times for the two machines is 2.2. The ratio of memory access times is 1.8. If one assumes the cycle counts for instructions to be roughly equivalent, then one would expect the speed ratio to bracket this range. A careful analysis of the coded kernels revealed that certain hardware features of the CRAY-1 resulted in the kernels being coded in fewer CRAY-1 instructions than CDC 7600 instructions, resulting in speed ratios greater than 2.2 in many cases. A summary of these features follows.

#### Impact of Hardware Features

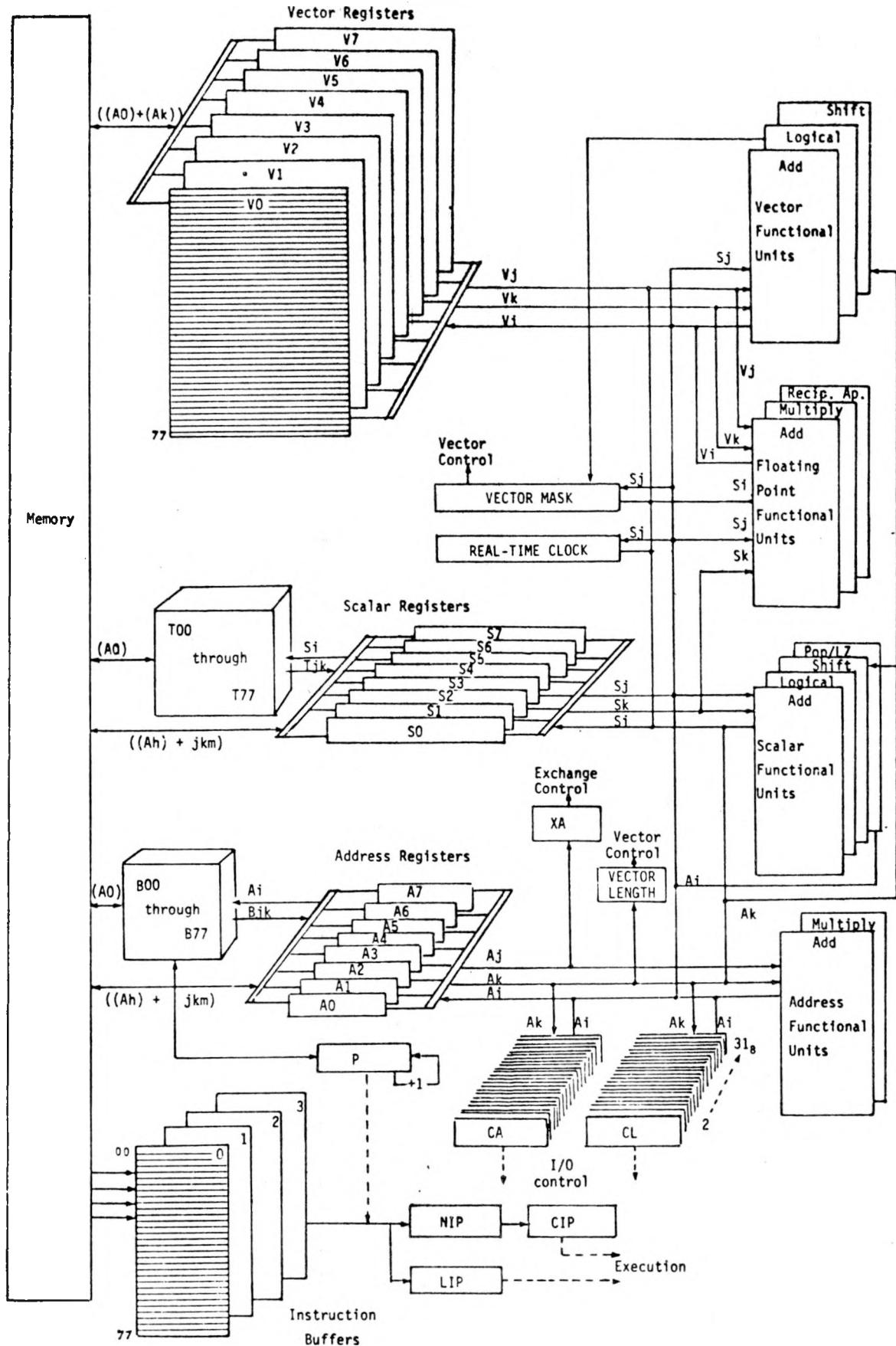

Out of the 26 kernels that were coded, 23 took fewer cycles to execute on the CRAY-1 than on the CDC 7600. In the opinion of the programmers, the CRAY-1 was also easier to program. Both of these facts can be attributed to hardware features that exist on the CRAY-1 and not on the CDC 7600. Some of these features are given here.

1. The B and T registers are available for temporary storage. These registers eliminate the use of memory for partial results that are calculated in a fairly elaborate Fortran expression.

2. Data can be fetched and stored out of all eight S registers. Given the Fortran expression  $I = J$ , it is necessary to fetch J and store it to location I. Since the fetch times are 10 and 8 cycles for the CRAY-1 and the CDC 7600, respectively, it would appear at first glance that the CDC 7600 should take fewer cycles than the CRAY-1. This is not true because the CDC 7600 fetches data into X registers 1-5 and stores out of X registers 6 and 7. So after J is fetched into X1, for example, it must be moved to X6 before being stored. Thus in this case the operation takes the same number of cycles on both machines.

3. Data can be fetched and stored directly to all A registers. This allows index calculations to be completely independent of the S registers and other floating

point calculations.

4. Results from the floating add unit are normalized before being returned to the S register. The floating add unit takes 6 cycles on the CRAY-1 and only 4 cycles on the CDC 7600. But if one adds the cost of normalizing, which is 3 cycles, the add and subtract times are better on the CRAY-1 than on the CDC 7600. Furthermore, because it takes two instructions to complete the add on the CDC 7600 there is always the chance of adding extra cycles due to access path delays.

5. All functional units are fully segmented. On the CDC 7600 the multiply and divide functional units are only partially segmented. The cycle times for the multiply units are 7 and 5 for the CRAY-1 and the CDC 7600, respectively. The full segmentation for the CRAY-1 overcomes this cycle count disadvantage at three successive multiplies. That is, if three successive multiplies are issued on both machines, the last result will be available on both machines at the same cycle.

6. The instruction buffer on the CRAY-1 is much larger than that of the CDC 7600. Forward branching on the CRAY-1 does not necessarily clear the instruction buffer, and in fact most of the forward branches in the kernels were to instructions contained in the instruction buffer.

#### Conclusions

The hypothesis that the CRAY-1 in scalar mode is greater than two times faster than the CDC 7600 was tested individually for three codes (the Class VI applications workload) and for a group of five codes (the Class VI workload). The hypothesis tested as true in all cases. Thus the CRAY-1 meets the scalar performance criterion for each of the three Class VI applications workload codes and for the Class VI workload.

The reader is cautioned that a careful interpretation of these results is necessary. First, the manner in which the kernels were implemented upon each machine was designed to be a test of the hardware, not software, of the system. The performance effects of compilers were not considered. If one assumes that the ability of a compiler to produce efficient code increases with

the man-years invested in the compiler, then one must assume that any CRAY-1 compiler when implemented because of its relative immaturity will produce less efficient code than the very mature optimizing compiler available on the CDC 7600. Second, the tests were made with the CRAY-1 in scalar mode. Since CRAY-1 vector operations are faster than the equivalent scalar operations, vectorization will normally result in higher speed ratios. Third, input/output was not considered in this test. Performance of input/output-bound codes will be determined by the relative performances of the two machines' I/O subsystems. However, it should be noted that on the basis of statistics generated by the STAT sampling routine, the Class VI applications workload codes are heavily CPU-bound on the CDC 7600. Finally, the sample size drawn, while statistically valid for the hypothesis test, is too small to provide us with statistically valid estimates of the total code's speed ratio. The CRAY-1 was tested against a performance threshold for efficient machine language computational kernels, and exceeded this threshold.

SECTION IVVECTOR

PERFORMANCE

CRAY-1 vector algorithms are typically two to five times faster than equivalent scalar algorithms, depending upon vector length and the algorithm's complexity. It is then obvious that the performance of the CRAY-1 relative to the CDC 7600 for a particular code will depend upon the vector operations that can be exploited by that code. Although it would be very desirable to characterize precisely the type and proportion of vector operations each code would employ on the CRAY-1, this is presently an unmanageable task. Converting codes to employ a significant amount of vector operations inevitably requires restructuring of the algorithms. This restructuring may be so trivial that it can be done during compilation or, more typically, may require the efforts of an experienced programmer. Such restructuring was beyond the resources, both time and human, of this evaluation.

The approach of categorizing the "vectorizability" and type of vector operations by automatic examination of source code is meaningless. Any such examination results in a "vectorized" proportion that inevitably increases, possibly by an order of magnitude, when the code is restructured for a vector machine. See Ref. 1 for a more detailed discussion of automatic "vectorization" of programs.

Thus, at this time it is not possible to obtain rigorously "representative" vector functions in order to test the CRAY-1 against the vector criteria. "Vectorized" codes exist at other installations, but none duplicate the LASL workload, and few have been written for the CRAY-1. The approach adopted was to test the CRAY-1 against vector algorithms submitted by the Applications Support and Research Group of the Computer Science and Services Division of LASL that, in their judgement, represented typical vector operations that user codes would perform on the machine. Five operations were chosen to evaluate the machine's vector performance versus vector length. The average of the five speed ratios was chosen to compare against the qualification criteria. Each vector kernel was coded as efficiently as was feasible in assembly language for each machine. In particular, the CDC 7600 kernels were coded so that

all instructions were maintained in the instruction stack of the machine during the operation loop, with functional units overlapped to the fullest extent--a scheme representing very efficient utilization of the CDC 7600.

The five functions were timed on both machines and speed ratios calculated. Timings are presented in Table IV-1. Fortran versions of the five functions are presented in Figure B-4. The average speed ratios of the CDC 7600 execution times to the CRAY-1 execution times for the five functions are 3.39, 4.50 and 5.12 for vector lengths of 20, 100 and 500, respectively. Thus the CRAY-1 meets the vector operations performance criteria as specified in Section III.A.2 of the Evaluation Plan (Appendix A).

---

1. Optimal Utilization of Supercomputers, Volume I - The Control Data 7600, April 1976, R&D Associates, P. O. Box 9695, Marina Del Rey, California.

Table IV-1. Vector Performance Summary.

## A. Execution times of the algorithms (milliseconds):

| Vector Length: | 20            | 100           | 500           |

|----------------|---------------|---------------|---------------|

| Machine:       | CRAY-1 7600   | CRAY-1 7600   | CRAY-1 7600   |

| VVSPVS         | .00190 .00732 | .00537 .02712 | .02268 .12612 |

| VVVPVV         | .00235 .00861 | .00788 .03509 | .03603 .16701 |

| VVVPV          | .00213 .00726 | .00660 .02816 | .02945 .13266 |

| DOTPRO         | .00312 .00649 | .00551 .02189 | .01650 .09889 |

| ADDVEC         | .00180 .00715 | .00523 .02489 | .02278 .11275 |

## B. Ratios of CDC 7600 execution times to CRAY-1 execution times:

|                   |      |      |      |

|-------------------|------|------|------|

| VVSPVS            | 3.85 | 5.05 | 5.51 |

| VVVPVV            | 3.60 | 4.45 | 4.64 |

| VVVPV             | 3.41 | 4.27 | 4.50 |

| DOTPRO            | 2.08 | 3.97 | 5.99 |

| ADDVEC            | 3.97 | 4.76 | 4.95 |

| C. Average Ratio: | 3.39 | 4.50 | 5.12 |

SECTION VRELIABILITY

## Approach

It was considered crucial that any Class VI computer considered for purchase be very reliable. Extended periods of downtime would be intolerable since the programmatic functions served by the computer could not be absorbed by other machines at the Laboratory. Thus rigorous reliability standards were formulated. In addition to "system availability," the single measure that is commonly used to define reliability, two additional reliability criteria were specified. Threshold reliability criteria of at least 80 percent system availability, at least four hours Mean-Time-to-Failure (MTTF) and at most one hour Mean-Time-to-Repair (MTTR) were established by LASL and ERDA as defining an acceptable level of reliability. The reader is referred to the Evaluation Plan (Appendix A) for a precise definition of these measures.

The reliability criteria would have to be met for a contiguous twenty-workday period for the machine to be considered for further procurement. The twenty-day period was established in order to smooth daily fluctuations expected for the measures; the period was considered long enough to prevent a machine meeting the criteria during a "fluke" period of good behavior. In order not to unfairly penalize newly constructed machines, the measures from the best twenty-workday period would be applied against the criteria.

Commonly adopted logging procedures for determining machine reliability were deemed inappropriate due to the special evaluation environment of the CRAY-1. This conclusion is the result of the two observations that:

1. The burden of logging machine reliability falls upon a large number of operators and programmers, and is vulnerable to human error; and

2. The complex environment and primitive operating system of the CRAY-1 make it difficult to isolate CRAY-1 hardware failures from a) operator errors, b) ECLIPSE hardware/software failures, and c) CRAY-1 benchmark operating system software errors (unless a hardware error

interrupt occurs and is handled correctly by the system).

The evaluation environment of the CRAY-1 resulted in the CPU being idle the greatest fraction of time. The mode of operation for running on the machine typically consists of a programmer performing nearly all tasks on the ECLIPSE and running a program on the CRAY-1 for only brief intervals. The CRAY-1 benchmark operating system presently does not have implemented the capability of running a "background" job to keep the machine busy.

#### The EXERCISER Program

The EXERCISER program was written in an attempt to overcome these limitations. The objective of the program is to approximate a production environment on the CRAY-1 by utilizing as many hardware features of the machine as possible for substantial periods of time. The EXERCISER program is self-verifying so that all machine failures, detected at the hardware level or not, will be noted. The program keeps a printed log of the time of each failure. Reliability statistics may be gathered from the printed log, thus minimizing the possibility of human error.

Hardware components specifically being tested are the vector and scalar functional units of the CPU, the memory, and input/output (I/O) components. Unfortunately, I/O was not available on the machine during the first two months of the evaluation.

EXERCISER was adapted from one of the first programs written for the CRAY-1 at LASL. Coded in CAL with PASCAL drivers, it solves for the vector  $x$  the matrix equation  $Ax=y$  by LU decomposition.

For each  $N \times N$  matrix,  $N+1$  systems of equations are solved. The  $A$  and  $y$  are parameterized such that every element of  $x$  in the  $N+1$ th system is near unity. Before  $N$  is incremented, every element of  $x$  is tested against unity. If a "near" unity test fails for any component of  $x$ , a message is dispatched to the operator and the event is logged by the program to a print file. The program then restarts the cycle until it is terminated by the operator. Most failures, such as parity errors, cause termination of the program and a message is dispatched to the operator by the operating system.

After June 15 substantial changes were made in the program in order for it to more fully meet its objective. First,  $N$  was fixed at 705, so as to "exercise" almost all of available memory. The

EXERCISER code and data require approximately 501 000 words.

The second substantial change was the addition of I/O to a DD-19 disk. The control flow of the EXERCISER program remains unchanged with the following exception. At the completion of solving the  $N^{\text{th}}$  system, the LU matrix is written to disk and then read from disk. The  $N+1^{\text{th}}$  system is then solved and the test against unity is made. Any disk errors will result in this test failing. As before, upon detection of a failure, the program logs the failure and transmits a message to the operator.

EXERCISER was run from five to eight hours per day, five days a week throughout the entire six-month period. A sample of the daily log is shown in Figure V-1.

#### Results and Conclusions

Results, by twenty-workday interval, calculated weekly, are displayed in Table V-1. The MTTF measures are also displayed graphically in Figure V-2. Failures are categorized in Table V-2. One sees that the CRAY-1 meets the threshold criteria for numerous periods.

An analysis of failures occurring during EXERCISER runs revealed that "intermittent" memory parity errors dominate. Hardware detection of a memory parity error prompts an interrupt which idles the machine and saves the program counter. EXERCISER is so constructed that from the program counter value and a memory dump, the exact memory bit causing the failure can be determined. According to Cray Research, Inc. (CRI), roughly 60 percent of the intermittent failures were diagnosed to this level of detail, of which all were caused by failure of a single bit. In all but 12 of the memory parity error failures the memory module incorporating that bit could not be made to fail again, neither during EXERCISER nor during various CRI memory diagnostic routines. In the 12 cases of reproducible failure, the memory module was judged defective and replaced. In the remaining cases, tests of the modules by CRI could determine no differences in operating characteristics between "once failing" and "never failing" modules. Once reinstalled in the machine, no module failed again.

CRI made various hardware changes in an attempt to eliminate the failure mode or cause it to replicate at a more rapid rate. None of the hardware changes appeared to affect the failure rate. An obstacle to diagnosing this problem was

the relatively long average interval between failures (4 hours), which implied very long running times during a change to determine if the failure rate had been changed.

Since the "once failing" module was seldom replaced, the MTTR measure should be more accurately labeled "mean-time-to-return," since hardware repairs were infrequent. In order to obtain a more accurate estimate of repair times, the mean-time-to-repair for all EXERCISER failures during which a repair was effected was calculated. For these 20 failures the total down-time was 8.37 hours, resulting in a MTTR of 0.41 hours. From this measure we conclude that only a minor portion of repair time was consumed by the actual hardware change, the major portion being consumed by alerting the engineer and running diagnostic routines.

Since memory parity errors so clearly dominate the statistics, an analysis of EXERCISER was made in an effort to relate its memory access rate to that of a production environment. Memory utilization by EXERCISER is divided into two phases. In the I/O phase, 497 025 memory locations are accessed twice during a 3.10-second period. This results in a memory access rate of approximately 0.0062 times the theoretical maximum of 80 million accesses per second (80 MAPS). In the computation phase of the program, a 705 by 705 matrix is initialized and decomposed and a system of 705 linear equations is solved. This phase lasts 14.11 seconds. The use of vector instructions in the inner computational loop results in 64 memory accesses every 78 clock cycles. The inner loop consumes roughly 90% of the time for this phase. Thus memory is driven at approximately  $0.9 \times 64/78 = .74$  of its maximum of 80 MAPS. Ignoring the memory accesses during the I/O phase, EXERCISER drives the CRAY-1 memory at .74 of its capacity for  $14.11/(14.11 + 3.10) = .82$  of the program's execution, for an overall memory access rate that is 0.61 of its maximum.

Predicting a typical memory access rate for a production environment with the above accuracy is not possible. However, it is plausible that the EXERCISER bandwidth is at least several times higher than that expected for a production workload. Thus we would expect the MTTF for a production workload on the CRAY-1 to be significantly higher than that observed under EXERCISER.

Figure V-1. Daily EXERCISER Log.

## EXERCISER LOG

**EXERCISER VERSION:**

DATE:

**SYSTEM VERSION:**

EXERCISER BEGIN TIME:

**COMMENTS:**

**EXERCISER END TIME:**

OPERATOR'S INITIALS:

CE'S INITIALS:

CE'S INITIALS:

## SUMMARY

Time between EXERCISER start and failure/between failures (minutes).

1. \_\_\_\_\_ 2. \_\_\_\_\_ 3. \_\_\_\_\_ 4. \_\_\_\_\_ 5. \_\_\_\_\_

6. \_\_\_\_\_ 7. \_\_\_\_\_ 8. \_\_\_\_\_ 9. \_\_\_\_\_ 10. \_\_\_\_\_

Time CE has machine for repair (minutes)

1. \_\_\_\_\_ 2. \_\_\_\_\_ 3. \_\_\_\_\_ 4. \_\_\_\_\_

5. \_\_\_\_\_ 6. \_\_\_\_\_ 7. \_\_\_\_\_ 8. \_\_\_\_\_

Time from last failure to

shut off

1.

### No time intervals

1.

Figure V-2. MFTF Graph.

Table V-1.

## Reliability Statistics Summarized by Week.