# SANDIA REPORT

SAND99-1171

Unlimited Release

Printed May 1999

## Thermal Analysis of a SHIELD Electromigration Test Structure

Robert T. Mitchell, David A. Benson, Duane J. Bowman

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia is a multiprogram laboratory operated by Sandia Corporation,

a Lockheed Martin Company, for the United States Department of

Energy under Contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

RECEIVED

JUN 01 1999

OSTI

Sandia National Laboratories

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831

Prices available from (615) 576-8401, FTS 626-8401

Available to the public from

National Technical Information Service

U.S. Department of Commerce

5285 Port Royal Rd

Springfield, VA 22161

NTIS price codes

Printed copy: A04

Microfiche copy: A01

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

SAND99-1171

Unlimited Release

Printed May 1999

## **Thermal Analysis of a SHIELD Electromigration Test Structure**

Robert T. Mitchell and David A. Benson

Advanced Microelectronic Packaging Department

Duane J. Bowman

Reliability Physics Department

Sandia National Laboratories

PO Box 5800

Albuquerque, NM 87185-1082

### **Abstract**

The steady state and transient thermal behavior of an electromigration test structure was analyzed. The test structure was a Sandia SHIELD<sup>©</sup> (Self-stressing HIgh frequency rELiability Device) electromigration test device manufactured by an outside vendor. This device has a high frequency oscillator circuit, a buffer circuit to isolate and drive the metal line to be tested (DUT), the DUT to be electromigrated itself, a metal resistance thermometry monitor, and a heater element to temperature accelerate the electromigration effect.

The original Sandia device was analyzed for the thermal effects of the heater. Significant changes to the thermal characteristics of the device were made when converting the design from the original Sandia fabrication technology to the vendor's fabrication technology. These changes made it necessary to thermally characterize the new device. The thermal effects of DUT self heating and the transient thermal behavior of the DUT due to the high frequency current pulses used to power it were also investigated.

The behavior of the device with only the heater powered was first measured using metal thermometry monitors on a test die and infrared microscopy. These data along with device cross sections were then used to create a 3D computer thermal model. The model was modified to include the effects of DUT self

heating and then further modified to observe the transient thermal behavior of the DUT.

This analysis characterized the temperatures that electronic circuits in the device are exposed to during test, the increase in DUT temperature due to self heating by the electromigration driving signal, and the amplitude of temperature variations along the DUT due to the frequency and amplitude of the electromigration driving signal.

# Contents

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| <b>CHAPTER 1: INTRODUCTION .....</b>                                       | <b>9</b>  |

| 1.1    Background .....                                                    | 9         |

| 1.2    Purpose of the Electromigration Test Structure .....                | 9         |

| 1.3    Importance of Work .....                                            | 9         |

| 1.4    The Electromigration Test Structure .....                           | 10        |

| 1.5    The Thermal Proble .....                                            | 12        |

| 1.6    Outline of Experimental Procedure .....                             | 12        |

| <b>CHAPTER 2: STEADY STATE MEASUREMENTS .....</b>                          | <b>15</b> |

| 2.1    Device Packaging .....                                              | 15        |

| 2.2    Calibration of Temperature Monitor Lines .....                      | 16        |

| 2.3    Infrared Microscope Test Procedure .....                            | 19        |

| 2.4    Results .....                                                       | 21        |

| <b>CHAPTER 3: PHYSICAL THERMAL MODEL ELEMENTS.....</b>                     | <b>23</b> |

| 3.1    Die Dimensions.....                                                 | 23        |

| 3.2    Other Physical Dimensions.....                                      | 26        |

| <b>CHAPTER 4: STEADY STATE THERMAL MODELING .....</b>                      | <b>27</b> |

| 4.1    Thermal Analysis Software .....                                     | 27        |

| 4.2    Material Thermal Conductivities .....                               | 27        |

| 4.2.1    Silicon.....                                                      | 27        |

| 4.2.2    Silicon Dioxide .....                                             | 29        |

| 4.2.3    Thermal Conductivity of Other Materials .....                     | 29        |

| 4.3    Quarter Section Thermal Model .....                                 | 29        |

| 4.4    Steady State Results.....                                           | 31        |

| <b>CHAPTER 5: SELF HEATING OF DUT .....</b>                                | <b>35</b> |

| 5.1    Construction of Half Section Model .....                            | 35        |

| 5.2    Calculation of Power Densities in DUT Volume Heating Elements ..... | 36        |

| 5.3    Effects of DUT Self Heating.....                                    | 36        |

| <b>CHAPTER 6: TRANSIENT HEATING OF DUT .....</b>                           | <b>41</b> |

| 6.1    Additional Transient Model Thermal Properties .....                 | 41        |

| 6.2    Results .....                                                       | 41        |

| <b>CHAPTER 7: CONCLUSIONS .....</b>                                        | <b>45</b> |

| 7.1    Annealing of the Temperature Monitor Element .....                  | 45        |

| 7.2    Heating of Nearby Electronics.....                                  | 45        |

| 7.3    Thermal Gradients along the DUT and Temperature Monitor .....       | 46        |

| 7.4    Effect of DUT Self Heating .....                                    | 48        |

| 7.5    Transient Thermal Response of DUT .....                             | 48        |

| 7.6    Limitations of this Analysis.....                                   | 48        |

| 7.7    Further Work .....                                                  | 49        |

| 7.8    Closing Remarks.....                                                | 50        |

| <b>APPENDIX A: INFRARED MICROSCOPY .....</b>                               | <b>51</b> |

| A.1    Overview .....                                                      | 51        |

| A.2    How the Infrared Microscope Measures Temperature .....              | 51        |

| A.2.1    Emissivity Determination .....                                    | 52        |

| A.2.2    Cancellation of Narcissus Effect .....                            | 53        |

| A.2.3    The Infrared Microscope Black Body Calibration Curve .....        | 53        |

|                                                                   |                                                             |    |

|-------------------------------------------------------------------|-------------------------------------------------------------|----|

| A.3                                                               | High Temperature Infrared Measurement Errors .....          | 53 |

| <b>APPENDIX B:DATA FROM INFRARED TESTS .....</b>                  | <b>55</b>                                                   |    |

| B.1                                                               | Temperature Plots.....                                      | 55 |

| B.2                                                               | Resistance Line Data.....                                   | 56 |

| <b>APPENDIX C:THERMAL MODELING SOFTWARE CODE VALIDATION .....</b> | <b>57</b>                                                   |    |

| C.1                                                               | The Thermal Modeling Software .....                         | 57 |

| C.2                                                               | Finite Difference Calculations.....                         | 57 |

| C.3                                                               | Example Problem .....                                       | 59 |

| C.3.1                                                             | Example: A 2D Plate with One Heated Edge .....              | 59 |

| C.3.2                                                             | Example: Transient Heat Flux at the edge of a 3D Solid..... | 61 |

| C.3.3                                                             | Example: 1D Fin with Convection .....                       | 63 |

| <b>REFERENCES.....</b>                                            | <b>65</b>                                                   |    |

# Figures

|                                                                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1. Block diagram of electromigration test structure .....                                                                                                                 | 10 |

| FIGURE 2. Layout drawing of electromigration test structure showing features drawn to scale and the 100 $\mu\text{m}$ by 100 $\mu\text{m}$ pads for electrical connections ..... | 11 |

| FIGURE 3. Top view of 3 x 4 mm test die showing electromigration test structures to be monitored .....                                                                           | 15 |

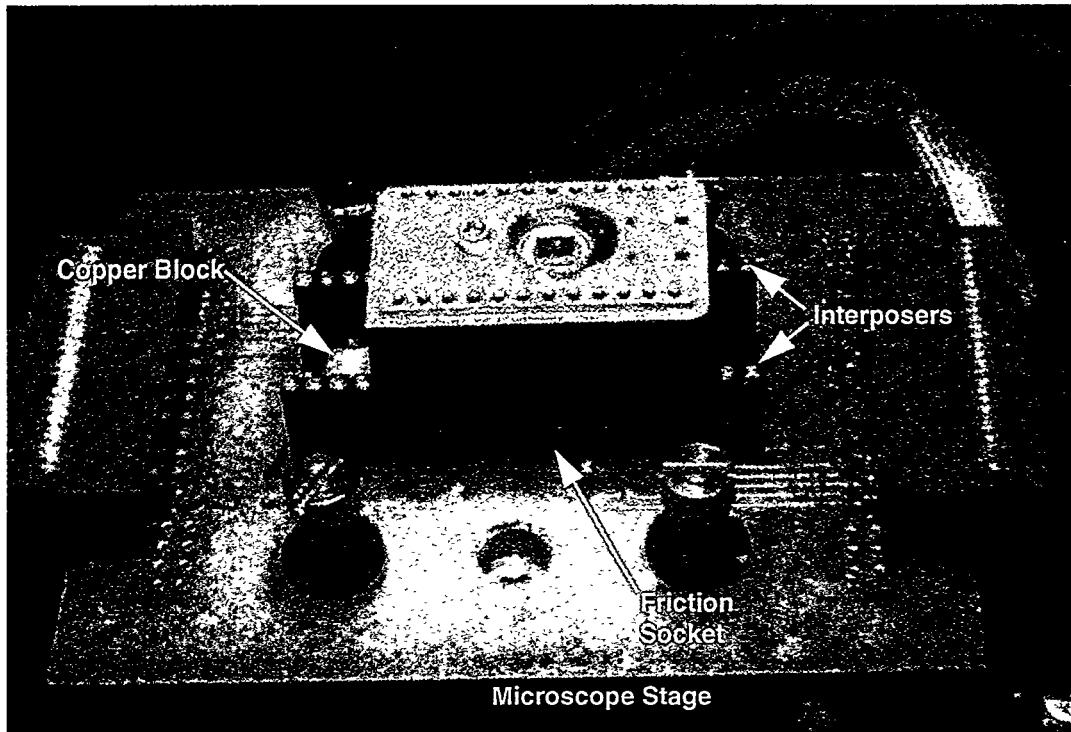

| FIGURE 4. Packaging of electromigration test die.....                                                                                                                            | 16 |

| FIGURE 5. Mounting of packaged part to infrared microscope stage.....                                                                                                            | 17 |

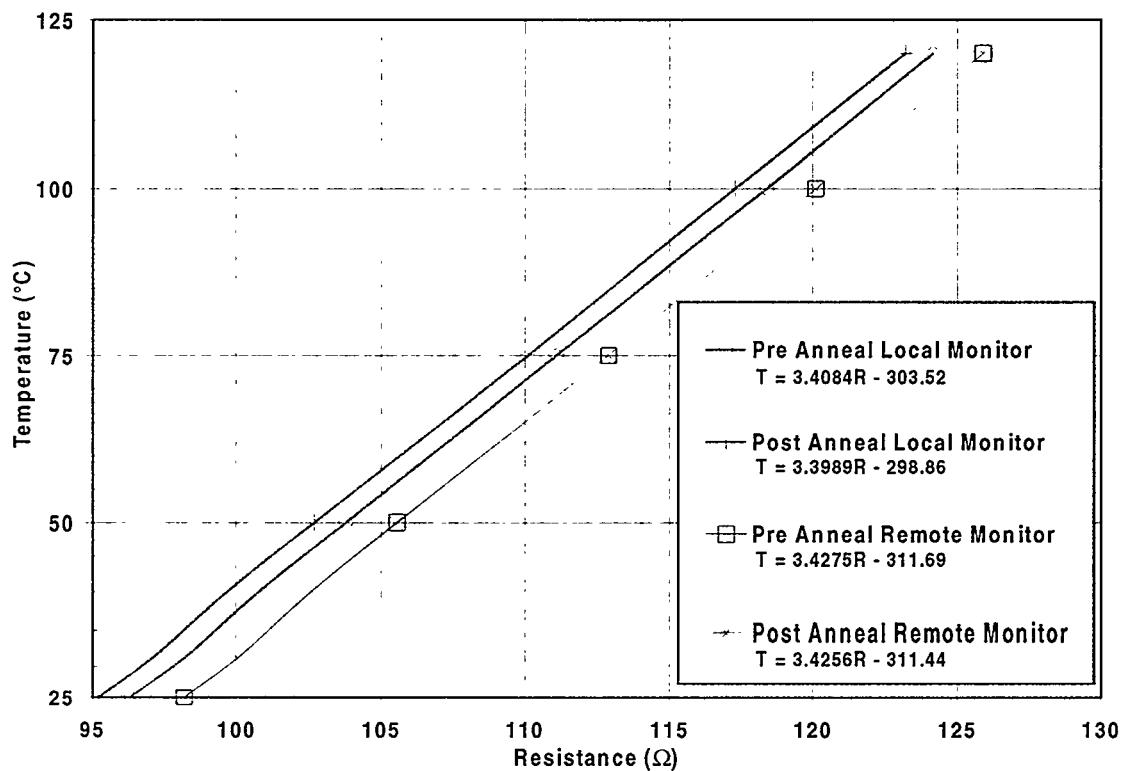

| FIGURE 6. Temperature calibration data for temperature monitor lines .....                                                                                                       | 18 |

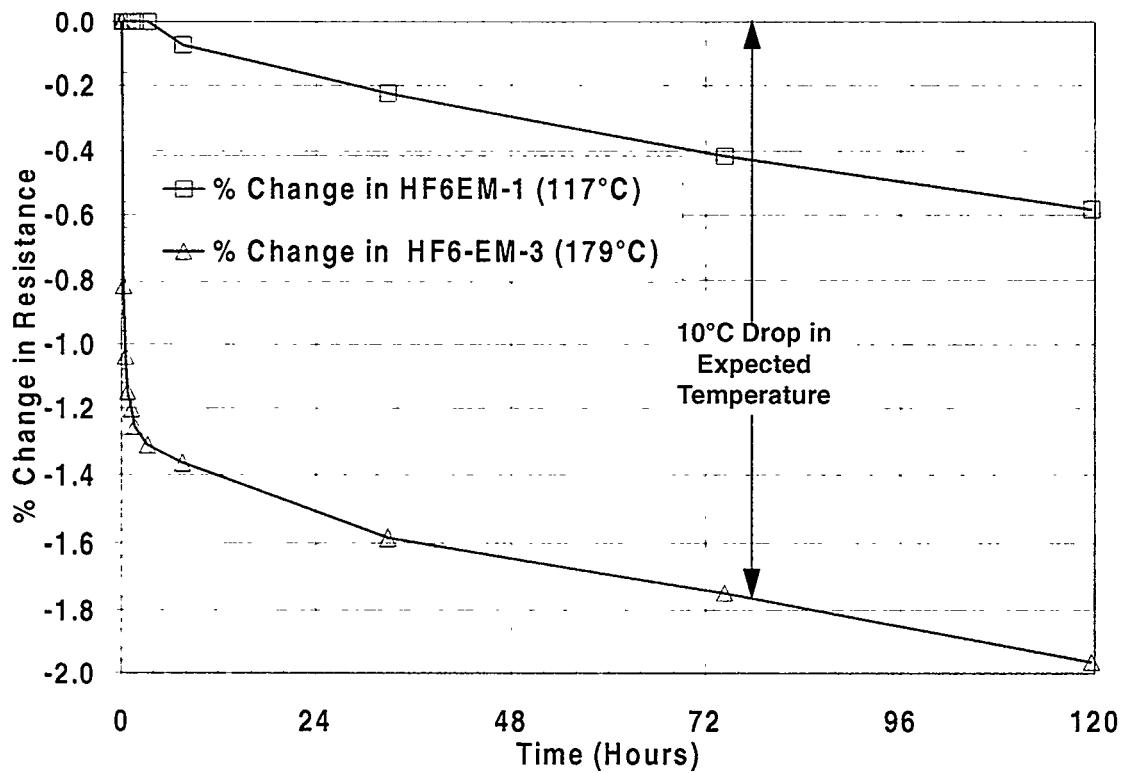

| FIGURE 7. Results of long-term annealing on temperature monitor resistances .....                                                                                                | 18 |

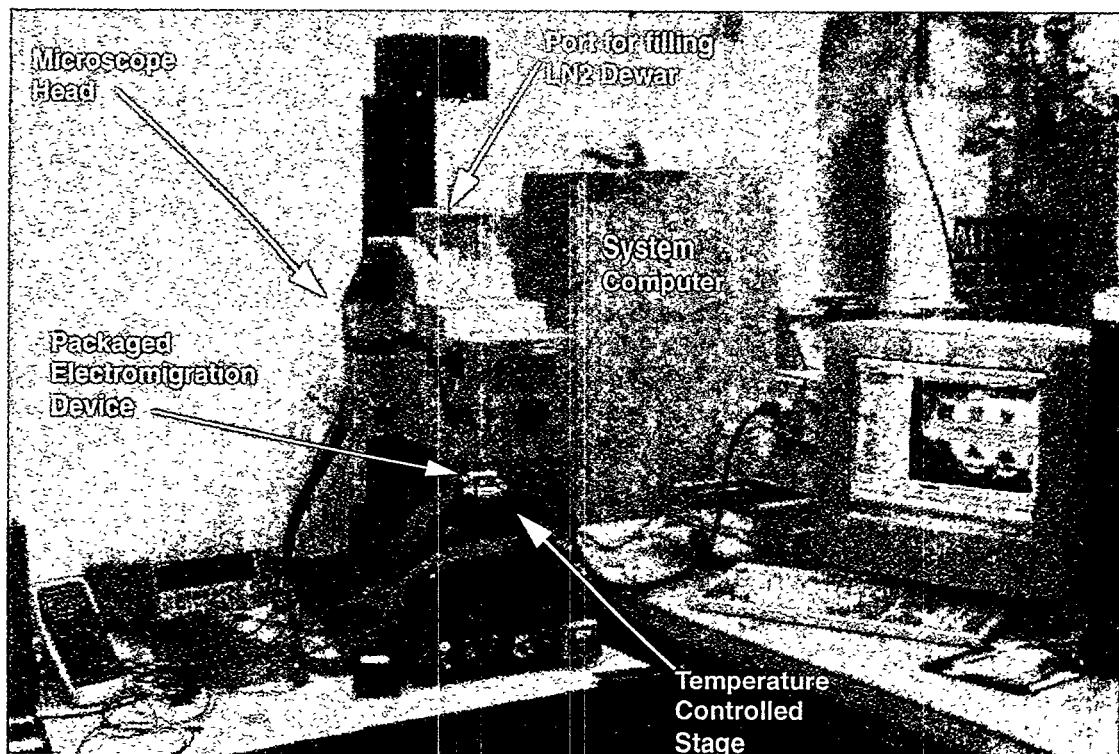

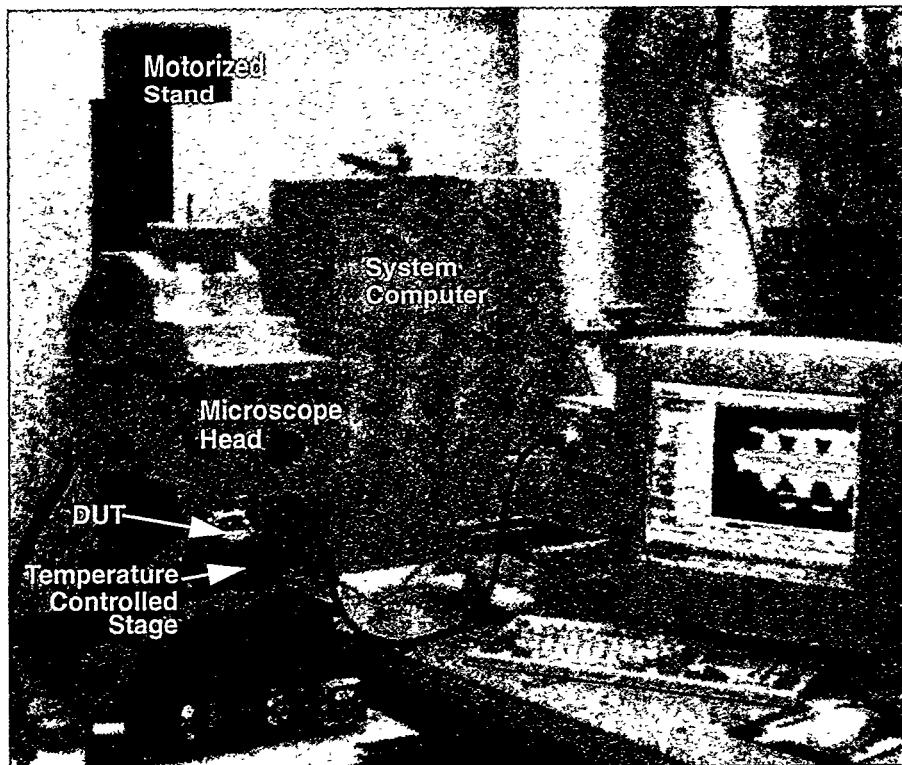

| FIGURE 8. Test setup using infrared microscope .....                                                                                                                             | 20 |

| FIGURE 9. Temperature versus test die xy dimension (mm) with 5 W of heater power at 1X magnification .....                                                                       | 20 |

| FIGURE 10. Infrared surface temperature data along heater length compiled from 1X and 10X measurements .....                                                                     | 22 |

| FIGURE 11. Infrared surface data across 15 $\mu\text{m}$ heater width and adjacent die surface ..                                                                                | 22 |

| FIGURE 12. Optical photo showing distance from buffer electronics to end of heater....                                                                                           | 23 |

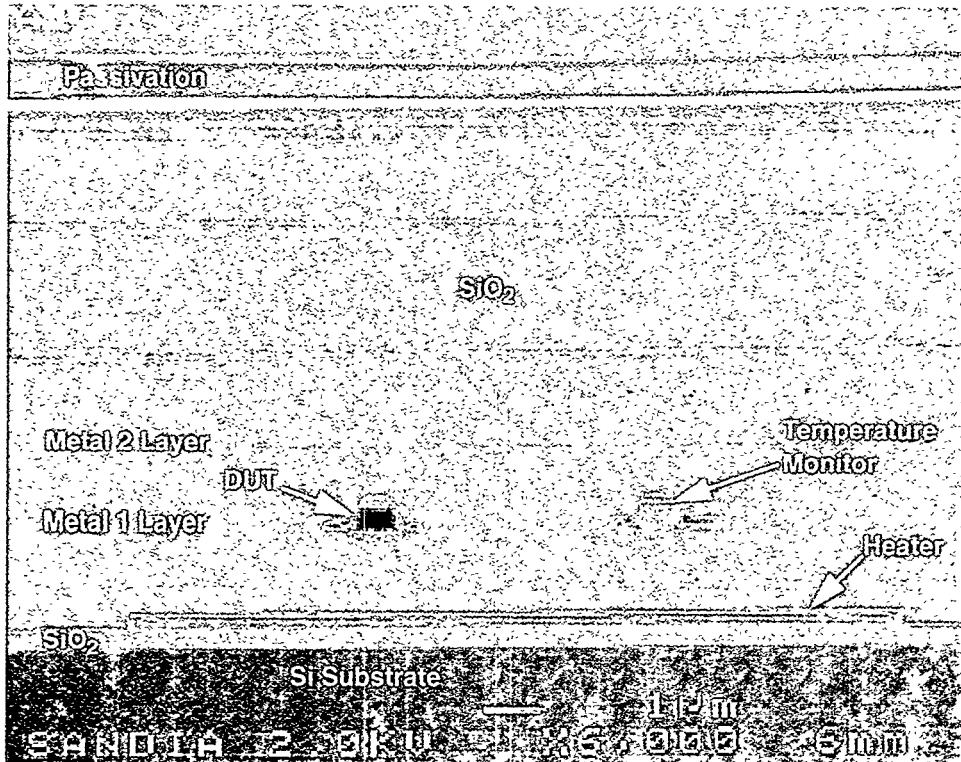

| FIGURE 13. SEM photograph of cross section of electromigration structure .....                                                                                                   | 24 |

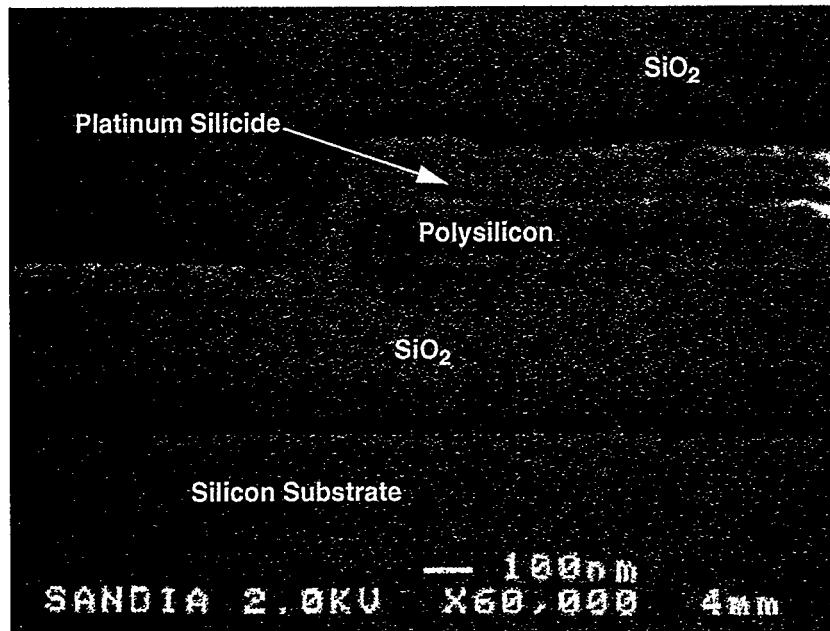

| FIGURE 14. SEM photograph of heater cross section .....                                                                                                                          | 25 |

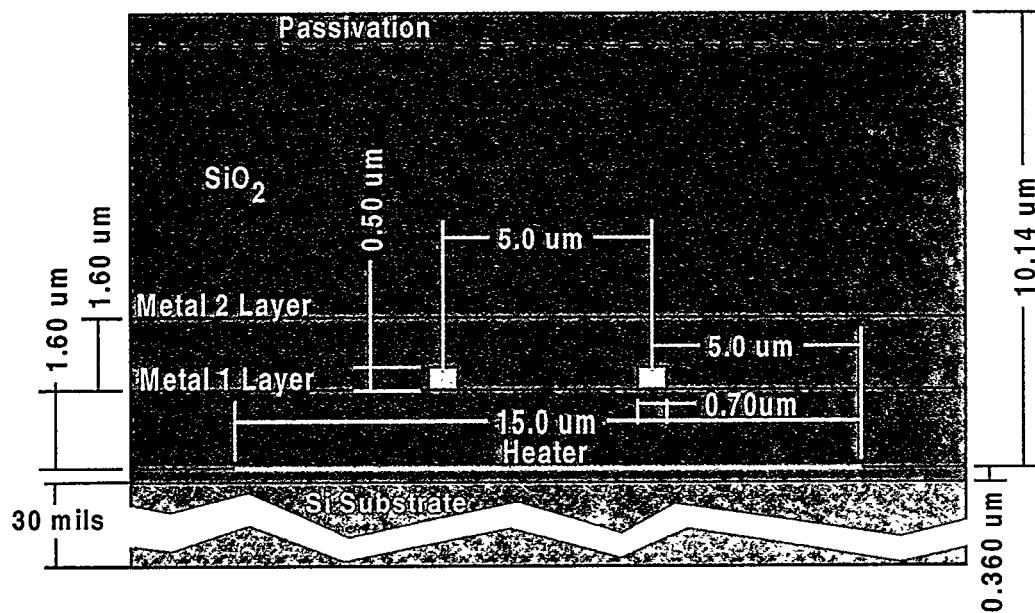

| FIGURE 15. Diagram of critical electromigration structure dimensions .....                                                                                                       | 25 |

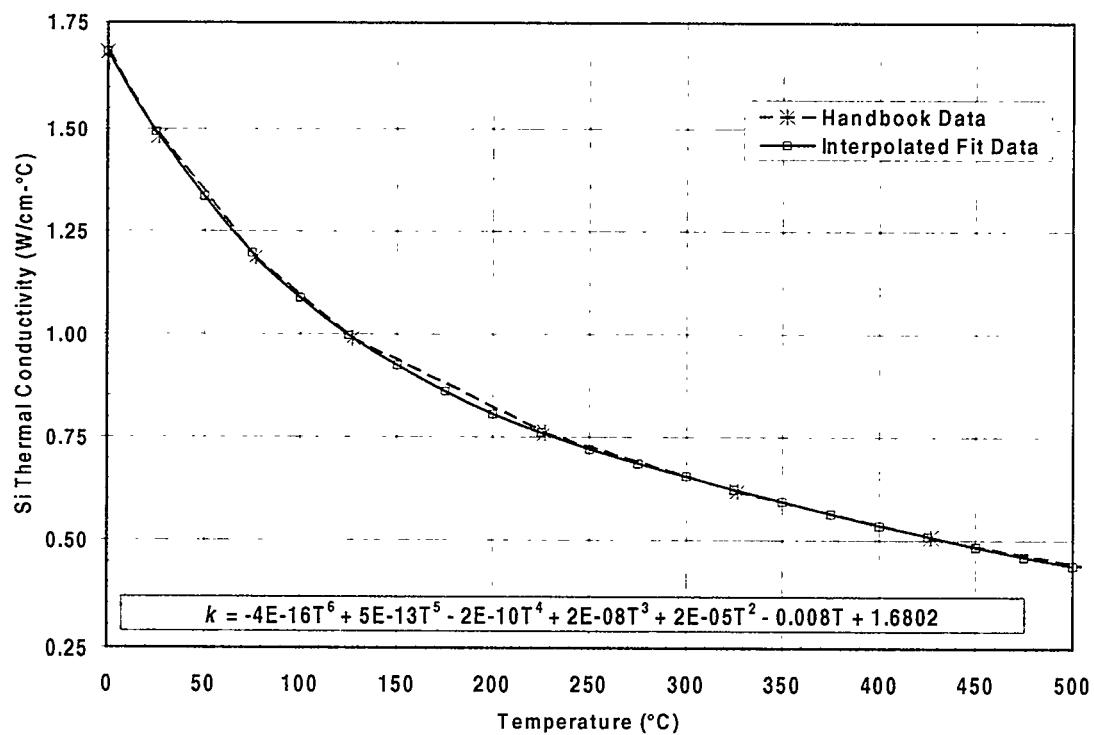

| FIGURE 16. Interpolated thermal conductivity of silicon .....                                                                                                                    | 28 |

| FIGURE 17. Interpolated and scaled $\text{SiO}_2$ thermal conductivity data .....                                                                                                | 28 |

| FIGURE 18. Quarter section model pictorial diagram .....                                                                                                                         | 30 |

| FIGURE 19. Fan style meshing of silicon near heater .....                                                                                                                        | 31 |

| FIGURE 20. Modeled data along heater length .....                                                                                                                                | 32 |

| FIGURE 21. Modeled surface temperatures across heater width.....                                                                                                                 | 33 |

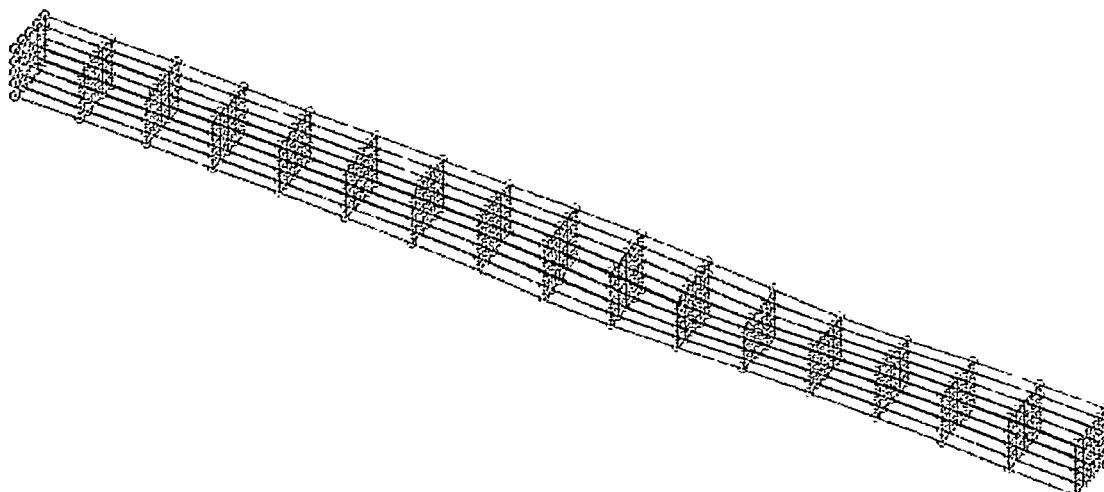

| FIGURE 22. Center elements of half section model .....                                                                                                                           | 35 |

| FIGURE 23. Self heating of DUT at 5 $\text{MA}/\text{cm}^2$ .....                                                                                                                | 37 |

| FIGURE 24. Effect of 7°C temperature error on extrapolated electromigration data .....                                                                                           | 37 |

| FIGURE 25. Self heating of DUT at various current densities .....                                                                                                                | 38 |

| FIGURE 26. Transient response of DUT at 5 MHz .....                                                                                                                              | 42 |

| FIGURE 27. Thermal rise and fall characteristics of DUT .....                                                                                                                    | 42 |

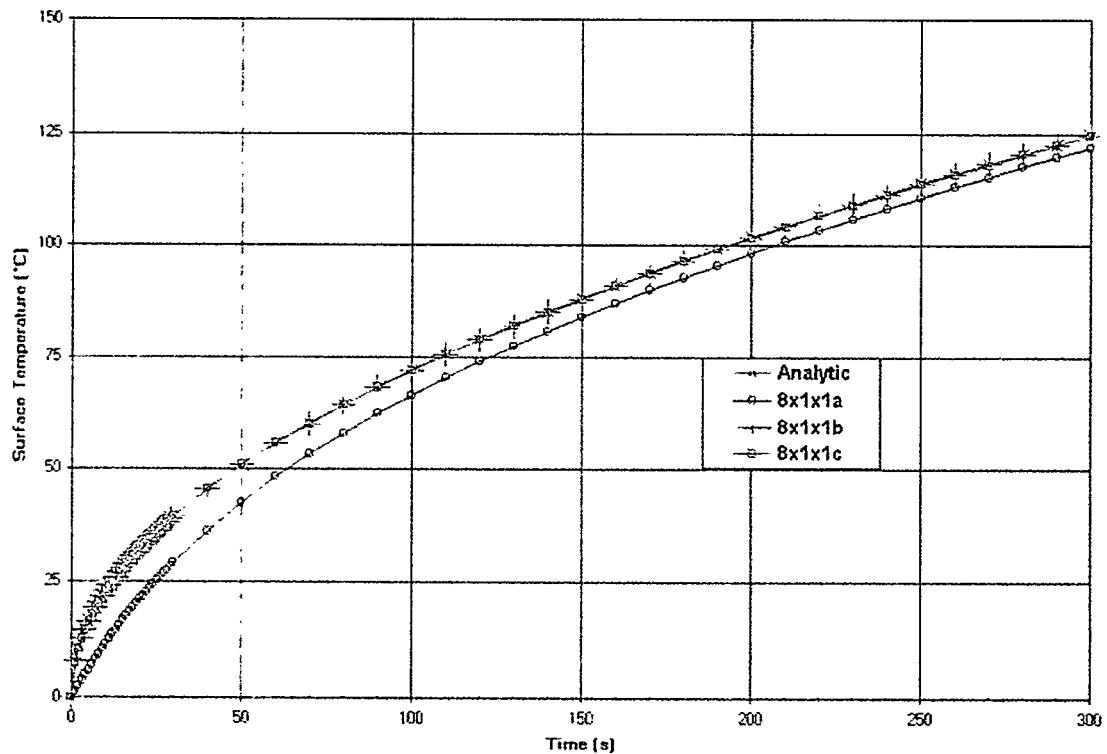

| FIGURE 28. Quarter of heater surface temperature profile at 5 W of power .....                                                                                                   | 47 |

| FIGURE 29. InfraScope infrared microscope .....                                                                                                                                  | 51 |

| FIGURE 30. Emissivity ( $\epsilon$ ) versus xy die dimensions ( $\mu\text{m}$ ) .....                                                                                            | 52 |

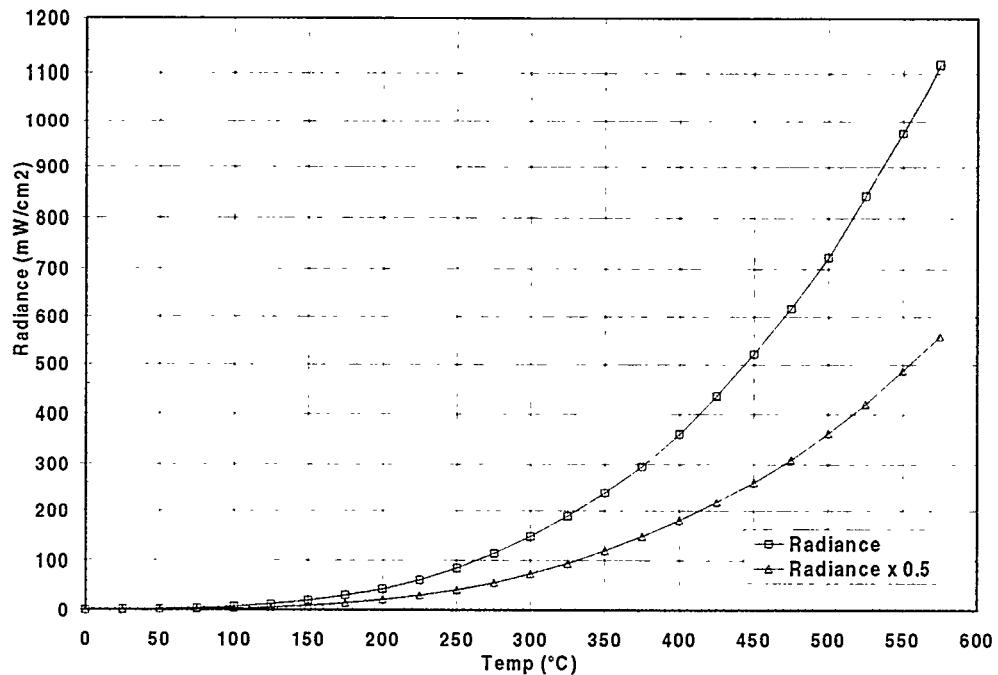

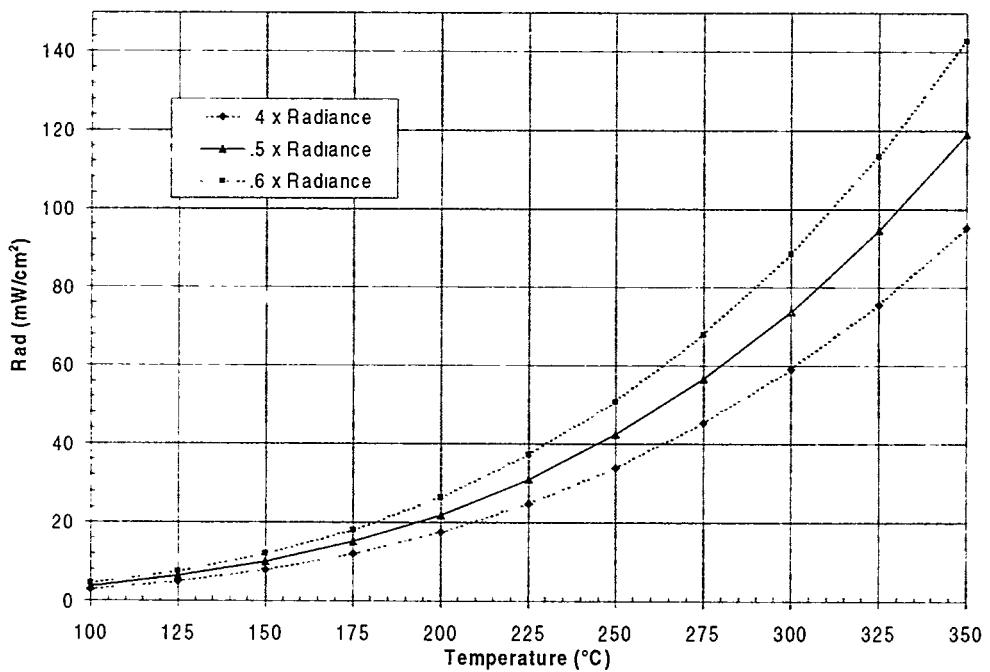

| FIGURE 31. Radiance vs. temperature for a black body at 100% and 50% emissivity....                                                                                              | 54 |

| FIGURE 32. Result of $\pm 20\%$ emissivity variation at various temperatures .....                                                                                               | 54 |

| FIGURE 33. Infrared temperature versus die xy dimension (mm) for die corner area using 5X lens .....                                                                             | 55 |

| FIGURE 34. Infrared temperature versus die xy dimension (mm) for heater area using 5x lens .....                                                                                 | 55 |

| FIGURE 35. 10X temperature versus die xy dimension ( $\mu\text{m}$ ) for end of powered heater.....                                                                              | 56 |

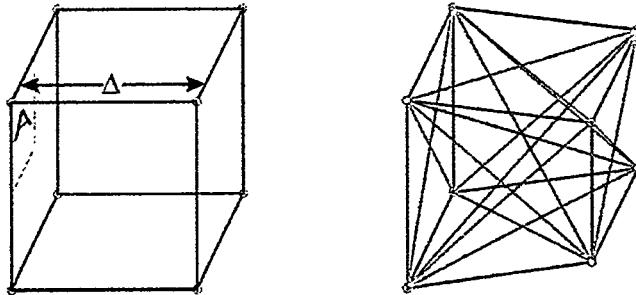

| FIGURE 36. Comparison of RC elements for rectangular and non-rectangular bricks .....                                                                                            | 57 |

|                                                                              |    |

|------------------------------------------------------------------------------|----|

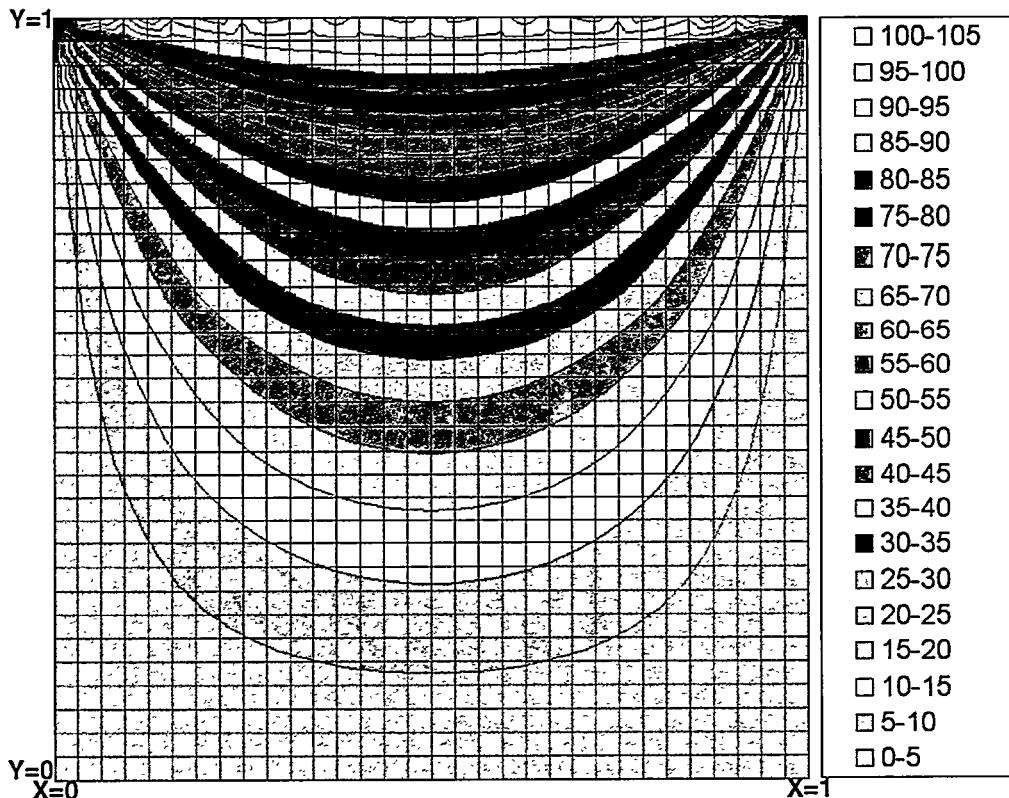

| FIGURE 37. 99 term Fourier analysis of plate showing temperatures (°C) ..... | 59 |

| FIGURE 38. TAS model of 2D plate problem temperatures (°C) .....             | 60 |

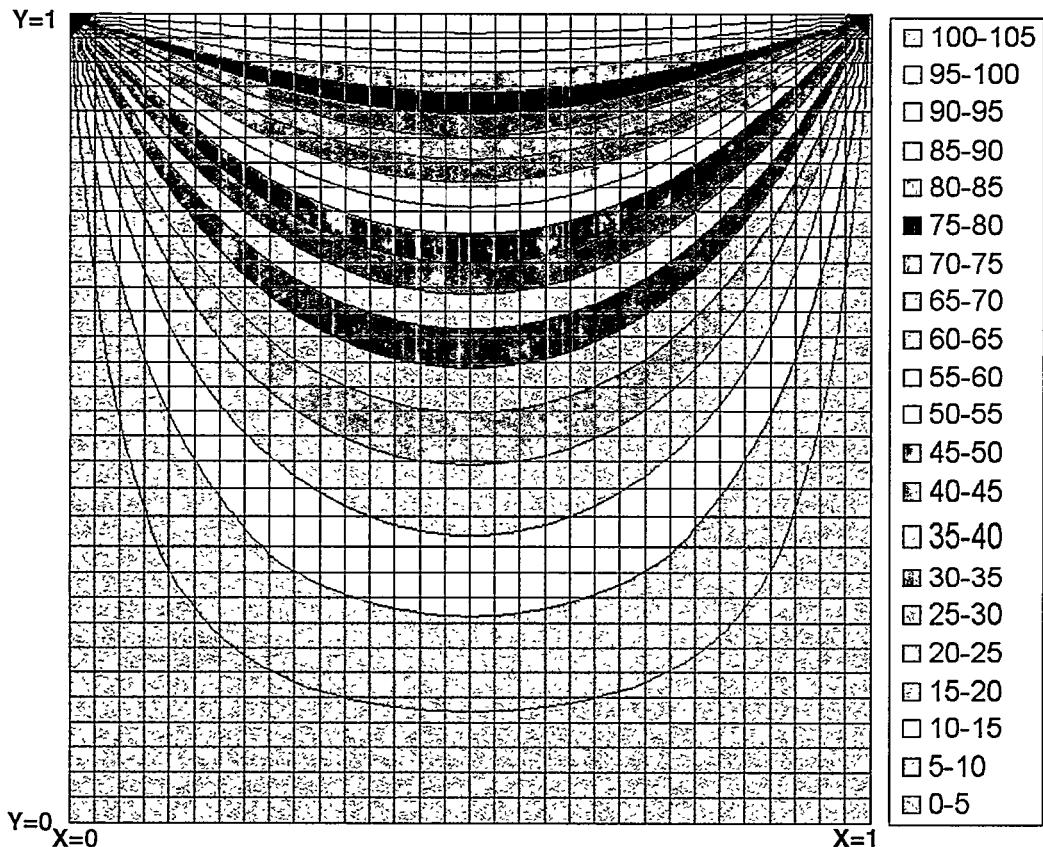

| FIGURE 39. TAS models for transient example .....                            | 62 |

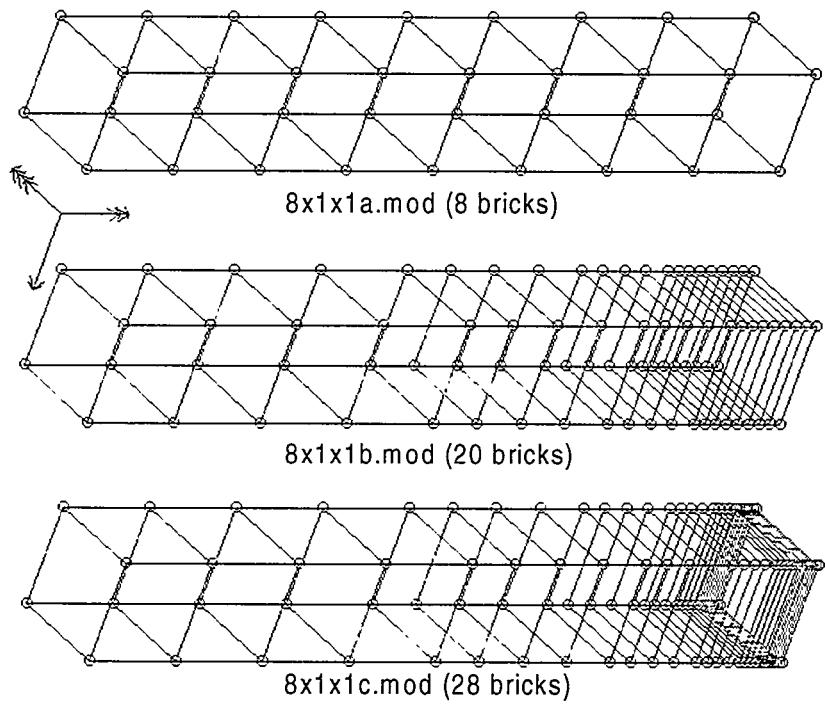

| FIGURE 40. Transient heating comparisons .....                               | 62 |

| FIGURE 41. TAS model of silicon fin .....                                    | 63 |

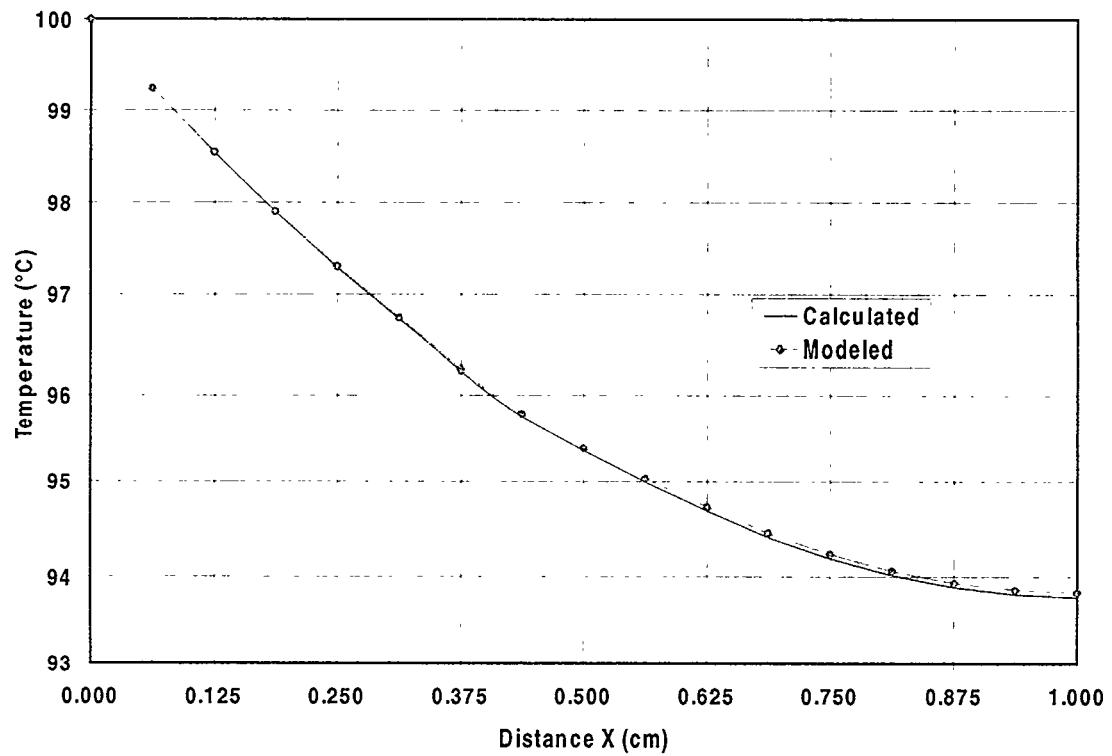

| FIGURE 42. Temperature profile along length of Si fin .....                  | 64 |

## Tables

|          |                                                                                          |    |

|----------|------------------------------------------------------------------------------------------|----|

| Table 1. | Current and power parameters for powered DUT .....                                       | 36 |

| Table 2. | Average DUT and Temperature Monitor (TM) temperatures at various current densities ..... | 38 |

| Table 3. | Additional property values for aluminum and SiO <sub>2</sub> .....                       | 41 |

| Table 4. | Variations in quarter section model temperatures .....                                   | 46 |

| Table 5. | Infrared test data .....                                                                 | 56 |

| Table 6. | Specific temperature (°C) values from Example 1 .....                                    | 60 |

Intentionally Left Blank

# CHAPTER 1: INTRODUCTION

## 1.1 Background

Sandia National Laboratories has developed a high-frequency self-stressing electromigration test structure on a silicon chip. This device is one in a series of SHIELD<sup>®</sup> (Self-stressing HIgh frequency rELiability Device) test structures<sup>1</sup> developed to aid in the study of high frequency reliability problems. The structure was originally manufactured using Sandia's 0.5  $\mu\text{m}$  CMOS 6 fabrication process. The Sandia device was characterized to determine the thermal effects of operating the heater on nearby CMOS circuitry.<sup>2</sup>

This device was later licensed by an outside vendor and manufactured in a 0.25  $\mu\text{m}$  CMOS process. This process supports five planarized metal interconnect layers as opposed to the original two metal layer Sandia process. As a result of the process change, the new device has different interlevel dielectric thicknesses and a substantially thicker oxide layer over the entire device. A heater structure within the device is used to accelerate the electromigration effect. The heater was narrowed in the new device to keep its resistance in the same range as the Sandia device. Since the new device is significantly different in fabrication from the old one, the new device will be thermally characterized as part of a performance evaluation.

## 1.2 Purpose of the Electromigration Test Structure

The Sandia electromigration test structure was designed to characterize high frequency electromigration phenomena in metal interconnects on integrated circuits at signal frequencies up to 500 MHz.<sup>3</sup> Most electromigration studies have concentrated on DC or low frequency pulsed DC electromigration. Until now, costly special packaging and test setups have made high frequency electromigration tests difficult to perform. This device allows higher frequency electromigration testing to be performed by combining an oscillator, a heater, a thermometry line and an electromigration test line (DUT) into a single test structure. Conductor lengths are minimized in this structure allowing higher frequency pulsed DC and bipolar signals to be used in characterizing the electromigration performance of metal interconnects. An advantage of this device is that electromigration testing can be performed at the wafer level. These test structures can be placed on production wafers. This allows electromigration characteristics of the metal in that product die to be accurately monitored for wafer to wafer process fluctuations using an in-line wafer probing station.

## 1.3 Importance of Work

This thermal characterization work is important for the following reasons:

- The rate of electromigration is extremely sensitive to temperature. A 10°C difference in test temperature can cause a factor of two difference in calculated device lifetime.

- The device electronics must be sufficiently cool to function and may require modification either in die design or packaging to meet this requirement.

- Temperature gradients along the DUT and the temperature monitor must be known. The temperature monitor will measure the average temperature along its full length. Gradients along the DUT length will cause uncertainty in the effective electromigration temperature.

- Self heating due to the high average DUT current during a test may cause the DUT temperature to be significantly different from that measured by the temperature monitor. This temperature difference must be characterized to properly analyze the electromigration data.

- The transient thermal effects of a high frequency pulsed DUT signal will cause deviations in the DUT temperature during a test, depending on the test current frequency and amplitude. This input-related temperature change needs to be characterized so the proper temperature conditions in the high frequency electromigration current model may be used.

## 1.4 The Electromigration Test Structure

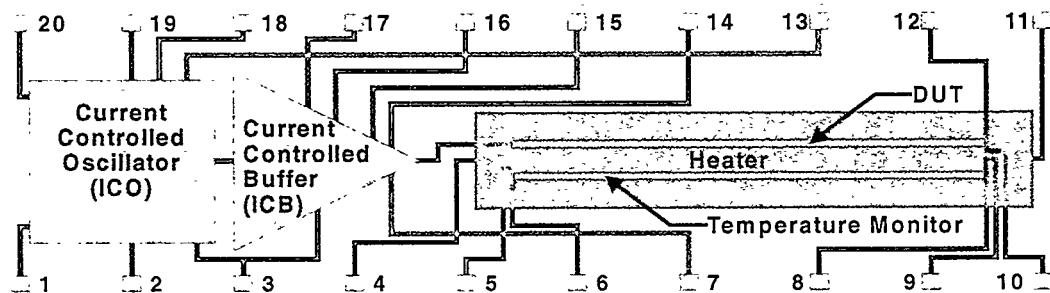

A block diagram of the electromigration test structure is shown in Figure 1. The structure has a current controlled oscillator coupled through a current controlled buffer to a metal line used as an electromigration test strip (DUT). This metal line, and a parallel metal line used as a temperature monitor, are heated by a polysilicon/platinum silicide heater.

The current controlled ring oscillator has two control current inputs. One input controls the time the oscillator remains in the '1' state and the other controls the time the oscillator remains in the '0' state. The oscillator frequency may be varied from 500 kHz to above 500 MHz by varying the current supplied to these inputs. The duty cycle of the oscillator may likewise be varied from 1% to 99%<sup>3</sup> by varying the ratio of the currents on these inputs. An externally generated test signal can be gated into the buffer through another input. The oscillator has two buffered outputs. One output monitors the test signal and the other drives the current controlled buffer stage.

FIGURE 1. Block diagram of electromigration test structure.

**FIGURE 2.** Layout drawing of electromigration test structure showing features drawn to scale and the 100  $\mu\text{m}$  by 100  $\mu\text{m}$  pads for electrical connections.

The current controlled buffer stage prevents loading of the oscillator and also controls the peak current applied to the DUT. A DC current input controls the peak current allowed to drive the DUT during both phases (1 or 0) of the oscillator cycle. This stage also has a separate power input (V<sub>DDB</sub>) to allow larger amplitude signals to drive the DUT. Either a unipolar or a bipolar rectangular signal may be generated and applied to the DUT by varying the ground level (V<sub>SS</sub>) and the power level voltages on both the oscillator and the buffer stages. The buffer stage also has a selectable input that allows the DUT resistance to be measured.

The DUT and the temperature monitor are parallel 0.5  $\mu\text{m}$  wide metal lines 800  $\mu\text{m}$  in length. The device was originally designed using a two layer metal process and different variations of the device place the DUT and the temperature monitor at either the metal 1 or the metal 2 layer. In one version, the temperature monitor is directly above the DUT, with the DUT being on the metal 1 layer and the temperature monitor being on the metal 2 layer. In this version both devices are centered over the heater. A layout drawing for a metal 1 electromigration structure is shown in Figure 2. A metal 1 electromigration structure was used for all of the experimental work in this paper. Thermal performance of this design can be related to other versions of the device using computer thermal modeling.

The heater is a polysilicon layer capped with a thin layer of platinum silicide to increase its electrical conductivity. The heater is 950  $\mu\text{m}$  long and 15  $\mu\text{m}$  wide. The original Sandia device used a 50  $\mu\text{m}$  wide heater and the narrower heater is expected to cause steeper thermal gradients in the vicinity of the DUT and temperature monitor. The heater is under the DUT and the temperature monitor and accelerates the electromigration effect through heating. The heater has only one connection at each end. However the temperature monitor has four connections to allow accurate four point resistance measurements for thermometry to be made.

Normally the polysilicon/silicide heater is driven between 275  $^{\circ}\text{C}$  and 400  $^{\circ}\text{C}$  to accelerate the electromigration effect in the DUT. It is desirable to maximize acceleration of the electromigration effect through heating to shorten test time. The test temperature depends on the amount of copper added to the aluminum lines. Copper is routinely added to aluminum interconnects to enhance electromigration resistance. If the DUT temperature is too high, copper in the DUT will go into solution in the line changing its properties so

they are not representative of the metal as deposited.<sup>4</sup> The temperature monitor is calibrated before the test so that its resistance can be used to determine the test temperature.

In a typical test, the oscillator is set to a desired frequency and duty cycle. The buffer is set to allow a specific peak current to drive the DUT and the supply voltages to both the oscillator and buffer are adjusted to drive the DUT with either a unipolar or bipolar DC signal. A temperature controller circuit monitors the thermometry line resistance to accurately control the DUT temperature. A load comparable to the DUT is connected from the DUT output to ground and the monitored voltage across that load indicates changes in resistance across the DUT. Tests can be run to a DUT electrically open state, or until the DUT resistance increases by some percentage indicating electromigration failure.

## 1.5 The Thermal Problem

The high temperatures on the electromigration test structure present several thermal problems. One problem is heating of the buffer and oscillator circuitry by the polysilicon heater. CMOS circuitry often fails at temperatures around 150°C due to thermal generation of carriers.<sup>5</sup> These intrinsic carriers swamp out the extrinsic carriers present in the material and cause leakage across wells in the device. Excessive heating will also decrease electron and hole mobility resulting in slower slew rates for the circuitry. The last buffer stage is about 75  $\mu$ m from the end of the heater and that temperature will be determined during testing.

Another possible problem is from thermal errors due to thermal gradients along the metal lines over the heater. Thermal gradients along these lines could cause mechanical stress causing them to fail early during testing. It is also desirable that the DUT and the temperature monitor be heated uniformly to the same temperature in order to ensure accurate performance of the device. If the temperature monitor is not uniformly heated, its resistance will represent the average temperature along its length. If the electromigration line is not uniformly heated, the electromigration effect will not be uniform along its length making it difficult to interpret. The thermal gradients along the DUT and temperature monitor are determined.

A second source of heating is a potential problem due to self heating of the DUT from the high peak current density ( $1E6$  A/cm $^2$  to  $10E6$  A/cm $^2$ ) of its test signal. This causes the DUT to actually be hotter than the temperature monitor. This effect is characterized.

Finally, the transient thermal behavior of the DUT will be investigated. The temperature of the DUT is often assumed to be constant during testing, but the driving signal will cause temperature fluctuations along the DUT at a low enough frequency. The amplitude of these temperature fluctuations at different frequencies are determined.

## 1.6 Outline of Experimental Procedure

The following experimental procedure was used to characterize the electromigration test structure.

1. A device was cut from a wafer and packaged to simulate the Sandia characterization packaging scheme. Two temperature monitors, one on the structure being characterized and one on a nearby test structure on the same die were thermally calibrated. Infrared microscopy and the temperature monitors in the test die were used to determine steady state temperatures across the device due to the heater being powered to a desired level.

2. External physical device dimensions were determined from layout drawings and optical microscopy. SEM photos of cross sectioned test die were used to determine internal device dimensions including critical device layer thicknesses.

3. A steady state thermal model of the device with the heater powered was constructed and thermally tuned using the results of 1 and 2 above. This model was used to determine the temperature of electronic circuits close to the heater.

4. The steady state thermal model was modified to include average heating effects of the DUT being powered. This model was then used to determine the thermal profile along the DUT length and any temperature differences between the DUT and the temperature monitor.

5. Transient effects due to the frequency of the DUT signal were added to the self heating model generated in 4 above. This model was used to determine the amplitude of temperature excursions on the DUT during testing.

Each of these sections is dealt with in a separate chapter below.

Intentionally Left Blank

## CHAPTER 2: STEADY STATE MEASUREMENTS

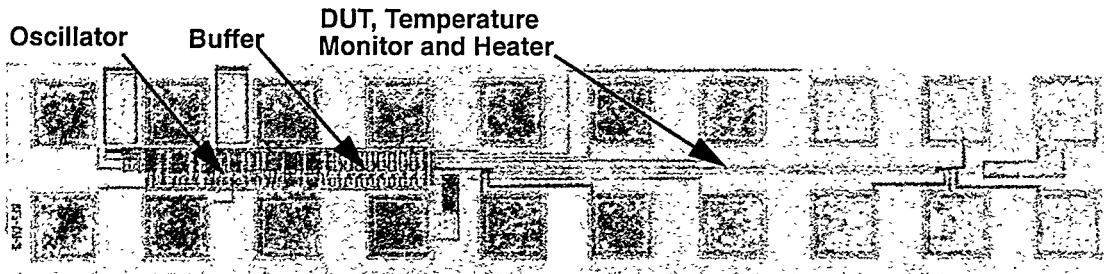

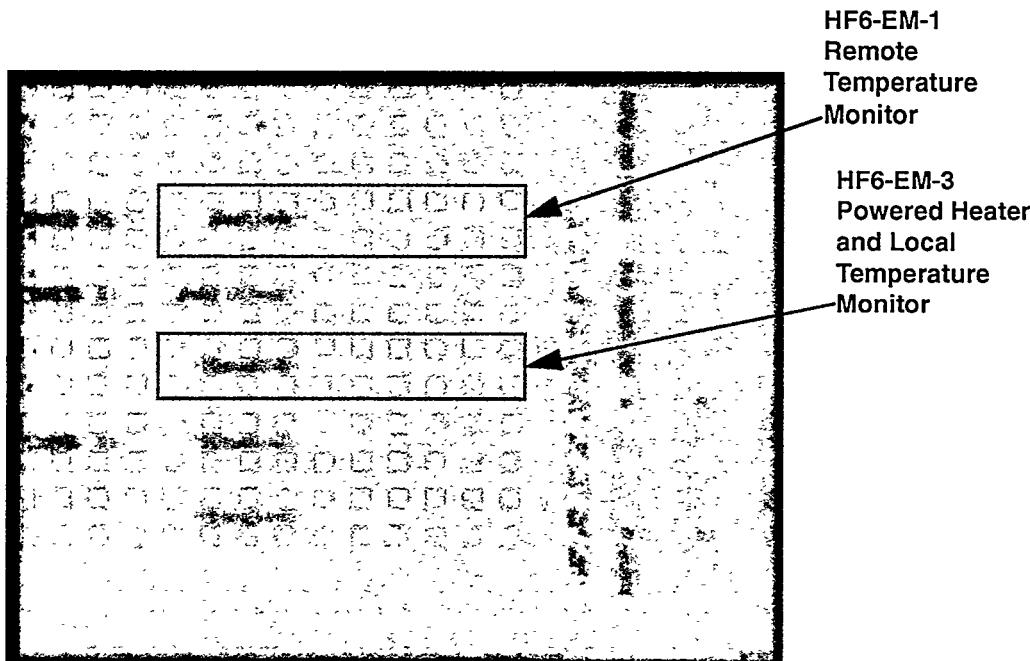

A photograph of a  $3.0 \times 4.0$  mm electromigration test die is shown in Figure 3. The die size was chosen based from previous experience with the Sandia version of the test structure. The size of the test die is important. If the die is made too small, the small die attach area will not allow enough heat conduction to effectively cool the die. A large die requires longer bond wires that can adversely effect high frequency performance. The die was cut to center the HF6-EM-3 electromigration test structure heater to be powered on its surface. The temperature from a nearby test structure (HF6-EM-1) was also monitored in this experiment. Five complete electromigration test structures are visible on this die. This die is cut from a 200 mm wafer and is 0.762 mm (30 mils) thick.

FIGURE 3. Top view of  $3 \times 4$  mm test die showing electromigration test structures to be monitored.

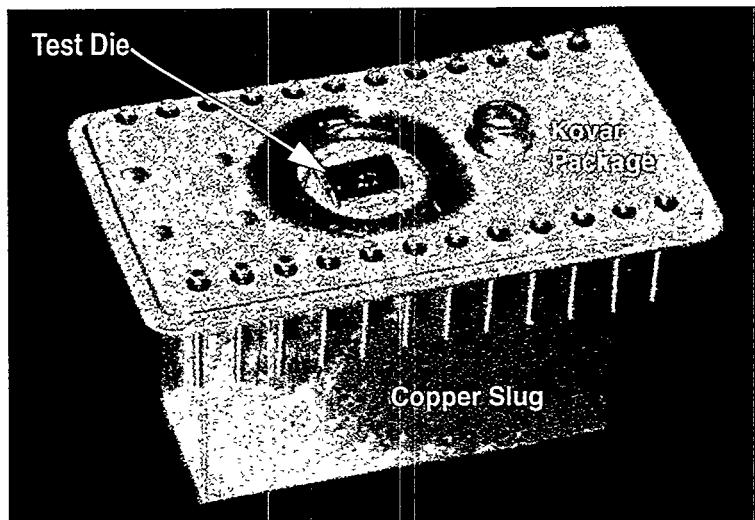

### 2.1 Device Packaging

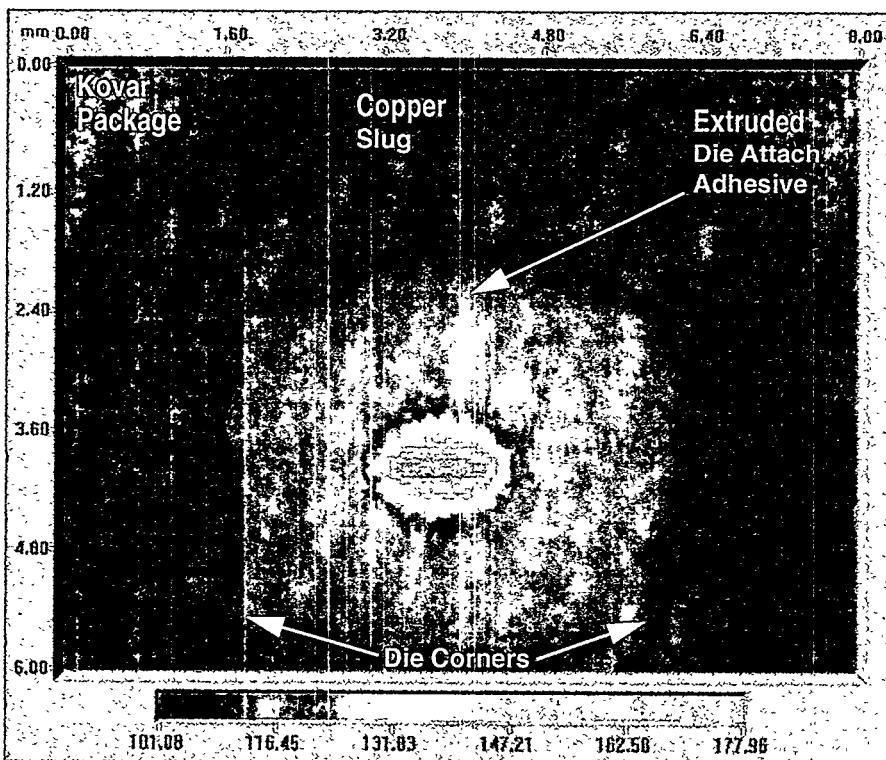

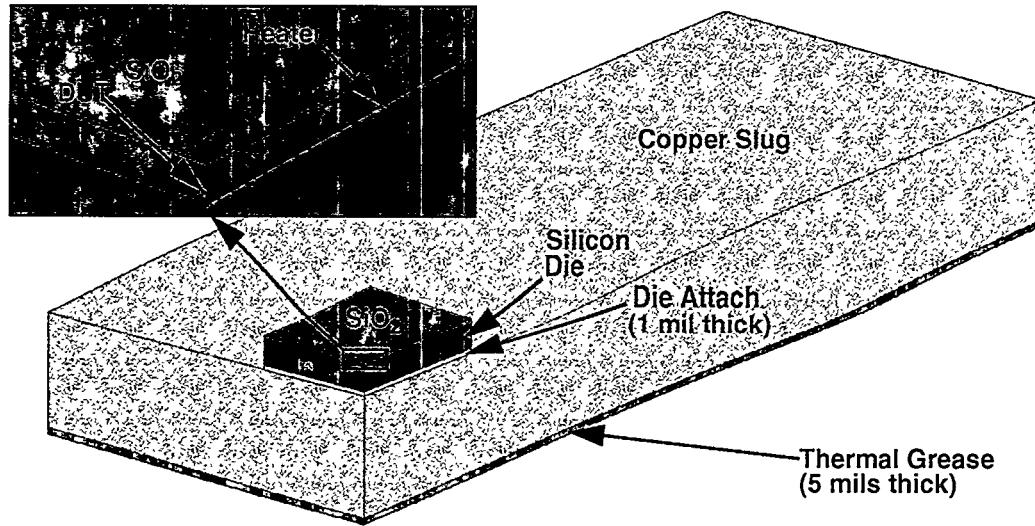

Kovar packages were used on earlier generations of electromigration test die. Kovar is an iron-nickel alloy extensively used in microelectronics packages because its thermal coefficient of expansion is close to that of silicon. The test die was die attached to a copper slug instead of a Kovar package to lower the temperature of the electronics near the powered heater on the test die. The thermal conductivity of copper is an order of magnitude greater than that of Kovar ( $3.9 \text{ W/cm} \cdot ^\circ\text{C}$  vs.  $0.15 \text{ W/cm} \cdot ^\circ\text{C}$  at room temperature) so the copper slug presents a lower thermal resistance for heat conduction out of the test die. This lower thermal resistance causes steeper temperature gradients around the powered heater and consequentially lower temperatures away from the heater on the test die.

FIGURE 4. Packaging of electromigration test die.

The device package used a slug of copper and a modified Kovar package to connect to the test system. A hole was drilled in the Kovar package to allow the top of the copper slug to be accessed for die attach. The copper slug was screwed and epoxied to the Kovar package and the test die was then directly die attached to the copper slug (Figure 4) using a stress reducing adhesive. This adhesive<sup>6</sup> is designed for use above its 80°C glass transition temperature. This minimizes problems with differing thermal coefficients of expansion (TCE) between the copper slug and the silicon die. All tests for this analysis were conducted with the copper slug and the die at temperatures exceeding 100°C to mimic real life test conditions.

Ten die pads were bonded out to the 24 pin kovar package. The device heater required two bonds, the local temperature monitor required four bonds and the additional remote temperature monitor required four bonds. This additional temperature monitor was used to obtain temperature measurements away from expected large thermal gradients in the vicinity of the powered heater. All of the pads were connected to the Kovar package using a wedge bonder with 1 mil aluminum wire.

## 2.2 Calibration of Temperature Monitor Lines

Accurate temperature measurements can be obtained from the temperature monitors if they are first calibrated. Temperature calibration is performed on the temperature controlled stage of an infrared microscope\* over the range of 25°C to 120°C. This method simplified the calibration procedure. An earlier calibration was performed on parts from the same lot using a convection oven and showed a linear correlation between temperature monitor line resistance and temperature from 25°C to 275°C.

A spring loaded test fixture with a friction socket and a copper block to conduct heat was used to thermally mount the packaged part to the microscope stage. The friction socket

\*Infrascope, EDO Barnes Engineering Division, 88 Long Hill Cross Roads, P.O. Box 867, Sheldon CN 06484-0867

FIGURE 5. Mounting of packaged part to infrared microscope stage.

on the test fixture was equipped with interposers to accommodate the modified device package. The microscope stage was coated with thermal grease\* and then the test fixture was screwed to the stage. The copper block provided thermal contact between the temperature controlled stage of the microscope and the bottom of the copper slug of the packaged part. The bottom of the copper slug on the packaged part was also coated with thermal grease and loaded into the top row of interposers (Figure 5).

The two temperature monitors were calibrated prior to initial testing. The local temperature monitor over the powered heater showed an initial decrease in resistance between test runs with the heater powered to 5 W. The local temperature monitor was apparently annealing during testing. This temperature monitor indicated a temperature of 279°C during testing with 5 W of heater power applied. The heater was powered up to 5 W and allowed to run for four hours to anneal the temperature monitor. Figure 6 on page 18 shows the temperature calibration data for both temperature monitors before and after annealing. Linear regression was used to determine the equations of straight lines best representing the data (Figure 6).

The higher temperature of the local temperature monitor caused it to anneal more than the cooler remote temperature monitor. The remote temperature monitor showed almost no change. Measurements of the remote temperature monitor indicate its temperature was 117°C during the 5 W tests. For subsequent testing, the resistances of the two temperature

---

\*Wakefield Engineering 126 Series Thermal Joint Compound

FIGURE 6. Temperature calibration data for temperature monitor lines.

FIGURE 7. Results of long-term annealing on temperature monitor resistances.

monitor lines were recorded after each test at the base microscope stage temperature of 100°C with the device heater unpowered to watch for further annealing. The temperature monitor lines did not appreciably anneal over the remaining tests due to the short time of each test.

A second packaged device was annealed under the same conditions for five days. The results are shown in Figure 7 on page 18. Noise in the remote temperature monitor data caused by the limited resolution of the measurement equipment is apparent during the first four hours of annealing. After 72 hours the error in the temperature measured by the local temperature monitor line is greater than 10°C. The annealing of these lines is a separate problem to be studied and could become a source of error in the electromigration analysis if not addressed in future work.

## 2.3 Infrared Microscope Test Procedure

A photograph of the infrared microscope is shown in Figure 8 on page 20. Temperature plots were obtained from the infrared microscope by using the following procedure. Before testing, the LN2 dewar on the microscope was filled and allowed to cool the microscope focal plane array for at least 30 minutes. A packaged part was then mounted to the temperature controlled stage of the microscope as previously described. Emissivity is measured over the field of view over a range of 100°C to 110°C. Settling times of five minutes were used at each of these temperatures to allow the test die to come to thermal equilibrium with the temperature controlled stage before data were taken. Appendix A (page 51) contains a detailed discussion of how the infrared microscope measures emissivity and temperature. The temperature controlled stage was then set to the base test temperature of 100°C and 5 W of power are applied to the device heater using a computer controlled power supply.

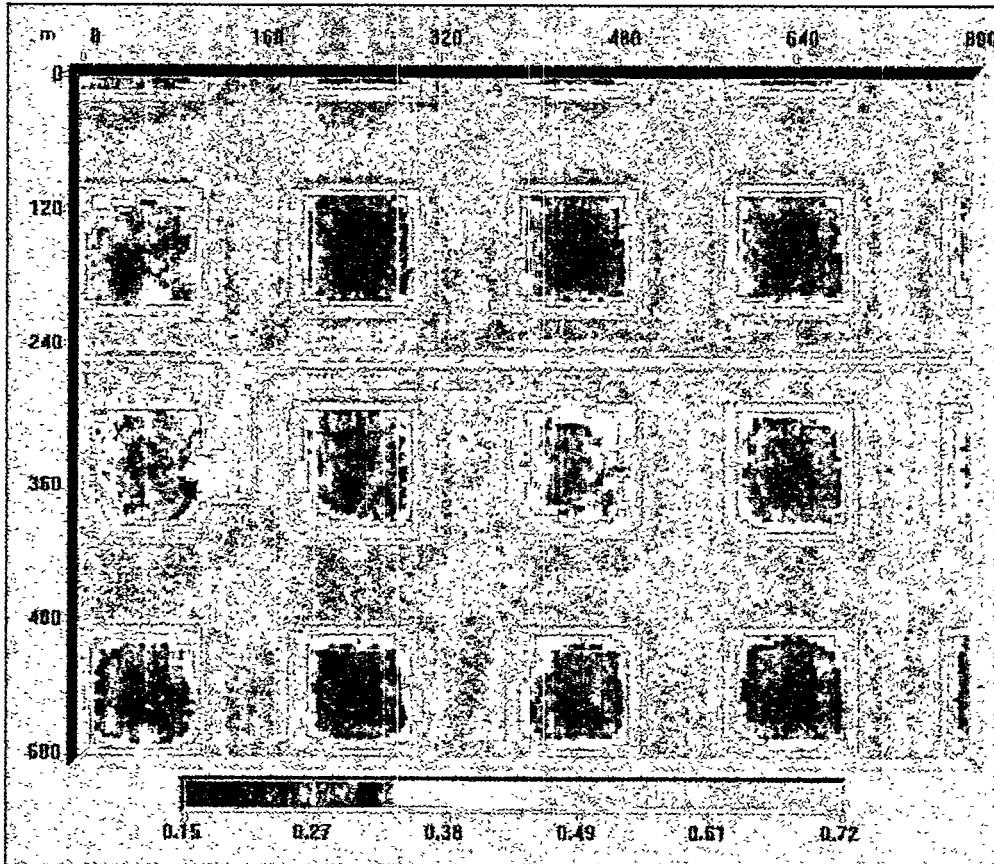

After allowing the device to come to thermal equilibrium, infrared temperature plots were obtained and resistance readings from the two thermometry lines were recorded along with other pertinent test data. Four different tests were run. The first used a 1X lens to get a thermal image of the entire die surface (Figure 9 on page 20). The second and third tests used a 5X lens to get higher resolution over the entire heater length and also to more accurately determine the temperatures at the corner of the die and on the copper slug. The fourth test used a 10X lens and viewed the end of the heater closest to the buffer circuitry. This test was performed to attempt to resolve peak temperatures near the heater. The remaining three temperature plots and a table showing other collected raw data from the tests is included in Appendix B on page 55.

FIGURE 8. Test setup using infrared microscope.

FIGURE 9. Temperature versus test die xy dimension (mm) with 5 W of heater power at 1X magnification.

## 2.4 Results

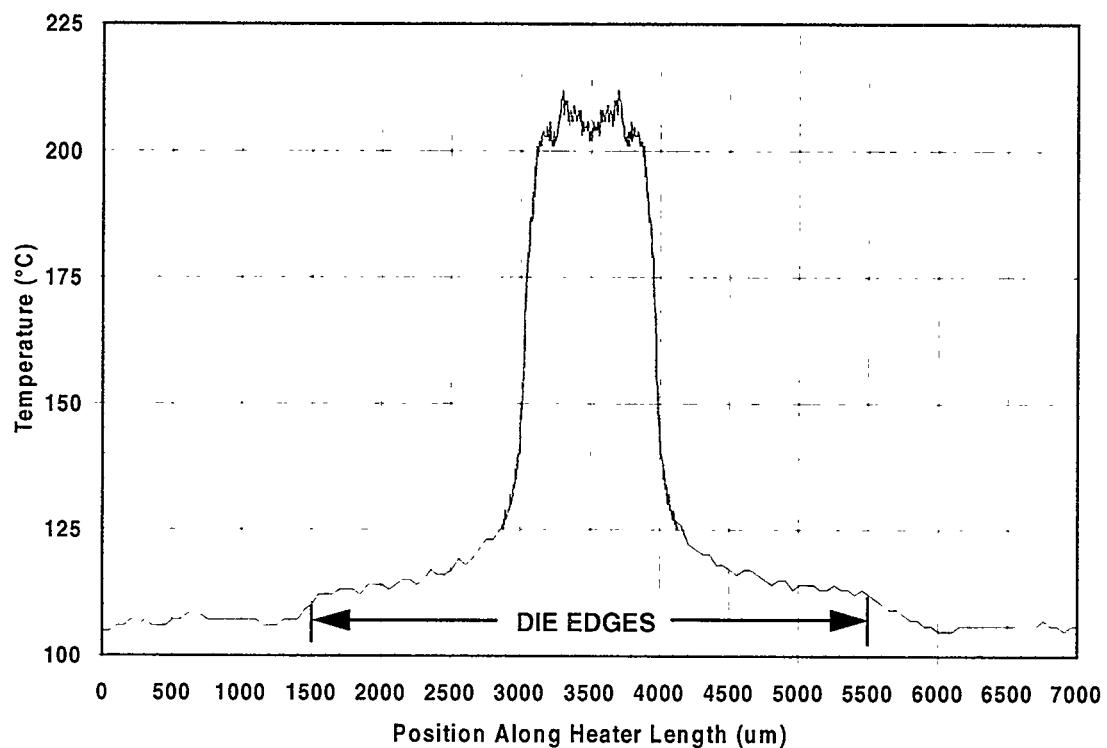

A line plot of surface temperatures recorded with the infrared microscope along the center of the length of the heater is shown in Figure 10 on page 22. This graph was produced by compiling both the 1X and the 10X infrared data sets. Both data sets were used to give an accurate depiction of the peak surface temperature measured by the infrared microscope. The 1X data set shows a peak temperature of only 178°C on the die over the heater due to resolution limitations of the infrared microscope. The central symmetry in the peak temperatures over the heater is caused by the mirroring of the 10X data to produce a 10X resolution data set for the full length of the heater. The heater didn't appear to heat uniformly in any of the temperature plots as indicated by the lower center heater temperatures. This effect appears as temperature variations along the heater length, and is probably due to processing defects within the heater element.

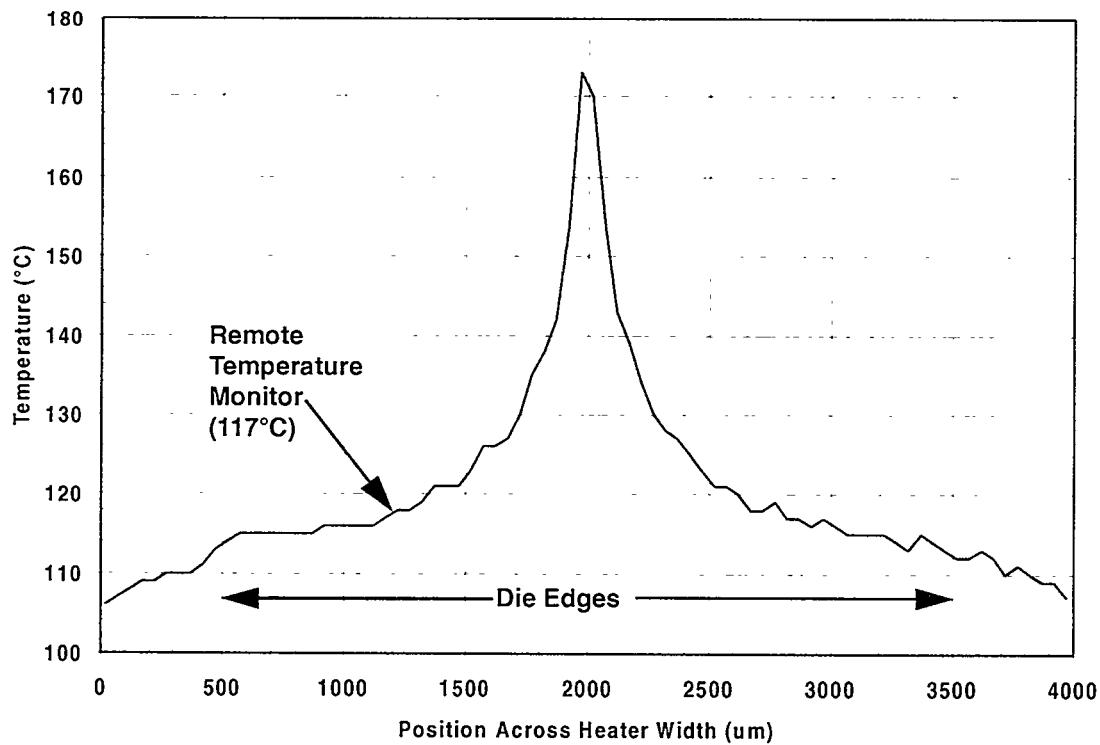

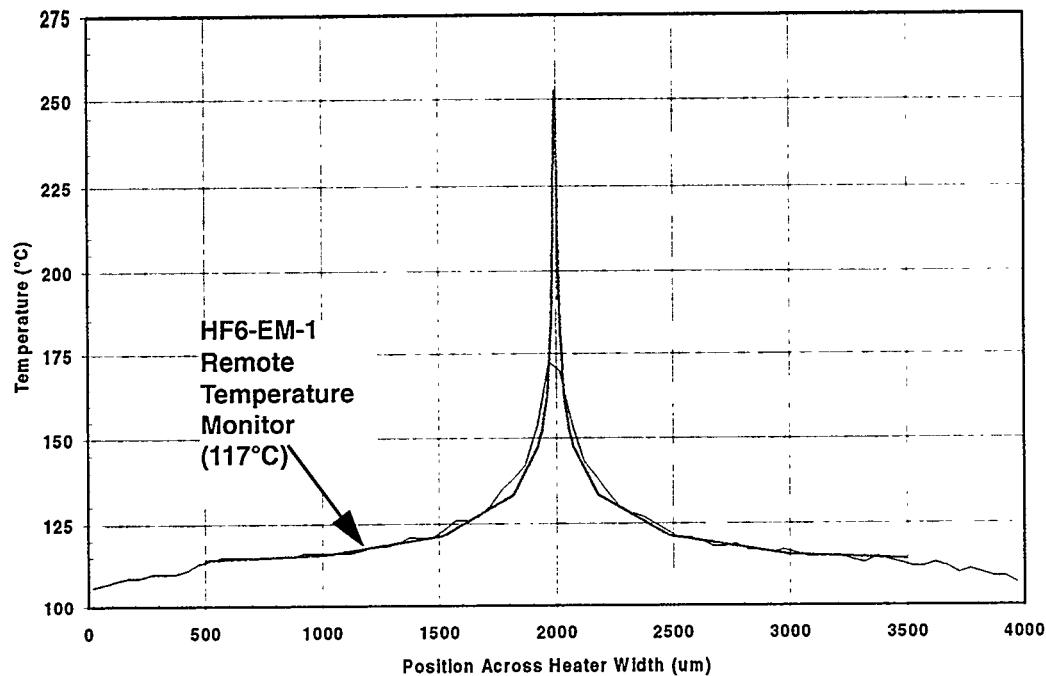

The infrared temperature measurement accuracy across the lower temperature areas of the die surface was checked by comparing the infrared results to the results determined by plotting temperatures across the heater width (Figure 11 on page 22). This plot was produced by taking a row of data from the 1X plot across the geometric centerline of the heater length. The peak temperature was lower than shown in Figure 10 due to the lower resolution of the 1X scale (50  $\mu\text{m}/\text{pixel}$ ). Temperatures across the 15  $\mu\text{m}$  heater were averaged into a 50  $\mu\text{m}$  pixel width at this resolution. The edges of the die are slightly obscured in this chart due to die attach adhesive beading up between the edge of the die and the top surface of the copper slug. This chart shows that the infrared microscope surface temperature over the remote temperature monitor 800  $\mu\text{m}$  from the heater is in agreement within 5 degrees to that indicated by the monitor.

The infrared microscope thermal data in Figure 10 indicate that the peak temperature at the surface over the powered heater is 212°C. This value is questionable because the local temperature monitor indicates an average metal 1 level temperature over the heater of 279°C. The die surface over the heater will be slightly lower than this value as we shall see from the thermal calculations later. The remote temperature monitor was approximately 800  $\mu\text{m}$  from the powered heater and indicates a temperature at the metal 1 level of 117°C. This temperature correlates well with the infrared surface data in this region of the device. The surface temperature near a corner of the die was 112°C as recorded by the infrared microscope and the temperature of the copper slug near this die corner was indicated to be 106°C.

FIGURE 10. Infrared surface temperature data along heater length compiled from 1X and 10X measurements.

FIGURE 11. Infrared surface data across 15  $\mu\text{m}$  heater width and adjacent die surface

## CHAPTER 3: PHYSICAL THERMAL MODEL ELEMENTS

Physical dimensions and properties of all significant thermal elements are required to build an accurate thermal model of the electromigration test device. Information for the thermal grease under the copper slug, the slug, the die attach adhesive, and the die are needed and discussed here.

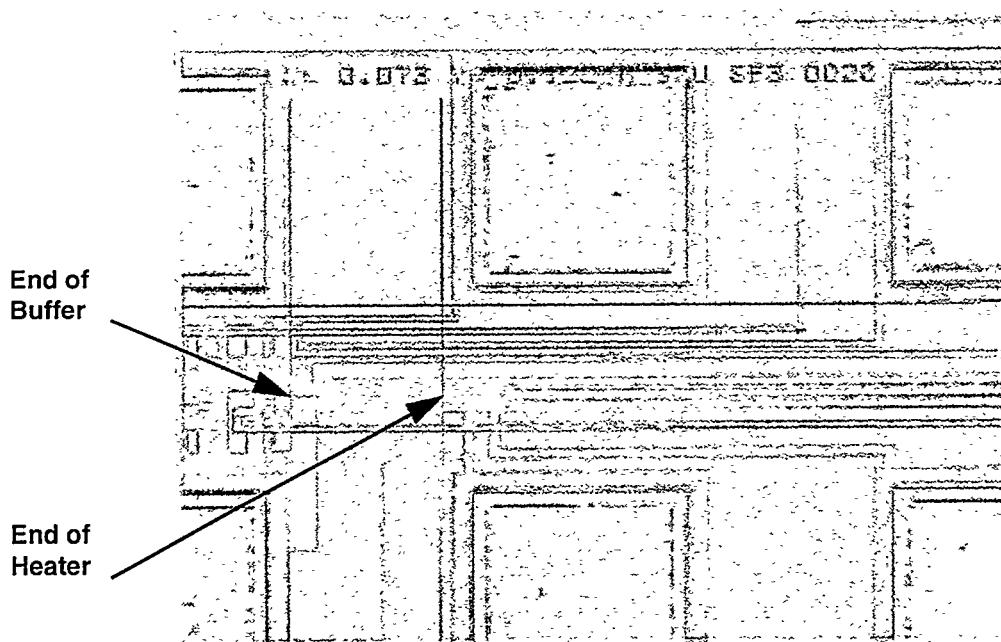

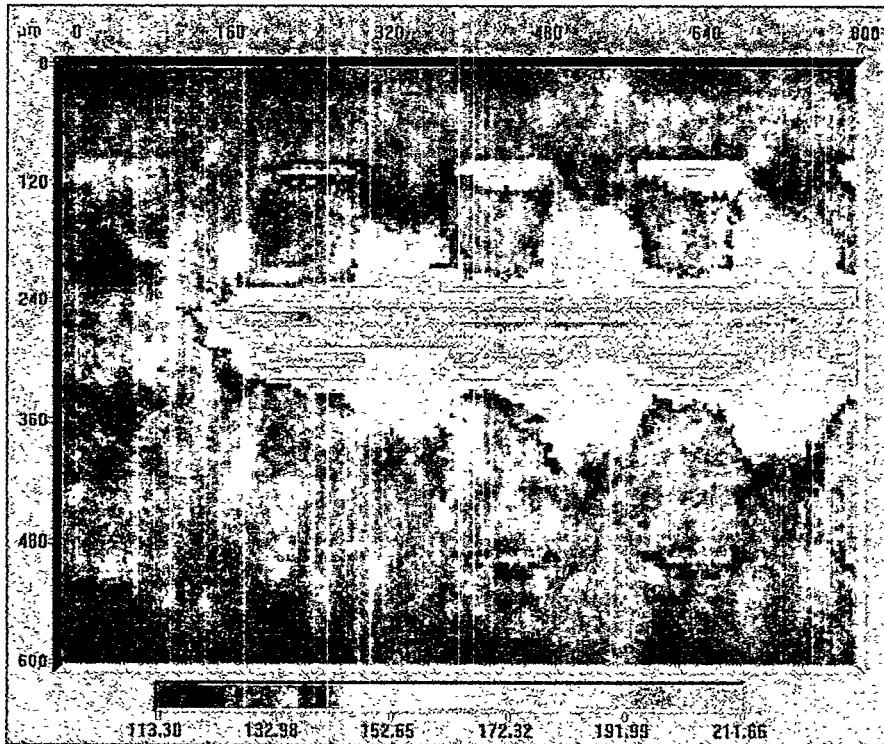

### 3.1 Die Dimensions

Feature sizes greater than 20  $\mu\text{m}$  across the surface of the die were determined using optical microscopy. A microscope equipped with a digital measuring device took the photo shown in Figure 12. The digital display was used to determine the heater length, the DUT and temperature monitor lengths, the distance of the remote temperature sensor from the local temperature sensor, and the distance of the buffer circuitry from the end of the heater.

The thicknesses of the layers of die material were determined by cross sectioning device die and then measuring SEM photos taken of the areas of interest. A SEM photograph of a cross sectioned device is shown in Figure 13 on page 24. This device is a metal 1 electromigration test structure cut across the heater width. Several devices from different areas of a wafer were sectioned across the heater element and then photographed in the SEM at different magnifications. The composition of the layers was not specified by the outside vendor, but was assumed to be  $\text{SiO}_2$  for all of the interlevel dielectrics. The composition of the die passivation layer was also unknown and is assumed to be either  $\text{SiN}$  or  $p$ -glass. This layer was assumed to be similar to  $\text{SiO}_2$  in its thermal characteristics for the model.

FIGURE 12. Optical photo showing distance from buffer electronics to end of heater.

The heater is polysilicon with a layer of platinum silicide on top of it. A SEM photograph of a cross section of the edge of a device is shown in Figure 14 on page 25. A thin layer is visible above the platinum silicide in this photograph. This layer is probably a spin on glass used to conformally coat the previously deposited layers before another oxide layer was deposited on the wafer. Thin layers in the die such as this one are ignored in the thermal model because they are too thin to cause a significant thermal effect and also because it is likely that their thermal properties are similar to the surrounding  $\text{SiO}_2$ .

FIGURE 13. SEM photograph of cross section of electromigration structure.

Most of the heater current goes through the platinum silicide layer and since this is quite thin with respect to the surrounding  $\text{SiO}_2$  layers, the heater will be modeled as a two dimensional surface heating element.

A diagram of the internal die layers to be modeled is constructed from the photographs. This diagram is shown in Figure 15 on page 25. Elements for only the metal 1 devices are illustrated. The metal 2 devices are similar except that the metal lines are 0.8  $\mu\text{m}$  tall instead of 0.5  $\mu\text{m}$ . For the line over line type of device, the metal 1 DUT and the metal 2 temperature monitor elements are centered over the heater width.

FIGURE 14. SEM photograph of heater cross section.

FIGURE 15. Diagram of critical electromigration structure dimensions.

### 3.2 Other Physical Dimensions

The copper slug was measured using a digital caliper and is 0.95 cm wide by 2.54 cm long by 2.54 cm tall.

The die attach adhesive thickness is approximately 1 mil (0.00254 cm) thick. The die is manually attached to the copper slug and substantial variations in die attach thickness are common. The model is later tuned to agree with the measured thermal resistance of this layer.

A 5 mil thickness is assumed for the thermal grease layer between the copper slug and thermal stage. This thickness and thermal resistance in the model also accounts for any additional resistance through the mounting to the temperature controlled chuck.

## CHAPTER 4: STEADY STATE THERMAL MODELING

The infrared microscope provided only limited thermal information about the test die. Surface temperatures near the powered heater have gradients too steep to resolve and internal die temperatures are not measurable through infrared microscopy. This analysis is used to describe temperatures of the DUT and the temperature monitor which are located 8.5  $\mu\text{m}$  below the surface of the die. Of course the infrared system only measures surface temperatures so that internal device temperatures and gradients can be characterized only by producing an accurate thermal model of the device.

### 4.1 Thermal Analysis Software

I constructed thermal models using a PC based thermal analysis package.\* This software supports 3D modeling and allows the use of temperature dependent material properties. Both steady state and transient (time varying) thermal problems may be modeled. This software supports conductive, radiative and convective thermal elements. A complete description of the software package operation and some example problems used to validate the analysis code are given in Appendix C on page 57.

### 4.2 Material Thermal Conductivities

Steady state models require that the software have either a fixed value or a temperature dependent array of thermal conductivities for each material in the model. The software performs a linear interpolation on array data to determine the thermal conductivity of a material at an intermediate temperature. I used a polynomial curve fit to approximate handbook data, and then performed a nonlinear interpolation every 25°C to improve the accuracy of the model solution.

#### 4.2.1 Silicon

A temperature dependent thermal conductivity array is used for the modeled silicon substrate. I used a temperature dependent thermal conductivity for the silicon elements because the silicon thermal conductivity varies greatly over the range of temperatures found in the die substrate. Values are obtained from a standard reference<sup>7</sup> and interpolated using a polynomial curve fit shown in Figure 16 on page 28. These values were placed in a data array for the analysis software.

---

\*TAS (Thermal Analysis System) from Harvard Thermal Inc., Harvard MA

FIGURE 16. Interpolated thermal conductivity of silicon.

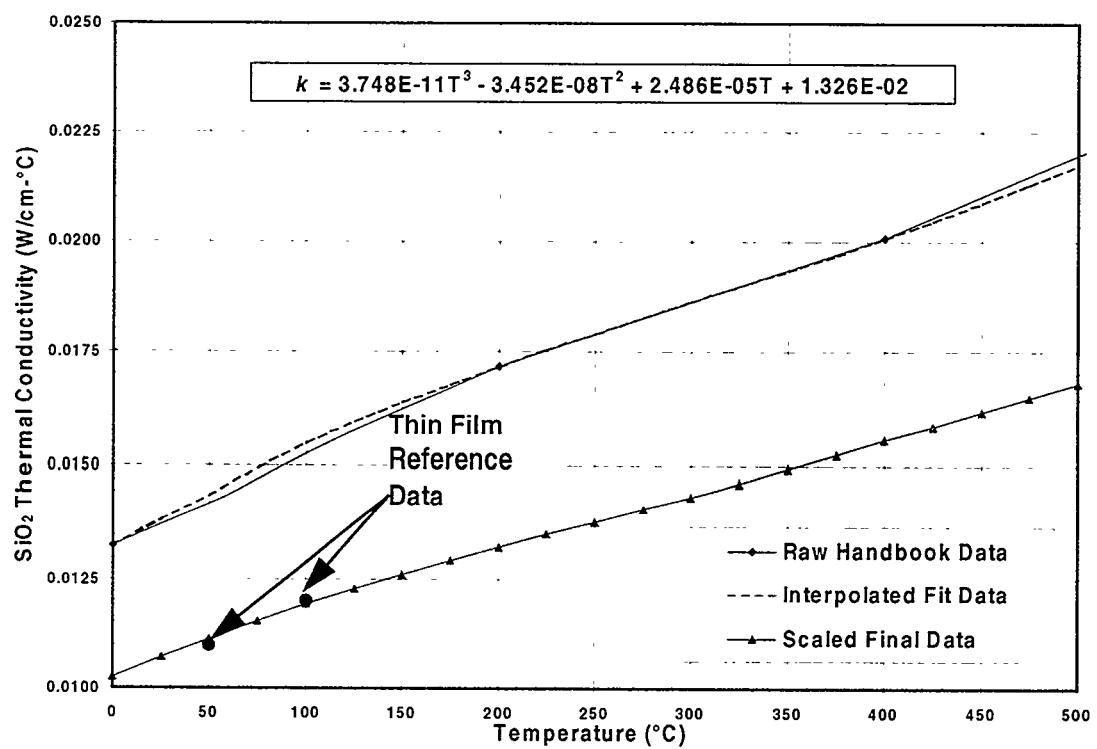

FIGURE 17. Interpolated and scaled SiO<sub>2</sub> thermal conductivity data.

#### 4.2.2 Silicon Dioxide

I also used a temperature dependent thermal conductivity array for the model elements representing  $\text{SiO}_2$  layers in the die. Again I choose an array of values for this thermal conductivity because the  $\text{SiO}_2$  model temperatures span a wide range. The values used were again obtained from a standard handbook<sup>8</sup> and then fit by a polynomial curve to allow interpolation in 25°C increments. A paper on thermal conductivity in thin  $\text{SiO}_2$  films<sup>9</sup> gives lower values than the handbook for the thermal conductivity of bulk  $\text{SiO}_2$  over the temperature range of interest. I scaled the interpolated data values by 77% to agree with the thin film data in this paper since it is based on  $\text{SiO}_2$  as deposited in modern semiconductor fabrication. A plot of the three data sets and several data points from the thin film reference are shown in Figure 17 on page 28.

#### 4.2.3 Thermal Conductivity of Other Materials

Temperature independent thermal conductivities were assumed for the rest of the materials included in the model. I obtained thermal conductivity values for the thermal grease and the die attach adhesive from the manufacturer's data sheets. The manufacturer reports a value of 4 W/m-K or 0.04 W/cm-K for the die attach adhesive. A value of 0.008 W/cm-K was given for the thermal grease. These thermal conductivity values were later tuned to account for thickness variations in these layers. Thermal conductivity values from the TAS software database were used for the copper slug and the aluminum lines. I assumed values for the metal line properties for pure aluminum instead of an aluminum 2% copper alloy. This small amount of copper added to aluminum should only slightly affect the thermal conductivities and has only a weak effect on the model. I used 3.91 W/cm°C for the copper thermal conductivity and 2.37 W/cm°C for the aluminum.

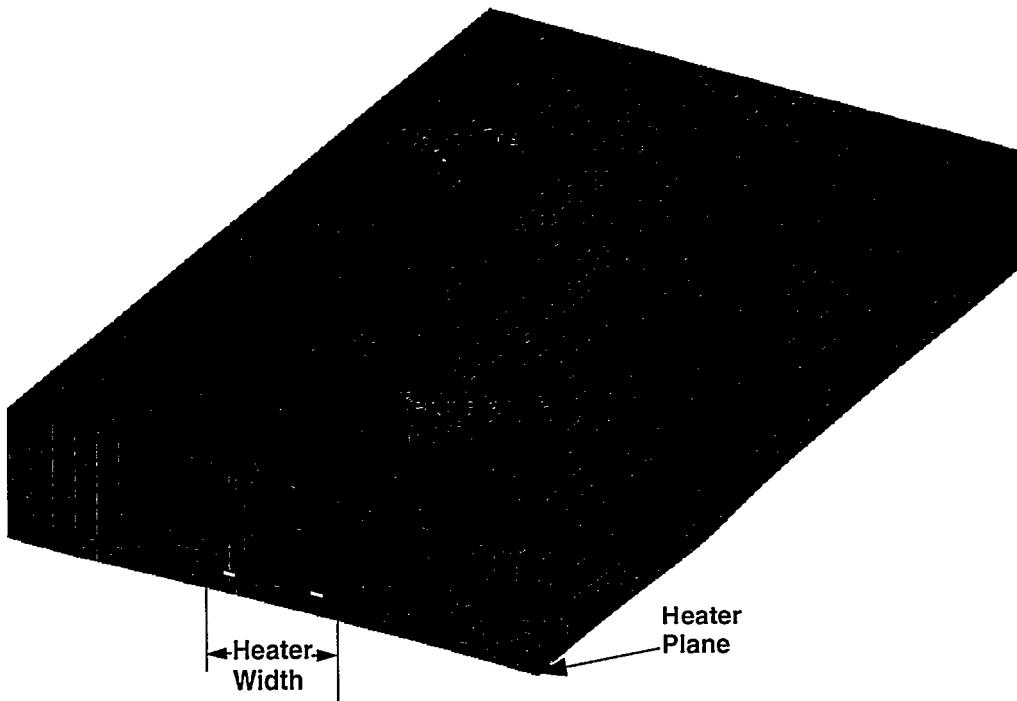

### 4.3 Quarter Section Thermal Model

The first model I produced was a quarter section model of the device. This model included the die, the die attach adhesive, the copper slug and the layer of thermal grease under the copper slug. I used this model to tune the simulation to match thermal resistance values for the thermal grease and the die attach adhesive, and to determine the operating temperature of the nearby electronic buffer circuitry.

A quarter section model was used to minimize the size of the computer model while allowing the highest possible temperature resolution within the device. Since the entire device as modeled was symmetrical about the center of the die top surface, the temperature profile of any quarter section of the device about the center of the die top surface will give the same results. A pictorial diagram of the quarter section model is shown in Figure 18 on page 30. The heater length runs parallel to the long axis of the copper slug. The copper slug is reduced in height in the model from 1.0" to 0.1" to facilitate timely solutions. Since the temperature gradient across the slug from top to bottom is less than 1°C and most of the heat flux spreads in the top 10 percent of the copper slug, this is a valid approximation. Values for the thermal conductivities of both the die attach and the thermal grease were tuned from the measured infrared data at run time. For example, the infrared data indicated a 6°C temperature rise from the copper block to the die corner with 5 W applied to the

FIGURE 18. Quarter section model pictorial diagram.

heater. If there is an assumed 1 mil (0.00254 cm) layer of thermal grease, the calculated thermal conductivity  $k$  is given by Equation 1:

$$k = \frac{q_{Heater} \cdot \Delta X_{DieAttach}}{Area_{Die} \cdot \Delta T} = \frac{5W \cdot 0.00254cm}{(0.3cm \cdot 0.4cm) \cdot 6^\circ C} = 0.0176 \frac{W}{cm \cdot ^\circ C} \quad (1)$$

I used this value in the model to match the measured thermal resistance instead of the 0.04 W/cm $^\circ$ C conductivity specified by the vendor. This difference is due to variations in die attach thickness from the assumed 1 mil and to voids existing in the die attach layer. The thermal grease at the bottom of the copper slug was also tuned at run time to take in account all of the thermal resistance from the top of the temperature controlled microscope stage to the bottom of the copper slug. This resistance included two layers of thermal grease and the copper block in the spring loaded test fixture illustrated in Figure 5 on page 17. The temperatures at the bottom of the copper slug increased to about 105 $^\circ$ C during testing due to this additional thermal resistance. This was 5 $^\circ$ C above the temperature controlled microscope stage set at 100 $^\circ$ C. I used a 5 mil layer of thermal grease with a thermal conductivity of 0.005 W/cm $^\circ$ C to account for this 5 $^\circ$ C temperature difference.

I meshed the model by trial and error to place the densest mesh where the greatest temperature gradients are found. The model temperatures were calculated many times to observe where the greatest thermal gradients were in the model. The shortest distance between nodes was under the heater in the oxide where six 60 nm (0.000006 cm) thick layers represent the thickness of oxide under the heater. The temperature gradient here was 2.37 million  $^\circ$ C/cm! The largest distance between connected adjacent nodes was 0.76525 cm, along the top surface of the copper slug. Here the temperature gradient is only 0.696  $^\circ$ C/cm. These numbers show that the model mesh density varies over five orders of

**FIGURE 19. Fan style meshing of silicon near heater.**

magnitude. The temperature gradients in the model varied over six orders of magnitude. A fan type of meshing is used in the silicon under the heater area to help mesh the model with this extreme variation in node density. The fan style meshing is shown in Figure 19. This allowed a fine mesh under the heater and a coarser mesh in the layers of silicon below. The finished model contains 26,906 nodes representing the corners of 24,360 bricks. Of these bricks, 12,012 represent the oxide on the die since this is where the most dramatic thermal gradients were found. I modeled the heater as an array of surface heating elements in the oxide. This assumes that most of the heater current goes through the platinum silicide layer and rather than the polysilicon part of the heater. The aluminum DUT line was also left out in this first model to further simplify the model meshing.

#### 4.4 Steady State Results

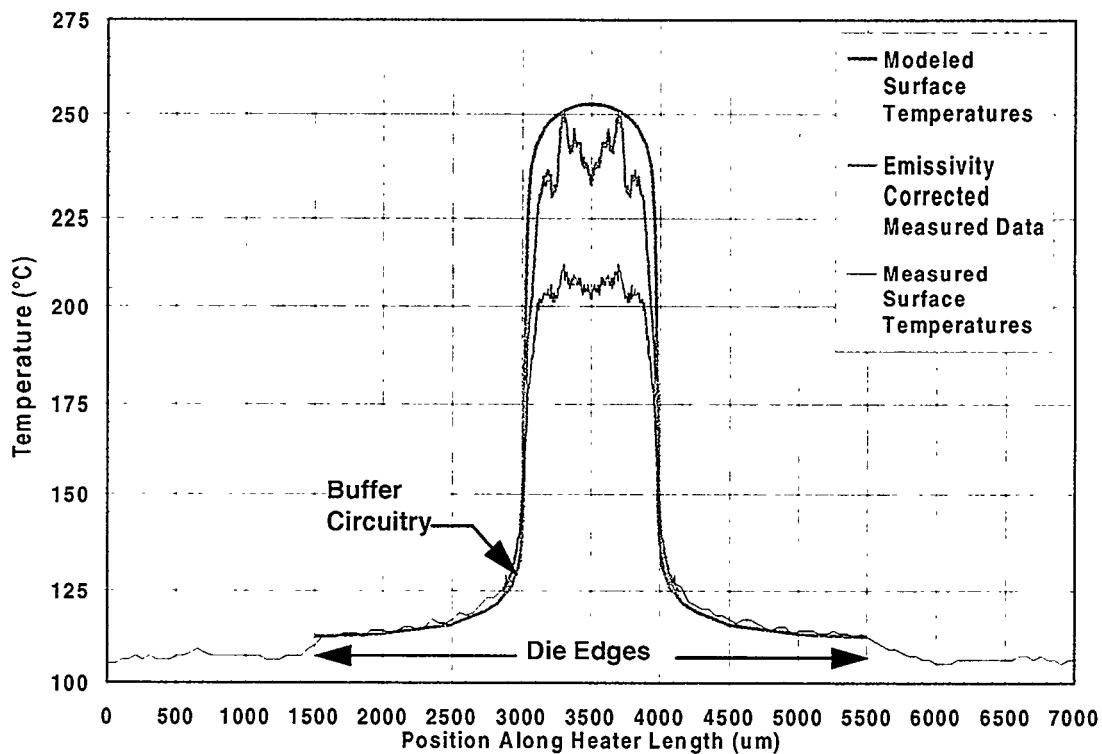

Figure 20 on page 32 compares modeled die surface temperatures along the heater length centered over the heater to measured infrared data. The modeled temperatures agree with the measurements except directly over the heater itself. There are several reasons for this.

1. The infrared microscope is only capable of 5 to 10  $\mu\text{m}$  resolution. Averaging over the modeled curve in 5  $\mu\text{m}$  increments would produce a lower peak temperature.

2. There was some movement of the part during measurement due to expansion during heating. This caused errors in the calculated emissivity of the device.

FIGURE 20. Modeled data along heater length.

3. A  $\pm 5\%$  change in radiance over the device due to system noise was measured between two 100°C radiance scans.

4. The infrared microscope magnifies emissivity errors at temperatures far from where it was originally calibrated.

5. The emissivity of the  $\text{SiO}_2$  decreases with temperature.

This test was performed several times with consistent results. The Emissivity Corrected Measured Data curve in Figure 20 shows the effect of decreasing the device emissivity linearly by 36% over the temperature range from 100°C to 300°C. These data assume an average heater emissivity of 0.47 at 100°C that drops to 0.294 at 300°C.

One goal of this work was to determine the maximum temperature seen by the device electronics. The nearest buffer stage was 75  $\mu\text{m}$  from the end of the heater. Figure 20 shows that the electronics were pulled up by 28.5°C above a 100°C base temperature when the heater was powered at 5 W.

Figure 21 on page 33 shows the surface profile across the center of the width of the heater. This graph again shows as we would expect, that the infrared data do not follow the modeled data at high temperatures. The lower measured peak temperature (<175°C) shows the effect of the limited resolution of the 1X lens on the infrared microscope and the uncertainty in high temperature emissivity. At the lower temperatures of interest, the data agree well. It can be seen that both the modeled data and the infrared data predict that the

temperature at the remote temperature monitor (HF6-EM-1) is 117°C, the same as measured using the resistance of that metal line itself.

FIGURE 21. Modeled surface temperatures across heater width.

Intentionally Left Blank

## CHAPTER 5: SELF HEATING OF DUT

The DUT is powered by a current signal from the buffer circuitry. For this model, I assumed a 50 percent duty cycle unipolar signal with a peak current density of between  $1 \text{ MA/cm}^2$  and  $10 \text{ MA/cm}^2$  powers the DUT. The heater was powered at 5 W, as in the previous section. This part of the modeling was performed to see what thermal effects powering the DUT will have on both its temperature profile and that of the temperature monitor.

### 5.1 Construction of Half Section Model

A view of the center elements of the half section model is shown in Figure 22. To construct this model I reduced the quarter section model to include only elements above the plane of the heater (all  $\text{SiO}_2$ ) and then converted the previously solved heater layer nodes to boundary temperature nodes. The surface heating elements representing the heater were then deleted allowing the boundary nodes to replace these elements. Next I mirrored these elements about a vertical plane through the center of the heater length to produce a half section model of the die oxide area of interest. I then modified the model mesh by adding bricks to represent aluminum for half of the length of the DUT and the temperature monitor. Volume heating elements were then added to the new aluminum DUT elements to simulate the power dissipated in the DUT.

FIGURE 22. Center elements of half section model.

## 5.2 Calculation of Power Densities in DUT Volume Heating Elements

Since volume heating elements were used to simulate the power dissipated in the DUT, the average power density dissipated in the DUT elements must be determined. I calculated both the peak and average power densities dissipated over the DUT volume by first assuming a  $176\ \Omega$  resistance for the entire DUT. This value was extrapolated from the measured temperature monitor line data\* at  $300^\circ\text{C}$ .

The peak current driving the DUT was calculated from the applied peak DUT current density and the cross sectional area of the DUT. Half of the total DUT resistance and the peak current were then used to calculate the peak power dissipated in the modeled half of the DUT. From this the peak volume power density was determined. This calculated power was then halved to give the average power for a 50% duty cycle waveform. The dissipated power was converted to a power density by dividing the power by the volume of the modeled section of the DUT. The half section was created to allow temperature increases on the temperature monitor to be modeled as well as those on the DUT. Table 1 lists the calculated DUT current and power parameters used in this section of the analysis.

---

**Table 1. Current and power parameters for powered DUT.**

| Peak Signal Current Density (MA/cm <sup>2</sup> ) | Peak DUT Current (mA) | Peak Power dissipated in ½ DUT (mW) | Peak DUT Power Density (MW/cm <sup>3</sup> ) | Average Power dissipated in ½ DUT (mW) | Average DUT Power Density (MW/cm <sup>3</sup> ) |

|---------------------------------------------------|-----------------------|-------------------------------------|----------------------------------------------|----------------------------------------|-------------------------------------------------|

| 1.0                                               | 3.50                  | 2.16                                | 7.708                                        | 0.54                                   | 3.854                                           |

| 2.5                                               | 8.75                  | 13.5                                | 48.18                                        | 3.37                                   | 24.09                                           |

| 5.0                                               | 17.5                  | 54.0                                | 192.7                                        | 13.5                                   | 96.36                                           |

| 7.5                                               | 26.3                  | 121                                 | 433.6                                        | 30.4                                   | 216.8                                           |

| 10                                                | 35.0                  | 216                                 | 770.8                                        | 54.0                                   | 385.4                                           |

## 5.3 Effects of DUT Self Heating

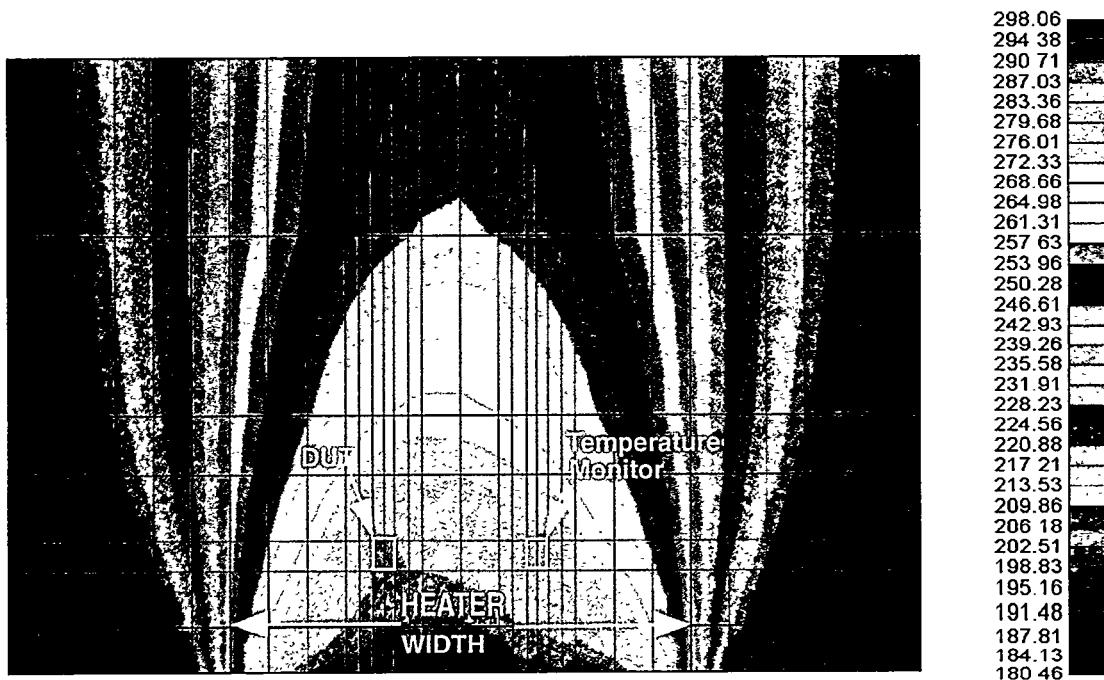

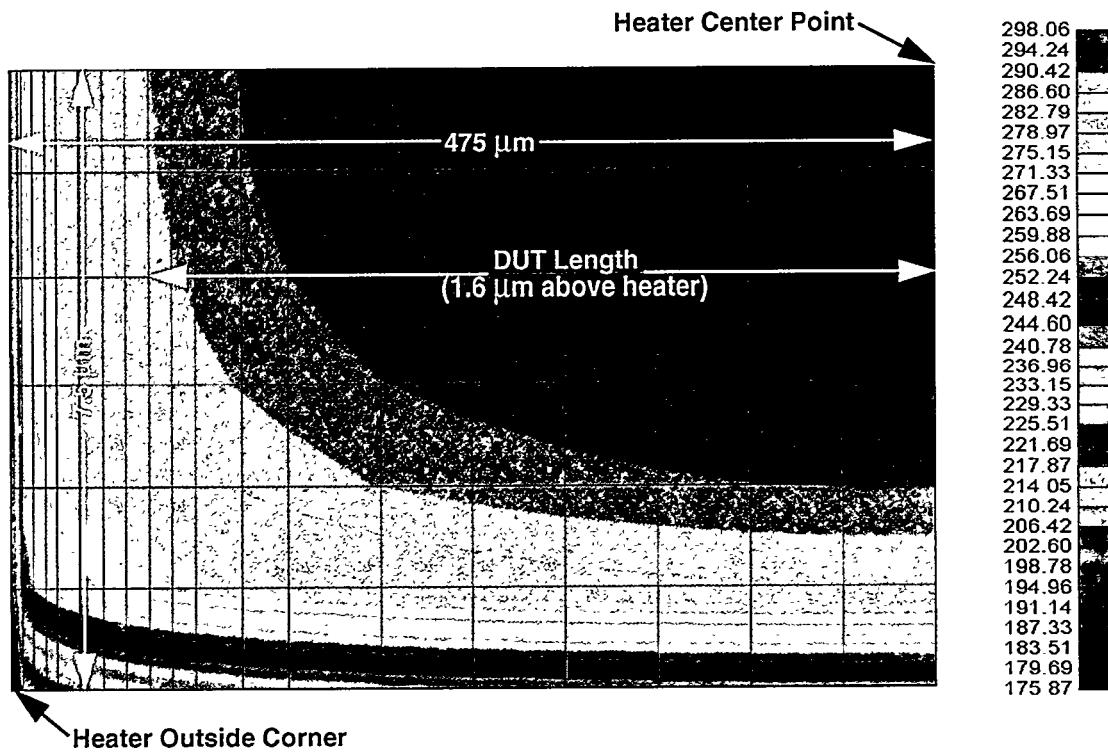

A cross section of the center of the model showing an isotherm map of calculated temperatures with an applied current density of  $5\ \text{MA}/\text{cm}^2$  is shown in Figure 23 on page 37. The center of the DUT is  $287^\circ\text{C}$  and the center of the temperature monitor is  $280^\circ\text{C}$ . It is apparent that the DUT power results in measurable self heating at this current level.

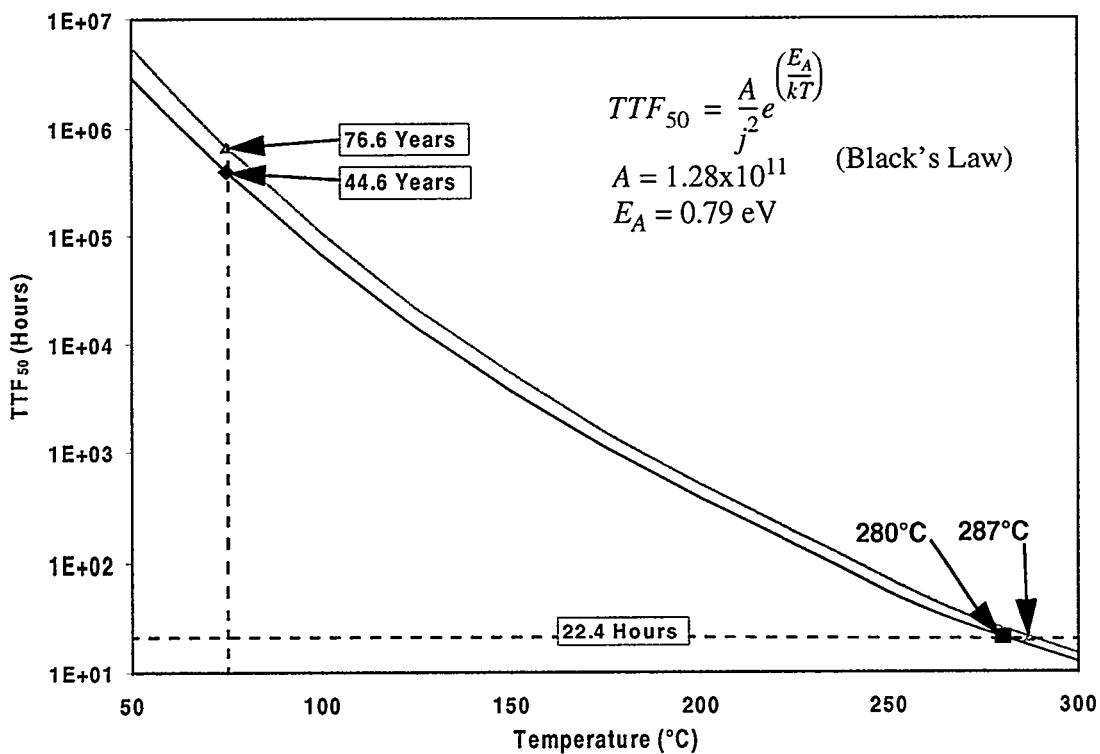

The  $7^\circ\text{C}$  difference in temperature shown in Figure 23 will shift the projected DUT lifetime as shown in Figure 24 on page 37. These curves were produced using Black's Law for a electromigration lifetime ( $TTF_{50}$ ) model assuming an activation energy for grain boundary diffusion in aluminum/copper lines of  $E_A = 0.79\ \text{eV}$ . The  $TTF_{50}$  axis refers to the time to failure for 50 percent of the devices using a failure criteria of a five percent increase in DUT resistance. The constant  $A$  is related to the metal thickness and width and is derived

---

\*See Figure 6 on page 18. The "Post Anneal Local Monitor" data curve was extrapolated.

FIGURE 23. Self heating of DUT at 5 MA/cm<sup>2</sup>.

FIGURE 24. Effect of 7°C temperature error on extrapolated electromigration data.

from measured data.<sup>10</sup> The upper curve shows the result for a DUT temperature of 287°C. The lower curve shows the result of assuming the DUT is at the same temperature as the temperature monitor, 280°C. When extrapolated back to 75°C these data show almost a factor of two error in lifetime. A line expected to last for 44 years at 75°C would last for 76 years due to this error in temperature alone. The temperature rise of the DUT due to self heating is significant and may need to be taken into account when performing accelerated electromigration testing.

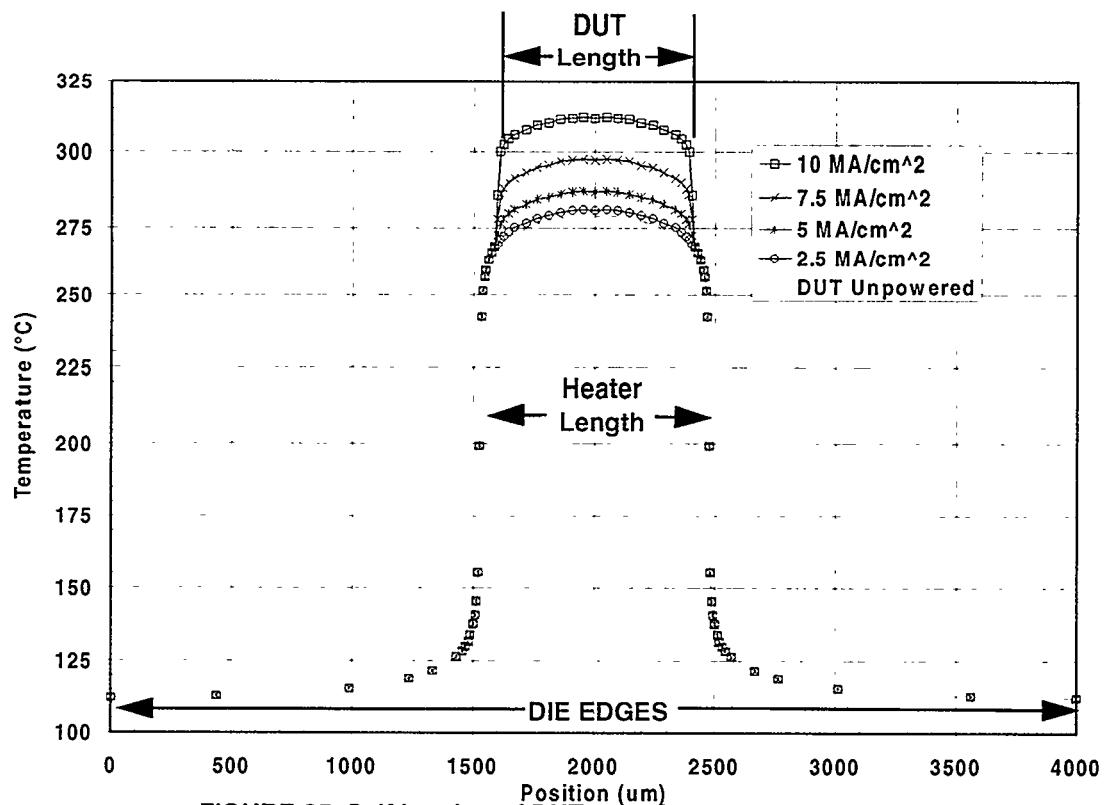

A plot of the average temperature distribution along the length of the DUT lines at several current densities is shown in Figure 25. This plot also shows the distribution of

FIGURE 25. Self heating of DUT at various current densities.

temperatures along the DUT length. Average temperature along the DUT profile for various DUT current densities is shown in Table 2. Self heating of the DUT caused the temperature monitor to be pulled up in temperature by more than 1°C only at current densities greater than 5 MA/cm<sup>2</sup>. The average DUT temperature was raised by more than 1°C at current densities greater than 1.0 MA/cm<sup>2</sup>.

**Table 2. Average DUT and Temperature Monitor (TM) temperatures at various current densities.**

| Current Density (A/cm <sup>2</sup> ) | 0.0E+00 |       | 1.0E+06 |       | 2.5E+06 |       | 5.0E+06 |       | 7.5E+06 |       | 1.0E+07 |       |

|--------------------------------------|---------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|-------|

| Device Element                       | DUT     | TM    |

| Average Temperatures (°C)            | 276.0   | 276.0 | 276.4   | 276.0 | 278.1   | 276.2 | 284.2   | 277.0 | 294.4   | 278.3 | 308.5   | 280.0 |

The average temperature along the monitor in Table 2 with zero DUT power is 3°C lower than the value measured using resistance thermometry of the temperature monitor in Chapter 2. This is due to the addition of the relatively high thermal conductivity aluminum elements that allow increased heat transfer through the SiO<sub>2</sub> along the length of the metal lines.

Intentionally Left Blank

## CHAPTER 6: TRANSIENT HEATING OF DUT

The power applied to the DUT is actually time varying instead of the constant average value as assumed in the previous chapter. Time varying temperature variations along the DUT exist and depend on the frequency, duty cycle, and amplitude of the input power waveform. This chapter characterizes the amplitude of DUT temperature variations as a function of the input signal current and frequency.

I used the half section model previously generated to determine the frequency response of the DUT temperature. Instead of applying an average steady state power to the DUT, the volume heating elements that represent DUT self heating are now represented as time varying arrays of power values. To model the transient response of the DUT it was necessary to include both densities and heat capacities for all the materials used in the model.

### 6.1 Additional Transient Model Thermal Properties

Only aluminum and  $\text{SiO}_2$  elements are used in the half section model. Default values from the TAS software database for both the densities and the heat capacities of these materials are used and shown in Table 3. The software used these values to calculate effective thermal capacitances between adjacent nodes.

---

**Table 3. Additional property values for aluminum and  $\text{SiO}_2$ .**

| Material       | Density (g/cm <sup>3</sup> ) | Heat Capacity (J/g-°C) |

|----------------|------------------------------|------------------------|

| Aluminum       | 0.0432                       | 0.9003                 |

| $\text{SiO}_2$ | 2.200                        | 7.448                  |

---

### 6.2 Results

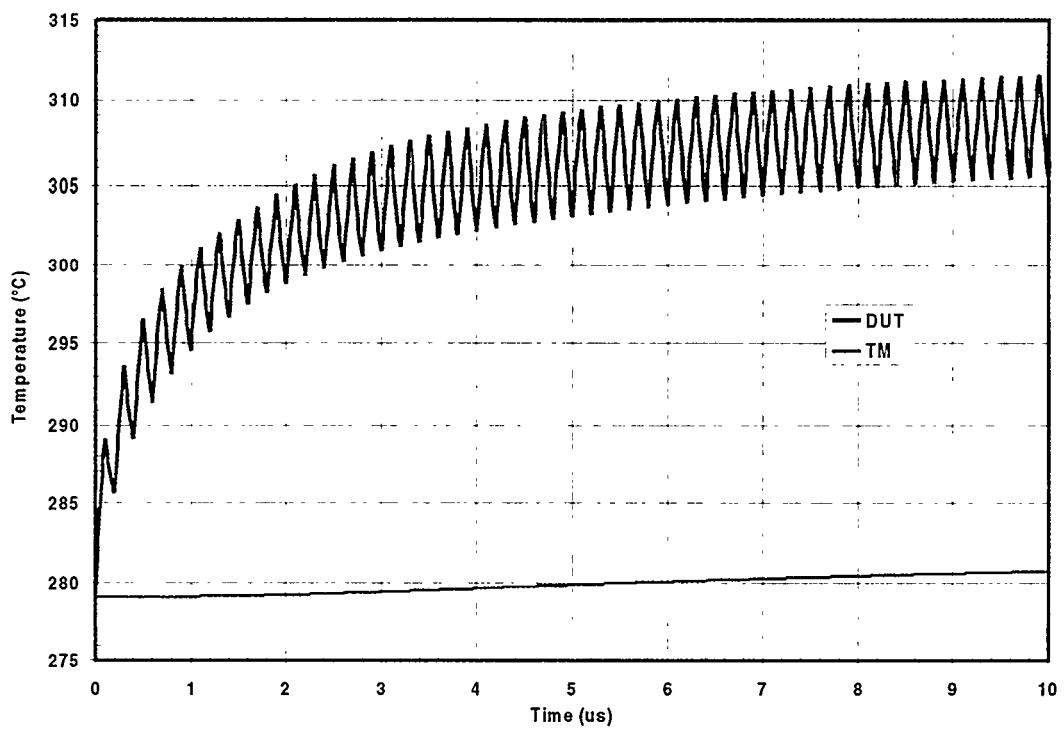

Figure 26 on page 42 shows the transient temperature of the DUT and temperature monitor at center nodes along their lengths when a 50% duty cycle, 5 MHz waveform with a peak current of  $5\text{MA}/\text{cm}^2$  was applied to the DUT. This graph indicates that both the DUT and the temperature monitor were effected by the self heating of the DUT, but that the transient effects of heating are only seen by the DUT at this frequency.

This graph never reaches a condition where the average DUT and temperature monitor temperatures are constant. The software calculated the temperature at every node in the model for each time step. The size of the calculation time step was determined by the software from the minimum distance between nodes and the material properties. The transient simulations used a time step on the order of  $4 \times 10^{-10}$  seconds. This made the transient simulation process quite slow. I chose to write out values to a hard drive during this simulation every  $0.02\ \mu\text{s}$  to give ten datum for each power cycle plotted. All node temperatures in the model are written to a disk every  $0.02\ \mu\text{s}$  of simulation time generating large data files.

FIGURE 26. Transient response of DUT at 5 MHz.

FIGURE 27. Thermal rise and fall characteristics of DUT.

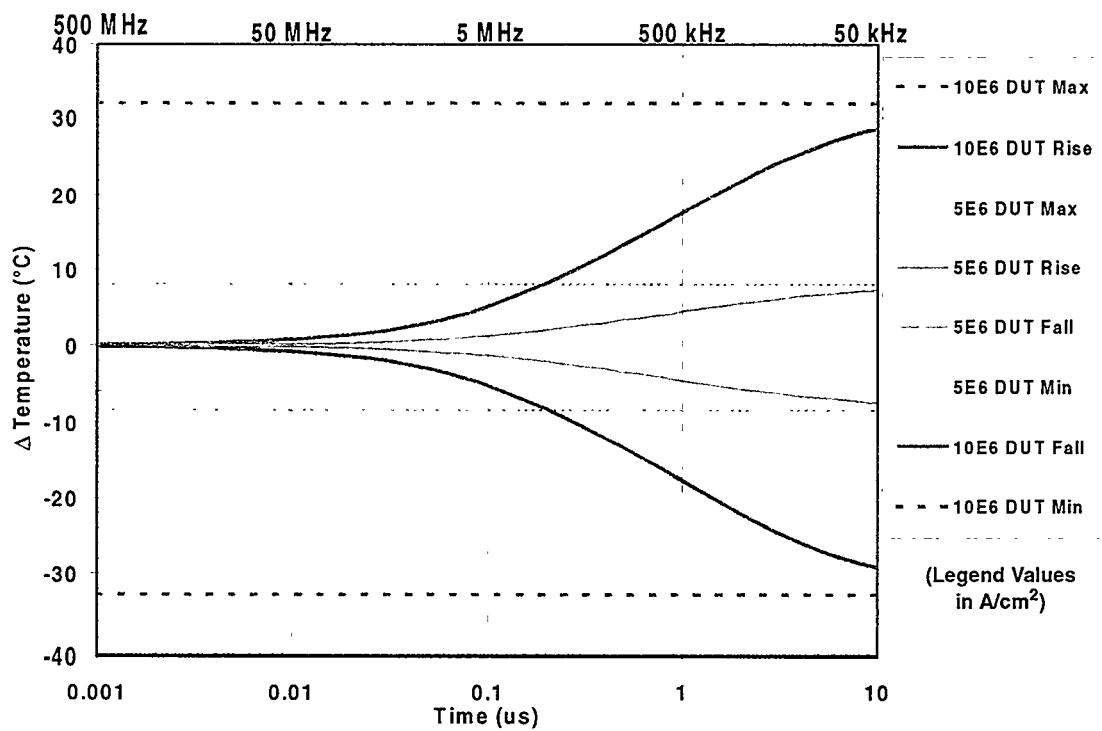

The transient response of the DUT was more efficiently generated by plotting only the rising and falling characteristics of the response at different power levels. Figure 27 on page 42 shows transient responses from steady state conditions including the effect of DUT self heating. Four curves were graphed for each of the two power levels shown in Figure 27. The maximum and minimum power levels were obtained from steady state self heating models with the DUT either fully powered or not powered. The transient characteristics were obtained by first solving a steady state self heating model to define the average temperatures throughout the model for a given average DUT power level. The DUT power level was doubled to its peak value at time zero to produce the rise time transient responses. The DUT power was set to zero at time zero to generate the fall time characteristics. Ten temperature data sets were collected for every time decade. The average temperature of the DUT was then subtracted from the data to produce a differential temperature graph. The frequencies at the top of this chart assume a 50% duty cycle waveform. For example, a 5 MHz square signal will rise for 0.1  $\mu$ s and fall for 0.1  $\mu$ s. A current density of 10 MA/cm<sup>2</sup> showed that the amplitude of the thermal transient on the DUT will be  $\pm 5^{\circ}\text{C}$  about the average DUT temperature. This gave a peak to peak amplitude of about 10°C for the thermal transient.

Rise and fall times were calculated from the data in Figure 27. The 5 MA/cm<sup>2</sup> peak current signal gave a rise time of 10.48  $\mu$ s and a fall time of 10.58  $\mu$ s. The larger 10 MA/cm<sup>2</sup> peak current signal showed rise and fall times of 10.22  $\mu$ s and 10.60  $\mu$ s respectively. The rise time is faster than the fall time for a given signal power level since the thermal conductivity of SiO<sub>2</sub> increases with temperature.

The data in Figure 27 shows that the transient response of the DUT is fairly symmetrical about the average DUT temperature. At a current density of 5 MA/cm<sup>2</sup>, the DUT temperature displayed a peak to peak temperature variation of less than 1°C at frequencies above 50 MHz. For the 10 MA/cm<sup>2</sup> response, the frequency must be doubled to 100 MHz to have the DUT temperature deviate by less than 1°C.

Intentionally Left Blank

## CHAPTER 7: CONCLUSIONS

There are too many combinations of heater power levels, device base temperatures, and DUT signals to completely characterize this device by directly measuring its temperature response. Rather, simulation tools that allow for further analysis of specific test conditions have been produced and their use demonstrated. This tool development provided an understanding of the device heating and the temperature effects on its operation. This chapter examines some of the issues that could result in enhanced test structure performance.

### 7.1 Annealing of the Temperature Monitor Element

Since annealing was observed in these elements over the course of a short test, I recommend for long term testing that the power to the DUT and the heater be switched off at regular intervals and a new temperature monitor calibration point at a known temperature be determined. Since only the y-intercept of the calibration data changed and not the slope of the data, this should be sufficient to prevent large temperature drift errors due to annealing.

### 7.2 Heating of Nearby Electronics

The temperature of the nearby buffer circuitry was determined to be 28.5°C above the 100°C base temperature of the device when the device heater was powered to 5 W. If the device heater is powered to a higher level during actual use to accelerate the rate of DUT electromigration, then this will raise the temperature of the electronics. The most direct way to reduce the temperature of the buffer electronics would be to move them further from the end of the heater or to reduce the heat sink temperature. If the distance between the end of the heater and the buffer electronics were increased from 75  $\mu$ m to 200  $\mu$ m, then the electronics would be 21.6°C hotter than the base temperature.

Table 4 on page 46 shows the effect of model variations on the temperatures of the metal 1 layer over the heater center and the end of the buffer electronics. The buffer electronics temperature was taken at the metal 1 level in the die and at that location the heater the vertical temperature drop to the die surface was less than 0.1°C in all cases. The Normalized Average Gradient column shows the average temperature gradient between the two points normalized to the original model conditions. I varied the base temperature of the device, the thickness of the oxide layer under the heater, the thermal conductivity of the die attach, and the power applied to the heater. The rows with higher Normalized Average Gradients show where the greatest temperature difference between the peak metal 1 and the buffer electronics temperatures occurred.

---

**Table 4. Variations in quarter section model temperatures.**

| Quarter Section Model Variation     | Peak Metal 1 Temperature (°C) | Buffer Electronics Temperature (°C) | Normalized Average Gradient |

|-------------------------------------|-------------------------------|-------------------------------------|-----------------------------|

| Base Case Calculation               | 284.7                         | 128.5                               | 1.000                       |

| 80°C Heat Sink Model Temperature    | 260.4                         | 107.5                               | 0.979                       |

| 120°C Heat Sink Model Temperature   | 309.0                         | 149.5                               | 1.044                       |

| 2X Die Attach Thermal Conductivity  | 280.7                         | 125.1                               | 0.996                       |

| Thinned Die (20 mil Si Substrate)   | 285.7                         | 128.6                               | 1.006                       |

| 300 nm Heater Oxide                 | 272.5                         | 128.5                               | 0.922                       |

| 600 nm Heater Oxide                 | 331.7                         | 128.5                               | 1.301                       |

| 2.5 W Heater Power                  | 191.1                         | 114.0                               | 0.494                       |

| 7.5 W Heater Power                  | 382.0                         | 143.4                               | 1.528                       |

| 7.5 W Heater Power / 80°C Heat Sink | 352.9                         | 120.0                               | 1.491                       |

Decreasing the device base temperature caused the thermal conductivity of the  $\text{SiO}_2$  to decrease slightly and allowed less heat flux directly to the substrate instead of out towards the electronics. Unfortunately this also decreased the peak temperature directly. Doubling the thermal conductivity of the die attach actually lowered the temperature gradient for the same reason as above. This shows that the die is large enough to allow heat flow through the die attach with minimal impedance. Thinning the die from 30 mils to 20 mils increased the temperature gradient due to minimization of the heat flux spreading distance in the silicon substrate. Increasing the thickness of the heater oxide to 600 nm from 360 nm insulated the heater from the substrate and allowed it to more effectively heat the area above it while not effecting the buffer electronics temperature. The 2.5 W and the 7.5 W heater power cases show that the temperature gradient is almost linearly related to heater power. The final case of 7.5 W and an 80°C base temperature shows the best way to run the device to keep the electronics cool is to lower the base temperature and boost the heater power.