2-13-78

J. H. Distr

Special

---

# Recommendations for **CAMAC\*** Serial Highway Drivers and LAM Graders for the **SCC-L2 Serial Crate Controller**

---

Adopted by

U.S. NIM Committee

(Nuclear Instrumentation Methods)

and ESONE Committee of European Laboratories

(European Standards on Nuclear Electronics)

---

January 1978

U.S. Department of Energy

Assistant Secretary for Environment

Division of Biomedical and Environmental Research

MASTER

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

---

# **Recommendations for CAMAC\* Serial Highway Drivers and LAM Graders for the SCC-L2 Serial Crate Controller**

---

**Adopted by

U.S. NIM Committee

(Nuclear Instrumentation Methods)

and ESONE Committee of European Laboratories

(European Standards on Nuclear Electronics)**

---

**January 1978**

**NOTICE**

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

**U.S. Department of Energy**

Assistant Secretary for Environment

Division of Biomedical and Environmental Research

Washington, D.C. 20545

## NOTICE

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

RECOMMENDATIONS FOR CAMAC SERIAL HIGHWAY DRIVERS

and

LAM GRADERS FOR THE SCC-L2

Prepared by:

ESONE Committee of European Laboratories

and

NIM Committee of U.S. Department of Energy

ABSTRACT and FOREWORD

This document describes the functional requirements of Drivers for the CAMAC Serial Highway defined in IEEE Standard 595-1976. The description is independent of the implementation, and in particular no assumption is made about the boundary between hardware and software within the Driver.

Topics covered are the user interface, the supporting system services required, demand handling, and a detailed discussion of the message analysis for various levels of error recovery. An appendix describes the recommended features of LAM Graders for use with the Serial Crate Controller Type L2 of IEEE Std 595-1976.

The ESONE Document corresponding to IEEE Std 595-1976 (to which this document is supplemental) is EUR 6100e. The basic CAMAC Specifications are defined in IEEE Std 583-1975 and the corresponding ESONE publication, EUR 4100e (1972).

The ESONE document corresponding to this report is ESONE/SD/02

Key Words

Data Transmission

Electronic Equipment

Computers

CAMAC

Drivers

Data Processing

Interfaces

Standards

---

# CAMAC SPECIFICATIONS AND REPORTS

| Title                                                                           | IEEE Std No.                                     | IEC No. | DOE No.                                   | EURATOM (EUR) No. or ESONE No. |

|---------------------------------------------------------------------------------|--------------------------------------------------|---------|-------------------------------------------|--------------------------------|

| Modular Instrumentation and Digital Interface System (CAMAC)                    | 583-1975*†                                       | 516     | **                                        | EUR 4100e                      |

| Serial Highway Interface System (CAMAC)                                         | 595-1976                                         | ††      | **                                        | EUR 6100e                      |

| Parallel Highway Interface System (CAMAC)                                       | 596-1976*                                        | 552     | **                                        | EUR 4600e                      |

| Block Transfers in CAMAC Systems                                                | 683-1976                                         | ††      | **                                        | EUR 4100 suppl                 |

| CAMAC Instrumentation and Interface Standards***                                | SH06437***<br>(Library of Congress No. 76-39660) | -       | -                                         | -                              |

| Amplitude Analogue Signals within a 50Ω System                                  | -                                                | -       | TID-26614                                 | EUR 5100e                      |

| The Definition of IML A Language for use in CAMAC Systems                       | -                                                | -       | TID-26615                                 | ESONE/IML/01                   |

| Multiple Controllers in a CAMAC Crate                                           | -                                                | -       | DOE/EV-0007<br>(Announced as TID-26617††) | EUR 6500ett                    |

| CAMAC Tutorial Articles                                                         | -                                                | -       | TID-26618                                 | -                              |

| Real-Time BASIC for CAMAC                                                       | -                                                | -       | TID-26619                                 | ESONE/RTB/02                   |

| Recommendations for CAMAC Serial Highway Drivers and LAM Graders for the SCC-L2 | -                                                | -       | DOE/EV-0006<br>(Announced as TID-27675)   | ESONE/SD/02                    |

\*Includes supplementary information

\*\*Superseded by corresponding IEEE Standard listed.

\*\*\*This is a hard cover book that contains IEEE Stds 583-1975, 595-1976, 506-1976 and 683-1976 plus introductory material

†Also American National Standard ANSI/IEEE 583-1975

††In preparation

## AVAILABILITY OF DOCUMENTS

|                      |                                                                                                             |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| IEEE                 | - IEEE Service Center, 445 Hoes Lane, Piscataway, New Jersey 08854, U.S.A.                                  |

| IEC                  | - International Electrotechnical Commission, 1, rue de Varembe, CH-1211 Geneva 20, Switzerland              |

| DOE<br>(TID-Reports) | - National Bureau of Standards, Washington, D.C. 20234, U.S.A., Attn: L. Costrell                           |

| EURATOM              | - Office of Official Publications of the European Communities, P. O. Box 1003, Luxembourg                   |

| ESONE                | - Commission of the European Communities, CGR-BCMN, B-2440 GEEL, Belgium, Attn: ESONE Secretariat, H. Meyer |

CONTENTS

Page No.

CAMAC SERIAL HIGHWAY DRIVERS

|                                                              | Page No. |

|--------------------------------------------------------------|----------|

| 1. Introduction . . . . .                                    | 4        |

| 2. The Serial driver . . . . .                               | 4        |

| 3. Messages . . . . .                                        | 5        |

| 4. Message Types . . . . .                                   | 6        |

| 4.1 Demand . . . . .                                         | 6        |

| 4.2 Reply without Read Data field . . . . .                  | 6        |

| 4.3 Reply with Read Data field . . . . .                     | 6        |

| 4.4 Error Reply . . . . .                                    | 6        |

| 4.5 Complete Command . . . . .                               | 6        |

| 4.6 Truncated Command . . . . .                              | 7        |

| 4.7 Undefined message . . . . .                              | 7        |

| 5. Organisation of Command/Reply Transactions . . . . .      | 7        |

| 5.1 Single Command/Reply Transactions . . . . .              | 7        |

| 5.2 Bursts of Command/Reply Transactions . . . . .           | 8        |

| 5.3 Error Recovery . . . . .                                 | 8        |

| 6. Block Diagram of the Serial Driver . . . . .              | 9        |

| 7. SD Command Handler and Transmitter . . . . .              | 10       |

| 8. Message Analysis, Summary and First Stage . . . . .       | 10       |

| 8.1 Summary. . . . .                                         | 11       |

| 8.2 First Stage of Analysis . . . . .                        | 12       |

| 9. Second Stage of Message Analysis . . . . .                | 13       |

| 9.1 Single CMD/RPY Transactions, basic analysis . . . . .    | 13       |

| 9.1.1 Criteria . . . . .                                     | 14       |

| 9.1.2 Decisions . . . . .                                    | 14       |

| 9.2 Single CMD/RPY Transactions, extended analysis . . . . . | 16       |

| 9.2.1 Criteria . . . . .                                     | 17       |

| 9.2.2 Decisions . . . . .                                    | 18       |

| 9.3 Bursts of Transactions . . . . .                         | 20       |

| 9.3.1 Criteria . . . . .                                     | 20       |

| 9.3.2 Decisions . . . . .                                    | 20       |

|                                                                                        | CONTENTS (Continued) | Page No. |

|----------------------------------------------------------------------------------------|----------------------|----------|

| 10. Demand Handler . . . . .                                                           | 21                   |          |

| 10.1 Identification of the source of a Demand . . . . .                                | 22                   |          |

| 10.2 System response to a Demand . . . . .                                             | 22                   |          |

| 10.3 Demand dispatching to the corresponding user program .                            | 23                   |          |

| 10.4 Re-enabling Demand message Initiation . . . . .                                   | 24                   |          |

| 10.5 Connection/Disconnection between a LAM and an Interrupt Service routine . . . . . | 24                   |          |

| 10.6 Explanation of the Flow Charts, Figs. 11a to 11c . . .                            | 24                   |          |

| 10.7 Hung Demand . . . . .                                                             | 25                   |          |

| 10.8 Recovery of lost Demand messages . . . . .                                        | 26                   |          |

| 11. System Services . . . . .                                                          | 29                   |          |

| 12. User Interface . . . . .                                                           | 30                   |          |

| 12.1 Declaration facilities . . . . .                                                  | 30                   |          |

| 12.2 User Requests . . . . .                                                           | 31                   |          |

| 13. System Initialisation . . . . .                                                    | 31                   |          |

| 13.1 Initialisation from a cold start . . . . .                                        | 32                   |          |

| 13.2 Request for Initialisation . . . . .                                              | 32                   |          |

| 14. Interaction between Serial Driver Tasks . . . . .                                  | 33                   |          |

#### ILLUSTRATIONS

|                                                                                      |    |

|--------------------------------------------------------------------------------------|----|

| Fig. 1: Serial Highway Message Types . . . . .                                       | 35 |

| Fig. 2: Block Diagram of a Serial Driver . . . . .                                   | 36 |

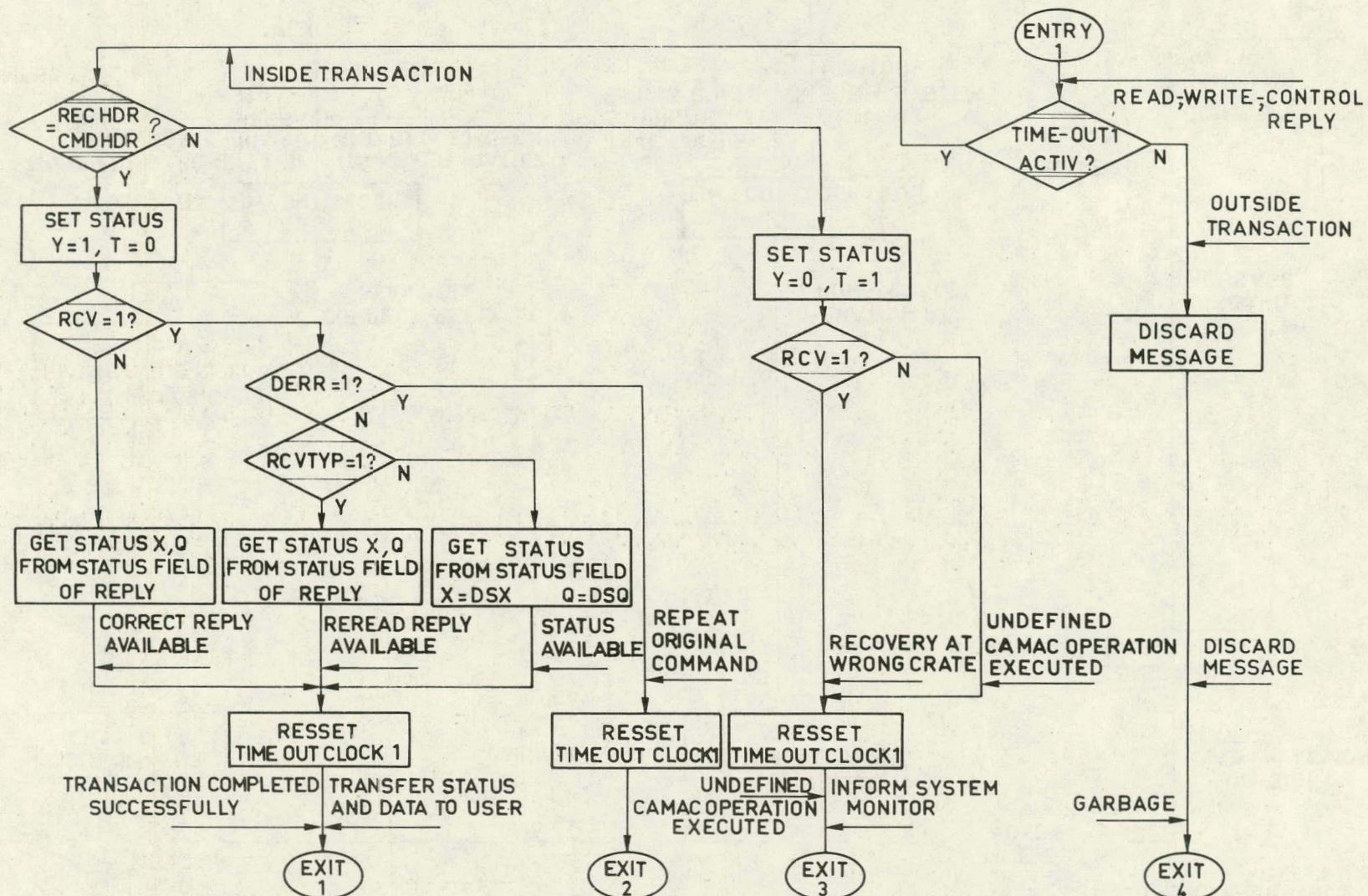

| Fig. 3a: Message Analysis for Single Command/Reply Transactions (Basic) . . . . .    | 37 |

| Fig. 3b: Message Analysis for Single Command/Reply Transactions (Extended) . . . . . | 38 |

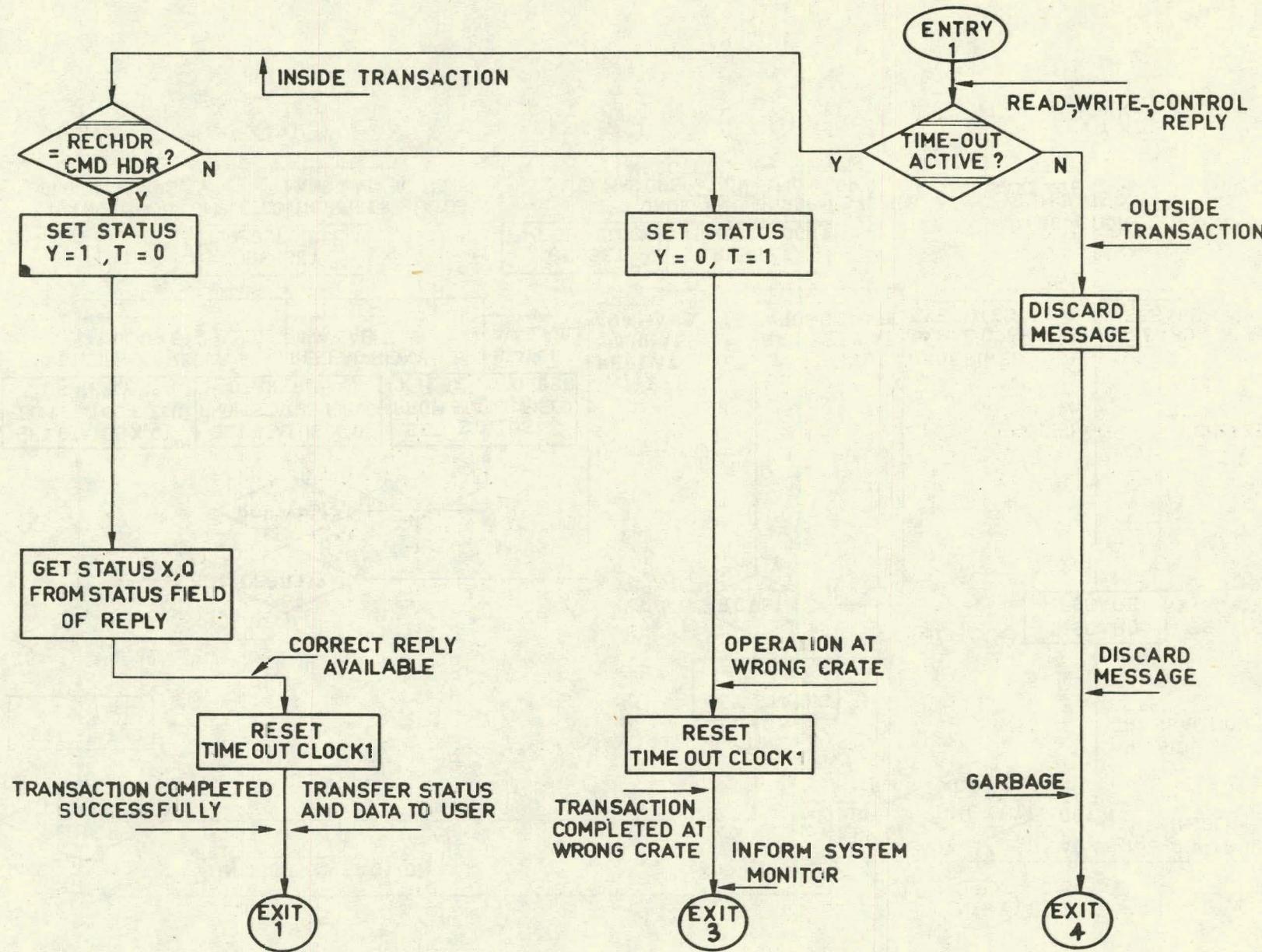

| Fig. 3c: Message Analysis for Bursts of Command/Reply Transactions . . . . .         | 39 |

| Fig. 4: Legend to Figs. 3a, 3b, 3c and Key to the Flow Charts                        | 40 |

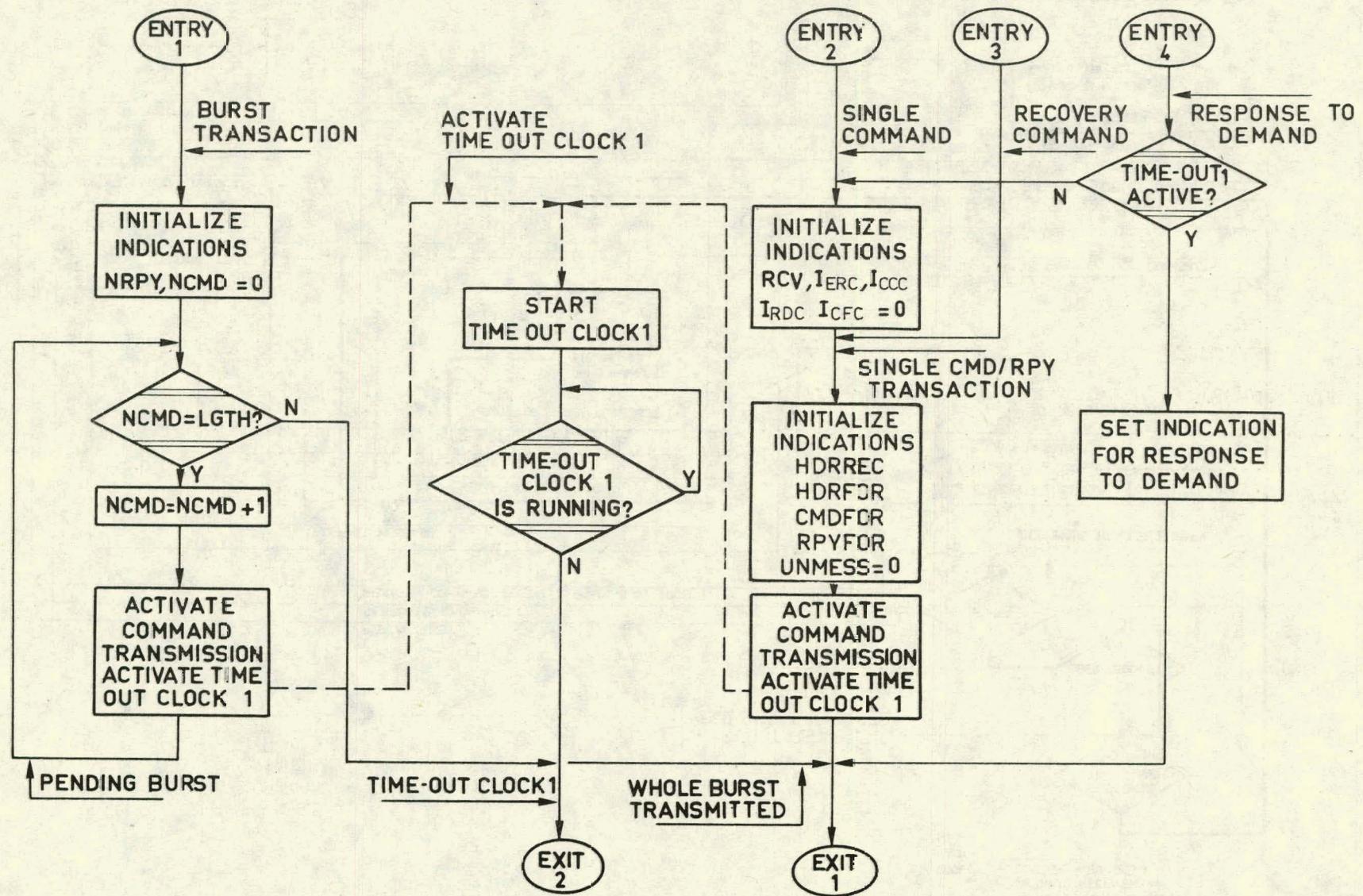

| Fig. 5: Flow Chart: Serial Driver . . . . .                                          | 41 |

| Fig. 6: Flow Chart: Command Handler . . . . .                                        | 42 |

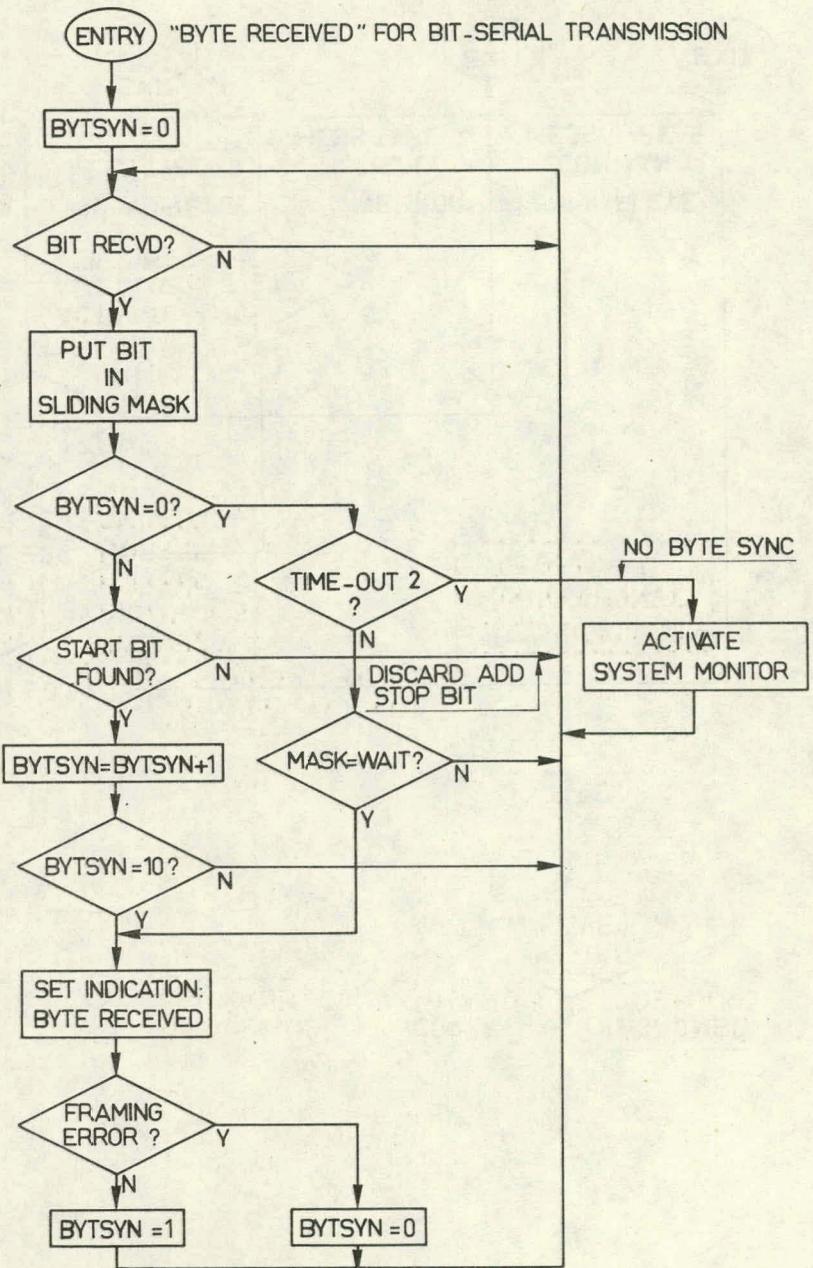

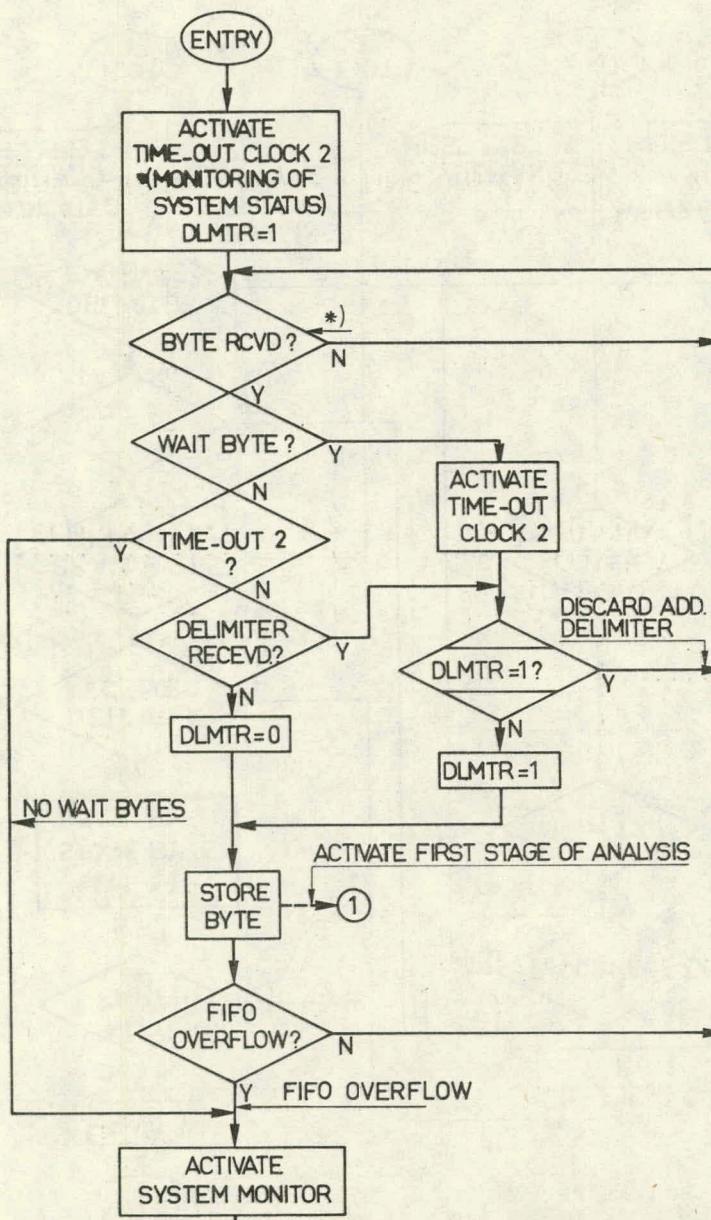

| Fig. 7: Flow Chart: Discarding of Additional Delimiter Bytes                         | 43 |

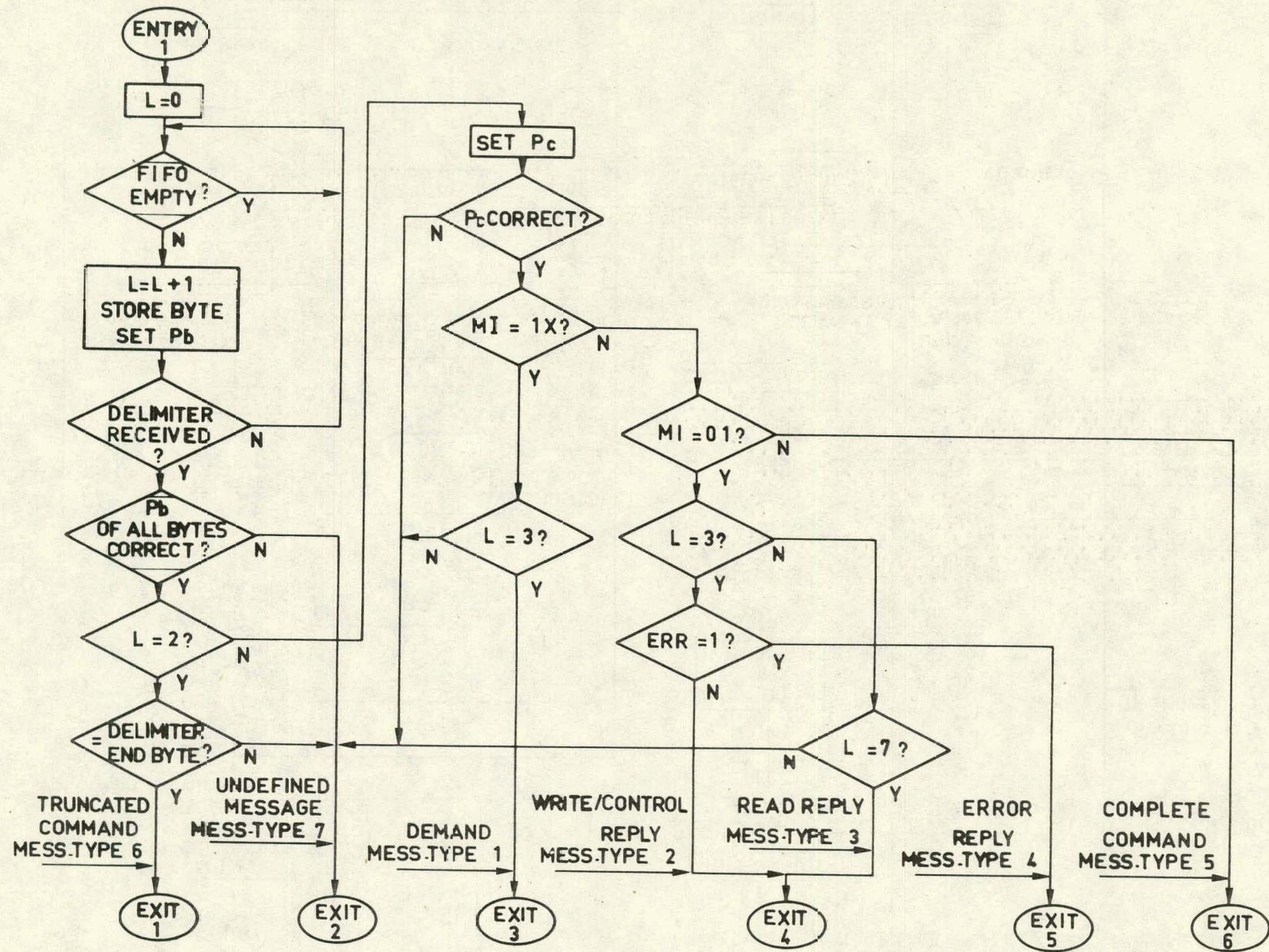

| Fig. 8: Flow Chart: First Stage of Analysis (Example) . . . .                        | 44 |

| Fig. 9a: Flow Chart: Reply Handler (Basic) . . . . .                                 | 45 |

| CONTENTS (Continued)                                                                                   | Page No. |

|--------------------------------------------------------------------------------------------------------|----------|

| Fig. 9b: Flow Chart: Reply Handler (Extended) . . . . .                                                | 46       |

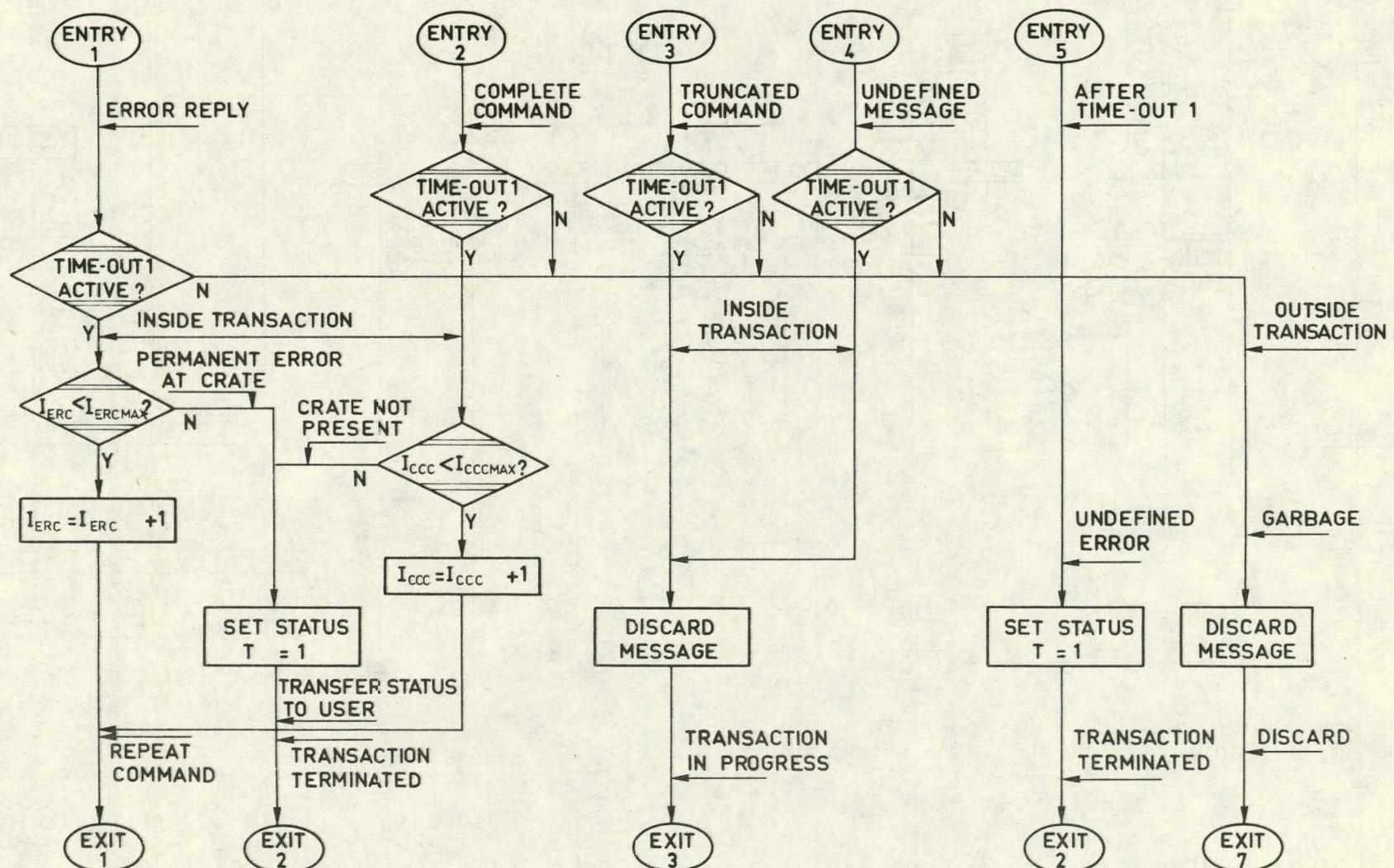

| Fig. 10a: Flow Chart: Error Handler (Basic) . . . . .                                                  | 47       |

| Fig. 10b: Flow Chart: Error Handler (Extended) . . . . .                                               | 48       |

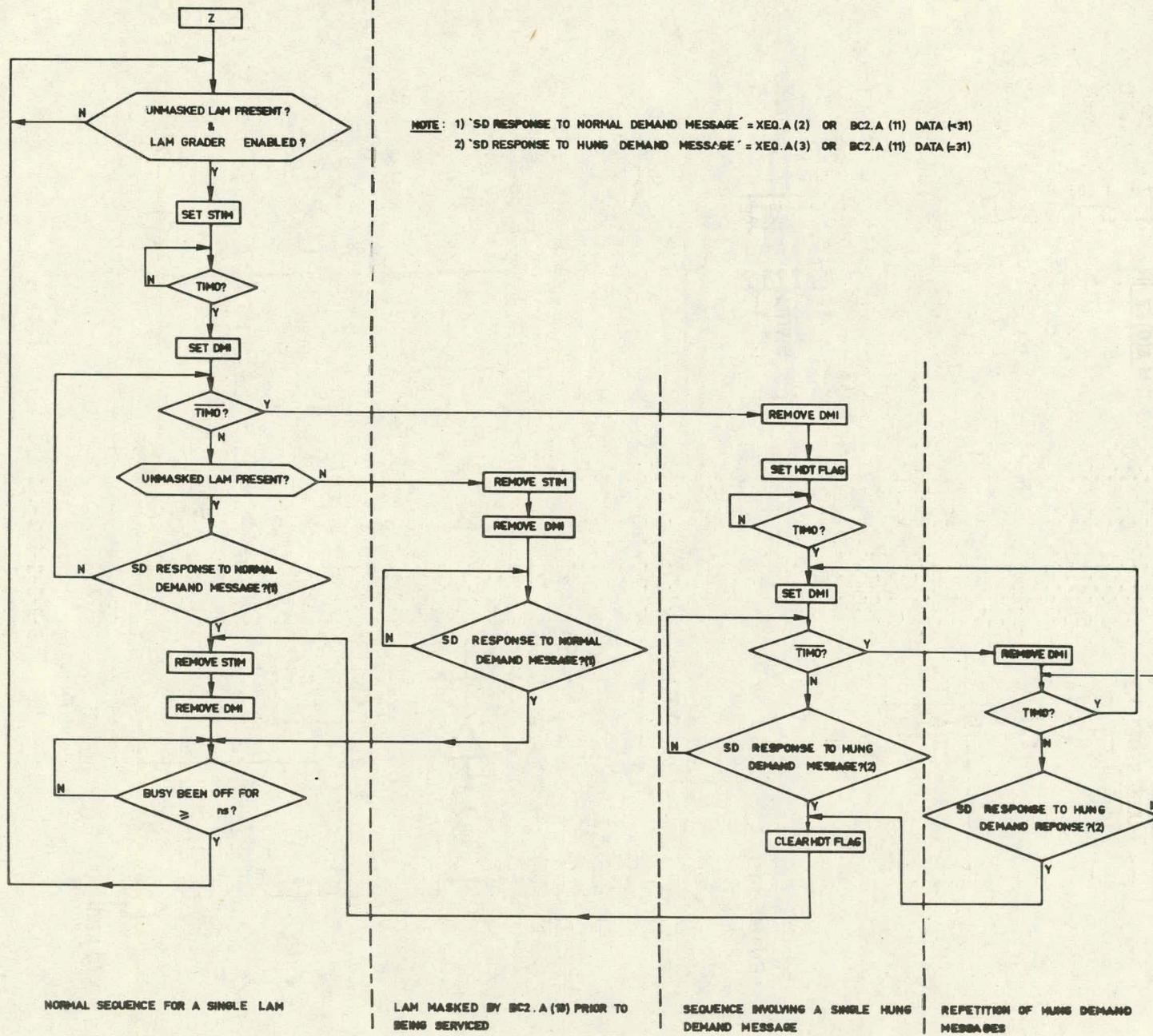

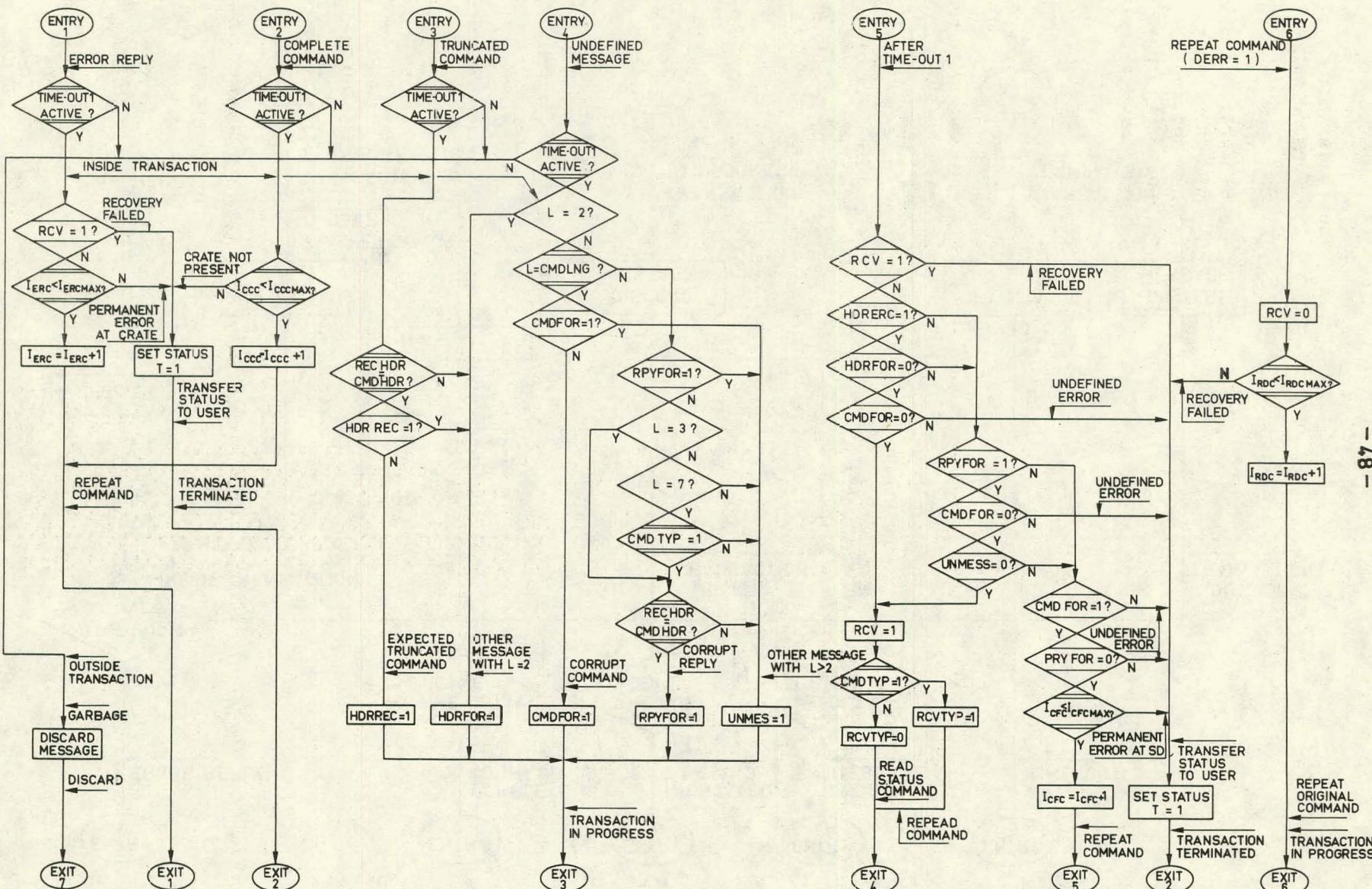

| Fig. 11a: Flow Chart: Demand Handler (with LAM Grader) . . . .                                         | 49       |

| Fig. 11b: Flow Chart: Demand Handler (without LAM Grader) . . .                                        | 50       |

| Fig. 11c: Flow Chart: Demand Handler (without LAM Grader,<br>with additional DISABLE Module LAM) . . . | 51       |

| Fig. 12: Flow Chart: Burst Handler . . . . .                                                           | 52       |

TABLE

|                                                              |    |

|--------------------------------------------------------------|----|

| Table 1: Principles of Handling Individual Demands . . . . . | 28 |

|--------------------------------------------------------------|----|

APPENDIX

Appendix A: LAM GRADERS FOR THE SERIAL CRATE CONTROLLER SCC-L2

|                                                        |     |

|--------------------------------------------------------|-----|

| A1. Introduction . . . . .                             | A-1 |

| A2. Features . . . . .                                 | A-1 |

| A2.1 L Status . . . . .                                | A-1 |

| A2.2 L Mask . . . . .                                  | A-2 |

| A2.3 L Request . . . . .                               | A-2 |

| A2.4 Encoded L Request . . . . .                       | A-2 |

| A2.5 Demand Message Generation . . . . .               | A-2 |

| A2.6 Using the LAM Grader . . . . .                    | A-3 |

| A2.7 Internal LAM . . . . .                            | A-4 |

| A2.8 Recommended Commands for Basic Features . . . . . | A-4 |

| A2.9 Additional Features . . . . .                     | A-5 |

| A2.10 Initialisation . . . . .                         | A-5 |

| A3. Treatment of LAM Numbers . . . . .                 | A-5 |

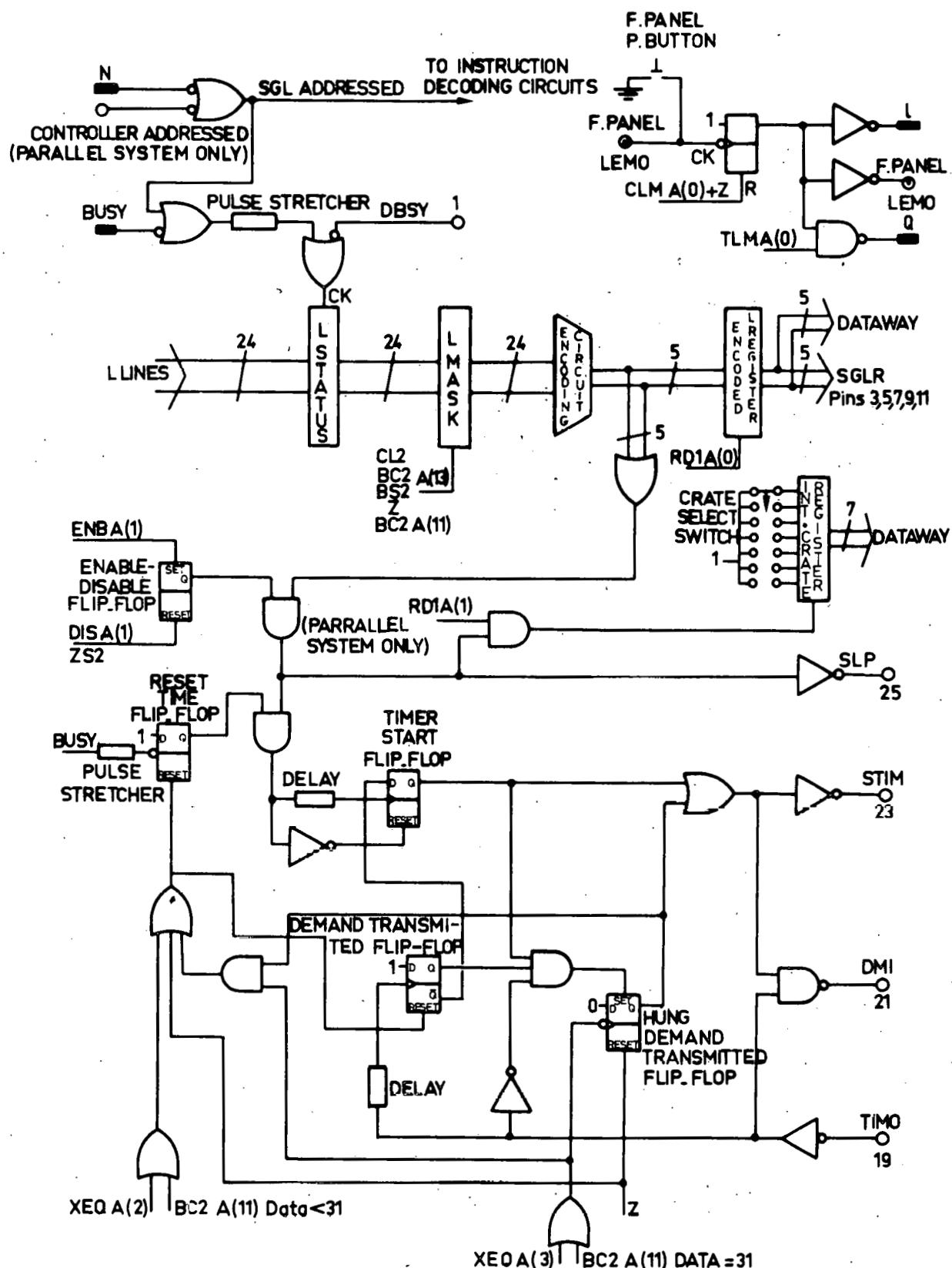

| A4. Description of the Block Diagram . . . . .         | A-5 |

ILLUSTRATIONS

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| Fig. A1: Methods of Using LAM Grader to handle an Individual<br>Demand . . . . . | A-7 |

| Fig. A2: Serial LAM Grader Recommendations . . . . .                             | A-8 |

| Fig. A3: Flow Chart: Sequence of Operation . . . . .                             | A-9 |

## CAMAC SERIAL HIGHWAY DRIVERS

### 1. Introduction

The CAMAC Serial Highway defined in Euratom Report EUR 6100e and IEEE Standard 595 (1976) provides a means of interconnecting up to 62 CAMAC Crate Assemblies (conforming to EUR 4100e and IEEE Standard 583-1976) to a computer. The Serial Highway communicates with the Dataway in each Crate Assembly via a Serial Crate Controller, and with the computer via a Serial Driver. The recommended Serial Crate Controller is Type L2, defined by an appendix to EUR 6100e and IEEE Standard 595.

This paper discusses the functional requirements for Serial Drivers for the CAMAC Serial Highway. It is intended to give some guidelines, especially on analysis of messages received at the Serial Driver Input, and on the internal processing required; these guidelines are a basis for a recommended practice to assist designers of Serial Drivers.

This paper is not intended to define any specific method of implementation or, in particular, the boundary between the hardware and software within a Serial Driver. However, it defines the interface between the Serial Driver and the User Program. This interface also includes facilities needed to drive parallel CAMAC systems.

It is noted that there is a fundamental difference between a Serial Driver (SD) and a Serial Crate Controller (SCC), in that the SD must accept and process all information from the highway, while the SCC only accepts and processes information which appears to be addressed to it. Thus an important feature of the SD is the ability to distinguish between relevant messages and spurious information (e.g. noise or distorted messages).

### 2. The Serial Driver

In this document the term 'Serial Driver' is used for the link between the User Program and the CAMAC Serial Highway. The Serial Driver is a compound of hardware and software. Obviously the hardware must include the ports to the physical highway, and the software must have an interface to the User Program. The internal boundaries between hardware and software are implementation dependent.

In order to examine the Serial Driver it is regarded as a combination of a Transmitter and a Receiver. These are effectively independent paths for information flow from the User Program to the CAMAC Highway and from the Highway to the User Program. However, some interaction between the transmitting and the receiving parts of the Serial Driver is essential for effective operation.

It should be recognised that the time required to perform a complete Command/Reply transaction, including a Dataway cycle, will generally be longer in a serial system than on a parallel highway. This time depends on the number of crates, logical byte delays, and the byte frequency. This may require some buffering between the user and the Serial Driver (see Fig. 2 and section 6).

Serial Crate Controllers Type L1, conforming to the final version of a preliminary document on the Serial Highway (ESONE document SH/01 and US ERDA TID 26488) are equivalent to type L2 for most practical purposes.

The algorithms described in this paper for the Serial Driver assume:

- that all the Serial Crate Controllers are the defined type SCC-L2, which truncate Commands (see message types, section 4)

- that all modules generate X=1 to indicate that the Command has been accepted (see error recovery using the Delayed Error-bit DERR, section 9.2).

- that old modules conforming to EUR 4100e 1969 (gating the L- signal with Dataway Busy) are not used in conjunction with SCC-L1 (generating Busy during Read Local LAM Pattern). This problem does not occur with SCC-L2, or if SCC-L1 is used with new modules.

### 3. Messages

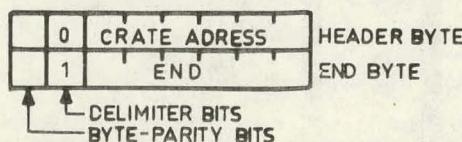

The input to the Serial Driver Receiver from the highway is a succession of bits (in bit-serial mode) or bytes (in byte-serial mode). The Receiver must assemble messages from this input, and provide status information relating to the assembly process.

- A message is defined as the sequence of bytes starting with the first non-delimiter byte after a delimiter byte, and ending with the first delimiter encountered subsequently.

- A delimiter is any byte with bit 7=1 and correct parity. Thus any other byte (i.e. bit 7=0 with any parity, or bit 7=1 with wrong parity) is a non-delimiter byte.

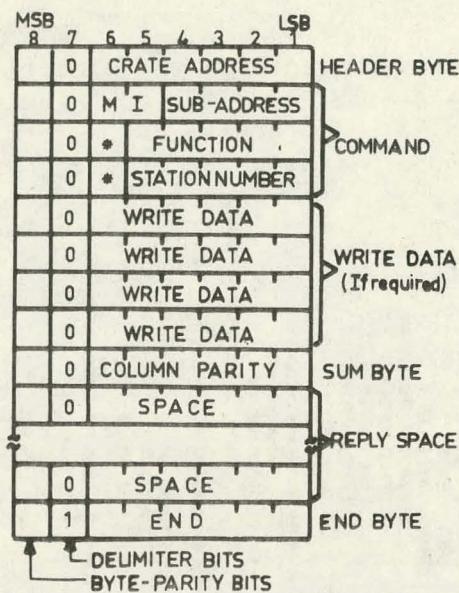

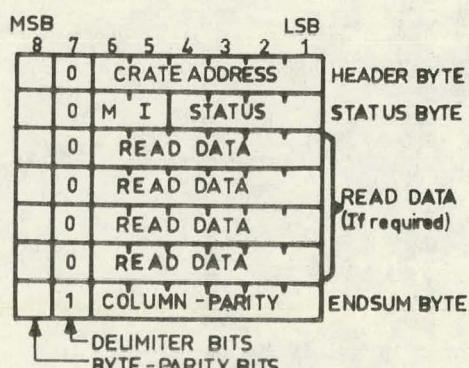

Section 3 of the Serial Highway Specification EUR 6100e 1976 (IEEE Std 595-1976) refers to four message types (Command, Truncated Command, Reply and Demand), and these are identified by the contents of the MI-field or their length (see Fig.1). Because errors may occur, the Serial Driver has to handle all messages, including any that differ from the standard types.

#### 4. Message Types

In a Serial Highway System incorporating only the defined Serial Crate Controller SCC-L2 the messages may be divided into the following categories (see also Fig. 3a, 3b, 3c, column 7):

##### 4.1 Demand

This message is an asynchronous request from any SCC. It can occur anywhere in the sequence of messages received by the SD.

##### 4.2 Reply without Read Data Field (Write/Control Reply)

This is the response of the addressed SCC to a Write or Control Command.

##### 4.3 Reply with Read Data Field (Read Reply)

This is the response of the addressed SCC to a Read Command.

##### 4.4 Error Reply (ERR=1)

This may be generated in response to any Command, and indicates a transmission error in the Command received at the SCC, such that the CAMAC operation was not executed.

Since the message indicates that a transmission error has been detected it can be generated either by the SCC to which the transmitted Command message was addressed, or by some other SCC (if there were errors in the Header byte of the command such that byte parity was preserved).

##### 4.5 Complete Command

A Complete Command message is received by the SD if the transmitted Command is passed around the Serial Highway without acceptance at a Serial Crate Controller. Each byte has a byte parity bit. Column parity (SUM byte) is presented in the ninth byte for Write Commands, and in the fifth byte for Read and Control Commands. The remaining bytes (SPACE plus END) have no column parity.

#### 4.6 Truncated Command

This is the Header byte of a Command message followed by an END byte. It has only byte parity. The receipt of a Truncated Command indicates that the Command message has been accepted by an SCC. However, if one WAIT byte within a stream of WAIT bytes is corrupted to a non-delimiter, it appears to be a Truncated Command message if the byte parity is correct.

##### NOTE:

The Serial Highway system Specification allows SCC's other than type SCC-L2. Thus, when some SCC's accept a Command message, they may retransmit all bytes up to and including the SUM byte. The length of the message received by the SD still indicates whether the Command message has been accepted by an SCC.

#### 4.7 Undefined Message

All other messages which do not fall into the classification given above are labelled "Undefined Message".

### 5. Organisation of Command/Reply Transactions

Command/Reply transactions and recovery from errors are organised as follows:

#### 5.1 Single Command/Reply Transactions

The normal sequence is that each command message is transmitted after the previous CMD/RPY transaction has been completed. The SD transmits the bytes of the Command message and receives the bytes of the truncated Command message and the expected reply to the command.

A single transaction is completed successfully when the SD has received the expected Write/Control/Read reply message. Demand messages can occur at any time within the sequence of received messages, and the appropriate actions to service the demand can be taken after any individual transaction.

A single transaction is completed unsuccessfully if the SD receives an Error Reply, a Reply message with unexpected Header byte, or a complete Command message. If none of these conditions for completion are satisfied, the transaction is abandoned after a preset time-out period has elapsed since the Command was transmitted.

Immediately after unsuccessful completion of a transaction, or after abandoning a transaction at the end of the time-out period, the SD can take appropriate action to recover from the error or to report it to the user program.

## 5.2 Bursts of Command/Reply transactions

An alternative method of organising transactions, appropriate to high-performance systems with low error rates, is described in Section 4.6.2 of EUR 6100e (IEEE Std 595). In this method the SD does not wait to receive the reply to one command before starting to generate the next. This document gives an example of one way in which the SD can handle burst transactions. A burst of transactions is completed successfully when the last Command message has been transmitted and the expected number of Reply messages (Read/Write/Control Replies only) have been received. Demand messages can be received at any time during the burst, but the appropriate servicing action can only be taken after the burst is completed.

A burst of transactions is completed unsuccessfully if the SD receives an Error Reply, or a complete Command, or a Reply with unexpected Header byte. If none of these conditions for completion is satisfied, the burst is abandoned after a preset time-out period has elapsed since transmission of the last Command. In burst transactions, any action to recover from an error or report it to the user program takes place after the end of the time-out period.

The operations within the burst should be such that the whole burst can be repeated if it is not completed successfully, for example they should not include 'Read and Clear' operations.

In both single transactions and bursts of transactions the preset time for time-out depends on the number of crates, the logical byte delays and the byte frequency.

## 5.3 Error recovery

Error recovery procedures are attempts to achieve the intended effect of single CMD/RPY transactions, or bursts of transactions, which have failed. These procedures may be performed by the SD in a way that is invisible to the User Program.

The analysis of received messages supports three means of error recovery:-

- repeating a single command. This simple procedure can only be applied safely when the original command has not been executed, due to errors in transmitting the Command message.

- using the procedures based on the Delayed Error (DERR) status and Re-read Data feature of SCC-L2, see Section 15.6 of EUR 6100e and IEEE Std 595. These can be applied when the original Command has been executed but the Reply message has been corrupted.

- repeating a burst of transactions. The procedures based on the DERR status cannot be applied to bursts of transactions. Some duplication of commands is inevitable, and data may be lost if the burst included operations that read data destructively.

## 6. Block Diagram of the Serial Driver

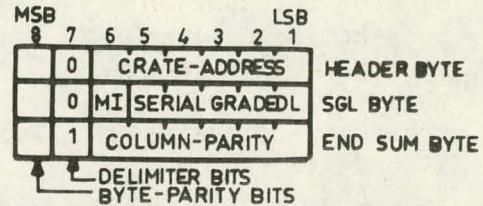

The block diagram of the SD (Fig.2) shows the data and status information paths within the Serial Driver. The structure shown is independent of its implementation in hardware or software.

The Serial Driver consists of two parts:

The first part is related to the Serial Highway, and contains:

- the Transmitter

- the Receiver and

- the first stage of Message Analysis

In this part there is no interaction between the transmitting and receiving part. Therefore the first stage of message analysis relies completely on the individual received messages, independently from the transmitted Command and other messages received (analysis independent of context and type of transaction, see Fig. 3 a, 3b, 3c, columns 1 to 9).

The second part can consist, for example, of:

- a Command handler

- a Reply handler

- an Error handler

- a Demand handler

- a Burst handler

- and a System monitor.

In this part there is a close interaction between the transmitting and receiving parts. Therefore the second (final) message analysis of a received message includes the context of transmitted Commands and other received messages. This message analysis including context is described in section 9. As a result of this final message analysis one of the following actions are performed:

- Data and parameter transfer

- Response to Demands

- Recovery from errors

- Discarding garbage.

The block diagram of the Serial Driver also shows the interconnection between the Serial Driver and the User Program via System Services which are system dependent and may contain:

- Queue

- CAMAC Address Check

- Data Buffer Address Check

- CAMAC Device protection against unauthorized user access

- Data and parameter transfer between SD and User Program

- Response to an event representing a LAM or an error.

## 7. SD Command Handler and Transmitter

The Serial Driver Command Handler (Fig. 6) may operate the Serial Highway with either single Command/Reply transactions or bursts of transactions. The Serial Driver assembles each Command message from the Header to the SUM byte, adds the appropriate number of SPACE bytes and terminates the message by an END byte.

The number of SPACE bytes is implementation dependent. It may be:

- a function of the Command transmitted,

- or a fixed, safe number for the system,

- or an indefinite number, generated until the Reply is received.

The last method of terminating a Command/Reply transaction needs interactions between the receiving and transmitting part of the Serial Driver. But note that upstream crates receive fewer WAIT bytes and thus have fewer opportunities to transmit Demand messages, or to re-synchronise.

NOTE: commands for system reconfiguration (Bypass, Loop Collapse) must set Time-out for more than 100ms and must force the Command Handler to generate SPACE bytes during this time (see section 13).

The Command message may be assembled partly in the Command Handler (e.g. to determine the number of SPACE bytes) and partly in the Transmitter (e.g. to generate parity).

The Serial Driver Transmitter generates WAIT bytes if no Commands are transmitted :

- 3 WAIT bytes minimum are required for switching out each delay buffer in the SCC's. Generation of WAIT bytes by the SD is especially required for SCC's near to the output port of the SD.

- 3 WAIT bytes minimum are required for re-synchronisation of an SCC-L2 operating in bit-serial mode (see section A1.5.1 of EUR 6100e and IEEE Std 595).

In bit-serial mode the byte framing must contain one stop bit. There may be additional pause bits.

## 8. Message Analysis, Summary and First Stage

Each message received by the SD is first analysed individually, without regard to the context in which it occurs. The intermediate result from this analysis is passed to a second stage which analyses the message in a context including any previous messages occurring in the same transaction. The final decision identifies the message and the action to be taken by the SD.

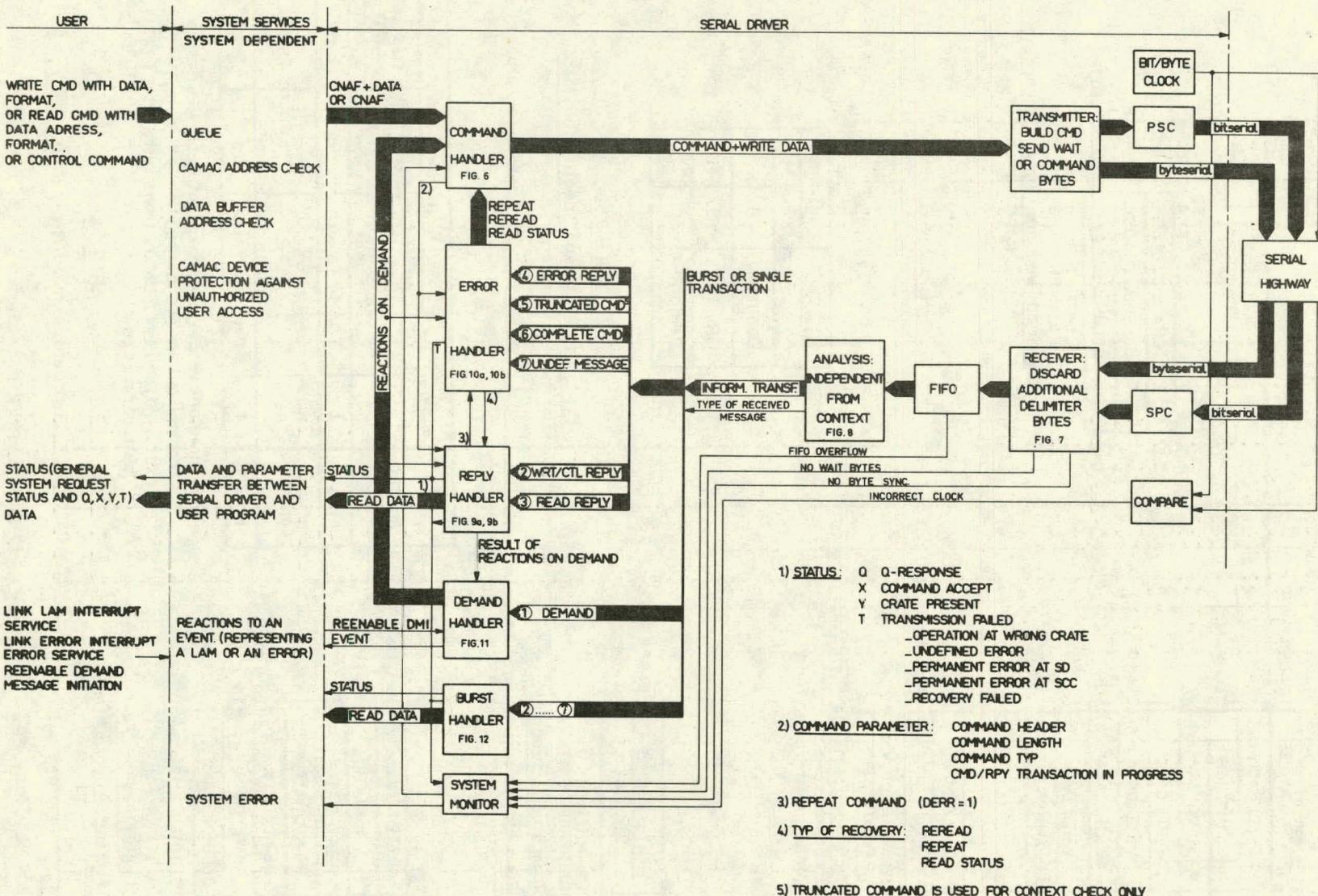

### 8.1 Summary

The analysis of messages in single CMD/RPY transactions is shown in basic form in Fig 3a and in an extended form in Fig 3b. The analysis of messages in a burst of transactions is shown in Fig 3c. In these diagrams the decisions associated with normal error-free operations are indicated by shading.

In each case the first stage of analysis is similar and is shown in the left-hand block in the diagrams. Here, characteristics of the message (Cols 1-6) that are independent of its context lead to decisions that identify the message in terms of the types defined in Section 4. These intermediate decisions (Cols 7,8,9) are passed to the second stage of analysis shown on the right-hand side of each diagram.

The basic second stage of analysis for single transactions is on the right-hand side of Fig 3a. In the upper block the decisions from the first stage (Col 10) and two context-independent characteristics of the message (Cols 11 and 12) lead to final decisions that identify the message (Cols 21,22) and indicate the appropriate action to be taken by the SD (Col 23). The lower block shows the very simple treatment of incomplete transactions that are terminated by time-out.

In the absence of errors, Demand messages occurring at any time are identified by the first stage, and the action (to respond to the demand) is indicated by the second stage (Class 1). Truncated Command messages are identified by the first stage and, if they occur within a transaction, are discarded by the second stage (Class 6), which expects that a Reply message will follow. Write/Control/Read Reply messages are identified by the first stage and, if they occur within a transaction and have the expected header byte, lead to second stage decisions that the transaction has been completed successfully (Classes 2a and 3b).

Some errors result in the SD receiving Error Reply messages or Complete Command messages. These are identified by the first stage and, if they occur within a transaction, lead to second stage decisions that the command has not been accepted by any SCC (Classes 4 and 5), so that the command can be repeated. Other errors result in messages during the transaction that cannot be identified by the first stage, or messages occurring outside the transaction. These are discarded by the second stage. A special class of errors results in Reply messages with unexpected header bytes (Classes 2b and 3a), and the second stage indicates that the SD should inform the system monitor and user program. When a transaction is not completed, but is terminated by time-out, the second stage indicates that an undefined error should be reported to the user program.

The extended second stage analysis for single transactions is on the right-hand side of Fig 3b. The analysis leading to the decisions for classes 1-5 is similar to Fig 3a, but the analysis for Classes 6-8 is more detailed and leads to some actions using the Delayed Error (DERR) status and Re-read Data feature of SCC-L2. This extended analysis takes into account not only the characteristics of the current message (Cols 10-13) but also the transmitted command (Col 14) and any previous messages received during the transaction (Cols 15-19). Decisions 6a-7e resulting from one message are taken into account in the analysis of later messages in the same transaction (as columns 15-19).

The second stage analysis for a burst of transactions is on the right-hand side of Fig 3c, which is generally similar to Fig 3a. The main difference is in Col 20. If the actual number of replies is less than the expected number, the normal analysis of Reply messages leads to the decision 'Command executed successfully' (Classes 2x and 3x) and the action to wait for more replies. If the actual number is equal to the expected number, the decision is 'Burst completed successfully' (Classes 2y and 3y). The actions for Classes 4 and 5 do not repeat the command.

## 8.2 First Stage of Analysis

The SD Receiver checks the framing and performs byte synchronisation (by receiving a WAIT byte) in bit-serial mode, and discards WAIT bytes and other additional Delimiter bytes (see flow diagram Fig. 7). A FIFO buffer of one byte (or more) allows some flexibility between the internal clock and the received byte clock.

The criteria applied to message analysis in the first stage rely only on the content of the received message, and are independent of context (see Fig. 3a, 3b, 3c, columns 1 to 6). These criteria are:

see Fig.3a, 3b, 3c, column

|                          |            |   |

|--------------------------|------------|---|

| - Byte parity            | (Pb)       | 1 |

| - Column parity          | (Pc)       | 2 |

| - Message length         | (L)        | 3 |

| - Message identifier     | (MI)       | 4 |

| - Transmission Error bit | (ERR)      | 5 |

| - Delimiter              | (END byte) | 6 |

Truncated Command messages are not fully protected by the Error Detection Code. Identification of these messages is strengthened by testing the Delimiter byte for the defined END byte pattern. The ENDSUM byte of Reply and Demand messages does not have a unique pattern.

For the Complete Command (type 5) the pattern of the Space bytes is not checked because the relevant information in this message is terminated by the SUM byte.

The message analysis performed at this stage is independent of the organisation of Serial Highway operations as individual transactions or bursts. It can be implemented either by inspecting each byte of a message as it is received, or by collecting all bytes of a message in a buffer and then performing the checks. The final decision about the message must be made after the end of the message has been received, to ensure that different implementations come to the same result.

The first stage analysis leads to the decisions shown in Figs. 3a, 3b and 3c, columns 8 and 9. The messages are analysed into the seven types described in section 4.

## 9. Second stage of Message Analysis

The criteria used for this stage of message analysis include the context of the message relative to the transmitted Command and other received messages.

The message analysis depends on whether the Serial Highway operations are organised as single transactions or bursts of transactions and, in the first case, whether undefined messages are analysed to identify cases where error recovery procedures based on DERR status can be used. Thus, three forms of second stage analysis are described below in sections 9.1, 9.2 and 9.3.

### 9.1 Single CMD/RPY Transactions, basic analysis

This basic form of second stage analysis does not analyse undefined messages. It supports simple error recovery actions that can be applied when the original command has not been executed, due to errors in transmitting the Command message. It is shown in Fig 3a, and uses the criteria shown in columns 10 to 12:

- Message types

- Transaction status

- Received Header = Transmitted Header

The first and second stage analyses lead to the decisions shown in Fig. 3a, columns 21 and 22:

- \* Demand message received

- \* Transaction completed successfully

- + Transaction completed at wrong SCC

- + Command not executed by SCC

- + Command not accepted by any SCC

- + Garbage received

- \* Truncated Command message received

- + Undefined message

- + Undefined error.

(\* normal, + abnormal)

These criteria and decisions are defined in more detail below.

### 9.1.1 Criteria

The criteria for the basic second stage analysis of single transactions, without further analysis of undefined messages, are based on the following conditions:

- Message Types (Fig. 3a, Col 10)

These are the seven message types identified by first stage analysis (see Section 4).

- Transaction status (Col 11)

This condition indicates whether a transaction is in progress (P), or not in progress (N). When a transaction is not completed, the end of the time-out period (T) causes certain decisions to be taken.

- Received Header = Transmitted Header (Col 12)

This condition indicates whether the Header byte of the received message matches, in all 8 bits, the Header byte of the transmitted Command message. In the analysis of Reply and Truncated Command messages this is evidence that the correct SCC has accepted the Command message.

### 9.1.2 Decisions

The second stage analysis of single transactions, without further analysis of undefined messages, uses the above criteria sequentially in any order, or simultaneously, and leads to the following decisions, shown in columns 21 and 22 of Fig. 3a:

- \* Demand message received (Class 1)

The result of the first stage analysis is accepted, without applying further criteria, and independently of the condition 'Transaction status'. The actions appropriate to the demand are performed after any current transaction has been completed.

- \* Transaction completed successfully (Classes 2a, 3b)

A Reply message, identified by the first stage as Type 2 or 3, has been received while a transaction is in progress, and has the expected Header byte. It is classified as the expected reply without applying other criteria, because of the strong protection given by the Error Detection code.

The status and, in the case of a Read reply, the data are passed to the user program.

- + Undefined CAMAC operation executed (Classes 2b, 3a)

A Reply message, identified by the first stage as Type 2 or 3, has been received while a transaction is in progress, but does not have the expected Header byte. It can be assumed that either the Reply was corrupted or the Command was executed at a wrong crate. However, the latter is unlikely due to the strong protection given by the error protection code.

The user program and System Monitor are informed.

+ Command not executed by SCC (Class 4)

An error Reply message, identified by the first stage as Type 4, has been received while a transaction is in progress. This indicates that the Command message has been accepted by an SCC (it is irrelevant whether this is the correct SCC) and not executed, because of a transmission error in the Command message.

The transaction can be repeated, with a limit on the number of repetitions.

+ Command not accepted by any SCC (Class 5)

A Complete Command message (type 5) has been received while a transaction is in progress. This indicates that the Command message has not been accepted by any SCC, but this may be due to temporary conditions such as lack of synchronism or a transmission error in the Command message. It is unnecessary to analyse the reason for the failure.

The transaction can be repeated, with a limit on the number of repetitions.

\* Truncated Command message received (Class 6)

A Truncated Command message (Type 6) has been identified by the first stage while a transaction is in progress. No further second stage analysis is performed and the Truncated Command message is discarded (but see Section 9.2.2 for analysis and actions when undefined messages are being processed).

+ Undefined message received (Class 7)

An Undefined message (Type 7) has been identified by the first stage while a Transaction is in progress. The Undefined message is discarded (but see Section 9.2.2 for analysis and actions when Undefined messages are being processed).

+ Undefined error (class 8)

At the end of the time-out period the first stage analysis has not identified a Reply message or a Complete Command message, or no message at all has been received.

There is insufficient evidence to show whether the command has been executed (but the reply lost), or has not been executed (eg. the command message lost). The user program is informed that the transaction has not been completed.

+ Garbage received

All messages, except Demands, received when no transaction is in progress are analysed as garbage, and are discarded.

A certain amount of garbage is expected depending on noise in the environment. It is recommended that the System Monitor should be informed if an abnormal amount of garbage is received.

(\* normal, + abnormal)

## 9.2 Single CMD/RPY Transactions, extended analysis

This optional extended form of second stage analysis performs further processing of Truncated Command messages and undefined messages. It supports further error recovery procedures based on the Delayed Error (DERR) status which can be applied when the command has been executed but the Reply message has been corrupted. It is shown in Fig.3b.

If the analysis of the received messages does not show whether the Command has been executed or not, a recovery procedure can be attempted in which the Delayed Error bit gives this information. The use of DERR is safe only if there is a reasonable indication that the original Command has addressed the intended SCC, so that the state of the DERR-bit corresponds to the current transaction.

The required indication can be obtained if all messages within the time-out period are inspected and classified. The only indications at the SD that a Command has been accepted by an SCC are the receipt of the Truncated Command and/or the Reply message.

An error recovery procedure using the DERR bit must not be performed more than once, because the recovery operation (Read Status or Reread) may change the state of the DERR bit in the SCC. (The DERR bit corresponds to the last operation in the SCC).

If in a Read Status or Reread operation the DERR bit is found to be DERR = 1, the original Command has not been executed and it can be repeated.

If the Reply message to this repeated command is again an undefined message of type 8a-d this indicates that the message has been accepted by the intended SCC - although doubtful whether executed or not. In this case it is correct to perform another Read Status or Reread operation. This sequence Command - Reread/Read Status - repeat original Command - Reread/Read Status - ... is correct but has to be limited.

The extended second stage analysis uses the additional criteria shown in Fig. 3b columns 13 to 17 while the transaction is in progress:

- Received message length (L)

- Read Command transmitted

- Expected Truncated Command received

- Corrupt Command received

- Corrupt Reply received

The first and extended second stage analyses lead to the more detailed decisions of class 6 and 7 shown in Fig. 3b in the columns 21 and 22 while the transaction is in progress:

- \* Expected Truncated Command received

- + Other message with L=2

- + Corrupt Write/Control/Error Reply received

- + Corrupt Read Reply received

- + Corrupt Command (not accepted by any SCC)

- + Other message with L > 2 .

(\* normal, + abnormal)

The extended second stage analysis uses the additional criteria shown in Fig. 3b in column 18 and 19 when the transaction has been terminated by Time-out:

- Other message with  $L = 2$

- Other message with  $L > 2$

The first and extended second stage analysis lead to the additional final decisions when the transaction is completed by Time-out shown in Fig. 3b in the column 21 and 22:

- + Reply lost

- + Corrupt Read Reply (expected) received

- + Corrupt Write/Control/Error Reply (expected) received

- + Corrupt Complete Command received

- + Undefined Error.

(+ abnormal)

The additional criteria and decisions are defined in detail in Sections 9.2.1 and 9.2.2.

#### 9.2.1 Criteria

The additional criteria for extended second stage message analysis are based on the following conditions:

- Received message length (Fig. 3b, Col 13)

The length of the undefined message is used to classify it as Command Form (length equal to that of the transmitted Command message) or Reply Form (length 3 or 7 bytes) or Other message with  $L = 2$ .

- Read Command transmitted (Col 14)

The transmitted Command included a Read Function, so that a 7-byte Reply or an Error Reply are expected.

- Expected Truncated Command received (Col 15)

The messages received while the transaction is in progress have already included one classified as Class 6a (see Section 9.2.2).

- Corrupt Command received (Col 16)

The messages received while the transmission is in progress have already included one classified as class 7c (see Section 9.9.2).

- Corrupt Reply received (Col 17)

The messages received while the transmission is in progress have already included one classified as class 7a or 7b (see Section 9.2.2).

- Other messages with L=2 received (Col 18)

The messages received while the transaction is in progress have already included one classified as Class 6b, 6c or 7d (see section 9.2.2) in place of, or in addition to, the expected Truncated command.

- Other message with L > 2 received (Col 19)

The messages received while the transaction is in progress have already included one or more with length more than two bytes that have either not had the appropriate length for Command Form or Reply Form, or are in addition to another Command Form or Reply Form message (Class 7e).

#### 9.2.2 Decisions

The first and extended second stage analyses for single transactions lead to the following additional decisions while the transaction is in progress, shown in Fig. 3b in columns 18 and 19.

- \* Expected Truncated Command received (Class 6a)

The first stage analysis has identified a Truncated Command message (Type 6) while the transaction is in progress, and the Header byte matches that of the transmitted Command message. This is evidence that the Command message has been accepted by the correct SCC. This is used as a condition in the analysis of undefined messages (see column 15) when the transaction is completed by Time-out.

- + Other message with L=2 received (Classes 6b, 6c, 7d)

The first stage analysis has identified a Truncated Command message while the transaction is in progress, and this either does not have the expected Header or is an additional Truncated Command with the expected Header. In case of class 7d the first stage has identified an Undefined message with a length of two bytes. This is evidence of certain types of malfunction, and is used in the analysis of undefined messages (see Column 18) when the transaction is completed by Time-out.

- + Corrupt Write/Control/Error Reply received (class 7a)

The first stage analysis has identified an Undefined message (Type 7) while the transaction is in progress and it is the first received 3-byte message where the header matches.

- + Corrupt Read Reply received (Class 7b)

The first stage analysis has identified an Undefined message (Type 7) while the transaction is in progress and it is the first received 7-byte message where the header matches and a Read Command has been transmitted.

- + Corrupt Command received (Class 7c)

The first stage analysis has identified an Undefined message (Type 7) while the transaction is in progress and it is the first received message where the length is equal to the transmitted Command message length.

- + Other message with  $L > 2$  received (Class 7e)

The first stage analysis has identified an Undefined message (Type 7) while the transaction is in progress and this message cannot be further classified into class 7a to 7d.

(\* normal, + abnormal)

The first and extended second stage analysis for single transactions lead to the following additional decisions when the transaction is completed by Time-out shown in Fig. 3b in the lower sections of columns 21 and 22:

- + Reply lost (Classes 8a, 8b)

The expected Truncated Command message has been received, but the time-out period has elapsed without a good Reply having been received. No other message with  $L = 2$  must have been received, in order to make sure that the expected Truncated Command message received is the only one which can be interpreted as such. It is reasonable to assume that the command has been accepted but the Reply has been lost or corrupted. The error recovery procedure described in EUR 6100e (IEEE Std 595) section 15.6 can be used, and the appropriate action is to read the Status Register of the SCC if the Command was Write or Control (Class 8a) and to Reread the data if the Command was Read (Class 8b).

- + Corrupt Write/Control/Error Reply received (class 8d)

The only Undefined message with  $L > 2$  received while the transaction is in progress has been a Reply Form. The expected Truncated Command has not been received. The evidence suggests that the Undefined message is a corrupted Reply in response to a Write/Control command. The appropriate error recovery action is to read the Status register of the SCC.

- + Corrupt Read/Error Reply received (Class 8c)

As the preceding decision, but a Read command has been transmitted so that the evidence suggests a corrupted Read Reply. The appropriate error recovery action is to Reread the data from the SCC.

- + Corrupt complete Command message received (Class 8e)

The only Undefined message with  $L > 2$  received while the transaction has been in progress is a Command Form. The expected Truncated Command has not been received. The evidence suggests that the Command has not been accepted by any SCC. The appropriate error recovery action is to repeat the transaction.

+ **Undefined Error (Classes 8f and 8g)**

The transmission has been completed by Time-out and the received messages do not correspond to classes 8a to 8e, or no messages at all have been received. There is insufficient evidence to show whether the Command has been executed or not. The user program is informed that the transaction has not been completed.

(+ abnormal)

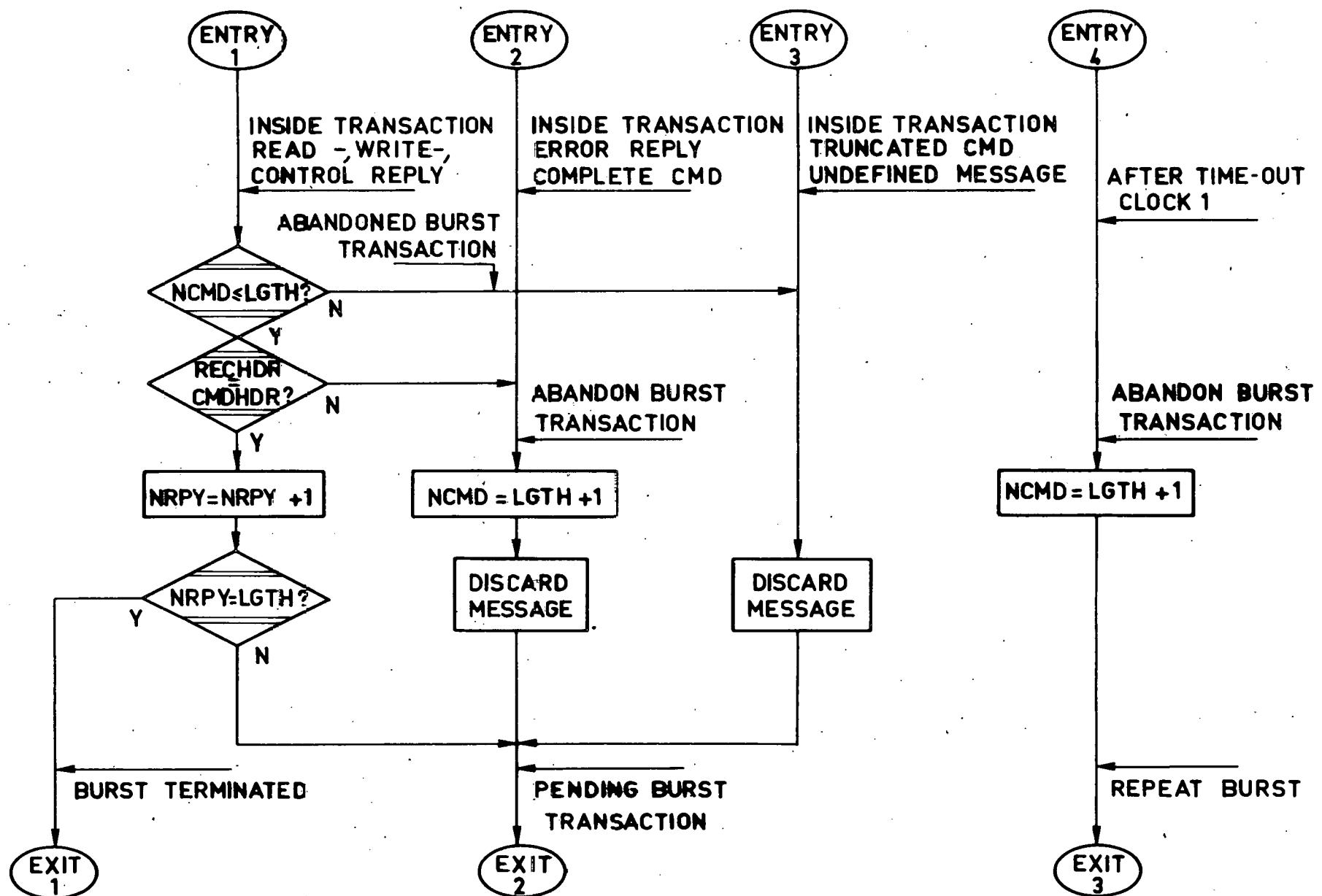

### 9.3 Bursts of transactions

The second stage of message analysis for a burst of transactions (Fig. 3c) is generally similar to the basic analysis of single transactions (section 9.1), but error recovery is restricted to repeating the whole burst. Recovery based on the DERR status cannot be used, because the DERR status of each transaction is overwritten by any subsequent transaction to the same SCC. Recovery by repeating particular failed transactions is not recommended because the effect of a transaction may depend on its context within the burst. Thus bursts of transactions can only be used when these restrictions can be accepted.

#### 9.3.1 Criteria

In addition to the conditions in section 9.1.1 there is the condition:

- **Expected number of replies received (Fig. 3c, Col 20)**

This indicates whether the number of Read/Write/Control Replies received (including the current message, if appropriate) is equal to the total number of commands in the burst.

#### 9.3.2 Decisions

The first and second stage analyses of messages in a burst of transactions lead to the following decisions, as shown in Fig. 3c, Columns 21 and 22:

- \* **Demand message received (Class 1)**

As in Section 9.1.2, but the demand is serviced after the burst has been completed.

- \* **Command executed successfully (Classes 2x, 3x)**

The received Reply message does not complete the expected number of replies. Wait for more replies.

- \* **Burst completed successfully (Classes 2y, 3y)**

The received Reply message completes the expected number. The status and data from all replies in the burst are transferred to the user program.

- + **Undefined CAMAC operation executed (Classes 2z, 3z)**

The Header byte of the received Reply message does not match that of the corresponding transmitted Command message. The burst of transactions is abandoned. After the time-out period has elapsed (so that all messages resulting from the burst have been received) all received messages except Demands are discarded, and the burst can be repeated.

- + Command not executed by SCC (Class 4)

An Error Reply has been received. The burst of transactions is abandoned, and can be repeated after the time-out period.

- + Command not accepted by any SCC (Class 5)

A complete Command message has been received. The burst of transactions is abandoned and can be repeated after the time-out period.

- ★ Truncated Command message received (Class 6)

All received Truncated Commands are discarded, and not analysed.

- + Undefined message received (Class 7)

All received Undefined messages are discarded, and not analysed.

- + Not enough replies (Class 8)

The time-out period has elapsed before the expected number of replies has been received. The burst of transactions is abandoned, all received messages except Demands are discarded, and the burst can be repeated.

- + Garbage received

All messages, except Demands, received when no Transaction is in progress are analysed as garbage and are discarded.

(\* normal, + abnormal)

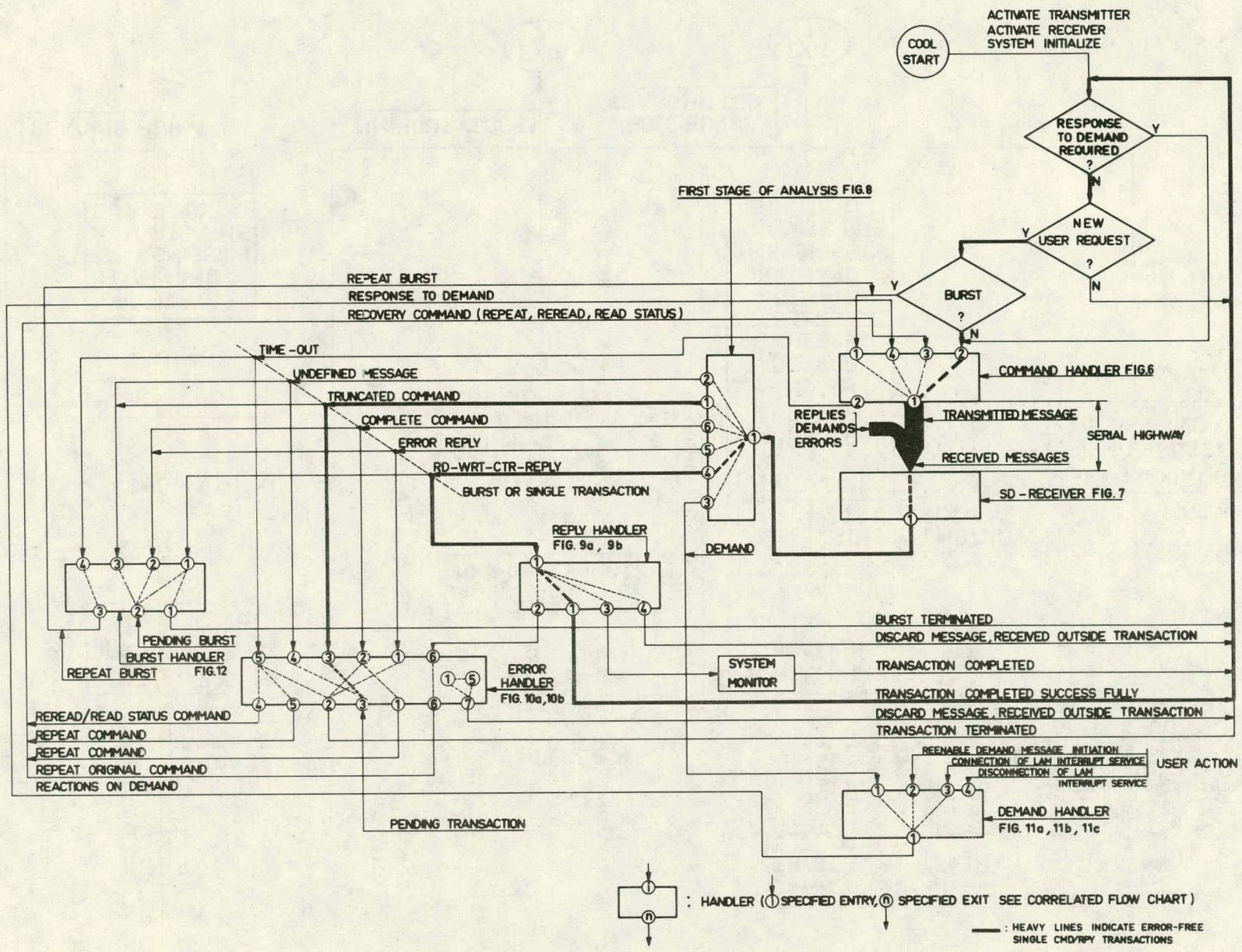

## 10. Demand handling

The Demand Handler should provide a secure way of handling LAM's by means of simple calls from the user program. The details of LAM handling at the hardware level should be hidden from the user, but the facilities provided will depend on the hardware and software support available (for example whether or not a LAM Grader is used, operating system facilities for task scheduling etc.). The following sections define the operations of the Demand Handler in various system configurations.

The actions of the Demand Handler upon receiving a Demand message from the first stage of analysis are:

- to identify its source

- to respond to the Demand

- to inform the corresponding user program that the demand has occurred.

A LAM Grader provides the first level of LAM handling by hardware. Systems with LAM Graders permit:

- fast identification of the LAM source (e.g. by coded station number in the SGL-field, comparable to a vectored interrupt),

- high system security because standard hardware functions are defined for masking individual LAM's. The Demand Handler itself can thus have the ultimate responsibility for handling LAM's.

However, for some systems the cost of LAM Graders is not justified. For systems without LAM Graders:

- the user program has the ultimate responsibility for handling all the LAM's in the system,

- LAM servicing is less efficient because the system can only disable Demands at the crate level, hence a LAM locks out other LAM's from the same crate until it is serviced,

- An additional Read operation is required for LAM identification in the Crate (comparable to a polling procedure).

The effect of a LAM locking out other LAM's until it is serviced can be avoided if the Demand Handler knows the individual Disable function code for each LAM. This allows the LAM to be disabled and the crate demand to be re-enabled immediately by the Demand Handler (see 10.2 below).

#### 10.1 Identification of the source of a Demand

For systems with LAM Graders, the identification is greatly simplified if the bit pattern in the SGL field of the Demand message represents the station number of the module generating the LAM. This facility can be provided by the recommended LAM Grader (see Appendix A).

Systems without LAM Graders require one additional READ operation (Read Local LAM Pattern, see WARNING below) to the appropriate SCC to obtain the same station number information.

In both systems (with or without LAM Graders) further identification of the source of the LAM within the module (LAM at a subaddress, LAM at a bit position, or other non-standard possibilities) can be performed at the system level only by means of tables in the Demand Handler, giving the further access procedure at the module level. The entries in this table can be conveyed from the user program by declaration statements. If this facility is not incorporated in the Demand Handler, the user program itself must perform a search within the module.

#### WARNING:

Modules conforming to EUR 4100e 1969 (gating the L-Signal with Dataway Busy) must not be used in conjunction with SCC-L1 (generating Busy during Read Local LAM Pattern). This problem does not occur with SCC-L2, or if SCC-L1 is used with new modules.

#### 10.2 System response to a Demand

In systems with LAM Graders using the LAM mask register, the system response is to clear a bit in the LAM Grader mask register,

corresponding to the SGL number in the Demand message, thus masking that particular LAM. The LAM Grader can be enabled immediately, so that a new Demand message from a different LAM in the crate can be initiated (see Table 1, mode 1), or Demand message initiation could be enabled after the user has serviced the LAM to avoid nesting interrupt service routines (see Table 1, mode 2).

For some applications the mask operation can be omitted (see Table 1, mode 3); however, a long interrupt service routine may lead to generation of a Hung Demand. Such a Hung Demand must not interrupt the current interrupt service routine, to avoid servicing the same LAM twice (see 10.7 below).

If the Demand Handler finds that no user program is assigned to service the LAM, the LAM should be masked out at the LAM Grader, and an 'unexpected LAM' error message should be generated.

In systems without LAM Graders, the Crate Demand must be disabled until the identified LAMs are cancelled (disabled or cleared) in order to avoid the generation of Hung Demands (see section 10.7). This problem arises because an SCC has only one DMI-line (see EUR 6100e, 1976 / IEEE Std. 595, 1976 section 14.2.4) which may remain activated due to other LAMs which occur before the original LAM has been cancelled.

The disadvantage of disabling the Crate Demand until the corresponding user program has cancelled the LAM (see Table 1, mode 4) can be avoided by disabling the LAM in the module by means of a procedure known to the Demand Handler. This allows the Crate Demand to be re-enabled immediately, and a new Demand message to be generated if further LAM's are present (see Table 1, mode 5). The Demand Handler must know (for example by declarations from the user program) how to disable the LAMs at module level. Modules which do not have a disable LAM feature cannot be serviced by this standard disable procedure in the Demand Handler, so in this case the user program must clear the LAM and re-enable the Crate Demand.

Systems without LAM Graders can only handle unexpected LAM's by disabling all demands from the offending crate. Recovery from this condition is only possible by manual intervention.

In systems with LAM Graders only the expected LAM's are unmasks.

### 10.3 Demand dispatching to the corresponding user program

After the Demand Handler has responded to the LAM so that it does not generate a Hung Demand, the appropriate information has to be passed to the corresponding user program. This can be accomplished via entries in a system table indicating for example the setting of event flags or the activation of user tasks.

#### 10.4 Re-enabling Demand Message Initiation

After servicing a LAM the user program issues a request to re-enable demands from that LAM source.

In systems with LAM Graders, the response to this request depends on the mode of operation. If the mask register is used, the Demand Handler must set the appropriate mask bit (see Table 1, mode 1 and 2). If Demand nesting is not allowed (see 10.2 above) the Demand Handler must also re-enable Demand message initiation (see Table 1, mode 2). If the mask register is not used, the Demand Handler need only re-enable Demand message initiation (see Table 1, mode 3).

In systems without LAM Graders, the Demand Handler may simply re-enable demands in the appropriate SCC, or it may read the Local LAM Pattern. If this is zero, it re-enables crate demands; if it is not zero, it proceeds as if a Demand message had been received (see Table 1, mode 4).

Alternatively, if the system performs the disable LAM function at the module level as described in 10.2 above, the response to the enable demand request is to re-enable the LAM in the module (see Table 1, mode 5). The crate demand will have been re-enabled in response to the Demand message.

#### 10.5 Connection/Disconnection between a LAM and an Interrupt Service Routine

For correct operation, the user program must declare the connection between a LAM and the Interrupt Service routine before the LAM occurs. This allows the Demand Handler to distinguish between expected (declared) and unexpected (undeclared) LAM's.

The connect statement contains the LAM address, and the actions which the Demand Handler must perform on receipt of the corresponding Demand messages (e.g. for some implementations the function codes for Disable/Enable LAM). A disconnect statement from the user program declares the corresponding LAM as 'unexpected'.

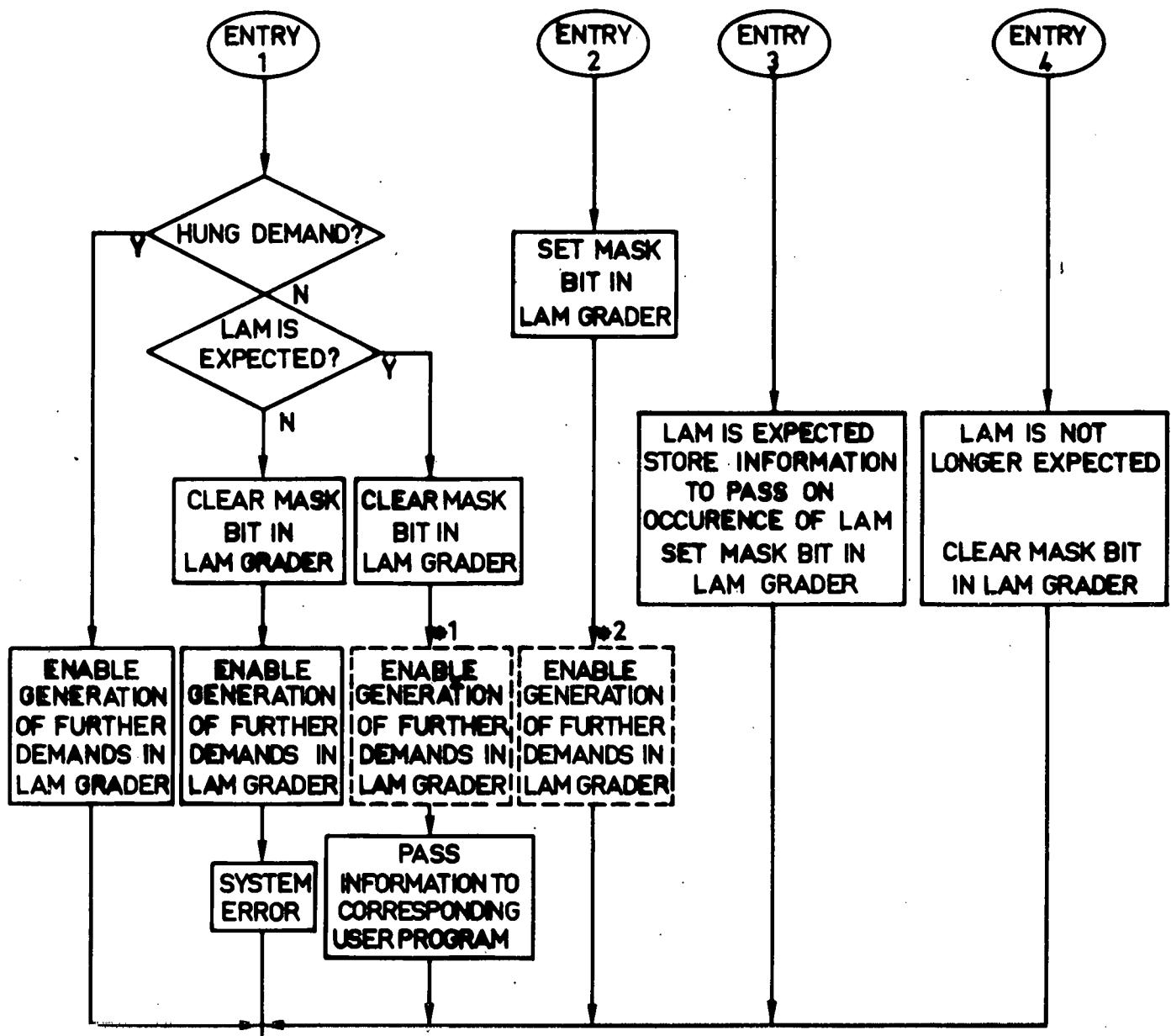

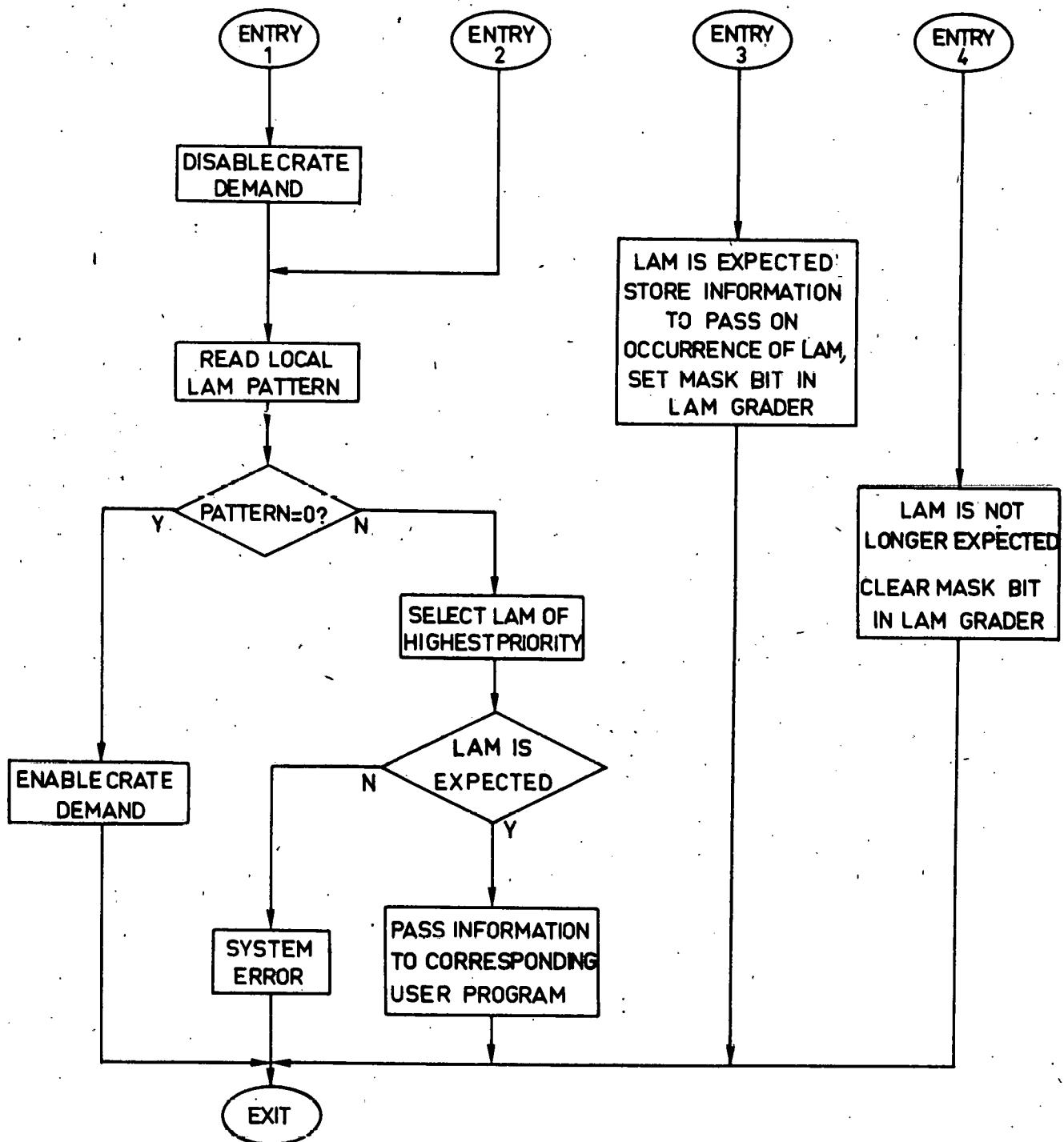

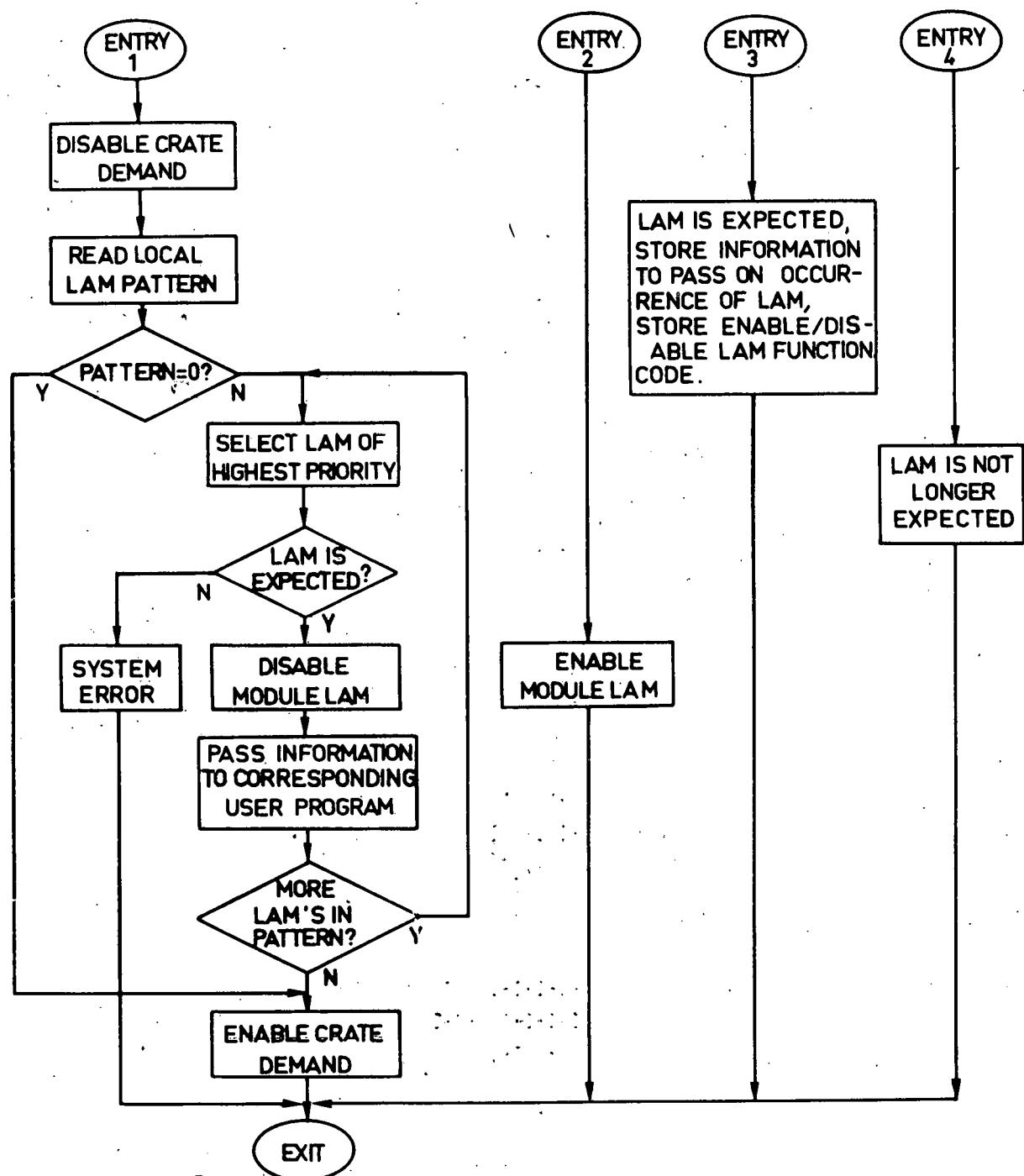

#### 10.6 Explanation of the flow charts 11a to 11c

Three examples of implementations are given in the flow charts 11a to 11c.

The flow chart 11a assumes the use of the recommended LAM Grader (see Appendix A). It offers security since the system has ultimate control of all LAM signals (only those LAMs which are declared in the user program are unmasked).

Systems using LAM Graders can re-enable Demand message generation in two ways:

- As soon as the corresponding bit in the LAM Grader is cleared, the mechanism for generating further Demand messages is enabled;

- Or further Demand message generation is disabled until the user has given the request to re-enable Demand message initiation after the LAM is serviced (see 10.2 above).

The first method allows the generation of further Demand messages from the same crate, even when the original LAM has not been serviced. The second method avoids nesting of interrupt service routines for one crate.

The flow chart 11b is for systems without LAM Graders. To maintain system security the user must ensure that all possible LAM's in a Crate can be serviced, since an unexpected LAM would lock up the whole LAM handling mechanism in a Crate.

The security of the system represented by the flowchart 11c also depends upon the user program servicing all possible LAM's. It is similar to the system represented by 11b, with the additional feature that the Demand Handler disables LAM's directly.

#### 10.7 Hung Demand

The Hung Demand message mechanism is provided to recover a lost Demand. This can occur if a Demand message becomes corrupted, when there cannot be any response to that Demand by the Demand Handler. After a predetermined time, the LAM Grader or the SCC initiates a Hung Demand Message indicating that some LAM is "hanging".

Problems can occur if Hung Demands are not handled correctly. In the following example a LAM is serviced twice - once as the result of handling a Hung Demand and again as the result of a normal Demand message. When LAM 'A' occurs this initiates a Demand Message 'A', but the response to this is too slow and so a Hung Demand message is initiated before the Demand Handler masks LAM 'A' and re-enables Demand message initiation. In the meantime a second demand LAM 'B' has occurred, and Demand Message 'B' is initiated when DMI is re-enabled. The Demand Handler processes this Hung Demand by reading the local LAM pattern, which includes the bit corresponding to LAM 'B'. This information is passed to the user program, which services LAM 'B'. Later, the Demand Handler receives Demand message 'B' and so the same demand is processed again. This problem can be avoided if the action in response to a Hung Demand does not depend on reading the local LAM pattern.

## 10.8 Recovery of lost Demand messages

For handling Demand messages via a LAM Grader, the following features are proposed:

When a normal Demand message (with GL-field < 31) has been generated by an SCC no further normal Demand messages will be initiated by the LAM Grader (described in Appendix A.5) until the initiation of further Demand messages has been re-enabled. The response to a Demand message is to clear the corresponding bit in a LAM mask register (thus disabling the LAM which has caused the Demand message) and to re-enable the initiation of further Demand messages. If an unmasked LAM is present a new Demand message is initiated. Disabling the LAM and enabling further Demand messages may be combined in one CAMAC command or they may be two different CAMAC commands from the Demand Handler to the LAM Grader (see section 10.6 and Appendix A.5).

If a LAM initiates a Demand message and is then not disabled within a predetermined time (given by a Repeat Timer) a Hung Demand message is initiated and a "Hung Demand Transmitted" flag (HDT) is set automatically in the LAM Grader. This flag inhibits the initiation of further normal Demand messages. Only additional Hung Demands may be initiated by the Repeat Timer.

The HDT flag is cleared by a command from the Demand Handler to the LAM Grader (see section 10.6 and Appendix A.5), thereby re-enabling the generation of normal Demand messages. If an unmasked LAM is present, a new Demand message is initiated. BUT NOTE: if the HDT flag is not set when the 'clear HDT flag' command is received, this command must not have any influence on the Demand message initiation. This is because more than one Hung Demand may be initiated in sequence, causing more than one Clear HDT flag instruction from the Demand Handler, but only the first of these clears the flag, and initiates a new normal Demand message if a LAM is present. (If the following clear HDT flag instructions are not ignored, this normal Demand message will be repeated illegally).

### SUMMARY:

The interaction of LAM Grader and Demand Handler is described in section 10.6. If a normal Demand message is lost, the corresponding LAM is not disabled a Hung Demand is initiated. The Demand Handler clears the HDT flag, re-enabling Demand messages. Thus the Demand message corresponding to the "hanging" LAM is repeated.

If a Hung Demand is lost in addition, the Hung Demand is repeated after a time determined by the Repeat Timer.

If a Hung Demand is generated due to overload of the computer, without loss of the normal Demand message, clearing the HDT flag enables the initiation of the next Demand message only, since the unserviced Demand will precede the Hung Demand in the demand queue. Therefore the corresponding LAM will have been masked before the Hung Demand is serviced (see Table 1, mode 1 and 2).

In systems not using the LAM mask register the generation of Hung Demands due to computer overload must be avoided, otherwise the occurrence of one LAM can be transferred to the user program twice. Therefore the user program must have high enough priority to respond to a LAM in time (see Table 1, mode 3).

For handling Demand messages without using LAM Graders the recovery of lost Demand messages is performed by acting on a Hung Demand message in the same manner as on a normal Demand message. No problem of Hung Demands due to overload of the computer arise if the Demand Handler disables the LAM in the module using knowledge of the specific function code (see Table 1, mode 5). In systems where the Demand Handler does not disable the LAM in the module the Demand Handler must have high enough priority to disable the Crate Demand in time (see Table 1, mode 4) to avoid Hung Demands due to computer overload, otherwise the occurrence of one LAM can be transferred to the user program twice.

TABLE 1: PRINCIPLES OF HANDLING INDIVIDUAL DEMANDS

| FACILITIES AND MODES OF OPERATION                    | MODE 1                                                                     | MODE 2                                                                          | MODE 3                          | MODE 4                 | MODE 5                                                             |

|------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------|------------------------|--------------------------------------------------------------------|

|                                                      | WITH LAM-GRADER                                                            |                                                                                 |                                 | WITHOUT LAM-GRADER     |                                                                    |

| ACTIONS AFTER A DEMAND/HUNG DEMAND.                  | MASK REGISTER USED BY OPERATING SYSTEM                                     | MASK REGISTER NOT USED BY OPERATING SYSTEM                                      |                                 | ONLY CRATE DEMAND      | DISABLE/ENABLE LAM AT MODULE LEVEL                                 |

|                                                      | DEMAND MESSAGE INITIATED IMMEDIATELY BY DEMAND HANDLER                     | SUBSEQUENT DEMAND MESSAGES DEFERRED UNTIL THE USER HAS SERVICED THE CURRENT LAM |                                 | DISABLE                |                                                                    |

| ACTION FOR LAM SOURCE IDENTIFICATION, BY DMD HANDLER | NO ACTION NEEDED (IDENTIFICATION IN DEMAND MESSAGE)                        |                                                                                 |                                 | READ LOCAL LAM PATTERN |                                                                    |

| RESPONSE TO HUNG DMD, BY DMD HANDLER                 | UNLOCK LAM GRADER BY XEQ COMMAND                                           |                                                                                 |                                 | DISABLE CRATE DEMAND   | DISABLE CRATE DEMAND + DISABLE LAM IN MODULE + ENABLE CRATE DEMAND |

| RESPONSE TO A REGULAR DEMAND, BY DEMAND HANDLER      | MASK THE LAM IN LAM GRADER + REENABLE DEMAND INITIATION                    | MASK THE LAM IN THE LAM GRADER                                                  | —                               |                        |                                                                    |

| DISPATCH DMD TO USER BY DEMAND HANDLER               | EG. : SET EVENT FLAG, ACTIVATE TASK                                        |                                                                                 |                                 |                        |                                                                    |

| USER INTERRUPT SERVICE                               | EVENTUAL SEARCH FOR THE LAM IN THE MODULE, IF NEEDET + CLEAR LAM IN MODULE |                                                                                 |                                 |                        |                                                                    |

| REENABLE DMD MESSAGE INITIATION BY REQUEST FROM USER | UNMASK THE LAM IN LAM GRADER                                               | UNMASK THE LAM IN THE LAM GRADER + REENABLE DMD MESSAGE INITIATION              | REENABLE DMD MESSAGE INITIATION | REENABLE CRATE DMD     | REENABLE LAM IN MODULE                                             |

## 11. System Services

In addition to the user (application) program and the Serial Driver, facilities referred to here as the 'System Services' are required. They may be parts of an operating system, or could be partly incorporated in the user program in applications without an operating system. The System Services are implementation dependent, therefore no detailed descriptions are given, only principles are discussed.

The following are the main facilities already listed in section 6.

### - Queue

To provide the flexibility of asynchronous input/output together with the execution of normal instructions, the system must contain an algorithm to manage queues where device handler requests are buffered.

### - CAMAC Address Check

In the case of CAMAC, it is good practice to perform address checks to increase system reliability as far as possible. In systems with static addresses at run time the address check could be done during assembly. In systems that allow dynamic address modification, these checks must be performed at run-time, at the expense of execution speed of the program.

A reasonable address check is a plausibility check of the CAMAC address, i.e. whether the CAMAC C,N,A,F lies in the permissible range.

### - Data Buffer Address Check

Another check is to test whether the user buffer address lies in the appropriate data space (memory protection facility).

### - CAMAC Device Protection Against Unauthorized User Access

To enable the System Services to block illegal accesses to CAMAC devices, the user program must declare the CAMAC space belonging to its corresponding process.

### - Response to an event representing a LAM or an error