# CAT: A Computer Code for the Automated Construction of Fault Trees

---

NP-705

Research Project 297-1

Interim Report, March 1978

Prepared by

School of Engineering and Applied Science

UNIVERSITY OF CALIFORNIA

Chemical, Nuclear and Thermal Engineering Department

Los Angeles, California 90024

Principal Investigators

G. E. Apostolakis

S. L. Salem

J. S. Wu

RECEIVED MN ONLY

RECORDED IN THIS REPORT ARE ILLLEGIBLE. IT

IS RECOMMENDED THAT THE BEST AVAILABLE

COPY BE PROVIDED TO THE BROADEST POSSIBLE AVAIL-

ABILITY.

Prepared for

Electric Power Research Institute

3412 Hillview Avenue

Palo Alto, California 94304

EPRI Project Manager

Boyer B. Chu

Nuclear Power Division

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

---

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

#### LEGAL NOTICE

This report was prepared by the University of California, Los Angeles (UCLA), as an account of work sponsored by the Electric Power Research Institute, Inc. (EPRI). Neither EPRI, members of EPRI, UCLA, nor any person acting on behalf of either: (a) makes any warranty or representation, express or implied, with respect to the accuracy, completeness, or usefulness of the information contained in this report, or that the use of any information, apparatus, method, or process disclosed in this report may not infringe privately owned rights; or (b) assumes any liabilities with respect to the use of, or for damages resulting from the use of, any information, apparatus, method, or process disclosed in this report.

## FOREWORD

Recent attempts have been made to develop an automated algorithm for constructing the logic models of fault trees. In a previous report, NP-288, a decision table method was introduced and applied to model component behavior. This report is an extension of report NP-288. It presents the application aspect of the decision table method for fault tree construction. Several nuclear subsystems are analyzed to demonstrate various usages of the CAT computer code. The report is also intended to serve as a CAT Code Users Manual; the code may be obtained from Electric Power Software Center.

System reliability analysis has been increasingly recognized as an integral part of design safety evaluations for nuclear power generation plants. Fault and event tree analysis has been extensively applied to quantify the systems and subsystems reliability both by the industry and regulatory agencies. The analysis generally involves the construction and evaluation of system logic models which describe various interconnections among components and their operation requirements. Several computer codes have been developed for the numerical evaluation of a given logic model. Model construction has still remained a manual task which usually contributes the bulk of time to probabilistic system analysis. The objectives of this automated fault tree construction could perhaps speed up the entire reliability analysis process. Several other concepts have been examined for computerized fault tree construction; it appears that the CAT code approach could provide a more adequate modeling capability to nuclear systems and subsystems.

Boyer B. Chu

Project Manager

Nuclear Safety & Analysis Dept.

## ABSTRACT

This report presents a computer code, CAT (Computer Automated Tree), which applies decision table methods to model the components behavior for systematic construction of fault trees. The decision tables for some commonly encountered mechanical and electrical components are developed; two nuclear subsystems, a Containment Spray Recirculation System and a Consequence Limiting Central Systems, are analyzed to demonstrate the applications of CAT code.

## TABLE OF CONTENTS

|                                                                             | Page |

|-----------------------------------------------------------------------------|------|

| CHAPTER 1. INTRODUCTION . . . . .                                           | 1    |

| CHAPTER 2. BASIC OPERATION OF THE CAT CODE . . . . .                        | 4    |

| 2.1 Terminology and Basic Concepts . . . . .                                | 4    |

| 2.2 Input Data . . . . .                                                    | 9    |

| 2.2.1 Outline of Input Data Organization . . . . .                          | 9    |

| 2.2.2 Data Deck Setup and General Input Considerations . . . . .            | 10   |

| 2.2.3 Program Control Data . . . . .                                        | 13   |

| 2.2.4 Library Data . . . . .                                                | 17   |

| 2.2.5 Component Cards . . . . .                                             | 18   |

| 2.2.6 Top Event Definition . . . . .                                        | 19   |

| 2.2.7 Boundary Conditions . . . . .                                         | 20   |

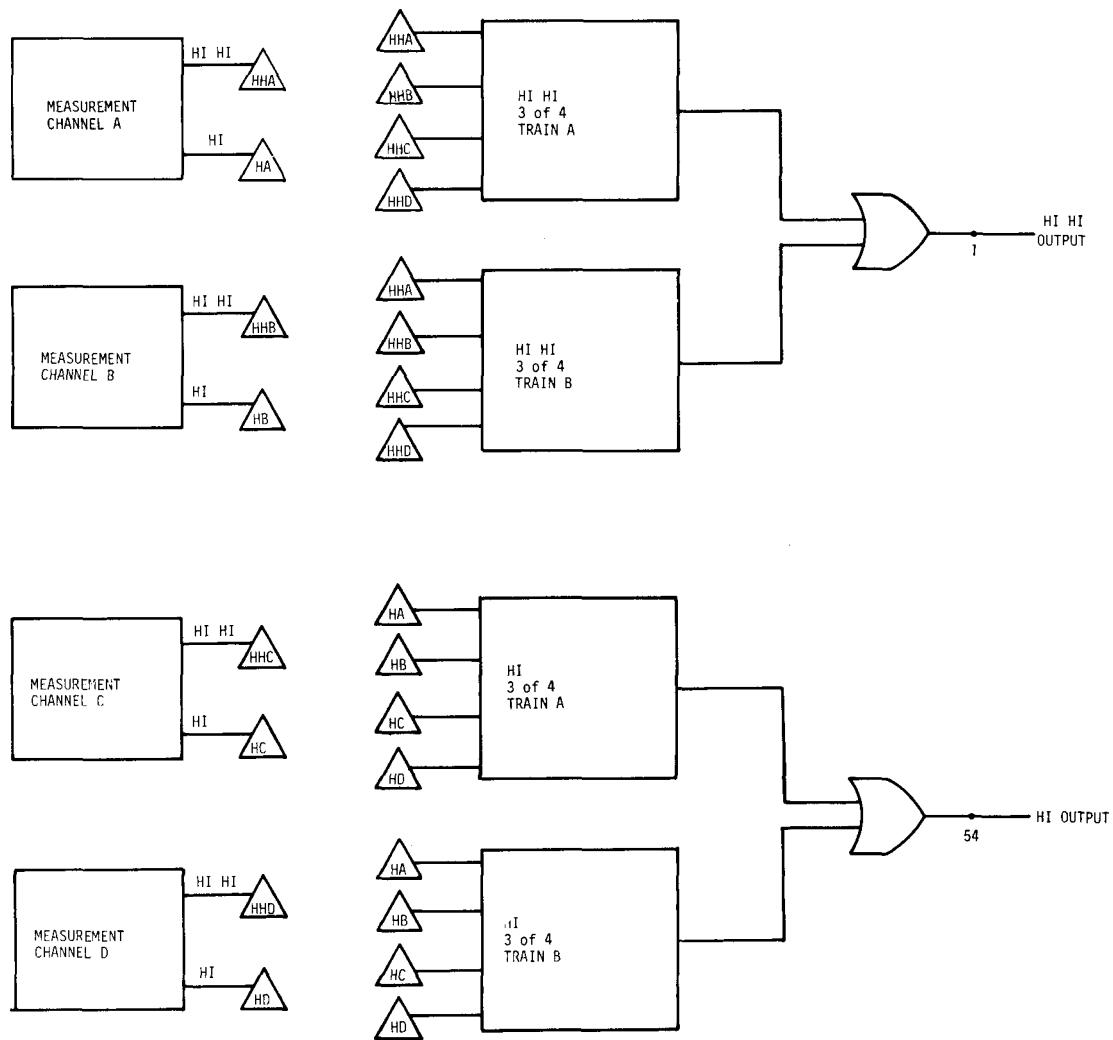

| 2.2.8 Failure and Repair Data . . . . .                                     | 21   |

| 2.2.9 Multiple Jobs . . . . .                                               | 23   |

| 2.3 CAT Output . . . . .                                                    | 25   |

| CHAPTER 3. DEVELOPMENT OF DECISION TABLES . . . . .                         | 27   |

| 3.1 Introduction . . . . .                                                  | 27   |

| 3.2 Inductive Method of Decision Table Development . . . . .                | 28   |

| 3.3 Deductive Method of Decision Table Development . . . . .                | 32   |

| 3.4 The Use of Decision Tables in the Construction of Fault Trees . . . . . | 35   |

| CHAPTER 4. APPLICATIONS . . . . .                                           | 37   |

| 4.1 Containment Spray Recirculation System (CSRS) . . . . .                 | 37   |

| 4.1.1 Description of CSRS . . . . .                                         | 37   |

| 4.1.2 TOP Event and Preliminary Considerations . . . . .                    | 39   |

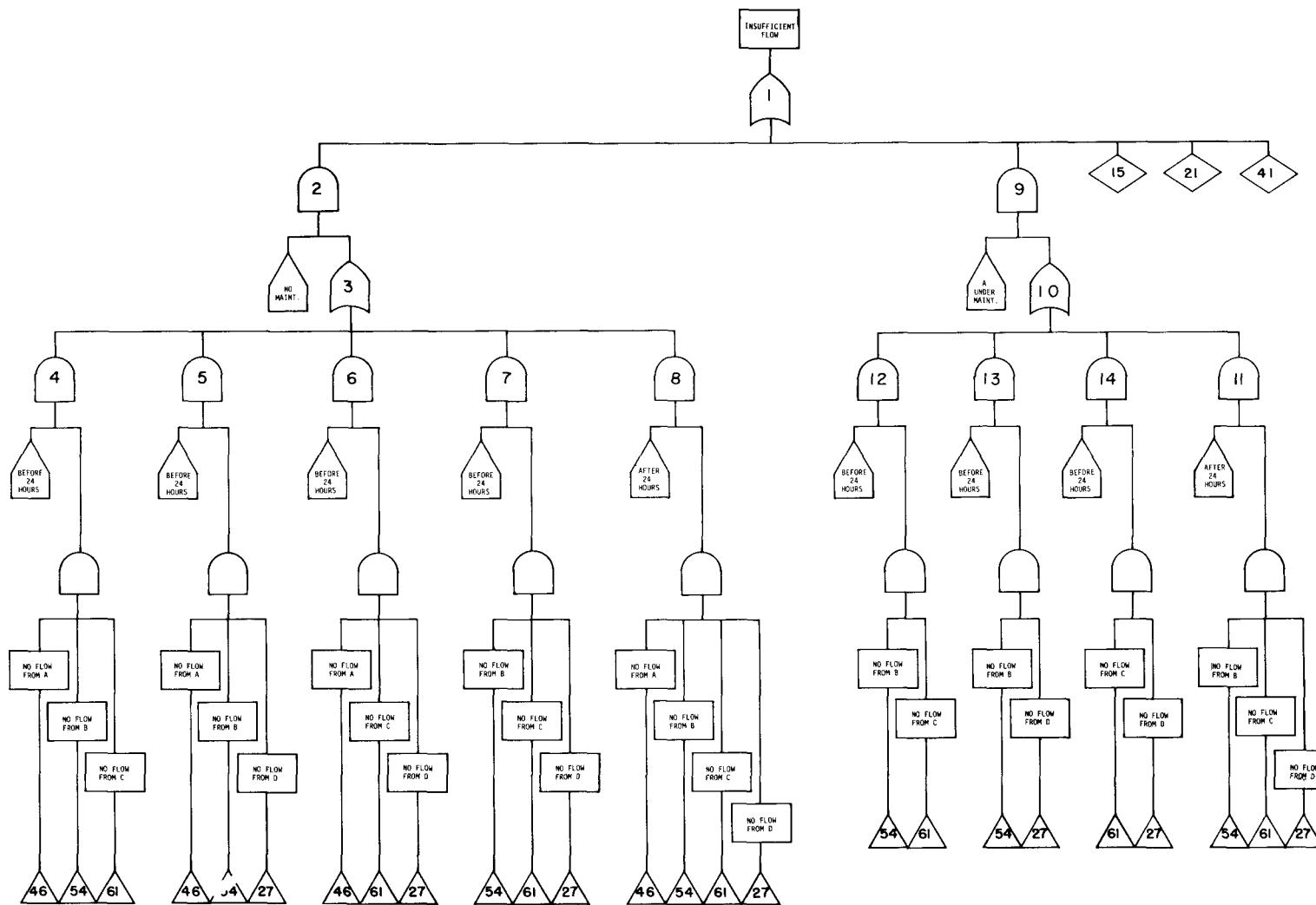

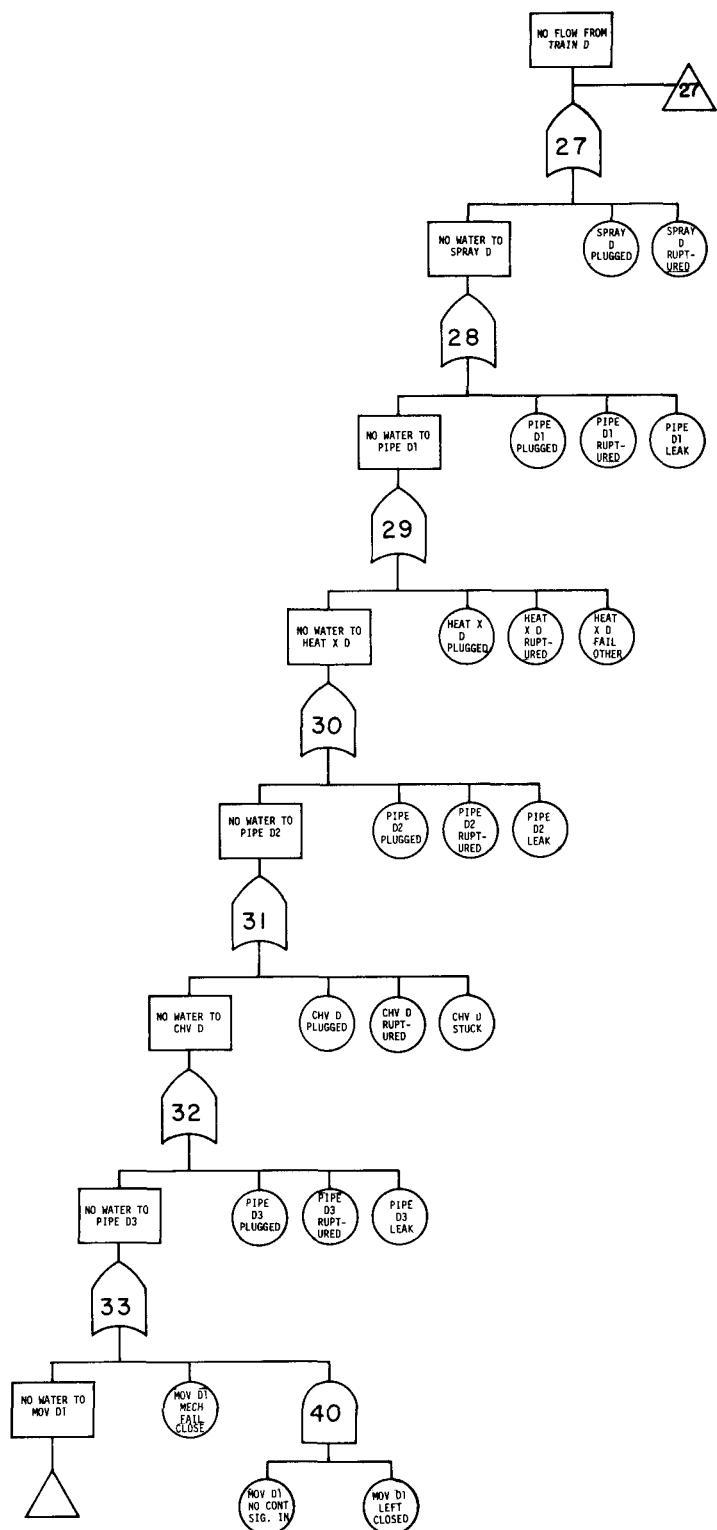

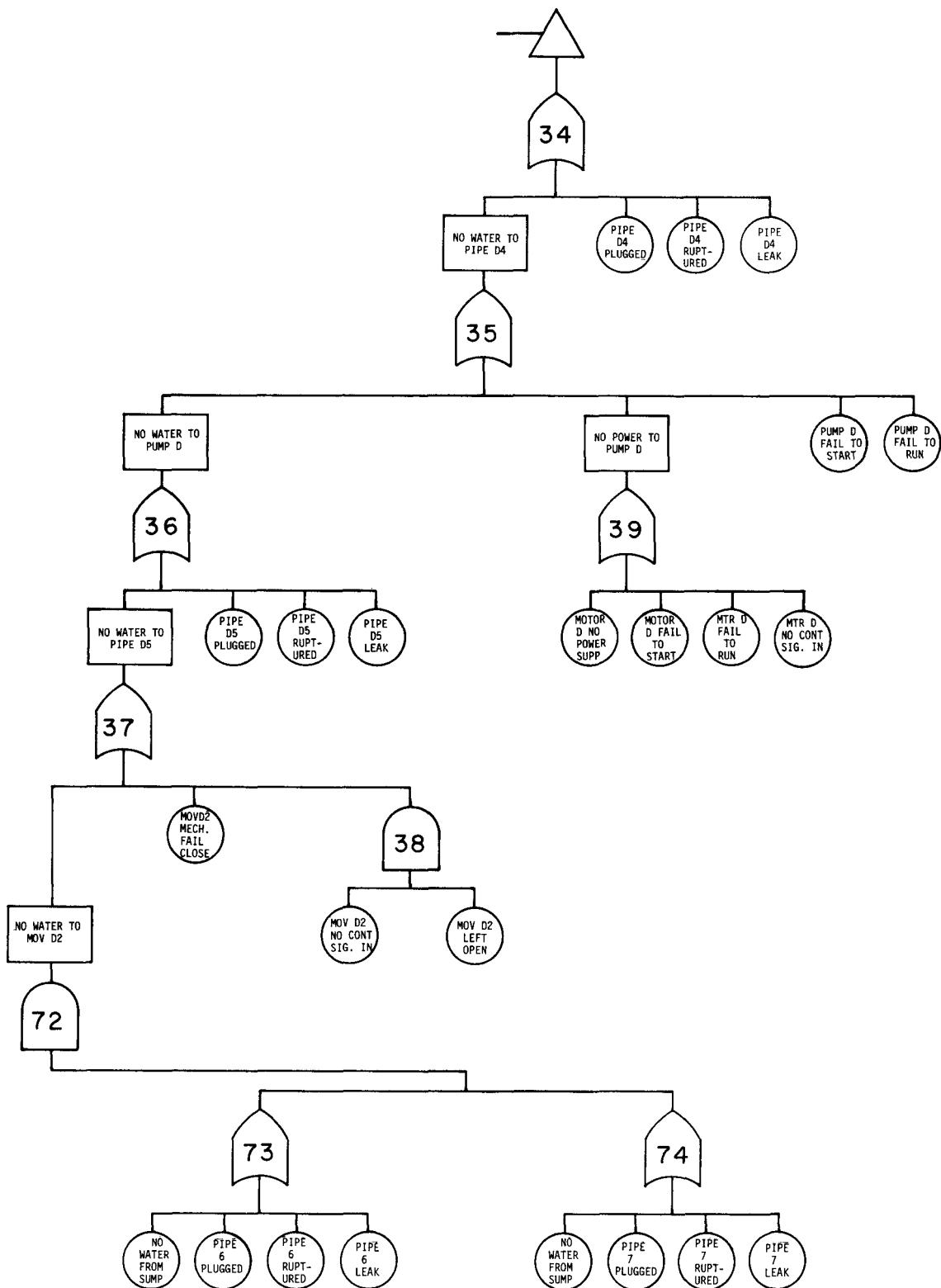

| 4.1.3 Discussion of Fault Tree . . . . .                                    | 41   |

| 4.2 Consequence Limiting Control System (CLCS) . . . . .                    | 46   |

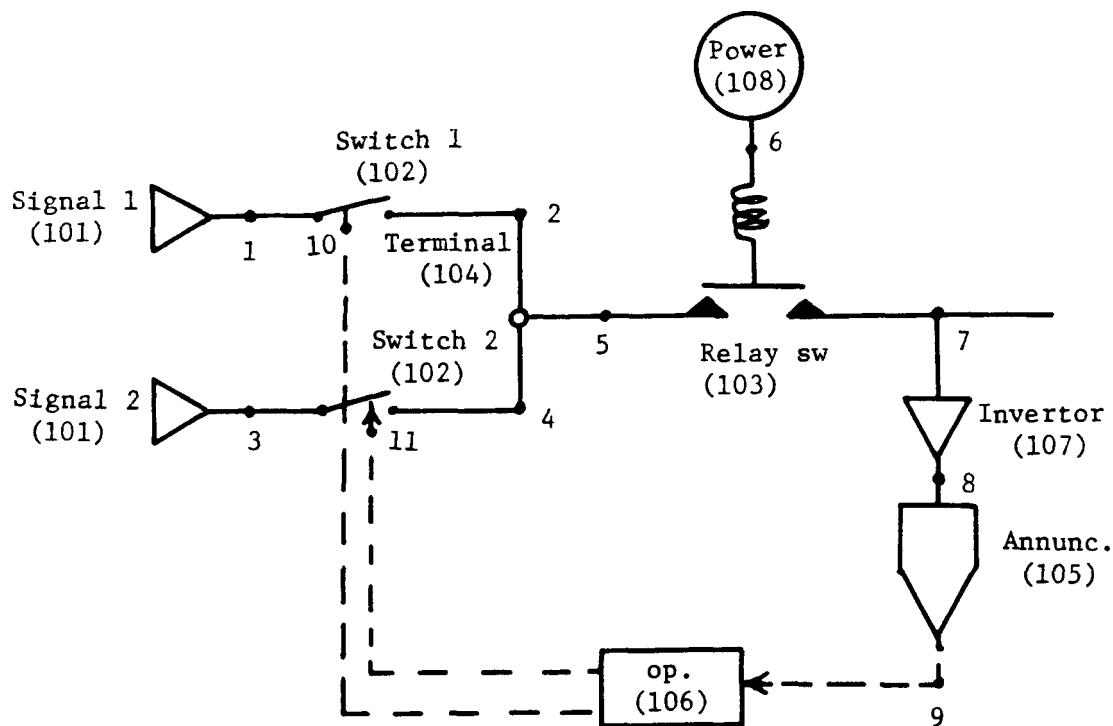

| 4.2.1 Description of CLCS . . . . .                                         | 46   |

| 4.2.2 Top Event and Preliminary Considerations . . . . .                    | 52   |

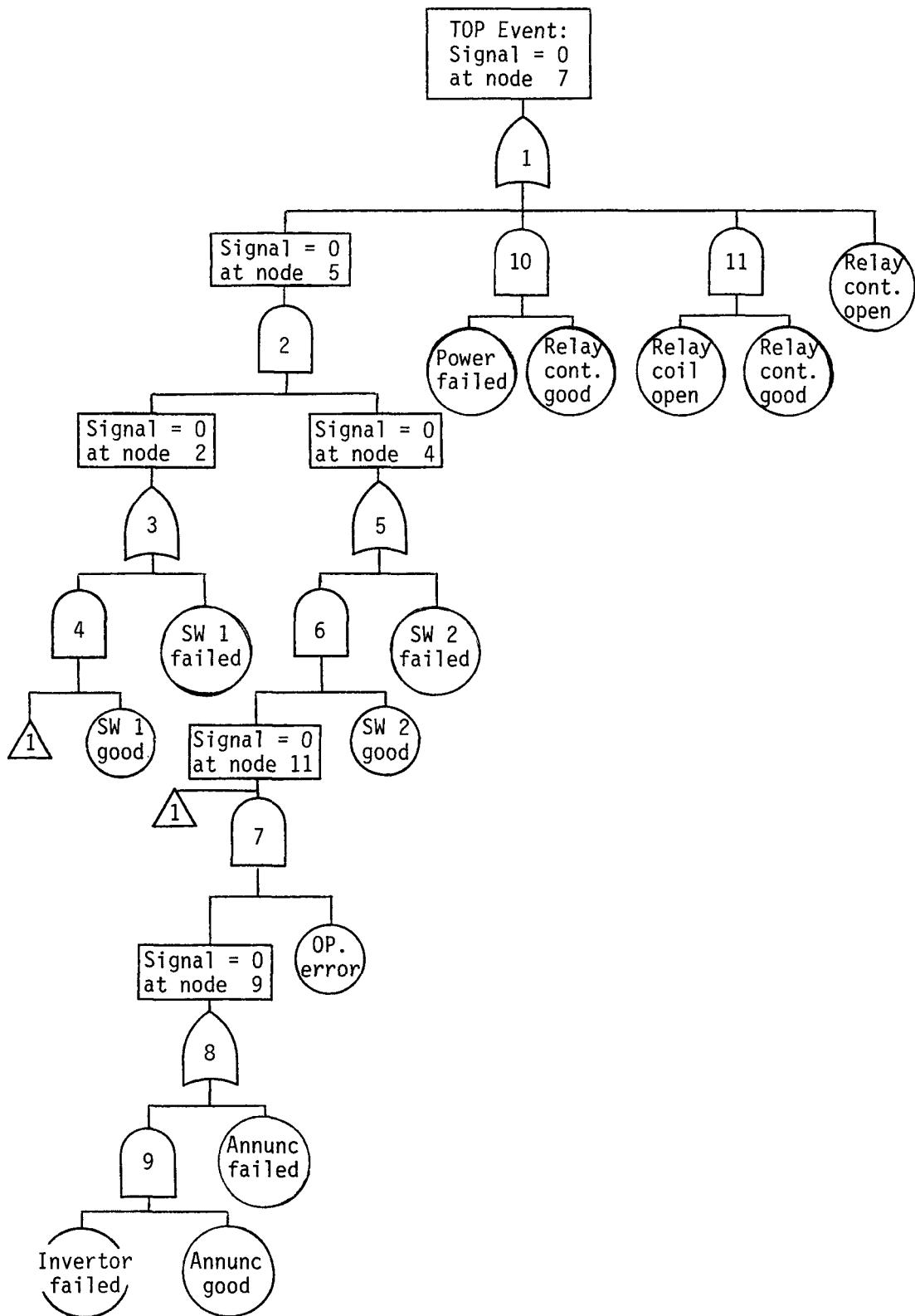

| 4.2.3 Discussion of Fault Tree . . . . .                                    | 56   |

| CHAPTER 5. CONCLUSIONS . . . . .                                            | 62   |

| REFERENCES . . . . .                                                        | 63   |

## TABLE OF CONTENTS (Continued)

|                                                                      | <i>Page</i> |

|----------------------------------------------------------------------|-------------|

| <b>APPENDIX A. CODE STRUCTURE AND SUBROUTINE FUNCTIONS . . . . .</b> | <b>64</b>   |

| A.1 Code Structure . . . . .                                         | 64          |

| A.2 System and Component Node Organization . . . . .                 | 67          |

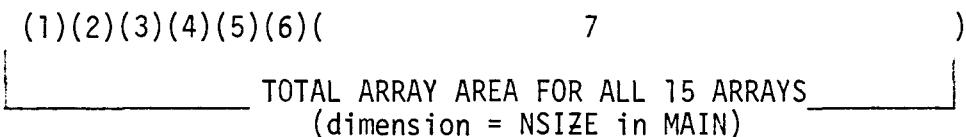

| A.3 MAIN Program and Program Dimensioning . . . . .                  | 69          |

| A.4 Subroutine DRIVER and Sub-Array Allocation . . . . .             | 71          |

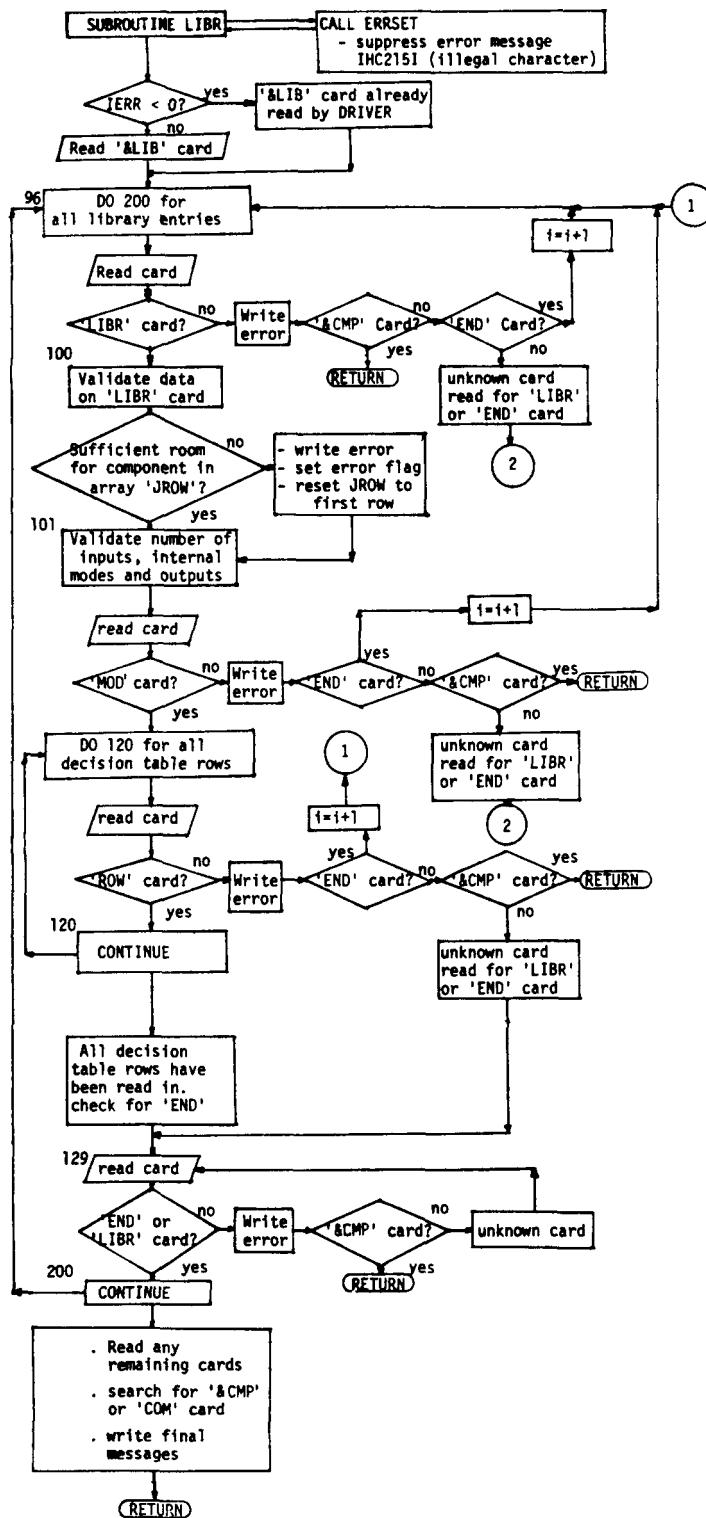

| A.5 Subroutine LIBR . . . . .                                        | 77          |

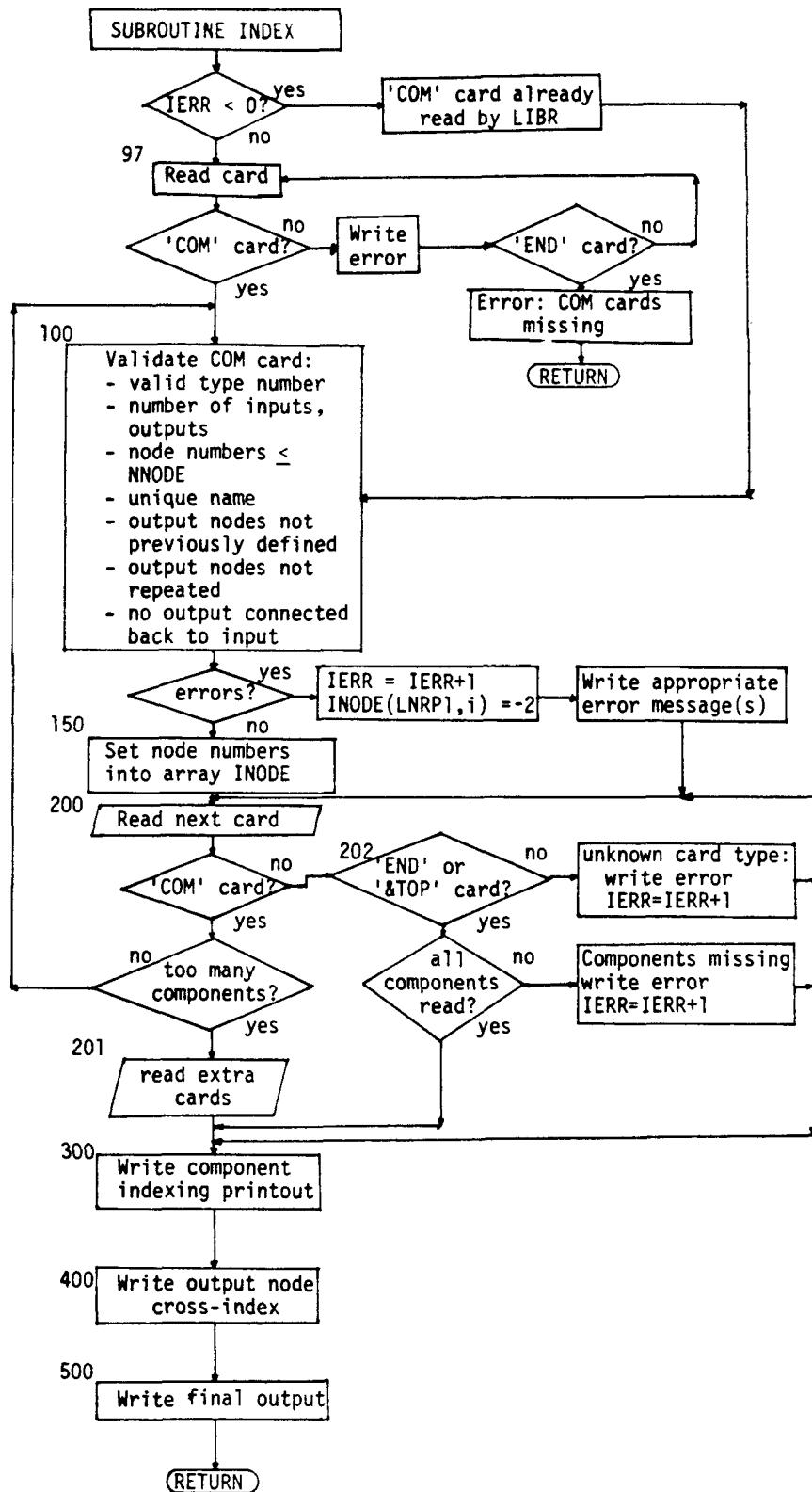

| A.6 Subroutine INDEX . . . . .                                       | 80          |

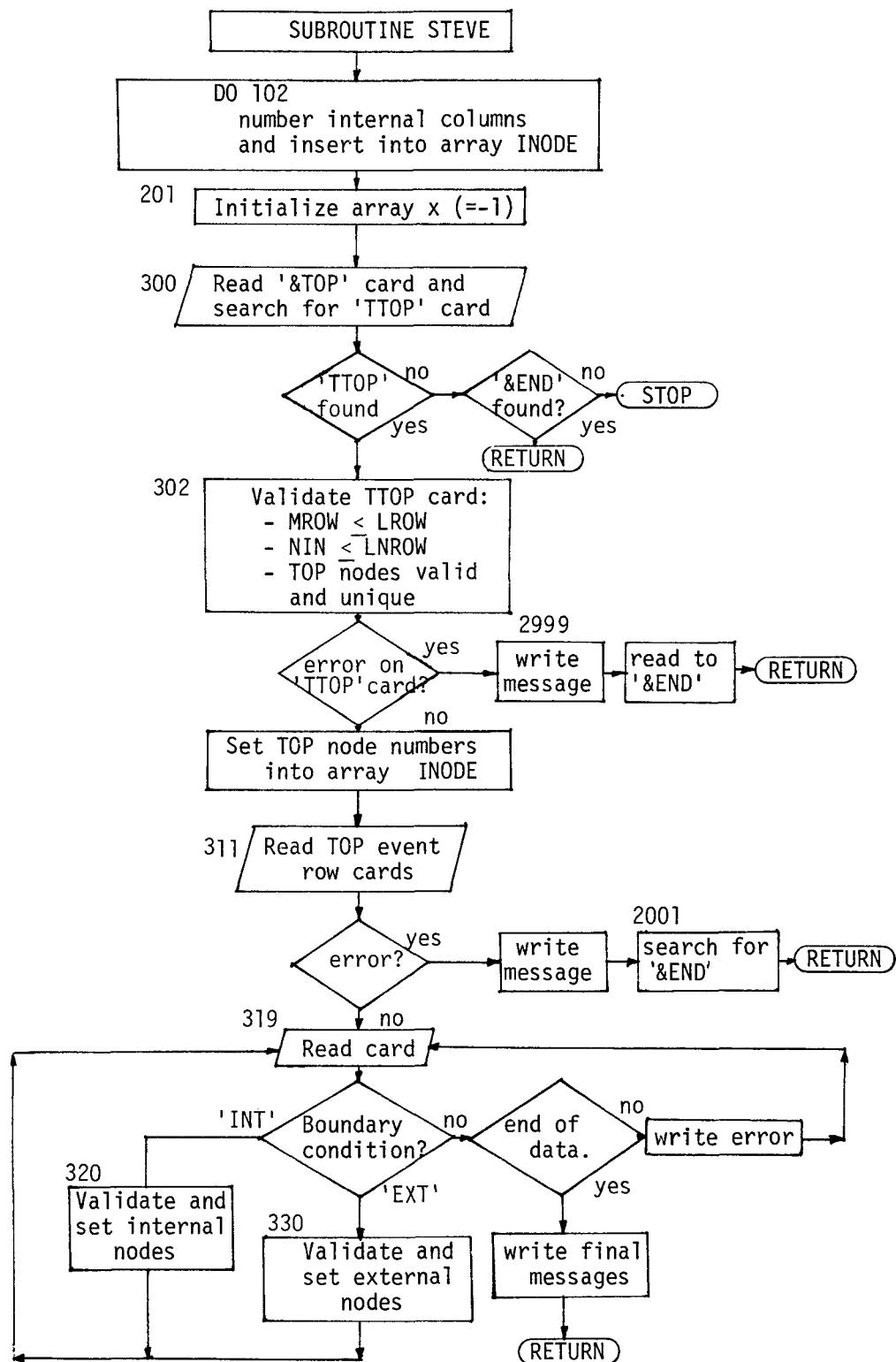

| A.7 Subroutine STEVE . . . . .                                       | 84          |

| A.8 Subroutine DO IT . . . . .                                       | 89          |

| A.8.1 Gate Construction . . . . .                                    | 89          |

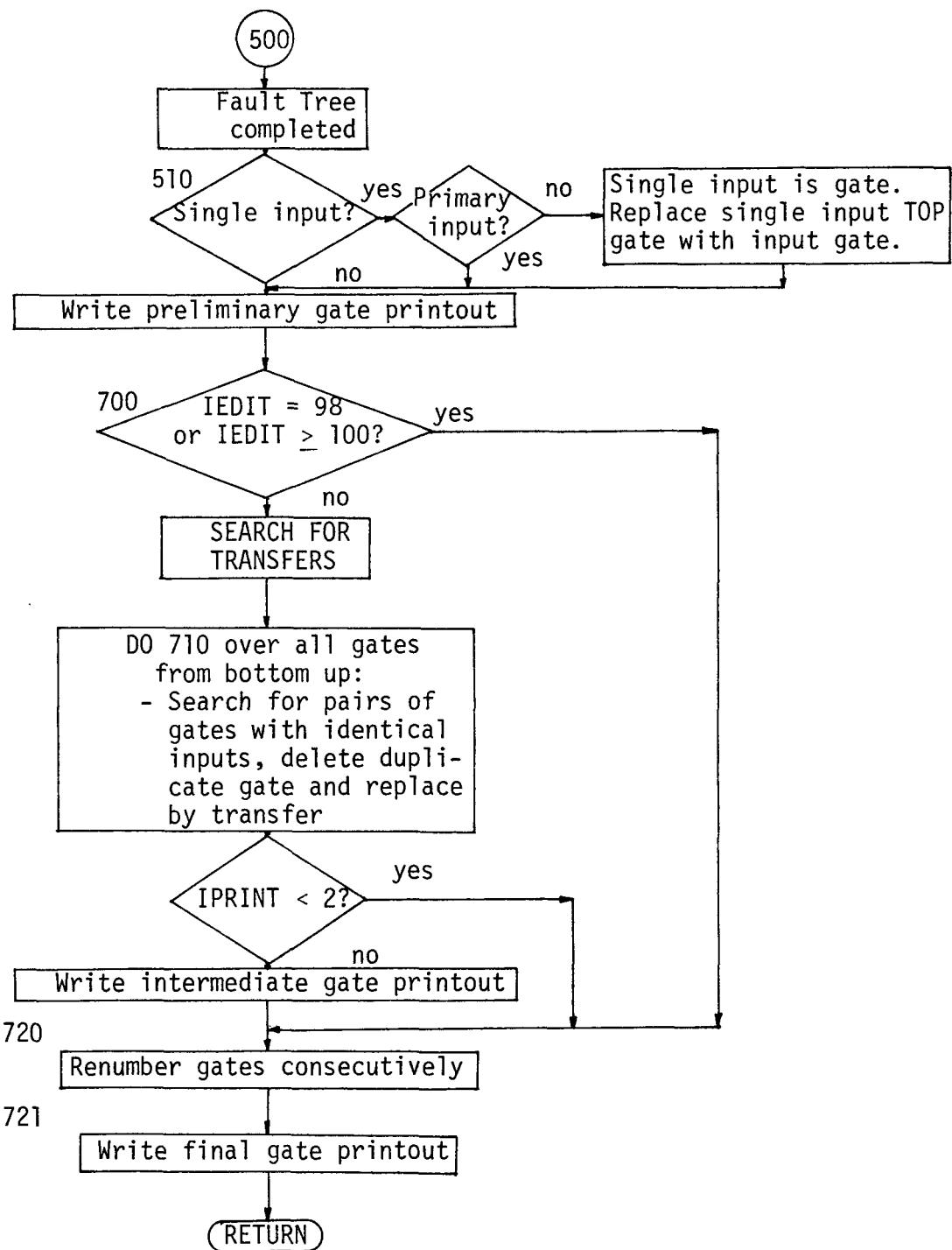

| A.8.2 Intermediate Editing . . . . .                                 | 96          |

| A.8.3 Final Editing . . . . .                                        | 103         |

| A.8.4 Error Messages from DO IT . . . . .                            | 105         |

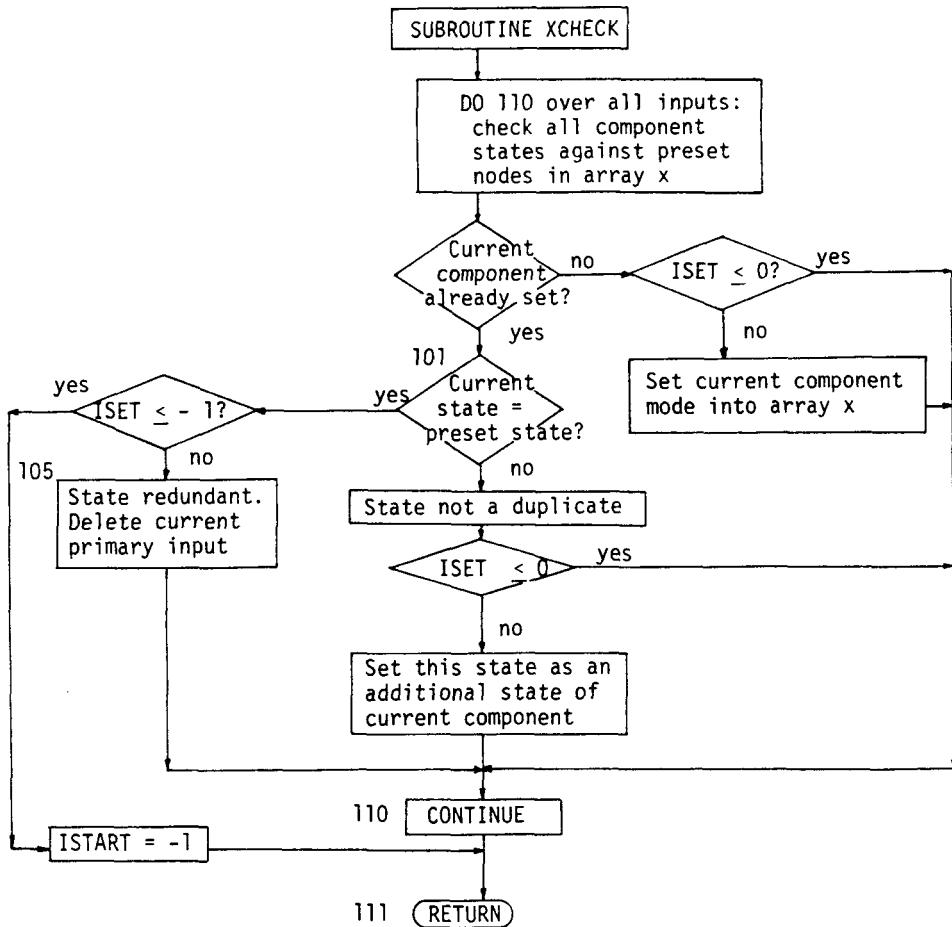

| A.9 Subroutine XCHECK . . . . .                                      | 107         |

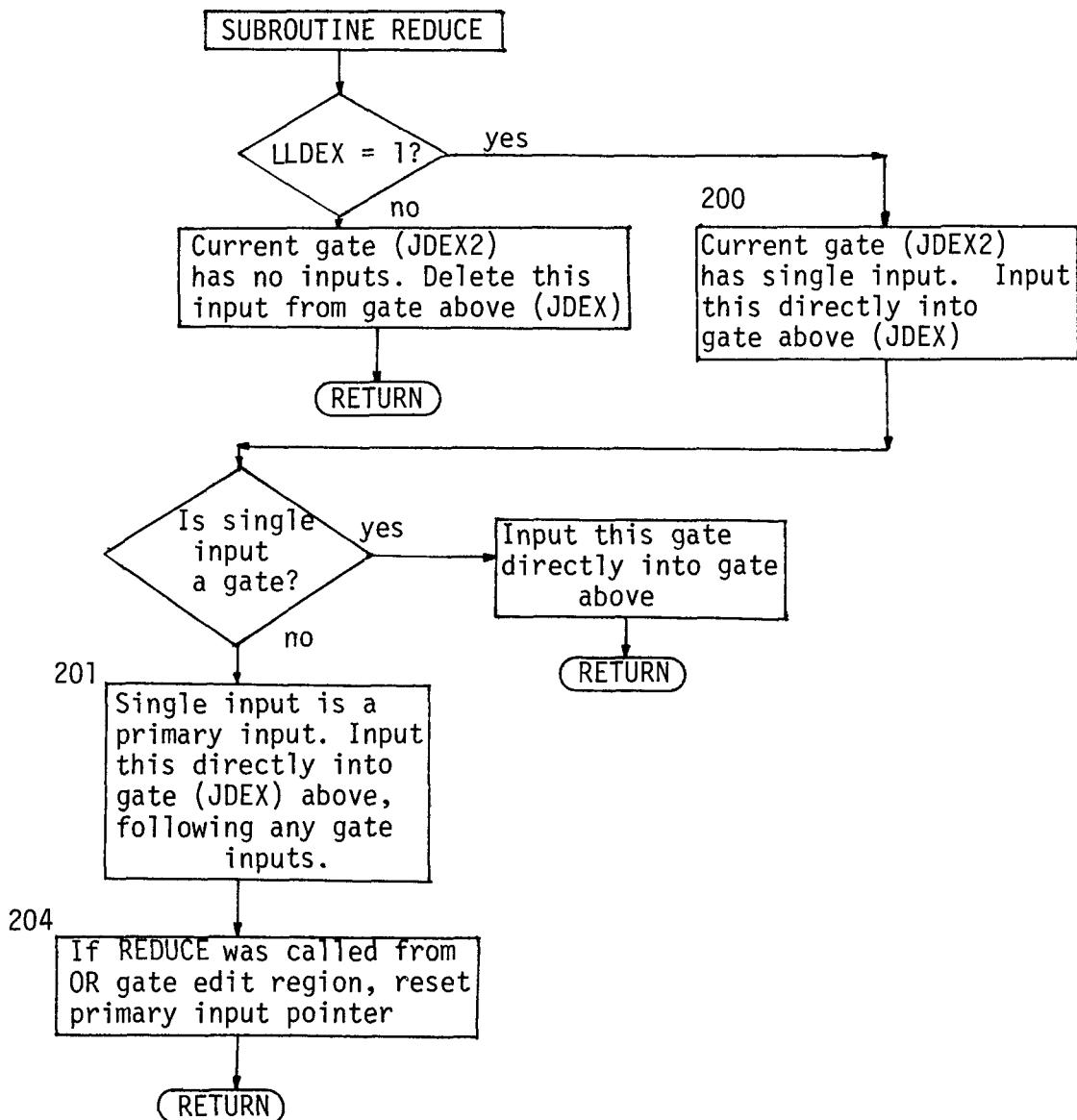

| A.10 Subroutine REDUCE . . . . .                                     | 110         |

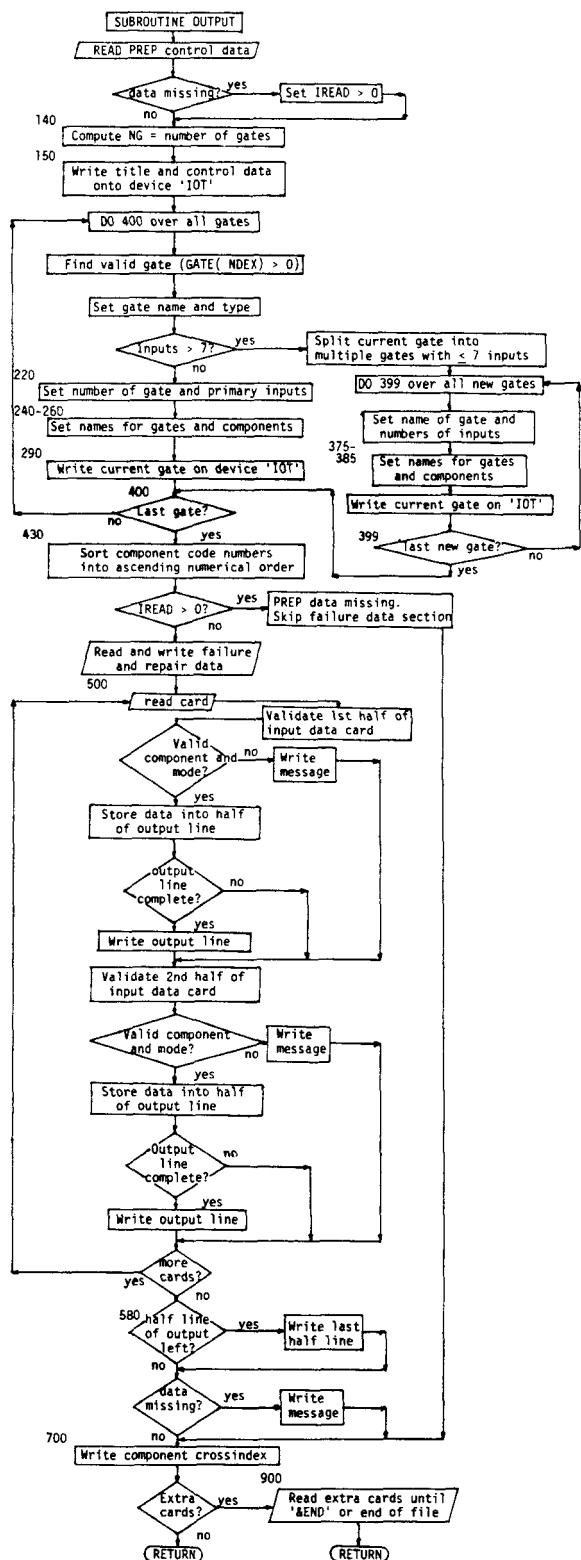

| A.11 Subroutine OUTPUT . . . . .                                     | 112         |

| References . . . . .                                                 | 118         |

| <b>APPENDIX B. DECISION TABLE MODELS . . . . .</b>                   | <b>119</b>  |

| References . . . . .                                                 | 130         |

| <b>APPENDIX C. SAMPLE CASE . . . . .</b>                             | <b>131</b>  |

| References . . . . .                                                 | 141         |

| <b>APPENDIX D. SAMPLE INPUT . . . . .</b>                            | <b>142</b>  |

| <b>APPENDIX E. SAMPLE OUTPUT . . . . .</b>                           | <b>147</b>  |

| References . . . . .                                                 | 154         |

| <b>APPENDIX F. PROGRAM LIST FOR CAT . . . . .</b>                    | <b>177</b>  |

## LIST OF FIGURES

|                                                                                               | Page |

|-----------------------------------------------------------------------------------------------|------|

| Figure 1. Mini-Fault/Success Tree I for Pump . . . . .                                        | 34   |

| Figure 2. Mini-Fault/Success Tree II for Pump . . . . .                                       | 34   |

| Figure 3. Simplified Flow Diagram for the<br>Containment Spray Recirculation System . . . . . | 38   |

| Figure 4. Upper Level Structure of Fault Tree for CSRS . . . . .                              | 42   |

| Figure 5. Development of Lower Events for CSRS<br>Fault Tree . . . . .                        | 44   |

| Figure 6. CLCS Simplified Diagram (5) . . . . .                                               | 48   |

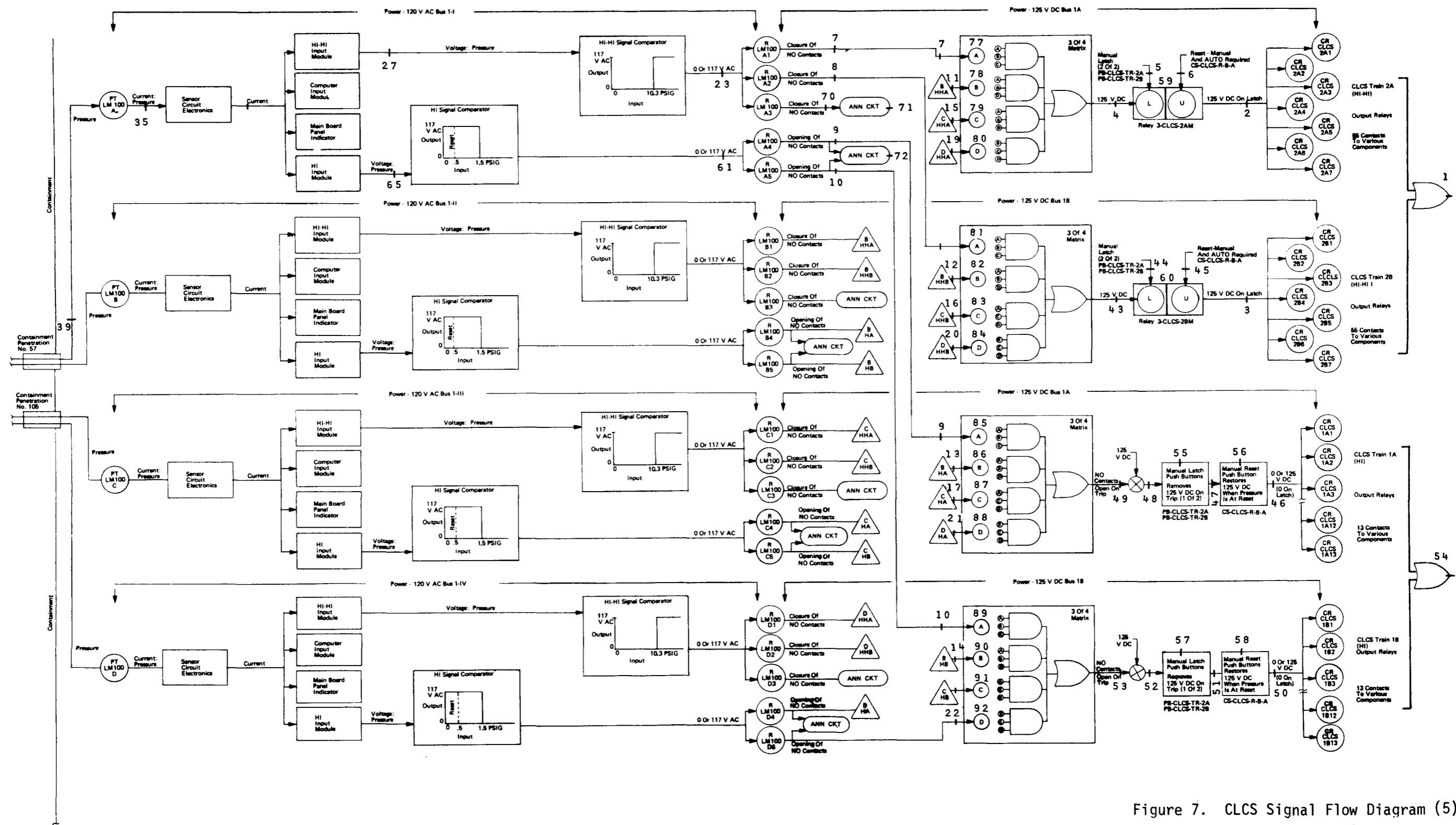

| Figure 7. CLCS Signal Flow Diagram (5) . . . . .                                              | 49   |

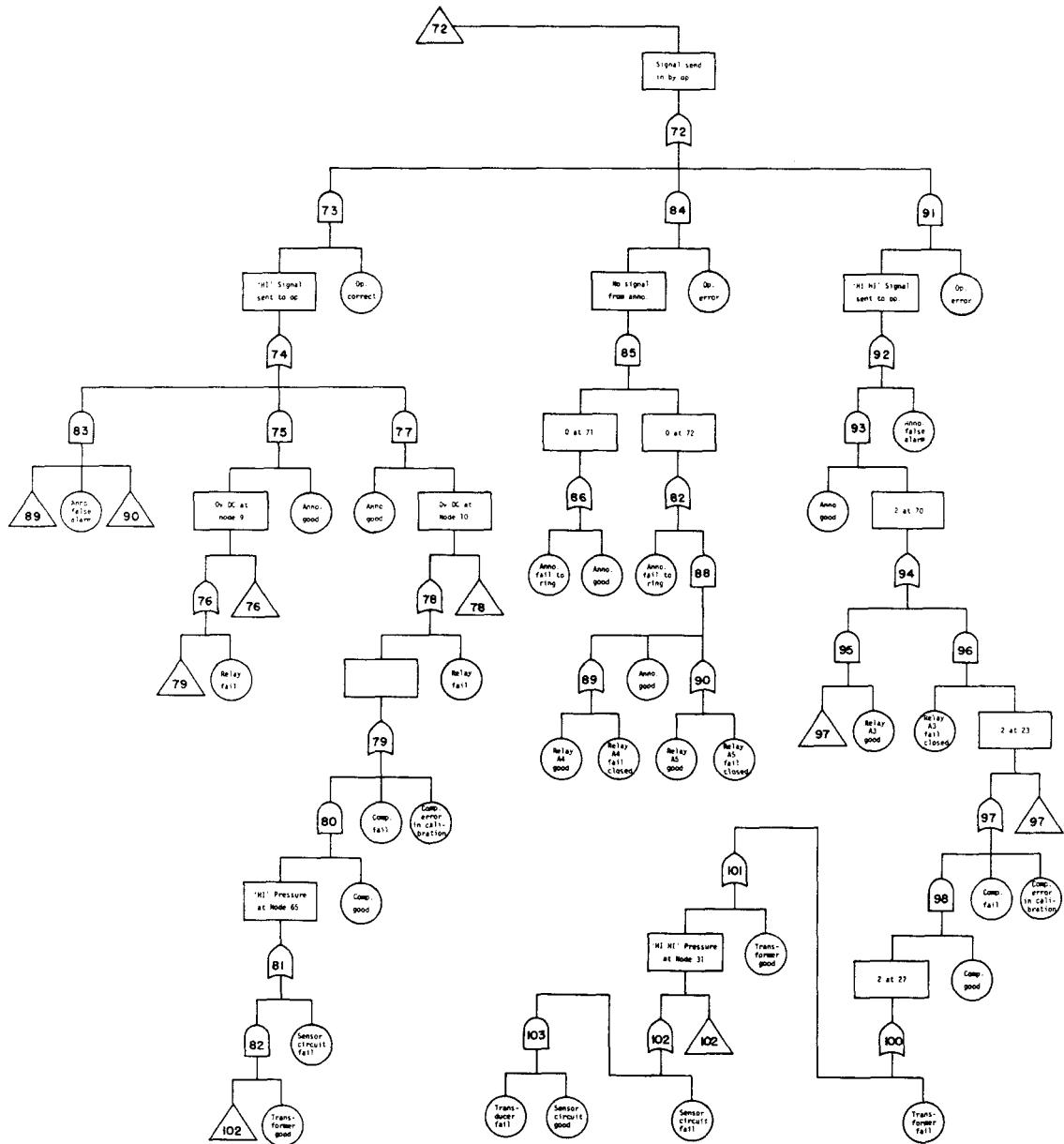

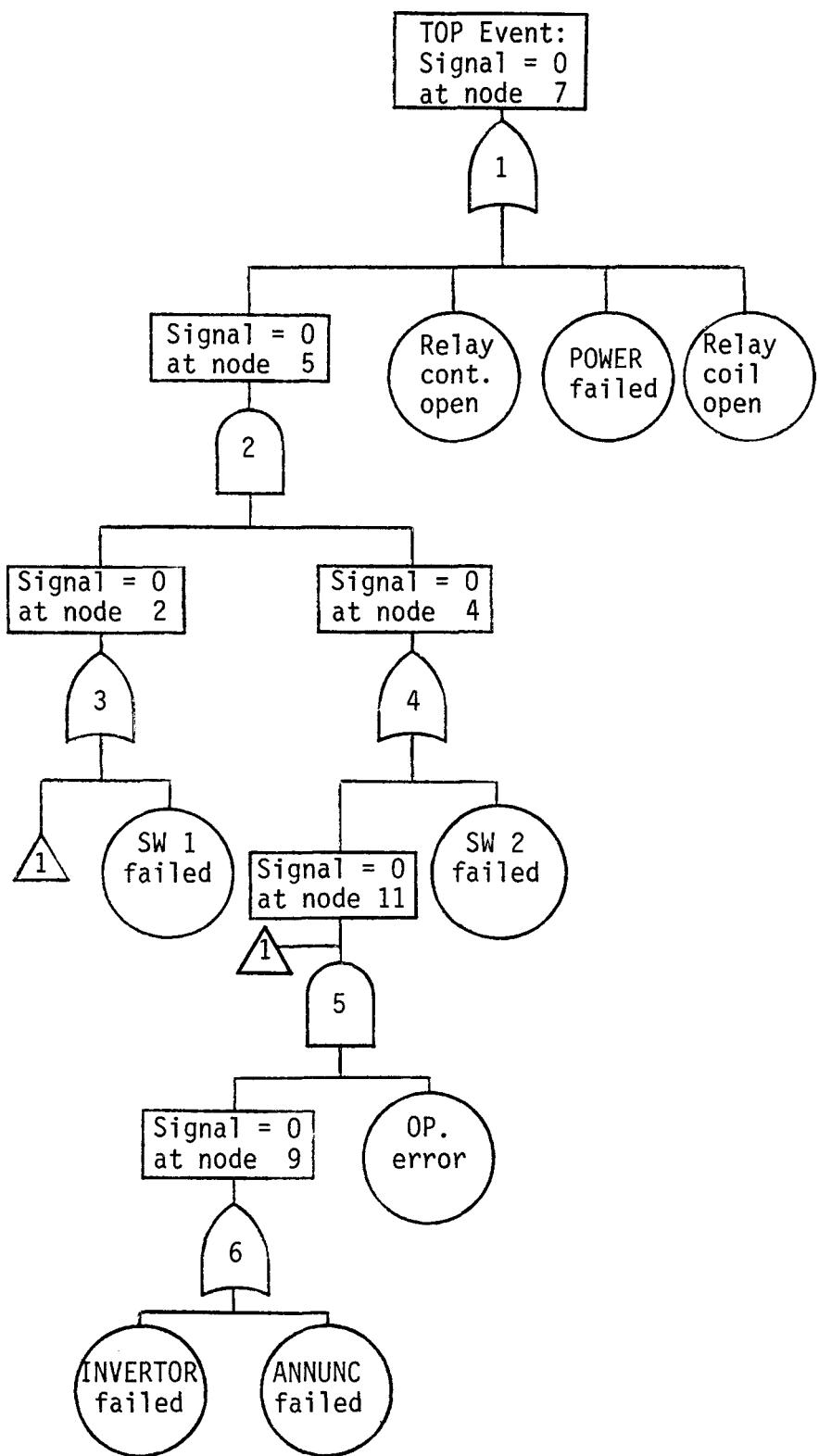

| Figure 8. Fault Tree of Consequence Limiting<br>Control System . . . . .                      | 59   |

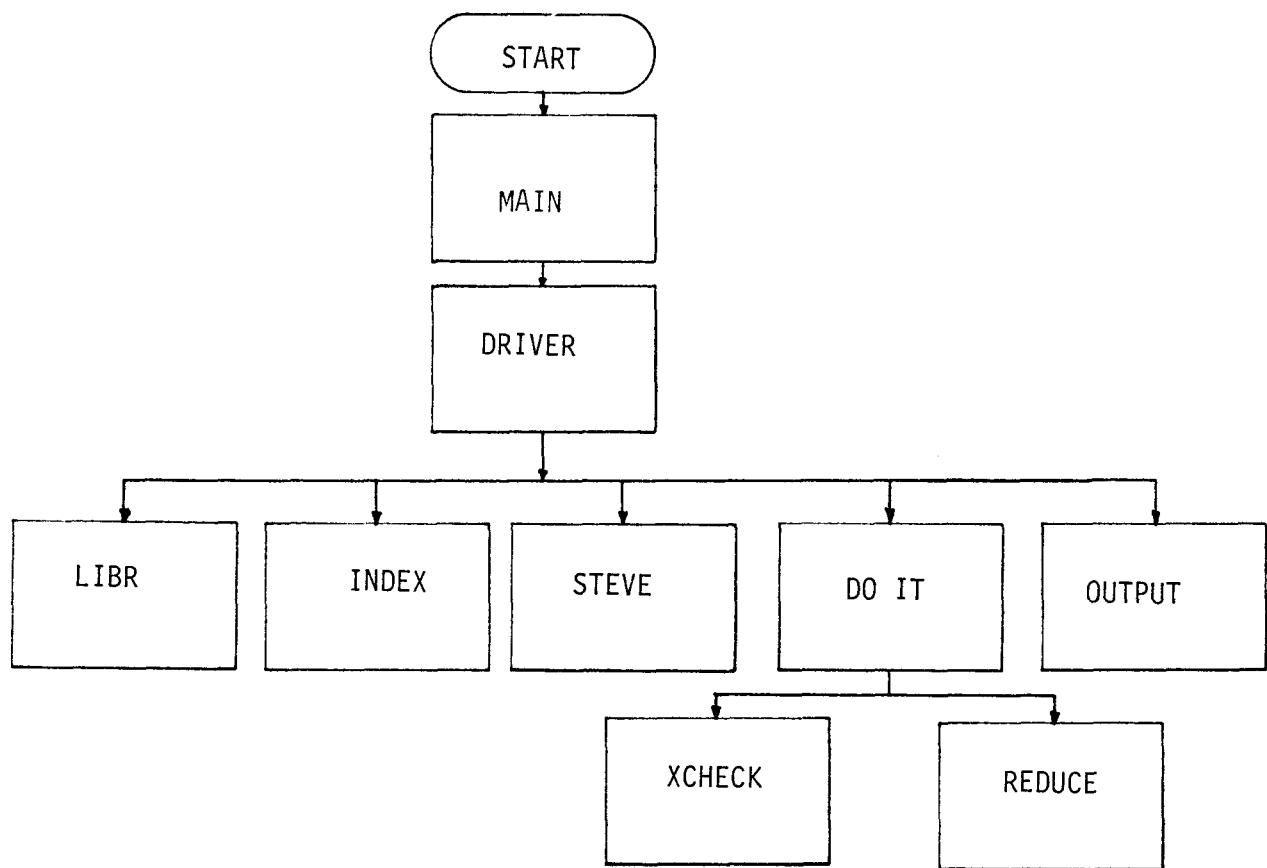

| Figure A-1 Subroutine Calling Sequence . . . . .                                              | 65   |

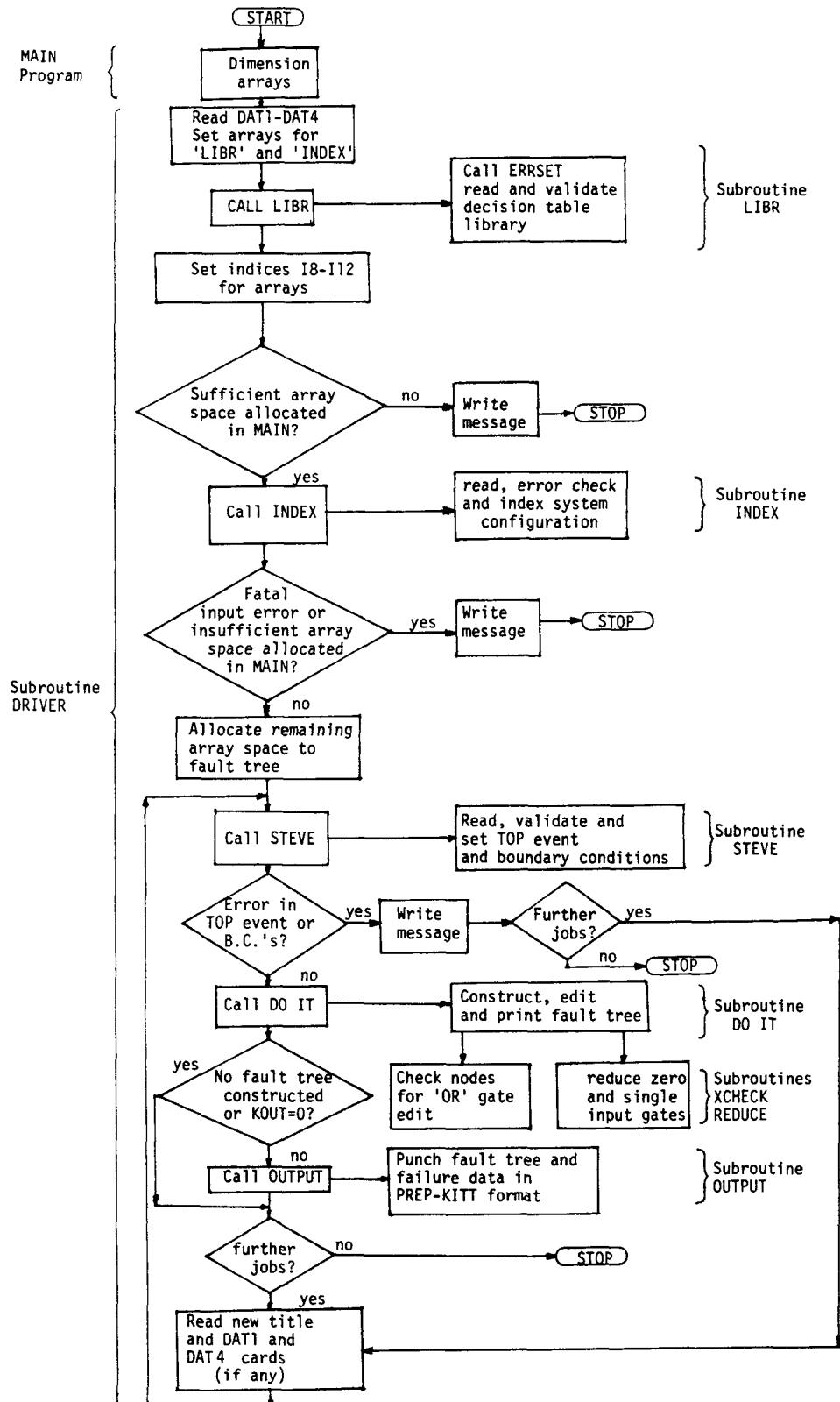

| Figure A-2 Flowchart for CAT Code . . . . .                                                   | 66   |

| Figure A-3 Flowchart for Subroutine LIBR . . . . .                                            | 78   |

| Figure A-4 Flowchart for Subroutine INDEX . . . . .                                           | 81   |

| Figure A-5 Flowchart for Subroutine STEVE . . . . .                                           | 85   |

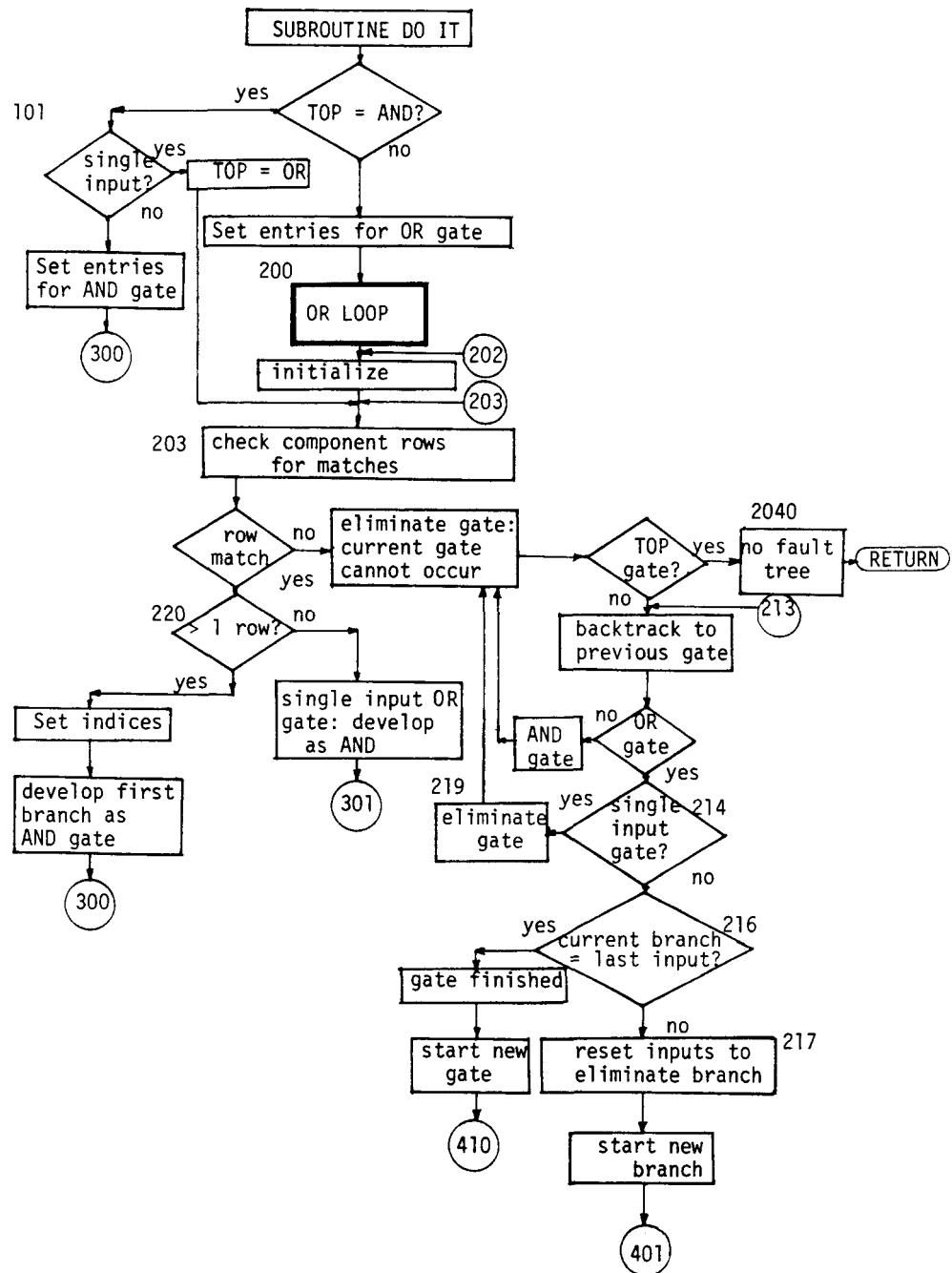

| Figure A-6 Flowchart for TOP Event and OR Gate Algorithm<br>of Subroutine DO IT . . . . .     | 91   |

| Figure A-7 AND Gate Construction Flowchart of Subroutine DO IT                                | 92   |

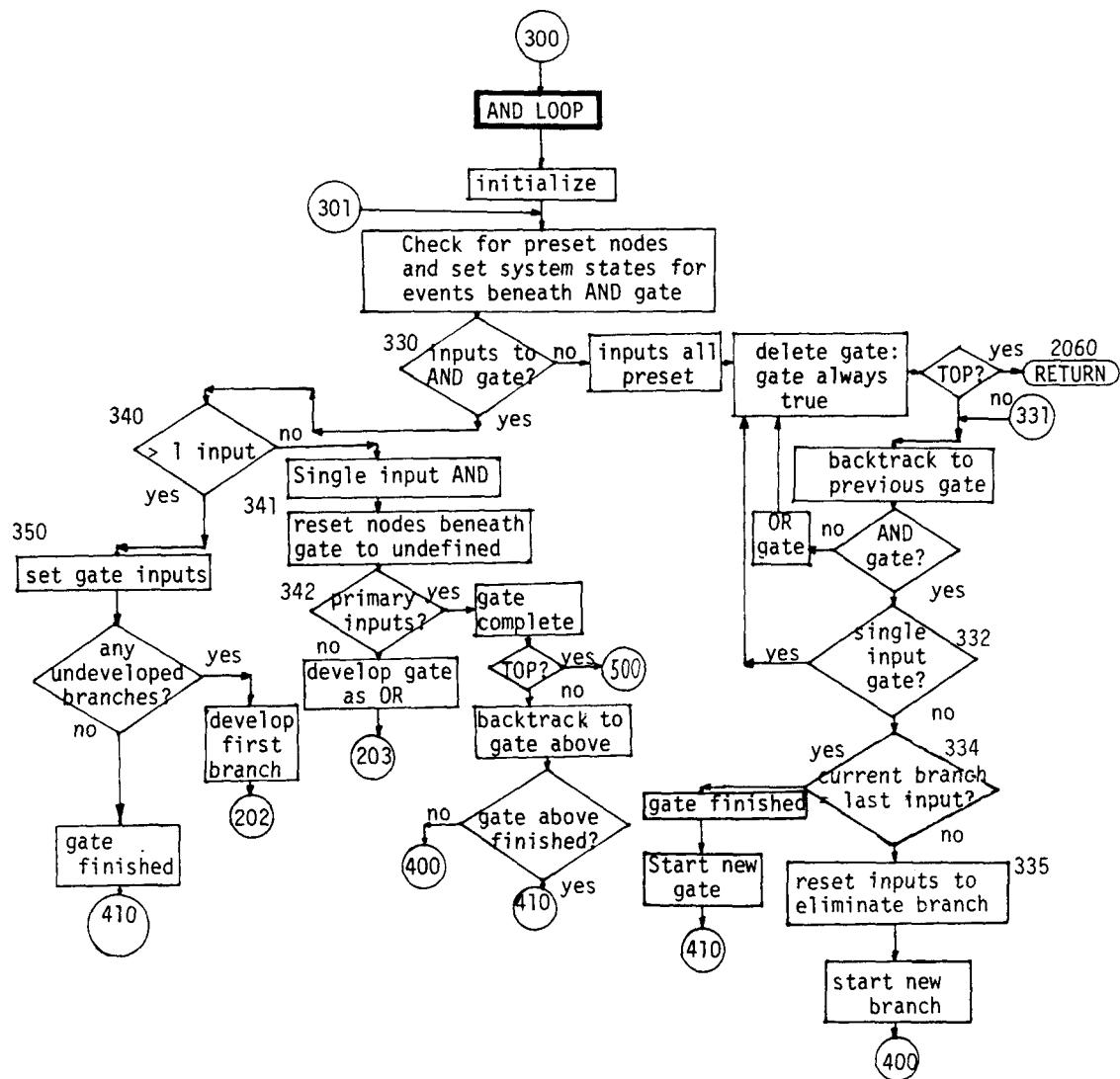

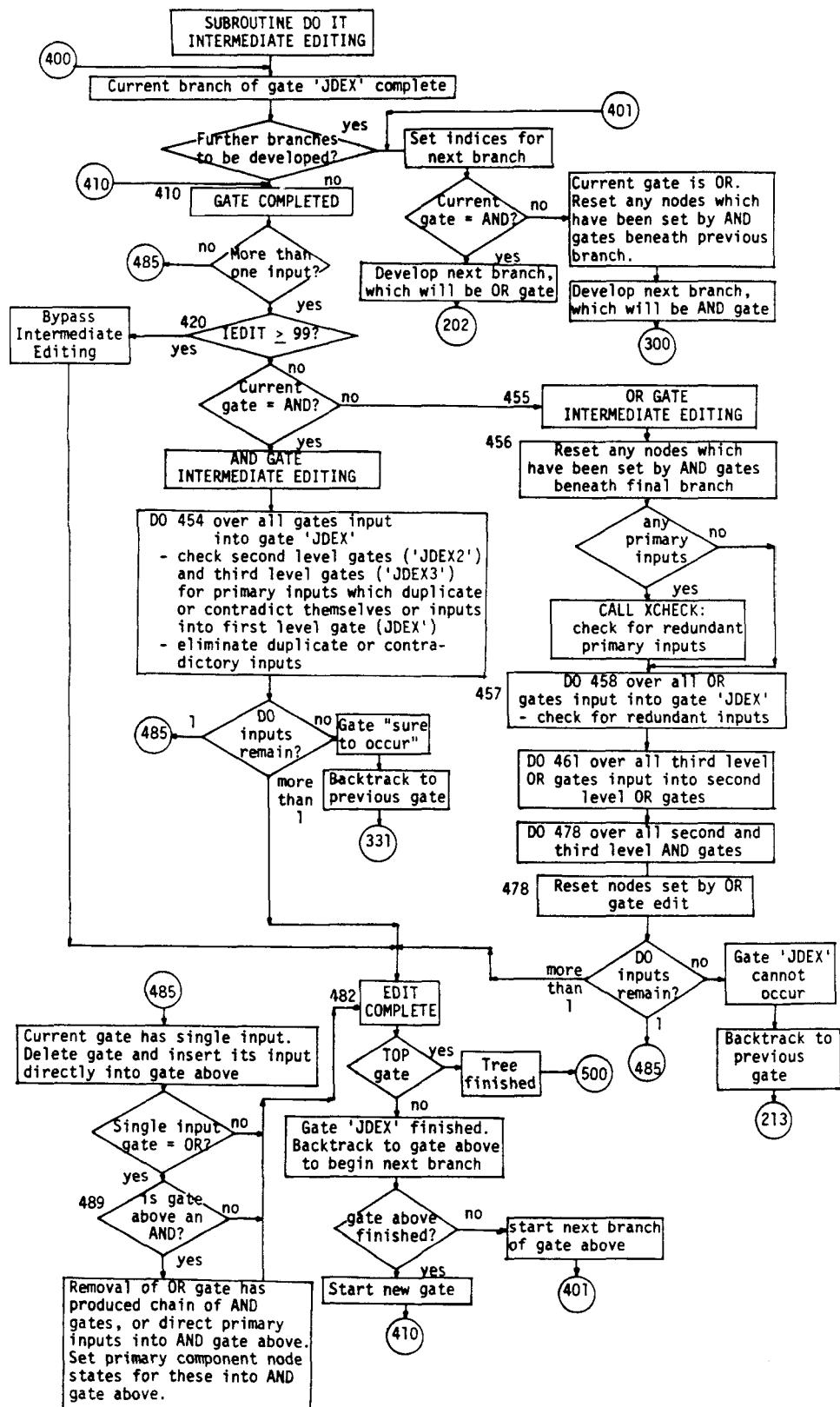

| Figure A-8 Flowchart for Intermediate Editing Loop of<br>Subroutine DO IT . . . . .           | 97   |

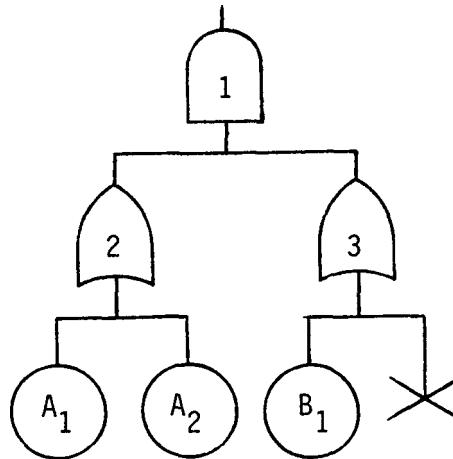

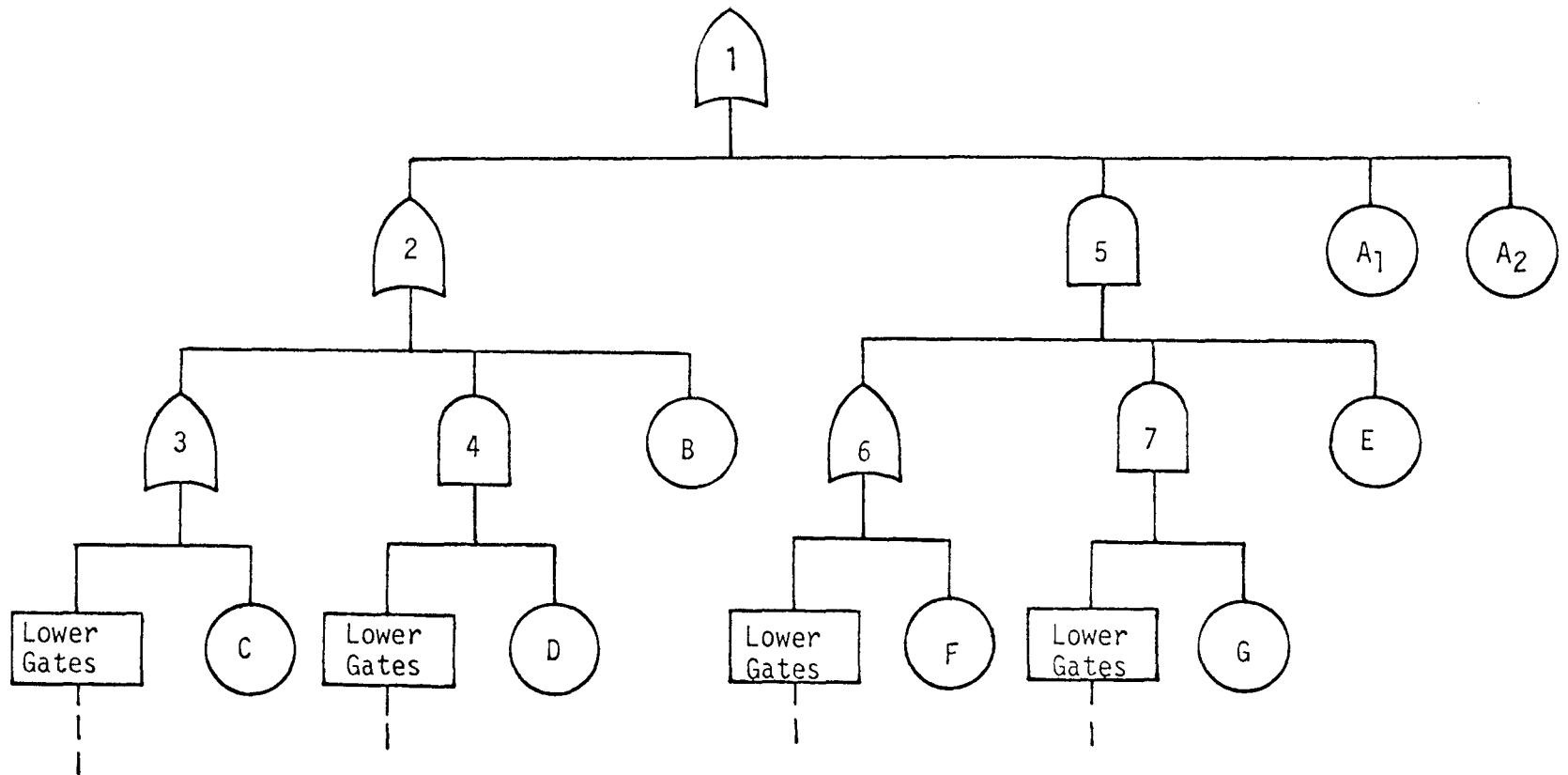

| Figure A-9 Sample Tree for Intermediate Editing . . . . .                                     | 101  |

| Figure A-10 Flowchart for Final Editing Phase of<br>Subroutine DO IT . . . . .                | 104  |

| Figure A-11 Flowchart for Subroutine XCHECK . . . . .                                         | 108  |

| Figure A-12 Flowchart for Subroutine REDUCE . . . . .                                         | 111  |

| Figure A-13 Flowchart for Subroutine OUTPUT . . . . .                                         | 113  |

## LIST OF FIGURES (Continued)

|                                                                               | Page |

|-------------------------------------------------------------------------------|------|

| Figure C-1 Sample System . . . . .                                            | 132  |

| Figure C-2 Fault Tree for Sample System . . . . .                             | 136  |

| Figure C-3 Fault Tree for Sample System With Good<br>States Removed . . . . . | 139  |

| Figure D-1 Data Deck for Sample Case . . . . .                                | 145  |

## LIST OF TABLES

|                                                                                                                        | Page |

|------------------------------------------------------------------------------------------------------------------------|------|

| Table 1. Representative System States . . . . .                                                                        | 6    |

| Table 2. General Failure State Categories . . . . .                                                                    | 8    |

| Table 3. Decision Table Failure States . . . . .                                                                       | 8    |

| Table 4. Input Data Deck for CAT . . . . .                                                                             | 11   |

| Table 5. Original Decision Table of Pump . . . . .                                                                     | 29   |

| Table 6. Reduced Decision Table of Pump . . . . .                                                                      | 31   |

| Table 7. Final Decision Table of Pump . . . . .                                                                        | 32   |

| Table 8. Decision Table for Pump by Deductive Method . . . . .                                                         | 35   |

| Table 9. Logic Model for Inhibit Condition . . . . .                                                                   | 40   |

| Table 10. Component Index Input Printout for CSRS . . . . .                                                            | 43   |

| Table 11. TOP Event Decision Table for: "Containment Pressure Normal, but Hi Signal Sent by Malfunction of CLCS" . . . | 53   |

| Table 12. Decision Table of Operator . . . . .                                                                         | 55   |

| Table 13. Component Index Input Printout for CLCS . . . . .                                                            | 57   |

| Table A.1 Integer Arrays . . . . .                                                                                     | 73   |

| Table A.2 Alphanumeric Arrays . . . . .                                                                                | 75   |

| Table A.3 Diagnostics Produced by Subroutine LIBR . . . . .                                                            | 79   |

| Table A.4 Diagnostics Produced by Subroutine LIBR . . . . .                                                            | 82   |

| Table A.5 Diagnostics Produced by Subroutine STEVE . . . . .                                                           | 87   |

| Table C.1 Signal (101) . . . . .                                                                                       | 131  |

| Table C.2 On/Off Switch (102) . . . . .                                                                                | 133  |

| Table C.3 Relay Switch (103) . . . . .                                                                                 | 134  |

| Table C.4 Junction (OR Gate, Type 104) . . . . .                                                                       | 134  |

| Table C.5 Operator (106) . . . . .                                                                                     | 135  |

| Table C.6 Relay Switch with Good States Removed . . . . .                                                              | 140  |

## SUMMARY

The CAT (Computer Automated Tree) methodology is a systematic approach to the construction of fault trees, based upon the use of decision tables. This approach consists of a scheme which utilizes these decision tables to model component behavior, a method of describing the specific system configuration including initial system states, and a means of defining a top event (or events) of interest. Given these inputs, the decision table models are used for the appropriate components within the system, and are combined and edited to form a completed fault tree for the TOP event desired. This fault tree may then be analyzed, either by hand, or by any of several fault tree analysis codes, in order to obtain the desired reliability (availability) information for the TOP event.

The current approach has several important features which make it especially useful in the analysis of nuclear systems, as well as of other, general types of systems. The decision table methodology is capable of modeling complex components of essentially any type, including mechanical, electrical and hydraulic. It can incorporate models for human interactions, environmental influences and provides a number of ways of treating common cause effects. Furthermore, the specific approach developed here also allows the analysis of systems containing feedback loops, such as may be found in many types of control circuits in use in nuclear plants.

This report documents a slightly newer version of the CAT code than presented by Salem, Apostolakis and Okrent in EPRI NP-288. This version has been updated by the incorporation of a new subroutine

('OUTPUT'), which produces the fault tree in a punched output format directly compatible with the PREP-KITT codes. This output will provide the complete data deck required as input for the PREP code, if desired. However, the input requirements for this version are identical with those of the previous one if the new output is not desired. Thus, the same data decks may be utilized with either version of the CAT code. If the new output option is to be utilized, however, additional failure and repair data must be provided.

EPRI NP-288 has presented the CAT methodology from a somewhat theoretical point of view. In the following chapters, those aspects most important to the user of the code itself will be emphasized. Actual details of the code itself will be included in the appendices.

In order to provide a general introduction to the CAT methodology, Chapter 2 begins by presenting some basic concepts and terminology used in this approach. The general organization of the input deck, and the specific requirements for all input data are then presented. Finally, the output produced by the code is briefly described.

Chapter 3 discusses the methods of developing the decision tables to be used by the code. Each method is illustrated by an example in order to familiarize the user with some of the techniques useful in decision table modeling. Also, the way in which such decision tables are used by the code in constructing fault trees is described. In combination with Chapter 2, this chapter completes the discussion of input required for operating the CAT code.

In Chapter 4, the use of the CAT code is illustrated by two applications: a Containment Spray Recirculation System, and a

Consequence Limiting Control System. These systems have been chosen to provide additional examples, complementing those of References [1,2], and will help to display various features of the code. New features illustrated by these examples include maintenance, TOP event logic which is a function of time, and the use of inhibit conditions.

Finally, Chapter 5 summarizes these results and provides a few concluding suggestions for the user.

This report is supplemented by several appendices, useful in running the CAT code. Appendix A describes the functional organization of CAT, and its specific subroutines. Appendix B provides a number of decision tables, many of them developed during the past year, as examples to guide the user in constructing his own tables. Appendix C presents a simple example system which, together with the sample input and output of Appendices D and E, provides a complete sample case which can be used to check out the operation of the code and to obtain familiarity with it. Finally, Appendix F contains a complete listing of the updated version of CAT for those interested in becoming more familiar with the actual mechanics of the code.

## 1. INTRODUCTION

With the increasingly important role being played by probabilistic risk assessment in the electric power industry, and the interest being expressed both by commercial groups and regulatory bodies, the development and improvement of methods of safety and reliability analysis are currently of great interest in the nuclear field. Fault tree analysis (FTA) is one of these techniques which is especially useful because of its advanced state of development, and acceptance and use by large segments of the technical community. The usefulness of FTA has been greatly augmented by the development and application of a number of computer codes for the numerical analysis of fault trees. However, the rapid analysis of a complex system using such codes has, until recently, had to await the much slower process of constructing the fault tree itself. This construction phase has traditionally been a manual task, relegated to the analyst himself, due to the lack of a systematic fault tree methodology which could be readily programmed on the computer.

In light of the relatively advanced state of fault tree analysis codes, the current effort was devoted to automating this one remaining phase. The benefits of this automation would include the speeding up of the entire fault tree analysis process as well as the freeing of much of the analyst's time for other tasks. Furthermore, an automated fault tree construction code would allow the preparation of additional fault trees for investigating other events of interest, or for evaluating various system modifications. The development and implementation of such an approach has been the goal of this work. The methodology has been described elsewhere [1,2]; the operation and use of the CAT

code, which implements this methodology, will be presented in detail in the following chapters of this report.

In order to see some of the other significant characteristics of such a methodology, a few of the features incorporated into the CAT code itself will be enumerated here. These include:

- 1) a simple, tabular decision table form for modeling component behavior,

- 2) capability of multiple state and multiple failure mode decision table models,

- 3) ability to develop both simple and highly detailed component models to produce fault trees of varying complexity,

- 4) ease of defining multiple TOP events for the construction of both fault and success trees for various events,

- 5) provision to define TOP events of any logical complexity,

- 6) ability to define initial states to specify initial system configurations,

- 7) simplicity of changing or modifying systems to analyze differences between various configurations,

- 8) essentially unlimited numbers of components, complexities of systems or sizes of fault trees produced,

- 9) specification of various levels of editing, and printout,

- 10) capability of interfacing with the PREP-KITT analysis codes,

- 11) repeatability of fault trees produced for identical input, and

- 12) ability to "pre-structure" fault trees by varying TOP event definitions and component models.

This report documents a slightly newer version of the CAT code than

presented by Salem, Apostolakis and Okrent [1,2]. This version has been updated by the incorporation of a new subroutine ('OUTPUT'), which produces the fault tree in a punched output format directly compatible with the PREP-KITT codes. This output will provide the complete data deck required as input for the PREP code, if desired. However, the input requirements for this version are identical with those of the previous one if the new output is not desired. Thus, the same data decks may be utilized with either version of the CAT code. If the new output option is to be utilized, however, additional failure and repair data must be provided.

Internally the only changes in the code have been to incorporate a call to the new subroutine, add input and error-checking sections for the new data, delete one array which was no longer needed, and change one variable in common.

In addition to a discussion of the fundamentals of the CAT methodology, this report presents sufficient material to allow the reader to understand and operate the code itself. Thus, Chapter 4 includes two examples of actual reactor systems analyzed by the code, and several appendices have been added to further help the potential user. These appendices contain a discussion of the code itself, with flowcharts, a library of sample decision table models, a complete example case with input and output listings, and a listing of the CAT code itself.

## 2. BASIC OPERATION OF THE CAT CODE

The CAT code has been developed as a systematic method of fault tree construction utilizing the methodology of decision table modeling [1,2]. Sufficient detail has been presented to allow the user to understand the basics of decision table modeling, and to construct fault trees by hand identical to those produced by the CAT code. This chapter will briefly review some essential terminology, and will discuss, in detail, the data required to actually operate CAT. A further discussion of specific subroutines and their functions will be found in Appendix A of this report. Furthermore, examples of input and output will be found in Appendices D and E.

### 2.1 Terminology and Basic Concepts

A number of definitions and fundamental ideas will first be presented. More detailed discussions will be found elsewhere [1,2]. The basic function of the code is to analyze a system, starting from a specific initial state, and to produce a fault tree for the TOP event of interest. This system can be any collection of units, known as "components", which performs some certain defined function or functions under specified conditions. These functions will be defined as the output of the system, and the specified conditions the inputs. Although the systems used here will generally be mechanical in nature, others, such as economic systems, corporate organizations, etc., are all equally valid.

Each system is first broken down into a set of components, which are the smallest elements to be individually modeled. With the CAT methodology, a component may actually consist of an entire system or

subsystem, as long as the features of interest can be accurately modeled by a single decision table. For a complex component or system, however, a number of coupled decision tables may be desirable.

Since there are often a number of similar or identical components within a single system, it is advantageous to employ a single model to describe the behavior of all such similar components. This introduces the concept of a component type. A component type is a unique description of the operational and failure modes of a component, represented by a single decision table. Any components which can be described by a single model will be considered as a single type, even though they may represent different physical components; thus, simple models for a fuse, resistor and circuit breaker might be represented by the same decision table. On the other hand, similar components with different characteristics (e.g., valves with different modes of operation), would be considered different types, each with a unique decision table representation. In either case, the models should be independent of the system itself in order to allow the development of libraries of component types to be used in systems of general interest.

Given a set of components, modeled by various component types, a system is then described in terms of the interconnections between these components. Each of these connections shall be defined as a node, or any point at which an output from one component is connected to the inputs of succeeding components. Note that one output may be connected to any number of succeeding inputs at a node; however, only a single output may exist at any one node. If outputs are to be connected together in parallel, they should be connected to the inputs

of a gate (junction), modeled by a decision table which represents the logical state formed by various combinations of the outputs to be connected.

At each node of a system, a system state may be defined to describe system conditions or signal states at that point. This state may have been set as an initial condition, or defined by later fault tree development, and must be consistent with all component inputs and outputs connected to that node. That is, this state must satisfy these two conditions:

- 1) it must exist as a valid output state in the decision table for the component output connected to that node, and

- 2) it must exist as a valid input state, or be allowed by don't care entries, in all decision tables of components whose inputs are connected to that node.

Table 1 contains a number of system states as examples of typical input, output and system states. These will be used in many of the models developed in Appendix B.

Table 1. REPRESENTATIVE SYSTEM STATES

| STATE | DEFINITION                                                                  |

|-------|-----------------------------------------------------------------------------|

| -1    | "Don't care" (signal state irrelevant or undefined)                         |

| 0     | no signal, or signal too low                                                |

| 1     | normal signal                                                               |

| 2     | overload (signal too high)                                                  |

| 3     | low signal (used if separate states are desired for "no" and "low" signals) |

| 101   | ground (zero) or short to ground                                            |

| 102   | floating (open, undefined)                                                  |

An internal mode represents an internal function of a component, and is represented by an "internal" column in a decision table. Since there may be several internal functions, or sub-components, within a complex component, a decision table may have several internal columns, each labeled by a specific sub-component function. For example, the motor-operated valve in Appendix B has the internal modes "position", "mechanical", "slip-clutch" and "relay". For each internal mode, or column, a component state may be defined to describe the internal state. The simplest states are simply "good" and "failed". However, since the mode of failure may determine the output state, it is often necessary to provide several failure states, such as "failed open" and "failed closed". Finally, it is important to consider all combinations of failure states of the various failure modes (columns) of a multiple-column component.

In order to utilize consistent decision table models, Table 2 was developed to systematically categorize failure states. This numbering scheme was then used to define a representative number of basic failure states, as shown in Table 3. Although use of such schemes is highly recommended, any similar categorization may be employed by the user.

Boundary conditions may now be described as system or component states which have been predefined as existing or not existing "initial" or "boundary" conditions within the system. These states exist initially, and continue to exist throughout the construction of the fault tree. In general, they will be used to determine the initial system configuration or operating conditions, and may be used to

TABLE 2. GENERAL FAILURE STATE CATEGORIES

| STATE     | DEFINITION                                          |

|-----------|-----------------------------------------------------|

| -1        | don't care (internal mode irrelevant)               |

| 0         | good                                                |

| 1-1000    | general faults                                      |

| 1001-2000 | electrical (shorts, surges, etc.)                   |

| 2001-3000 | mechanical                                          |

| 3001-4000 | fluid (leak, rupture, plugged, etc.)                |

| 4001-5000 | electronic (logic errors, etc.)                     |

| 5001-6000 | human                                               |

| 6001-7000 | environmental (temperature, pressure, stress, etc.) |

TABLE 3. DECISION TABLE FAILURE STATES

| STATE | DEFINITION                                             |

|-------|--------------------------------------------------------|

| 1     | failed open (fails to close; fails to transmit signal) |

| 2     | fails closed (shorted; fails to open; welded shut)     |

| 3     | internal failure (general, undefined)                  |

| 4     | fails to start (fails to actuate or change position)   |

| 5     | fails to operate properly (fails during operation)     |

| 6     | operates prematurely (starts without signal to start)  |

| 1001  | short to ground                                        |

| 1002  | short to power                                         |

| 1003  | power surge (power supply failure mode)                |

| 3001  | leak                                                   |

| 3002  | rupture                                                |

| 3003  | plugged                                                |

| 3004  | stuck                                                  |

| 5001  | calibration error                                      |

| 5002  | design error                                           |

| 5003  | general operator error                                 |

specify certain components as being failed at the start. Furthermore, they may be used to qualify the TOP event description.

Finally, the TOP event is that event which defines the failed (or successful) state of the system for which the fault tree is to be constructed. The basic requirement for the TOP event is that it be definable in terms of system states at specific nodes, which then serve as starting points for the fault tree construction process. Furthermore, if more than one event (or state) is used in the TOP event definition, these must have some logical relationship to each other in order to structure the tree beneath. For example, the TOP event "failure of systems A and B" might be represented by simultaneous states of zero at two nodes, logically connected by an AND gate. The resulting fault tree would then have a top AND gate connecting these two events.

## 2.2 Input Data

### 2.2.1 Outline of Input Data Organization

The input to the CAT code consists of the following information:

- 1) Program Control Data,

- 2) Decision Table Models,

- 3) System Configuration,

- 4) TOP Event definition,

- 5) Initial or Boundary Conditions,

- 6) Failure and repair data (for use with PREP-KITT output option).

The first of these inputs, as described below, consists of program dimensions used to define the sizes of the component library and system

configuration, and flags to control the printing and editing options to be used. The decision table models comprise the bulk of the input, and will be described in detail in Chapter 3. The system configuration, initial conditions and TOP event definition will all be described later in this chapter.

Output from the code consists of two parts. First is the printed output of all input data, cross-references and the fault tree itself. Secondly, if desired, is a punched deck (or tape or disk file) consisting of the fault tree and failure data in a format compatible with the PREP-KITT codes. This is produced by a separate subroutine, 'OUTPUT', which can be modified or replaced to interface with any code of the user's option. This routine will be discussed later in this chapter, and in the appendices.

### 2.2.2 Data Deck Setup and General Input Considerations

The input data deck is arranged as shown in Table 4. Each set of data will be described individually; general information is provided below.

Each card (except the failure and repair data) begins with a four character code which identifies to the computer what type of information is to follow. This also facilitates later runs in which the input must be modified on certain cards. On all except the 'DAT' cards, the four character field can be followed by up to six columns of information. Thus, the 'ROW' cards can be numbered in column 5, the 'LIBR' codes can be followed by the appropriate type number, etc. (see sample input data). This information is for the user's convenience and is not read by the code. It is important to note that, on

TABLE 4. INPUT DATA DECK FOR CAT

```

graph TD

A["TITLE

&DAT

(Data cards)"]

B["END

&LIB

(Library cards)"]

C["END

&CMP

(Component cards)"]

D["END

&TOP

(TOP event description)"]

E["END

&BC

(Boundary conditions)"]

F["END

&OUT

(Failure and repair data)"]

G["END

&END"]

H["TITLE (optional)

&DAT

DAT1

END

&TOP

(New TOP)"]

I["END

&BC

(New boundary conditions)"]

J["END

&OUT

(New failure data)"]

K["END

&END"]

A --> B

B --> C

C --> D

D --> E

D --> F

D --> G

D --> H

E --> I

F --> J

G --> K

I --> J

J --> K

H --> I

H --> J

H --> K

I --> K

J --> K

```

The diagram illustrates the structure of a TOP event description. It starts with a main block containing 'TITLE (optional)', '&DAT', 'DAT1', 'END', '&TOP', and '(New TOP)'. This is followed by a series of optional sections: '&BC' (Boundary conditions), '&OUT' (Failure and repair data), 'END', and '&END'. Brackets indicate the scope of these sections, and arrows point to the right with labels 'if necessary'. A separate arrow points to the right with the label 'cards for additional runs'.

certain cards, the four column code begins with a blank column.

The major sections begin with '&---' cards and terminate with 'END' cards. These codes allow the program to search for the next set of data if terminal errors occur in any section. The '&DAT' section contains the basic parameters for the job. This consists of four cards, format (A4, I1, 12I5). However, cards 'DAT1' and 'DAT4' may be omitted if default values of all parameters so skipped are desired.

The second section, beginning with the '&LIB' card, contains the library of component type decision tables. Each table begins with a 'LIBR' card which contains the basic information for that table. There follows a 'MOD' card which lists the names of that component's internal failure mechanisms. The decision table itself is input on a set of 'ROW' cards, concluded by an 'END' card.

The components themselves are described by the '&CMP' section, one card per component. On them are given the component name, type number and input/output node numbers.

The '&TOP' segment begins with a 'TTOP' card defining the size of the TOP event decision table and the node numbers referring to the columns of the table. This is followed by the 'TOP' cards, on which the rows of the table are input.

If any boundary conditions are to be included, they follow the '&BC' card. Both internal component modes and system nodes may be initialized by use of cards coded 'INT' and 'EXT' respectively.

Should fault tree output be desired for use by the PREP-KITT codes, a section labeled '&OUT' follows. The first two cards contain

control data to be used by PREP, followed by failure and repair data. Since the input formats are similar to those used by PREP, the initial four letter codes are not used on these cards.

The last group of input cards must be followed by both its own 'END' card and a final '&END' card. These signify the end of the data section and the end of the job. Following the '&END' card, second and succeeding jobs may begin. Although each job of a multiple run uses the same library and system description, new boundary conditions and parameters from the 'DAT1' card may be defined, as well as the required redefinition of the TOP event. Furthermore, new failure and repair data must be provided, if necessary.

### 2.2.3 Program Control Data

The CAT input deck begins with a title card (20A4), followed by the program control data, in the '&DAT' section. This data section consists of four sets of program flags and dimensioning information, and is contained on cards labeled 'DAT1' - 'DAT4'. These cards have the formats (A4, I1, 12I5), and the four character code field 'DATn' must be preceded by a blank. This group of cards must be preceded by an '&DAT' card and followed by an 'END' card. The data on these cards are as follows:

#### Title Card

```

&DAT

DAT1      IJOB      IPRINT      KOUT      IEDIT      IOT

DAT2      NLIB      LNROW      MAXINT      MXNROW

DAT3      NNCMP      NNODE

DAT4      MROW

END

```

The parameters on these cards are described below. Note that the parameters on cards 'DAT1' and 'DAT4' have default values. In the

event that all parameters on the 'DAT1' card are to be set to the default values, the 'DAT1' card may be omitted. Similarly, if MROW = 1, the 'DAT4' card may be eliminated. However, if the DAT1 card is used, all values must be defined, since a blank location will be read as 'zero.'

The following is a description of the program control parameters used for CAT.

#### IJOB

IJOB is the identification number of the first job of a particular sequence, and is incremented by 1 for each succeeding job. This value is merely for the convenience of the user.

Default = 1.

#### IPRINT

This parameter determines the amount of printout from the fault tree construction and editing phases. Any integer from -1 to 4 may be specified, with each increasing value producing additional output. For an absolute minimum of output, code IPRINT = -1; however, a value of IPRINT of 0 or larger is suggested to provide the most useful information. Values of 1 or 2 allow the complete construction and editing phases to be followed step by step. IPRINT = 3 or 4 produces printouts of certain intermediate arrays during editing. A value of 4 includes the maximal number of arrays. This last value is not suggested, since large amounts of output will be produced. The most useful printouts will be obtained by setting IPRINT = 0, 2 or 3, as needed.

Default = 0.

#### KOUT

The KOUT parameter determines whether output is to be produced for use by PREP-KITT. KOUT = 0 for no output, and KOUT = 1 for output to be

produced on output device (unit) IOT. Note that KOUT = 1 requires additional CAT input in input section '&OUT'.

Default = 0.

#### IEDIT

This parameter is used to omit certain editing phases. Values below 98 produce full editing. IEDIT = 98 will bypass the search for transfers within the tree. IEDIT = 99 skips the intermediate editing stage. A value of IEDIT of 100 or above will omit both these editing sections.

Default = 0.

#### IOT

IOT is the unit number for fault tree and data output produced for PREP-KITT when KOUT = 1. This can be punched, or written onto disc or tape, depending upon the specification of IOT, and the user's installation. This output is also printed, along with other editing information, as part of the CAT output. If IOT is left blank for the first job of a multiple job run, it is set equal to the default value. If it is left blank in a subsequent job, it is set equal to IOT of the previous job in that run.

Default = 10.

#### NLIB

NLIB defines the number of component types to be input into the library section. A number which is erroneous may produce one of two effects. If the number is too large a warning will be produced, but the program will continue. If NLIB is too small, the extra component types will be skipped. However, the program will continue unless the system itself requires one of the component types so bypassed.

## LNROW

LNROW should be set to the maximum number of columns of any of the decision tables, including that of the TOP event.

## MAXINT

Set the value of MAXINT to the largest number of internal failure mode columns of any component table. This value is used to determine the number of failure mode names to be read by the program.

## MXNROW

This variable is the total number of rows of all decision tables to be input. It need be only an estimate, and is used in determining whether sufficient space has been allocated for the total decision table library.

## NNCMP

NNCMP defines the number of components in the system, as input by block 3 of the program. This value must be exact.

## NNODE

NNODE is the largest node number used in the system flowchart. If NNODE is greater than the largest node number, its value will be correctly redefined later in the program. If modifications in the system being analyzed will change the numbering of nodes in later cases, NNODE may be set to the largest value anticipated and not changed for any of the runs.

## MROW

MROW is set to the largest number of rows in any of the TOP event decision tables for one group of jobs. If any TOP event table exceeds MROW, that tree will be terminated and the next job begun.

Default = 1.

## 2.2.4 Library Data

The second section of program data is the decision table library input group. This consists of one set of cards for each component type (there will be NLIB sets in all). Each set is input in the following order:

|      |       |       |     |      |      |      |                        |

|------|-------|-------|-----|------|------|------|------------------------|

| LIBR | NAME1 | NTYPE | NIN | NINT | NOUT | NROW | (A4, 6X, A8, 2X, 12I5) |

| MOD  | NAME2 | NAME3 | ... |      |      |      | (A4, 6X, 7(A8, 2X))    |

| ROW1 |       |       | i1  | i2   | i3   | ...  | (A4, 16X, 12I5)        |

| .    |       |       |     |      |      |      |                        |

| .    |       |       |     |      |      |      |                        |

| ROWn |       |       | n1  | n2   | n3   | ...  |                        |

| END  |       |       |     |      |      |      |                        |

The 'LIBR' card contains the basic information for the component type. NAME1 is the 8 character name of the component type, NTYPE is a unique 5 digit type number, and NIN, NINT and NOUT are the numbers of inputs, internal failure mechanisms and outputs of the component. That is, NIN + NINT + NOUT is the length of each row of the decision table which is to follow. Furthermore, NIN + NOUT is the number of nodes assigned to that component type. Finally, NROW is the number of rows of the decision table.

The 'MOD' card lists the 8 character names of the component internal mechanisms. There should be exactly NINT of these. Note that, even if NINT = 0, this card is required.

Finally, the decision table itself will be input on the 'ROW' cards. There will be 'NROW' of these, one for each row of the decision table. The columns must be arranged in the order: inputs - internals - outputs, and must have exactly NIN + NINT + NOUT entries. A "don't care" state will be indicated by a '-1' in the appropriate column. Note that each component type group must end with its own 'END' card.

As pointed out previously, any library entries in excess of the 'NLIB' groups specified on 'DAT2' will be ignored. However, as it is not necessary that every library type be used in the system itself, the program

will not terminate unless one of the extra types is specifically required. Furthermore, if several different models will be used for one component in various runs, it may be convenient to include all models in the library using different type numbers. In each run, only the specific component type desired will be used.

### 2.2.5 Component Cards

Following the '&CMP' card is the group describing the system itself. This consists of a total of NNCMP cards, one per component. The format is (A4, 6X, A8, 2X, 1215), and the input is as follows:

|     |      |       |       |       |       |     |

|-----|------|-------|-------|-------|-------|-----|

| COM | NAME | ITYPE | NODE1 | NODE2 | NODE3 | ... |

|-----|------|-------|-------|-------|-------|-----|

Notice that the code 'COM' begins in column 2, and that the following six column field has been used, in the sample inputs, to number the component cards. This is solely for the convenience of the user, since the six columns following 'COM' are not read by the code. 'NAME' is the 8 character name of the component, and must be unique. In setting later boundary conditions, this will be used to identify the specified components. ITYPE is the component type number of the decision table to be used for this component. Finally NODE1, NODE2, etc., are the input/output node numbers of the component. Referring to component type ITYPE, there must be a total of NIN + NOUT node numbers, the first NIN of which will be inputs, with the final NOUT as outputs.

The requirements for the node numbers are that:

- 1) All output node numbers be unique. This refers to multiple outputs of a single component, and to all outputs of other components.

- 2) No component output may be connected directly to an input of the same component. However, an output and input may be connected to each other through any other component, including a simple "piece of wire."

- 3) All inputs must be connected to valid output nodes from other components; that is, no component may be left with undefined inputs. However, any output may be left unconnected. If a particular input node is not going to be used, it may be connected to a "dummy" component. For example, if it is desired to set a boundary condition at the input of a component such as a sensor, a dummy component must still be connected to that node. A simple dummy component that is often used would have the following decision table inserted into the library:

| <u>ROW</u> | <u>Internal</u> | <u>Output</u> |

|------------|-----------------|---------------|

| 1          | 0               | 0             |

| 2          | 1               | 1             |

Note that this component type has no inputs and only one output. A 'COM' card would then be set up for the dummy component of this type, whose single output node would be connected to the input node in question. Finally, the boundary state could be defined at this node, as in Section 2.2.7. With a boundary condition defined at that node, the dummy decision table would never be used, and its exact form is irrelevant. However, the NIN and NOUT parameters on the 'LIBR' card for the dummy decision table (0 and 1 in this example) must agree with the number of nodes defined on the dummy 'COM' card.

#### 2.2.6 TOP Event Definition

The TOP event is input in much the same way as the decision tables for the component types. After the '&TOP' card, the basic data for the TOP

is input on the 'TTOP' card, followed by the decision table itself, on the 'TOP' cards.

|      |      |      |     |       |       |     |                        |

|------|------|------|-----|-------|-------|-----|------------------------|

| TTOP | NAME | NROW | NIN | NODE1 | NODE2 | ... | (A4, 6X, A8, 2X, 12I5) |

| TOP1 |      | I1   | I2  | ...   |       |     | (A4, 16X, 12I5)        |

| TOP2 |      | J1   | J2  | ...   |       |     |                        |

| TOPn |      |      |     |       |       |     |                        |

| END  |      |      |     |       |       |     |                        |

The 'TTOP' card contains an 8 character identification ('NAME'), for the TOP, followed by the number of rows and number of columns of the decision table (NROW and NIN). It is important to remember that NROW must be less than or equal to MROW given by the 'DAT4' card. Finally, the system nodes at which the TOP event decision table is defined (one per column) are input, up to a maximum of 10. The decision table is input on the 'TOP' cards. Note that the code 'TOP' begins in column 2, and that the numbers directly following are for the user's convenience, and are not read by the code.

### 2.2.7 Boundary Conditions

This data group, if required, contains the specification of the boundary conditions. If this group is needed, it begins with an '&BC' card and is followed, in any order, by 'INT' and 'EXT' cards defining the boundary (initial) values of internal component modes and external system states respectively. The form of the data is thus:

|     |      |       |        |     |       |        |                        |

|-----|------|-------|--------|-----|-------|--------|------------------------|

| &BC |      |       |        |     |       |        |                        |

| INT | NAME | MODE1 | MODE2  | ... |       |        | (A4, 6X, A8, 2X, 12I5) |

| EXT |      | NODE1 | STATE1 | ... | NODE6 | STATE6 | (A4, 16X, 12I5)        |

| END |      |       |        |     |       |        |                        |

Each 'INT' card specifies the predefined states for one component's internal modes. NAME is the 8 character identification of the component as given by NAME on the appropriate 'COM' card. Then one value is defined for each internal mechanism (column) of the component, including a -1 for

any mode which is not to be set as a boundary condition. Note that no state should be left as a blank, even if only one state is to be defined. Any blanks will be read as zeros, and thus a "good" state will be set, rather than being left undefined (i.e., set equal to -1).

The 'EXT' cards set the boundary conditions at system nodes. Each card can define up to 6 node conditions, by first specifying the appropriate node, followed by the state to be set. Notice that any number of 'EXT' cards may be used and may be intermixed with the 'INT' cards. This data group must be followed by an 'END' card.

#### 2.2.8 Failure and Repair Data

If output is desired to be used with the PREP-KITT codes, one final data group is required. This data begins with an '&OUT' card, and contains the control information and failure and repair data. This information, combined with the fault tree produced by CAT, is output to a card punch (or disc or tape file) in a format suitable for input to PREP-KITT. The input in this data group is as follows:

```

&OUT

NG      MIN      MAX      IDEX1  IDEX2  NPROB      (6I10)

MC      NREJEC   NTR      IREN      TAA      (4I10,F20.3)

NAME1      λ1      τ1  INT1 STATE1NAME2      λ2      τ2  INT2 STATE2

.

.

.

NAMEi      λi      τi  INTi STATEiNAMEj      λj      τj  INTj STATEj

END

```

The first two cards contain the control information for PREP, in the same format as used by that code. A description of these variables may be found in the PREP-KITT manual [3]. (Note that NPROB is an extra

variable, used only by the UCLA version of PREP, and may be omitted for other versions.) Since NG, the number of gates, is supplied by CAT, it may be left blank.

The remaining cards contain the failure and repair data for the components, supplied one or two sets to a card, at the user's option. Since each component may have several failure modes, with several states for each mode, several sets of data may be required for each component. Each set contains the following information:

| Data      | Format | Description                                                                        |

|-----------|--------|------------------------------------------------------------------------------------|

| Name      | A8, 2X | 8 character name of component, same as used on 'COM' card.                         |

| $\lambda$ | F10.6  | Failure rate (per $10^6$ hour).<br>Note: $\lambda \geq 10^{-9}$ , or $\lambda < 0$ |

| $\tau$    | F10.6  | Repair time (hours) $10^6 > \tau \geq 10^{-3}$                                     |

| INT       | I5     | Internal failure mode (column of decision table)                                   |

| STATE     | I5     | Failure state                                                                      |

Note that each  $\lambda$  and  $\tau$  represent the data for one specific failure state of one internal failure mode (column), where 'INT' is the column number and 'STATE' is the failure state. (For a component with only one internal column in its decision table, INT will always = 1.) Then, for each column, one set of data is required for each state which appears in that column in the decision table, unless it is known that a specific state will not appear in the final decision table. The use of a component as an inhibit condition is also allowed as an input option to PREP by setting  $\lambda \leq 0$ , and  $\tau$  as a number between 0 and 1 (see reference 3, page 31 for definitions).

As an example of the above, the following two rows of a decision table

will be used to represent a simple system:

| <u>Input</u> | <u>Maintenance</u> | <u>Internal Failure</u> | <u>Output</u> |

|--------------|--------------------|-------------------------|---------------|

| -            | -                  | 5                       | 0             |

| -            | 101                | -                       | 0             |

Internal failure 5 represents a failure to run, and maintenance = 101 means system unavailable due to maintenance. Assuming a failure rate of  $5 \times 10^{-4}$  ( $500 \times 10^{-6}$ ), 24 hour repair time, and 1% maintenance unavailability, the input data for 'SYSTEM-A' would be:

|          |       |      |   |     |

|----------|-------|------|---|-----|

| SYSTEM-A | 500.0 | 24.0 | 2 | 5   |

| SYSTEM-A | -1.0  | 0.01 | 1 | 101 |

These sets may be input in any order and intermixed with other components. However, all data in this input data group must obey the following FORTRAN rules:

- 1) all names must be left justified, and

- 2) all integers must be right justified.

Finally, the last data card must be followed by an 'END' card.

#### 2.2.9 Multiple Jobs

The data for the first job terminates with an '&END' card, and may be followed by further jobs. Each job must utilize the same system and library, but may define a new TOP and boundary conditions, as well as new failure data. We will see, however, that changes in a system may often be made simply by appropriate changes in boundary conditions.

The new job may begin, if desired, with a new title (20A4). Furthermore, the parameters of the DAT1 card, may be redefined, again as an optional feature. This would be done with the following setup.

```

&DAT

DAT1      IJOB      IPRINT      KOUT      IEDIT      IOT

END

```

If the DAT1 card is included, all values must be defined. If DAT1 is not used, neither the &DAT nor END cards are needed.

The TOP definition is the only required data for the new run, and is input exactly as before. For the new run, all boundary conditions will be reset to undefined states. All boundary conditions must be set, as before, by the '&BC' section following the TOP event definition. If KOUT is set to 1 (or left from the previous run), new PREP-KITT data is required, even if identical to the previous run. This is input in the '&OUT' section, as described in section 2.2.8. Finally, an '&END' card terminates this new run, which may be followed by further jobs.

Although the system may not be redefined in succeeding jobs, one may use switches, set by different boundary conditions, to switch in new subsystems, different component models, etc., at any points in the system.

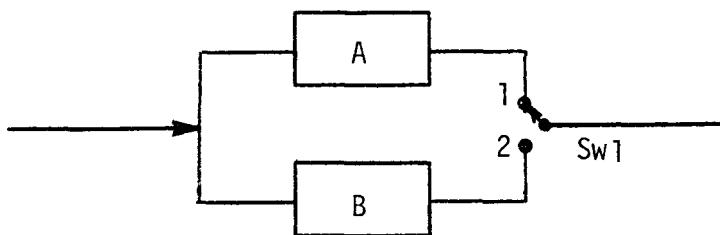

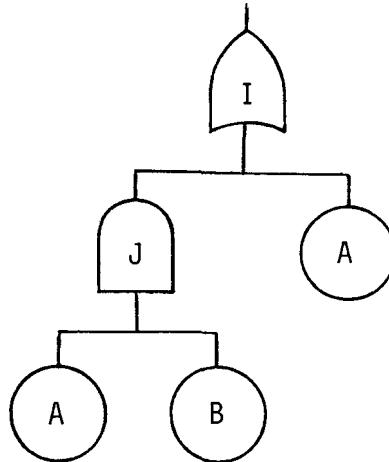

Consider the block diagram below:

By defining switch 1 to be in position 1 or 2 in successive runs, components (or systems) A and B are alternately switched into the overall system. Other capabilities include the possibility that A and B are simply different models for the same component. Both would be defined as part of the original system on 'COM' cards, and the appropriate one

would be chosen by the switch position.

### 2.3 CAT Output

The output from the CAT code consists of five phases illustrated in more detail in the sample output in Appendix E. First is a listing of all input data, excepting the PREP-KITT data (if any). This includes extensive error checking and diagnostics to pinpoint input errors, inconsistencies or missing data.

Second is a set of cross-references, listing input and output nodes, and specific component names for all inputs to each component.

Next is the step-by-step construction of the fault tree. The output of this phase is controlled by the IPRINT flag on the 'DAT1' card. This is followed by the final fault tree printout itself.

Finally, if KOUT = 1, CAT produces the PREP-KITT output. In addition to the punched (or tape or disc) output, is an identical printed output of the tree. This includes the '\*' cards required by the PREP code. This printed output also includes error messages to indicate extra or missing data. Note that the fault tree output will be produced in all cases where KOUT = 1, even if the failure data is missing. However, in this case, the output will not contain the required failure data for PREP.

Since PREP can only accept a single failure mode for each component, CAT must construct a unique name for each component-failure mode-failure state set. This is listed in a final table, along with the original component name, failure mode and state. This name is simply an eight digit code consisting of the internal mode number (4 digits) and the failure state (4 digits). Using the example in Section 2.2.8, assume that the internal (computer generated) mode number for maintenance for SYSTEM-A was 123, and for internal failure was 124 (corresponding to

columns 1 and 2 of the table). Then, the code for: SYSTEM-A, internal failure, state 5 would be:

01240005,

and the code for: SYSTEM-A, maintenance, state 101, would be:

01230101.

Notice that, in this case, the "component" 01230101 would represent an inhibit condition (see Section 2.2.8) and 01240005 would represent a primary component failure.

### 3. DEVELOPMENT OF DECISION TABLES

#### 3.1 Introduction

The development of accurate decision table models is a central requirement in the current approach. However, since the components and systems of interest are so diverse, and models of various levels of sophistication are desirable, an effective method of constructing such tables is needed. Two general methods for developing decision tables of components will be described in the following sections, and a number of decision tables which have been studied and used previously will be outlined in Appendix B and will serve as a reference to the users.

Two ways of generating decision tables will be described in this report. The first approach (*inductive*) consists of systematically constructing the decision table by enumerating all possible combinations of input states and internal modes, and then finding the appropriate output state for each combination. This is a typical method of constructing decision tables which assures a complete, though complex table. The second approach begins by considering all possible output states and tracing back to all possible input states. This deductive method is similar to that used by CAT itself in constructing fault trees.

The advantage of the first method, as pointed out, is the assurance of completeness, at the expense of complexity. For example, a component with 2 inputs, each with 3 states, and 3 internal modes, each with 3 states, would result in a table with 6 columns and  $3^5 = 243$  rows before reduction. The reduction itself, although tedious, is a process amenable to computer implementation. The second method, although not as straightforward, has the advantage of allowing one to immediately

concentrate on the output states of most interest. It has the serious drawback, however, of allowing the possible oversight of some important features unless a careful check of completeness is made.

### 3.2 Inductive Method of Decision Table Development

The first step in this method is to enumerate all combinations of input states and internal modes of the component. Then, the output state(s) for each combination are determined essentially by a failure modes and effects analysis. Finally, a decision table reduction method may be utilized to produce a compact table, suitable for use with the code. A step by step description of the process of generating decision tables by this method is given in following paragraphs. As an example a decision table for a pump is developed.

Step 1. First, an investigation must be made of the physical characteristics and design considerations of the component, in order to determine all of its possible input states and internal modes. For a pump, there are two inputs, one internal mode and one output:

Input 1: Main flow (pressure) input

0 - no pressure in or pressure too low

1 - normal pressure

Input 2: Power input

0 - no power in

1 - power in

Internal

Mode: Condition of pump

0 - pump in good condition

4 - pump fails to start

5 - pump fails to run normally

Output: Main flow (pressure) output

0 - no pressure out or pressure out too low

1 - pressure out

Note that in other analyses, these states may differ, depending upon the specific nature of the pump, and the depth of analysis desired.

For example, the state "fails to run normally" could further be broken down into specific failures such as impeller failure, shaft failure, etc., if specific data on these are available, and it is desired to separate out these failures. This could be especially useful in trying to isolate potential common mode failures, etc.

Step 2. An initial decision table is then constructed by listing these combinations of input states and internal modes, along with the output state which results. For the pump as example, there are  $2 \times 2 \times 3 = 12$  possible rows:

TABLE 5. ORIGINAL DECISION TABLE OF PUMP.

| Row | Input 1<br>Main flow | Input 2<br>Power | Internal<br>Mode | Output |

|-----|----------------------|------------------|------------------|--------|

| 1   | 0                    | 0                | 0                | 0      |

| 2   | 0                    | 0                | 4                | 0      |

| 3   | 0                    | 0                | 5                | 0      |

| 4   | 0                    | 1                | 0                | 0      |

| 5   | 0                    | 1                | 4                | 0      |

| 6   | 0                    | 1                | 5                | 0      |

| 7   | 1                    | 0                | 0                | 0      |

| 8   | 1                    | 0                | 4                | 0      |

| 9   | 1                    | 0                | 5                | 0      |

| 10  | 1                    | 1                | 0                | 1      |

| 11  | 1                    | 1                | 4                | 0      |

| 12  | 1                    | 1                | 5                | 0      |

Table 5 is the original decision table of the pump. Row 1 of Table 5 shows that if there is no fluid input, no power input, and the pump is good, there will be no flow at the output. Row 10 shows that if the flow (pressure) input is high enough, the power is on, and the pump is good, there will be flow at the output side of the pump. The other rows can be understood in a similar manner.

Step 3. The decision table is now ready to be reduced. Although the decision table developed in the previous steps can be used as the input data for CAT code, it is very lengthy. A modification can be made by introducing "don't care" states into the table, in order to make it simpler, as well as to save computer time and memory in the process of constructing the fault tree.

The basic rule for reducing decision tables is as follows. If several rows have identical output, input, and internal states except for one input or internal mode, and if this exception includes all possible states which can occur, then these rows can be combined into a single row with a "don't care" state. For example, in Table 5, rows 1, 2 and 3 all have 0 as output, 0 main flow input, and 0 power input. Furthermore, the remaining column, the internal mode, includes all three states possible (0, 4 and 5). This implies that, regardless of the internal state, the output will be 0 as long as the flow input is at low pressure and no power is present at input 2. Thus, rows 1, 2 and 3 can be combined into a single row with a 'don't care' state, i.e.,

0      0      -1      0

Similarly, rows 4, 5 and 6 in Table 5 can be reduced to

0      1      -1      0,

and rows 7, 8 and 9 can be reduced to

1 0 -1 0.

Finally, similar reduction can be done to rows 2, 5, rows 3, 6, rows 8, 11, rows 9, 12, and a reduced decision table of the pump can be obtained as shown in Table 6.

TABLE 6. REDUCED DECISION TABLE OF PUMP.

| <u>Row</u> | <u>Input 1<br/>Main Flow</u> | <u>Input 2<br/>Power</u> | <u>Internal<br/>Mode</u> | <u>Output</u> |

|------------|------------------------------|--------------------------|--------------------------|---------------|

| 1          | 0                            | 0                        | -1                       | 0             |

| 2          | 0                            | 1                        | -1                       | 0             |

| 3          | 1                            | 0                        | -1                       | 0             |

| 4          | 1                            | 1                        | 0                        | 1             |

| 5          | 1                            | -1                       | 4                        | 0             |

| 6          | 1                            | -1                       | 5                        | 0             |

| 7          | 0                            | -1                       | 4                        | 0             |

| 8          | 0                            | -1                       | 5                        | 0             |

If we look at rows 1 and 2 in Table 6, both of them have 0 as output, 0 as flow input and -1 as the internal mode; furthermore, the power input includes both 0 and 1, the only possible states of that input. In this case rows 1 and 2 of Table 2 can be combined again into:

0 -1 -1 0.

Similarly rows 1 and 3 in Table 6 can be combined into:

-1 0 -1 0.

Similar reductions are done to rows 5, 7, and rows 6 and 8. The decision table of the pump is further reduced as Table 7.

TABLE 7. FINAL DECISION TABLE OF PUMP.

| Row | Input 1<br>Main Flow | Input 2<br>Power | Internal<br>Mode | Output |

|-----|----------------------|------------------|------------------|--------|

| 1   | 0                    | -1               | -1               | 0      |

| 2   | -1                   | 0                | -1               | 0      |

| 3   | 1                    | 1                | 0                | 1      |

| 4   | -1                   | -1               | 4                | 0      |

| 5   | -1                   | -1               | 5                | 0      |

Table 7 is much simpler than the initial decision table as shown in Table 5. A discussion about this reduced form of decision tables has been worked out in reference [1] which indicates the reduced form is equivalent to the original decision table in the sense of probability considerations in the construction of fault trees, but with the advantage of being simpler than the original form.

### 3.3 Deductive Method of Decision Table Development

One should bear in mind that the purpose of the decision tables is to supply information for constructing the fault trees of various systems. Each system fault tree starts from the TOP event and is then traced back to the primary events. In this way, the decision table is actually used in the reverse direction. For instance, in the pump example, the information desired will be of the following type: "What causes can produce 'no pressure or pressure too low' at the output?", or "What events are required to obtain 'normal pressure' at its output?" From such investigations, we can obtain a mini-fault/success tree [4] for each possible output state. By collecting these trees for all possible outcomes, one obtains the decision table for the component. A pump is again used as an example in this case.

Step 1. First, the investigator must become familiar with the physical characteristics and design purpose of the component. From these, the analyst then finds different source reasons for malfunctions (this is essentially a FMEA process). The analyst should also collect the available failure history of each component in actual industry experience.

For the case of a pump, the only situation in which there will be output is when the pump is good, there is power input to the pump, and the flow input has 'pressure in'.

The internal mode of the pump can either be 'good', 'fails to start' or 'fails to run', each with a different probability; the total, however, will sum up to one.

Step 2. Define all the possible states of inputs, internal modes and outputs of the component. For a pump, there are two inputs, one internal mode and one output as described previously.

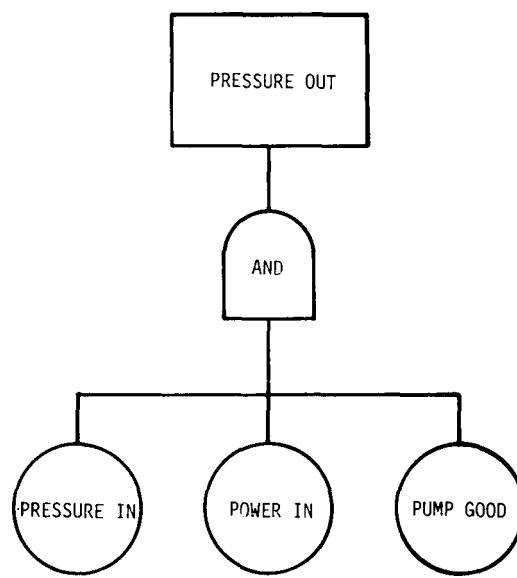

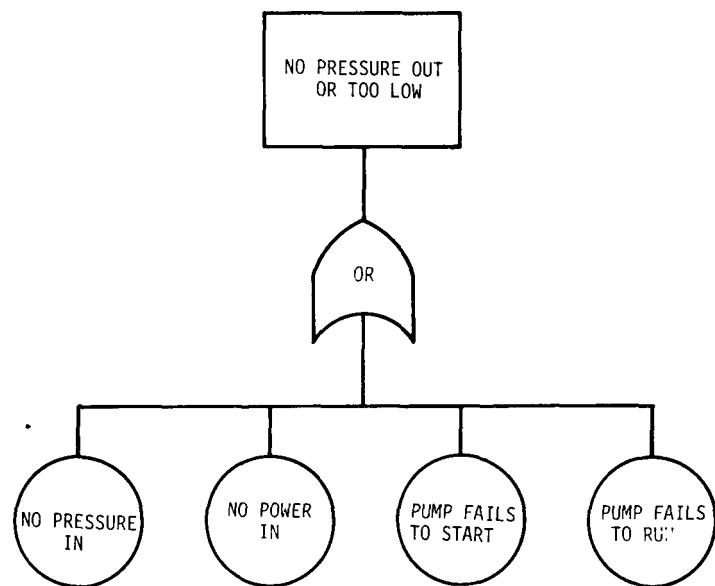

Step 3. Construct the mini-fault/success tree. As an example, Figures 1 and 2 show the mini-fault/success trees for a pump.

Step 4. Construct the decision table by using the mini-fault/success trees, treating blank spaces as 'don't care' states. Table 8 shows the decision table for a pump obtained in this way. Notice the equivalence between Tables 7 and 8.

FIG. 1 MINI-FAULT/SUCCESS TREE I FOR PUMP

FIG. 2 MINI-FAULT/SUCCESS TREE II FOR PUMP

TABLE 8. DECISION TABLE FOR PUMP BY DEDUCTIVE METHOD.

| Row | Main Flow | Input 2 Power | Internal Mode | Output |

|-----|-----------|---------------|---------------|--------|

| 1   | 0         | -1            | -1            | 0      |

| 2   | -1        | 0             | -1            | 0      |

| 3   | -1        | -1            | 4             | 0      |

| 4   | -1        | -1            | 5             | 0      |

| 5   | 1         | 1             | 0             | 1      |

Step 5. Check the completeness of decision tables. Make sure each mode of operation of the component has been included in the decision table unless it is impossible or negligible.

### 3.4 The Use of Decision Tables in the Construction of Fault Trees

In order to construct fault trees for general systems, information is required both to describe the system itself, and the operation of the specific components within the system. The decision table methodology has been used to describe the operation of the specific components of the system. The use of such decision tables in constructing fault trees will now be illustrated referring to Table 8 of Section 3.3. The event "no output from pump" will be used as an event to be analyzed. This might be the TOP event of a tree, or some intermediate event which would be required to produce a zero input to a succeeding component.

Given the desired output state, a search is made for rows with the correct state, in this case Rows 1 through 4 of Table 8. Since any one of these rows has the correct output, they are connected by an OR gate, each row being a single input (see the mini-fault tree used for the pump).

Since in all rows, two of the three signals are of the "don't care" type, each row is replaced by a single event. Thus, Row 2 is replaced by the event "no power," which must be developed further with the use of another decision table. Row 4 is replaced by the event "pump fails to start", which is a primary failure and thus becomes a direct primary input event.

If the desired output state were "normal output from pump", then a search of the rows reveals that only row 5 gives the correct output. Here, there are three states defined, all of which must be true for the output state to be 1. The result, then, is an AND gate with the three appropriate inputs. In this case, one input represents a primary event (pump good), and thus terminates that branch. However, the other inputs to the AND gate are component input states, and must therefore, be traced backwards to the previous components and developed further.

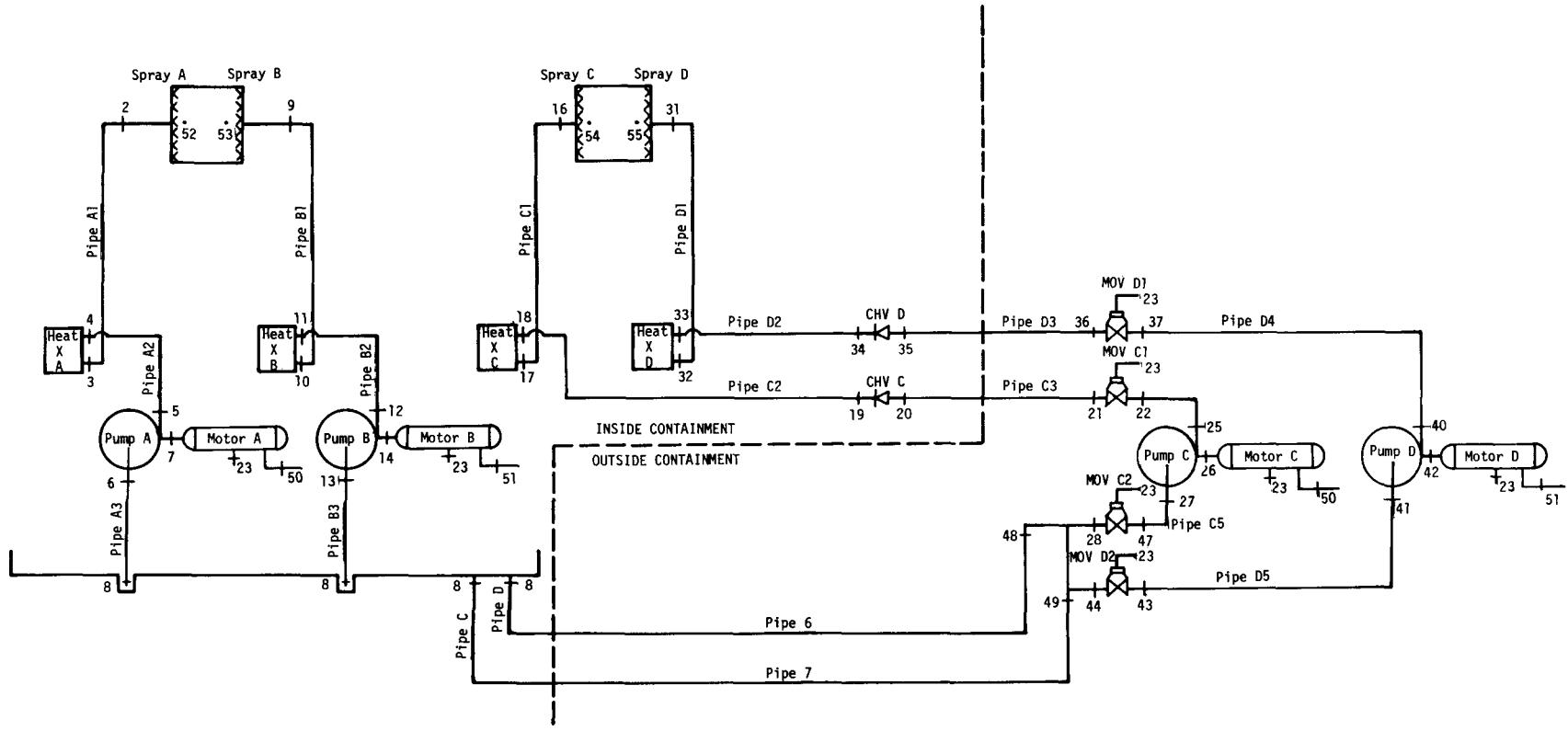

## 4. APPLICATIONS