# **Optimization of Processing and Modeling Issues for Thin-Film Solar Cell Devices**

**Annual Report

3 February 1997 - 2 February 1998**

R.W. Birkmire, J.E. Phillips, W.N. Shafarman,

S.S. Hegedus, and B.E. McCandless

*Institute of Energy Conversion*

*University of Delaware*

*Newark, Delaware*

National Renewable Energy Laboratory

1617 Cole Boulevard

Golden, Colorado 80401-3393

A national laboratory of the U.S. Department of Energy

Managed by Midwest Research Institute

for the U.S. Department of Energy

under contract No. DE-AC36-83CH10093

# **Optimization of Processing and Modeling Issues for Thin-Film Solar Cell Devices**

**Annual Report

3 February 1997 - 2 February 1998**

R.W. Birkmire, J.E. Phillips, W.N. Shafarman,

S.S. Hegedus, and B.E. McCandless

*Institute of Energy Conversion*

*University of Delaware*

*Newark, Delaware*

NREL technical monitor: B. von Roedern

National Renewable Energy Laboratory

1617 Cole Boulevard

Golden, Colorado 80401-3393

A national laboratory of the U.S. Department of Energy

Managed by Midwest Research Institute

for the U.S. Department of Energy

under contract No. DE-AC36-83CH10093

Prepared under Subcontract No. XAK-7-17609-01

November 1998

## **NOTICE**

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

Available to DOE and DOE contractors from:

Office of Scientific and Technical Information (OSTI)

P.O. Box 62

Oak Ridge, TN 37831

Prices available by calling 423-576-8401

Available to the public from:

National Technical Information Service (NTIS)

U.S. Department of Commerce

5285 Port Royal Road

Springfield, VA 22161

703-605-6000 or 800-553-6847

or

DOE Information Bridge

<http://www.doe.gov/bridge/home.html>

Printed on paper containing at least 50% wastepaper, including 10% postconsumer waste

## Summary

The overall mission of the Institute of Energy Conversion is the development of thin film photovoltaic cells, modules, and related manufacturing technology and the education of students and professionals in photovoltaic technology. The objectives of this four-year NREL subcontract are to advance the state of the art and the acceptance of thin film PV modules in the areas of improved technology for thin film deposition, device fabrication, and material and device characterization and modeling, relating to solar cells based on  $\text{CuInSe}_2$  and its alloys, on a-Si and its alloys, and on CdTe.

### ***CuInSe<sub>2</sub>-based Solar Cells***

#### **High Bandgap CuInSe<sub>2</sub> Alloys**

$\text{CuInSe}_2$  has a bandgap of 1.0 eV and most  $\text{Cu}(\text{InGa})\text{Se}_2$ -based devices have absorber layers with  $\text{Ga}/(\text{In}+\text{Ga}) = 0.25$  which gives a bandgap of 1.15 eV and results in devices with open circuit voltages  $< 0.65\text{V}$ . Higher Ga concentrations to increase the  $\text{Cu}(\text{InGa})\text{Se}_2$  bandgap result in a trade-off of higher open circuit voltage and lower short circuit current which may allow increased cell efficiency. Further, module performance should be improved due to lower resistive losses, thinner ZnO with less optical loss and/or greater interconnect spacing with reduced associated area-related losses.

We have previously demonstrated  $\text{Cu}(\text{InGa})\text{Se}_2$  solar cells with 15% efficiency for  $\text{Ga}/(\text{In}+\text{Ga}) = 0.5$  or bandgap ( $E_g = 1.3\text{ eV}$  [101, 102]. With higher bandgap a decrease in cell efficiency was shown to be caused by poor collection of light generated minority carriers in the  $\text{Cu}(\text{InGa})\text{Se}_2$  absorber layers and in this report, we have expanded the characterization of  $\text{Cu}(\text{InGa})\text{Se}_2$  devices with increasing Ga content and bandgap. Further, we have begun to investigate other  $\text{CuInSe}_2$ -based alloy materials,  $\text{CuInS}_2$  and  $\text{Cu}(\text{InAl})\text{Se}_2$ , which may provide alternative means to achieve improved device performance with  $E_g > 1.3\text{ eV}$ .

#### **Reduced Cu(InGa)Se<sub>2</sub> Deposition Temperature and Thickness**

There are many technical issues which need to be addressed to effectively enable the transfer of  $\text{Cu}(\text{InGa})\text{Se}_2$  deposition and device fabrication technology from the laboratory to manufacturing scale. In general, these issues provide a means to reduce thin film semiconductor process costs. Shorter deposition time can be achieved with reduced film thickness and increased deposition rate. Thinner absorber films reduce the total amount of material used and allow faster process throughput. The minimum thickness of the  $\text{Cu}(\text{InGa})\text{Se}_2$  absorber layer may be determined by the nucleation of the film to form a continuous layer or by the film morphology. From a device perspective, the minimum thickness may be determined by the minority carrier diffusion length and optical absorption coefficient of the  $\text{Cu}(\text{InGa})\text{Se}_2$  or the ability to incorporate optical confinement.

Lower substrate temperature ( $T_{ss}$ ) can lower processing costs by reducing thermally induced stress on the substrate, allowing faster heat-up and cool-down, and decreasing the heat load and stress on the entire deposition system. In addition, with lower substrate temperature, stress on the glass substrate can be reduced and alternative substrate materials, like a flexible polymer web, could be utilized.

We have addressed the need to improve process throughput by reducing the  $\text{Cu}(\text{InGa})\text{Se}_2$  thickness and deposition temperature. The approach during this work has been to first define a baseline process for  $\text{Cu}(\text{InGa})\text{Se}_2$  deposition by multisource elemental evaporation and solar cell fabrication. All other deposition parameters are then held fixed to determine the effects of varying either the substrate temperature or, by changing the deposition time, film thickness. Material

properties of the resulting Cu(InGa)Se<sub>2</sub> films have been characterized and their device behavior has been measured and analyzed.

## Team Participation

IEC is a member of the National CIS Team under the NREL Thin Film Partnership Program. The CIS Team effort includes four working groups (WG). Of these, IEC has been a member of the Transient Effects WG and the New Junction WG, for which William Shafarman is the Group Leader.

### *New Junction*

The New Junction WG has identified two tasks and IEC has contributed to work on each. The objective of the first task is to develop non-cadmium containing buffer layers. The priority is on vacuum processes which could potentially be incorporated in-line, and chemical bath deposition is not considered a primary option. The objective of the second task is to develop improved TCO layers to minimize losses for module fabrication and quantify the effect of TCO layers on module performance. This task is focusing on the high conductivity TCO layers.

### *Transient Effects*

The CuInSe<sub>2</sub> thin film partnership program organized a transient effects team to determine if present I-V testing procedures can predict the daily output of CuInSe<sub>2</sub>-based modules and cells under field conditions; and, if they cannot, to determine what new testing procedures are needed.

## **a-Si:H-based Solar Cells**

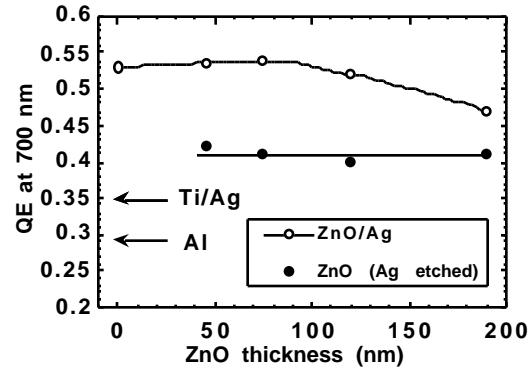

The focus of a-Si research was on contacts and interfaces. This work was motivated by results from the previous year which showed that the electrical behavior of the n-layer/TCO contact was critical to incorporating a high performance TCO/Ag back reflector and achieving efficiencies over 10%.

## **Current-Voltage Characterization of TCO Contacts**

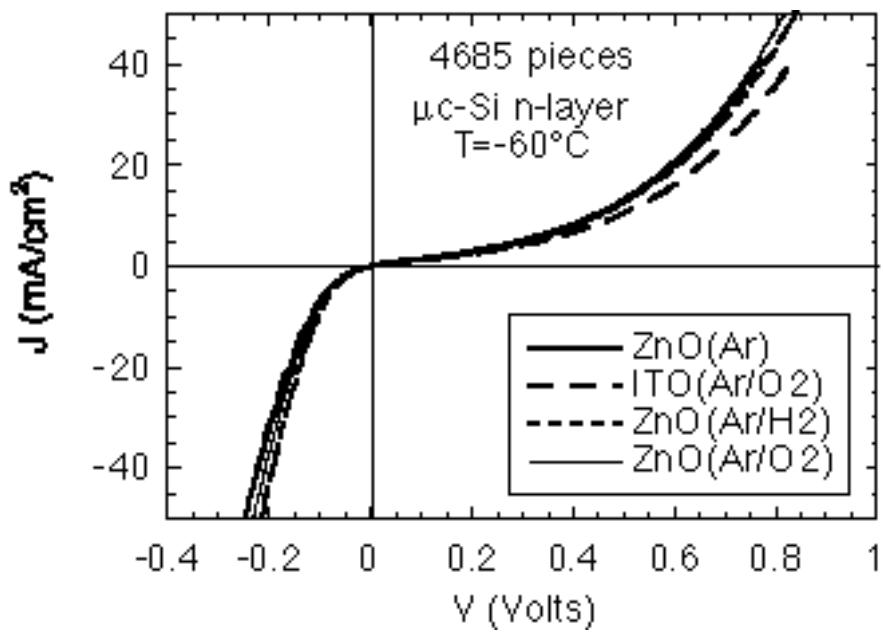

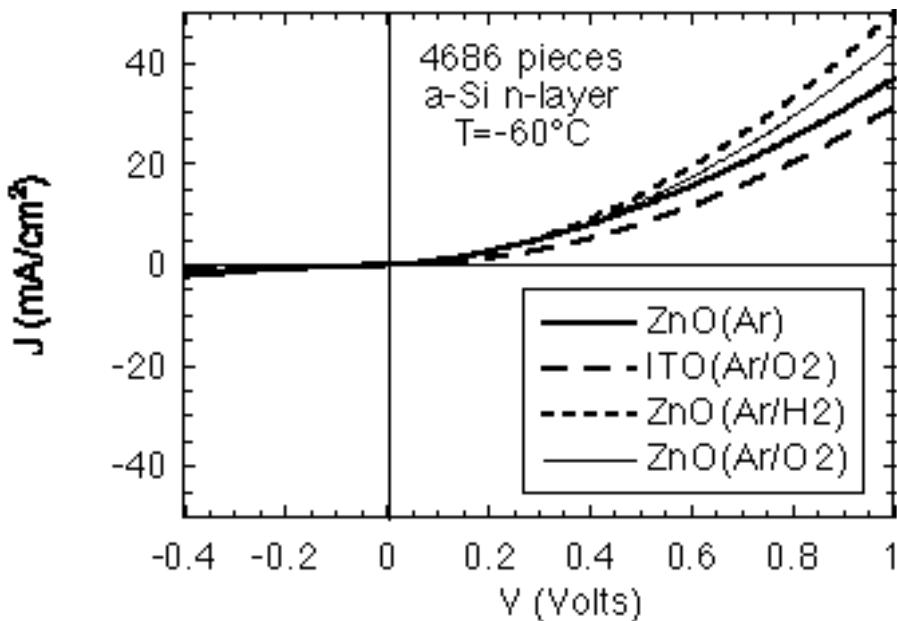

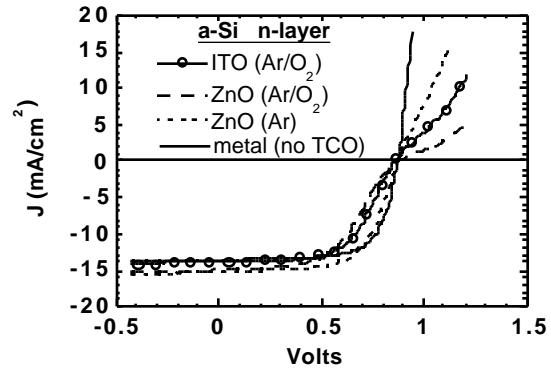

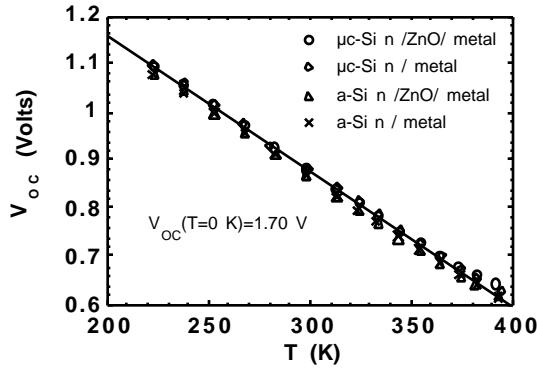

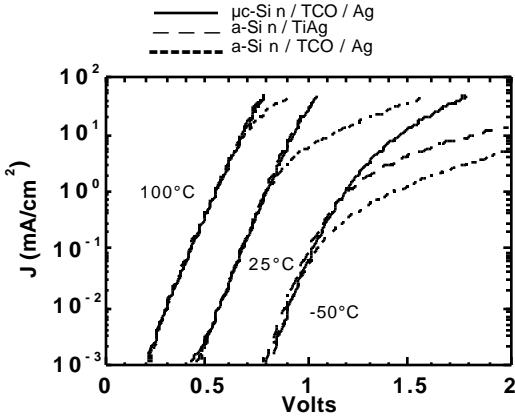

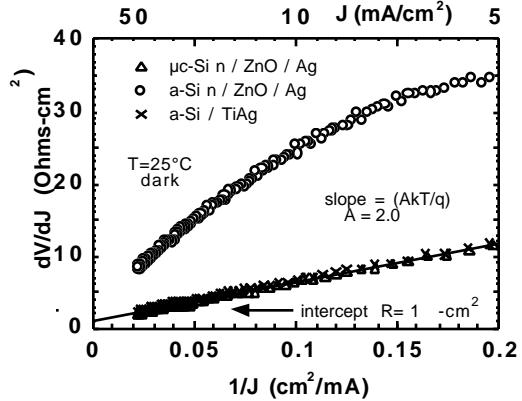

We investigated the current-voltage-temperature dependence of the following contacts, where TCO refers to sputtered ITO or ZnO: TCO/a-Si i-layer, TCO/a-Si n-layer, TCO/μc-Si n-layer, textured SnO<sub>2</sub>/a-Si n-layer and textured SnO<sub>2</sub>/μc-Si n-layer. Regarding the contact between sputtered TCO and a-Si i-layers, ITO has a larger barrier compared to ZnO. Thus, ITO makes a better junction, hence poorer Ohmic contact, with a-Si i-layers. Also, sputtering ZnO in Ar/O<sub>2</sub> gives a higher barrier and more blocking contact with a-Si compared to sputtering ZnO in Ar or Ar/H<sub>2</sub>. Thus, the barrier between ZnO and a-Si depends on the ZnO sputtering conditions. It is not known if this is an interfacial or bulk effect. Regarding the contact between sputtered TCO and a-Si or μc-Si n-layers, it was found that the μc-Si n-layers have nearly-Ohmic behavior with ITO, ZnO or SnO<sub>2</sub> contacts at T > 25°C unlike a-Si n-layers. The μc-Si n-layers have lower contact resistance than a-Si n-layers. JV behavior at T > 25°C with the a-Si or μc-Si n-layers was nearly independent of the various sputtered TCO contacts. We found that the a-Si n/SnO<sub>2</sub> contact is more blocking at T < 25°C than is the μc-Si n/SnO<sub>2</sub> contact. Thus, μc-Si n-layers are essential for good Ohmic contacts to TCO for either top or bottom contacts. Their high conductivity allows the decoupling of the electrical requirements for the contact from the optical requirements, and allows the device to achieve full benefit of an optical back reflector or other transparent contact without any additional electrical losses.

We also investigated the contact between the p-layer and various glass/TCO substrates for superstrate p-i-n cells as part of our on-going study of ZnO/p contacts and ZnO substrates in collaboration with R. Gordon at Harvard University. It was found that a new process for APCVD ZnO yields much better device performance than previous APCVD ZnO material, and that straightforward changes to the deposition of the p-layer, such as increasing the B dopant flow can give significant improvements in FF and  $V_{oc}$  of ZnO/p-i-n devices.

### **Effect of Interface on $V_{oc}$**

In an effort to improve the stabilized  $V_{oc}$ , we attempted to duplicate studies from Penn State, NREL and elsewhere by modifying the initially deposited i-layer to include either hydrogen dilution or graded a-SiC. This resulted in only a small (~10 mV) improvement in initial  $V_{oc}$  and no improvement in degraded  $V_{oc}$  or efficiency. We conclude that without hydrogen dilution of the bulk i-layer we will not see gains reported by others with hydrogen diluted interface layers since the bulk degradation dominates.

### **Team Participation**

IEC is a member of the National a-Si Team under the Thin Film Partnership Program. Steve Hegedus is the group leader of the Device Design and Interface team. Much of the work described above was performed as part of the teaming activities.

### **CdTe-based Solar Cells**

Production of reliable and reproducible CdS window layers and contacts for stable, high performance CdS/CdTe solar cells are the key issues confronting development of thin-film CdTe solar cells. Meeting these objectives with manufacturing-compatible processes is crucial to satisfying the overall NREL program goals and requires an understanding of the controlling properties and mechanisms. IEC research in this phase was concentrated on: 1) quantifying and controlling CdS-CdTe interaction; 2) analyzing CdTe contact formation and properties; and 3) analyzing device behavior after stress-induced degradation. Through extensive interaction with the National CdTe R&D Team, the applicability of the results and processes to CdS/CdTe cells made by different techniques has been demonstrated, enabling a consistent framework to be used for understanding the relationship between device fabrication and operation.

### **Devices With Thin CdS**

IEC demonstrated improved understanding and control of CdS diffusion by employing evaporated  $\text{CdTe}_{1-x}\text{S}_x$  absorber layers and by modifying post-deposition treatments to anneal crystal defects prior to  $\text{CdCl}_2$  delivery. Significant results include: 1) determining the effect of  $\text{CdTe}_{1-x}\text{S}_x$  alloy composition on the effective CdS diffusion rate; 2) reducing CdS window layer consumption by 3X; 3) fabricating devices with  $J_{sc} > 25 \text{ mA/cm}^2$  with evaporated CdS layers; 4) determining device performance as a function of *final* CdS thickness; and 5) development of an all-vapor cell fabrication process.

### **Quantification of CdS-CdTe Interdiffusion**

During Phase I, fundamental issues confronting fabrication of devices with ultra-thin CdS were investigated, allowing the CdS consumption process to be understood and controlled. Through teaming activity, the role of TCO properties was further elucidated. In particular: 1) measurement protocols were developed to analyze pinholes in the CdS layer and CdS diffusion into the absorber layer; 2) low-temperature equilibrium data points were added to the CdS-CdTe phase diagram; 3) CdS diffusion into CdTe-based absorber layers with a range of sulfur content was quantified; 4)

CdS diffusion in CdTe was examined for varying post-deposition treatment conditions; 5) the micro-crystal structure of the resulting absorber and absorber-window layer interface was examined by TEM for varying post-deposition treatment conditions; 6) a complete materials analysis with respect to interdiffusion in CdTe/CdS cells was made using CdTe/CdS furnished by six groups of the CdTe Team, leading to development of a phenomenological model of CdTe/CdS devices; and 7) TCO properties were identified which render the device structure more tolerant to complete CdS loss, leading to improvements in baseline efficiency of physical vapor deposited CdTe/CdS devices.

## **Contact to CdTe**

A key chemical component of working CdTe contacts was clearly identified for the “wet chemical” fabrication processes typically employed and an alternative, all-vapor, method for fabricating low resistance contacts was developed. Measurement protocols using variations in light intensity and temperature during current-voltage measurements were employed to analyze the CdTe contact characteristics of devices made by different processes having different contacts. Coupled with the stress-induced degradation and recontacting studies being carried jointly with the CdTe Stability Team, a model is being formulated which links operational and stability aspects of CdTe/CdS cells.

## **Team Participation**

IEC actively participated in the National CdTe R&D Team by fabricating contacts for the stability sub-team and devices for the CdS sub-team, analyzing films and devices for both sub-teams, reporting results through presentations and written reports, and hosting a full-day team meeting on April 30, 1997. In particular, devices were fabricated on different TCO to augment investigation of TCO/CdTe junction influence as  $d(CdS)$  is reduced. Contacts to CdTe were deposited and evaluated on CdTe/CdS samples from Solar Cells, Inc., using five different conductors, and from Golden Photon, Inc. A comprehensive x-ray diffraction analysis was performed on samples made by six groups within the team, and a full report was submitted at the April, 1997 team meeting.

## **LIST OF CONTRIBUTORS**

### **PRINCIPAL INVESTIGATORS**

Robert W. Birkmire

Steven S. Hegedus

Brian E. McCandless

James E. Phillips

T.W.F. Russell

William N. Shafarman

### **PRINCIPAL RESEARCHERS**

Wayne A. Buchanan

Marylin Huff

### **VISITING PROFESSIONALS**

Erten Eser, Visiting Scientist

Dirk Hofmann, Visiting Scholar

Josef Kallo, Visiting Scholar

Sylvain Marsillac, Visiting Scholar

Julius Mwabora, Fulbright Fellow

Nese Orbey, Visiting Engineer

Issakha Youm, Fulbright Scholar

Xiangbo Zeng, Visiting Scholar

### **POST-DOCTORAL FELLOWS**

Michael Maldei

Matheswaran Marudachalam

Sandeep Verma

Robert Wunder

Jie Zhu

### **TECHNICAL SUPPORT**

Charles Debo

Ronald Dozier

Shannon Fields

Sally Gordon

Dmitriy Gusakov

Kevin Hart

Tom Hughes-Lampros

John Laker

Herbert Wardell

### **GRADUATE STUDENTS**

Daniel Aiken

Michael Engelmann

Hao Feng

Moses Haimbodi

Greg Hanket

Wei Liu

Chao Ying Ni

Atul Pant

David Smith

Jochen Titus

Zhao-Hui Yang

**STUDENTS**

Brian Atkinson

George Brown

Chris Campbell

Carrie Desimone

Daniel Eichenwald

Kelly Kuhns

Natalie Paolantonio

Johnny Yu

**DOCUMENT PREPARATION**

Linda Granger

## TABLE OF CONTENTS

|                                                                                     |            |

|-------------------------------------------------------------------------------------|------------|

| <b>SUMMARY.....</b>                                                                 | <b>i</b>   |

| <b>LIST OF CONTRIBUTORS .....</b>                                                   | <b>v</b>   |

| <b>TABLE OF CONTENTS.....</b>                                                       | <b>vii</b> |

| <b>LIST OF FIGURES.....</b>                                                         | <b>ix</b>  |

| <b>LIST OF TABLES.....</b>                                                          | <b>xiv</b> |

| <br>                                                                                |            |

| <b>1. INTRODUCTION .....</b>                                                        | <b>1</b>   |

| <b>1.1 CuInSe<sub>2</sub>-based Solar Cells .....</b>                               | <b>1</b>   |

| <b>1.2 a-Si:H-based Solar Cells.....</b>                                            | <b>1</b>   |

| <b>1.3 CdTe-based Solar Cells .....</b>                                             | <b>2</b>   |

| <b>1.4 Organization of the Report.....</b>                                          | <b>2</b>   |

| <br>                                                                                |            |

| <b>2. CuInSe<sub>2</sub>-BASED SOLAR CELLS .....</b>                                | <b>3</b>   |

| <b>2.1 High Bandgap CuInSe<sub>2</sub> Alloys.....</b>                              | <b>3</b>   |

| 2.1.1 Introduction .....                                                            | 3          |

| 2.1.2 Cu(In,Ga)Se <sub>2</sub> device analysis.....                                 | 3          |

| 2.1.3 CuInS <sub>2</sub> .....                                                      | 5          |

| 2.1.4 Cu(InAl)Se <sub>2</sub> .....                                                 | 8          |

| <b>2.2 Reduced Cu(InGa)Se<sub>2</sub> Deposition Temperature and Thickness.....</b> | <b>12</b>  |

| 2.2.1 Introduction .....                                                            | 12         |

| 2.2.2 Experimental procedures.....                                                  | 12         |

| 2.2.3 Results: Deposition temperature .....                                         | 13         |

| 2.2.4 Results: Film thickness .....                                                 | 16         |

| 2.2.5 Device measurements and analysis.....                                         | 16         |

| <b>2.3 Teaming Results .....</b>                                                    | <b>18</b>  |

| 2.3.1 Introduction .....                                                            | 18         |

| 2.3.2 New junction results .....                                                    | 18         |

| 2.3.3 Transient Effects.....                                                        | 21         |

| <br>                                                                                |            |

| <b>3. a-Si:H-BASED SOLAR CELLS.....</b>                                             | <b>40</b>  |

| <b>3.1 Summary.....</b>                                                             | <b>40</b>  |

| <b>3.2 PECVD system operational improvements.....</b>                               | <b>40</b>  |

|                                                                                                                   |            |

|-------------------------------------------------------------------------------------------------------------------|------------|

| <b>3.3 Device deposition conditions .....</b>                                                                     | <b>41</b>  |

| <b>3.4 Devices with continuous plasma “soft start” p-layer.....</b>                                               | <b>42</b>  |

| <b>3.5 Effect of interface layers on <math>V_{oc}</math> and stability.....</b>                                   | <b>43</b>  |

| <b>3.6 Effect of p-layer doping and alternate TCO substrates: ZnO and<br/>SnO<sub>2</sub>/ZnO.....</b>            | <b>45</b>  |

| <b>3.7 Electrical and optical study of high performance TCO/metal<br/>back reflector .....</b>                    | <b>47</b>  |

| <b>3.8 Electrical characterization of sputtered TCO junctions on a-Si<br/>and μc-Si n and i-layers.....</b>       | <b>47</b>  |

| <b>4. CdTe-BASED SOLAR CELLS.....</b>                                                                             | <b>58</b>  |

| <b>4.1 Summary.....</b>                                                                                           | <b>58</b>  |

| 4.1.1 Devices with Thin CdS .....                                                                                 | 58         |

| 4.1.2 Quantification of CdS-CdTe Interdiffusion.....                                                              | 58         |

| 4.1.3 Contact to CdTe.....                                                                                        | 58         |

| 4.1.4 Team Participation.....                                                                                     | 59         |

| <b>4.2 Background.....</b>                                                                                        | <b>59</b>  |

| 4.2.1 Framework Relating CdTe/CdS Fabrication Technologies.....                                                   | 59         |

| 4.2.2 Critical issues .....                                                                                       | 66         |

| <b>4.3 CdS-CdTe Interaction .....</b>                                                                             | <b>66</b>  |

| 4.3.1 Approach and Techniques.....                                                                                | 66         |

| 4.3.2 CdS Window-Absorber Layer Interaction.....                                                                  | 79         |

| 4.3.3 Devices with CdTe <sub>1-x</sub> S <sub>x</sub> Absorber Layers and Modified Post-Deposition Treatment..... | 91         |

| 4.3.4 Influence of TCO.....                                                                                       | 102        |

| <b>4.4 CdTe Contacting in Device Structures .....</b>                                                             | <b>103</b> |

| 4.4.1 Introduction .....                                                                                          | 103        |

| 4.4.2 Physio-chemical Analysis of Contact Operation.....                                                          | 104        |

| 4.4.3 Electronic Analysis of Contact Operation.....                                                               | 106        |

| 4.4.4 Stress Testing and Analysis.....                                                                            | 107        |

| 4.4.5 Operational Model.....                                                                                      | 111        |

| <b>5. ABSTRACT.....</b>                                                                                           | <b>112</b> |

| <b>6. REFERENCES.....</b>                                                                                         | <b>113</b> |

## LIST OF FIGURES

|                                                                                                                                                                                                                                           |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

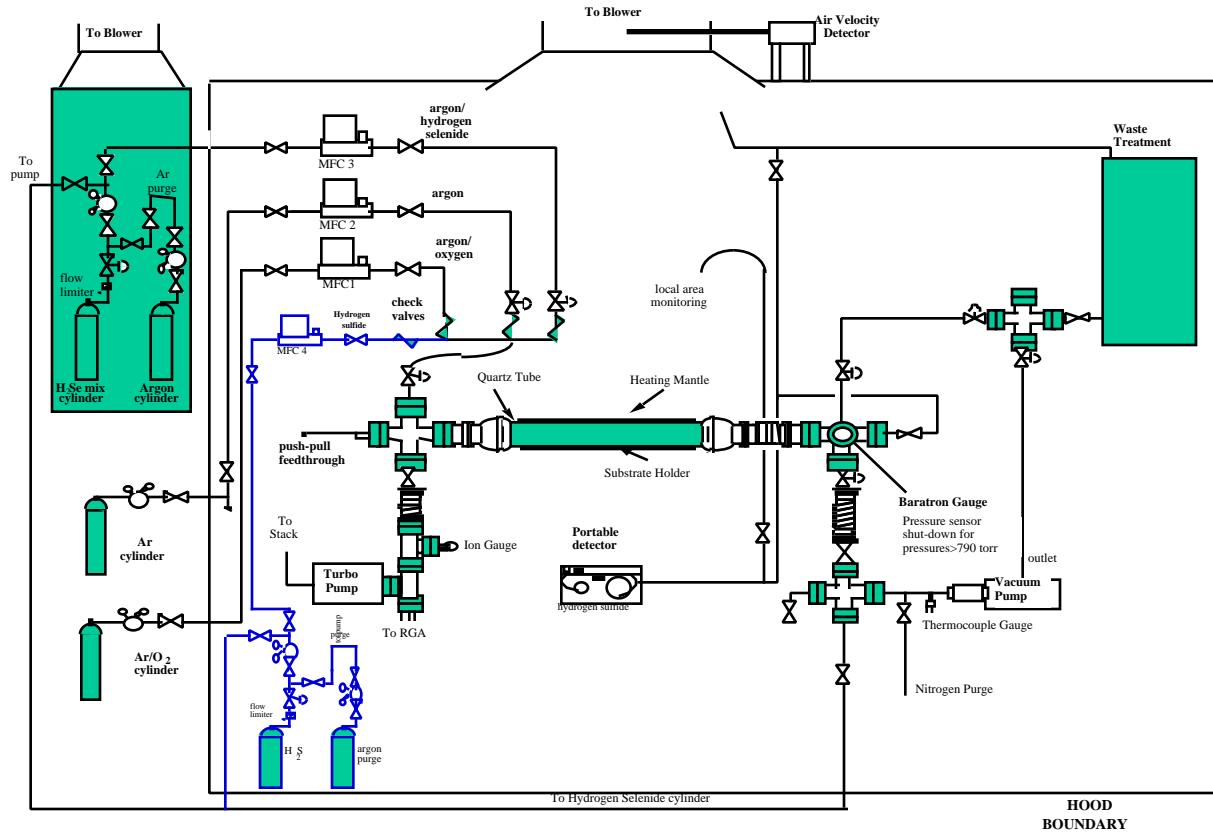

| <b>Figure 2.1 Schematic diagram of the H<sub>2</sub>Se/H<sub>2</sub>S CVD reactor including gas handling and waste treatment. ....</b>                                                                                                    | <b>7</b>  |

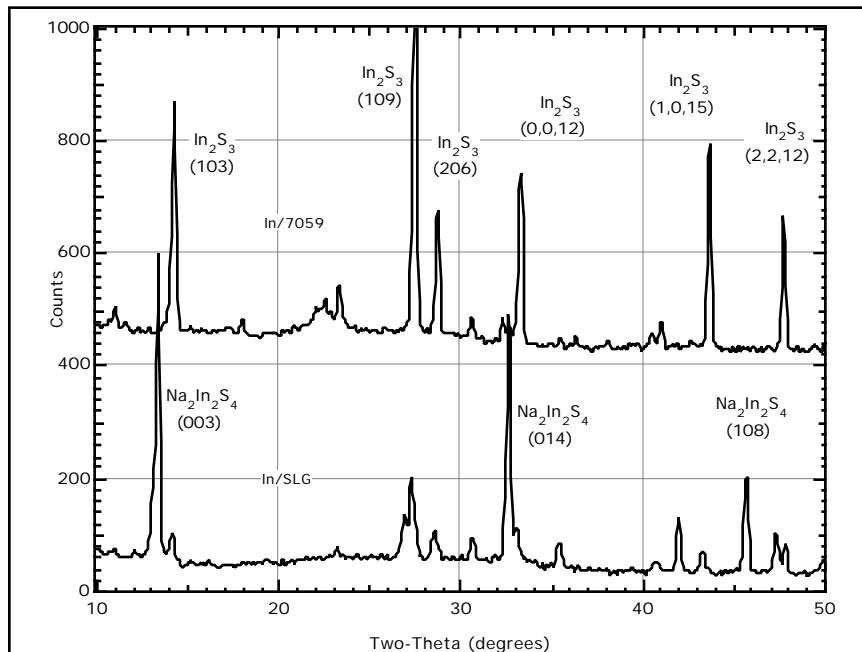

| <b>Figure 2.2 XRD scans of In films on 7059 (top) and soda lime (bottom) substrates after they were reacted in H<sub>2</sub>S at 550°C for 90 min.....</b>                                                                                | <b>7</b>  |

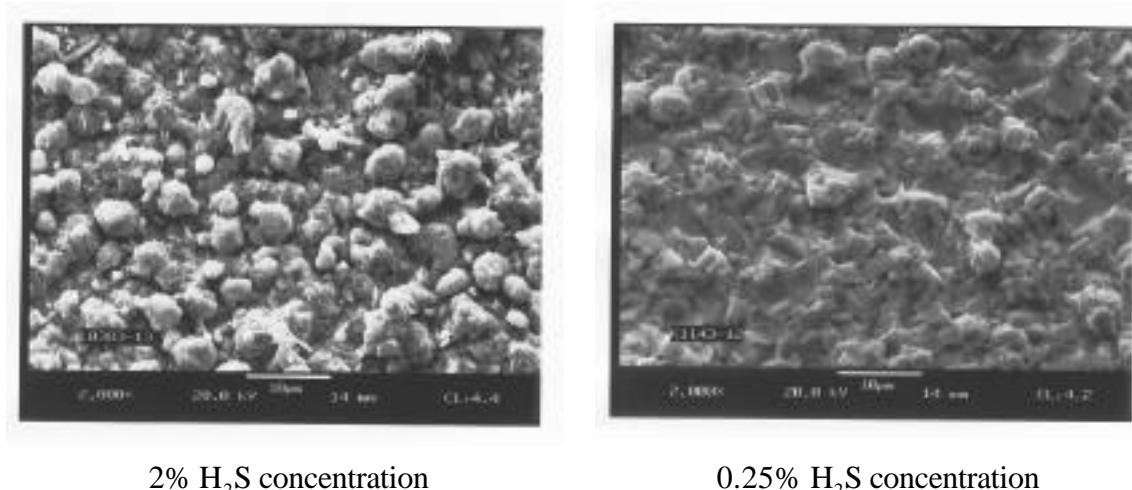

| <b>Figure 2.3 SEM micrographs at 2000x magnification showing the change in morphology of Cu/In films reacted at different H<sub>2</sub>S concentrations. ....</b>                                                                         | <b>8</b>  |

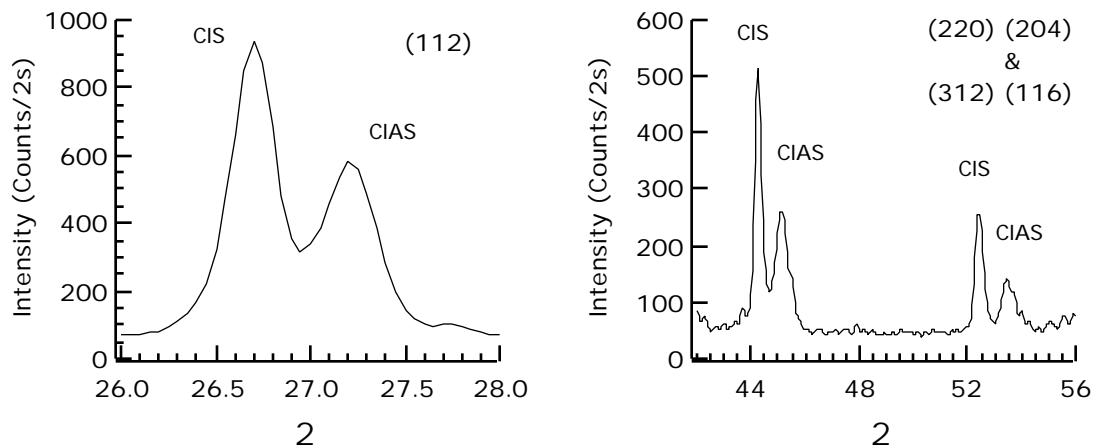

| <b>Figure 2.4 XRD pattern of a film obtained by selenizing Al/In/Cu precursor at 550°C. The Al/(Al+In) ratio in the precursor is 0.45.<br/>CIS = CuInSe<sub>2</sub>, CIAS = CuIn<sub>1-x</sub>Al<sub>x</sub>Se<sub>2</sub>.....</b>       | <b>10</b> |

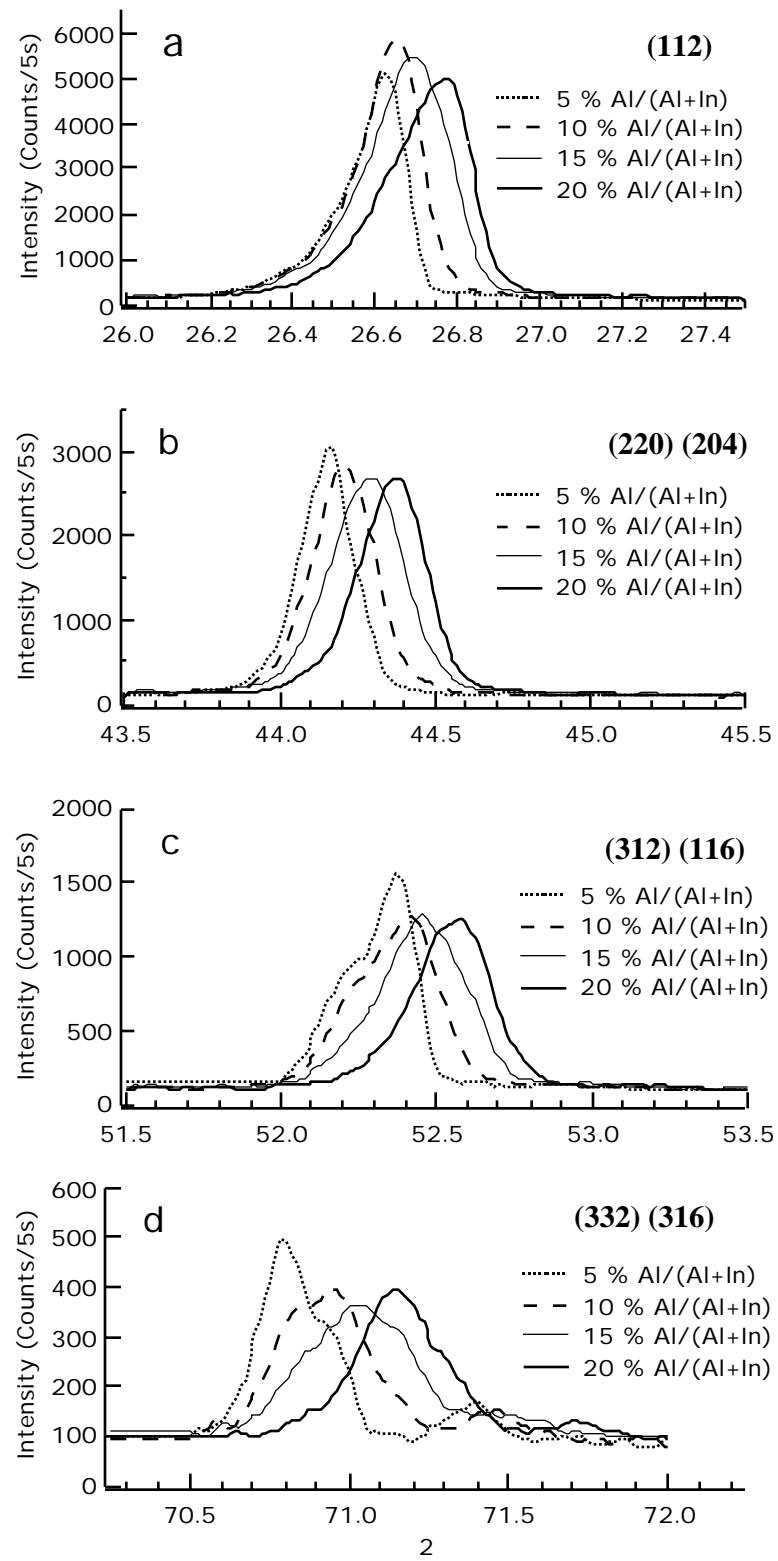

| <b>Figure 2.5 XRD plots of various peaks of a CuIn<sub>1-x</sub>Al<sub>x</sub>Se<sub>2</sub> films (from run L0393). The Al/(Al+In) concentrations in the legends are intended ratios in the precursors. ....</b>                         | <b>11</b> |

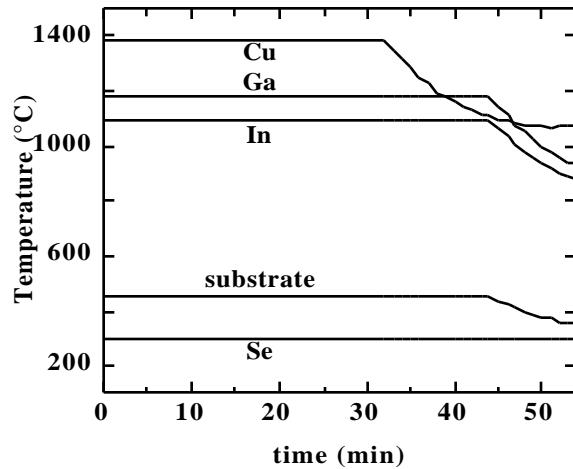

| <b>Figure 2.6 Deposition profile showing source and substrate temperatures for a standard run with T<sub>ss</sub> = 450°C. ....</b>                                                                                                       | <b>13</b> |

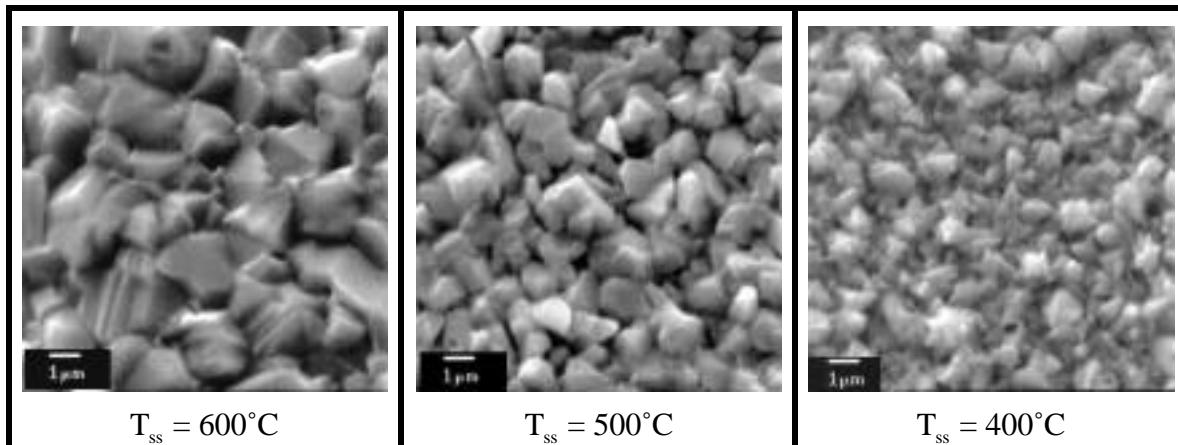

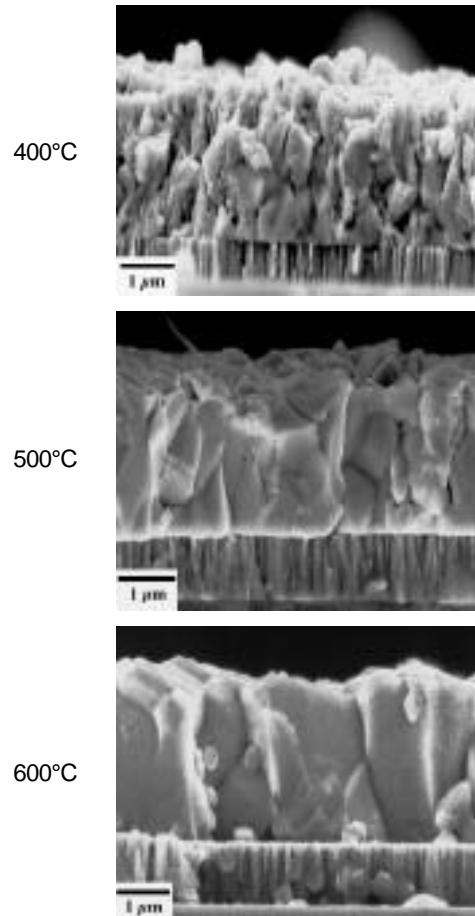

| <b>Figure 2.7 SEM micrographs showing a decrease in grain size as T<sub>ss</sub> decreases from 600 to 400°C.....</b>                                                                                                                     | <b>14</b> |

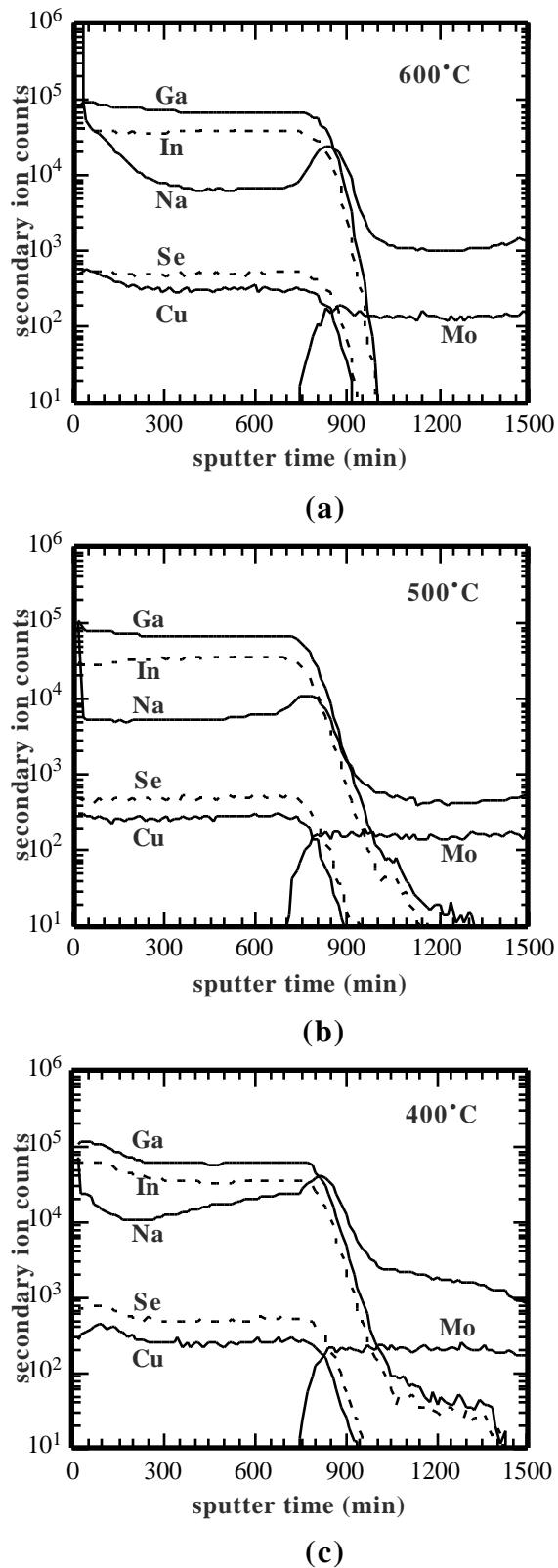

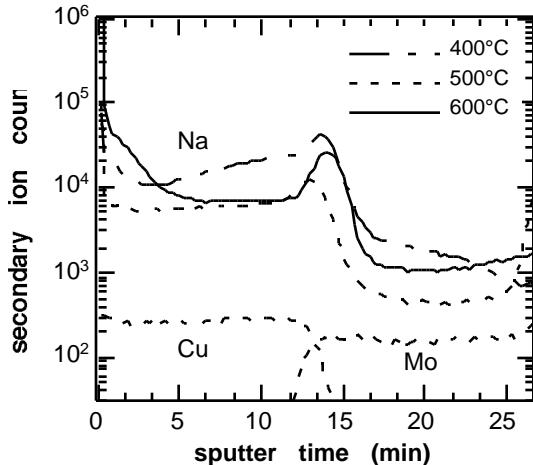

| <b>Figure 2.8 SIMS depth profiles of Cu, In, Ga, Se, Mo, and Na for films deposited with (a) T<sub>ss</sub> = 600°C, (b) 500°C, and (c) 400°C.....</b>                                                                                    | <b>15</b> |

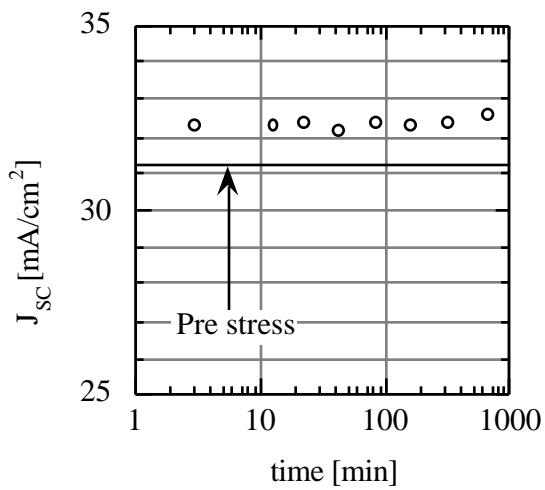

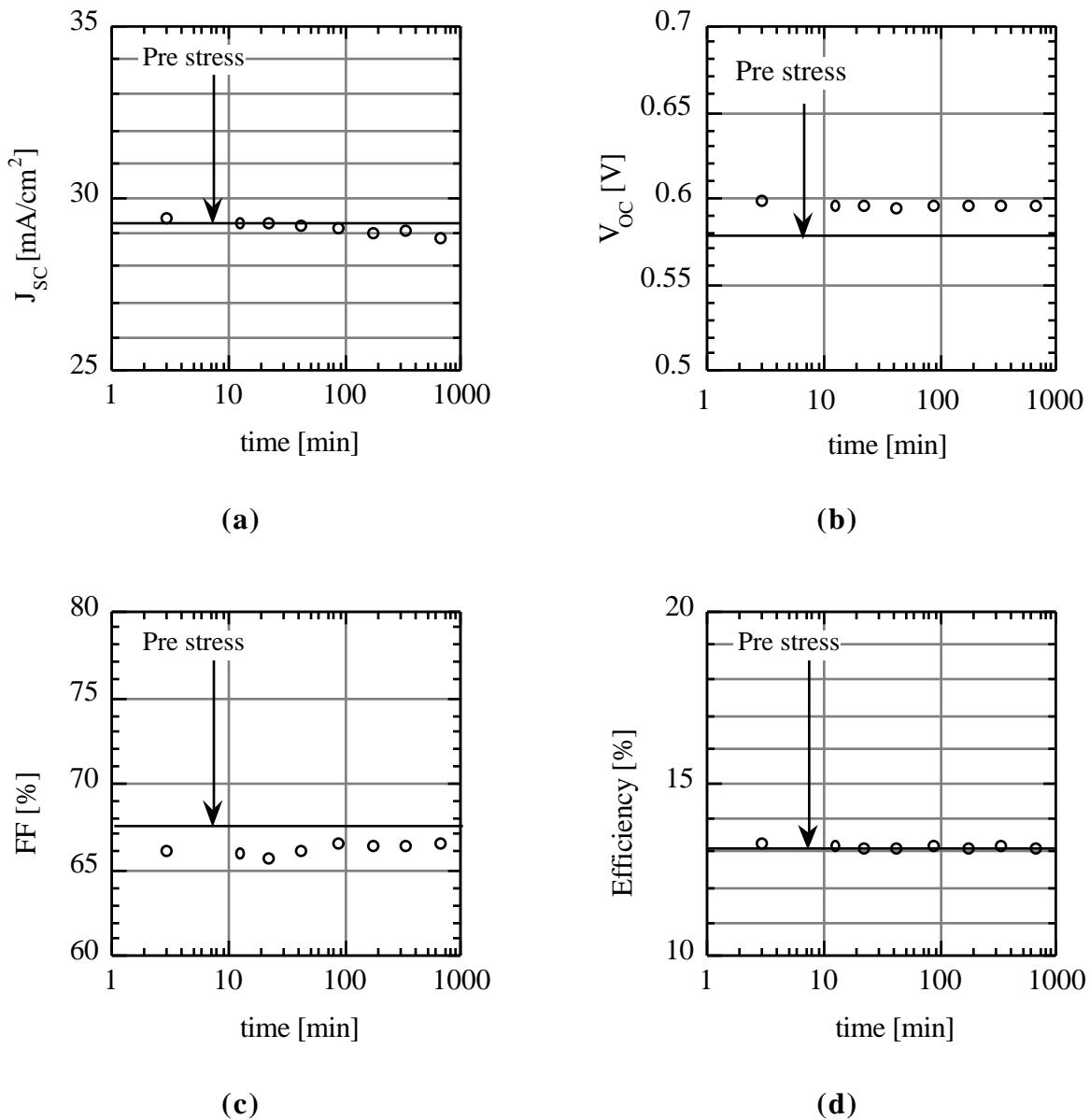

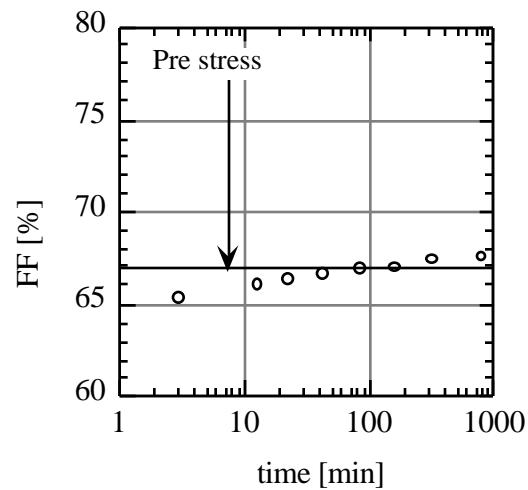

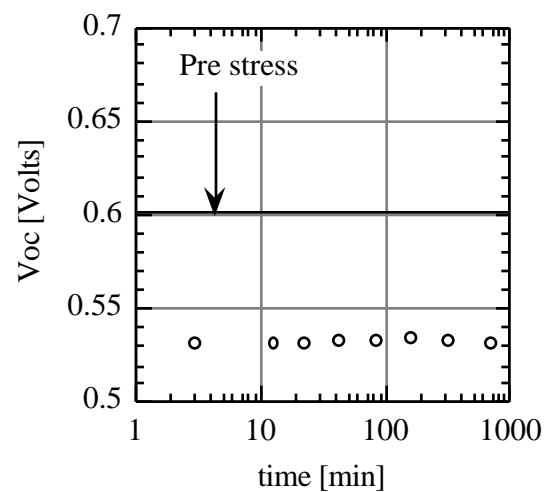

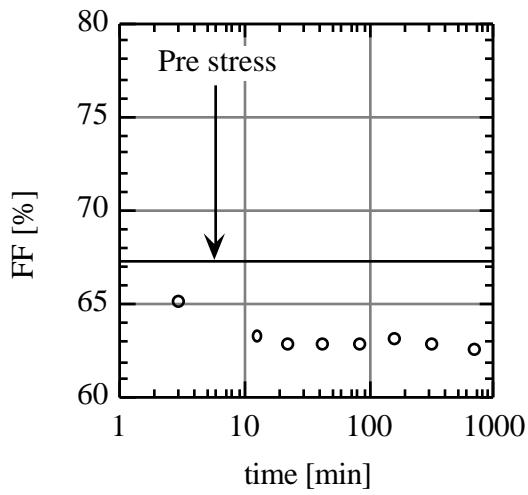

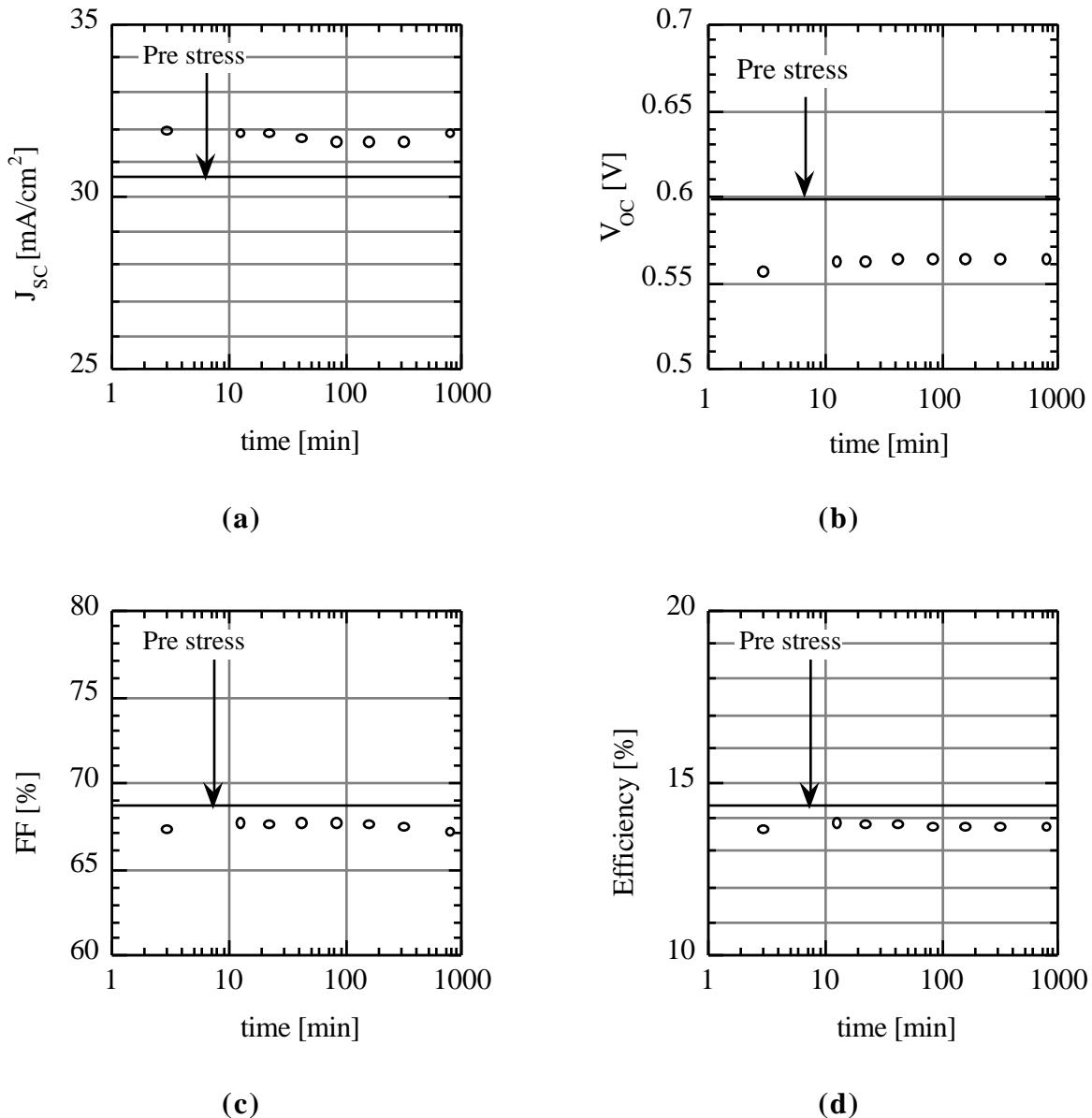

| <b>Figure 2.9 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, in the dark and 0 V for 12 hours.....</b>                                              | <b>22</b> |

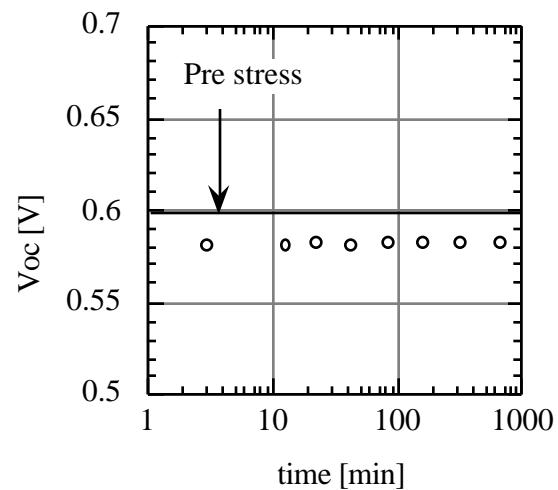

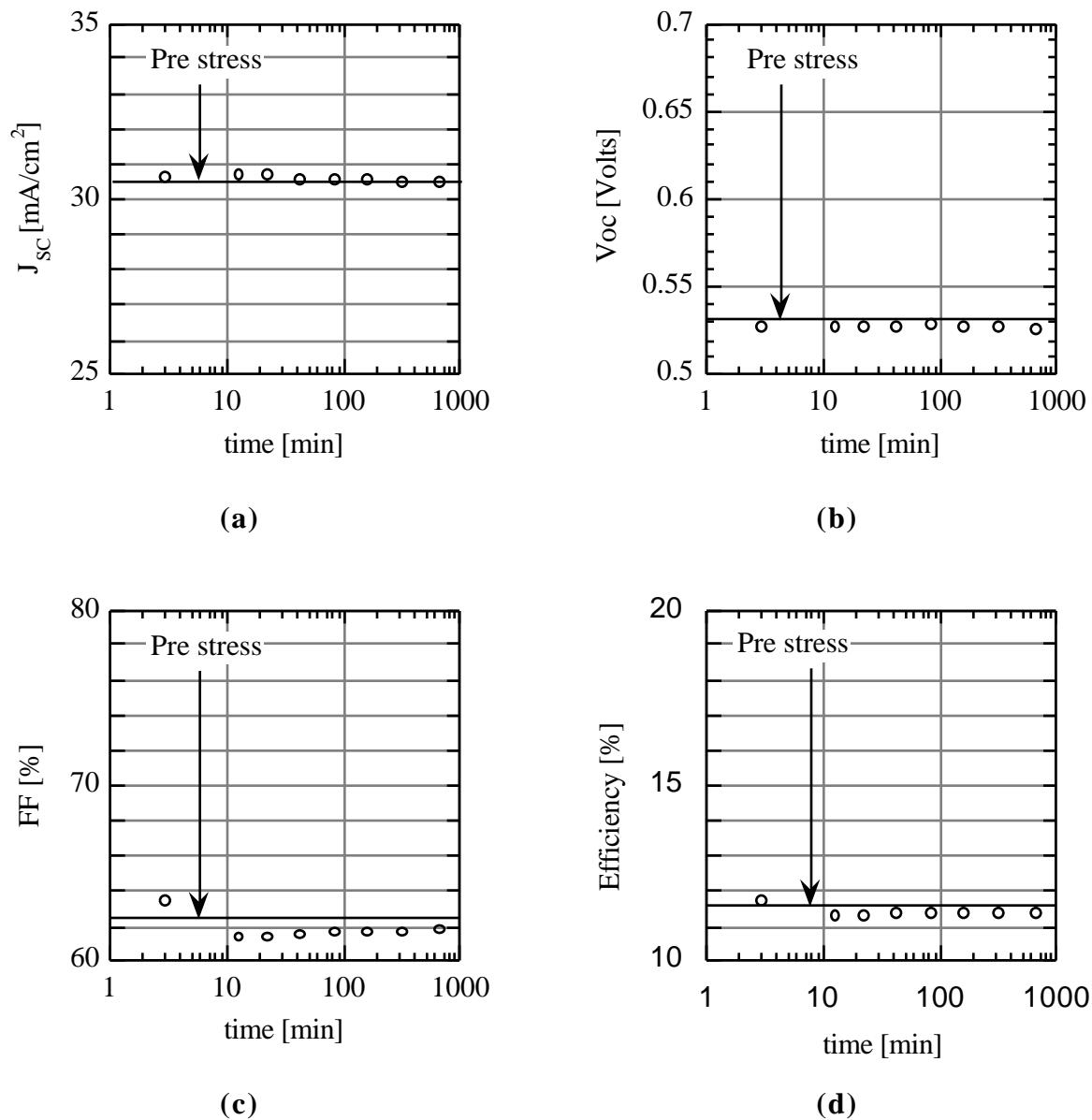

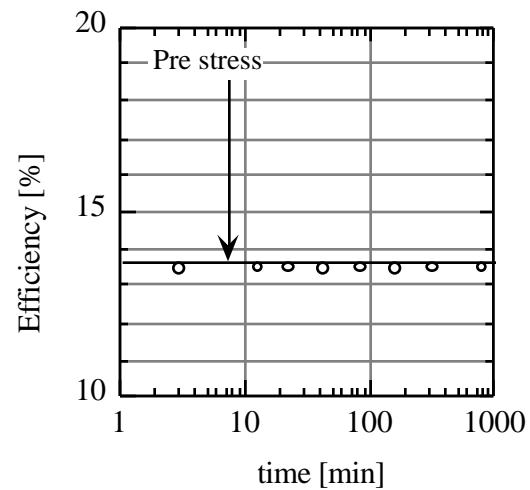

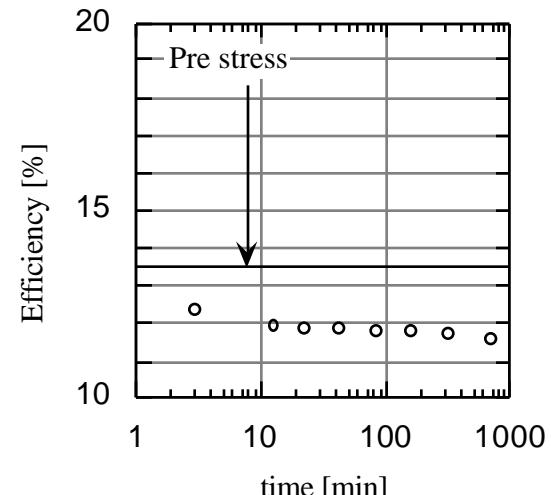

| <b>Figure 2.10 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, in the dark and at a forward current of 30 mA/cm<sup>2</sup> for 10 hours.....</b>    | <b>23</b> |

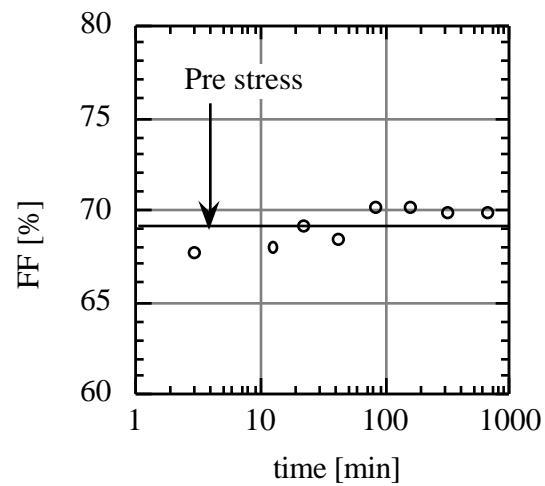

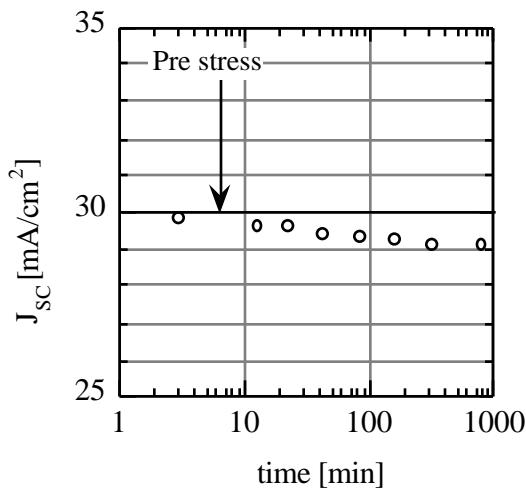

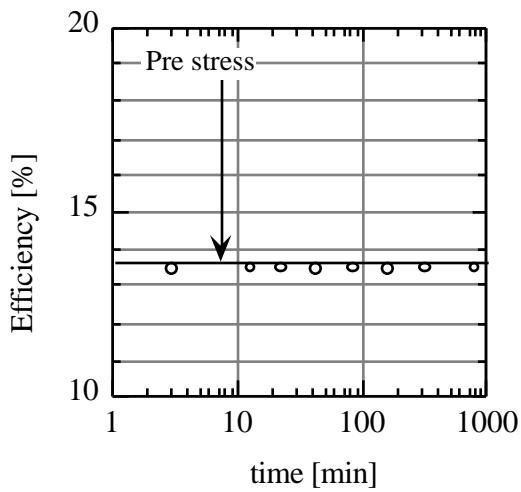

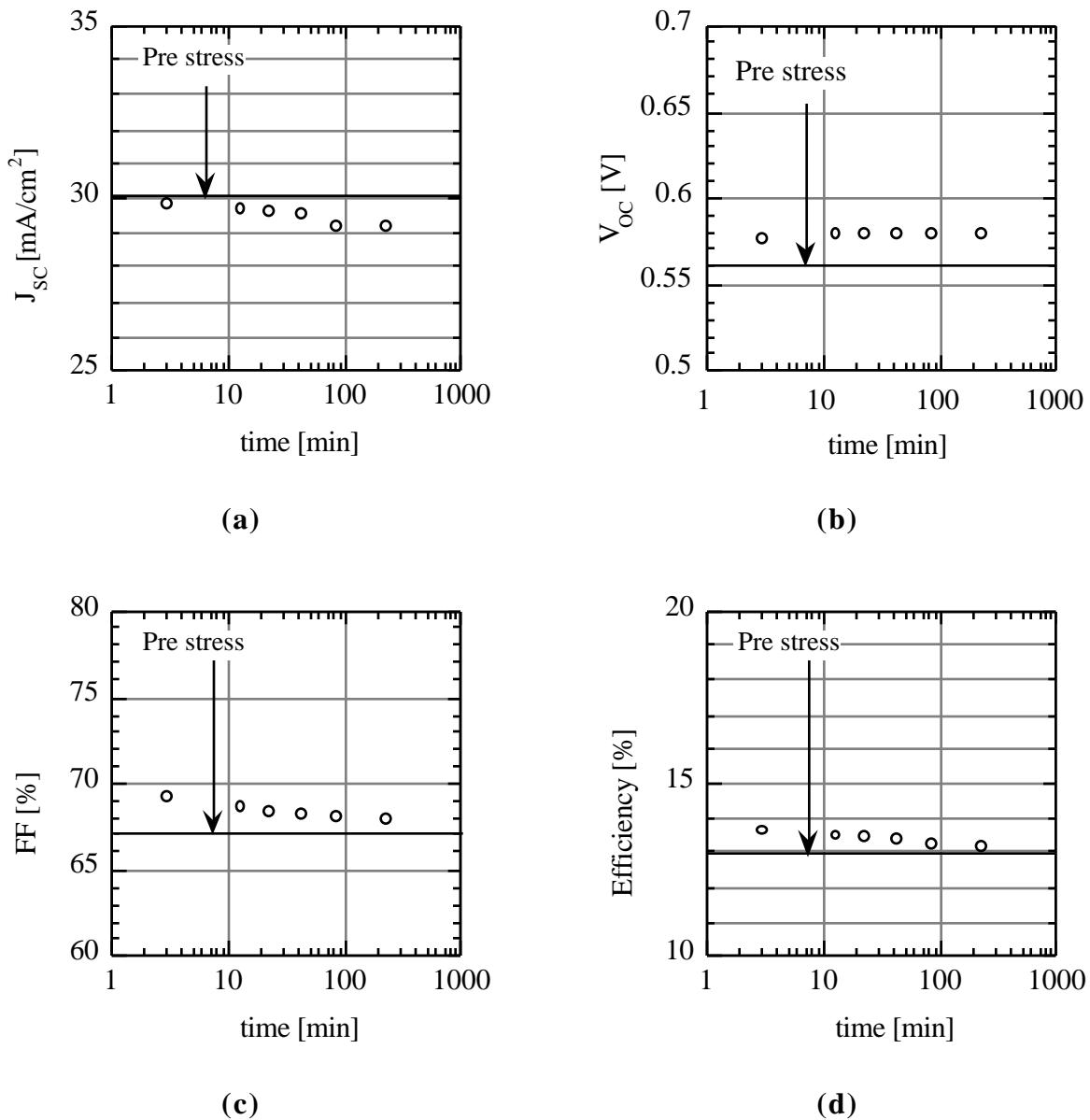

| <b>Figure 2.11 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, in the dark and at V = -0.5 V for 12 hours. ....</b>                                  | <b>24</b> |

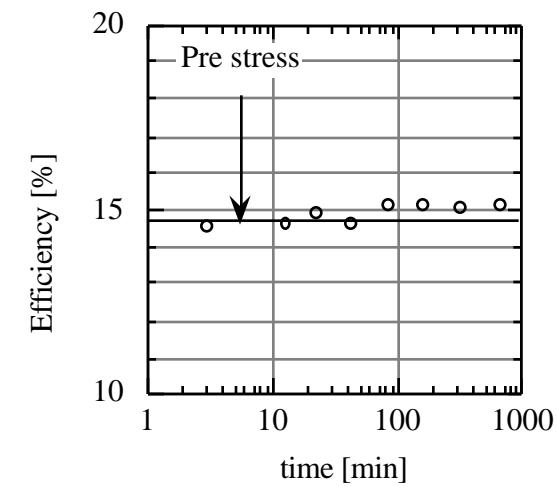

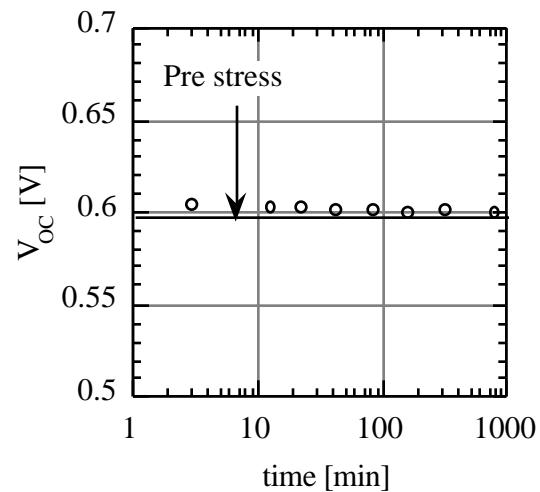

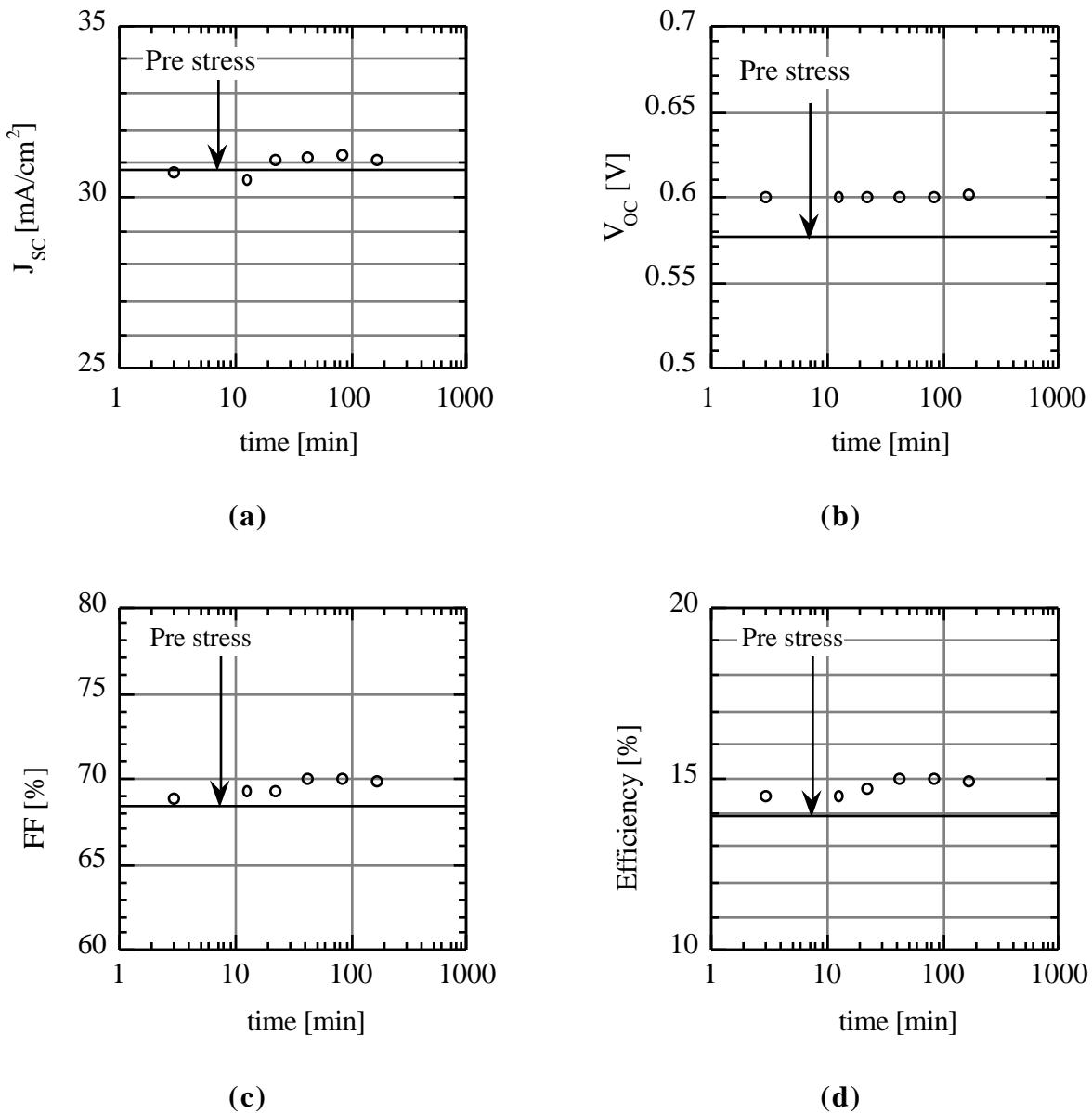

| <b>Figure 2.12 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, AM1 illumination and at a forward current of mA/cm<sup>2</sup> for 12 hours. ....</b> | <b>25</b> |

| <b>Figure 2.13 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, AM1 illumination and at V = -0.5 V for 12 hours. ....</b>                             | <b>26</b> |

| <b>Figure 2.14 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, AM1 illumination and R<sub>L</sub> = 12.6 -cm<sup>2</sup> for 10 hours.....</b>       | <b>27</b> |

| <b>Figure 2.15 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, AM1 illumination and at V<sub>oc</sub> for 8.5 hours.....</b>                         | <b>28</b> |

| <b>Figure 2.16 J<sub>sc</sub>, V<sub>oc</sub>, FF and efficiency vs. recovery time for device IEC-32702-32-7 after stress at a temperature of 80°C, AM1 illumination and at J<sub>sc</sub> for 11 hours. ....</b>                         | <b>29</b> |

|                                                                                                                                                                                                                                                                            |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Figure 2.17 Picture of a Siemens Solar Industries substrate with two CuInSe<sub>2</sub>-based solar cells (area ~ 1.0 cm<sup>2</sup>)</b> .....                                                                                                                         | <b>30</b> |

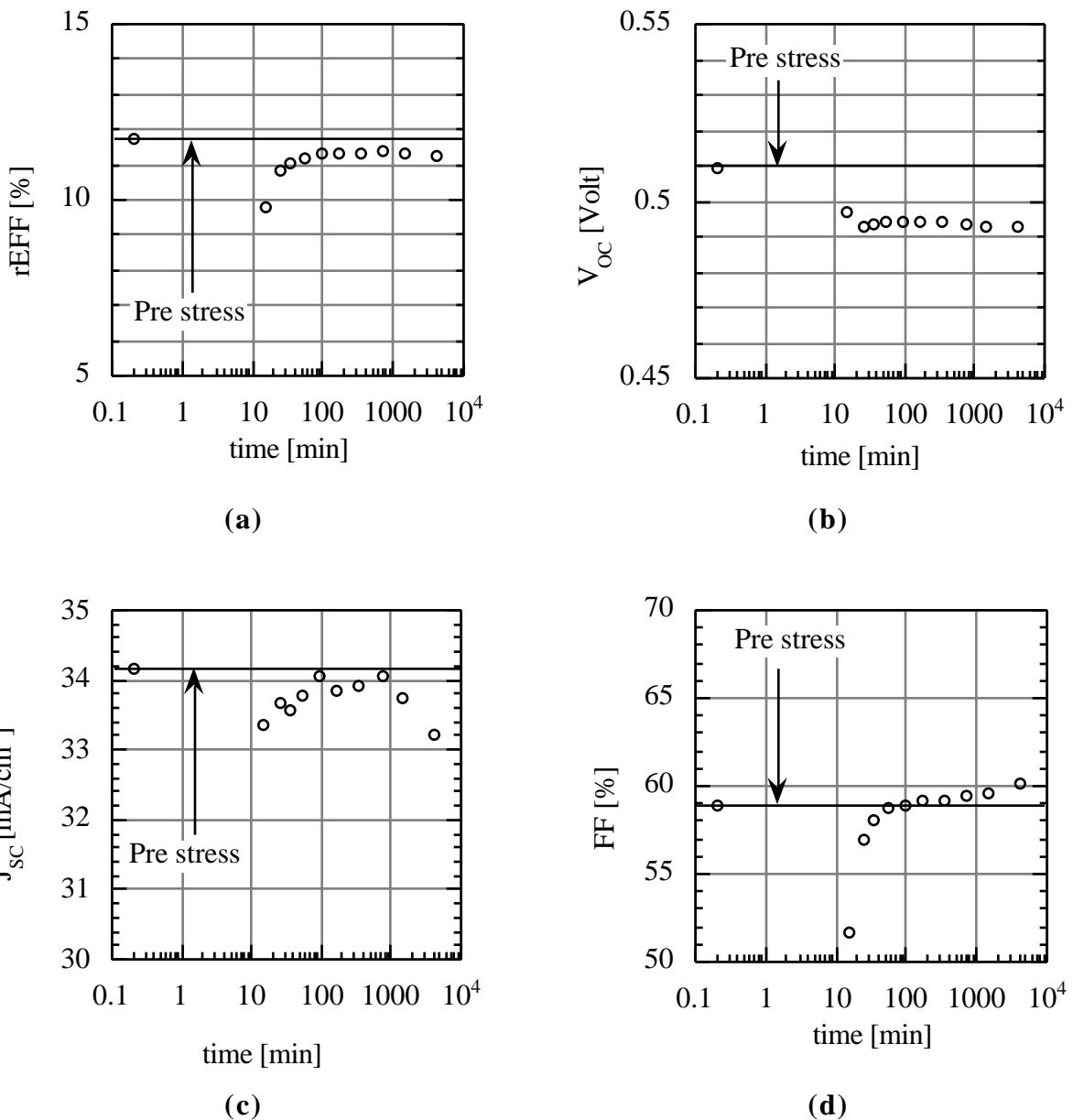

| <b>Figure 2.18 Efficiency, V<sub>oc</sub>, J<sub>sc</sub> and fill factor recovery under illumination at 25°C of device SSI-255-F2 after being subject to a lamination cycle (see text)</b> .....                                                                          | <b>31</b> |

| <b>Figure 2.19 A plot of the slope of the J-V curve at various times during recovery (see text)</b> .....                                                                                                                                                                  | <b>32</b> |

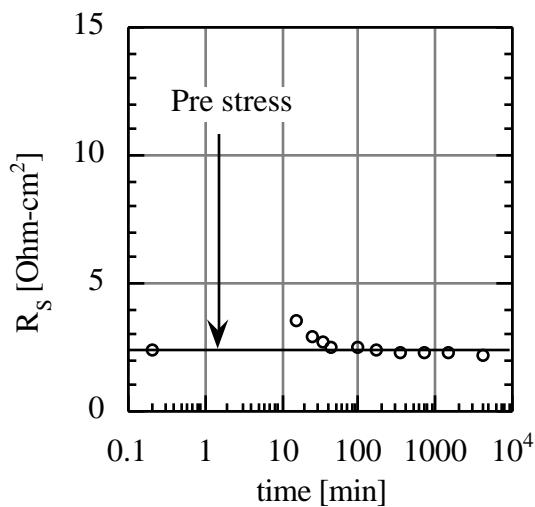

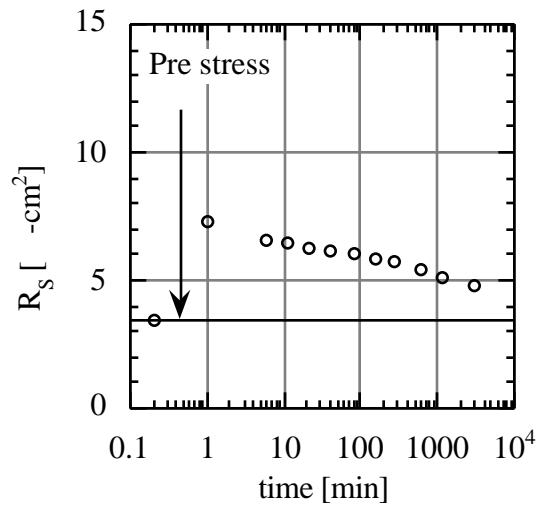

| <b>Figure 2.20 Series resistance recovery under illumination (see text)</b> .....                                                                                                                                                                                          | <b>32</b> |

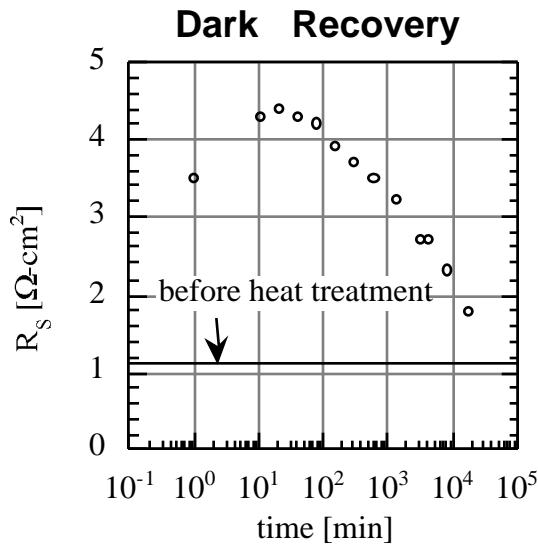

| <b>Figure 2.21 Series resistance recovery in the dark (except for J-V testing)</b> .....                                                                                                                                                                                   | <b>33</b> |

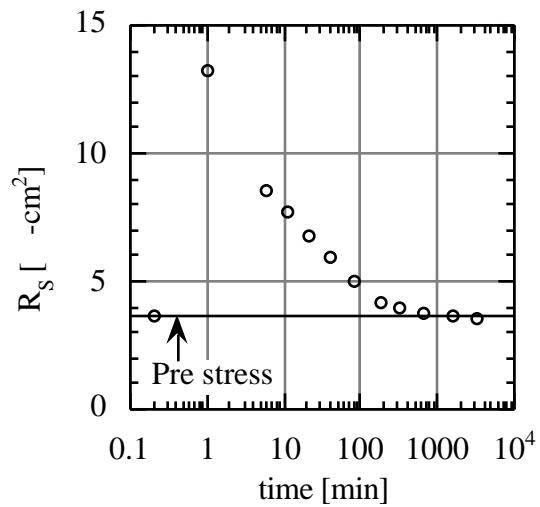

| <b>Figure 2.22 Series resistance recovery with "blue" light (except for J-V testing)</b> .....                                                                                                                                                                             | <b>33</b> |

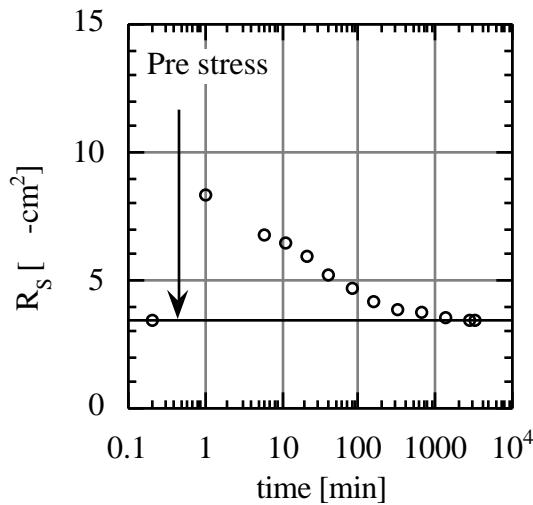

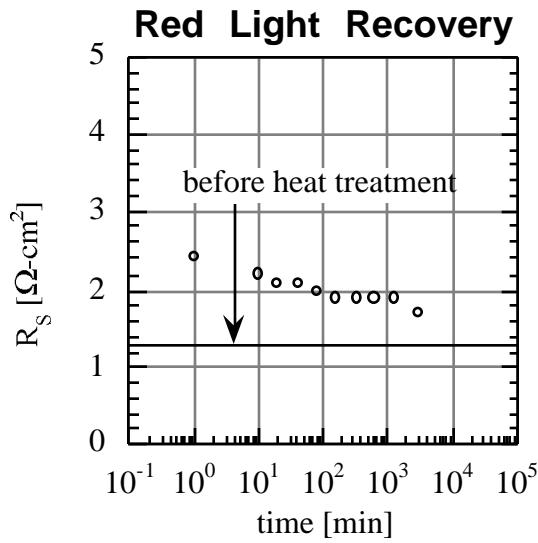

| <b>Figure 2.23 Series resistance recovery with "red" light (except for J-V testing)</b> .....                                                                                                                                                                              | <b>34</b> |

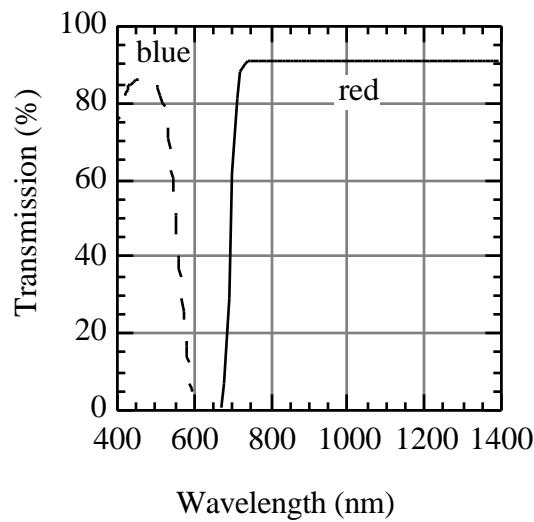

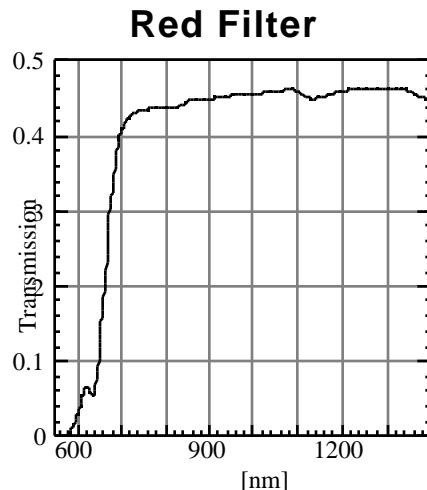

| <b>Figure 2.24 Transmission characteristics of the filters used to produce "blue" and "red" illumination</b> .....                                                                                                                                                         | <b>34</b> |

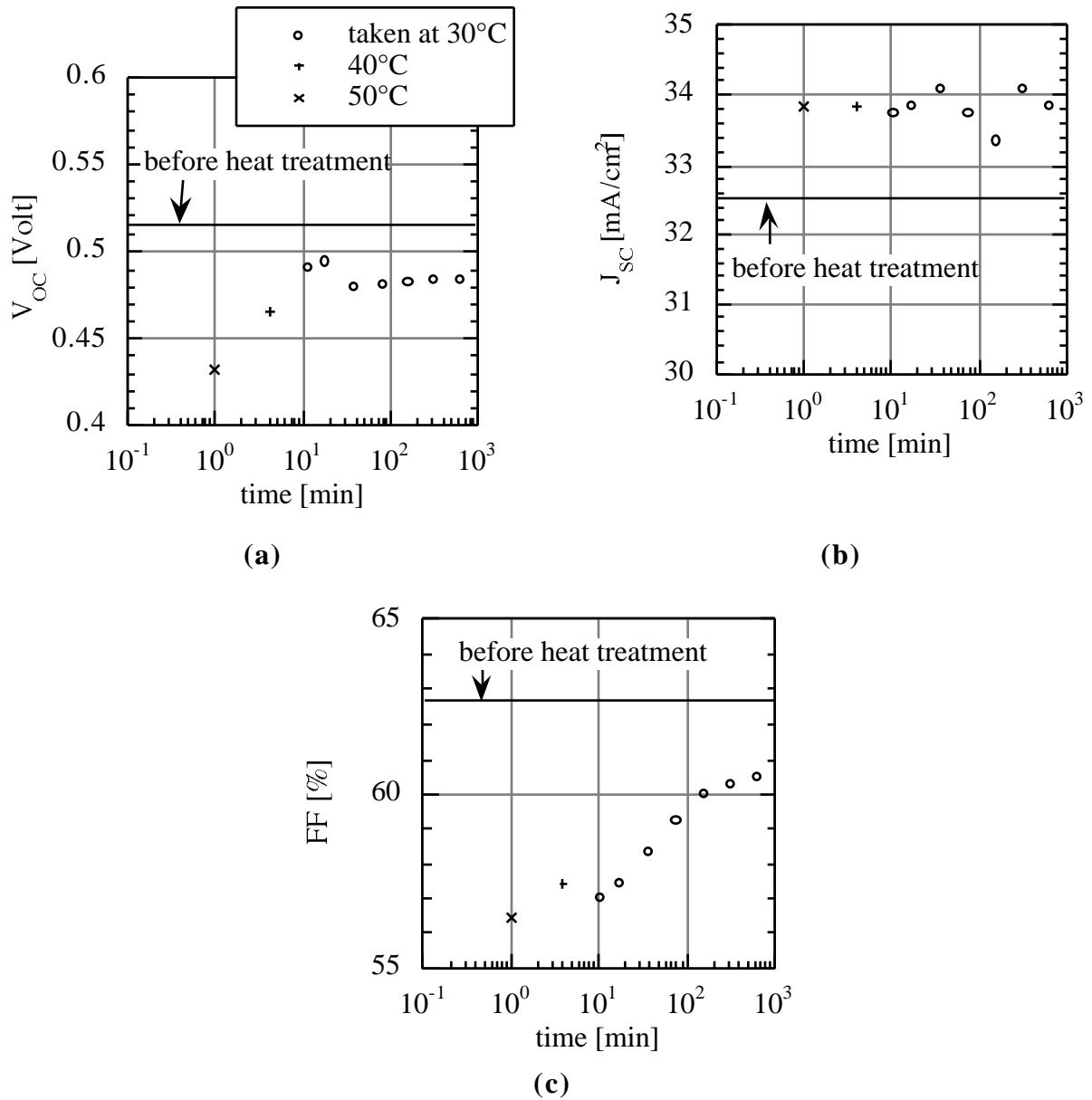

| <b>Figure 2.25 V<sub>oc</sub>, J<sub>sc</sub> and FF recovery under illumination at 30°C of mini-module SSI-260-98 after being subject to a lamination cycle</b> .....                                                                                                     | <b>35</b> |

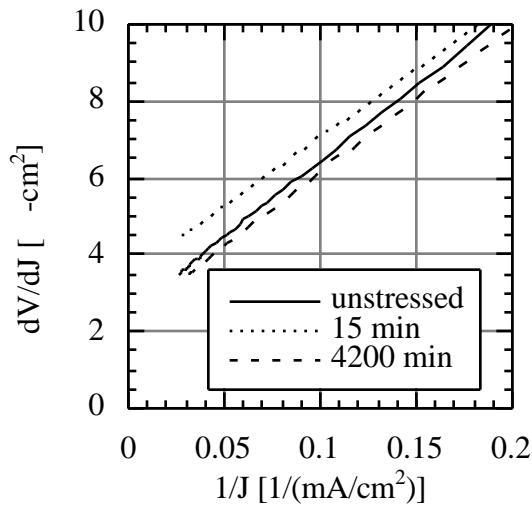

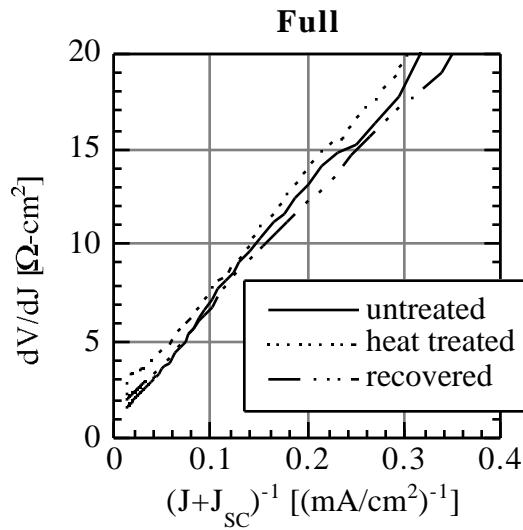

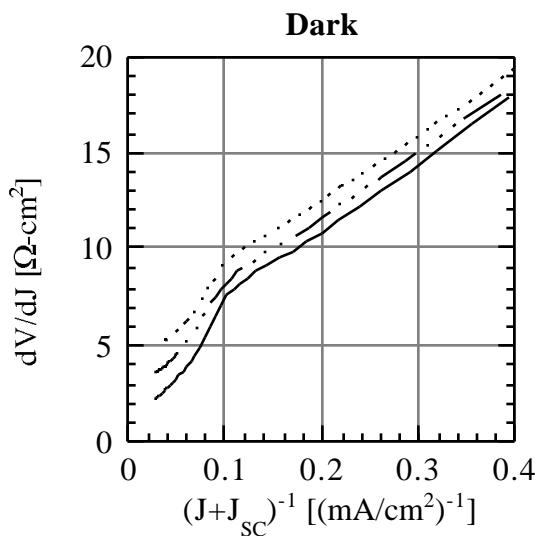

| <b>Figure 2.26 dV/dJ behavior of mini-module SSI-260-98 before and after lamination and after recovery at full illumination</b> .....                                                                                                                                      | <b>36</b> |

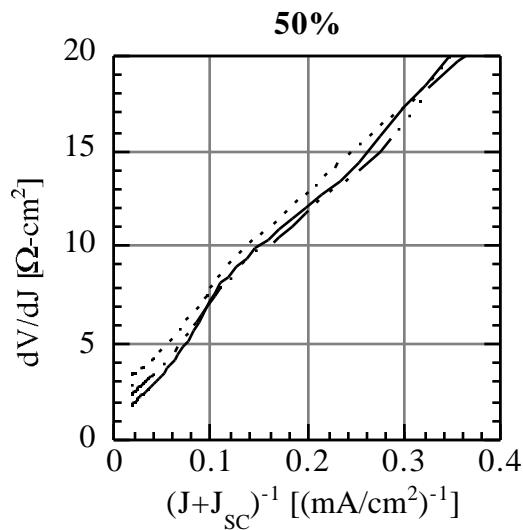

| <b>Figure 2.27 dV/dJ behavior of mini-module SSI-260-98 before and after lamination and after recovery at 50% illumination</b> .....                                                                                                                                       | <b>36</b> |

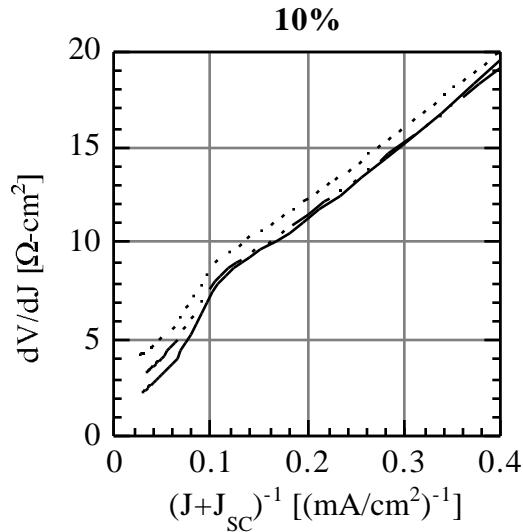

| <b>Figure 2.28 dV/dJ behavior of mini-module SSI-260-98 before and after lamination and after recovery at 10% illumination</b> .....                                                                                                                                       | <b>37</b> |

| <b>Figure 2.29 dV/dJ behavior of mini-module SSI-260-98 before and after lamination and after recovery in the dark</b> .....                                                                                                                                               | <b>37</b> |

| <b>Figure 2.30 R<sub>s</sub> recovery in the dark at 30°C of mini-module SSI-260-108 after being subject to a lamination cycle</b> .....                                                                                                                                   | <b>38</b> |

| <b>Figure 2.31 R<sub>s</sub> recovery in "red" light at 30°C of mini-module SSI-260-105 after being subject to a lamination cycle</b> .....                                                                                                                                | <b>38</b> |

| <b>Figure 2.32 Transmission characteristics of the "red" filter used for the illumination of mini-module SSI-260-105</b> .....                                                                                                                                             | <b>39</b> |

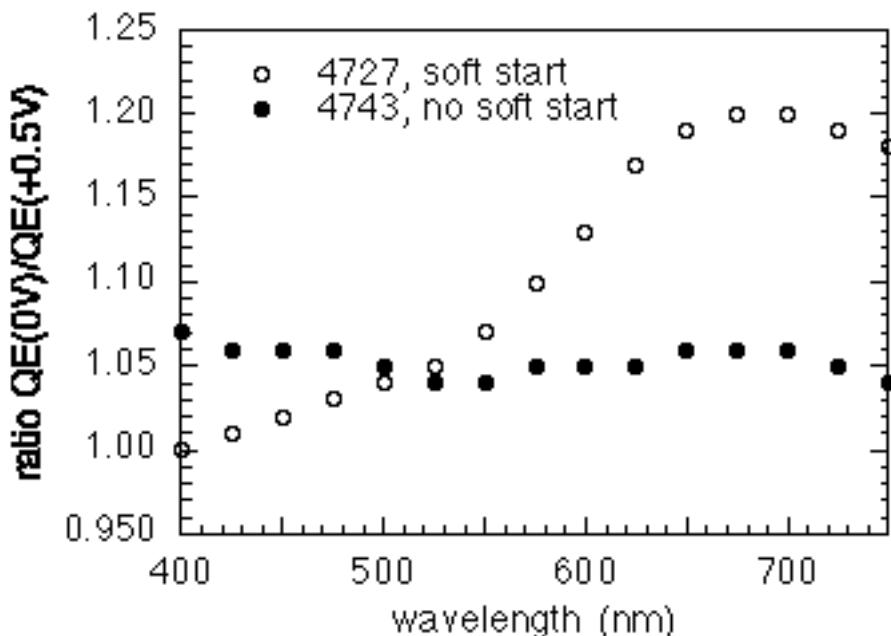

| <b>Figure 3.1 Voltage dependent QE ratio for devices with and without soft start p-layers. X<sub>c</sub> is ratio of QE/(0v)/(+0.5V) at 700 nm to that at 450 nm. Run numbers refer to Table 3.2</b> .....                                                                 | <b>43</b> |

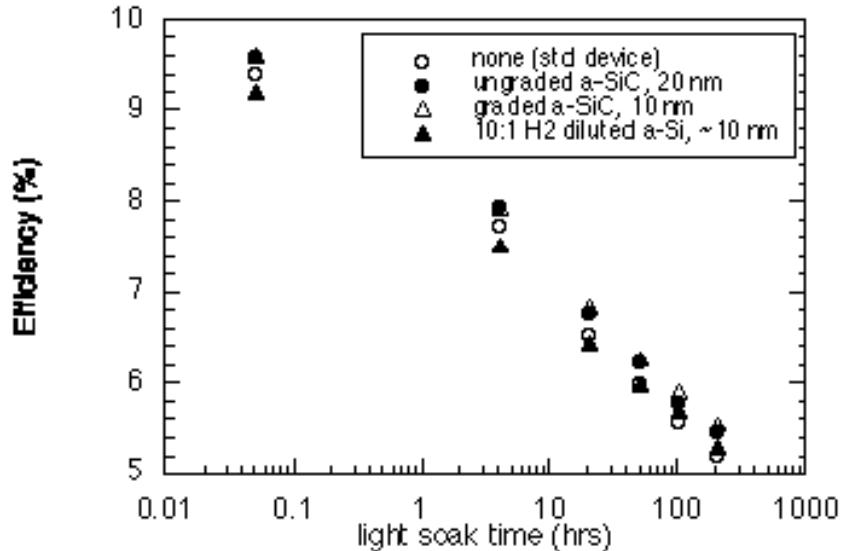

| <b>Figure 3.2 Stability of four devices with different i<sub>1</sub> layers during 200 hour light exposure. Note that there was no difference in degradation and that no stabilization occurs within 200 hours. The i<sub>2</sub> layer was not hydrogen diluted</b> ..... | <b>45</b> |

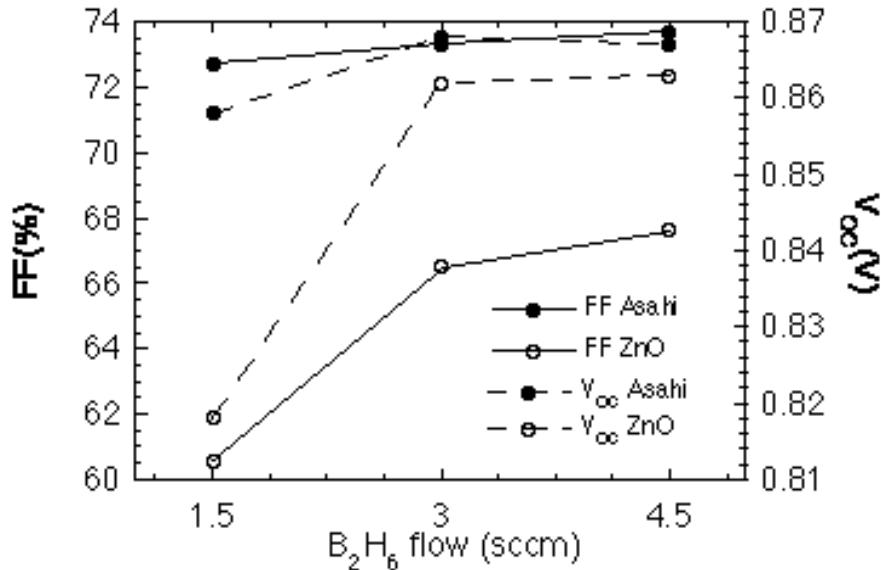

| <b>Figure 3.3 FF and V<sub>oc</sub> for devices on SnO<sub>2</sub> (textured, Asahi) and ZnO (smooth, Harvard) for different B<sub>2</sub>H<sub>6</sub> flows in the a-SiC p-layer</b> .....                                                                               | <b>47</b> |

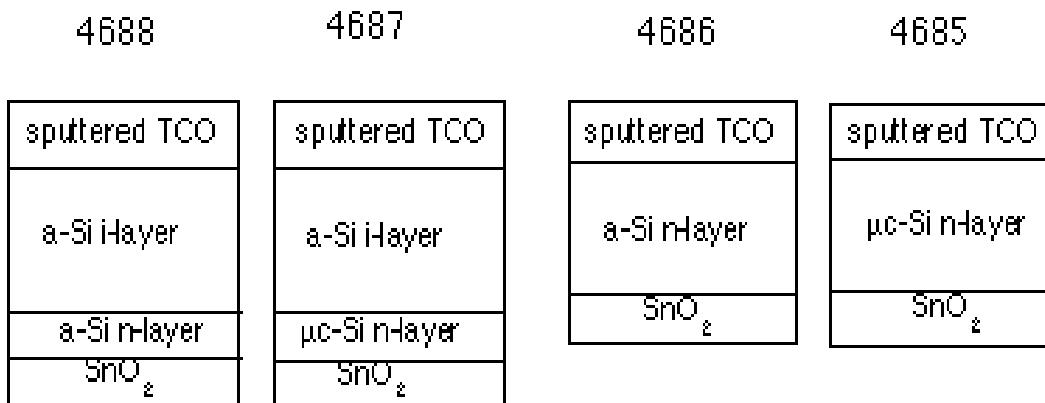

| <b>Figure 3.4 Four device structures (depositions 4685-4688) used to study sputtered TCO and SnO<sub>2</sub> contacts with a-Si and μc-Si i-layers and n-layers</b> .....                                                                                                  | <b>48</b> |

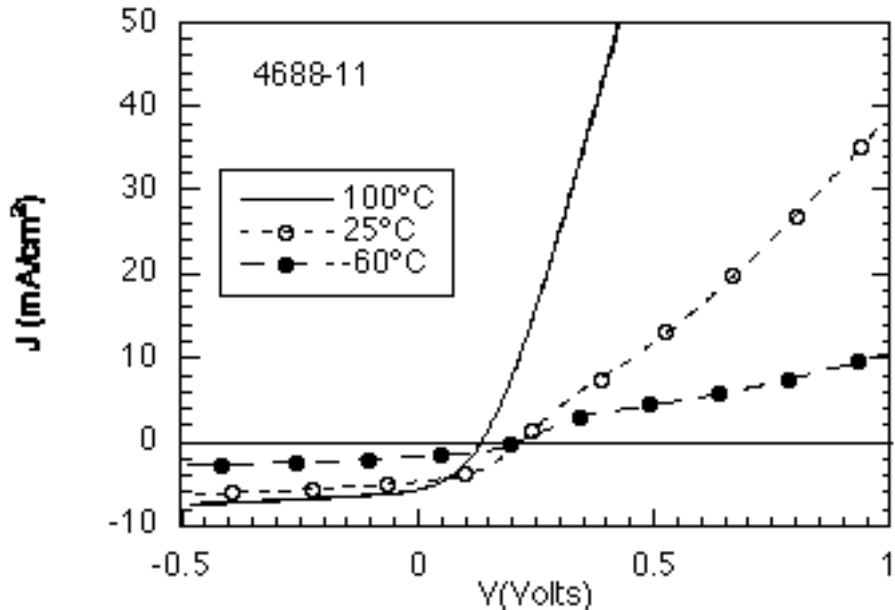

| <b>Figure 3.5 Illuminated JV curves at 100, 25, and -60°C for glass/SnO<sub>2</sub>/n-i/TCO devices with a-Si n-layer (4688-11)</b> .....                                                                                                                                  | <b>49</b> |

|                                                                                                                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

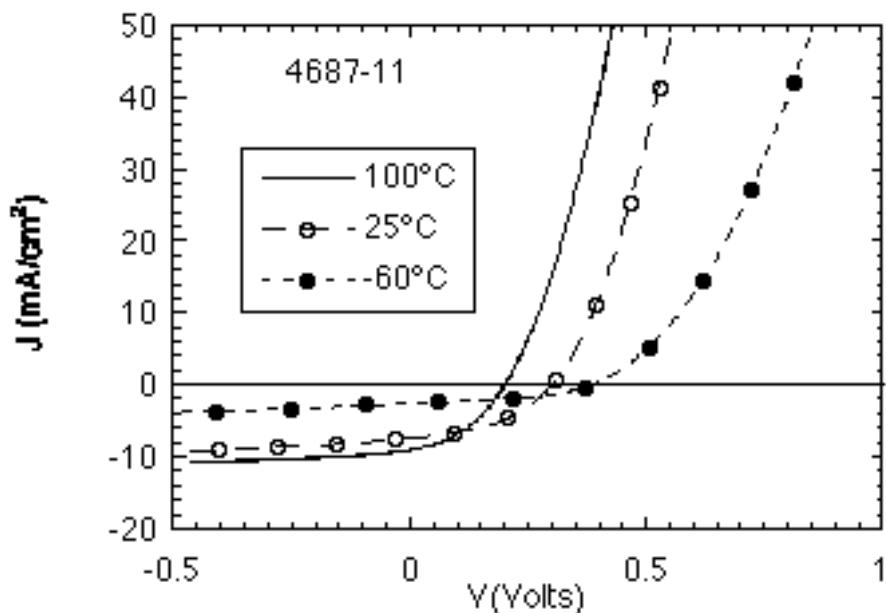

| Figure 3.6 Illuminated JV curves at 100, 25, and -60°C for glass/SnO <sub>2</sub> /n-i/TCO devices with μc-Si n-layer (4687-11).....                                                                                                                                  | 49 |

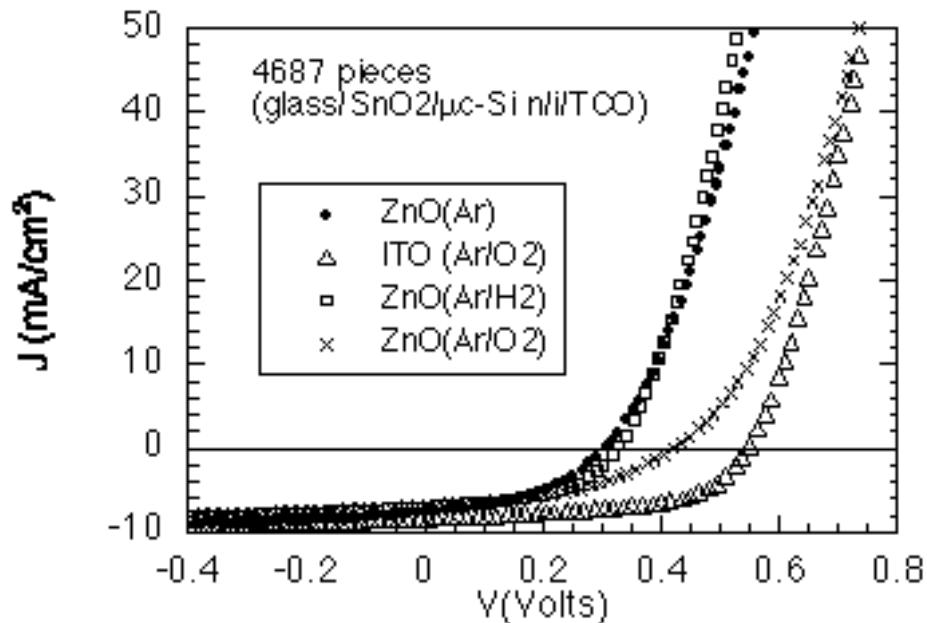

| Figure 3.7 Illuminated JV curves at 25°C for glass/SnO <sub>2</sub> /n-i/TCO devices with μc-Si n-layers and four different sputtered TCO contacts.....                                                                                                               | 50 |

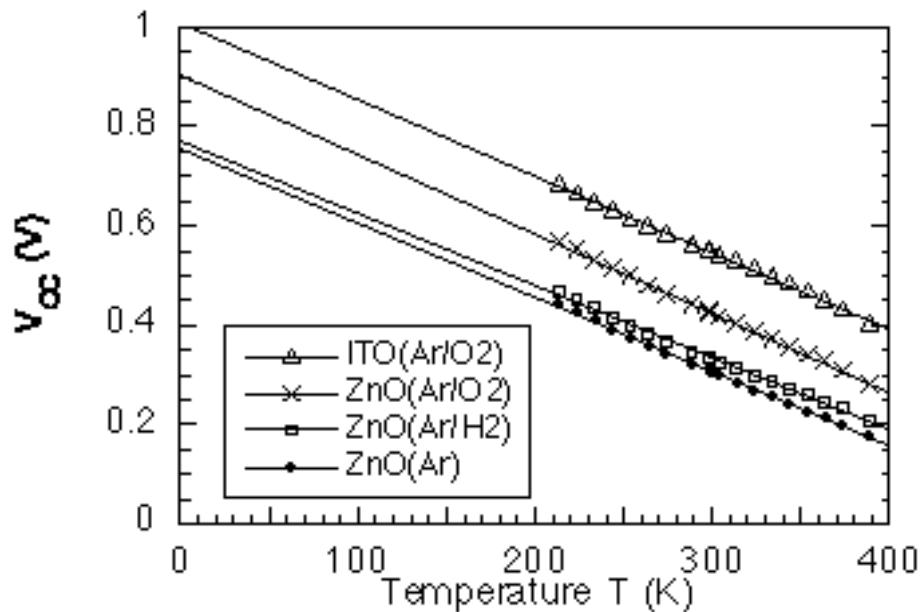

| Figure 3.8 Temperature dependence of V <sub>oc</sub> for four devices from Figure 3.7 with μc-Si n-layer.....                                                                                                                                                         | 51 |

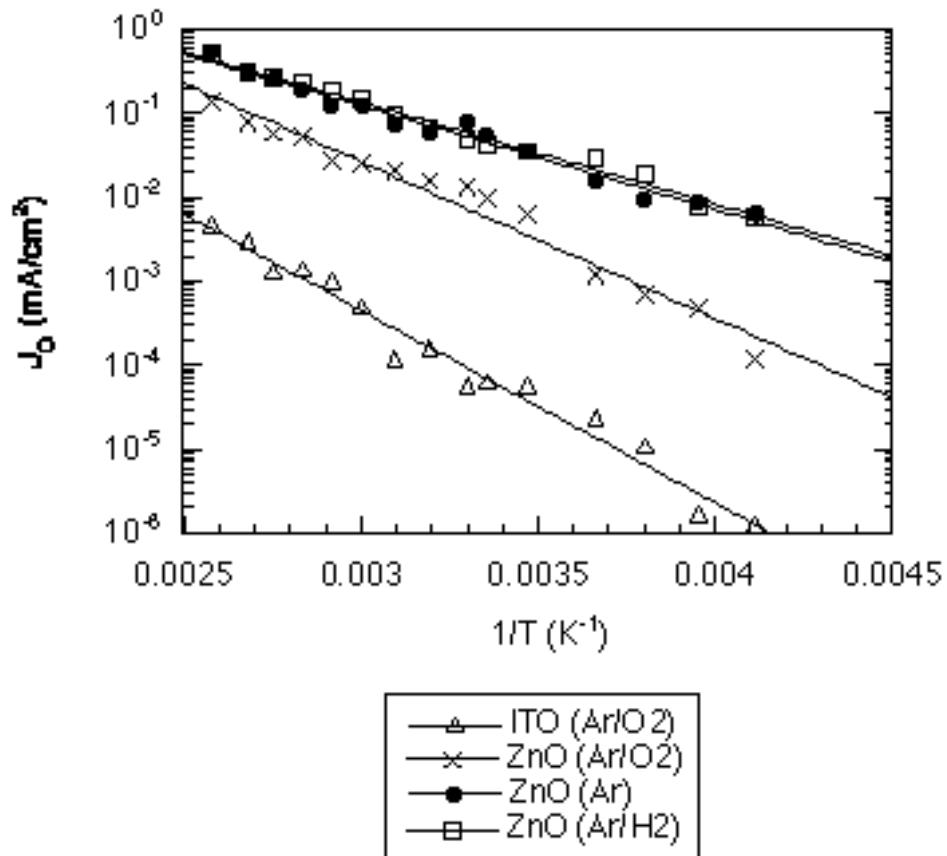

| Figure 3.9 Temperature dependence of J <sub>o</sub> for four devices from Figure 3.8 with μc-Si n-layer.....                                                                                                                                                          | 52 |

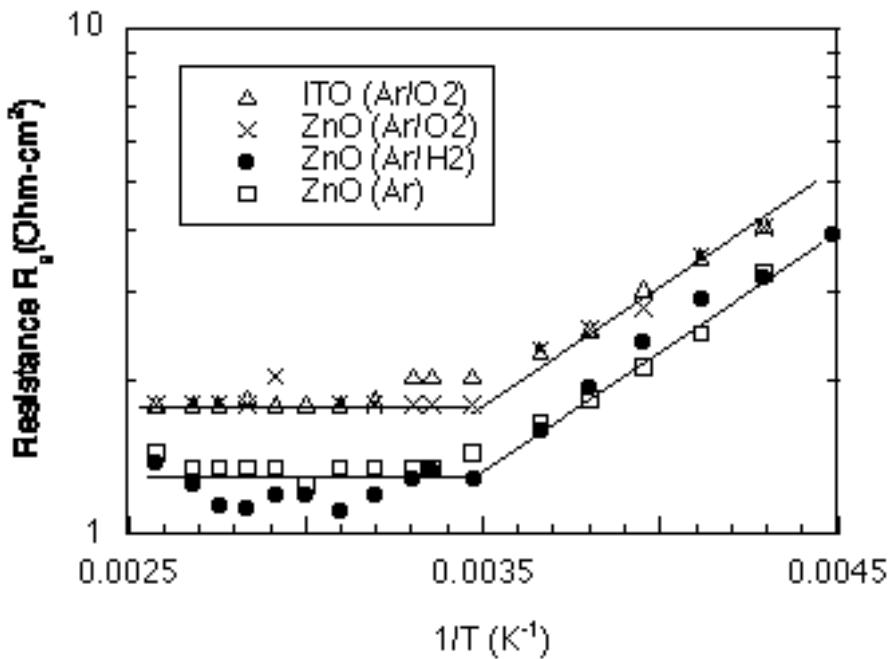

| Figure 3.10 Temperature dependence of series resistance R <sub>s</sub> from light JV of devices from 4687 (glass/SnO <sub>2</sub> /μc-Si n/i/TCO). Lines are drawn to guide the eye. Activation energy for 1/T > 0.0036 K <sup>-1</sup> is approximately 0.08 eV..... | 53 |

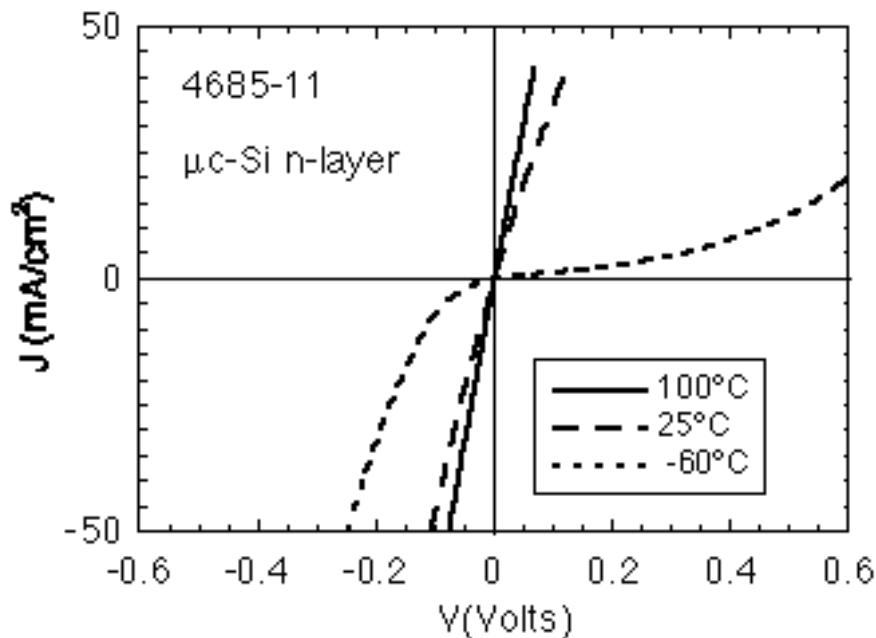

| Figure 3.11 JV curves at 100, 25, and -60°C for device with μc-Si n-layer (4685-11) and sputtered ZnO (Ar) contact. Device structure is glass/SnO <sub>2</sub> /μc-Si n/ZnO.....                                                                                      | 54 |

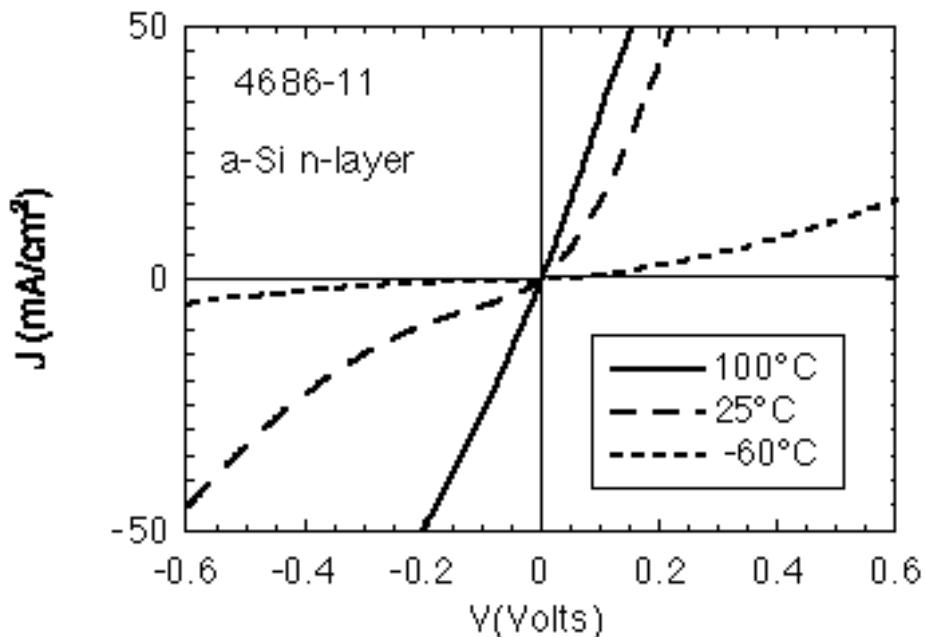

| Figure 3.12 JV curves at 100, 25, and -60°C for device with a-Si n-layer (4686-11) and sputtered ZnO (Ar) contact. Device structure is glass/SnO <sub>2</sub> /a-Si n/ZnO.....                                                                                        | 54 |

| Figure 3.13 JV curves at -60°C for devices with c-Si n-layer (4685 pieces) and sputtered TCO contacts.....                                                                                                                                                            | 57 |

| Figure 3.14 JV curves at -60°C for devices with a-Si n-layer (4686 pieces) and sputtered TCO contacts.....                                                                                                                                                            | 57 |

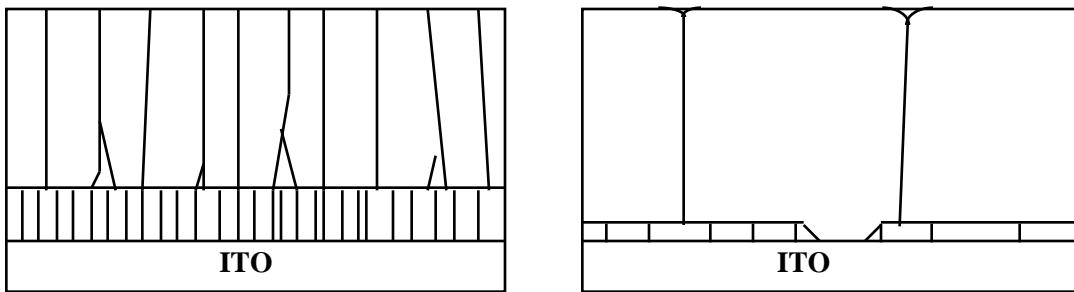

| Figure 4.1 Schematic cross-sectional views of as-deposited (left) and CdCl <sub>2</sub> -treated CdTe/CdS cells.....                                                                                                                                                  | 64 |

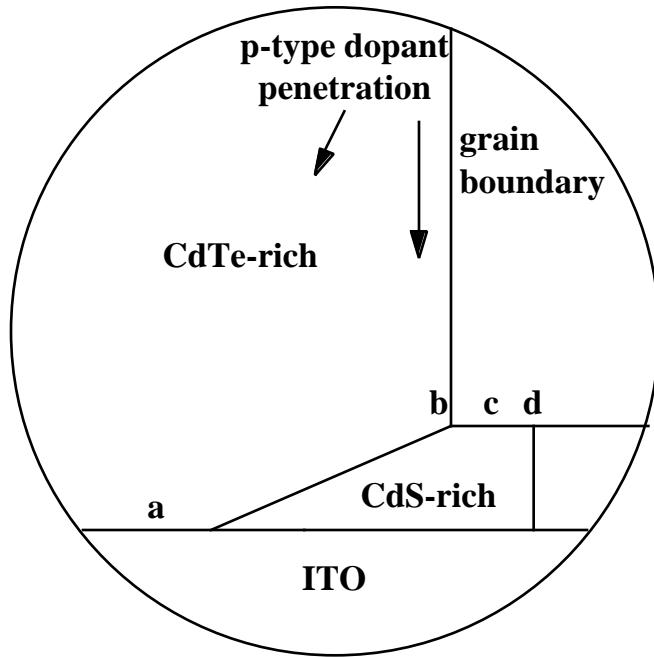

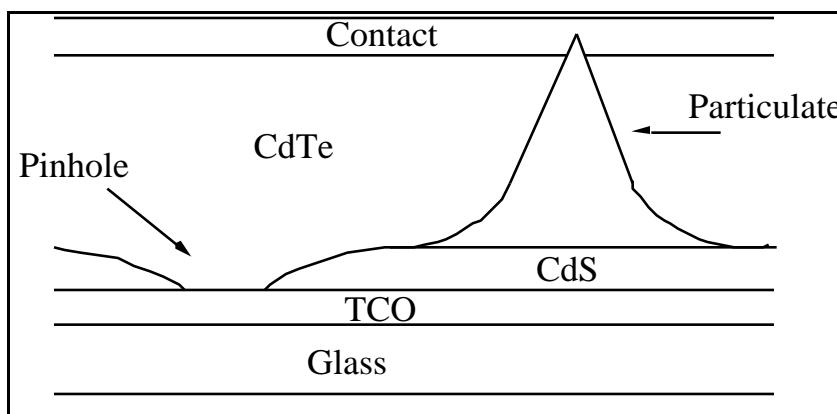

| Figure 4.2 Schematic detail of the junction region in a CdTe/CdS device.....                                                                                                                                                                                          | 64 |

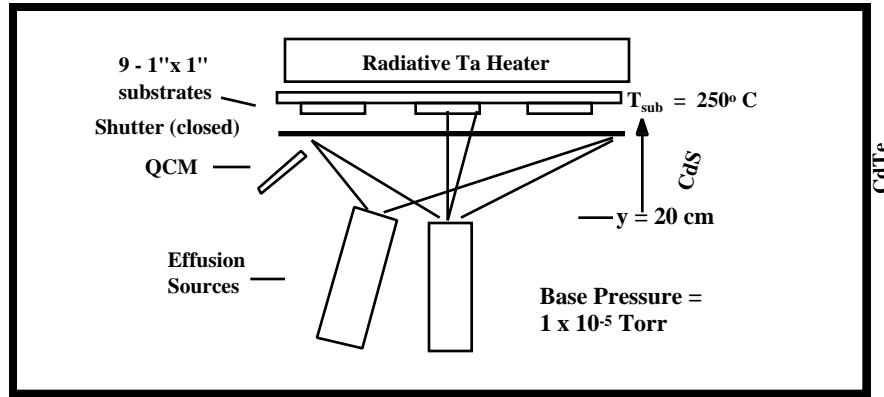

| Figure 4.3 Schematic cross-section view of physical deposition system for CdTe <sub>1-x</sub> S <sub>x</sub> absorber layers.....                                                                                                                                     | 68 |

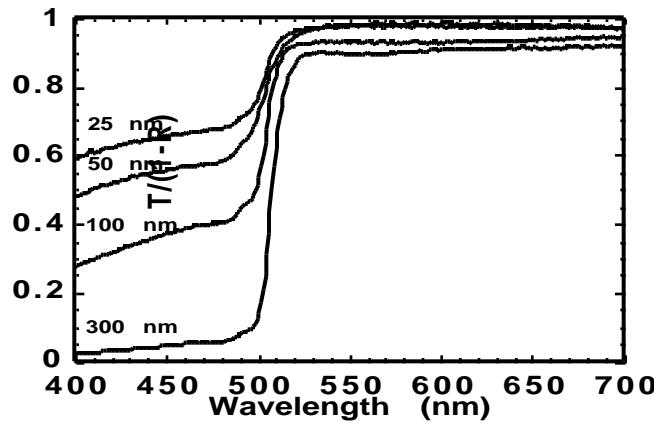

| Figure 4.4 Measured optical transmission, normalized for reflection of CdS/ITO/7059 (samples from depositions 12148, 12157, 12176, and 12143).....                                                                                                                    | 69 |

| Figure 4.5 V <sub>oc</sub> -limiting defects attributable to CdS and TCO processing.....                                                                                                                                                                              | 69 |

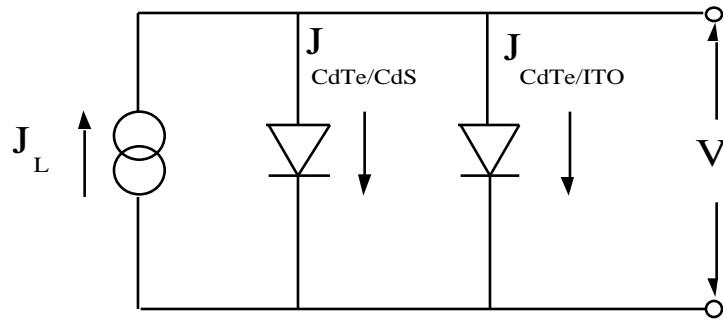

| Figure 4.6 Equivalent circuit and equation for parallel diodes between CdTe/CdS and CdTe/TCO.....                                                                                                                                                                     | 70 |

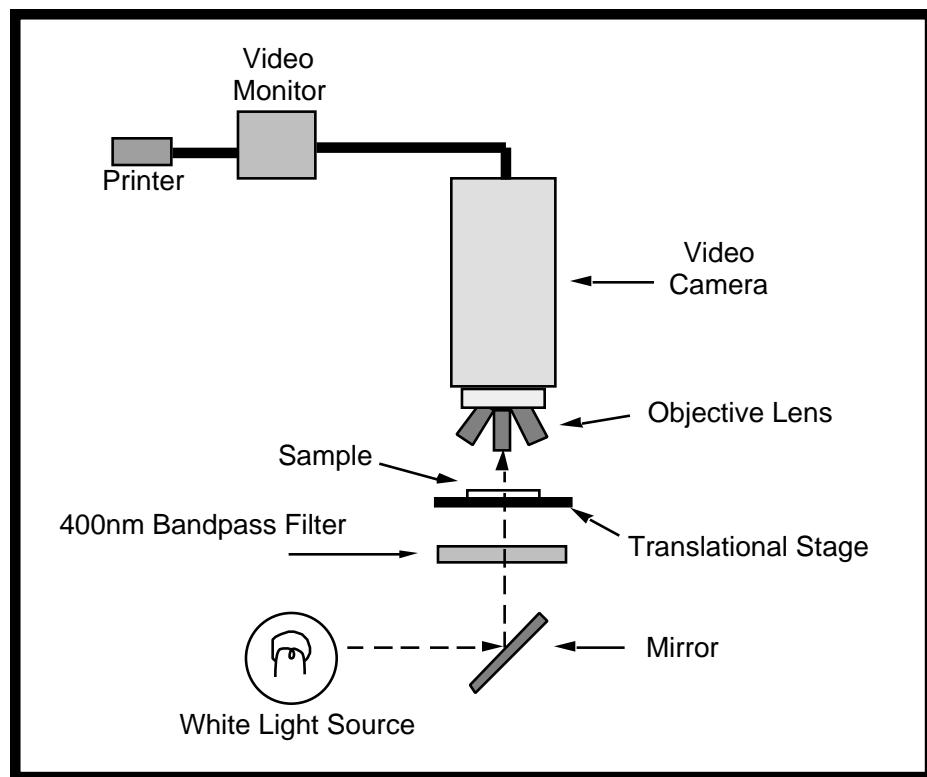

| Figure 4.7 Optical arrangement used to survey CdS films.....                                                                                                                                                                                                          | 71 |

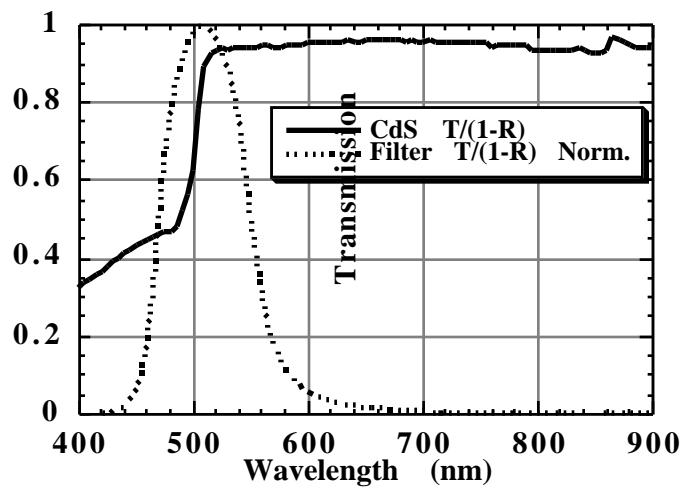

| Figure 4.8 Optical transmission of CdS film and Corion 400 nm bandpass filter.....                                                                                                                                                                                    | 71 |

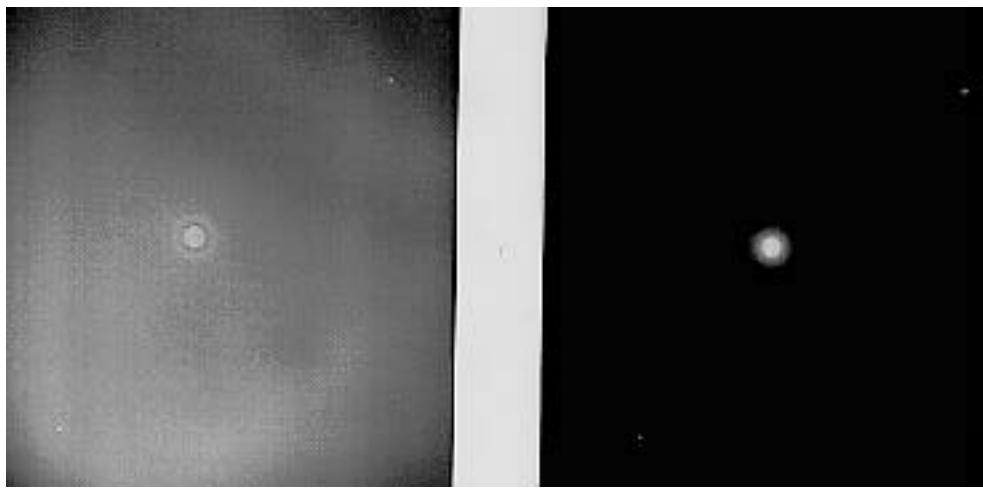

| Figure 4.9 Optical micrographs of pinholes in PVD CdS film 120 nm thick.....                                                                                                                                                                                          | 72 |

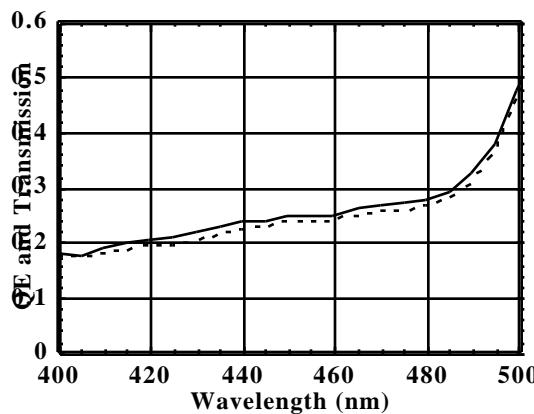

| Figure 4.10 Short wavelength quantum efficiency of CdTe/CdS thin-film device (solid line) compared to CdS transmission (dotted line) after removal of Te-rich layers (sample 40992.31/12127.31).....                                                                  | 74 |

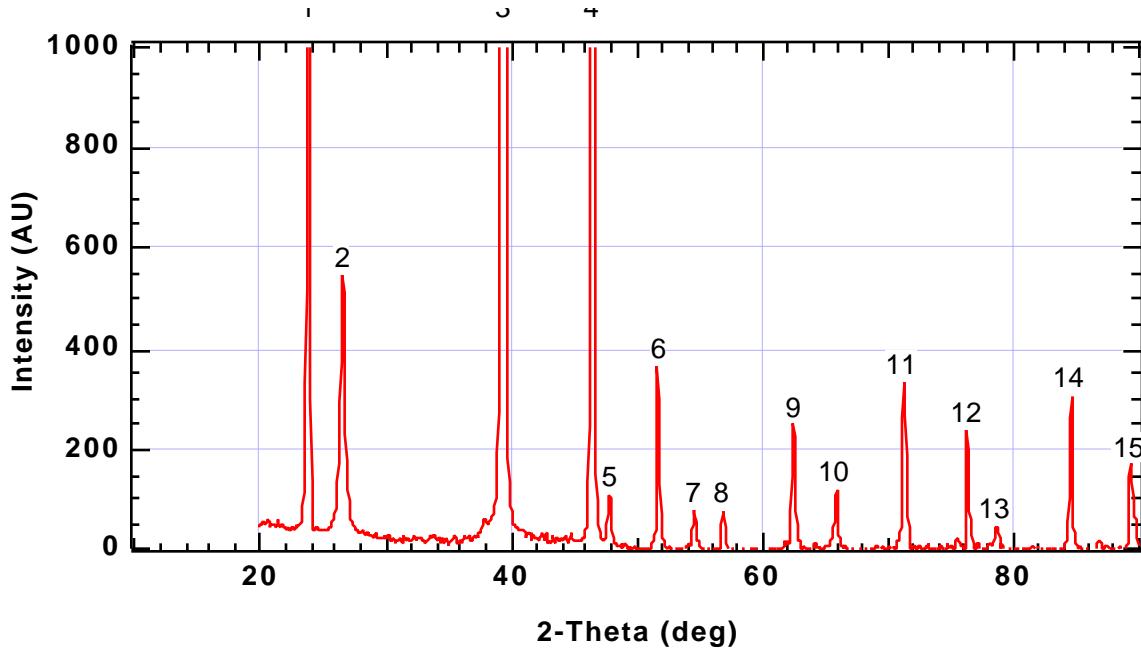

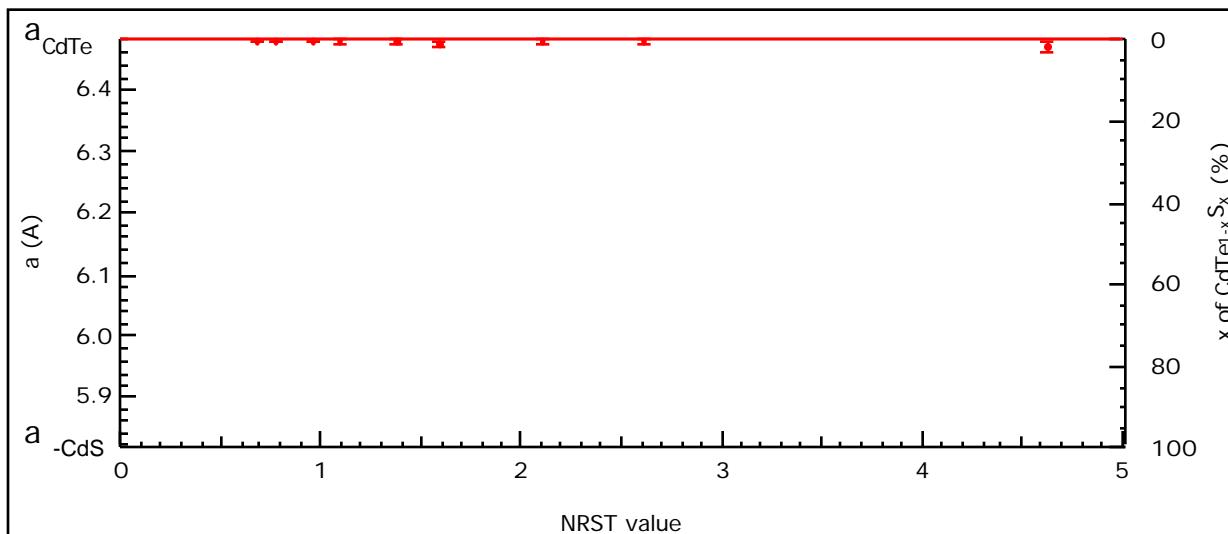

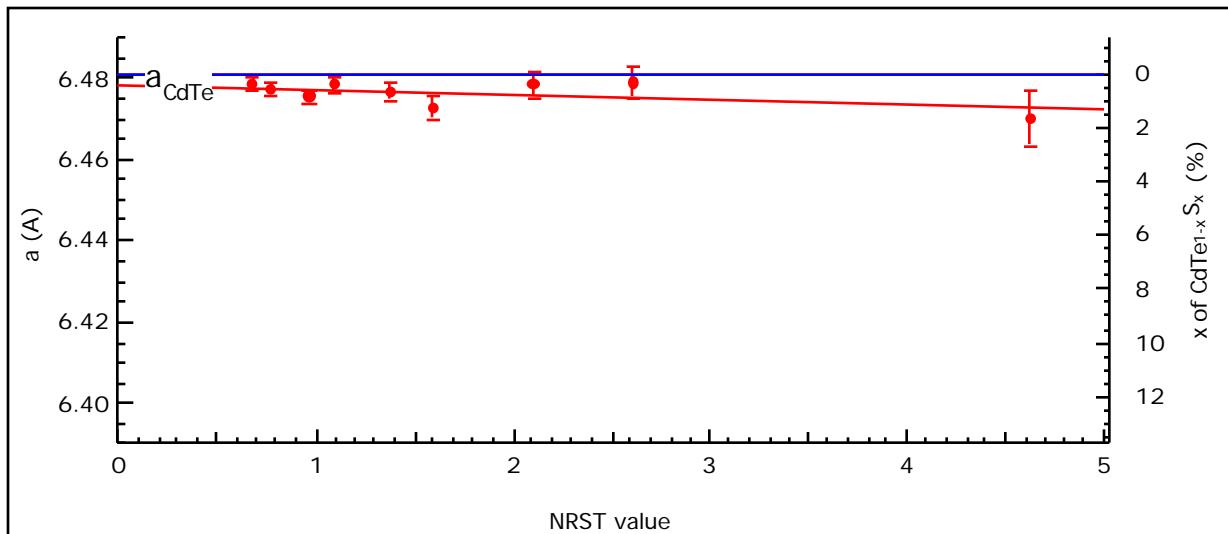

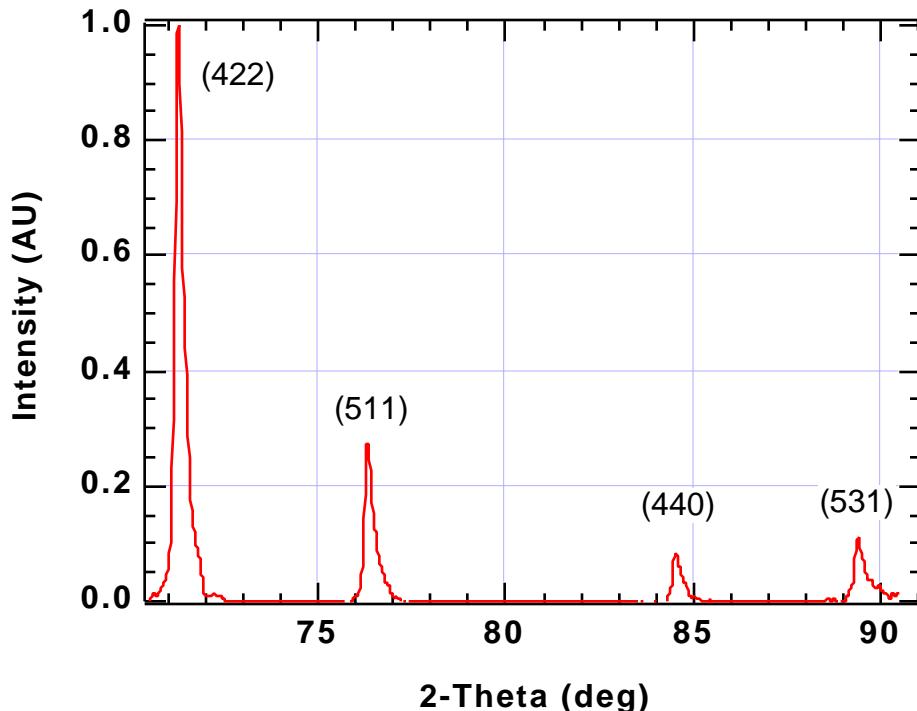

| Figure 4.11 Data Example 1 - Broad scan and peak table - SCI 005 after thinning to 2 μm. ....                                                                                                                                                                         | 77 |

| Figure 4.12 Data Example 2 - NRST reduction of CdTe <sub>1-x</sub> S <sub>x</sub> peaks of Example 1. ....                                                                                                                                                            | 78 |

|                                                                                                                                                                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

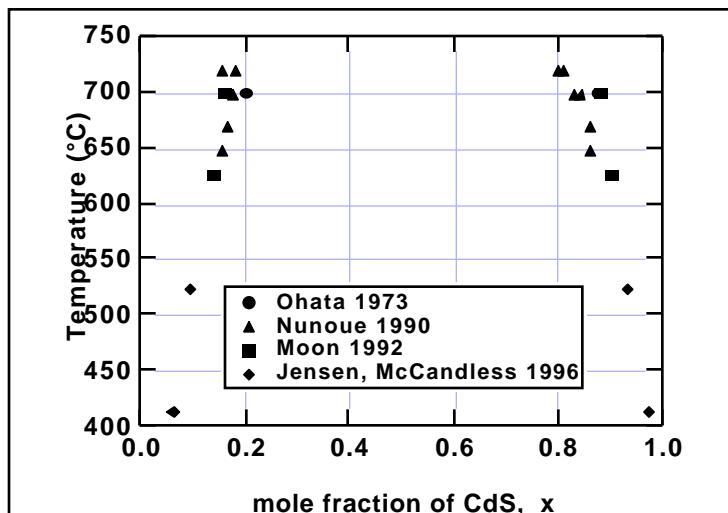

| Figure 4.13 Equilibrium phase diagram for CdTe-CdS incorporating IEC data for films and powder and film data from References 163, 164, 165.....                                                                                                                   | 79 |

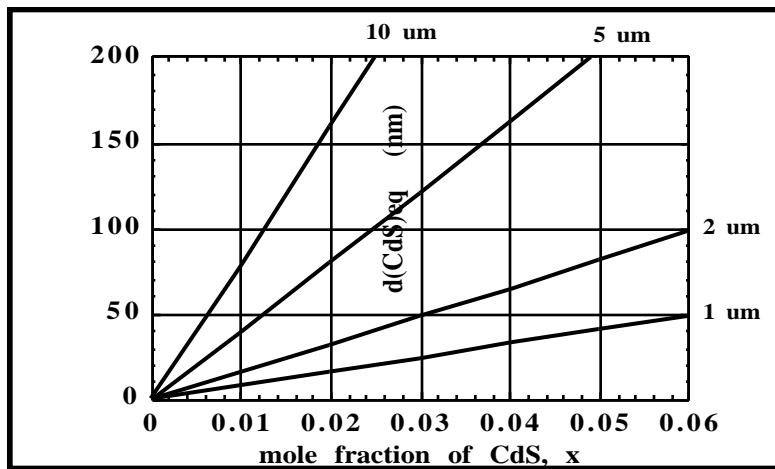

| Figure 4.14 Equivalent CdS thickness versus molar fraction of CdS in $\text{CdTe}_{1-x}\text{S}_x$ for different total alloy film thicknesses. Single crystal densities were assumed in this approximation.....                                                   | 80 |

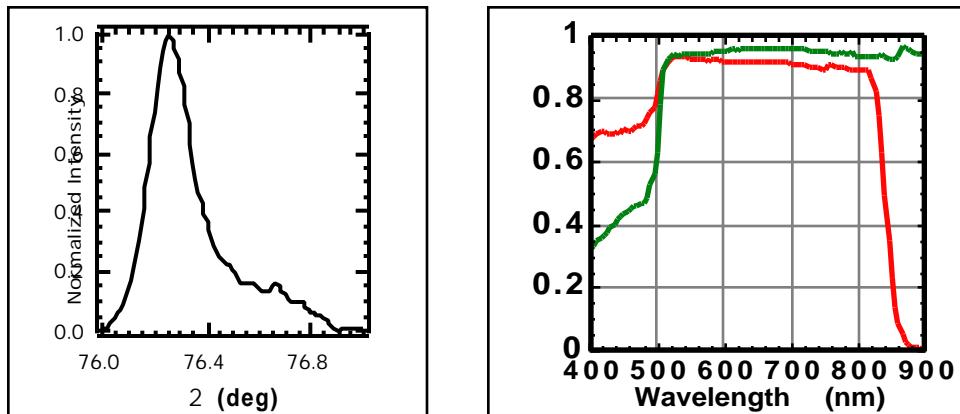

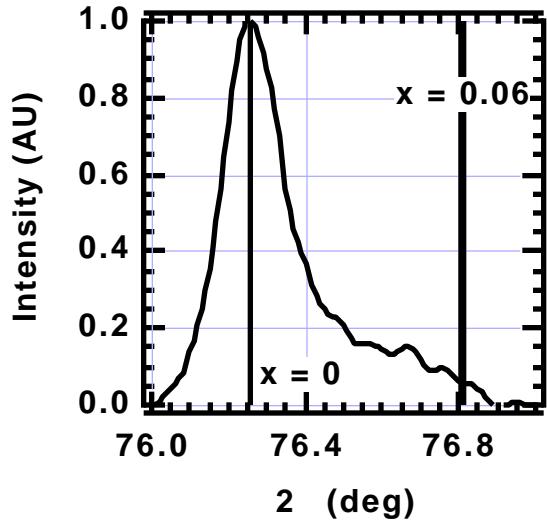

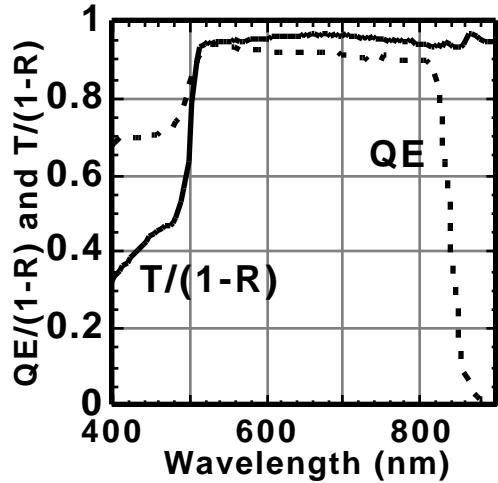

| Figure 4.15 X-ray diffraction line profile of $\text{CdTe}_{1-x}\text{S}_x$ (511) after device processing (left) and optical transmission of CdS before processing and device quantum efficiency (right).....                                                     | 80 |

| Figure 4.16 Narrow angle XRD peaks of different (hkl) for IEC sample 913.12 after thinning to 2 $\mu\text{m}$ .....                                                                                                                                               | 83 |

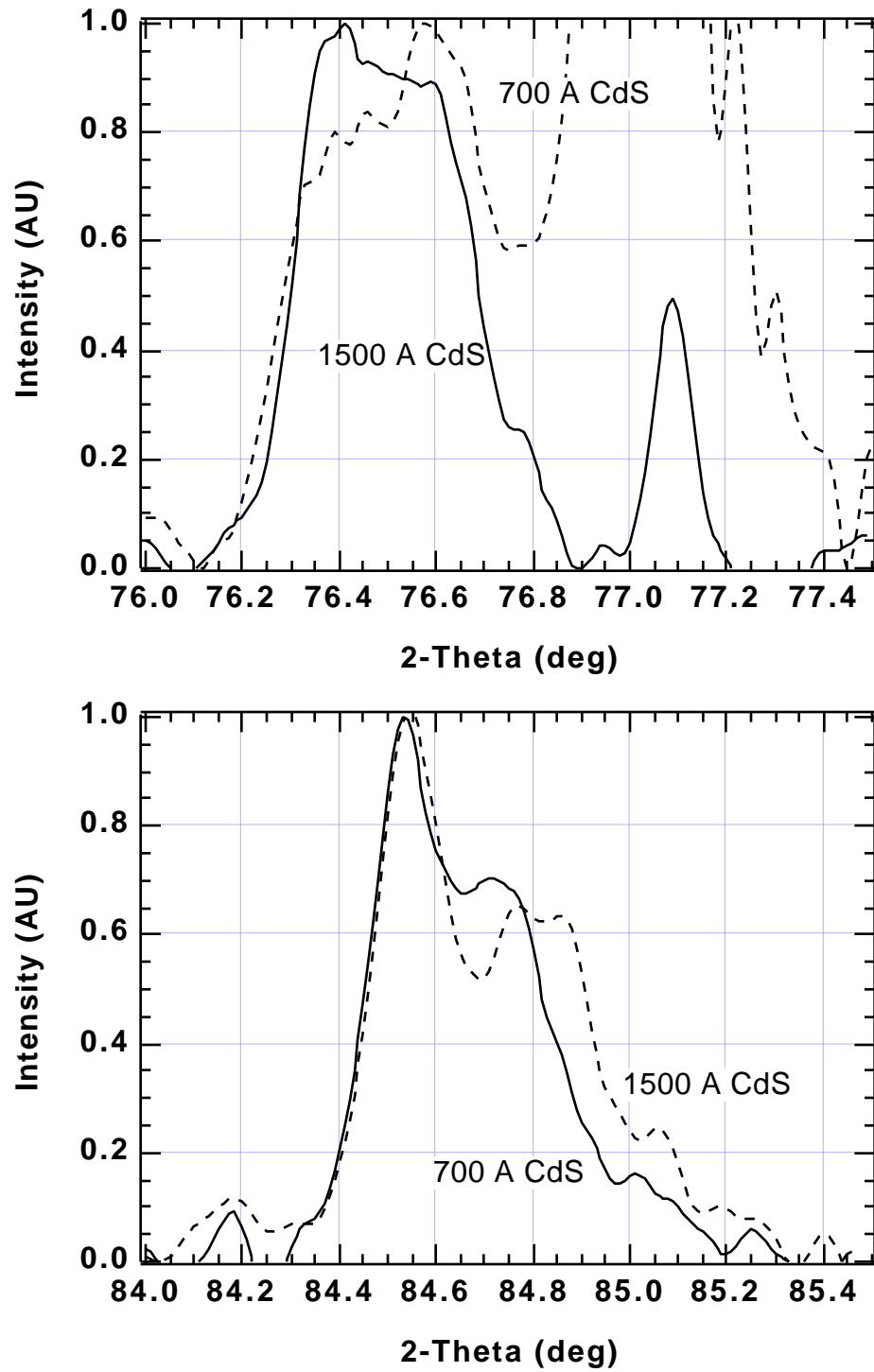

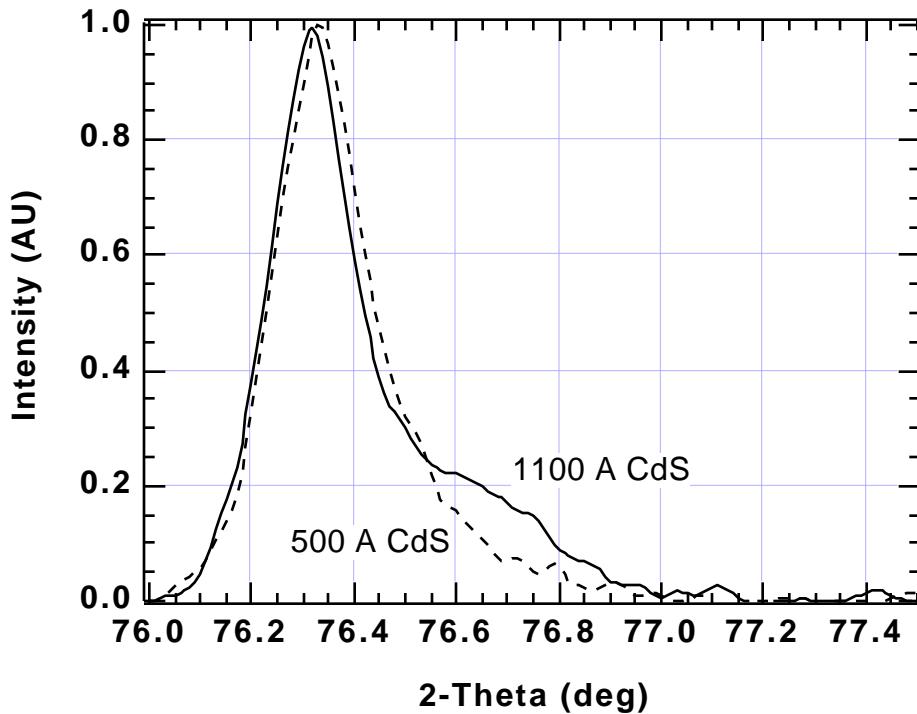

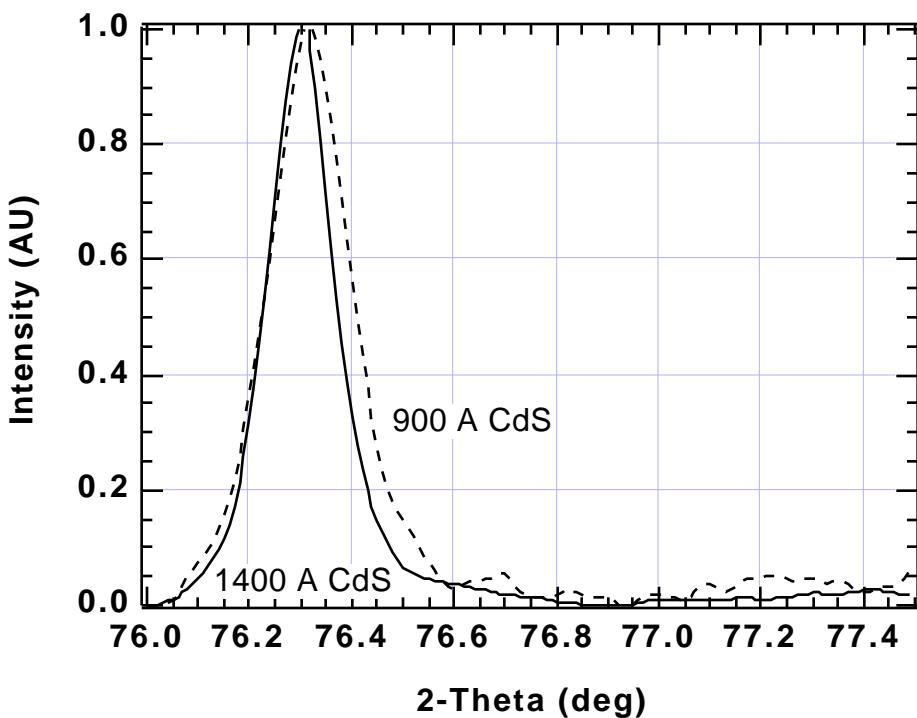

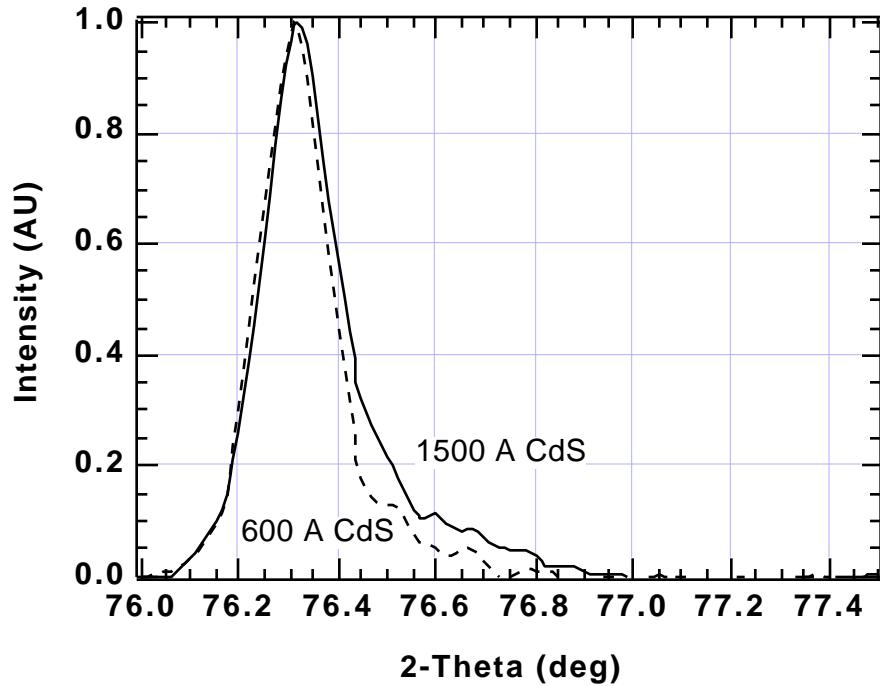

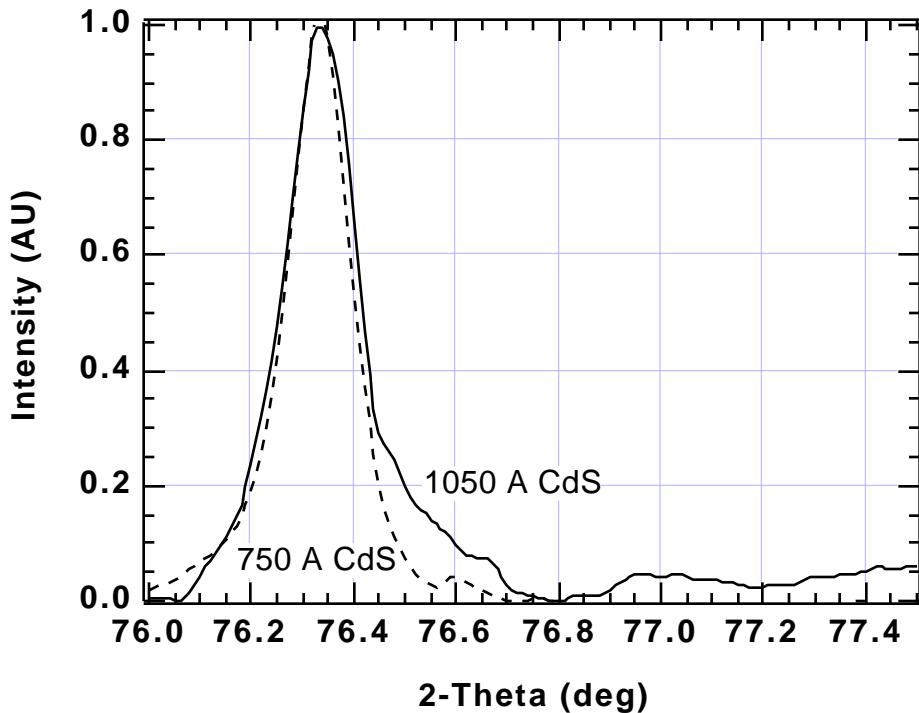

| Figure 4.17 Narrow angle (511) (top) and (440) (bottom) XRD peak profiles for CSM samples with different CdS thickness. ....                                                                                                                                      | 84 |

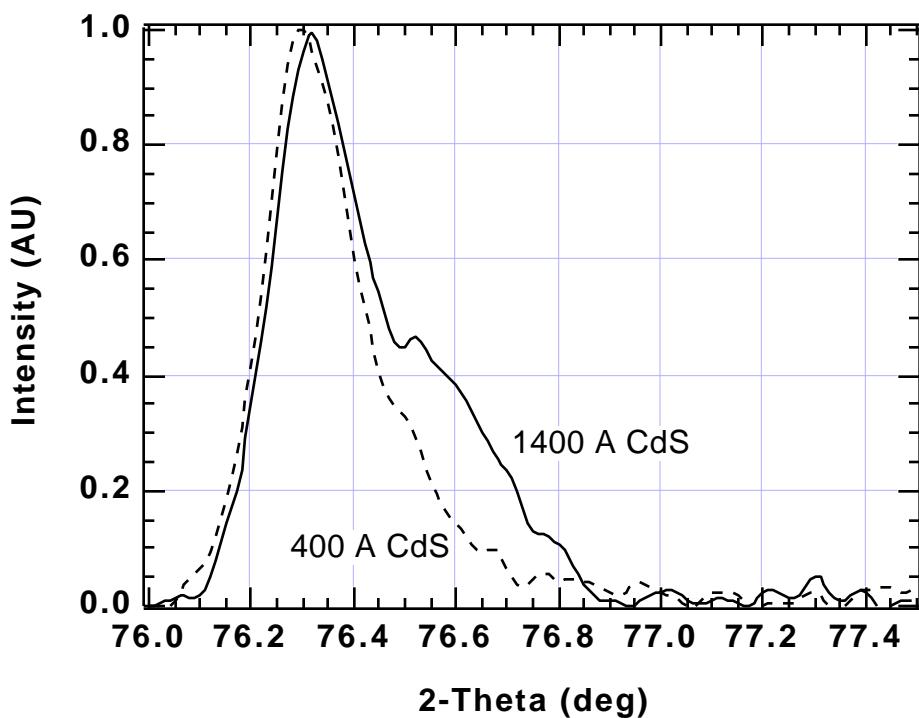

| Figure 4.18 Narrow angle (511) XRD peak profiles for IEC samples with different CdS thickness after thinning the CdTe layer to $\sim 2 \mu\text{m}$ .....                                                                                                         | 85 |

| Figure 4.19 Narrow angle (511) XRD peak profiles for NREL samples with different CdS thickness after thinning the CdTe layer to $\sim 2 \mu\text{m}$ .....                                                                                                        | 85 |

| Figure 4.20 Narrow angle (511) XRD peak profiles for SCI samples with different CdS thickness after thinning the CdTe layer to $\sim 2 \mu\text{m}$ .....                                                                                                         | 86 |

| Figure 4.21 Narrow angle (511) XRD peak profiles for USF samples with different CdS thickness after thinning the CdTe layer to $\sim 2 \mu\text{m}$ .....                                                                                                         | 86 |

| Figure 4.22 Narrow angle (511) XRD peak profiles for UT samples with different CdS thickness.....                                                                                                                                                                 | 87 |

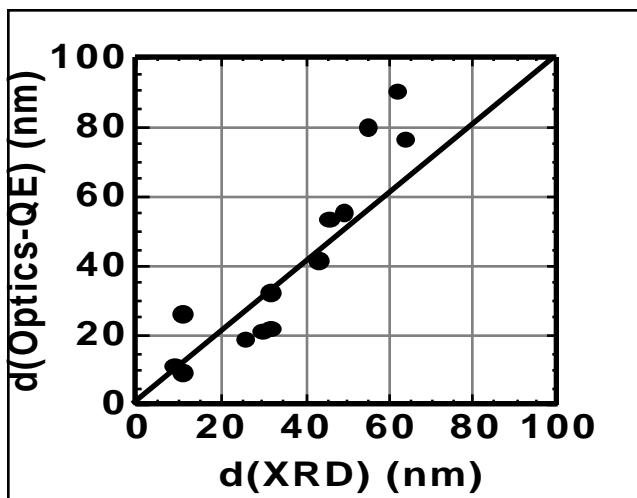

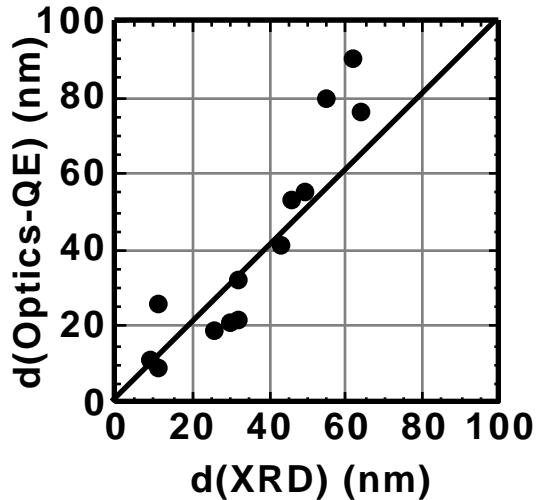

| Figure 4.23 Change in CdS thickness derived from optical methods compared to that derived from X-ray diffraction measurements. ....                                                                                                                               | 88 |

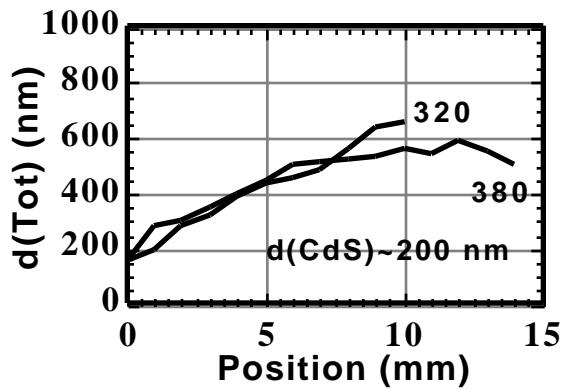

| Figure 4.24 Total thickness profile of CdTe/CdS on quartz thinned with 0.05% $\text{Br}_2\text{-CH}_3\text{OH}$ .....                                                                                                                                             | 90 |

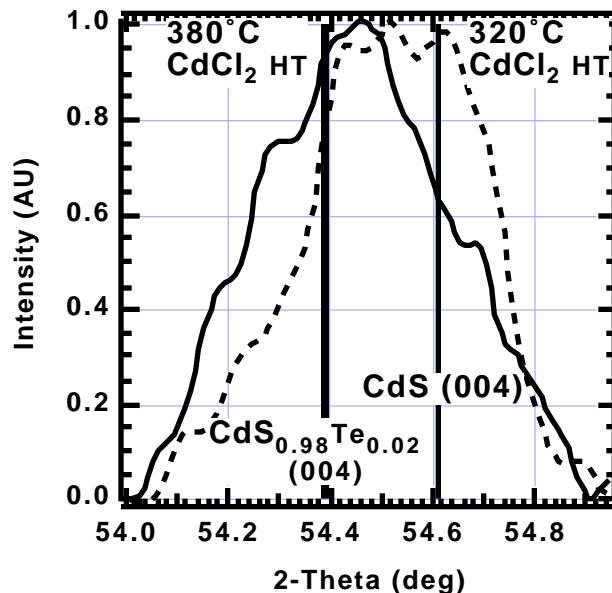

| Figure 4.25 Glancing incidence XRD of CdS (004) on $\text{CdCl}_2$ -treated CdTe/CdS/Quartz with CdTe thinned to profile shown in Figure 4.24; 4° incidence Cu-k .....                                                                                            | 90 |

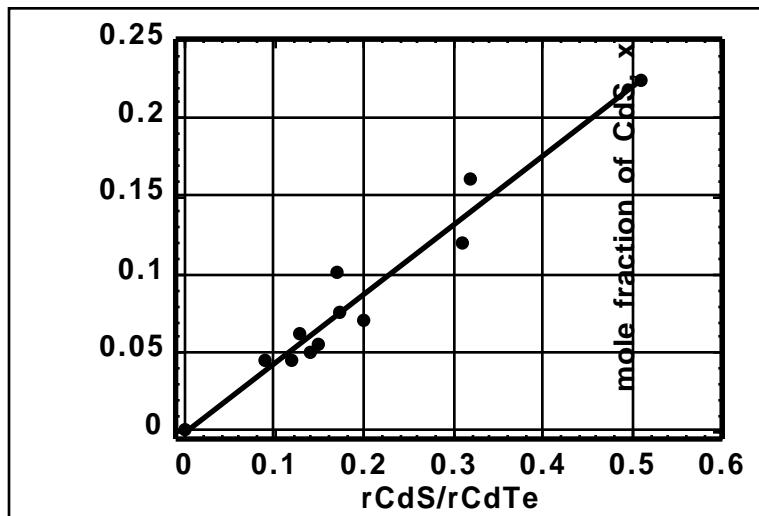

| Figure 4.26 Molar fraction, x, of CdS in $\text{CdTe}_{1-x}\text{S}_x$ films versus effusion rate ratio of CdS and CdTe evaporation sources. Molar fraction determined by EDS measurement of central piece in substrate array. ....                               | 92 |

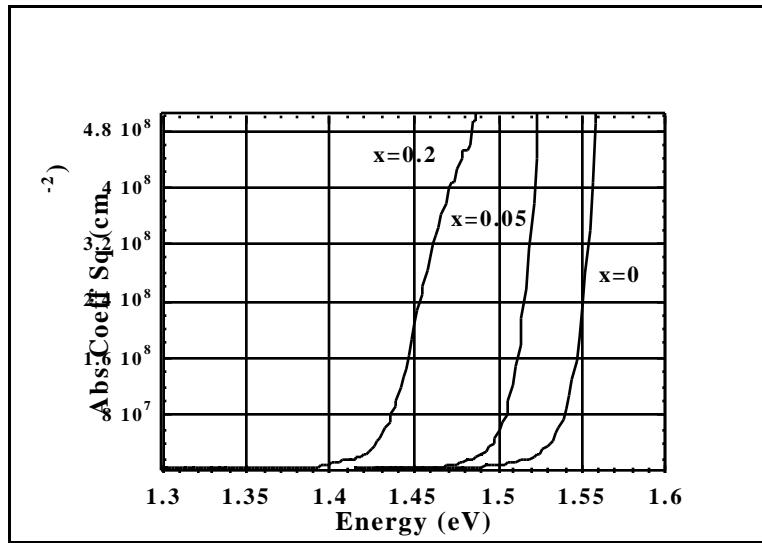

| Figure 4.27 Absorption coefficient squared versus energy for selected $\text{CdTe}_{1-x}\text{S}_x$ films on CdS/ITO window layers over the range of as-deposited composition indicated.....                                                                      | 93 |

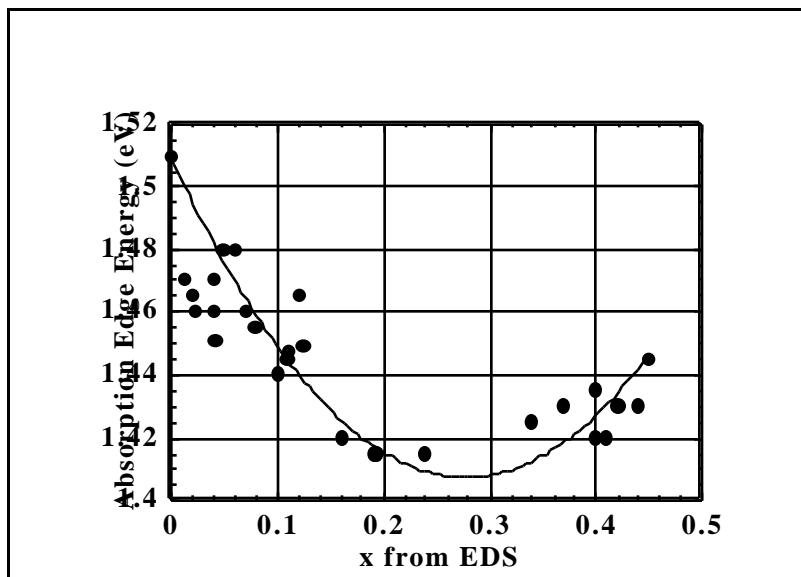

| Figure 4.28 Absorption edge energy versus molar fraction, x, of CdS in $\text{CdTe}_{1-x}\text{S}_x$ for alloy layers on CdS/ITO. The solid line represents the function in Equation 4.8.....                                                                     | 93 |

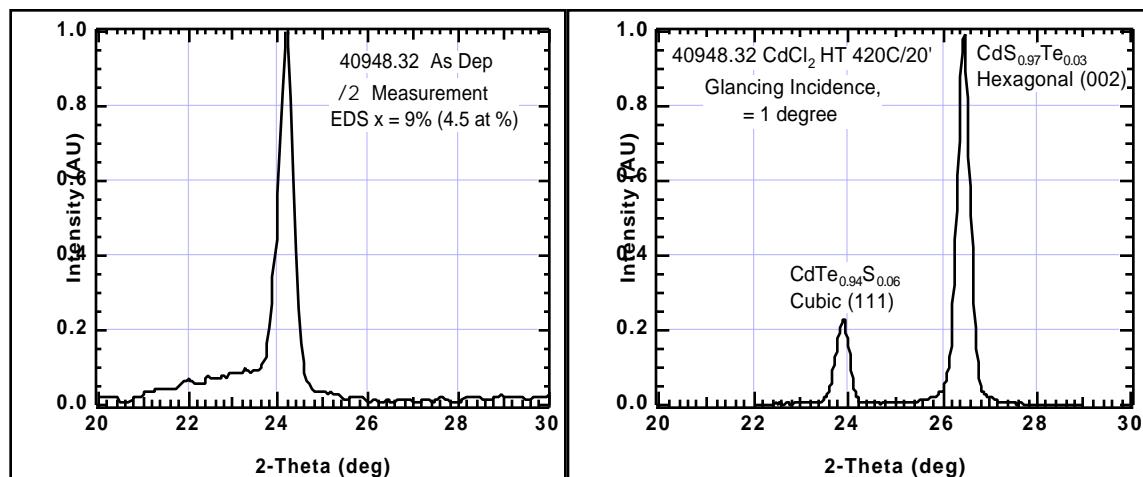

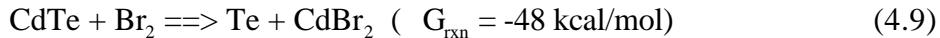

| Figure 4.29 XRD spectra of single phase as-deposited $\text{CdTe}_{0.91}\text{S}_{0.09}$ and the same sample after heat treatment with $\text{CdCl}_2$ at 420°C in air.....                                                                                       | 94 |

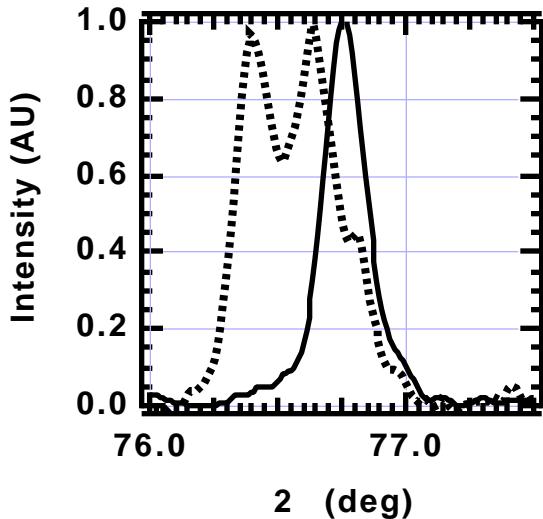

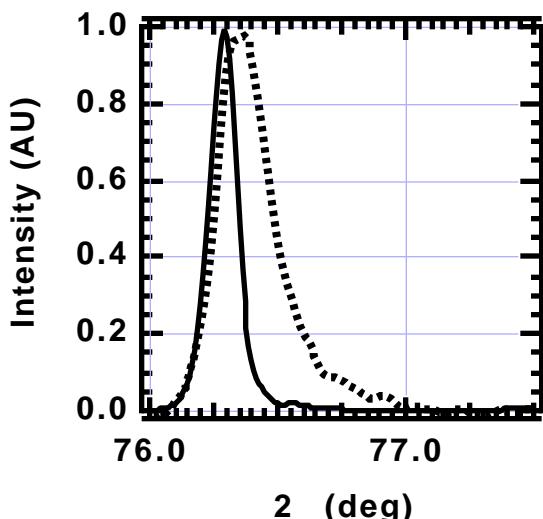

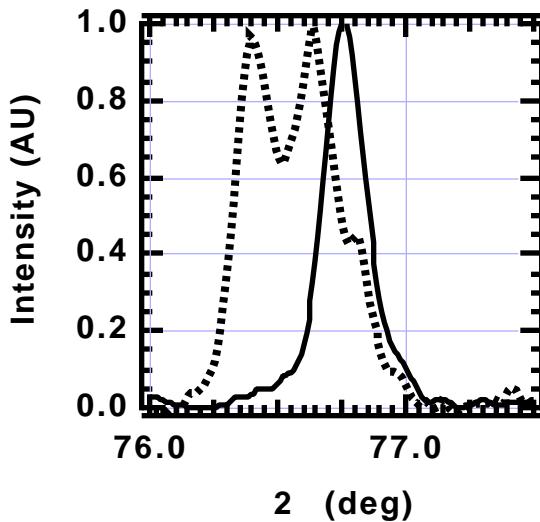

| Figure 4.30 XRD (511) line profile of 2.5 $\mu\text{m}$ CdTe/0.2 $\mu\text{m}$ CdS (dotted) and 2.5 $\mu\text{m}$ $\text{CdTe}_{0.95}\text{S}_{0.05}$ /0.2 $\mu\text{m}$ CdS (solid) after $\text{CdCl}_2$ treatment with high $\text{CdCl}_2$ concentration..... | 95 |

|                                                                                                                                                                                                                                                                            |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

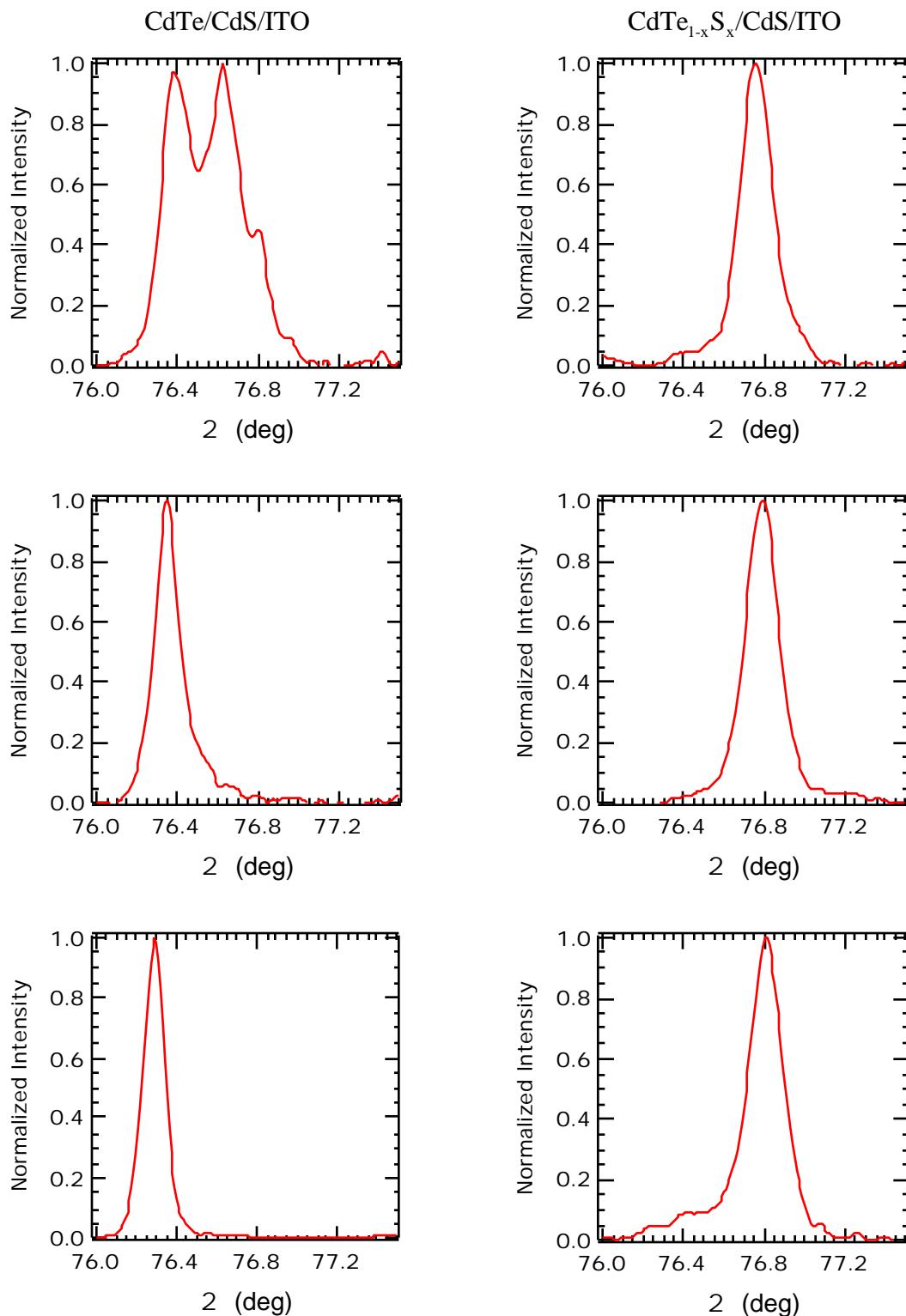

| <b>Figure 4.31</b> X-ray diffraction line profiles for $\text{CdTe}_{1-x}\text{S}_x$ after chloride processing at $420^\circ\text{C}$ for 30 minutes in air. Top = $\text{CdCl}_2:\text{MeOH}$ ; Middle = $\text{CdCl}_2$ vapor; Bottom = HTA + $\text{CdCl}_2$ vapor..... | <b>96</b>  |

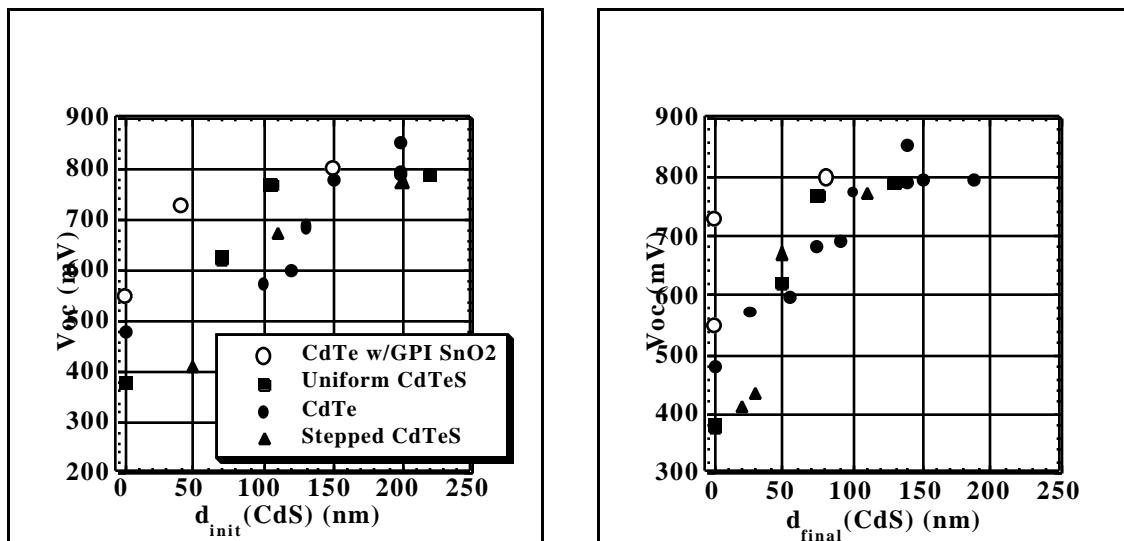

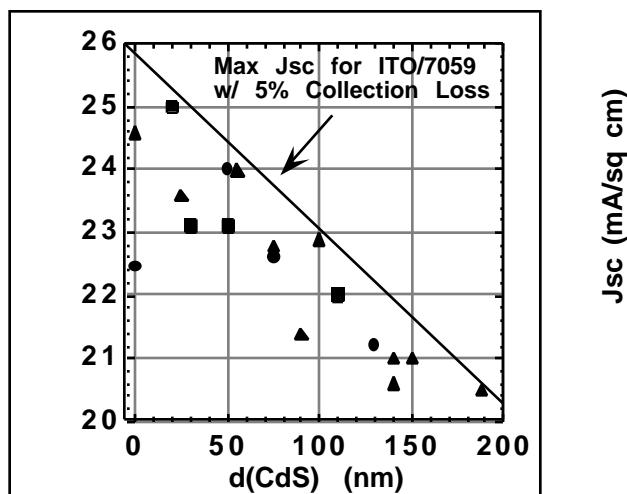

| <b>Figure 4.32</b> $V_{\text{oc}}$ versus CdS thickness for different alloy absorber layer configurations. Filled markers are for devices on ITO/7059. Open circles are for devices with bi-layer $\text{SnO}_2$ superstrates, to be discussed in the next section.....    | <b>98</b>  |

| <b>Figure 4.33</b> $J_{\text{sc}}$ versus final CdS thickness in the devices of Figure 4.32.....                                                                                                                                                                           | <b>98</b>  |

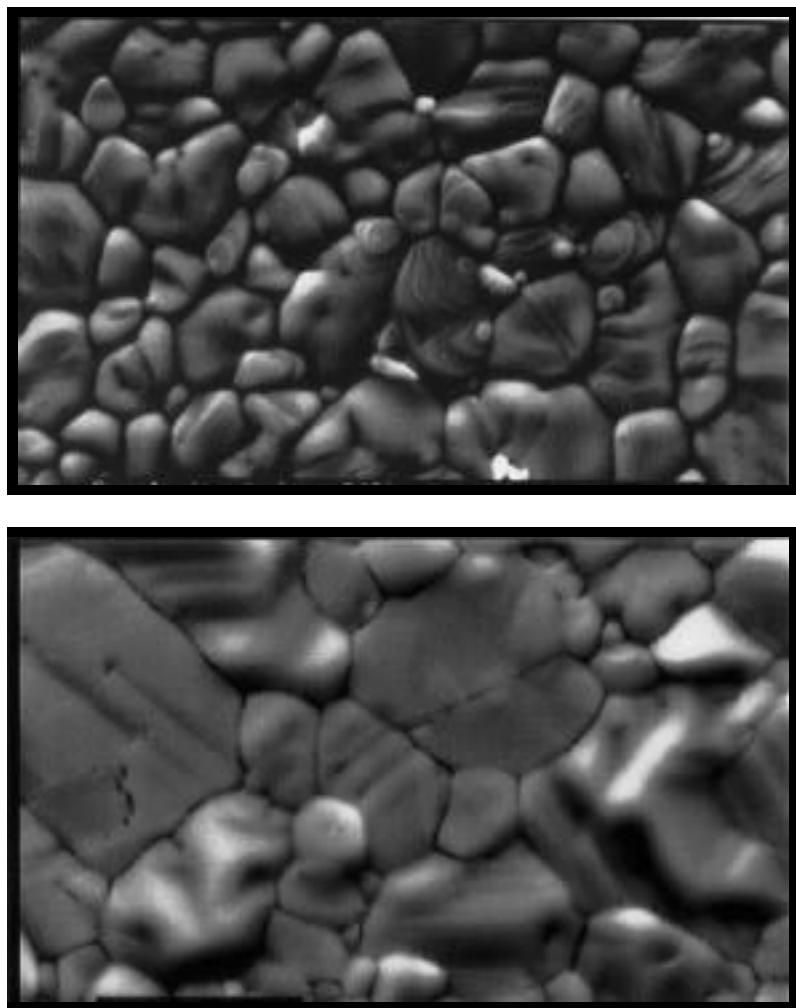

| <b>Figure 4.34</b> SEM photographs of $\text{CdCl}_2$ treated $\text{CdTe}/\text{CdS}$ – no anneal (top) and HTA (bottom) prior to $\text{CdCl}_2$ treatment.....                                                                                                          | <b>99</b>  |

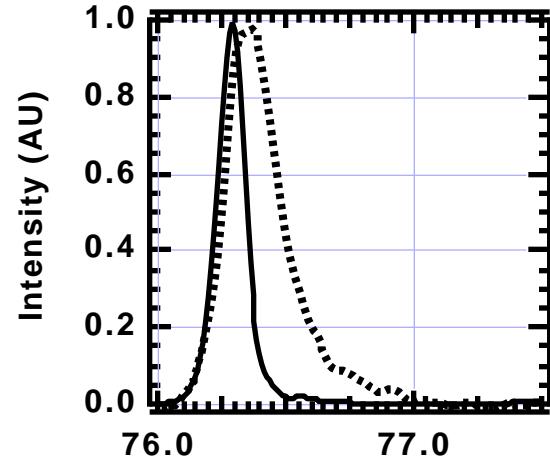

| <b>Figure 4.35</b> XRD (511) line profile of $2.5\ \mu\text{m}$ $\text{CdTe}/0.2\ \mu\text{m}$ CdS after $\text{CdCl}_2$ vapor treatment (dotted) and after anneal in argon at $580^\circ\text{C}$ for 10 minutes followed by $\text{CdCl}_2$ treatment (solid).....       | <b>100</b> |

| <b>Figure 4.36</b> Cross-sectional TEM images of $\text{CdTe}-\text{CdS}$ interface region on $\text{CdCl}_2$ -treated samples with anneal (left) and without anneal (right) prior to chloride treatment.....                                                              | <b>100</b> |

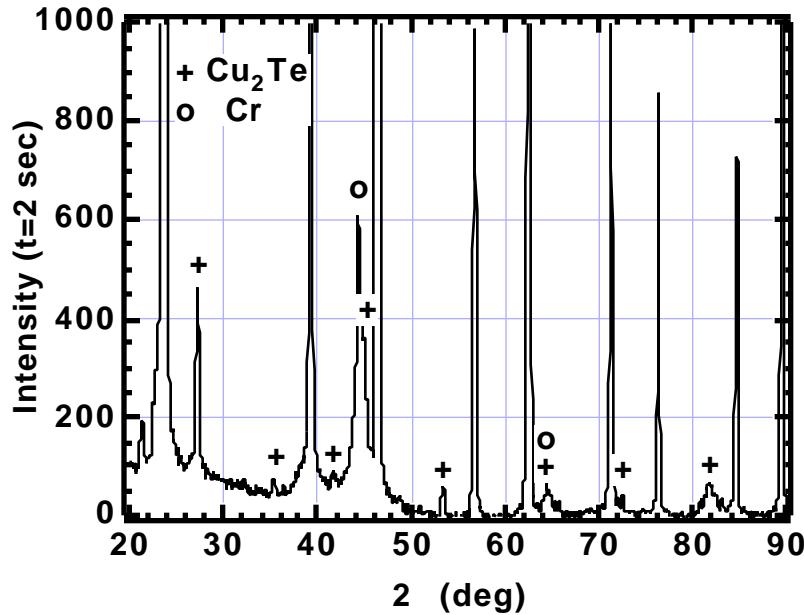

| <b>Figure 4.37</b> Glancing incidence ( $4^\circ$ ) x-ray diffraction pattern of $\text{CdTe}$ device through thin chromium metal contact showing $\text{Cu}_2\text{Te}$ phase.....                                                                                        | <b>105</b> |

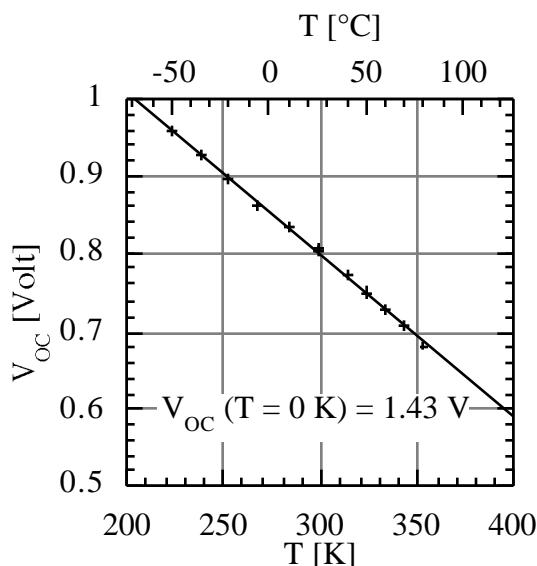

| <b>Figure 4.38</b> $V_{\text{oc}}$ vs T for device #40929-21-5 at AM1.5G. ....                                                                                                                                                                                             | <b>106</b> |

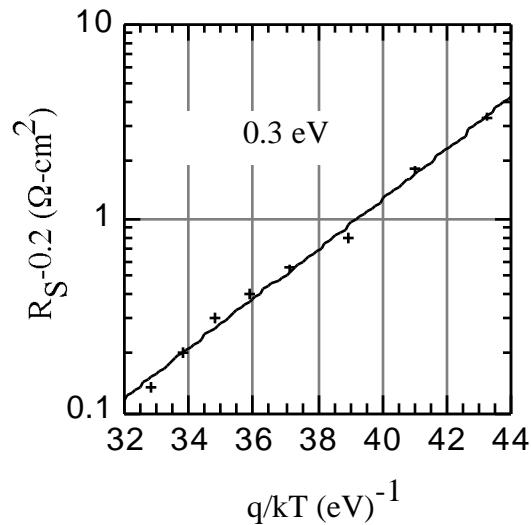

| <b>Figure 4.39</b> Series resistance versus $1/T$ for the same device shown in Figure 4.38.....                                                                                                                                                                            | <b>107</b> |

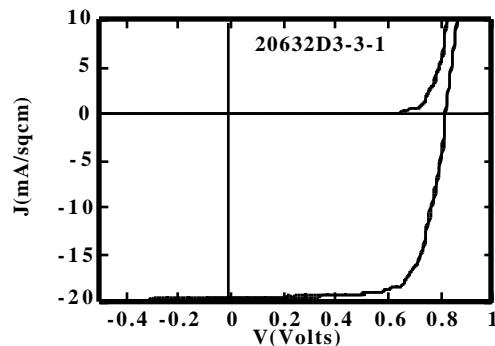

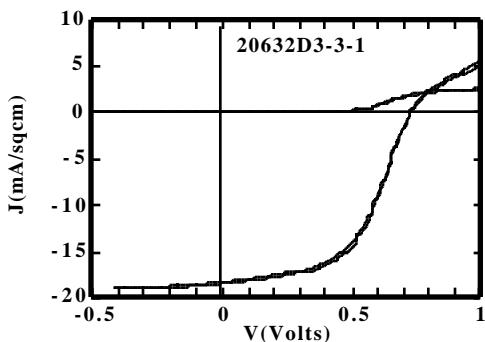

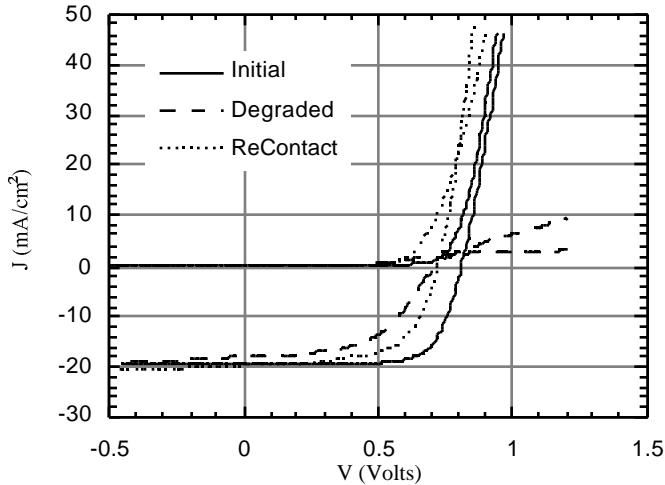

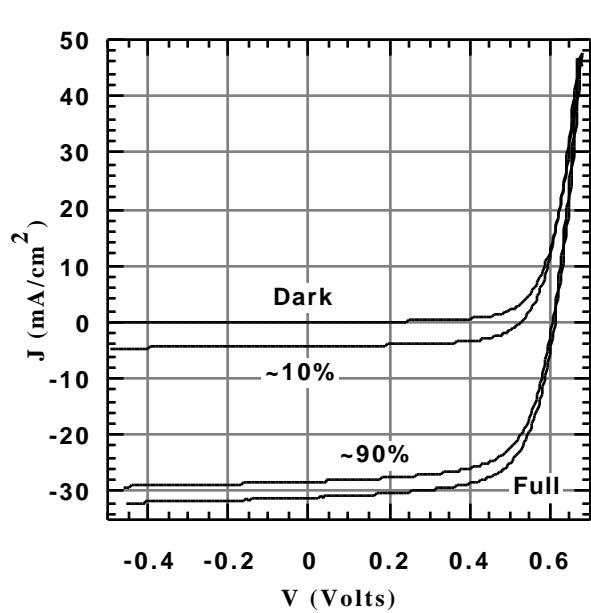

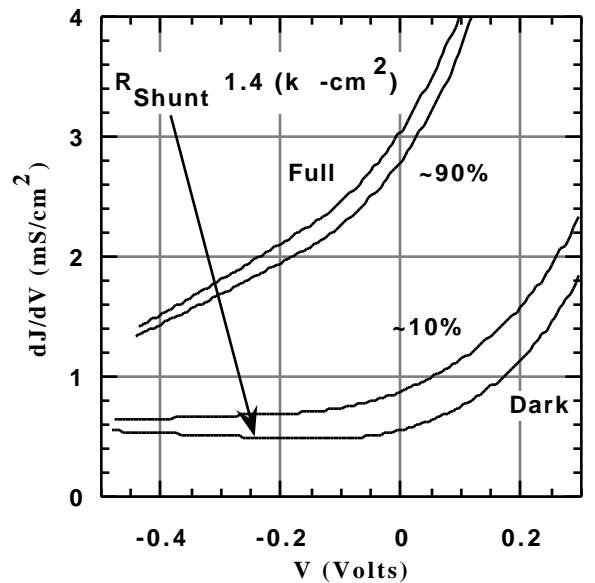

| <b>Figure 4.40</b> J-V behavior of SCI cell with IEC carbon contact before stressing. ....                                                                                                                                                                                 | <b>107</b> |

| <b>Figure 4.41</b> J-V behavior of same cell after stress at $100^\circ\text{C}$ , 2 suns, 6 weeks @ $V_{\text{oc}}$ .....                                                                                                                                                 | <b>108</b> |

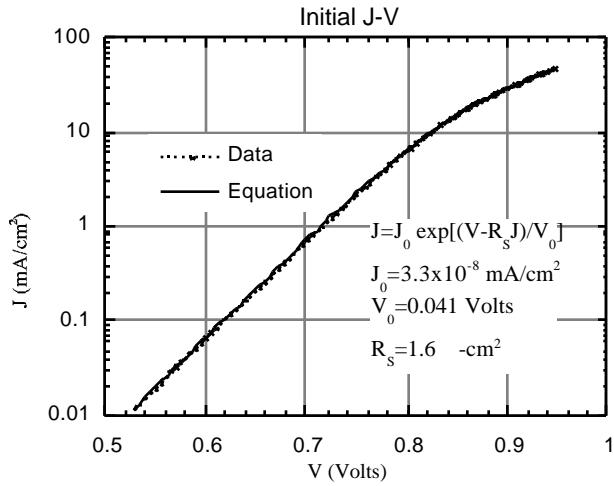

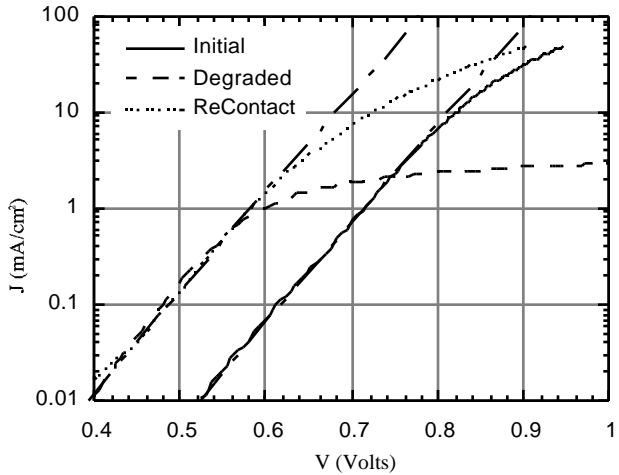

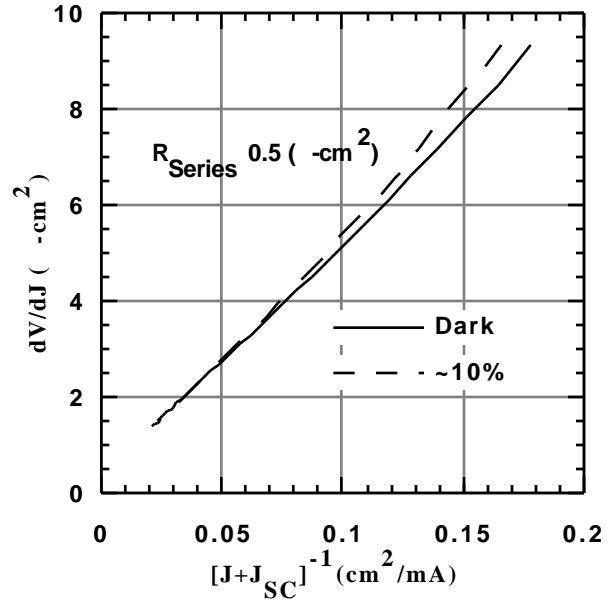

| <b>Figure 4.42</b> Summarized J-V behavior of device # SSI 20632D3-3-1.....                                                                                                                                                                                                | <b>109</b> |

| <b>Figure 4.43</b> Dark J-V data and equivalent circuit fit for before degradation..                                                                                                                                                                                       | <b>109</b> |

| <b>Figure 4.44</b> Summarized dark J-V data and equivalent circuit diode parameters. ....                                                                                                                                                                                  | <b>110</b> |

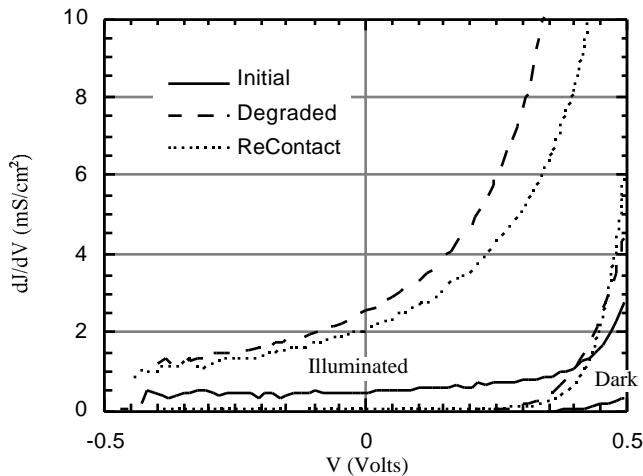

| <b>Figure 4.45</b> Summarized $dJ/dV$ behavior of device # SSI 20632D3-3-1. ....                                                                                                                                                                                           | <b>111</b> |

## LIST OF TABLES

|                                                                                                                                                                                                                                                                                                                                                                                       |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Table 2.1 J-V parameters for various Cu(In,Ga)Se<sub>2</sub> devices measured and analyzed (see text). ....</b>                                                                                                                                                                                                                                                                    | <b>4</b>  |

| <b>Table 2.2 Phases observed by XRD in Cu, In, and Cu/In precursor films on soda lime and 7059 glass substrate and reacted in H<sub>2</sub>S at different temperatures.....</b>                                                                                                                                                                                                       | <b>6</b>  |

| <b>Table 2.3 J-V parameters with varying substrate temperature.....</b>                                                                                                                                                                                                                                                                                                               | <b>14</b> |

| <b>Table 2.4 J-V parameters with decreasing Cu(InGa)Se<sub>2</sub> thickness for films deposited at T<sub>ss</sub> = 450°C.....</b>                                                                                                                                                                                                                                                   | <b>16</b> |

| <b>Table 2.5 Statistics of all the device J-V parameters for each sample made into cells as a function of substrate temperature. Parameters were taken from the best average efficiency test. *Shorted or heavily shunted (dJ/dV@J<sub>sc</sub> ≥ 25 mS/cm<sup>2</sup>) not included in the statistics.....</b>                                                                       | <b>17</b> |

| <b>Table 2.6 Statistics of all the device J-V parameters for each sample made into cells as a function of Cu(InGa)Se<sub>2</sub> thickness. Parameters were taken from the best average efficiency test. *Shorted or heavily shunted (dJ/dV @ J<sub>sc</sub> ≥ 25 mS/cm<sup>2</sup>) not included in the statistics. ....</b>                                                         | <b>18</b> |

| <b>Table 2.7 J-V parameters for Cu(InGa)Se<sub>2</sub>/ZnO devices completed and tested at IEC.....</b>                                                                                                                                                                                                                                                                               | <b>20</b> |

| <b>Table 2.8 Device results with ZnO buffer layers deposited on Cu(InGa)Se<sub>2</sub> in Ar and Ar:H<sub>2</sub> sputter gases.....</b>                                                                                                                                                                                                                                              | <b>21</b> |

| <b>Table 2.9 Sheet resistances of different TCO materials deposited on glass and glass/CdS substrates.....</b>                                                                                                                                                                                                                                                                        | <b>21</b> |

| <b>Table 3.1 Deposition conditions of standard devices .....</b>                                                                                                                                                                                                                                                                                                                      | <b>41</b> |

| <b>Table 3.2 Results from series with new "soft start" for different p-layer deposition times. All devices had ZnO/Ag contacts. R<sub>oc</sub> is slope at V<sub>oc</sub>, R<sub>s</sub> is intercept of dV/dJ vs 1/J from dark diode (series or contact resistance). 4719-22 and 4743-22 were deposited without a soft start p-layer before and after the soft start series.....</b> | <b>43</b> |

| <b>Table 3.3 Initial and light soaked performance of four p-b-i<sub>1</sub>-i<sub>2</sub>-n devices with different i<sub>1</sub> layers. All i<sub>2</sub> layers were 0.5 μm deposited without H<sub>2</sub> dilution. Light soaking for 200 hours at 25°C under ELH lights @ 100 mW/cm<sup>2</sup>. Light soaked values in ( ). ....</b>                                            | <b>44</b> |

| <b>Table 3.4 Results for four devices deposited in run 4741 on different TCO substrates.....</b>                                                                                                                                                                                                                                                                                      | <b>46</b> |

| <b>Table 3.5 Structure and thicknesses of a-Si and μc-Si layers in test structures used for sputtered TCO contact study.....</b>                                                                                                                                                                                                                                                      | <b>48</b> |

| <b>Table 3.6 Sputtered TCO layers used to contact each piece from runs 4685-4688. Balance of gas flow is Ar.....</b>                                                                                                                                                                                                                                                                  | <b>48</b> |

| <b>Table 3.7 Illuminated JV parameters of glass/SnO<sub>2</sub>/μc-Si n/a-Si/ i/sputtered TCO devices from 4687 under ELH light. V<sub>oc</sub>, J<sub>sc</sub>, FF and R<sub>oc</sub> from measurement at 25°C as shown in Figure 3.7, while V<sub>oc</sub>/A, E<sub>a</sub>, and J<sub>oo</sub> from temperature dependence of Figure 3.8 and Figure 3.9.....</b>                   | <b>50</b> |

|                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Table 3.8</b> Resistance $dV/dJ$ at 0V in $\Omega\text{-cm}^2$ at $25^\circ\text{C}$ for glass/SnO <sub>2</sub> /n-layer/TCO devices with $\mu\text{-Si}$ (4685) and a-Si (4686) n-layers.....                                                                                                                                                                                                         | 55  |

| <b>Table 4.1</b> As-deposited methods and selected properties.....                                                                                                                                                                                                                                                                                                                                        | 59  |

| <b>Table 4.2</b> Selected properties after treatment at $\sim 400^\circ\text{C}$ .....                                                                                                                                                                                                                                                                                                                    | 60  |

| <b>Table 4.3</b> CdS deposition methods and film properties.....                                                                                                                                                                                                                                                                                                                                          | 61  |

| <b>Table 4.4</b> CdTe deposition methods and as-deposited film properties.....                                                                                                                                                                                                                                                                                                                            | 61  |

| <b>Table 4.5</b> Film properties in finished device structures based on analysis performed by IEC for NREL CdTe - Thin CdS Team.....                                                                                                                                                                                                                                                                      | 62  |

| <b>Table 4.6</b> Device results for representative samples of Table 4.3, Table 4.4 and Table 4.5, receiving contacts at IEC. NREL and Golden Photon results are based on published data.....                                                                                                                                                                                                              | 62  |

| <b>Table 4.7</b> Results of CdS film pinhole and surface particulate survey. Column definitions are as follows: TCO# = run #; $d(\text{CdS})$ = Thickness; Area $h$ = area of pinholes in survey region; $F_h$ = fractional area of pinholes; Area $p$ = area of particulates in survey region; $F_p$ = fractional area of particulates; $F_h+F_p$ = sum of pinhole and particulate fractional areas..... | 72  |

| <b>Table 4.8</b> Estimated drop in $V_{oc}$ versus $F$ for CdTe/CdS/ITO.....                                                                                                                                                                                                                                                                                                                              | 73  |

| <b>Table 4.9</b> Participating groups, deposition processes, and approximate film thicknesses for Set #1 samples used in x-ray diffraction study: CSS = close-space sublimation, ED = electrodeposition, EVD = elemental vapor deposition, PVD = physical vapor deposition, RFSD = rf sputter deposition.....                                                                                             | 81  |

| <b>Table 4.10</b> Summary of sample identification, preparation and XRD measurements performed.....                                                                                                                                                                                                                                                                                                       | 82  |

| <b>Table 4.11</b> Orientation and CdTe <sub>1-x</sub> S <sub>x</sub> composition from broad XRD scans before (Initial) and after thinning (Thinned) CdTe layer to 2 $\mu\text{m}$ .....                                                                                                                                                                                                                   | 82  |

| <b>Table 4.12</b> Summary of CdTe peak profile and estimate of CdS uptake by CdTe film. The instrument HWHM for CdTe is $0.06^\circ$ . Determinations made by analysis of XRD peak profiles are compared to those made by change in CdS transmission. Composition of the doublet component is indicated in parentheses in atomic percent.....                                                             | 87  |

| <b>Table 4.13</b> Composition of CdTe <sub>1-x</sub> S <sub>x</sub> absorber layers determined by EDS and XRD methods.....                                                                                                                                                                                                                                                                                | 92  |

| <b>Table 4.14</b> Treatment conditions and materials data for 2.5 $\mu\text{m}$ thick absorber layers on CdS/ITO after CdCl <sub>2</sub> processing at $420^\circ\text{C}$ for 30 minutes in air. The third sample in each group received a high temperature anneal (HTA) at $600^\circ\text{C}$ for 15 minutes prior to CdCl <sub>2</sub> vapor treatment.....                                           | 95  |

| <b>Table 4.15</b> CdS thickness from optical and QE data compared to device J-V parameters for different alloy configurations.....                                                                                                                                                                                                                                                                        | 97  |

| <b>Table 4.16</b> CdS thickness from optical and QE data and device parameters for different heat treatments.....                                                                                                                                                                                                                                                                                         | 101 |

| <b>Table 4.17</b> Device fabrication conditions and J-V results using alternative TCO.....                                                                                                                                                                                                                                                                                                                | 103 |

|                                                                                                                          |            |

|--------------------------------------------------------------------------------------------------------------------------|------------|

| <b>Table 4.18</b> Device fabrication steps and J-V results for cells with hydrazine etch prior to copper deposition..... | <b>105</b> |

| <b>Table 4.19</b> Device results for device # SSI 20632D3-3-1. ....                                                      | <b>108</b> |

| <b>Table 4.20</b> Diode parameters of the straight line fits shown in Figure 4.44. .                                     | <b>110</b> |

## 1. Introduction

Photovoltaic modules based on thin film systems of a-Si:H and its alloys, CuInSe<sub>2</sub> and its alloys, and CdTe are promising candidates to meet DOE long range efficiency, reliability and manufacturing cost goals. The commercial development of these modules is at different stages and there are generic research issues that need to be addressed.

- quantitative analysis of processing steps to provide information for efficient commercial scale equipment design and operation;

- device characterization relating the device performance to materials properties and process conditions;

- development of alloy materials with different bandgaps to allow improved device structures for stability and compatibility with module design;

- development of improved window/heterojunction layers and contacts to improve device performance and reliability; and

- evaluation of cell stability with respect to illumination, temperature and ambient and with respect to device structure and module encapsulation.

The critical issues that are being addressed under this four-year NREL program for the specific thin film materials system are discussed below.

### 1.1 CuInSe<sub>2</sub>-based Solar Cells

CuInSe<sub>2</sub> has a bandgap of 1 eV and the devices typically have  $V_{oc}$  less than 0.5 V. This bandgap is about 0.5 eV less than required for a single junction device to have optimal efficiency for terrestrial applications. Further, the high  $J_{sc}$  of these devices reduces module performance because of higher cell spacing and series resistance losses, and because devices with low operating losses typically suffer larger fractional losses as the devices are operated under real PV module operating conditions (module operating temperatures of 50° to 60°C) as compared to operation under standard measurement conditions (25°C). Champion cells have been made with bandgaps of about 1.2 eV through the addition of Ga. It is desirable to further increase the bandgap from 1.4 to 1.6 eV for improved module performance.

Presently, most companies developing CuInSe<sub>2</sub> for modules form the CuInSe<sub>2</sub> films by the selenization of Cu/In films in either an H<sub>2</sub>Se or Se atmosphere. Progress has been made in characterizing the chemical pathways to film growth and estimating the reaction rate constants. As the process evolves to include the CuInSe<sub>2</sub> alloys, characterization of the reaction chemistry and kinetics needs to be extended to the alloys. While reaction pathways have been identified that lead to the formation of near stoichiometric CuIn<sub>1-x</sub>Ga<sub>x</sub>Se<sub>2</sub> when the processing temperatures are limited to below 400°C, all cells with record-level efficiencies were produced by reacting the absorber layers at temperatures above 500°C. Such high processing temperatures limit the choice of substrate materials (e.g., lightweight Kapton foil) and make processing and substrate handling in general more difficult. It is presently not well understood why the champion cells had to be processed at such high temperatures.

### 1.2 a-Si:H-based Solar Cells

Amorphous silicon (a-Si) PV modules were the first thin-film PV modules to be commercially produced and are presently the only thin-film technology that had an impact on the overall PV markets. However, the efficiencies of these modules have not yet reached the levels that were predicted in the 1980s. To a significant degree this is due to the intrinsic degradation of a-Si under illumination. The amount of light-induced degradation can be limited to 20 to 30% in models

operating under prevailing outdoor conditions. Both material processing schemes and device design schemes have been developed to improve the stabilized solar cell efficiency of a-Si solar cells. The use of multijunction devices (allowing the use of thinner absorber layers in the component cells) and the use of employing light-trapping appear to be the most powerful device design schemes to improve stabilized device performance.

The US industry is currently using these approaches to build a-Si-based modules. The so-called substrate type devices are built on stainless steel foil, covered with a “back reflector.” The superstrate devices are built on glass coated with transparent conductors (TCO). The texture and transparency of the TCO contacts are critical to improve light-trapping and  $J_{sc}$ . Reducing optical losses in the TCO will allow thinner i-layers to generate the same  $J_{sc}$ , thus improving stability.

The national amorphous silicon teams have broken down the optimization of stabilized cell performance into the individual high-, mid-, and low-bandgap component cells. However, the optimization of two-terminal dual or triple-junction cells has further requirements such as to minimize the electrical and optical losses in the internal p/n junctions. The p and n layers of a cell have to be optimized not only to result in optimum performance of the component cells, but also to give the lowest losses in multi-junction devices.

### **1.3 CdTe-based Solar Cells**

Instability of CdTe-based solar cells and modules is commonly assumed to be related to the rear contact, especially if this contact is Cu-doped. There is a need to further develop a stable ohmic contact for CdTe compatible with monolithic integration technologies. New contacts must be tested and a method developed to rapidly characterize stability. It appears likely that the optimization of such a contact depends also on the details of the other layers used in the device (CdTe, CdS, SnO, type of glass).

The effects of high temperature processing, either during deposition or after film growth, and CdCl<sub>2</sub> treatments on the operation of the device are not well characterized. Of particular concern is the uniformity of large-area modules and the “robustness” of such processes. Questions concerning CdS-CdTe interdiffusion, O and Cl doping, and chemical reactions between CdCl<sub>2</sub> and CdTe need to be addressed quantitatively.

Although many researchers have produced devices with 12% efficiency, few have exceeded 14%. The challenge is to obtain high values for  $J_{sc}$  without loss of  $V_{oc}$ , and a good spectral response at short wavelengths ( $< 500$  nm) without sacrificing the spectral response at longer wavelengths. It is important to understand which factors lead to cells in which such losses can be avoided. It has been established that cell parameters are sensitive to the details of the CdS/CdTe interface. Understanding the mechanisms in detail would accelerate device optimization, which is more and more realized to be an interactive process requiring the optimization of each layer in the device depending on all the other layers present.

### **1.4 Organization of the Report**

This report is organized into three technical sections: CuInSe<sub>2</sub>-based solar cells, a-Si:H-based solar cells, and CdTe-based solar cells. Each section describes the progress made in addressing the critical issues discussed above during phase I of the program. Based on the results of this phase, the statement of work for phase II was evaluated and modified accordingly.

## 2. CuInSe<sub>2</sub>-based Solar Cells

### 2.1 High Bandgap CuInSe<sub>2</sub> Alloys

#### 2.1.1 Introduction

CuInSe<sub>2</sub> has a bandgap of 1.0 eV and most Cu(InGa)Se<sub>2</sub> based devices have absorber layers with Ga/(In+Ga) = 0.25 which gives a bandgap of 1.15 eV and results in devices with open circuit voltages < 0.65V. Higher Ga concentrations to increase the Cu(InGa)Se<sub>2</sub> bandgap result in a tradeoff of higher open circuit voltage and lower short circuit current which may allow increased cell efficiency. Further, module performance should be improved due to lower resistive losses, thinner ZnO with less optical loss and/or greater interconnect spacing with reduced associated area related losses.

We have previously demonstrated Cu(InGa)Se<sub>2</sub> solar cells with 15% efficiency for Ga/(In+Ga) = 0.5 or bandgap (Eg) = 1.3 eV [101, 102]. With higher bandgap a decrease in cell efficiency was shown to be caused by poor collection of light generated minority carriers in the Cu(InGa)Se<sub>2</sub> absorber layers. In this work we have continued characterization of Cu(InGa)Se<sub>2</sub> devices with increasing Ga content and bandgap. In addition, we have begun to investigate other Cu(InGa)Se<sub>2</sub> based alloy materials, CuInS<sub>2</sub> and Cu(InAl)Se<sub>2</sub>, which may provide alternative means to achieve improved device performance with Eg > 1.3 eV.

#### 2.1.2 Cu(In,Ga)Se<sub>2</sub> device analysis

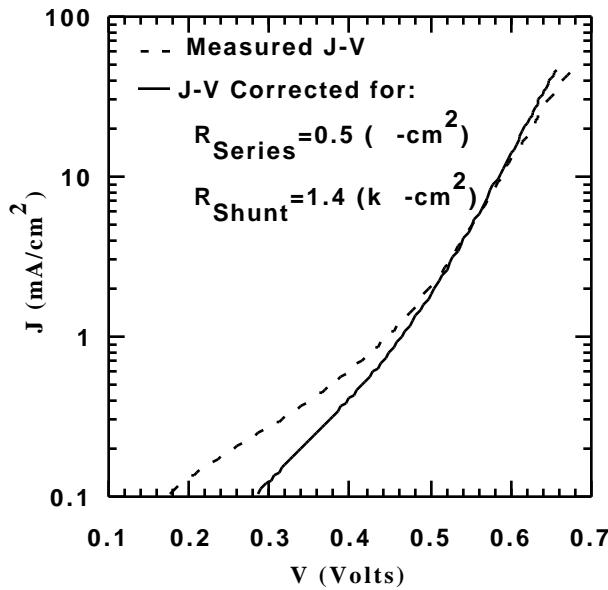

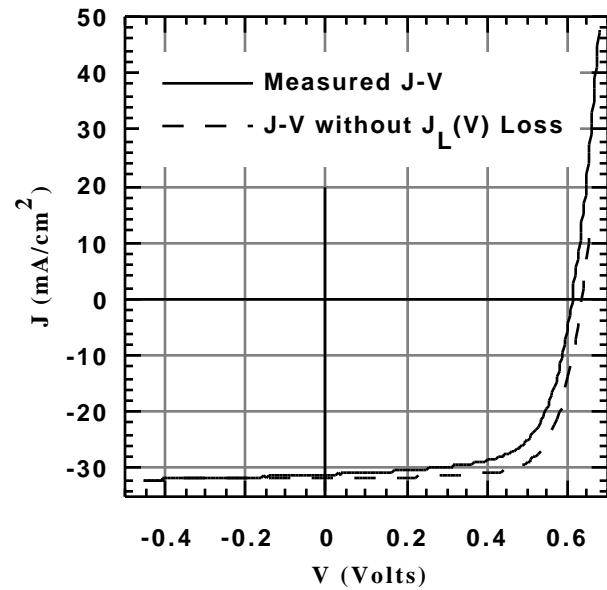

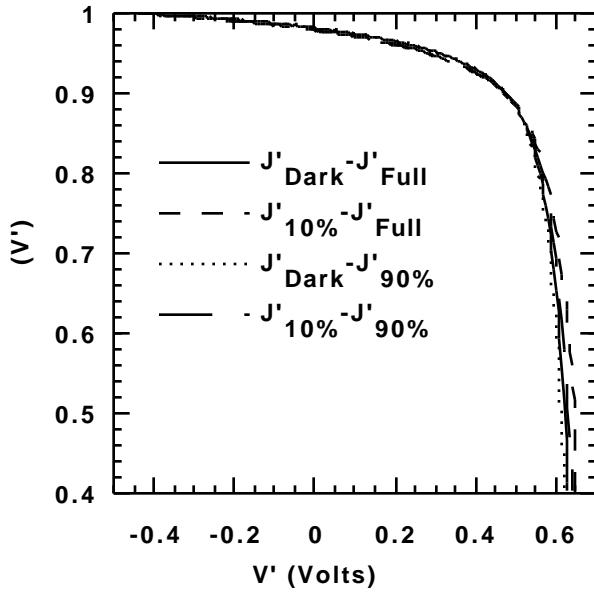

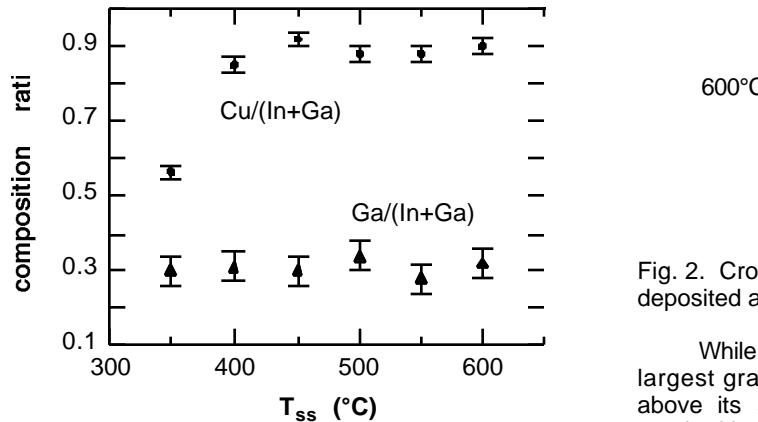

As the bandgap of CuInSe<sub>2</sub> is increased by alloying with Ga or S, the loss in efficiency due to the decrease of light generated current with increasing voltage becomes important. The standard technique of quantifying this loss is to analyze spectral response measurements made as a function of applied voltage. Instead, it is shown how to determine the voltage dependence of the light generated current by an analysis of the current-voltage (I-V) measurements made at two different light intensities. By adding an I-V measurement at a third light intensity one can also determine if the analysis technique is valid ([103] and Appendix 1).

##### 2.1.2.1 Experimental procedures

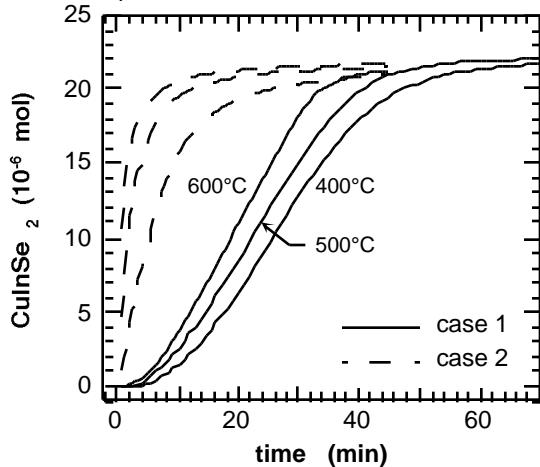

It has been demonstrated that the loss in efficiency of Cu(In,Ga)Se<sub>2</sub> solar cells with high Ga content is due to a decrease in fill factor, and to a lesser extent  $V_{oc}$  which is caused by a drop in the light generated current with increasing forward voltage [101, 102]. This type of loss mechanism is well known in amorphous silicon solar cells where I-V measurement and analysis techniques have been developed to determine the voltage dependence of the light generated current,  $J_L(V)$ , [104, 105].