245

6-15-81

jw/a

②

DR-2756

SERI/PR-9080-1-T3

## MIS SOLAR CELLS ON THIN POLYCRYSTALLINE SILICON

Progress Report No. 3 for Period September 1–November 30, 1980

By

Wayne A. Anderson

MASTER

December 1980

Work Performed Under Contract No. AC02-77CH00178

State University of New York at Buffalo

Electrical Engineering Department

Amherst, New York

63

Disk 197

UT5-25

# U.S. Department of Energy

Solar Energy

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

## DISCLAIMER

"This book was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof."

This report has been reproduced directly from the best available copy.

Available from the National Technical Information Service, U. S. Department of Commerce, Springfield, Virginia 22161.

Price: Printed Copy A05

Microfiche A01

**MIS SOLAR CELLS ON THIN

POLYCRYSTALLINE SILICON**

**Progress Report No. 3**

**September 1, 1980-November 30, 1980**

**Wayne A. Anderson**

**December 1980**

**The State University of New York at Buffalo

Electrical Engineering Department

4232 Ridge Lea Road

Amherst, New York 14226**

**Prepared for the

Solar Energy Research Institute

Photovoltaic Programs Office

1617 Cole Boulevard

Golden, Colorado 80401

Solar Energy

Under Sub-Contract XM-0-9080-1**

## OBJECTIVES

Task 1 of this project involves electron-beam deposition of thin silicon films on low cost substrates. The goal is to obtain 20  $\mu\text{m}$  thick films having 20  $\mu\text{m}$  diameter crystallites which may be recrystallized to > 40  $\mu\text{m}$ . Material characterization and device studies are to be included in efforts to reach a 6% conversion efficiency by March 1981.

The second task deals with MIS solar cell fabrication on various types of silicon including poly-Si, ribbon-Si, silicon on ceramic, and thin film silicon. Conduction mechanism studies, optimum engineering design, and modification of the fabrication process are to be used to achieve 13% efficiency on Xtal-Si and 11% efficiency on poly-Si.

Task 3 involves more detailed test procedures and includes spectral response, interface and grain boundary effects, computer analysis, materials studies, and grain boundary passivation. Stability and degradation studies will be performed as part of Task 4.

## NOTE

ANY OPINIONS, FINDINGS, CONCLUSIONS, OR RECOMMENDATIONS IN THIS PUBLICATION ARE THOSE OF THE AUTHOR AND DO NOT NECESSARILY REFLECT THE VIEW OF THE DEPARTMENT OF ENERGY.

## TABLE OF CONTENTS

|                                                                              | <u>Page</u> |

|------------------------------------------------------------------------------|-------------|

| COVER PAGE . . . . .                                                         | i           |

| OBJECTIVES . . . . .                                                         | ii          |

| CONTENTS . . . . .                                                           | iii         |

| FIGURES. . . . .                                                             | iv          |

| TABLES . . . . .                                                             | v           |

| 1. SUMMARY. . . . .                                                          | 1           |

| 2. INTRODUCTION . . . . .                                                    | 2           |

| 3. THIN FILM SILICON DEPOSITION AND ANALYSIS. . . . .                        | 3           |

| 3-1 Thin Film Silicon Déposition and Surface Analysis (M. Jackson) . . . . . | 3           |

| 3-2 Thin Film Silicon Electrical Studies (F. Kai) . . . . .                  | 9           |

| 4. Cr-MIS SOLAR CELL FABRICATION. . . . .                                    | 14          |

| 4-1 Device Processing Techniques (G. Rajeswaran) . . . . .                   | 14          |

| a) Planar Etch (P.E.) . . . . .                                              | 14          |

| b) One Cleaning, One Oxide Process (OO) . . . . .                            | 15          |

| c) Double Cleaning, Double Oxide Process (DO) . . . . .                      | 15          |

| d) Double Cleaning, One Oxide Process (DO) . . . . .                         | 16          |

| 4-2 Summary of Photovoltaic Data (G. Rajeswaran) . . . . .                   | 16          |

| 5. ANALYSIS OF MIS SOLAR CELLS. . . . .                                      | 25          |

| 5-1 Grain Boundary Studies by C-V-f and G-V-f (V. J. Rao) . . . . .          | 25          |

| 5-2 Auger, ESCA and Ellipsometer Studies. . . . .                            | 31          |

| 6. RELIABILITY STUDIES (M. Thayer) . . . . .                                 | 34          |

| 7. REFERENCES . . . . .                                                      | 36          |

| 8. CONCLUSIONS. . . . .                                                      | 37          |

| 9. PLANS FOR THE NEXT QUARTER . . . . .                                      | 37          |

| 10. RESEARCH PARTICIPANTS. . . . .                                           | 38          |

| 11. REPORTS/PUBLICATIONS/PRESENTATIONS . . . . .                             | 38          |

## LIST OF FIGURES

| <u>Figure</u> |                                                                                                                            | <u>Page</u> |

|---------------|----------------------------------------------------------------------------------------------------------------------------|-------------|

| 1A            | SEM micrograph (100X) showing an e-beam Si film on a Wacker Si substrate. Replication of the substrate is obvious. . . . . | 5           |

| 1B            | SEM micrograph (1500X) showing whisker-like columnar growth at the edge of a Si substrate . . . . .                        | 5           |

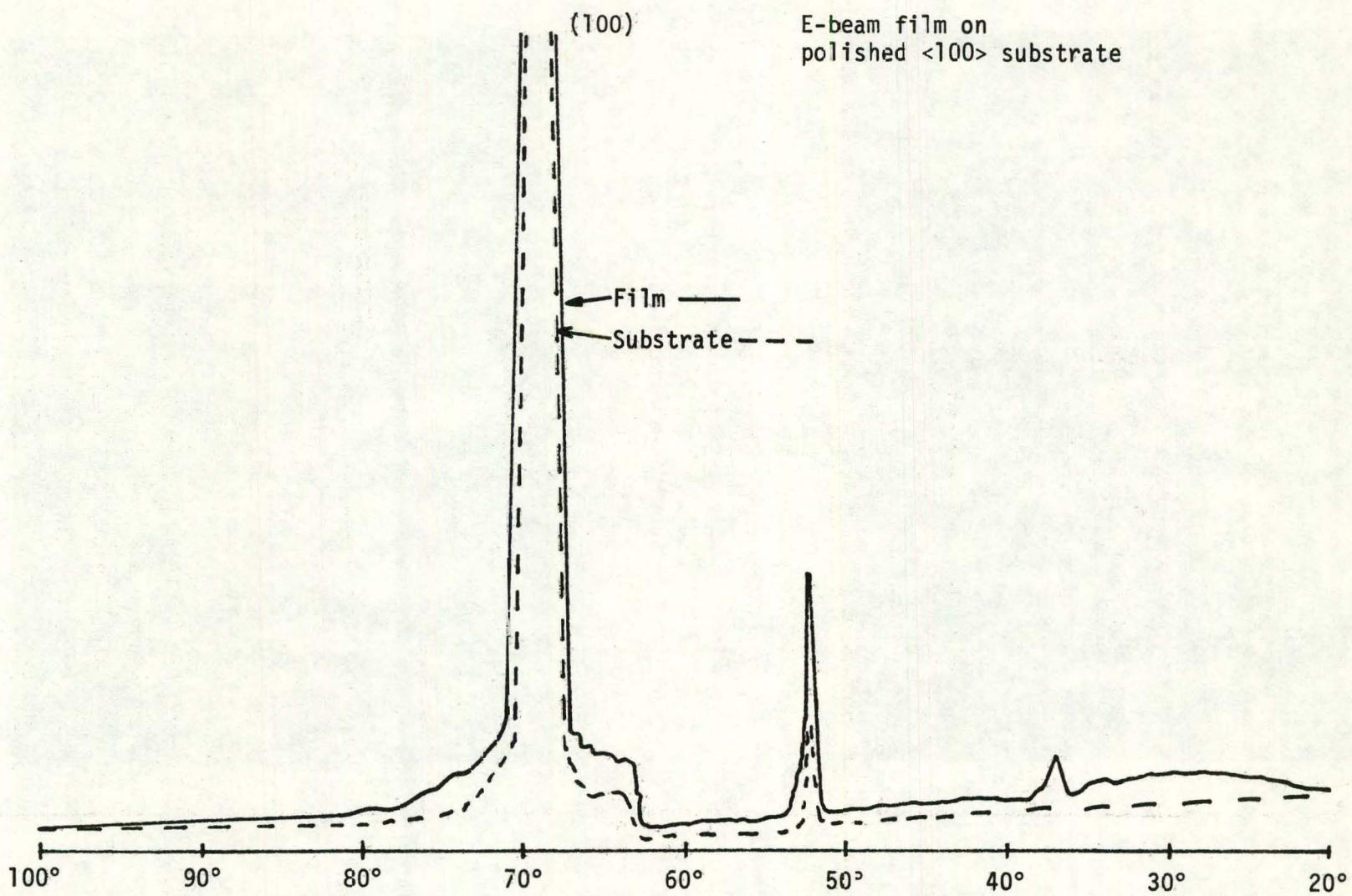

| 2             | X-ray data for an e-beam Si film on a (100) Si substrate. . . . .                                                          | 6           |

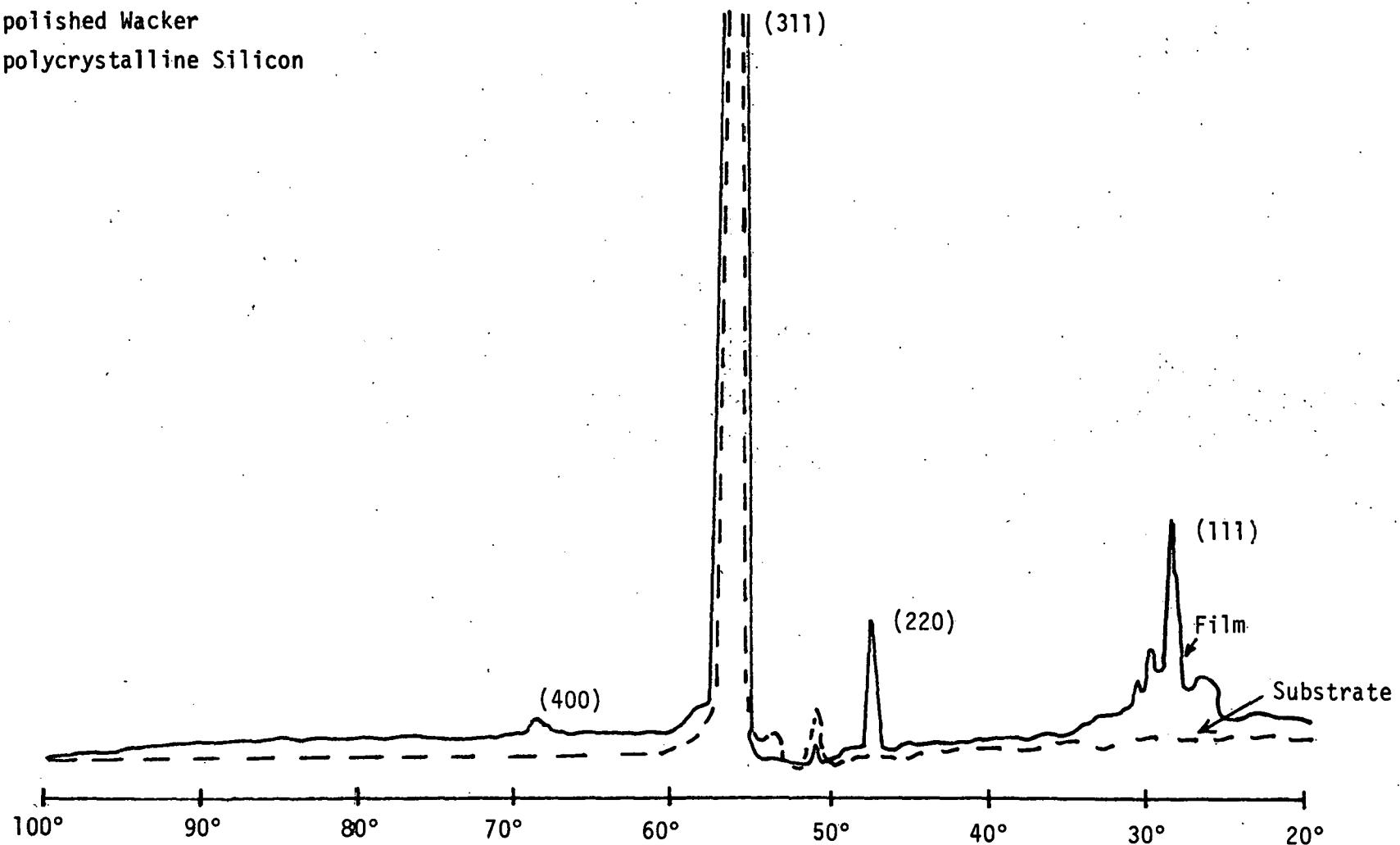

| 3             | X-ray data for an e-beam Si film on a Wacker Si substrate . . . . .                                                        | 7           |

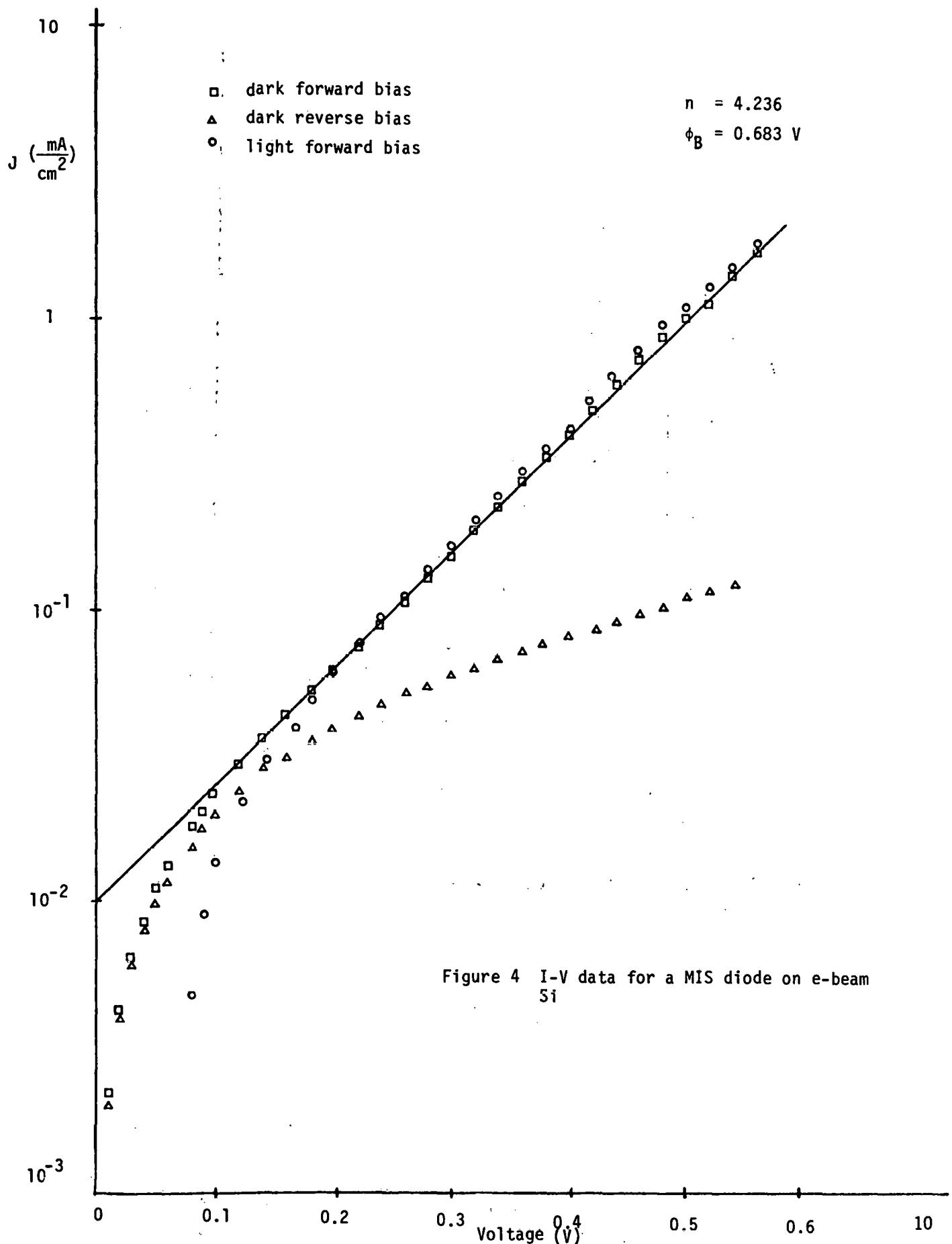

| 4             | I-V data for a MIS diode on e-beam Si . . . . .                                                                            | 10          |

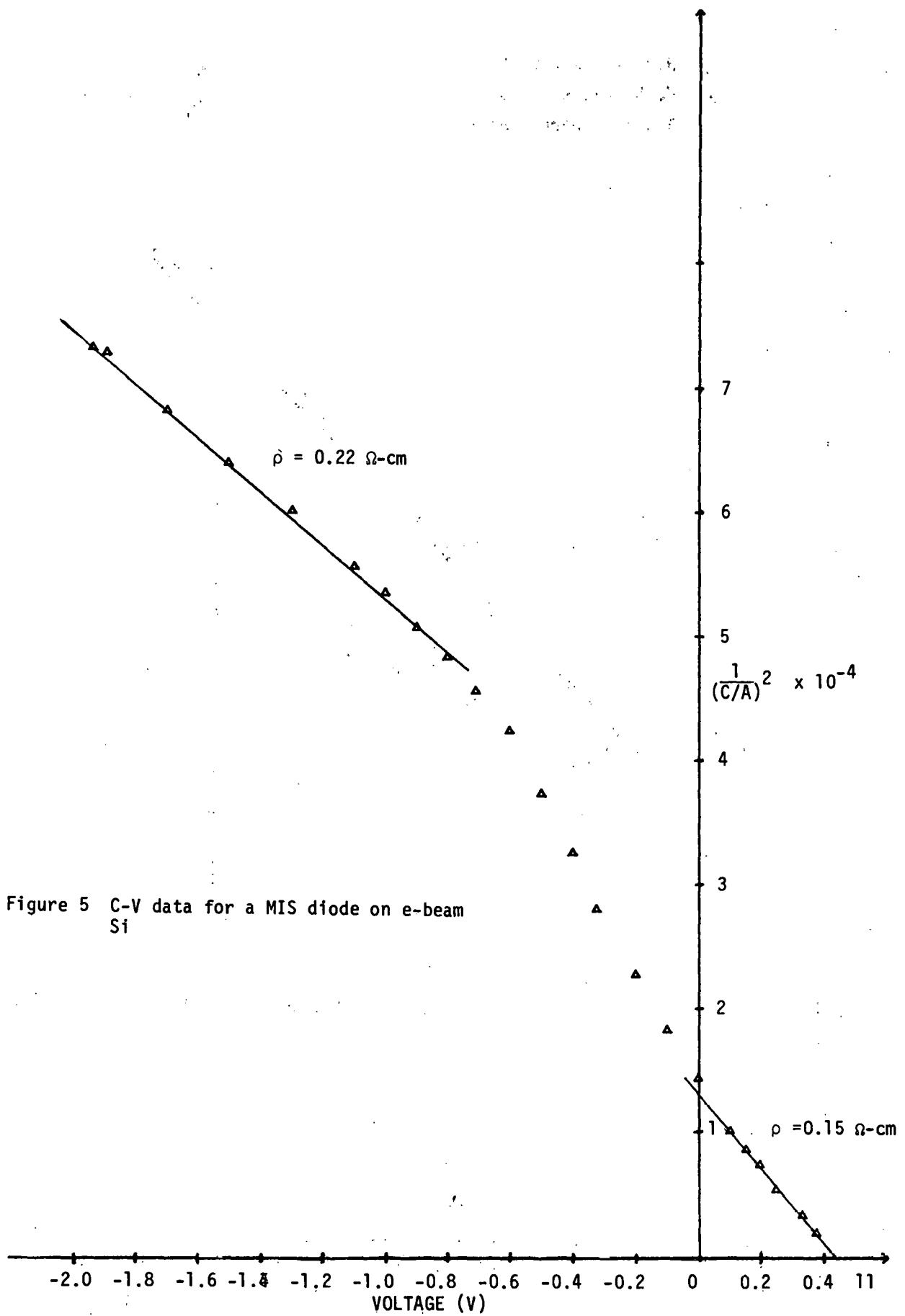

| 5             | C-V data for a MIS diode on e-beam Si . . . . .                                                                            | 11          |

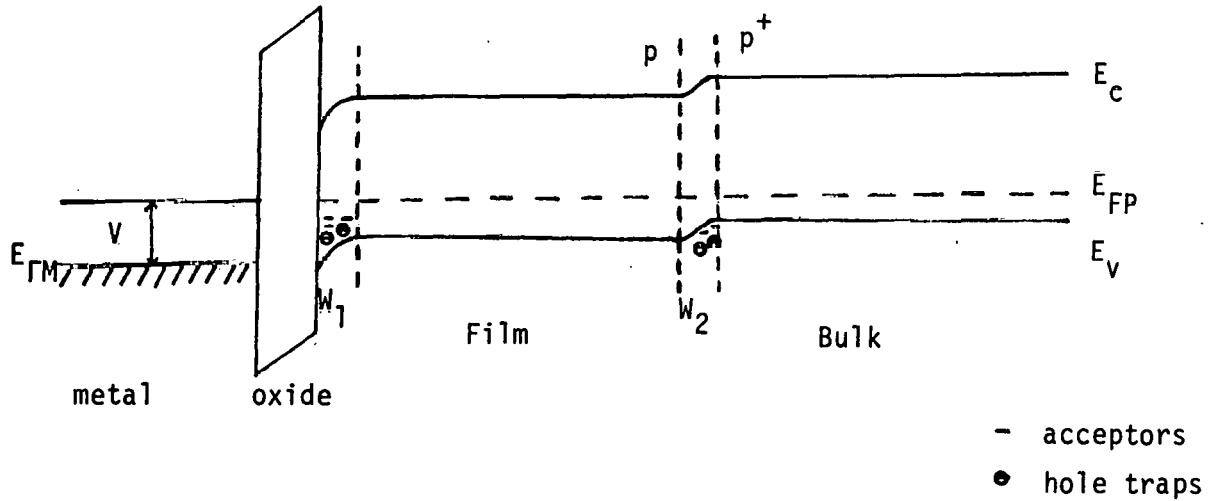

| 6             | Band diagram which may explain C-V data for a MIS device using an e-beam Si on Si substrate. . . . .                       | 12          |

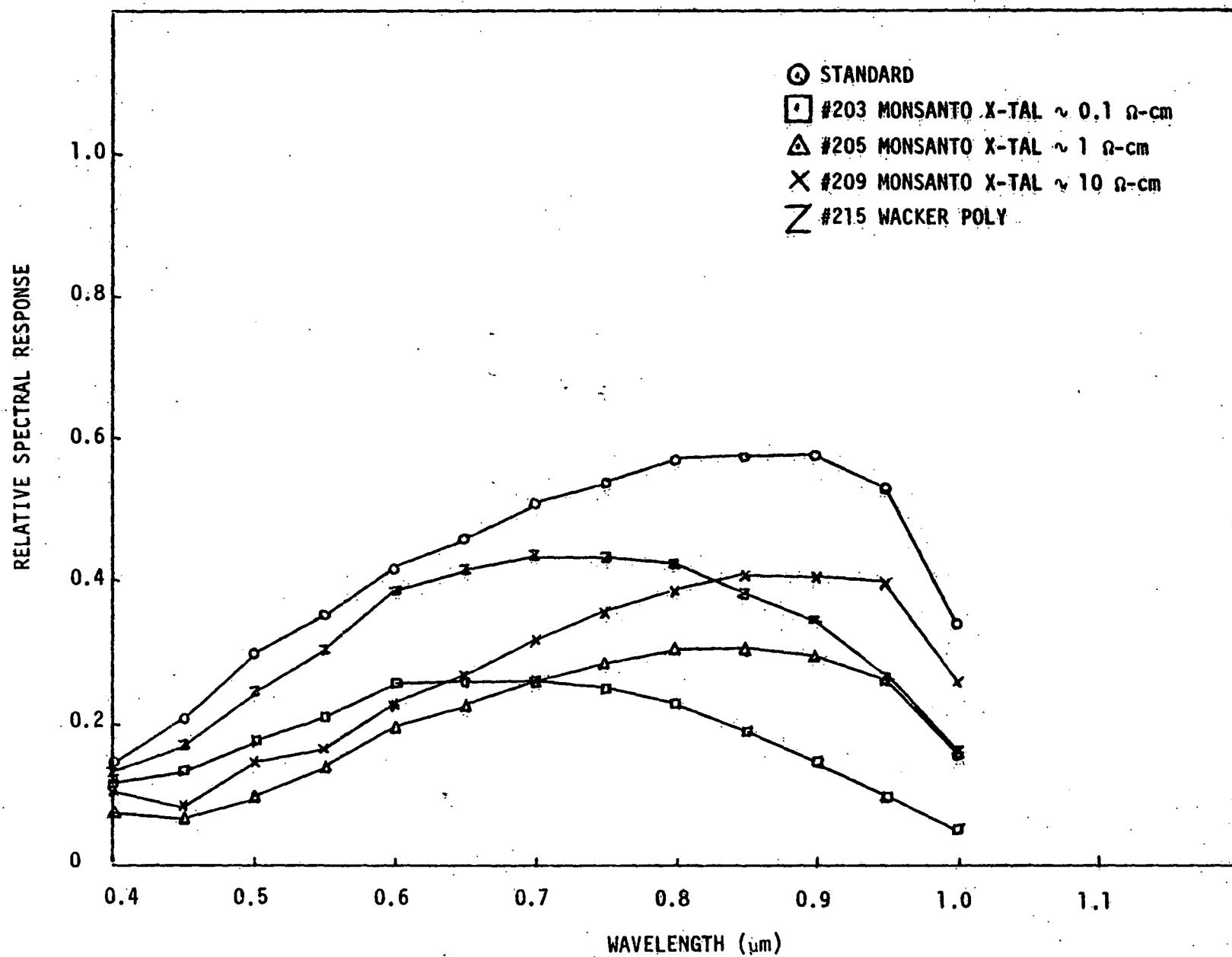

| 7             | Spectral response of Cr-MIS cells as a function of substrate resistivity. . . . .                                          | 19          |

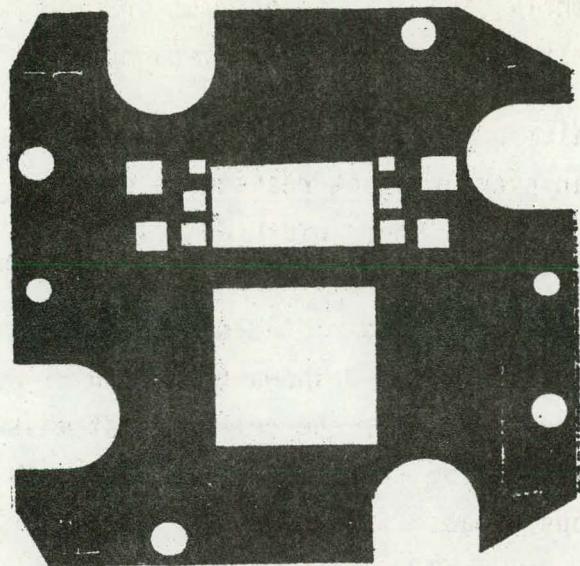

| 8             | New mask design for Cr-MIS cells. . . . .                                                                                  | 21          |

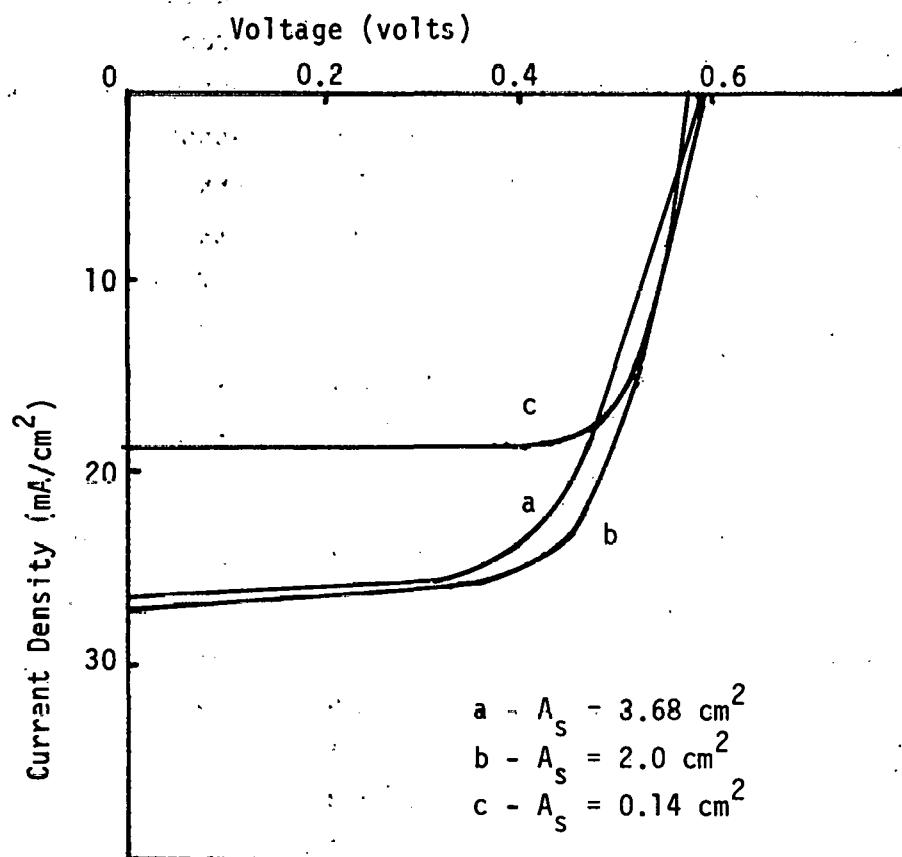

| 9             | Photovoltaic I-V data comparing $4 \text{ cm}^2$ , $2 \text{ cm}^2$ and small area cells. . . . .                          | 24          |

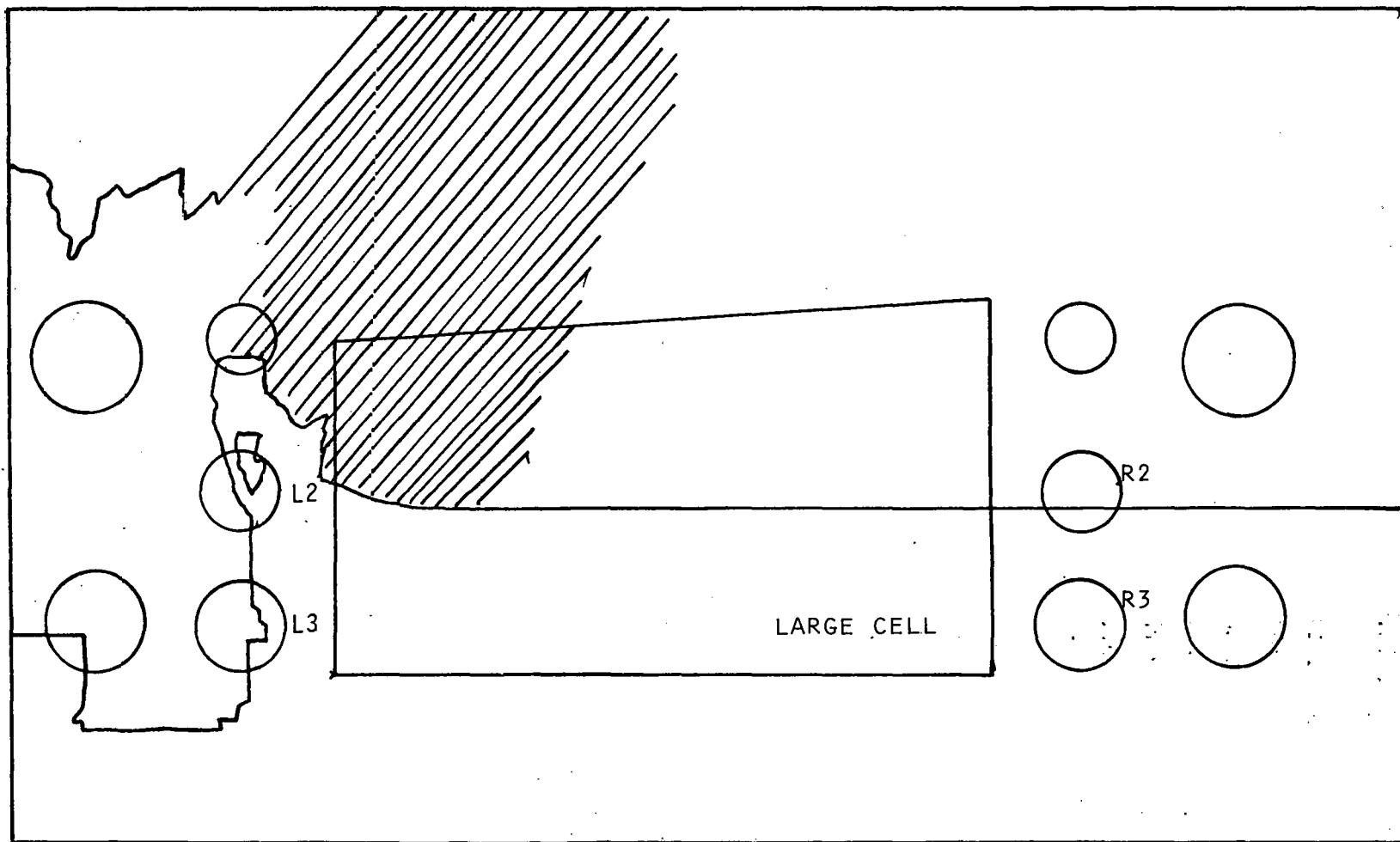

| 10            | Sample configuration for grain boundary studies . . . . .                                                                  | 27          |

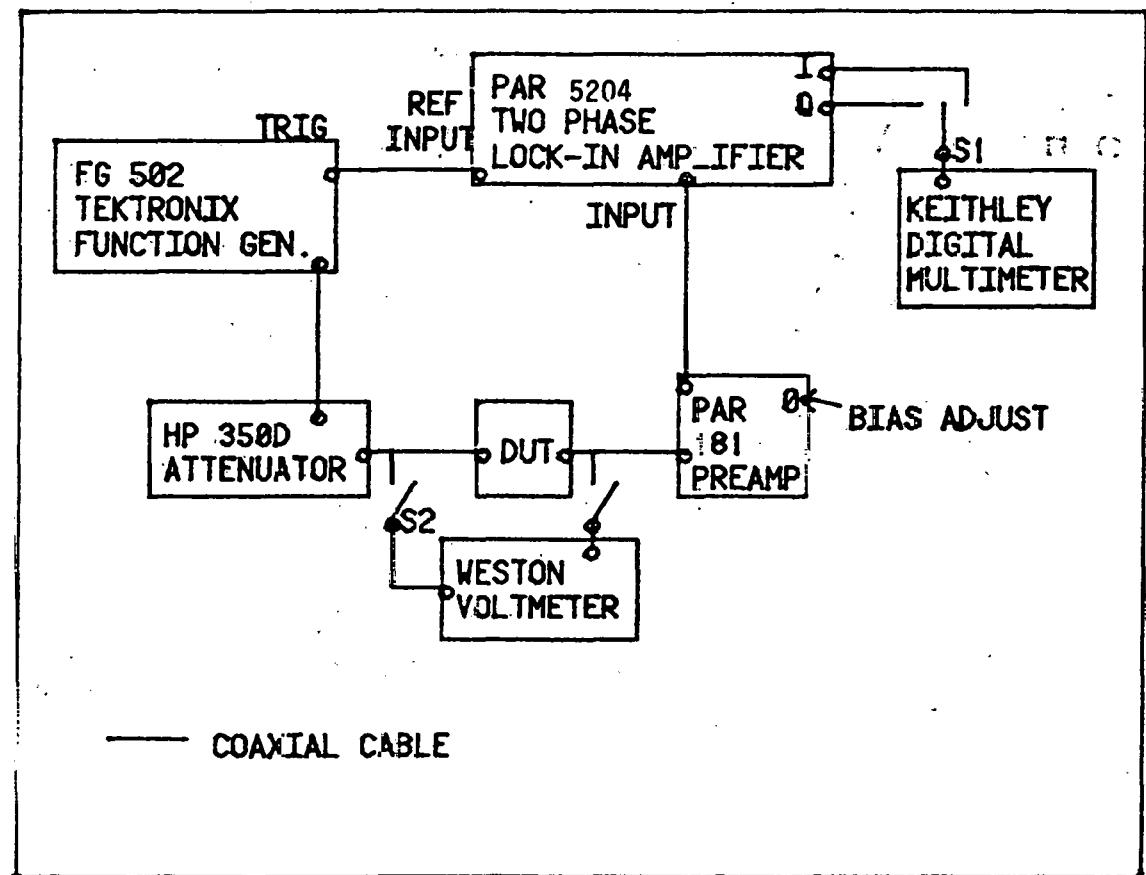

| 11            | Lock-in-amplifier circuit for C-V-f and G-V-f studies . . . . .                                                            | 28          |

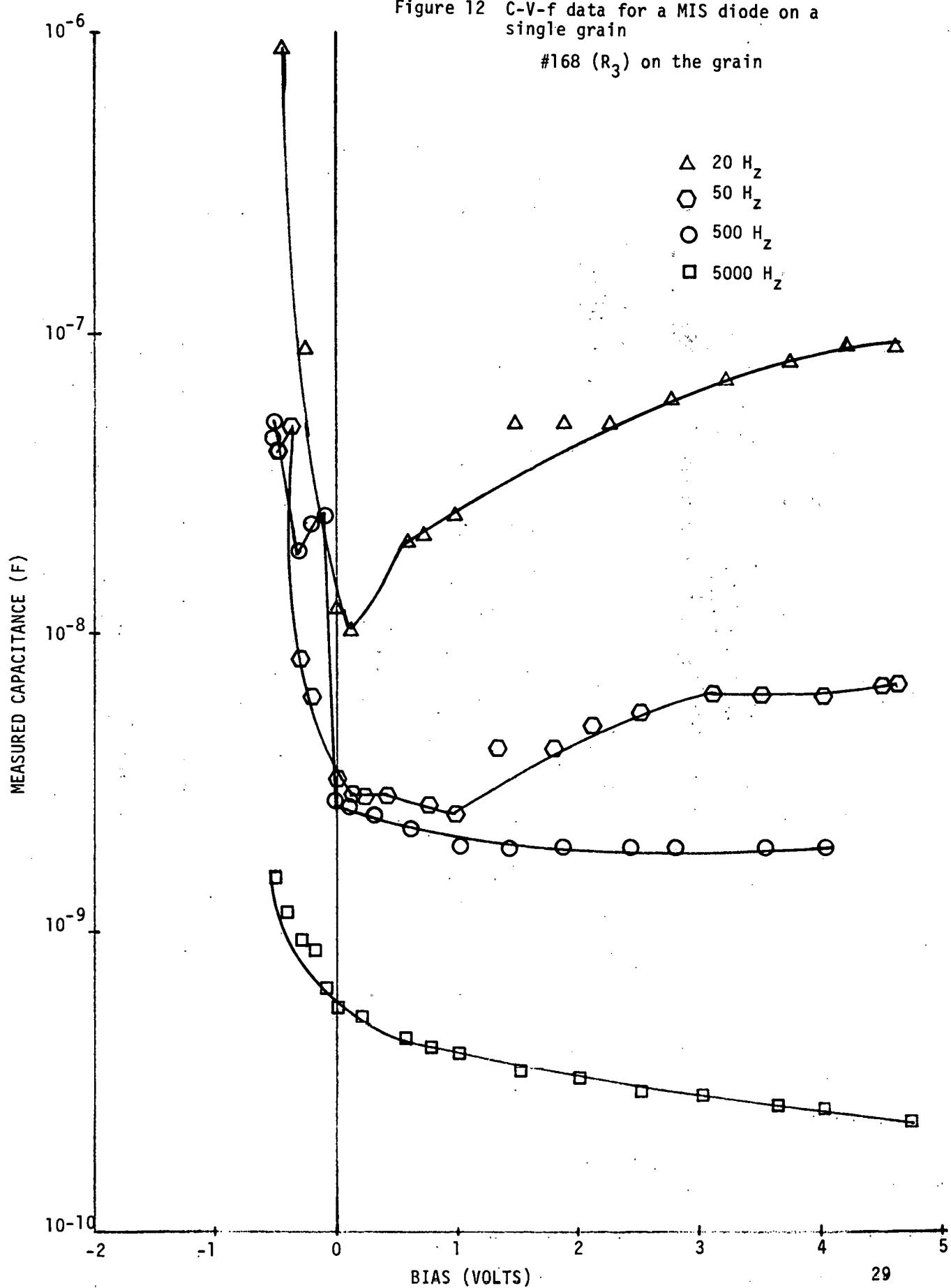

| 12            | C-V-f data for a MIS diode on a single grain. . . . .                                                                      | 29          |

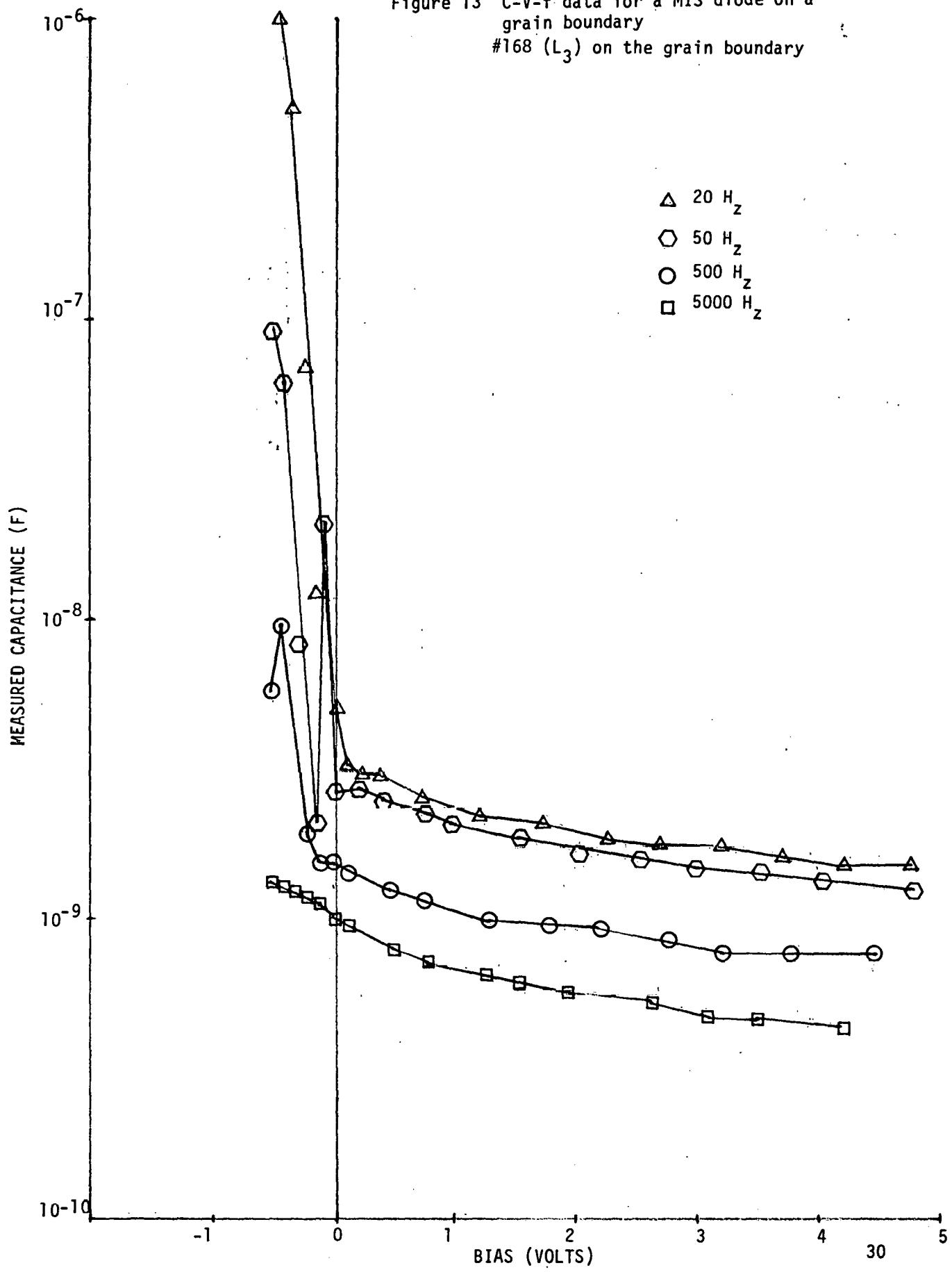

| 13            | C-V-f data for a MIS diode on a grain boundary. . . . .                                                                    | 30          |

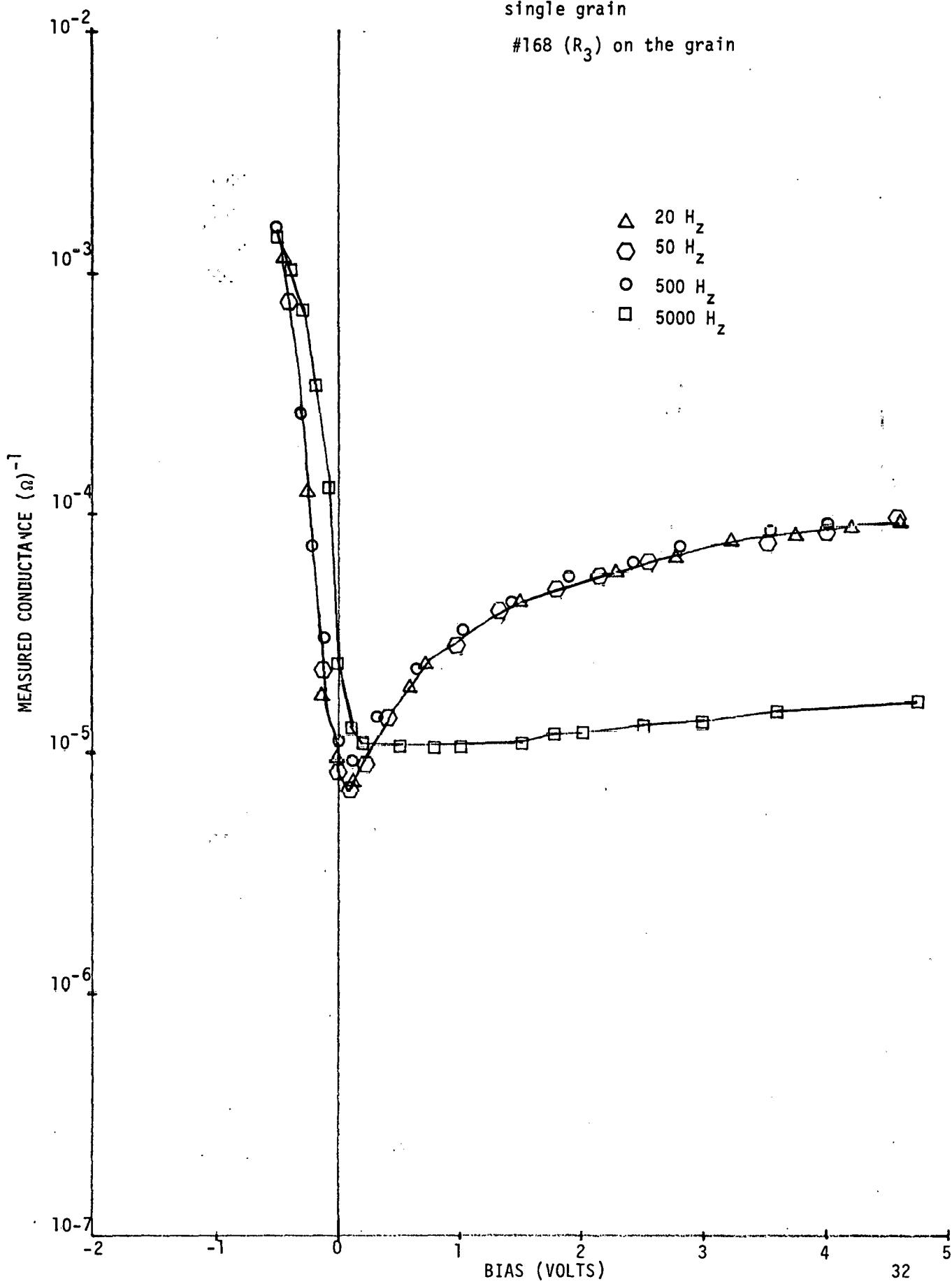

| 14            | G-V-f data for a MIS diode on a single grain. . . . .                                                                      | 32          |

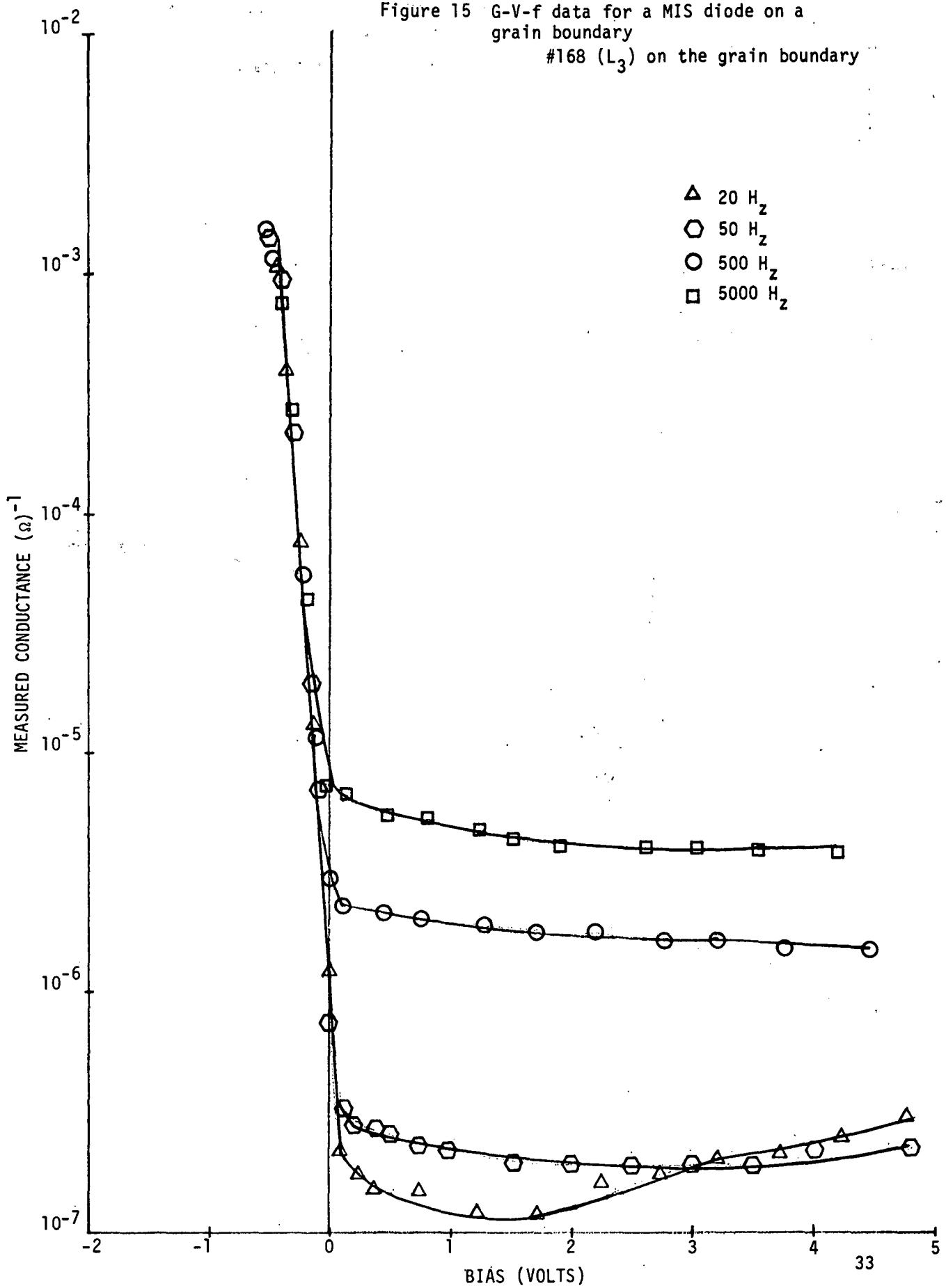

| 15            | G-V-f data for a MIS diode on a grain boundary. . . . .                                                                    | 33          |

## LIST OF TABLES

| <u>Table</u> |                                                                           | <u>Page</u> |

|--------------|---------------------------------------------------------------------------|-------------|

| 1            | SIMS ANALYSIS OF E-BEAM SILICON PRIOR TO RE-DESIGN OF THE SYSTEM. . . . . | 3           |

| 2            | SUMMARY OF E-BEAM DEPOSITIONS . . . . .                                   | 8           |

| 3            | SUMMARY OF SOLAR CELL PHOTOVOLTAIC DATA . . . . .                         | 17          |

| 4            | DIFFUSION LENGTH DATA . . . . .                                           | 18          |

| 5            | NEW MASK DATA . . . . .                                                   | 22          |

| 6            | PHOTOVOLTAIC DATA ON LARGE-TO-SMALL AREA CELLS (NEW GRID) .               | 23          |

| 7            | SOLAR CELL RELIABILITY DATA . . . . .                                     | 35          |

## 1. SUMMARY

Thin (10-30  $\mu\text{m}$ ) Si films are deposited on Si substrates by electron beam deposition. The substrates are held at 500-600° C during deposition in a vacuum of about  $5 \times 10^{-5}$  Torr and a rate of about 1  $\mu\text{m}/\text{min}$ . Depositions on (100), (111) and Wacker poly-Si show the film to replicate the substrate when it comes to surface features and X-ray diffraction data. The new Ti pump chamber gives a factor of 10 improvement in vacuum. A new crucible design was introduced to eliminate certain impurities from the Si film. The results of this step are yet to be seen.

Electrical characterization of the e-beam Si films is being done by spreading resistance measurement and evaluation of MIS diodes.  $\ln(I)-V$  data give a linear plot but a high n-factor.  $\frac{1}{C^2}V$  data give two straight line sections which must be evaluated. Photovoltaic response shows  $J_{\text{scmax}} = 1.5 \frac{\text{mA}}{\text{cm}^2}$  and  $V_{\text{ocmax}} = 125 \text{ mV}$ . This low photovoltaic response may be caused by 1) impurities, 2) a dead layer between substrate and film, or 3) high defect density in the film. These possibilities are being investigated. We are also evaluating all previous work on grain boundary models to aid in deriving a model which fits our experimental data.

MIS cell fabrication has involved the use of a new mask which gives 4  $\text{cm}^2$  cells with 7% grid shading. Cells have been made on Wacker poly-Si and Monsanto Xtal-Si, both of which were polished in our laboratory. An effort is being made to improve etching and polishing techniques.

MIS analysis centers on I-V-T, G-V-f and C-V-f studies of grain boundaries. G-V-T data do not give consistent trends for evaluating grain boundaries. C-V-f and G-V-f show some significant grain boundary effects in a frequency range from 5 Hz - 50 Hz. This indicates that grain boundary interface states predominate from d.c. to about 100 Hz. A quantitative evaluation will be given in the next report.

Reliability studies continue on Cr-MIS cells under shelf-life, light bias and out-of-doors conditions. Good stability is shown for the first two situations. A rapid degradation in the grid contact is shown in the out-of-doors study. A new grid design is being evaluated to remedy the situation. An evaluation of the quality of the D.I.  $\text{H}_2\text{O}$  used in wafer cleaning is being conducted to 1) improve on  $V_{\text{oc}}$  and 2) to eliminate the trend towards reduced  $V_{\text{oc}}$  with time.

## 2. INTRODUCTION

This project is undertaken to develop a low-cost, thin-film, MIS solar cell which will eventually sell for < 50¢/watt. This MIS process is being optimized for single crystal silicon and poly-Si prior to application to thin-film Si. This involves fabrication, grain boundary effects, and reliability studies. Thin Si films are e-beam deposited on Si, stainless steel, Ti, and glass substrates to evaluate the potential for future use as a low-cost semiconductor. It is our intent to combine the optimized MIS process with the thin e-beam Si film to produce a low-cost vacuum process to fabricate solar cells.

Our studies during this reporting period involve most of these areas of interest. The e-beam Si deposition work has concentrated on the use of different Si substrates, SEM analysis, X-ray diffraction, and some electrical characterization. Some samples have been sent out for SIMS analysis and an evaluation of defect density as well as crystallinity. An evaluation of all previous studies on grain boundary mechanisms is being made to aid in comparing theoretical and experimental data concerning conduction mechanisms. A new grid design is now in use which gives about 7% shading. We now can make cells with several areas including  $2\text{ cm}^2$  and  $4\text{ cm}^2$  on a single wafer. I-V-T analysis have been conducted to evaluate grain boundary conduction mechanisms. C-V-f and G-V-f data are also used to evaluate grain boundary effects. Reliability studies continue with the main emphasis on preparing new cells for study.

### 3. THIN FILM SILICON DEPOSITION AND ANALYSIS

#### 3-1. Thin Film Silicon Deposition and Surface Analysis (M. Jackson)

Electron beam deposition of silicon onto a variety of substrates continued this quarter. The work on stainless steel substrates, reported in the last quarter, has been suspended in favor of using low resistivity, crystalline silicon substrates. The strategy is to optimize the deposition parameters so that a crystalline silicon film is obtained on these substrates. Once this goal is achieved, less expensive substrates such as metallurgical grade silicon or metals may be utilized. Ultimately, a highly crystalline silicon film or an inexpensive substrate is desired for use in low cost solar cells.

A SIMS analysis was performed on a silicon film on silicon substrate sample. The results are listed in Table 1. Carbon and copper were the major impurities with concentrations in excess of one part per hundred. These results led to the following changes in the e-beam deposition unit.

Table 1

SIMS ANALYSIS OF E-BEAM

SILICON PRIOR TO RE-DESIGN OF THE SYSTEM

| <u>Element</u> | <u>SIMS Data</u>                 | <u>Impurity (ppm)</u> |

|----------------|----------------------------------|-----------------------|

| B              | $1.1 \times 10^{17}/\text{cm}^3$ | 2.2                   |

| C              | $5.3 \times 10^{20}$             | 10,600                |

| F1             | <                                | -                     |

| Na             | $5.2 \times 10^{17}$             | 10.4                  |

| Mg             | $2.2 \times 10^{17}$             | 4.4                   |

| Al             | $2.3 \times 10^{17}$             | 4.6                   |

| C1             | <                                | -                     |

| K              | $10^{16}$                        | 0.2                   |

| Ti             | $2.4 \times 10^{15}$             | 0.05                  |

| Cr             | $2.1 \times 10^{17}$             | 4.2                   |

| Fe             | $3.4 \times 10^{17}$             | 6.8                   |

| Ni             | $3.9 \times 10^{17}$             | 7.8                   |

| Y              | $2 \times 10^{15}$               | 0.04                  |

| Zr             | $1.9 \times 10^{17}$             | 3.8                   |

| Cu             | $5.1 \times 10^{20}$             | 10,200                |

A new copper crucible was designed with an inch and a quarter diameter. The old crucible had a diameter of seven-eights of an inch. It is felt that the e-beam had contacted the sides of the old crucible and this led to copper contamination of the silicon source. Backstreaming of oil vapor from the mechanical pump was considered to be the source of the carbon. A coaxial trap was placed in the foreline to eliminate any oil vapors. In an effort to remove the other impurities, the screws used to hold the substrates to the substrate heater were replaced with #304 stainless steel screws. Two quartz heater lamps, used for baking out the chamber, were removed. An exterior heating system is being considered.

A titanium sublimation pump was added to the system. A drop in the base pressure of the system from  $5 \times 10^{-6}$  Torr to  $8 \times 10^{-7}$  Torr was observed. Deposition now takes place at a pressure of  $5 \times 10^{-6}$  Torr as opposed to  $1 \times 10^{-5}$  Torr prior to adding the Ti-sublimation pump. Next quarters report should contain a SIMS analysis of a sample made after the above changes were implemented.

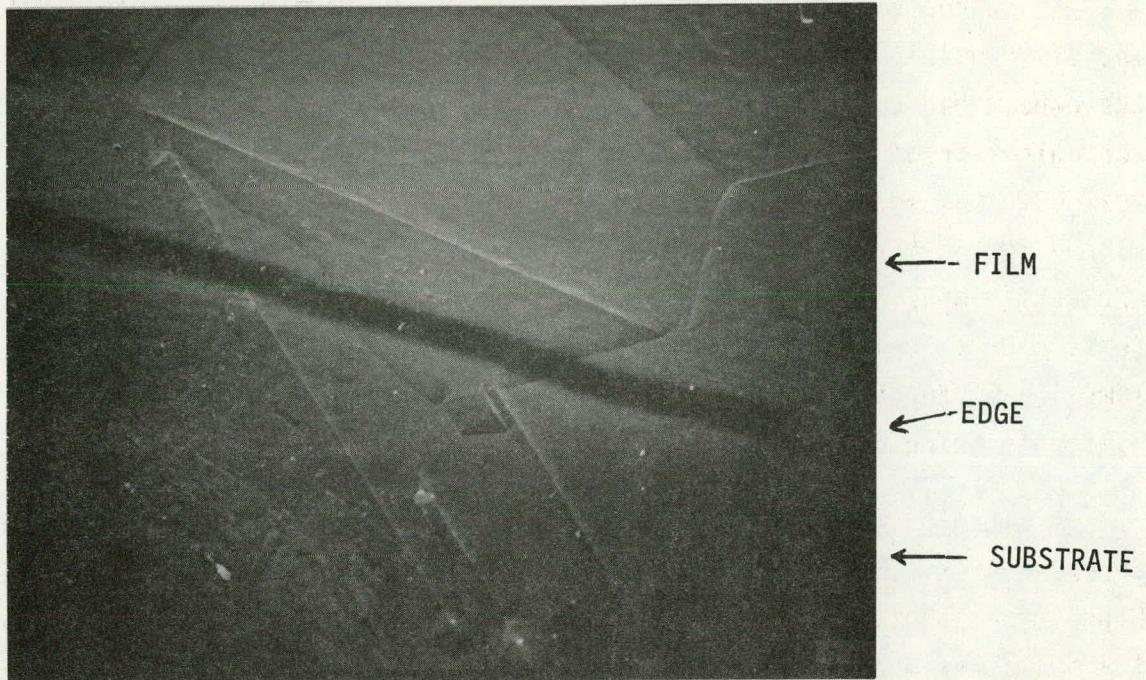

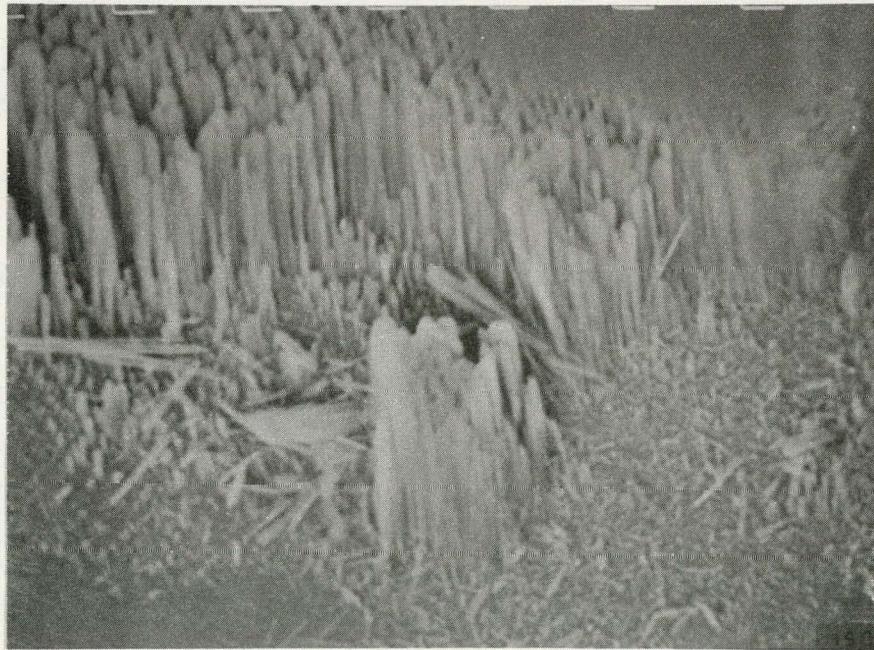

This quarter's runs are summarized in Table 2. The majority of the samples prepared were silicon films on (111) silicon substrates. The substrates were unpolished or polished. The surface features and crystallinity of these films were discussed in last quaters's report. Suffice it to say, that the films duplicated the surface structure of the substrate and oriented themselves in the (111) direction. Repeated success using the (111) substrates led to the use of polished (100) single crystal and Wacker polycrystalline silicon substrates. Figure 1 shows SEM micrographs of the films obtained on (100) silicon and the Wacker poly. Once again, the replication of the substrate surface is obvious. Figures 2 and 3 show X-ray analysis of the two films. Again the film structure contains crystals having the same preferred orientation as the substrate. No grain boundaries are evident under the SEM, but more work needs to be done to determine the actual size of the film's crystallites. One should be aware that the X-ray analysis for the Wacker poly silicon film is highly position dependent. The peaks on the X-ray analysis will change (grow or shrink) in response to position changes of the sample in the X-ray beam.

In conclusion, the e-beam deposited thin films take on the surface features of the underlying substrate. The crystal orientation of the film appears to be the same as that of the underlying substrate. The size of the crystallites in the film has yet to be determined, but the SEM micrographs do not show any

Figure 1A SEM micrograph (100X) showing an e-beam Si film on a Wacker Si substrate. Replication of the substrate is obvious

Figure 1B SEM micrograph (1500X) showing whisker-like columnar growth at the edge of a Si substrate

Figure 2 X-ray data for an e-beam Si film

on a (100) Si substrate

Figure 3 X-ray data for an e-beam Si film

on a Wacker Si substrate

E-beam film on

polished Wacker

polycrystalline Silicon

cracks or grain boundaries. Next quarters work should shed some light on this question.

Table 2

SUMMARY OF E-BEAM DEPOSITIONS

| <u>Date</u> | <u>Vacuum<br/>(Torr)</u> | <u>Substrate<br/>Temperature<br/>(° C)</u> | <u>Film<br/>Thickness<br/>(<math>\mu</math>m)</u> | <u>Average*<br/>Deposition Rate<br/>(<math>\mu</math>m/min)</u> |

|-------------|--------------------------|--------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|

| 9/30/80     | $8 \times 10^{-6}$       | 545                                        | 7                                                 | 0.25                                                            |

| 10/10/80    | $8 \times 10^{-6}$       | 550                                        | 12                                                | 0.55                                                            |

| 11/6/80     | $7 \times 10^{-6}$       | 550                                        | 17                                                | 0.85                                                            |

| 11/13/80    | $5 \times 10^{-6}$       | 525                                        | 7                                                 | 0.47                                                            |

| 11/25/80    | $5 \times 10^{-6}$       | 500                                        | 25                                                | 1.25                                                            |

\* Average Rate is film thickness divided by total deposition time. Initial deposition rates are usually very low, hence rates above 1  $\mu$ m/min have been regularly observed.

### 3-2 Thin Film Silicon Electrical Studies (F. Kai)

Electron-beam deposited polycrystalline silicon MIS diodes have been tested by "Current-Voltage" (I-V) and "Capacitance-Voltage" (C-V) measurements. The I-V measurements are studied to determine the "barrier height"  $\phi_B$ , and the ideality factor, "n" value. From an I-V test we can also study the "series resistance" and "shunt resistance" effects. In this study three classes of I-V curves have been plotted: (1) under dark forward bias, (2) under light forward bias, (3) under dark reverse bias. For the single crystal-silicon Schottky-barrier or thin-oxide MIS diodes, a plot of  $C^{-2}$  versus V can determine the doping,  $N_A$ , of the device. If  $N_A$  is constant throughout the depletion region, the curve should be a straight line. A study of the doping profile in thin film silicon and substrate is made possible by the "C<sup>-2</sup> versus V" plot.

The I-V characteristic of the electron-beam deposited thin-film silicon on p-type silicon is plotted in Figure 4. The ideality factor is 4.24. The barrier height is calculated from the plot to be 0.683 eV. The dark log J-V characteristics do not show serious series resistance effects. The light J-V characteristics also do not show series resistance effects. The dark current at zero-bias is extrapolated to be  $10^{-2}$  mA/cm<sup>2</sup> which is a very high value. The dark reverse-biased plot shows a large reverse current. This may be due to a high trap density distribution.

The C-V plot for this sample is shown in Figure 5. There are three regions shown in the curve:

- (i) small forward-biased region

- (ii) small reverse-biased region

- (iii) large reverse-biased region.

The results indicate that there are different doping (impurity and trap) concentrations throughout the sample. It has previously been pointed out herein from X-ray analysis, that the thin film silicon deposited by e-beam grows in the same orientation as the silicon substrate. The doping concentrations in the film and the substrate are different. The substrate-film interface may result in a layer of deep traps.

The curve shape for the forward bias applied in (i) is close to the approximation of a Schottky barrier with uniform negative charge density equal to the acceptor density  $N_A$ . The small reverse bias applied in (ii)

shows a steeper slope. The actual mechanism of this region is not clear now. It may represent a "transition region."

The large negative bias is applied in (iii) with a smaller slope in the absolute value sense. The space-charge region contains both the acceptors and the empty hole traps which are enhanced by the large reverse bias. The film-substrate interface forms a p-p<sup>+</sup> junction. The total capacitance C measured is composed by three capacitance:

$$\frac{1}{C} = \frac{1}{C_i} + \frac{1}{C_{sc1}} + \frac{1}{C_{sc2}}$$

where

$C_i$  = insulator layer capacitance

$C_{sc1}$  = space-charge capacitance due to oxide-film interface

$C_{sc2}$  = space-charge capacitance due to film-substrate interface.

The energy band diagram is shown below in Figure 6.

Figure 6 Band diagram which may explain C-V data for a MIS device using an e-beam Si on Si substrate

The I-V and C-V measurements of the e-beam deposited polycrystalline thin-film diode can be used as a tool to analyze the doping and trap density distributions throughout the sample and the current-conduction mechanisms as well. The I-V plot obeys an exponential law. This can be studied further to understand the "space-charge limited current" contribution to the device. From C-V measurement, the effect of "deep traps" and the film-substrate interface trap densities can be analysed. In the next report, more experimental work and theory will be developed. Appendix A contains a condensed analysis of some previous work on grain boundary effects in poly-silicon. The next report will finish this survey and outline new directions for a model which fits our experimental data on small grain poly-silicon.

#### 4. Cr-MIS SOLAR CELL FABRICATION

##### 4-1 Device Processing Techniques (G. Rajeswaran)

The Cr-MIS solar cell is considered to be a structural design that would ultimately produce a > 10% efficient device on thin film polycrystalline silicon. We have previously reported<sup>[1]</sup> a revised processing scheme to increase efficiency and reproducibility in Cr-MIS cells. Such a processing technique was shown to be applicable to various types of potentially low cost silicon substrates.<sup>[2]</sup> In this report, we discuss these device processing techniques and the modifications that were introduced to make reproducible cells.

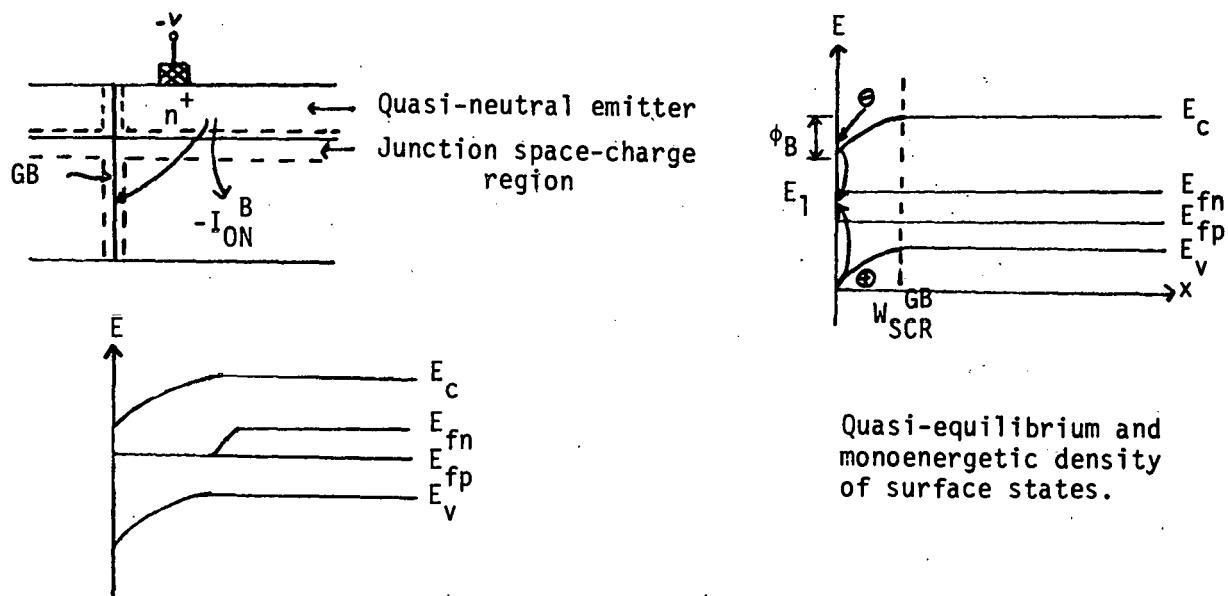

The Cr-MIS cell is normally fabricated using the structure 710 Å SiO<sub>x</sub> A/R coating/Al grid/60 Å Cu conductive layer/30 Å Cr/20 Å SiO<sub>x</sub>/p-type silicon/Al ohmic contact. The top metallic layers and the A/R coating are deposited in a one pump-down process after the silicon surface is cleaned and oxidized. It is imperative that the silicon surface be extremely clean before oxidation. All our processing variations were introduced at this stage of fabrication.

###### a) Planar Etch (P.E.)

MIS devices are surface oriented devices. The nature and quality of these surfaces play an important role in shaping the characteristics of these devices. The rougher the surface, the higher is the density of surface states and poorer the quality of the device. A planar etch that would react with all crystal orientations at the same rate is necessary to conform with a single processing technique that deals with all types of silicon substrates. A mixture of 75% HNO<sub>3</sub>, 17% CH<sub>3</sub>COOH and 8% HF serves this purpose.<sup>[3]</sup> A treatment of this planar etch on any type of silicon substrate for approximately one hour produces an uniform, polished surface.<sup>[2]</sup> The volume ratio of the constituents acutely governs the accuracy of the planar etch. A very small variation from a 75:17:8 ratio results in a preferential rate of etch on different crystal orientations, causing etch pits. As an initial step in the fabrication sequence, all unpolished silicon substrates were treated with the planar etch solution for an hour. This step was omitted on mechanically polished silicon wafers obtained from the manufacturer. Agitation of the planar etch solution produced uneven

surfaces, whereas, a free standing planar etch solution resulted in a high degree of polish on one side of the wafer and striations on the other.

The metal-insulator-semiconductor (MIS) junctions were formed on the smooth, glossy side of the silicon wafers and the aluminum (Al) back contacts made on the striated, coarser side.

b) One Cleaning, One Oxide Process (00)

In the 00 process, the silicon wafers are degreased and treated with deionized (DI) water. The thin native oxide is stripped by immersion in hydrofluoric acid (HF), washed in DI water, blown dry in a stream of dry Nitrogen ( $N_2$ ) and immediately placed in a vacuum system and pumped down. The back aluminum contact is then evaporated on the coarser side of the wafers. A near-perfect ohmic contact is made by sintering the samples in a muffle furnace at  $600^\circ C$  in air. This produces a thin oxide ( $\sim 20-25 \text{ \AA}$ ) on the front surface at the same time. On cooling, the samples are re-mounted in the vacuum system and the top metallic layers and the anti-reflection coating are evaporated consecutively in a one pump-down process at a pressure of  $1 \times 10^{-5}$  Torr.

This process was frequently used in our earlier investigations. The results were never consistent and the photovoltaic data scattered. The contamination of the front surface, when removed from high vacuum, for the purpose of back contact sintering, was a prime suspect for this random device behaviour. The one cleaning, one oxide process was abandoned and a double cleaning, double oxide process was introduced.

c) Double Cleaning, Double Oxide Process (DD)

The back contact is sintered at  $600^\circ C$  and a thin oxide grown on the front surface simultaneously using the one cleaning, one oxide process. To counter the contention that the front surface is contaminated prior to ohmic contact formation, this surface has to be cleaned again in HF without destroying the aluminum on the back. By spreading a layer of photoresist on the Al and by curing it, the back contact can be protected from further cleaning steps. The front surface is then cleaned in a DI, HF, DI cycle without exposure to air. Next, the photoresist is removed with acetone, and the wafer washed thoroughly in a DI water stream, blown dry

in dry nitrogen and the thin oxide regrown in the muffle furnace at 580° C. In cooling, the wafer is remounted in a vacuum system, pumped down and the top layers evaporated.

The DD process of fabrication resulted in consistent photovoltaic data on similar substrates and even an increased efficiency.<sup>[1]</sup>

d) Double Cleaning, One Oxide Process (DO)

The back aluminum contact is sintered twice in the DD process. The double cleaning, one oxide process eliminates the first sintering while otherwise maintaining the same fabrication sequence as the DD process.

The advantage of the DO process over the other two is that the elegance of the DD process is preserved while eliminating a fabrication step at the same time.

4-2 Summary of Photovoltaic Data (G. Rajeswaran)

A summary of solar cell photovoltaic data from a study conducted on substrates of varying resistivities is given in Table 3. For comparison, the data from a Wacker-Chemitronic polycrystalline silicon solar cell is also shown.

The lower the resistivity of the substrate, the lower the lifetime of the minority carriers and hence a smaller short circuit current ( $J_{sc}$ ) results. The series resistance ( $R_s$ ) is lower on the other hand and contributes to a higher fill factor. With increasing resistivity,  $J_{sc}$  increases and the fill factor drops. The anomalous case of smaller  $J_{sc}$  on the cell made on 8-15  $\Omega\text{-cm}$  substrate is due to a bad anti-reflection coating and a diffused grid pattern which reduces the active area of solar insulation. We have seen in our previous investigations that a resistivity of between 1  $\Omega\text{-cm}$  and 5  $\Omega\text{-cm}$  results in an optimum efficiency solar cell. The substrates of the class (1-4  $\Omega\text{-cm}$ ) consistently exhibited higher efficiencies than the other resistivities. Nevertheless, it was observed that these so called higher efficiencies are always  $\leq 10\%$ , which led us to the conclusion that the quality of the silicon substrates was questionable.

Spectral response studies on the cells of Table 3 and on some other cells are shown in Table 4. At long wavelengths, the ratio of spectral responses approximately correspond to ratios of diffusion lengths.<sup>[2,4]</sup>

Table 3

SUMMARY OF SOLAR CELL PHOTOVOLTAIC DATA

| SUBSTRATE      | RESISTIVITY<br>Ω-cm | V <sub>OC</sub><br>V | J <sub>SC</sub><br>mA/cm <sup>2</sup><br>** | FF   | EFFICIENCY η%  |               | PROCESSING                 |

|----------------|---------------------|----------------------|---------------------------------------------|------|----------------|---------------|----------------------------|

|                |                     |                      |                                             |      | ACTIVE<br>AREA | TOTAL<br>AREA |                            |

| MONSANTO <100> | 0.05-0.15           | 0.58                 | 17.0                                        | 0.75 | 7.4            | 6.1           | P.E., DD Process (600° C)* |

| MONSANTO <100> | 1-4                 | 0.57                 | 23.0                                        | 0.71 | 9.2            | 7.7           | P.E., DD Process (600° C)* |

| MONSANTO <100> | 8-15                | 0.53                 | 19.0                                        | 0.67 | 6.8            | 5.6           | P.E., DD Process (600° C)* |

| WACKER POLY    | 1-10                | 0.53                 | 21.0                                        | 0.72 | 8.0            | 6.6           | P.E., DD Process (600° C)* |

| WACKER POLY    | 1-10                | 0.52                 | 25.5                                        | 0.63 | 8.2            | 6.9           | P.E., DD Process (590° C)* |

\* Temperature at which oxide is grown

\*\* Based on NASA-Lewis calibration and using ELH lamp @ 100 mW/cm<sup>2</sup>

$$\text{Active area} = 2.0 \text{ cm}^2$$

$$\text{Total area} = 2.42 \text{ cm}^2$$

Table 4

DIFFUSION LENGTH DATA

| Substrate      | Resistivity<br>Ω-cm | Relative<br>Response at<br>1.0 μm | Diffusion<br>Length<br>(μm) |

|----------------|---------------------|-----------------------------------|-----------------------------|

| STANDARD p-n   | -                   | 0.3382                            | 184                         |

| MONSANTO <100> | 0.05-0.15           | 0.0471                            | 26                          |

| MONSANTO <100> | 1-4                 | 0.1568                            | 85                          |

| MONSANTO <100> | 8-15                | 0.2567                            | 140                         |

| MONSANTO <100> | > 5                 | 0.2164                            | 118                         |

| WACKER POLY    | 1-10                | 0.1582                            | 86                          |

Using this fact, and a calibrated silicon solar cell, it is found that the diffusion length of single crystal silicon of optimum resistivities (1-4 Ω-cm) is 85 μm. This is of the same order as Wacker polycrystalline silicon. This is indicative of the bad quality of Xtal silicon used in our recent fabrication studies. Figure 7 shows the spectral response curves as a function of substrate resistivities. As anticipated, the diffusion length of minority carriers increases from low to high resistivity substrates.

Series resistance is an important parameter in solar cell design and fabrication. It is a power dissipating factor<sup>[5]</sup> and the maximum achievable output power of a solar cell is decreased. This effect can be seen in the "softening" of its current-voltage characteristic in the fourth quadrant. The series resistance in a Cr-MIS solar cell arises from the contribution of the top metal layers and the grid ( $R_G$ ) and also the semiconductor base resistance ( $R_B$ ).  $R_G$ , the contribution of the metallic layers and the grid metal, can be minimized by an optimum grid design. Smaller finger widths and increasing distances of separation between them will reduce the grid shading loss but the minority carriers will have to flow a longer distance

Figure 7 Spectral response of Cr-MIS cells as a function of substrate resistivity

61

to the current collecting fingers. Evidently, there is an optimum spacing for a maximum short circuit current and minimum front layer resistance.

A vacuum deposited 3000 Å layer of aluminum has a sheet resistance of  $1.56 \Omega/\text{cm}^2$ . 30 Å Cr/60 Å Cu layers have an average sheet resistance of  $50 \Omega/\text{cm}^2$ . A new grid was designed<sup>[6]</sup> with a grid finger width of 0.1 mm and the spacing between the fingers being 1.67 mm. There were two large area cells, the largest being  $4 \text{ cm}^2$ , and many small test diodes and cells with different solar (active) and dark areas. Figure 8 shows the Cr/Cu metal mask (actual size) with different area openings, the grid-contact mask for different areas and the antireflection coating mask. Table 5 summarizes the data on the diodes and cells of various areas.

The grid mask was fabricated on a thin molybdenum sheet by a photolithographic process following by chemical etching. Care was taken in the design to account for undercut and side etching at grid fingers. The Cr/Cu mask and the A/R mask were made on thin brass (2 mils).

Table 6 summarizes the preliminary data on solar cells fabricated with the new mask. A higher  $J_{SC}$  on all devices comparable to those in Table 3 indicates a lower shadow loss. The fill factor is consistently smaller on  $4 \text{ cm}^2$  cells than on  $2 \text{ cm}^2$  cells. The equation governing the operation of a solar cell as given by ( $R_{sh} \rightarrow \infty$ )

$$J = J_L - J_0 \left[ \exp \left\{ \frac{q(V+I \cdot \frac{A_T}{A_s} \cdot R_s)}{nkT} \right\} - 1 \right] \quad 4-1$$

where

$$R_s, \text{ the series resistance} = R_G + R_B \quad 4-2$$

$R_G = 0.212 \Omega$  for a 24 line structure, as in  $4 \text{ cm}^2$  cell

$R_B = 0.497 \Omega$  for a 12 line structure, as in  $2 \text{ cm}^2$  cell

and

$R_G$  = resistance due to the grid and Cr/Cu layers

$$R_B = \text{semiconductor resistance} = \frac{\rho_B H}{A} \quad 4-3$$

and  $H$  = thickness of the wafer,  $A$  = the area of the cell and  $\rho_B$  = resistivity of silicon.

Figure 8a New Cu/Cr mask.

Figure 8b New grid mask.

Figure 8c New A/R mask.

Table 5

## NEW MASK DATA

| CELL<br>IDENTIFIER | AREA (cm <sup>2</sup> ) |                      | SHADING<br>$\frac{A_T - A_S}{A_T} \times 100$<br>(%) | NO. OF<br>FINGERS | GRID CONTRIBUTION<br>TO<br>SERIES<br>RESISTANCE<br>( $\Omega$ ) |

|--------------------|-------------------------|----------------------|------------------------------------------------------|-------------------|-----------------------------------------------------------------|

|                    | ACTIVE A <sub>S</sub>   | TOTAL A <sub>T</sub> |                                                      |                   |                                                                 |

| LARGEST            | 3.68                    | 4.0                  | 8.0                                                  | 24                | 0.212                                                           |

| LARGE              | 2.0                     | 2.12                 | 5.65                                                 | 12                | 0.49                                                            |

| R5, L5             | 0.1856                  | 0.2                  | 7.2                                                  | -                 | -                                                               |

| R4, L4             | 0.1356                  | 0.15                 | 9.6                                                  | -                 | -                                                               |

| R3, L3             | 0.0856                  | 0.1                  | 14.4                                                 | -                 | -                                                               |

| R2, L2             | 0.0656                  | 0.08                 | 18                                                   | -                 | -                                                               |

| R1, L1             | 0.0336                  | 0.04                 | 16                                                   | -                 | -                                                               |

Grid finger width = 0.1 mm

Spacing between fingers = 1.67 mm

For solar cells of two different areas made with the same processing at the same time, the  $(I \cdot \frac{A_T}{A_S} \cdot R_S)$  drop is higher for larger cells than for smaller ones, resulting in a slightly smaller fill factor for large area cells.

$R_G$  of large area cells can be reduced by increasing the thickness of grid metal deposition or by replacing it with a higher conductivity metal grid. It is significant to comment on the (High Quality) Monsanto wafer shown in Table 6. This substrate gave a much better  $V_{oc}$  and  $J_{sc}$  than the others ( $V_{oc} = 0.59$  V and  $J_{sc} = 26-27$  mA/cm<sup>2</sup>). These are due to 1) a highly polished surface which reduces surface state density and 2) improved diffusion length. Illuminated I-V data for cells on this wafer are shown in Figure 9. Thicker grid metal will increase fill factor in future samples.

Table 6

PHOTOVOLTAIC DATA ON LARGE-TO-SMALL AREA CELLS (NEW GRID)

| SUBSTRATE                        | RESISTIVITY<br>( $\Omega\text{-cm}$ ) | AREA ( $\text{cm}^2$ ) |       | $V_{\text{oc}}$<br>(V) | $J_{\text{sc}}^{**}$<br>( $\text{mA/cm}^2$ ) | FF   | EFFICIENCY $\eta\%$ |        | PROCESSING                 |

|----------------------------------|---------------------------------------|------------------------|-------|------------------------|----------------------------------------------|------|---------------------|--------|----------------------------|

|                                  |                                       | ACTIVE                 | TOTAL |                        |                                              |      | ACTIVE              | TOTAL  |                            |

| MONSANTO <100>                   | 0.05-0.15                             | 3.68                   | 4.0   | 0.51                   | 21.7                                         | 0.68 | 7.5                 | 6.8    | P.E., DO Process (580° C)* |

|                                  |                                       | 2.0                    | 2.12  | 0.50                   | 20.5                                         | 0.70 | 7.2                 | 6.8    |                            |

| MONSANTO <100><br>(High Quality) | 1.5-2                                 | 3.68                   | 4.0   | 0.59                   | 26.1                                         | 0.62 | 9.6                 | 8.9    | DO Process (600° C)*       |

|                                  |                                       | 2.0                    | 2.12  | 0.59                   | 27.0                                         | 0.66 | 10.6                | 10.0   |                            |

|                                  |                                       | 0.14                   | 0.15  | 0.58                   | 18.4                                         | 0.76 | 8.1***              | 7.3*** |                            |

| MONSANTO <100>                   | > 5                                   | 3.68                   | 4.0   | 0.54                   | 24.5                                         | 0.60 | 7.9                 | 7.2    | DO Process (580° C)*       |

|                                  |                                       | 2.0                    | 2.12  | 0.54                   | 26.0                                         | 0.61 | 8.5                 | 8.1    |                            |

|                                  |                                       | 0.14                   | 0.15  | 0.53                   | 19.2                                         | 0.51 | 5.2***              | 4.7*** |                            |

\* Temperature at which oxide is grown

\*\* Based on NASA-Lewis calibration and using ELH lamp @ 100 mW/cm<sup>2</sup>

\*\*\* No anti-reflection coating

In future cells, a high efficiency will be achieved by

- 1) Better polishing techniques to give  $V_{oc} \approx 0.59$  V.

- 2) Better grid performance using a solder dip to give  $FF \approx 0.75$ .

- 3) Improved A/R coating to give  $J_{sc} \approx 30$  mA/cm<sup>2</sup>.

Figure 9 Photovoltaic I-V data comparing

4 cm<sup>2</sup>, 2 cm<sup>2</sup> and small area cells

## 5. ANALYSIS OF MIS SOLAR CELLS

### 5-1 Grain Boundary Studies by C-V-F and G-V-f (V. J. Rao)

In the course of our investigations on polycrystalline Si MIS solar cells, we have undertaken the work on C-V, G-V, G/f - f measurements of polycrystalline MIS diodes in order to evaluate the grain boundary effects on interface states. To date, neither theoretical nor experimental data are available on C-V measurements of grain boundaries in polycrystalline silicon solar cells.

The determination of the density of states distribution in the grain boundaries of polycrystalline silicon is very useful in developing our understanding of the physical properties of the material and in particular of the role of grain boundaries. Capacitance-voltage and conductance-voltage measurements on Schottky diodes appear to be a promising technique for the determination of density of states. The purpose of this work is to explore the frequency dependence of both the conductance and capacitance of Schottky devices in order to deduce the depletion width and density of states in the region of the Fermi level and below. If the frequency dependence is measured and analysed with and without externally applied dc voltage, as is the case for most of the present work, very useful data could be obtained about the role of grain boundary effects.

The electrical properties of interface states are characterized by interface state density, the position in the energy gap of the silicon and the capture cross section. The most widely used tool for investigating these interface state properties is the MIS diode. Dispersion of the capacitance can be used to obtain information about the energy distribution and density of interface states.<sup>[8]</sup> The capacitance technique, however, has severe limitations. Essentially, the difficulty is that interface state capacitance must be extracted from measured capacitance which consists of oxide capacitance, depletion layer capacitance and interface state capacitance. This difficulty does not apply to the equivalent parallel conductance because conductance arises solely from the steady state loss due to the capture and emission of carriers by interface states and is thus a more direct measure of these properties. Conductance measurements yield more accurate and reliable results particularly when the density of interface states is low as in the thermally oxidized system. Both the capacitance and

equivalent parallel conductance as functions of voltage and frequency contain identical information about interface states. Greater inaccuracies arise in extracting this information from the capacitance.

In order to evaluate MIS measurements with regard to interface states, it is desirable to have one dimensional current flow perpendicular to the interface. This condition may not apply when the silicon underneath the field plate and beyond is inverted. Then the capacitance and conductance are dominated by the lateral a.c. current-flow. Because of the positive polarity of surface charge, p-type silicon is normally inverted and is therefore most easily investigated in the inversion region.

A study of grain boundary effects is made using a wafer of Hamco poly-silicon having very large grains. A comparison in data is made for a small diode having a single grain boundary and another small diode of the same area with no grain boundary. A sketch showing diodes and grain boundary location for this study is given in Figure 10. Measurements of capacitance  $C(f, V)$  and conductance  $G(f, V)$  as a function of frequency are made using the in phase and quadrature components from a PAR 5204 lock-in-amplifier. Modulation voltage remained at 25 mV peak to peak. An operational pre-amplifier to combine a.c. and d.c. components, facilitated measurements of  $C(f, V)$  and  $G(f, V)$  under bias. During the measurements, the sample remained at room temperature in air. The system set-up to measure capacitance and conductance was previously given<sup>[7]</sup> (Figure 11). Standard glass capacitors are used to calibrate the lock-in-amplifier.

Figures 12 and 13 show the  $C(f, V)$  curves for diodes on the grain ( $R_3$ ) and grain boundary ( $L_3$ ) at various frequencies ( $20 \text{ Hz} < f < 5000 \text{ Hz}$ ). A description of the main features of the curves will be presented. Significant changes in C-V and G-V data are noted when comparing diodes with and without grain boundaries. One significant feature is the nature of the capacitance-voltage characteristics in the voltage range where the semiconductor surface is inverted. The specific features which deserve reference are 1) the  $20 \text{ Hz}$  and  $50 \text{ Hz}$  curves in case of a diode on the grain exhibit an increase in the capacitance when the top contact is reverse biased while the diode on the grain boundary shows a decrease in capacitance and becomes saturated. It appears in case of  $R_3$  that the signal frequency is low enough so that the minority carriers within the inversion region become mobile and

Figure 10 GRAIN BOUNDARY LOCATION FOR I-V-T STUDY

## LOCK-IN AMPLIFIER SYSTEM

Figure 11 Lock-in-amplifier circuit for

C-V-f and G-V-f studies

Figure 12 C-V-f data for a MIS diode on a single grain

#168 ( $R_3$ ) on the grain

Figure 13 C-V-f data for a MIS diode on a

grain boundary

#168 ( $L_3$ ) on the grain boundary

would follow the variations of the measurement signal and contribute to the capacitance in an additive manner to the space charge capacitance which therefore will be higher than in the high frequency case. Accordingly, with increased inversion the capacitance rises and becomes saturated with applied bias.

It can be seen that in the 500 Hz frequency range, the capacitance becomes practically constant in both the cases  $R_3$  and  $L_3$ , when the semiconductor surface is inverted. This constant capacitance corresponds to the limit reached by the depletion region width. In this frequency range, the majority carriers would be able to follow the dc bias but not the ac signal.

At very high frequencies in both cases, the capacitance decreases as a function of bias, which may mean that the minority carriers cannot accumulate near the surface even in the bias range corresponding to inversion. The minority carriers cannot follow the a.c. bias and hence do not accumulate at the surface or d.c. bias changes rapidly to the inversion side and capacitance is measured before minority carriers can accumulate near the surface. This may correspond to the transient case.

The two curves of 20 Hz and 50 Hz for  $R_3$  exhibit a minimum at about 0.1 and 1 volt respectively, which is followed by an increase in the capacitance. This may be due to the fact that all charge within the semiconductor consists of acceptor ions and therefore the depletion region is comparatively large and correspondingly the space charge capacitance is small.

Conductance for both  $R_3$  and  $L_3$  is plotted as a function of bias at various frequencies and they are shown in Figures 14 and 15, respectively. One significant feature is that conductance decreased in the bias range 0-0.5 mV followed by an increase in the conductance which becomes saturated when it is reverse biased in the case of  $R_3$ . In the case of  $L_3$ , conductance decreases and then becomes saturated. The conductance curves at high frequency have not changed appreciably in shape but have in magnitude. The magnitude of the conductance is higher at all frequencies for  $R_3$  compared to  $L_3$ . Also, conductance data are much more frequency dependent for  $L_3$ .

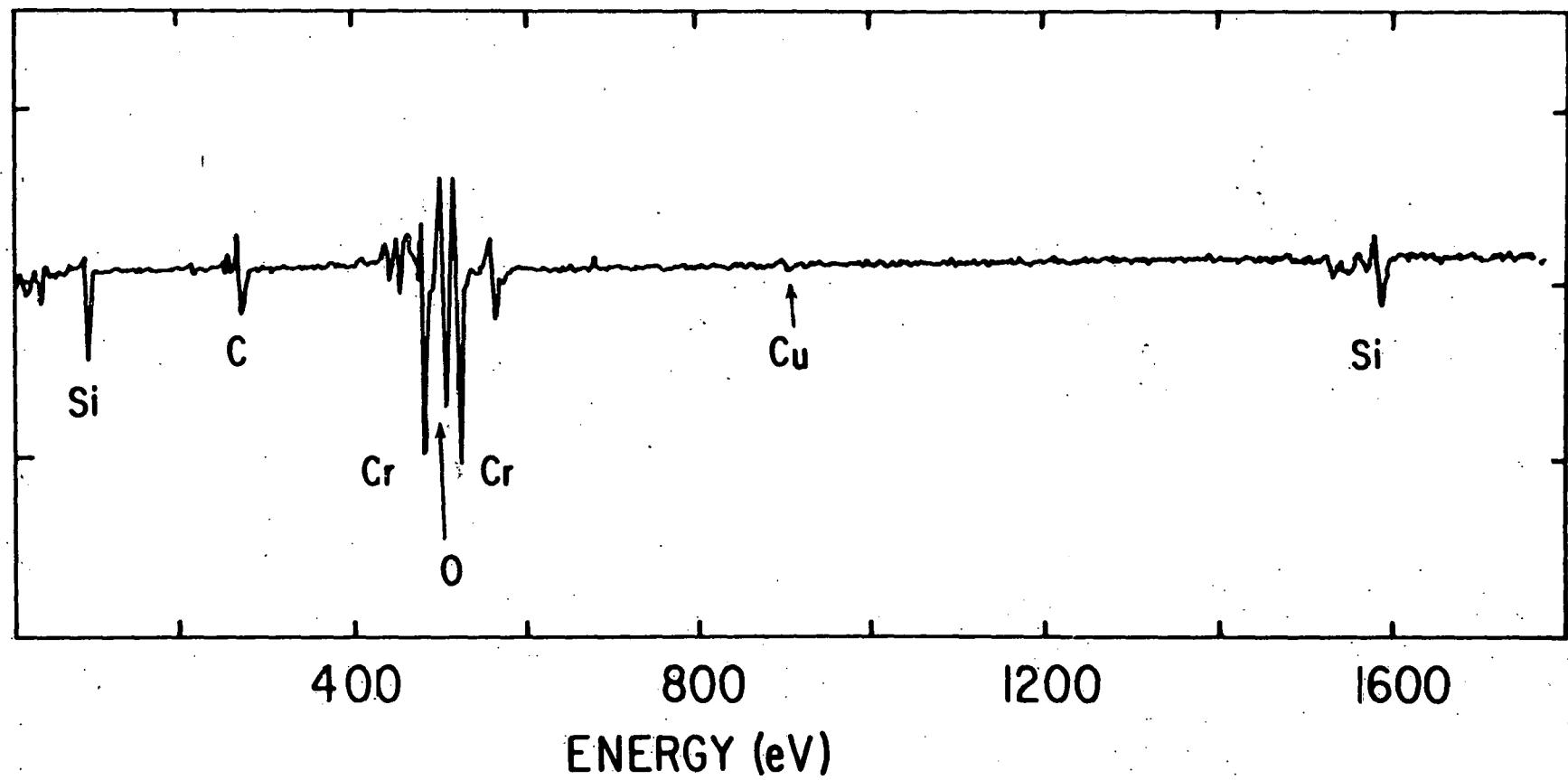

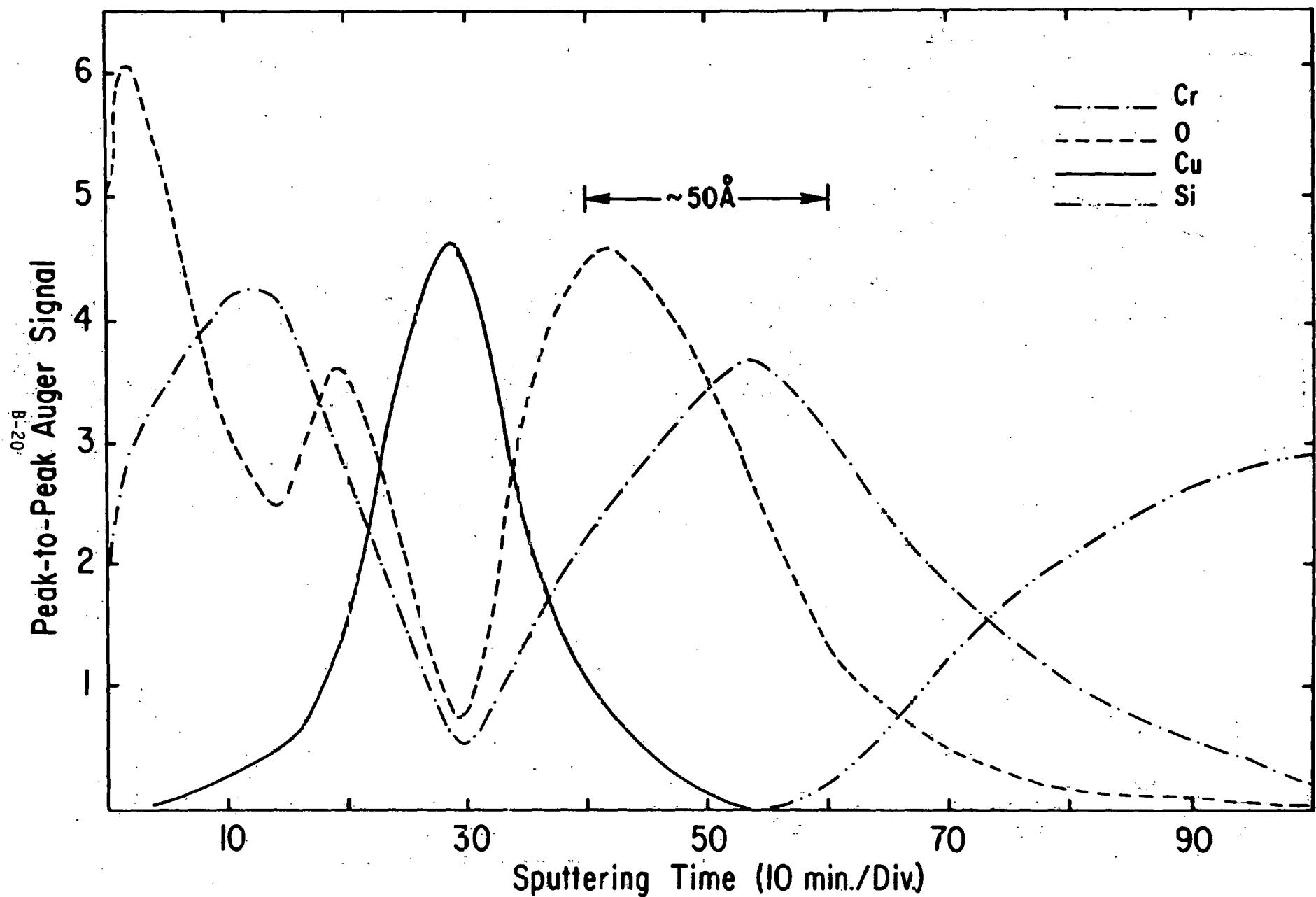

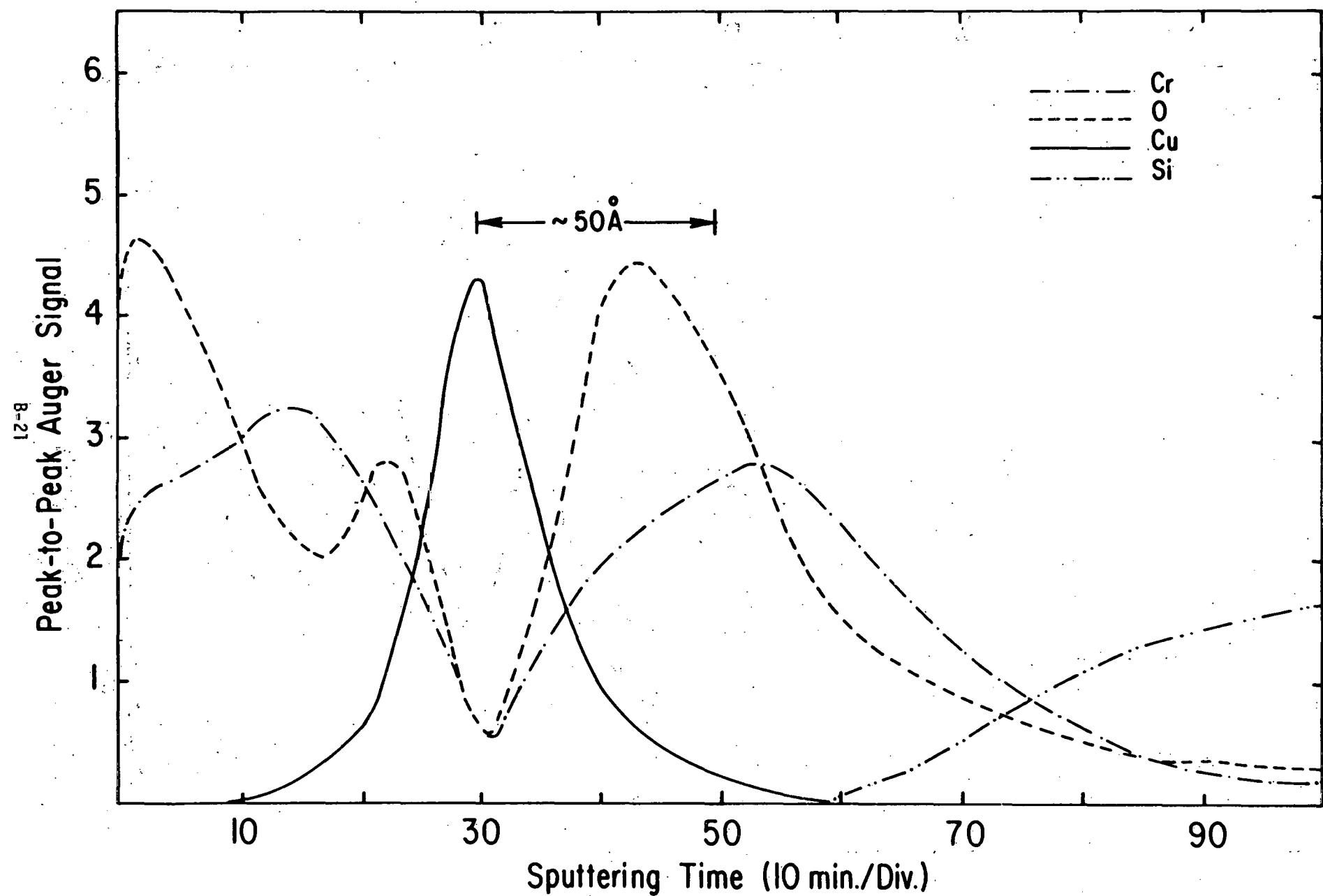

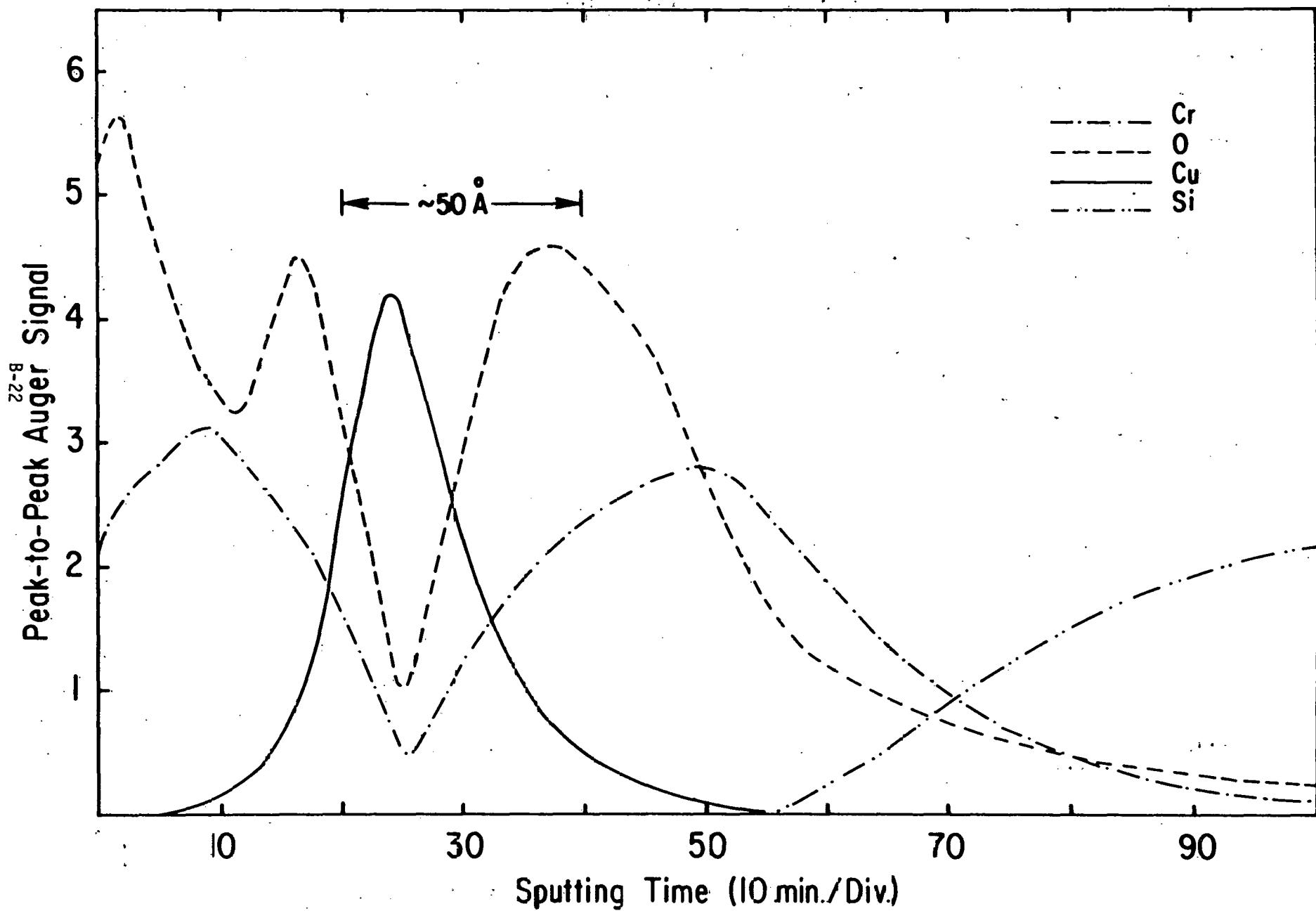

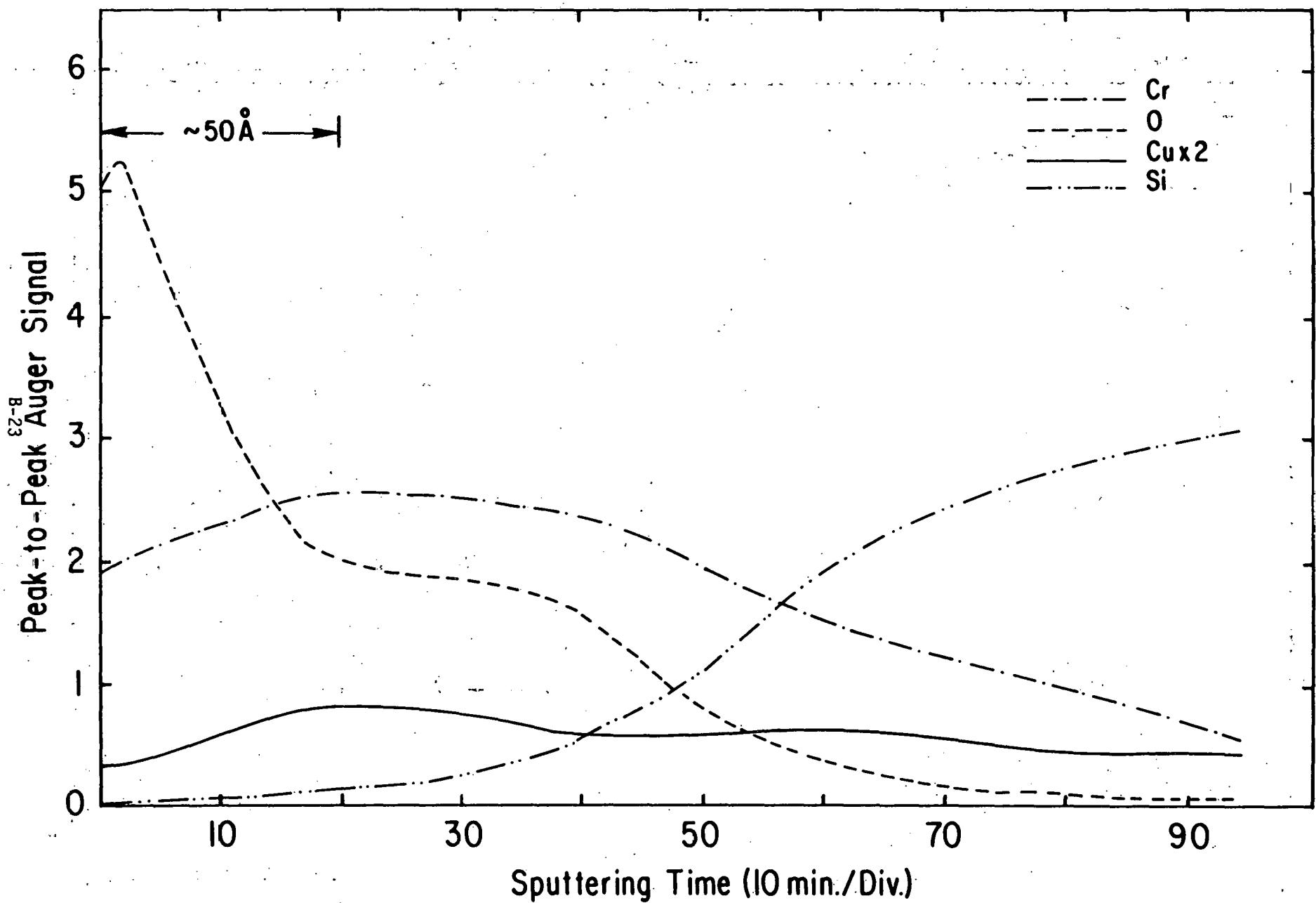

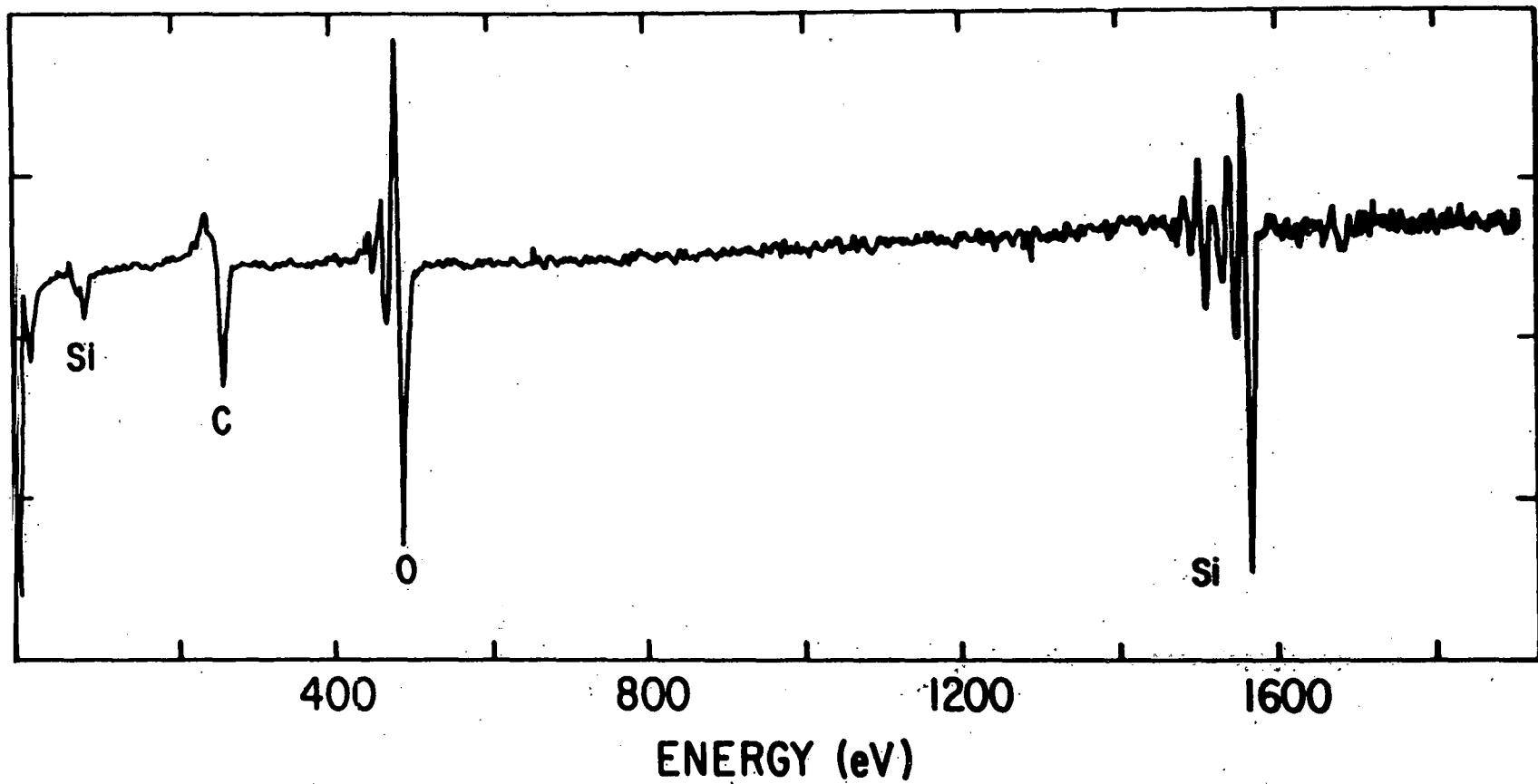

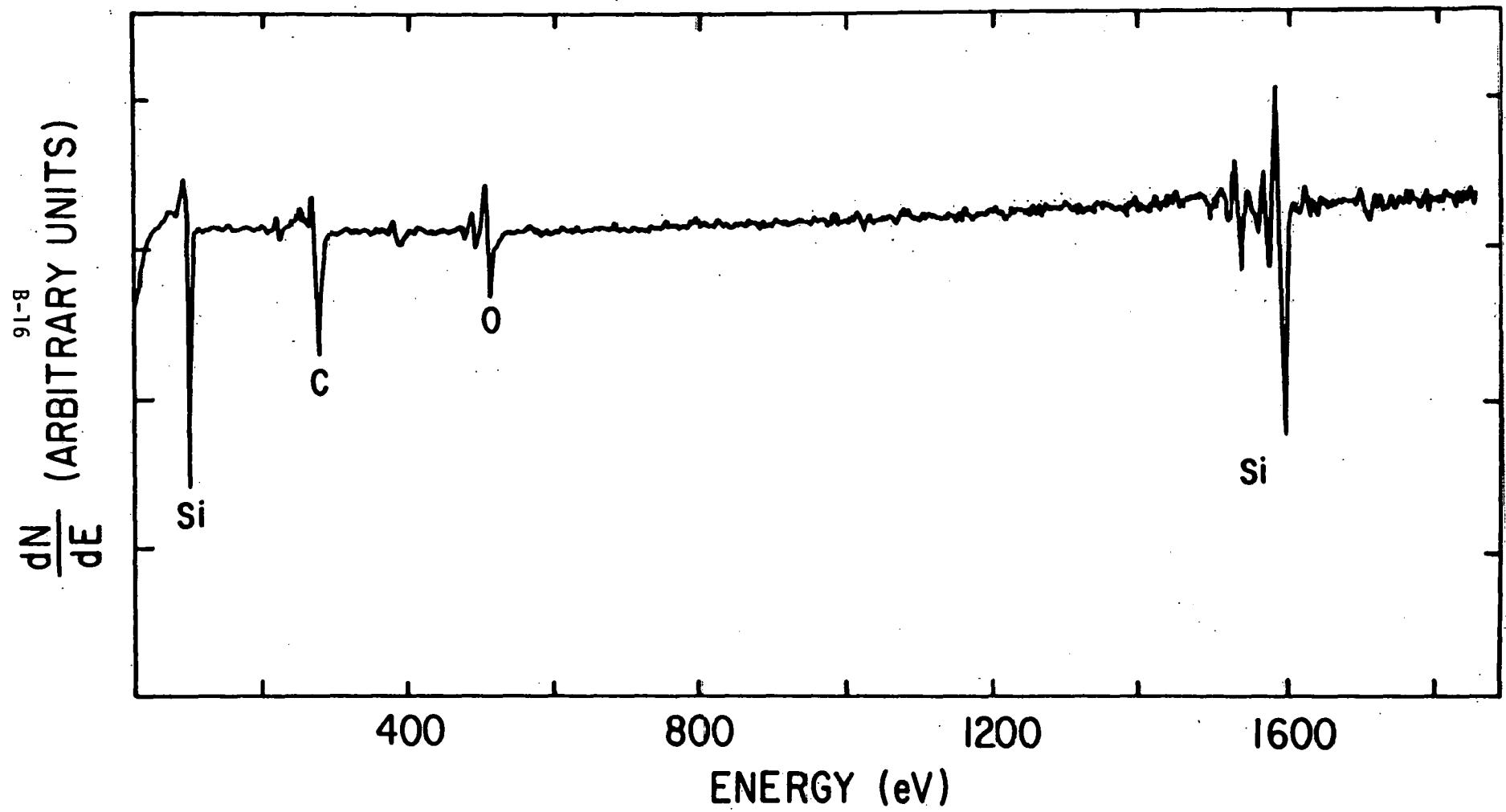

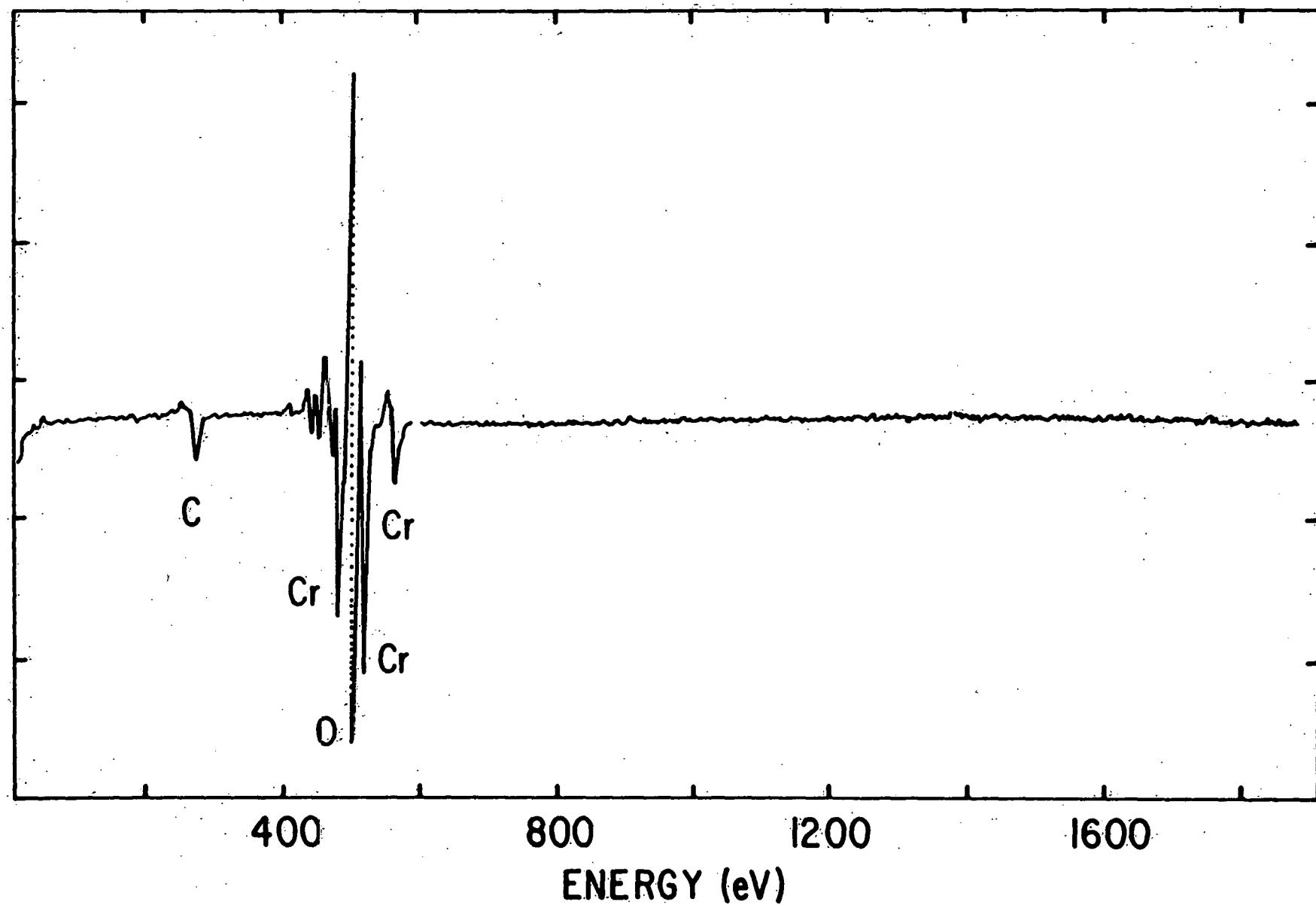

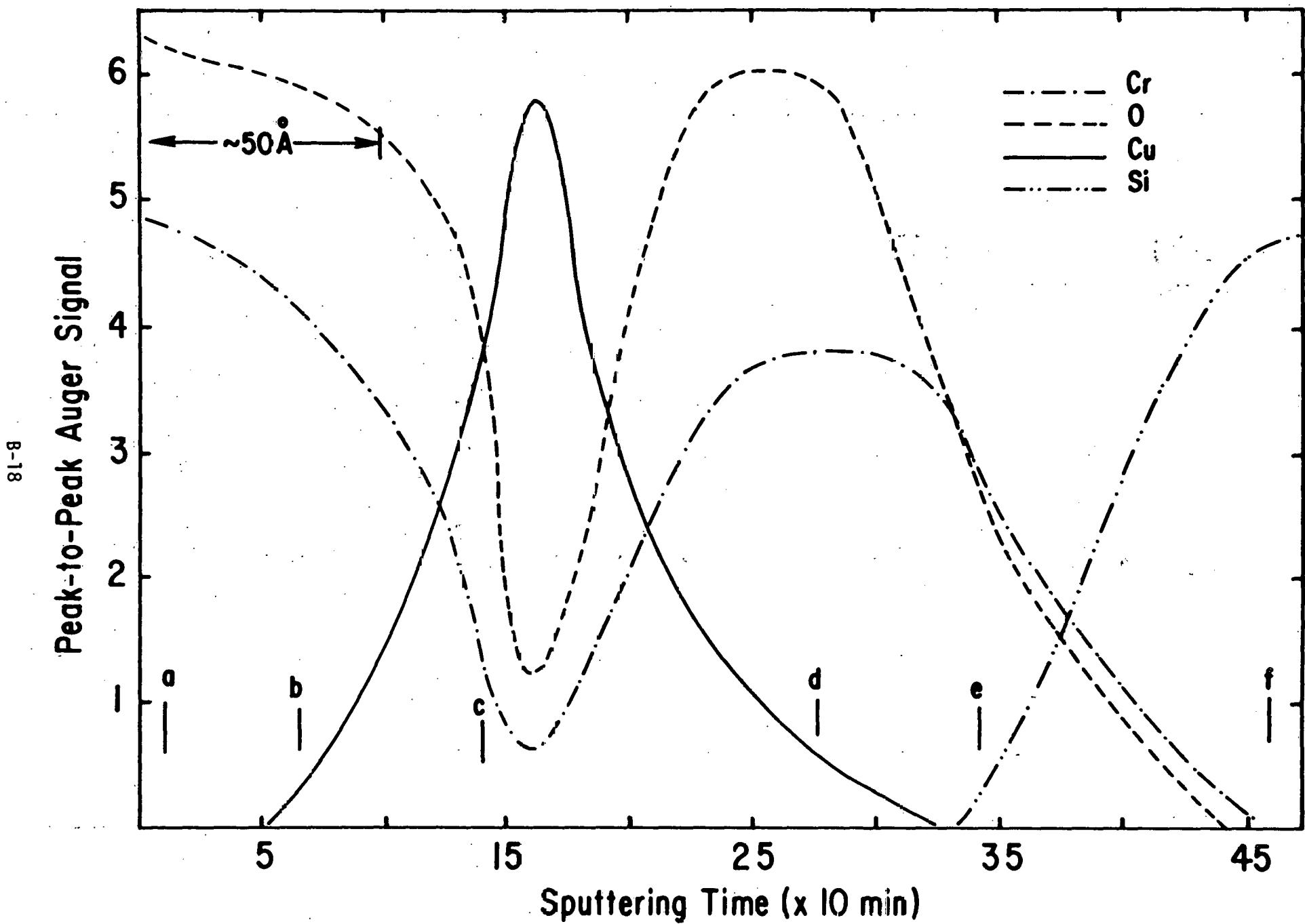

## 5-2 Auger, ESCA, and Elliposmeter Studies

A paper written by Dr. B. W. Lee is given in Appendix B which describes these studies related to the stability of the Cr-MIS solar cell. This work was partially reported in one of our previous reports. [8]

Figure 14 G-V-f data for a MIS diode on a single grain

#168 ( $R_3$ ) on the grain

Figure 15 G-V-f data for a MIS diode on a

grain boundary

#168 ( $L_3$ ) on the grain boundary

## 6. RELIABILITY STUDIES (M. Thayer)

This reliability study explores the degradation of MIS cells exposed to light, dark, or environmental conditions. An ELH lamp calibrated at AM1 illumination was used to test each cell. Test results of the cells subject to light or dark conditions are summarized in Table 7. Cells used in the light bias study were continuously illuminated by a 300 W tungsten lamp. The open circuit voltage ( $V_{oc}$ ) and efficiency ( $\eta$ ) of these cells initially dropped 15% but are now at a relatively constant value. After a year of testing, the shelf-life study still indicates that little degradation of the MIS cells has occurred.

A solar panel consisting of nonencapsulated and encapsulated cells was placed on the roof. After a week of exposure, the fill factor of the non-encapsulated cell had dropped from .66 to .3. This indicates that the series resistance of the contact had increased. Visual inspection indicated that both the anti-reflective (AR) coating and the aluminum contact had degraded. The aluminum contact had degraded to such an extent, that in order to obtain a good contact, test probes were pierced through the anti-reflective (AR) coating further down the aluminum bus bar. Once this was done the fill factor was found to be 0.6. This is conclusive proof of degradation found in exposed contacts. Sylgard 184 was used as an encapsulant for the cells that were placed outdoors. After two months of operation the open circuit voltage had dropped 35%. Microscopic examination of an encapsulated cell indicates degradation of the aluminum grid.

Degradation of the encapsulated cells could be due to:

- 1) Chemical reaction.

- 2) Ionic transport of aluminum.

- 3) Impurity migration of Al into the surrounding layers.

- 4) Moisture.

- 5) Degradation of silicon, silicon oxide barrier.

Moisture tests can be performed by placing cells in 95% relative humidity. Encapsulated cells could be sprayed with saline solution. Methods of encapsulation could be improved by encapsulating cells in a vacuum or in a controlled atmosphere. Chromium could be deposited beneath the aluminum grid to prevent diffusion of aluminum into copper. Results from these tests will indicate whether to continue using Sylgard 184.

Table 7

SOLAR CELL RELIABILITY DATA

**A. SHELF LIFE STUDY**

| <u>Cell</u> | <u>Date</u> | <u><math>V_{oc}</math> (V)</u> | <u><math>J_{sc}</math> (<math>\frac{mA}{cm^2}</math>)</u> | <u>FF</u> | <u><math>P_o</math> (<math>\frac{mW}{cm^2}</math>)</u> | <u>Comments</u> |

|-------------|-------------|--------------------------------|-----------------------------------------------------------|-----------|--------------------------------------------------------|-----------------|

| 53          | 9/21/79     | 0.51                           | 24.0                                                      | 0.72      | 8.8                                                    | XTAL            |

|             | 3/6/80      | 0.51                           | 24.5                                                      | 0.65      | 8.1                                                    |                 |

|             | 4/29/80     | 0.48                           | 23.5                                                      | 0.70      | 7.9                                                    | Now Illuminated |

| 65          | 8/22/79     | 0.53                           | 28.5                                                      | 0.71      | 10.7                                                   | XTAL            |

|             | 1/24/80     | 0.54                           | 26.5                                                      | 0.72      | 10.3                                                   |                 |

|             | 5/8/80      | 0.53                           | 25.5                                                      | 0.69      | 9.4                                                    |                 |

|             | 5/27/80     | 0.52                           | 23.5                                                      | 0.70      | 8.6                                                    |                 |

|             | 7/30/80     | 0.52                           | 27.0                                                      | 0.73      | 10.3                                                   |                 |

|             | 8/25/80     | 0.53                           | 26.0                                                      | 0.75      | 10.3                                                   |                 |

|             | 10/5/80     | 0.52                           | 23.5                                                      | 0.74      | 9.0                                                    |                 |

|             | 10/28/80    | 0.53                           | 26.0                                                      | 0.72      | 9.8                                                    |                 |

| 206         | 10/12/79    | 0.53                           | 28.6                                                      | 0.63      | 9.6                                                    | XTAL            |

|             | 4/8/80      | 0.51                           | 30.0                                                      | 0.68      | 10.4                                                   |                 |

|             | 4/29/80     | 0.51                           | 30.5                                                      | 0.61      | 9.4                                                    |                 |

|             | 5/27/80     | 0.50                           | 28.0                                                      | 0.68      | 9.5                                                    |                 |

|             | 6/27/80     | 0.50                           | 29.0                                                      | 0.66      | 9.6                                                    |                 |

|             | 7/30/80     | 0.50                           | 31.5                                                      | 0.69      | 10.7                                                   |                 |

|             | 8/25/80     | 0.51                           | 30.0                                                      | 0.72      | 10.9                                                   |                 |

|             | 10/5/80     | 0.49                           | 30.0                                                      | 0.66      | 9.7                                                    |                 |

|             | 11/28/80    | 0.50                           | 28.5                                                      | 0.68      | 9.7                                                    |                 |

**B. LIGHT BIAS STUDY**

|     |          |      |      |      |     |                            |

|-----|----------|------|------|------|-----|----------------------------|

| 126 | 3/18/80  | 0.53 | 26.0 | 0.68 | 9.4 | Hamco,                     |

|     | 5/8/80   | 0.51 | 25.5 | 0.67 | 8.7 | Pressure                   |

|     | 5/27/80  | 0.51 | 22.5 | 0.70 | 8.0 | Contract                   |

|     | 6/27/80  | 0.51 | 23.5 | 0.68 | 8.2 |                            |

|     | 7/30/80  | 0.51 | 24.5 | 0.66 | 8.3 |                            |

|     | 8/25/80  | 0.51 | 24.0 | 0.68 | 8.4 |                            |

|     | 10/15/80 | 0.50 | 25.0 | 0.66 | 8.2 |                            |

|     | 11/12/80 | 0.47 | 22.0 | 0.60 | 6.2 | Placed outdoors (10/15/80) |

| 162 | 4/1/80   | 0.50 | 23.5 | 0.63 | 7.4 | Wacker,                    |

|     | 5/8/80   | 0.49 | 22.0 | 0.58 | 6.3 | Silver                     |

|     | 5/27/80  | 0.48 | 19.5 | 0.54 | 5.0 | Epoxy                      |

|     | 6/27/80  | 0.49 | 21.5 | 0.51 | 5.4 |                            |

|     | 7/30/80  | 0.49 | 20.0 | 0.55 | 5.4 |                            |

|     | 8/25/80  | 0.49 | 22.0 | 0.50 | 5.1 |                            |

|     | 10/6/80  | 0.49 | 21.0 | 0.48 | 5.0 |                            |

|     | 12/5/80  | 0.49 | 21.0 | 0.50 | 5.2 |                            |

| 53  | 5/27/80  | 0.48 | 21.5 | 0.72 | 7.4 | XTAL                       |

|     | 6/27/80  | 0.48 | 23.5 | 0.72 | 8.2 |                            |

|     | 7/30/80  | 0.48 | 24.0 | 0.72 | 8.3 |                            |

|     | 8/25/80  | 0.48 | 23.5 | 0.72 | 8.1 |                            |

|     | 10/6/80  | 0.47 | 22.5 | 0.71 | 7.5 |                            |

|     | 12/5/80  | 0.47 | 23.0 | 0.70 | 7.7 |                            |

## 7. REFERENCES

1. W. A. Anderson, G. Rajeswaran, K. Rajkannan and G. Hoeft, "A Revised Process to Increase Efficiency and Reproducibility in Cr-MIS Solar Cells," IEEE Electron Device Letters, Vol. EDL-1, No. 7, pp. 128-130, July 1980.

2. W. A. Anderson and G. Rajeswaran, "An Evaluation of Potentially Low Cost Silicon Substrates for MIS Solar Cells," J. Appl. Physics, accepted for publication.

3. K. E. Bean, "Anisotropic Etching of Silicon," IEEE Trans. Elec. Dev., ED-25, 1185, 1978.

4. S. K. Dey, W. A. Anderson, A. E. Delahoy and C. Cartier, "Spectral Response and Diffusion-Length Studies of Amorphous, Polycrystalline, Ribbon, Epitaxial and Single Crystal Silicon MIS Solar Cells," J. Appl. Physics, 50 (6), June 1979, pp. 4425.

5. K. Rajkannan and J. Shewchun, "A Better Approach to the Evaluation of the Series Resistance of Solar Cells and Area Dependence of Performance Characteristics," Solid State Electronics, Vol. 22, pp. 193-197, 1979.

6. R. J. Handy, "Theoretical Analysis of the Series Resistance of a Solar Cell," S. S. Elec., 10, p. 765, 1967.

7. J. K. Kim, W. A. Anderson and S. L. Hyland, "Relating Computer Simulation Studies with Interface State Measurements of MIS Solar Cells," IEEE Trans. Elec. Dev., ED-26, p. 1777, 1979.

8. W. A. Anderson, "MIS Solar Cells on Thin Polycrystalline Silicon," SERI Report No. 2 on contract XM-0-9080-1, dated September 1980.

## 8. CONCLUSIONS

1. E-beam Si films on Si substrates replicate the substrate in surface features and crystallite orientation.

2. MIS cells scaled from  $2 \text{ cm}^2$  to  $4 \text{ cm}^2$  show about the same efficiency. Scale-up to large area is not a problem.

3. G-V-f and C-V-f data may eventually give quantitative data on defect density at the interface of grain boundaries.

## 9. PLANS FOR THE NEXT QUARTER

1. Continue e-beam Si deposition and further evaluate electrical properties.

2. Improve etching and D.I.  $\text{H}_2\text{O}$  procedures in preparing Si.

3. Improve MIS cell efficiency.

4. Continue evaluating grain boundaries by C-V-f and G-V-f.

5. Expand reliability studies.

## 10. RESEARCH PARTICIPANTS

|               |   |                                            |

|---------------|---|--------------------------------------------|

| B. W. Lee     | - | Assistant Professor - Auger Study, Rutgers |

| V. J. Rao     | - | Post Doctoral                              |

| G. Rajeswaran | - | Research Assistant                         |

| F. Kai        | - | Research Assistant                         |

| M. Jackson    | - | Research Assistant                         |

| M. Westcott   | - | Undergraduate Assistant, Work Study        |

| M. Thayer     | - | Undergraduate Assistant                    |

| P. Talarico   | - | Technician                                 |

| J. Bennett    | - | Secretary                                  |

## 11. REPORTS/PUBLICATIONS/PRESENTATIONS

1. W. A. Anderson, G. Rajeswaran, K. Rajkaran and G. Hoeft, "A Revised Process to Increase Efficiency and Reproducibility in Cr-MIS Solar Cells," IEEE Electron Devices Letters, Vol. EDL-1, pp. 128-130, July 1980.

2. W. A. Anderson, M. A. Jackson and F. Y. T. Kai, "E-Beam Deposited Thin Silicon Films for Solar Cells," IEEE Conference on Electron Devices Activities in Western New York, Rochester, New York, October 16, 1980.

3. W. A. Anderson, G. Rajeswaran, F. Kai and M. Jackson, "Studies Leading to a Thin Film MIS Solar Cell," 4th Annual Photovoltaic Advanced R & D Conference, Colorado Springs, Colorado, November 18-20, 1980.

## APPENDIX A

### SURVEY OF PREVIOUS WORK ON CONDUCTION MECHANISMS IN SMALL CRYSTAL POLY-SILICON

#### Introduction:

During the past ten years thin film polycrystalline silicon has been studied by many researchers because of the possible application to low cost, large area solar cells. Experiments as well as theories on the electrical properties of small grain size polycrystalline silicon films are studied. This section is a survey of some of the previous work done by these researchers in order to give a clear picture to study the current conduction mechanisms which will permit us to fabricate low cost, large area polycrystalline Si solar cells. Our next report will present a survey of other work and outline our approach to the problem.

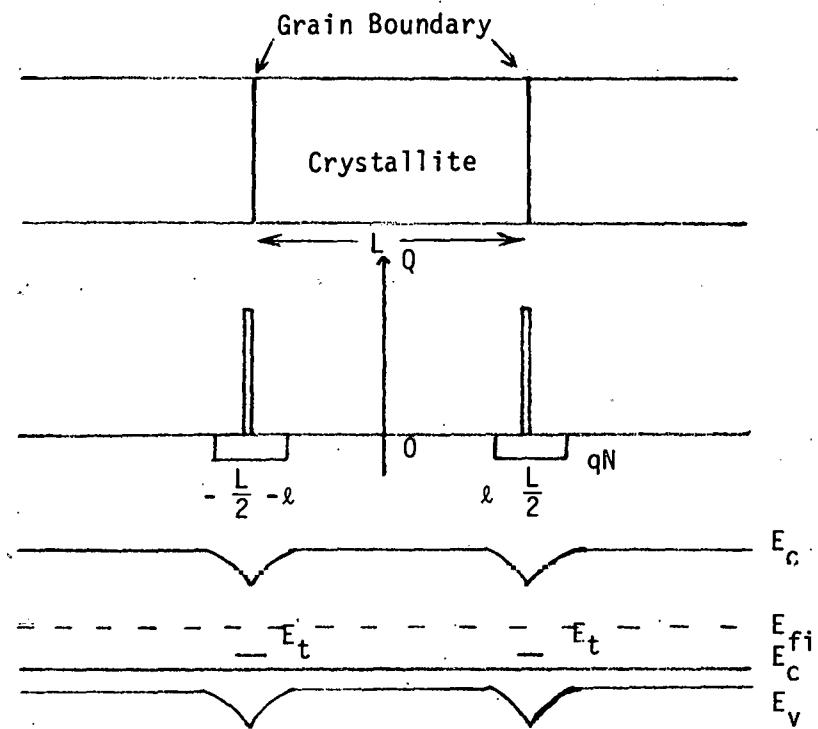

#### (A) John Y. W. Seto<sup>1</sup>

##### (i) Sample Preparation:

Polycrystalline films ion implanted with boron to precisely control doping concentration.

##### (ii) Assumptions:

- (1) Does not believe in "impurity segregation"<sup>2</sup> at the grain boundary.

- (2) Electrical transport properties of polycrystalline films governed by "carrier trapping" at the grain boundary.<sup>3,4</sup>

- (3) One type of impurity atom present. Impurity atoms are totally ionized, and uniformly distributed with a concentration of  $N/cm^3$ .

- (4) Grain boundary thickness is negligible compared to grain size  $L$ . It contains  $Q_t/cm^2$  of traps located at  $E_t$  with respect to the intrinsic Fermi level. The traps are assumed to be initially neutral and become charged by trapping a carrier.

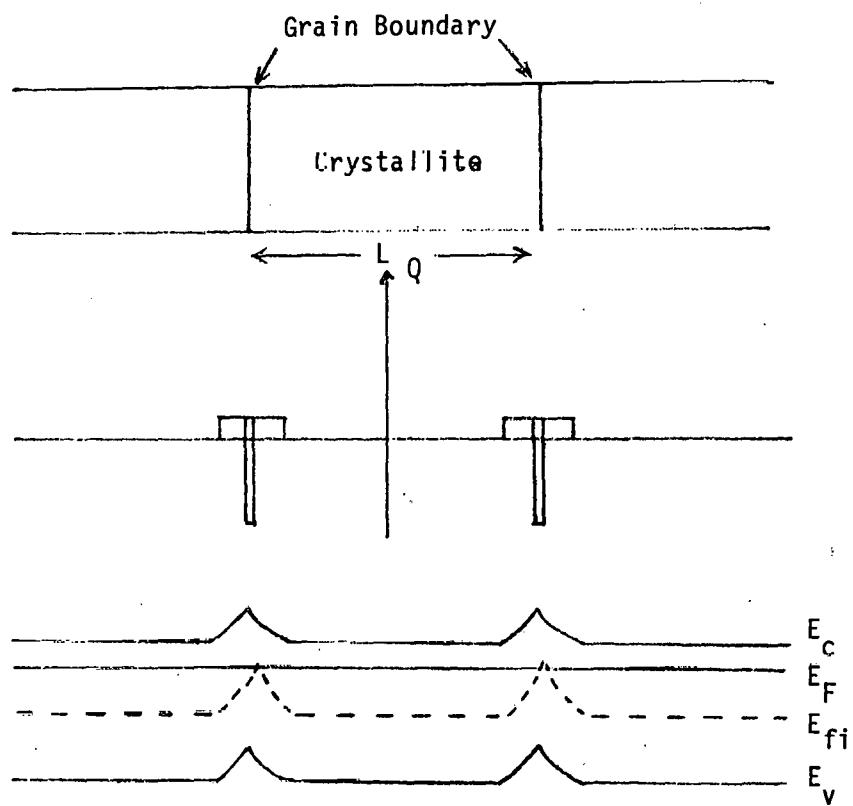

Figure A-1. Model Used by Seto<sup>(1)</sup>

Figure A-2. Model Used by Baccarain et.al.<sup>(5)</sup>

(5) Neglect the contribution to the resistivity by the bulk of the crystallites and consider only the resistance of the grain-boundary region.

(iii) Basic Model:

The two important contributions to the current across the grain boundary are:

- a) Thermionic emission

- b) Tunneling (field emission)

In this paper tunneling is neglected and the dominant current is from thermionic emission. We will see below the different expressions for conductivity in the two cases and the existence of a mobility minimum.

Define:

$$p_a = \frac{n_i}{Lq} \left( \frac{2\pi\epsilon kT}{N} \right)^{\frac{1}{2}} \exp\left(\frac{E_B + E_f}{kT}\right) \exp\left[\frac{qL}{2} \left( \frac{N}{2\epsilon kT} \right)^{\frac{1}{2}}\right] \quad A-1$$

$$J_{th} = qp_a \left( \frac{kT}{2\pi m} \right)^{\frac{1}{2}} \exp\left(-\frac{qV_R}{kT}\right) \left[ \exp\left(\frac{qV_R}{kT}\right) - 1 \right] \quad A-2$$

If  $V_a \ll kT$

$$J_{th} = q^2 p_a \left( \frac{1}{2\pi m kT} \right)^{\frac{1}{2}} \exp\left(-\frac{qV_R}{kT}\right) V_a \quad A-3$$

$$\sigma = L q^2 p_a \left( \frac{1}{2\pi m kT} \right)^{\frac{1}{2}} \exp\left(-\frac{qV_R}{kT}\right) \quad A-4$$

Case (1):  $LN < Q^*$

Under case (1) the crystallite is completely depleted of carriers and the traps are partially filled.

$$E_B \propto N \quad A-5$$

$$LN = \frac{Q_t}{2\exp[(E_t - E_f)/kT]H} \quad A-6$$

$$E_f = E_t - kT \ln[\frac{1}{2}Q_t/LN - 1]$$

A-7

$$\sigma \propto \exp[-(\frac{1}{2} E_g - E_f)/kT]$$

A-8

$$\mu_{\text{eff}} = \frac{1}{2\pi m} \frac{1}{kT} \exp(-\frac{E_B}{kT})$$

A-9

Case (2):  $LN > Q_t$

Under case (2), only part of the crystallite is depleted of carriers.

$$E_B \propto \frac{1}{N}$$

A-10

$$\sigma \propto T^{\frac{1}{2}} \exp(-\frac{E_B}{kT})$$

A-11

(iv) Conclusions:

From eqs. (5) and (10), the energy barrier,  $E_B$ , exhibits a maximum as a function of doping. Eq. (9) shows that the mobility will have a minimum as a function of doping. The minimum occurs at

$$LN = Q_t$$

This behaviour is explained well by trapping state theory.

(B) Baccarani, Ricco and Spadini<sup>5</sup>

(i) Sample preparation:

Phosphorus-doped sputter deposited polycrystalline silicon films.

(ii) Assumption:

- a) The existence of monovalent trapping centers.

- b) Grain-boundary traps consist of states with a uniform density of acceptors in the upper half of the band-gap and donors in the lower half.

(iii) Basic Model:

(1) Monovalent trapping states at the grain boundary

Define:  $N_t$  = acceptor states of grain boundary traps

$N_D$  = impurity concentration

$N_D^*$  = impurity concentration such that when

$N < N_D^*$ , the crystallites are entirely depleted.

W = depletion width

L = grain size

$E_B$  = barrier height

$E_a$  = activation energy

For  $N_D < N_D^*$ , the crystallites are entirely depleted:

$$E_B = \frac{q^2 L^2 N_D}{2\epsilon} \quad B-1$$

$$\sigma \propto \exp\left(-\frac{E_a}{kT}\right) \quad B-2$$

where

$$E_a = \frac{1}{2} E_G - E_t \quad B-3$$

For  $N_D > N_D^*$ , the crystallite are partially depleted:

$$(i) \quad E_B = \frac{q^2 N_t^2}{8\epsilon N_D} \quad \text{for } E_F - E_t - E_B \gg kT \quad B-4$$

$$(ii) \quad E_B = \frac{1}{2} E_G - E_t + kT \ln\left\{qN_D^{\frac{1}{2}}N_t/[N_c(2\epsilon N_B)^{\frac{1}{2}}]\right\} \quad \text{for } E_t + E_B - E_F \gg kT \quad B-5$$

$$\sigma \propto \frac{1}{T} \exp\left(-\frac{E_a}{kT}\right) \quad E_a = E_B \quad B-6$$

$$(iii) \quad \sigma \propto \frac{(E_B)^{\frac{1}{2}}}{(kT N_t)} \exp\left(-\frac{E_a}{kT}\right) \quad B-7$$

(2) Continuous energy distribution of interface states

The limiting value of the impurity concentration  $N_D$  corresponding to complete depletion of the crystallite is  $N_D^*$ :

$$N_D^* = \left( \frac{N_{SS}}{L} \right) \left( 1 + \frac{q^2 N_{SS} L}{8\epsilon} \right)^{-1} kT \ln \left( \frac{N_D^*}{n_i} \right) \quad B-8$$

For  $N_D < N_D^*$

$$\sigma \propto \frac{1}{T} \exp \left( -\frac{E_a}{kT} \right) \quad B-9$$

when

$$E_a = \frac{1}{2} E_G - \frac{LN_D}{N_{SC}} \quad B-10$$

For  $N_D > N_D^*$

$$E_B = \frac{q^2 N_{SS}^2 E_F^2}{8\epsilon N_D} \quad \text{for } N_D \gg \frac{q^2 N_{SS}^2 E_F^2}{2\epsilon} \quad B-11$$

$$E_B = E_F \quad \text{for } N_D \ll \frac{q^2 N_{SS}^2 E_F^2}{2\epsilon} \quad B-12$$

(iv) Conclusion:

- a) Impurity segregation and carrier trapping at the grain boundary both take place in polycrystalline silicon. Experimental data show evidence of some impurity segregation at the grain boundary, at least when it is phosphorus doped.

- b) Trapping states are nearly monovalent, and peaked at midgap.

(c) H. C. Card and W. Hwang<sup>6</sup>

(i) Sample preparation: Not mentioned.

(ii) Assumption:

The dark-carrier transport in Schottky barriers on polycrystalline silicon is dominated by both majority carrier and minority carrier transport. For certain values of grain sizes, the minority carrier injection dominates so that the metal-polysilicon contact resembles a p-n junction rather than a Schottky barrier.

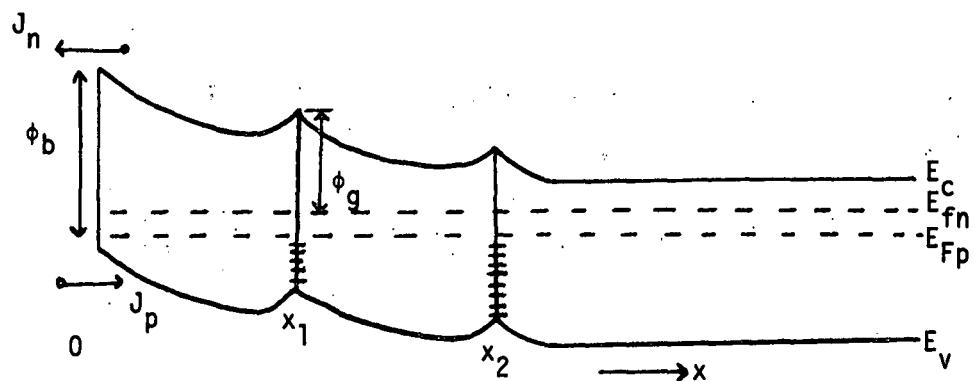

Figure A-3. Model Used by Card and Hwang<sup>(6)</sup>

Figure A-4. Model Used by Fossum and Lindholm<sup>(9)</sup>

(iii) Basic Model:

For n-type semiconductor, the majority carrier current is

$$J_n = A^* T^2 \exp\left(-\frac{q\phi_b}{kT}\right) \left[\exp\left(\frac{qV}{kT}\right) - 1\right] \quad C-1$$

The contribution to the dark current from the injection of minority carriers:

$$J_p = \frac{qD_p n_i^2}{L_p N_d} \left[\exp\left(\frac{qV}{kT}\right) - 1\right] \quad C-2$$

For low doping concentrations  $J_p/J_n$  is negligible for  $\phi_b \leq 1.0$  eV

For polycrystalline silicon the effective value of  $L_p$  may be expected to be short.  $J_p/J_n$  may be expected to increase to exceed unity. Consider two different cases in majority (or minority) carrier transport in the polysilicon Schottky barrier.

(A) Majority-Carrier Transport:

1) Electrode-Limited Conduction:

Transport of electrons across the grain boundaries does not restrict the current.

2) Bulk-Limited Conduction:

The majority-carrier current is dominated by the transport across the grain boundaries; the contact potential  $\phi_b$  does not restrict the current.

(The case for the low  $\phi_b$ )

Assuming there are  $N$  grain boundaries each of barrier height  $\phi_g$  within the silicon film and these are parallel to the surface of the semiconductor:

$$J_n = 2A^* T^2 \exp\left(-\frac{q\phi_g}{kT}\right) \sinh\left(\frac{qV}{2NkT}\right) \quad C-3$$

Define:  $V_1$  = voltage drop across the Schottky barrier

$V_2$  = voltage drop across the total of the  $N$  grain boundaries

$$\begin{aligned}

J_n &= A^* T^2 \exp\left(-\frac{q\phi_b}{kT}\right) \left[ \exp\left(\frac{qV_1}{kT}\right) - 1 \right] \\

&= A^* T^2 \exp\left(-\frac{q\phi_b}{kT}\right) \sinh\left(\frac{qV_1}{2kT}\right)

\end{aligned} \tag{C-4}$$

$$\text{The applied voltage } V = V_1 + V_2$$

(B) Minority-Carrier Transport:

- 1) The presence of grain boundaries in polycrystalline silicon is expected to reduce the majority-carrier current for a given voltage.

- 2) The minority-carrier injection current is increased by the presence of the grain boundaries. The efficient recombination centers reduce  $L_p$ .

The recombination rate at the grain boundary:

$$J_{r1} = qN_{is} \sigma v n(x_1) V_1 \tag{C-5}$$

$N_{is}$  = interface state density at the grain boundary

$\sigma$  = capture cross-section for electrons

$v$  = thermal velocity

$n(x_1)$  = electron concentration of the first grain boundary at position  $x = x_1$ .

The recombination current ( $J_{r1}$ ) of (5) assumes that all interface states between the quasi-Fermi levels  $E_{fn}$  and  $E_{fp}$  for electrons and holes contribute equally to the recombination. It assumes that the recombination traffic through these states is limited by the supply of electrons rather than of holes.

The effective diffusion length ( $L_p^*$ ) for the injected minority carriers:

$$L_p^* = N_r d \tag{C-6}$$

$N_r$  = no. of grain boundaries near the silicon surface

$d$  = grain size to allow all of the injected minority carriers to recombine.

$$J_r = qN_{is} \sigma v N_e \exp\left(-\frac{q\phi_q}{kT}\right) V_1 \quad C-7$$

$$J_p = \sum_r J_{ri} = N_r J_r = \frac{qD_p n_i^2}{L_p N_d} \left[ \exp\left(\frac{qV_1}{kT}\right) - 1 \right] \quad C-8$$

After some manipulation, the minority-carrier injection current is obtained:

$$J_p = qn_i \left( \frac{D_p N_c N_{is} \sigma v V_1}{N_d} \right)^{1/2} \exp\left(-\frac{q\phi_q}{2kT}\right) \exp\left(\frac{qV_1}{2kT}\right) \quad C-9$$

The minority-carrier injection ratio is defined as:

$$\gamma = \frac{J_p}{J_n + J_p} \quad C-10$$

It is very close to unity in the polycrystalline Schottky barrier; the minority-carrier injection often dominates the dark current..

#### (iv) Conclusion:

- (1) Majority-carrier transport in metal-polysilicon Schottky barriers undergoes a transition with bias voltage from electrode-limited to bulk-limited.

- (2) For a range of grain sizes, and of interface state densities at the grain boundary, the dark current may be dominated by the injection of minority carriers.

- (3) The minority-carrier current obeys an  $\exp(\frac{qV}{2kT})$  dependence reminiscent of the high-injection regime of single-crystalline Si.

- (4) A transition from an  $\exp(\frac{qV}{2kT})$  to  $\exp(\frac{qV}{kT})$  dependence is observed with the low-voltage component due to minority carrier diffusion current.

(D) A. K. Ghosh and T. Fang<sup>7,8</sup>

(i) Sample Preparation: