A WIDEBAND PRECISION ANALOG TELEMETRY LINK

USING DIGITAL TECHNIQUES \*

William E. Hearn

Lawrence Berkeley Laboratory

University of California

Berkeley, CA 94720Summary

A highly linear Wideband Analog Fiber Optic Link is described which samples at a 1 MHz rate with 10-bit accuracy and transmits and receives by means of a high speed PDM code. Aliasing and sampling effects are fully suppressed and a nearly Gaussian pulse response is attained with a 2 psec risetime. Analog signals are recovered with very low distortion and d.c. drift and a S/N ratio of better than 52 db.

Introduction

Wideband Isolated Analog Telemetry links are used at Lawrence Berkeley Laboratory for communication of monitor and control signals where large potential differences exist between transmitter and receiver. In a typical application, a link spanning 120,000 volts or more sends and receives  $\pm 10$  volt analog signals and has a signal bandwidth of D.C. to 200 kHz. Such a link must exhibit low D.C. drift, good S/N ratio, and excellent pulse response. Most recent link designs utilize FM/PLL Techniques (1).

This paper will describe the development of an improved Wideband Analog Link using high speed digital techniques. The need for an improved Wideband Link is first noted and a new design is proposed. A block diagram is presented. A complete schematic of the link is discussed. Attention is given to the circuitry for generating and receiving the high speed PDM serial code used. Test results of the unit and conclusions follow.

A New Wideband Analog Link

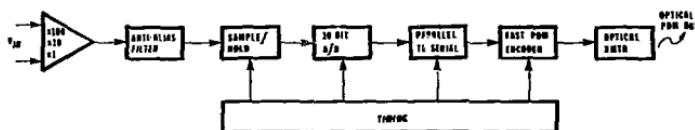

Until recently, FM links of the type described in Reference 1 have been used at LBL. While satisfactory performance has often been obtained, there have been recurrent problems with drift, S/N ratio and reliability. Because of this, it was determined to utilize high speed digital encoding in the design of a new wideband telemetry link. The block diagram of the new Wideband Analog Link is shown in Figs. 1 and 2.

In the transmitter of Fig. 1, the input signal is applied to a wideband differential input amplifier

having high common mode rejection and is processed by an anti-aliasing filter to remove frequencies above 400 kHz. The signal is then sampled and held at a 1 MHz rate and digitized by a fast single-chip 10-bit successive approximation A/D converter. The parallel information is converted to a fast serial PDM code consisting of a series of ten wide (52 nsec) and narrow (27 nsec) pulses and is transmitted via fiber optic cable.

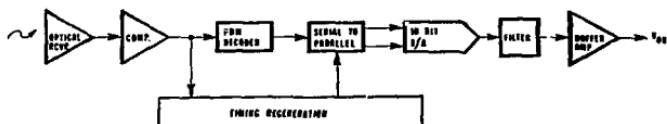

In the receiver of Fig. 2, the optical PDM signal is first amplified by a fast photodiode amplifier capable of resolving the 27- and 52 nsec pulses. After conversion to TTL levels, the information is decoded from the PDM code and applied to a 10-bit D/A converter. Low-pass filtering at 300 kHz is applied to remove the 1 MHz carrier and reconstructed signal is processed by a buffer amplifier. The resultant signal output at the receiver will be a linear duplicate of the transmitter input. Distortion due to the sampling process is minimized and good overall pulse response is ensured by the correct choice of filters in the transmitter and receiver.

The use of digital transmission in the wideband analog link of Fig. 1 and 2 has some practical benefits. These are:

1. Digital transmission inherently contributes no noise, drift, or nonlinearity to the recovered signal. The necessary performance trade-off between noise and linearity seen in FM links does not occur.

2. DC performance of a link of this type depends almost solely on the quality of the A/D and D/A converters. Several excellent units are available.

3. There is no need, as there is with some FM units, to align transmitters and receivers as pairs to achieve optimum linearity. Further, the use of digital signal encoding results in uncomplicated calibration and test procedures which may be performed using simple test fixtures. Maintenance is improved, important where many channels are in service.

\*This work was supported by the Director, Office of Energy Research, Office of Fusion Energy, Development & Technology Division, of the U. S. Department of Energy under Contract No. DE-AC03-76SF0009B.

DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the U.S. Government nor any agency thereof, nor any of their employees, make any representation, express or implied, or assume any liability or responsibility for the accuracy, completeness, or usefulness of any information contained in this report. This report does not necessarily reflect opinions of any agency of the United States Government. It is the property of the United States Government, is loaned to the contractor, and is to be used only for the purpose of this contract. It and its contents are not to be distributed outside the contractor's organization, or made available to other persons, without the written permission of the United States Government or any agency thereof. The views and conclusions expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

*MWP*

FIG. 1. TRANSMITTER BLOCK DIAGRAM

FIG. 2. RECEIVER BLOCK DIAGRAM

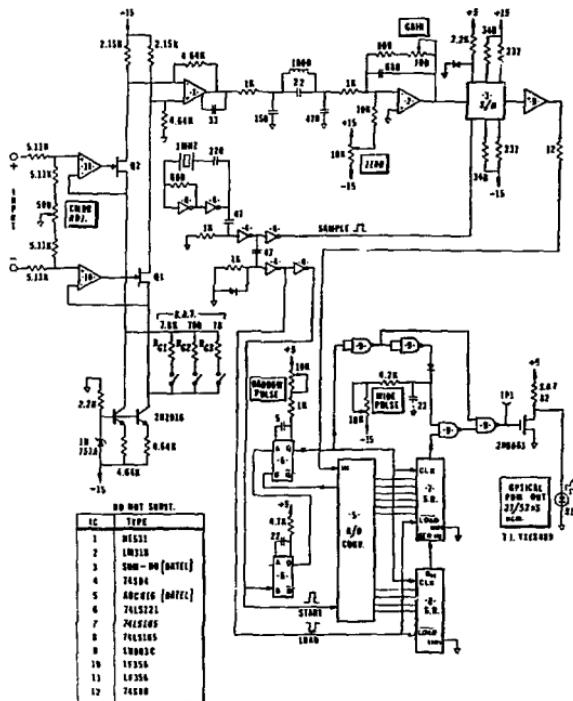

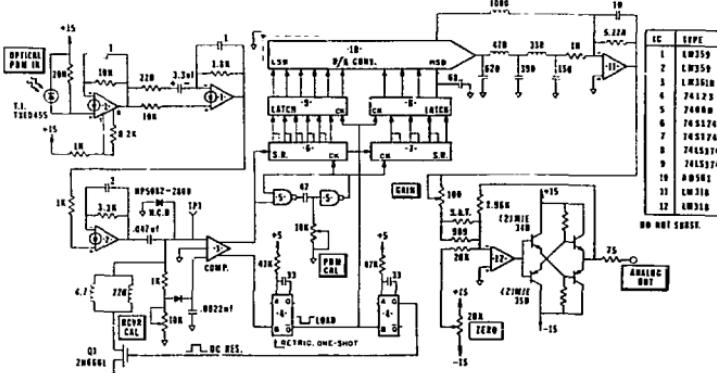

FIG. 3. LINK TRANSMITTER

## Link Design

Figure 3 is a schematic diagram of the transmitter. The input amplifier, consisting of IC 10, IC 11, Q1, Q2, and IC 1, is configured so that the gain may be changed by a single switched resistor, RG. In addition to excellent common mode rejection, this amplifier has very little change of bandwidth when gain is varied over several decades. Resistors RG 1, RG 2, and RG 3 are computer selected at initial checkout to provide overall system gain of 1, 10, and  $100 + .05\%$ .

The input amplifier is followed by a four-pole low-pass anti-aliasing filter. The characteristics of this filter include a transmission zero at the system sampling frequency (1MHz). The filter is adjusted for optimum phase linearity in the signal passband, ensuring good pulse response.

IC 4 in the transmitter is a 1 MHz crystal oscillator which is the clock for the system. IC 4 generates a sample/hold strobe, a load pulse for the parallel to shift register IC 8 and IC 7, and a start pulse for the A/D converter IC 5.

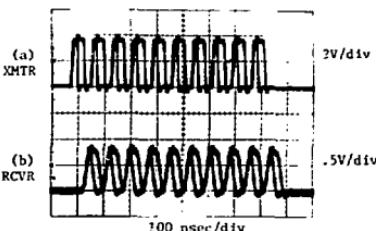

The process of A/D conversion and PDM encoding takes place as follows: On the trailing edge of the sample/hold strobe ( $\sim 50$  ns), the contents of the A/D converter are loaded into registers IC 7 and IC 8. At the same time, IC 5 begins A/D conversion (by successive approximation) of the input voltage. The A/D clock pulses from IC 5 are utilized to cause IC 7 and IC 8 to serially output the previously stored 10-bit word at a rate of approximately one bit per 80 ns. IC 9 converts this serial data to a succession of ten wide (52 ns) and narrow (27 ns) pulses. The PDM code is transmitted by means of V-mos transistor Q3 and the optical source S1. Figure 5(a) is an oscilloscope photograph of the encoded signa<sup>t</sup> at TPI. Transmitter input in this photo is a  $\pm$  full-scale triangle wave of approximately 100 Hz, so that wide and narrow pulses are seen as superimposed.

In the receiver of Fig. 4, IC 1 and IC 2 comprise a low-noise photo diode preamplifier with a bandwidth of approximately 30 MHz. The circuit, which is composed of very fast LM 359 "Norton" amplifiers, presents a very low ( $\sim 7$  ohm) input impedance to the photodiode without the use of feedback. The effect of input shunt capacitance is thus cancelled without the risk of instability. Response of the amplifier is shown in Figure 5(b). Layout of this amplifier is critical: A "ground plane" pc board is used.

After conversion to TTL levels by comparator IC 3, the serial data is decoded by IC 5 and self-clocked into registers 6 and 7. Retriggerable one-shot IC 4 clocks latches 8 and 9 at the end of each ten-bit word and also provides d-c restoration to the data signal via Q1. The inherent advantage of the self-clocking PDM digital code is seen here: decoding is accomplished by a single 40 nsec one-shot (IC 5).

FIG. 5. EAST RDM CODE

FIG. 4. LINE RECEIVER

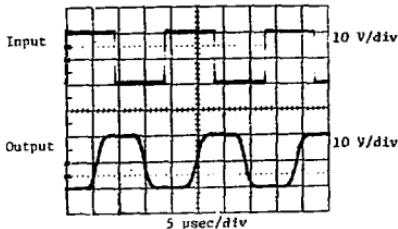

FIG. 6. OVERALL PULSE RESPONSE

The 10-bit DAC IC 10 converts the parallel binary input data, which is updated at a 1 MHz rate, to a proportional output current. The network at the input of IC 11 is a 5-pole low-pass filter with a nominal 3 db bandwidth of 300 kHz and essentially linear phase response. Buffer amplifier IC 12, with cross coupled output transistors, is suitable for driving either short lengths of unterminated cable or long terminated 75 ohm lines.

#### Construction

The wideband analog transmitter and receiver units were each packaged in a single width NIM module. High speed "ground plane" printed circuit boards were used. Although it would be physically possible to package two units in a single width module, this was not done because of thermal considerations. Non-standard  $\pm 15$  volt supplies are used which permit the filling of an entire NIM bin with transmitters or receivers. Provision is also made for operation with standard NIM supplies ( $\pm 12$ ,  $\pm 24$ v) where only a few transmitters or receivers are required.

#### Performance

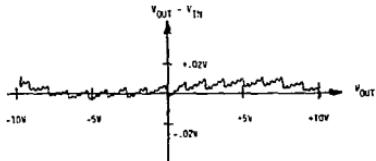

Tests on a prototype link showed that the combined overall error due to drift, noise, and non-linearity was less than  $\pm 1$  LSB over a temperature range of  $15^{\circ}\text{C}$  to  $30^{\circ}\text{C}$  ambient. Figure 7 is a plot of linearity versus DC input level. The AC performance of the link is shown in the oscilloscope photograph of Fig. 6. Overall response of the link to 50 kHz square waves shows negligible overshoot and a rise time of 2 usec. At the time of writing, production on twenty links was in process for use by the MFE group at LBL. Further testing and characterization will be done on these units.

#### Conclusions

The highest priority of this design was to achieve low DC drift and clean, wideband pulse performance in a 1-microsecond, 10-bit system. It was found that the use of digital processing could not only solve problems of drift and linearity inherent in FM and PWM systems (3)(4), but was capable of analog signal fidelity in no way inferior to previous designs. Distortions due to the digitizing process (e.g., "quantizing error") were suppressed so effectively as to be not visible on an oscilloscope at signal level 20 db below the maximum.

FIG. 7. OVERALL D.C. LINEARITY

Because AC pulse response was a prime consideration, phase linearity of the filters employed was most important. This resulted in a gradually sloping frequency response which is 3 db down at 200 kHz.

Just prior to the testing of the prototype at LBL, it was learned that the Dupont Fiber Optic cable used in this design, Type PFX-PIR-40, would be discontinued. A new type will be selected.

#### References

1. Stover, G.S. "A Precision Analog Fiber Optic Transmission System" (M.S. Thesis), LBL Engineering & Technical Services Division, LBL-13352

2. Lau, Norman C. "Results of Studies of Fiber Optic Links for MFTF". Proc. of 9th Symposium on Engineering Problems of Fusion Research, PP. 981-984, Oct. 26-29, 1981.

3. Cutsogeorge, G. "Wideband Fiber Optic Analog Data Link". Proc. of 9th Symposium on Engineering Problems of Fusion Research, PP. 1030-1032.

4. Dyer, G. R. "A Method for Transmitting Analog Data Over a Fiber Optic Link". Proc. of 9th Symposium on Engineering Problems of Fusion Research, PP. 1026-1029.

This work was supported by the Director, Office of Energy Research, Office of Fusion Energy, Development & Technology Division, of the U. S. Department of Energy under Contract No. DE-AC03-76SF00098.