CONF-9010220-5

CONF-9010220--5

DE91 002332

## A BIPOLAR MONOLITHIC PREAMPLIFIER FOR HIGH-CAPACITANCE SSC SILICON CALORIMETRY

C. L. Britton, Jr.

*Oak Ridge National Laboratory*

*P. O. Box 2008, Oak Ridge, TN 37831-6006*

E. J. Kennedy

*Dept. of Electrical and Computer Engineering*

*The University of Tennessee*

*Knoxville, TN 37996*

*and Oak Ridge National Laboratory*

W. M. Bugg

*Dept. of Physics*

*The University of Tennessee*

*Knoxville, TN 37996*

To be presented at the IEEE Nuclear Science Symposium

Crystal City, VA

October 25, 1990

### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

The submitted manuscript has been

authorized by a contractor of the U.S.

Government under contract No DE-

AC05-84OR21400. Accordingly, the U.S.

Government retains a nonexclusive,

royalty-free license to publish or reproduce

the published form of this contribution, or

allow others to do so, for U.S. Government

purposes.

MASTER

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

# A BIPOLAR MONOLITHIC PREAMPLIFIER FOR HIGH-CAPACITANCE SSC SILICON CALORIMETRY\*

C. L. Britton, Jr.<sup>♦</sup>, E. J. Kennedy<sup>†</sup>, W. M. Bugg<sup>†</sup>

<sup>♦†</sup>Oak Ridge National Laboratory

P. O. Box 2008, Oak Ridge, TN 37831-6006

<sup>†</sup>Dept. of Electrical and Computer Engineering

The University of Tennessee

Knoxville, TN 37996

<sup>†</sup>Dept. of Physics

The University of Tennessee

Knoxville, TN 37996

## Abstract

This paper describes a preamplifier designed and fabricated specifically to address the requirements of silicon calorimetry for the Superconducting Super Collider (SSC). The topology and its features are discussed in addition to the design methodology employed. The simulated and measured results for noise, power consumption, and speed are presented. Simulated and measured data for radiation damage effects as well as data for post-damage annealing are also presented.

## I. INTRODUCTION

The ever-increasing detector sizes necessary for large-volume calorimetry place severe requirements upon the associated interface electronics regardless of the detector media. For silicon calorimetry, the preamplifier must preserve the fast risetime intrinsic to the detector media while simultaneously sinking the large (100  $\mu$ A) leakage currents expected from the detector after several years of radiation damage during operation. The preamplifier must have a dynamic range from the charge due to a single minimum ionizing particle (MIP), approximately 36,000 electrons, to that of 5000 or more MIPs. In the case of high-capacitance detectors, the associated preamplifier is required to be designed for a variety of conflicting needs. The large detector capacitances (30 pF - 500 pF) present a difficult hurdle to the designer who desires the best possible signal-to-noise ratio. The capacitance also restricts the speed at which charge integration can be performed, a serious problem since SSC events can occur at 16 ns intervals. These two areas of performance can usually be improved for a given detector-preamplifier by simply increasing the current consumption of the preamplifier. The problem with this approach is that, in a large calorimeter like those proposed for the SSC, thousands of preamplifiers will be needed. Obviously, the preamplifier must be designed for low power consumption since small increases are greatly magnified for the overall system.

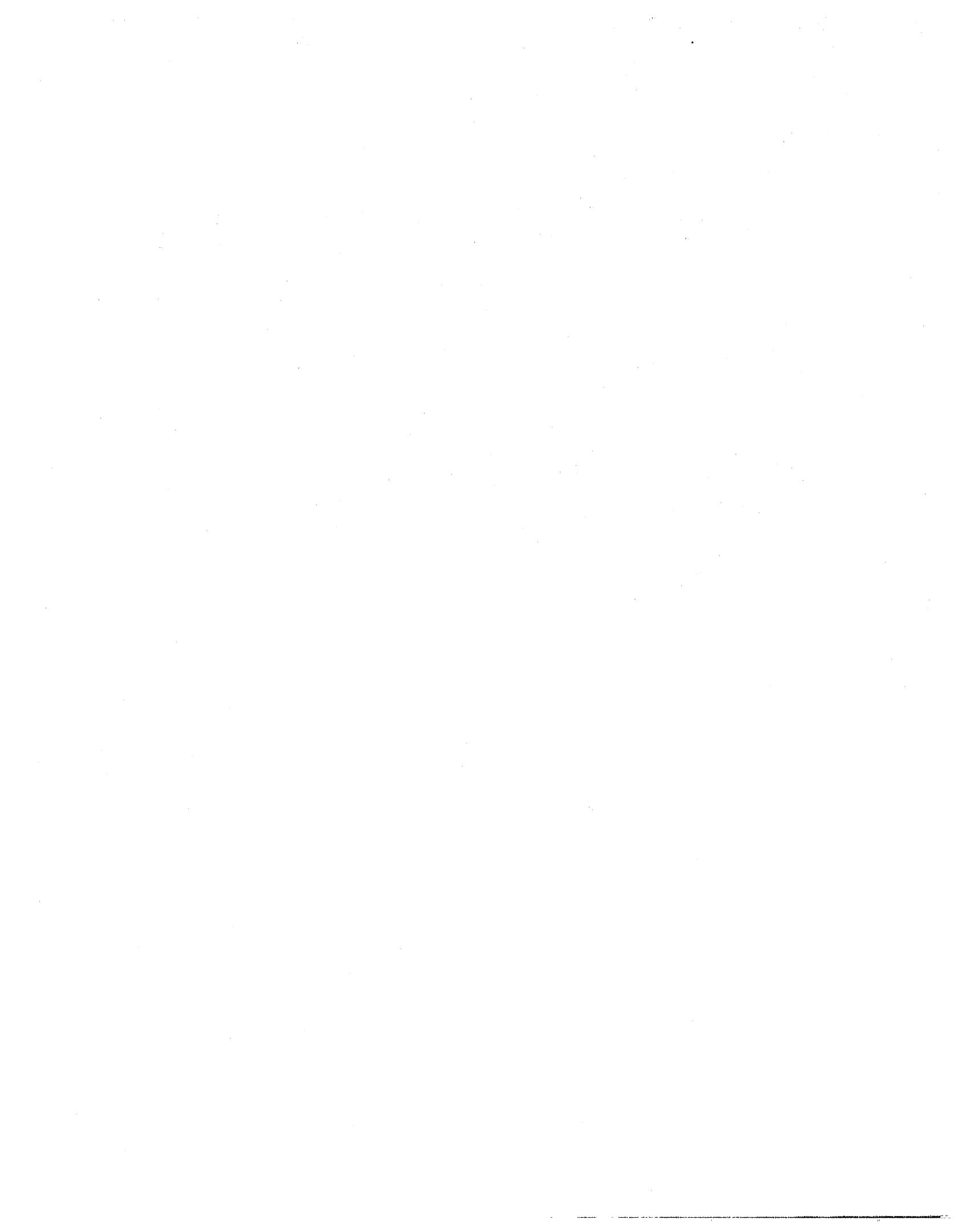

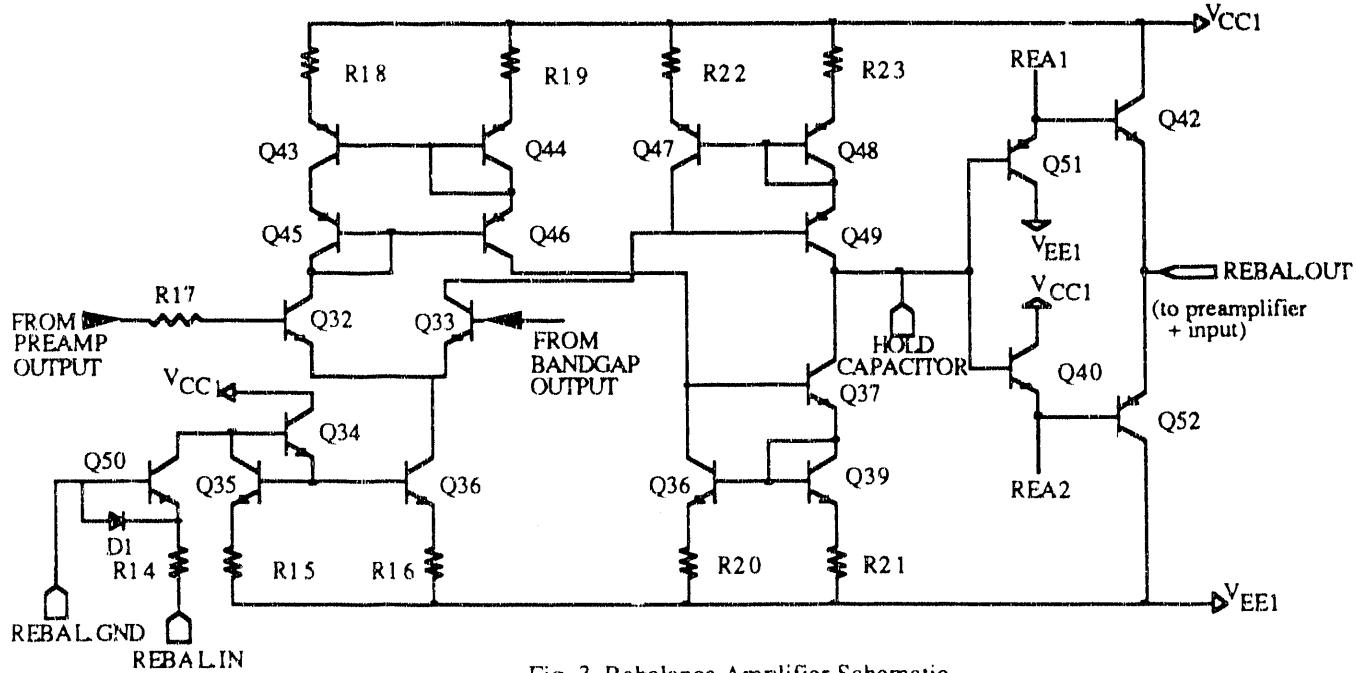

This paper will describe a preamplifier designed at Oak Ridge National Laboratory (ORNL) to specifically address the requirements of silicon calorimetry for the SSC. In particular, the preamplifier, illustrated in Fig. 1, employed a charge-sensitive configuration with a gated rebalance controller to correct for leakage current due to radiation damage in both the silicon detector and the large-area input bipolar transistor. An internal voltage reference was also implemented to allow an offset voltage at the output of the preamplifier to extend the dynamic range. Detailed schematics of the design are presented in Figs. 2, 3, and 4. Current feedback topology was chosen for this preamplifier. This type of feedback is traditionally not used in charge-sensitive applications but does have several advantages that make it appropriate for the application. Current feedback allows high slew-rates to be achieved with relatively low standing bias currents. Further, the series noise of the preamplifier was also relatively low compared with other topologies. The primary disadvantage was that of higher parallel noise when compared with more traditional topologies. This effect was reduced, however, since the preamplifier was designed for the short peaking times necessary for the SSC.

Fig. 1 Preamplifier - error amplifier

Block Diagram

\*Research performed at Oak Ridge National Laboratory, operated for the U. S. Department of Energy under contract DE-AC05-84OR21400 with Martin Marietta Energy Systems, Inc.

## II. CURRENT FEEDBACK PREAMPLIFIER TOPOLOGY

The initial design philosophy of this preamplifier was to develop a circuit for use with a silicon detector of  $\sim 100\text{pF}$  capacitance and exhibit a noise of  $<7500\text{ rms electrons (erms)}$  for a CR-RC peaking time of approximately 50 ns. The risetime was to be  $<10\text{ ns}$  to allow the use of shorter peaking times if desired. The power dissipation was required to be  $<10\text{ mW}$ , charge sensitivity was to be approximately  $0.2\text{ V/pC}$ , and maximum charge input was to be 17 pC which corresponds to approximately a 3000 MIP event (more recent developments at ORNL using  $\pm 5\text{ V}$  power supplies are capable of greater than 8000 MIPS). The power supply rails were chosen to be  $\pm 3.5\text{ V}$  for reduced power dissipation and because the high-frequency bipolar process used had low breakdown voltage ( $\text{BV}_{\text{CEO}} < 10\text{V}$ ).

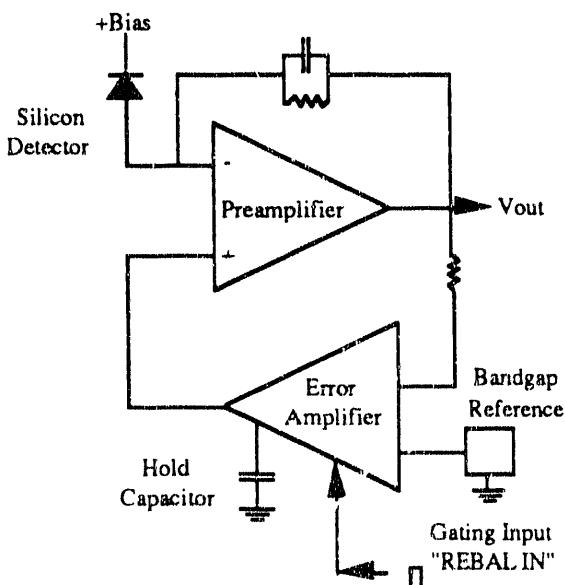

The topology chosen for the first preamplifier development was that of current-feedback (CF) described by Comlinear Corporation<sup>1</sup> and Kennedy<sup>2</sup>. Current-feedback has many advantages when compared with more traditional topologies such as differential input<sup>3</sup> or grounded source (grounded emitter)<sup>4,5,6</sup>. The most distinct advantages are short settling time, excellent loop stability at low closed-loop gains, and high bidirectional slew-rate for low static power

dissipation. The major drawback is that the input parallel noise (i.e., the equivalent noise current) is significantly larger than either of the other topologies by approximately the beta of the input device.

A general understanding of current-feedback can be obtained by reference to the electrical schematic of Fig. 2. Transistors Q8, Q11-Q13, and Q16, along with resistor R13 represent a constant-current source for the entire circuit. Current-mirrored transistors Q3 and Q19 define the currents for Q27 and Q28, which in turn define collector currents of Q29 and Q30 via emitter-base ratios. In the standard CF topology, the load resistors for Q29 and Q30 (R7 and R8) are Wilson current mirrors, which replicate IC29 and IC30 to the dominant node for the circuit, at the collectors of Q6 and Q21. Thus in a standard CF circuit, the input error current at the inverting input (equal to  $IE30 - IE29$ ) is equal to the current at the dominant node, which is available to charge the dominant node capacitance and, therefore, to define slew-rate. In this circuit (Fig. 2), we chose to use load resistors (R7 and R8) at the collectors of Q29 and Q30 to replace the normal Wilson current mirrors to provide additional current gain to the dominant pole, much larger voltage gain for the first stage and, therefore, lower overall input noise than with the standard CF topology.

Fig. 2 Current Feedback Amplifier Schematic

The inverting input for CF circuits offers a very low input resistance whereas the noninverting input has a reasonably large input resistance. As seen in Fig. 2, when looking into the inverting input, one sees  $r_{e29}||r_{e30}$ , or essentially  $130\Omega$  with  $I_{C29} = I_{C30} = 100\mu A$ . The paralleled Q29-Q30 inputs also mean that the series noise is determined by the parallel series noise of Q29-Q30; in the actual circuit this amounts to less than  $100\Omega$  input equivalent noise resistance. The primary advantage of this very low inverting-input resistance is that it is in parallel with the detector capacitance, thereby offering the capability of using quite large detectors (high capacitance) without seriously degrading the loop transmission (i.e., the loop gain) for the amplifier, since the time-constant  $r_{in}C_{det}$  is much less than with either a differential or a cascode input network. This translates into a more stable high-frequency amplifier, with a much enhanced gain-bandwidth product. Conversely, since Q29-Q30 in Fig. 2 are common-base stages with a current gain of only  $\alpha$  ( $\sim 1.0$ ), then the parallel input noise (i.e., the equivalent noise current) is much larger than that for other types of preamplifiers, being determined not only by the shot-noise of the base currents of Q29 and Q30 but also by base current noise of Q6-Q7 and Q21-Q22 as well as the thermal noise current of R7 and R8. Fortunately, for the short shaping times necessary for the SSC, the increased current noise should be acceptable.

### III. REBALANCE LOOP

One of the design goals of this project was to allow the detector to be directly coupled to the preamplifier, thus precluding the need for a bulky external coupling capacitor. The current flowing from the detector into the input and, subsequently, the feedback resistor of the preamplifier, shifts the dc bias point of the preamplifier as the detector current

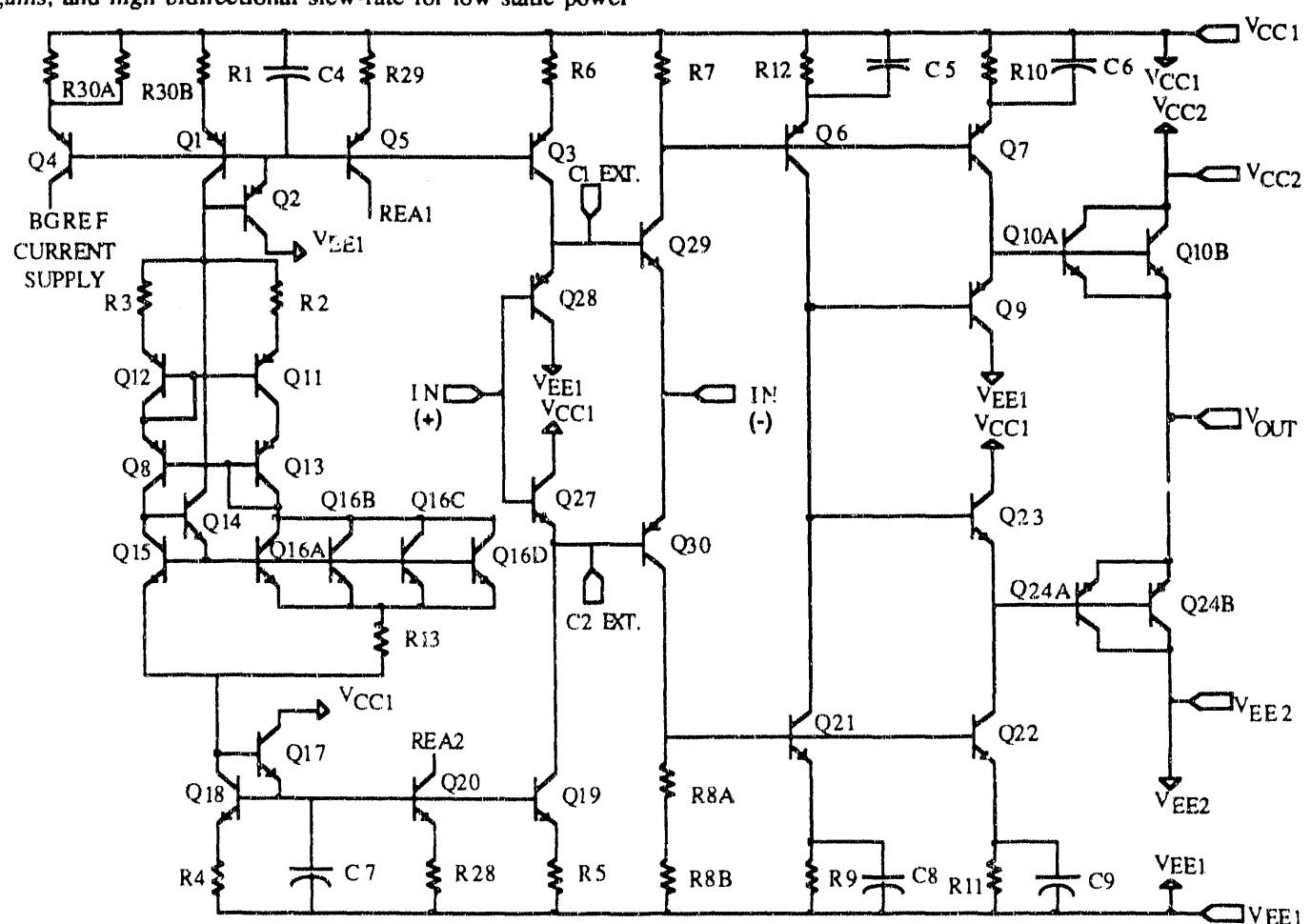

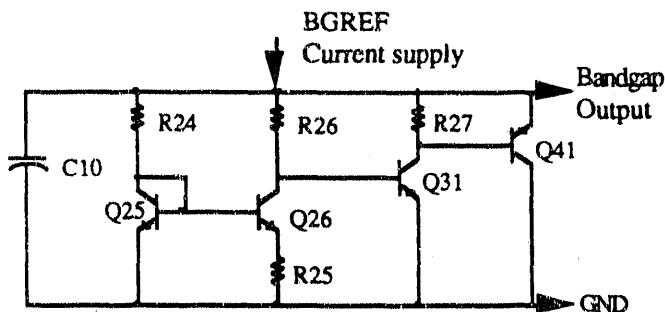

increases with progressive detector radiation damage. The shift in bias point causes two problems. The first and most apparent is that the output of the preamplifier moves closer to the negative supply rail (see Fig. 1). This reduces the output signal amplitude and, therefore, the dynamic range that can be processed prior to overload (the lower supply voltages required for low power dissipation only compound this problem). The second and less obvious, is that as bias point changes, the preamplifier gain changes because of the nonlinear nature of the transistors, resistors, and capacitors comprising the circuit, an effect normally described as differential nonlinearity<sup>7</sup>. One desirable feature of a preamplifier would be to provide a method of restoring the dc operating point with minimal effect upon the impulse response, noise, or power of the circuit. The circuit shown in Fig. 1 employs a gated rebalance amplifier (error amp) that samples the output for 10  $\mu s$  to 50  $\mu s$  every 40 ms and restores the preamplifier output to a value equal to the bandgap reference voltage which allows the preamplifier to continue to operate within its optimum range of performance despite increases in detector leakage current. The particular implementation shown in Fig. 3 will correct for up to 25  $\mu A$  of detector leakage current. The error amplifier of Fig. 3 is basically a gated transconductance amplifier, with a low leakage unity-gain buffer added. A 'HIGH' (+3.5 V) input at the "REBAL IN" terminal will bias Q32-Q33 into an active linear mode, thereby biasing Q49 and Q37 as well. The error voltage stored on the hold capacitor is that required to restore  $V_{OUT}$  of the preamplifier to +1.6 V, the dc reference value of the bandgap reference (Fig. 4). This approach could be adapted for much greater leakages by varying the design and the operating parameters. The performance parameters stated above are typical only for this particular design.

Fig. 3 Rebalance Amplifier Schematic

Fig. 4 Bandgap Reference Schematic

#### IV. IRRADIATION TESTING OF DEVICES

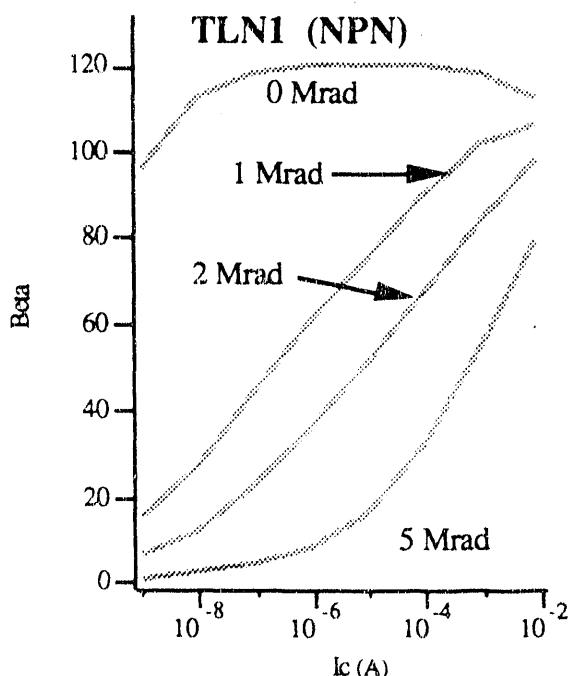

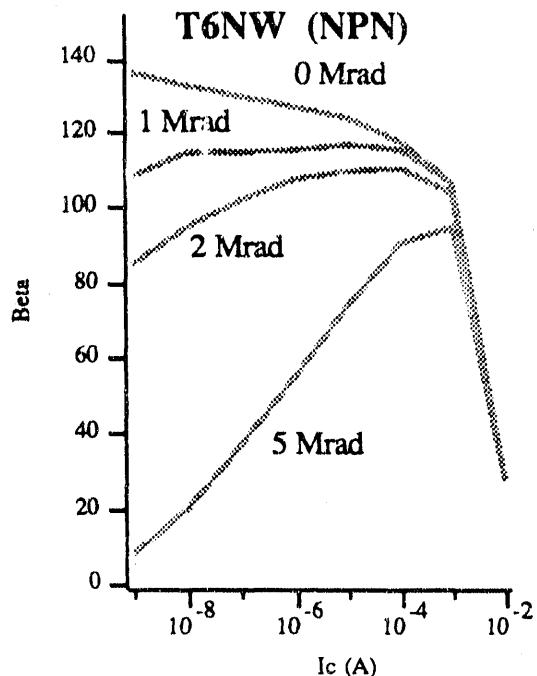

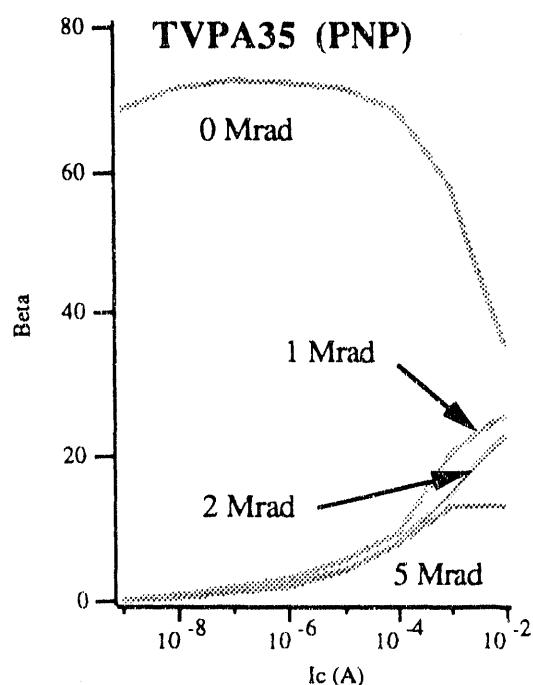

After evaluation of the circuit requirements, we chose to fabricate the overall circuit by using the VTC, Inc. high-frequency bipolar process. The VTC VJ900 npn transistors have a maximum gain-bandwidth product,  $fT_{max}$ , of ~ 6 GHz, while pnp's have  $fT_{max}$  ~ 1.5 GHz. Some of the devices available in the VTC VJ900 arrays were available on a separate chip that could be used for pre-design testing. The chips were used for two types of testing; SPICE model confirmation and radiation effects SPICE model correction. The non-irradiated chips were characterized for dc parameters using the Hewlett-Packard Model 4145B Semiconductor Parameter Analyzer and were generally found to be within quoted SPICE parameters. The chips were then irradiated with 1, 2, and 5 Mrads of  $^{60}\text{Co}$  Gamma rays and retested. From these data, new SPICE models were obtained to more accurately describe the process after irradiation, and thus allow modelling and design of a robust chip. The measurements of  $h_{FE}$  vs.  $I_C$  are presented in Figs. 5, 6, and 7 for 1, 2, and 5 Mrad<sup>8</sup>. Table I presents the Early voltage measurements for non-irradiated devices and for 5 Mrad irradiation.

Fig. 5 VTC TLN1 Beta vs. Collector Current for 0 Mrad to 5 Mrad

Fig. 6 VTC T6NW Beta vs. Collector Current for 0 Mrad to 5 Mrad

Fig. 7 VTC TVPA35 Beta vs. Collector Current for 0 Mrad to 5 Mrad

Table I

VTC Early Voltage Measurements With Gamma Dose

| Type   | Dose Mrad | $I_C$ ( $\mu$ A) | $V_A$ (V) | $V_A$<br>% Diff. |

|--------|-----------|------------------|-----------|------------------|

| TLN1   | 0         | 4.9              | 26.1      |                  |

|        | 5         | 4                | 17.5      | -33.0            |

| TLN1   | 0         | 22.5             | 29        |                  |

|        | 5         | 23               | 23.9      | -17.6            |

| T6NW   | 0         | 67               | 33.1      |                  |

|        | 5         | 66               | 30.1      | -9.0             |

| TVPA35 | 0         | 3.5              | 10.7      |                  |

|        | 5         | 2.7              | 7.6       | -28.8            |

## V. RESULTS

The preamplifier speed, noise, and power were measured pre- and post-radiation at 1 and 5 Mrad gamma exposures. The simulated pre-rad risetime was 5 ns and noise was 5975 erms for 60 ns CR-RC peaking time. The simulated pre-rad power dissipation was 7 mW. After 5 Mrad gamma dose, the simulated risetime was 8 ns, noise was 7187 erms, and dissipation was 2.3 mW. These values compare favorably to the measured values shown in Table II, except the post-rad risetime was worse than the simulation. The changes in risetime and power dissipation are believed to be due to a shift in the operating point of the biasing circuitry. The reduced power indicated that supply currents had dropped causing the circuit to become 'starved'. The annealing process caused the biasing to return somewhat to normal and, therefore, bring the circuit closer to initial performance. The annealing cycle was tested because collaborations had expressed interest in an annual anneal cycle to repair radiation damage in both detectors and electronics. From the perspective of preamplifier performance, this would appear to be a useful process.

Table II

Results of Tests

| Condition                          | Risetime | Power<br>(+/-3.5 V) | ENC<br>(60 ns Peaking) |

|------------------------------------|----------|---------------------|------------------------|

| Pre-rad                            | 6.3 ns   | 7.5 mW              | 6300 erms              |

| 5.3 Mrad                           | 20 ns    | 2.1 mW              | 6600 erms              |

| 5.3 Mrad<br>4 hrs.<br>100°C anneal | 9 ns     | 5 mW                | 6800 erms              |

## VI. FUTURE WORK

This preamplifier was designed specifically for a detector size of 100 pF. A need for several different detector sizes with capacitances ranging from 30 pF to >400 pF has been subsequently identified. ORNL personnel have designed seven preamplifiers using the HARRIS Semiconductor VHF dielectrically isolated process for use with these detectors. Results from this development will be reported at a later date.

## VII. CONCLUSION

A preamplifier designed at ORNL specifically for high-capacitance silicon calorimetry has been described. The pre- and post-radiation performance has been discussed for both the preamplifier devices and the preamplifier itself.

## VIII. ACKNOWLEDGEMENTS

The authors are indebted to Bryce Gray for his help in the device testing, Melanie Kemper and Cheryl Russell for their help in figure preparation, Shirley Shugart for her poster preparation, and especially to Norma Hensley for her tireless patience in preparing the manuscript and final copy.

## IX. REFERENCES

- [1] Application Note, "Current-Feedback Amplifiers", 1989 Comlinear Databook, pp. 12-3 through 12-8.

- [2] John Williams [Ed.], Analog Circuit Design: Art, Science, and Personalities, Butterworth Publications, 1991.

- [3] Paul R. Gray and Robert G. Meyer, Analysis and Design of Analog Integrated Circuits, pp. 194-211, John Wiley and Sons (1984).

- [4] V. Radeka, "Signal, Noise, and Resolution in Position-Sensitive Detectors", IEEE Trans. Nucl. Sci., NS-21, Feb. 1974 (51-64).

- [5] Neven Karlovac and Terry L. Mayhugh, "A Fast Low-Noise Charge Preamplifier", IEEE Trans. Nucl. Sci., NS-24, No. 1, Feb. 1977 (327-334).

- [6] Charles L. Britton and Thomas H. Becker, "Design and Characterization of a Low Power Consumption, HPGe Spectrometer", IEEE Trans. Nucl. Sci., NS-32, No. 1, Feb. 1985 (36-40).

- [7] Glenn F. Knoll, Radiation Detection and Measurement, p. 659, John Wiley (1989).

- [8] R. B. Gray, "The Effects of Gamma Radiation On JFET and Bipolar Transistors With Applications To The SSC", a thesis presented for the Master of Science degree, the University of Tennessee (1990).

**END**

**DATE FILMED**

11/27/90