30

6/17/89 053

## TIMING AND RF SYNCHRONIZATION FOR FILLING PEP/SPEAR WITH THE SLC DAMPING RINGS\*

M. T. RONAN, D. J. LAMBERT AND K. L. LEE

Lawrence Berkeley Laboratory, Berkeley, California 94720

and

D. R. BERNSTEIN, P. CORREDOURA, R. K. JOBE, M. C. ROSS, B. ROSTER, J. VANCRAEYNST AND G. ZAPALAC

Stanford Linear Accelerator Center, Stanford University, Stanford, California 94309

## ABSTRACT

An innovative timing and RF synchronization system has been built and commissioned which allows the direct injection of 1 mm  $\sigma_x$ ,  $e^+$  or  $e^-$  bunches from the SLC Damping Rings ( $\nu_{RF} = 714$  MHz) into the storage rings PEP ( $\nu_{RF} = 353$  MHz) and SPEAR ( $\nu_{RF} = 358$  MHz). The required relative stability of these oscillators is  $10^{-9}$  since the beams may be stored in each damping ring (DR) for up to 0.2 sec., during which no timing correction is made, and must be delivered within a 0.5 nsec window. This stability has been obtained by phase-locking the storage ring RF to the LINAC-DR master oscillator. In order to obtain bunched beams for acceleration in the LINAC 10.5 cm RF structure while maintaining the storage ring timing requirements, the Subharmonic Buncher and Damping Ring RF are phase-shifted using GaAs digital circuitry. This paper describes (1) the phase-locked loops, (2) the RF distribution system, (3) the S-band resettable dividers and (4) the interpulse timing system components used in this project.

## 1. INTRODUCTION

Recently, the PEP and SPEAR  $e^+e^-$  storage rings at the Stanford Linear Accelerator Center have been operated again for High Energy Physics. With the upgrade of the linac for operation of the SLC having been completed, the new accelerator systems including an Electron Gun with a Subharmonic Buncher, an off-axis high-yield Positron Source as well as electron and positron Damping Rings, are now being used to fill the storage rings. Using the high intensity beams from the Electron Gun and Positron Source and the low emittances obtained using the Damping Rings in conjunction with the Subharmonic Buncher which compresses the electron pulse from the gun to fill only one linac RF bucket, the storage rings were being filled efficiently in minutes. Several improvements to the linac timing and control systems, which were needed in order to allow the new accelerator systems to be controlled by the storage rings and to synchronize the storage ring filling operation with the SLC damping rings, are described in this paper.

## 2. SLAC TIMING SYSTEM

The LINAC Timing System<sup>1</sup>, as modified for the Stanford Linear Collider (SLC) project, provides a multitude of programmable trigger signals with a jitter of less than 100 psec with respect to the beam and the Klystron 2.856 GHz RF over the three kilometer length of the linear accelerator. Using sub-harmonics of 476 MHz for the linac Master Oscillator to drive the RF reference lines via a temperature stabilized Main Drive Line (MDL) and 8.5 MHz for the Damping Ring revolution frequency, the timing system was designed to provide triggers at a fixed time with respect to beams in the damping rings and at a fixed phase of the 360 Hz line frequency to reduce power line AC effects in accelerator operation.

Basically, a trigger signal generated on the first edge of the 8.5 MHz falling within a gate derived from the 360 Hz zero-crossing in the Master Trigger Generator (MTG) produces a fiducial which is superimposed on the 476 MHz signal in the Fiducial Generator and is then transmitted on the MDL. At each of 30 sectors, the composite signal is picked-off and amplified for multiplication to 2.856 GHz by the Klystron subboosters. A fiducial detector unit (FIDO) scales down the reference RF to generate a reasynchrotron 119 MHz clock with a missing-pulse marker for resettable delay counters.

\*Work supported by Department of Energy contracts DE-AC03-76SF00098 and DE-AC03-76SF00515.

Programmable Delay Units<sup>2</sup> (PDU's) use the 119 MHz signal to generate precision trigger signals in delay increments of 8.4 nsec for up to several interlaced beams.

The PEP and SPEAR storage rings operate at RF frequencies of 353.210 MHz and 358.540 MHz, respectively. Unfortunately, these frequencies are not harmonics of the linac RF frequency, 476 MHz, so that the storage rings are not simply locked to the linac Master Oscillator. During storage ring filling, in the past, the linac fiducial pulse was derived from the timing of the particular storage ring RF bucket to be filled. The PEP and SPEAR timing systems provide a 1.7-msec-long burst of pulses, synchronized to the revolution of the particular bucket being filled, at frequencies corresponding to the revolution frequencies of 136 kHz and 1.28 MHz, respectively. These ~10 MHz bandwidth signals are transmitted upstream on the MDL to the linac injector where the first pulse within a power line zero-crossing gate generates a fiducial pulse which triggers the linac timing system and selects the referred storage ring turn. Just prior to beam time, a pattern reference pulse is sent by the storage ring timing system to the injector where it is used to determine the actual timing of the gun trigger.

Electrons and positrons from an in-line positron source were simply timed to the storage ring pattern reference pulse and delivered within the selected 2.8 nsec RF bucket window; however, each 1-2 nsec thermionic gun pulse would fill several linac 2.856 GHz RF buckets, thus dominating the timing error in filling a storage RF bucket. In addition, the relatively low yield of positrons with large beam emittance from the in-line target made positron filling quite a challenge. The new timing system eliminates the need for the old positron source and takes advantage of the high intensity, low emittance SL<sup>+</sup> beams from the damping rings.

## 3. TIMING SYSTEM UPGRADE

We have designed, built and operated the electronic timing system required to fill PEP and SPEAR using beams from the SLC Damping Rings. The timing constraints were that all linac pulses occur at a fixed phase of the 360 Hz power line cycle (as is done for other modes of linac operation), that the CW devices in the linac (Subharmonic Buncher and Damping Rings) be phase-shifted to the S-Band bucket chosen by the storage ring burst, that the storage ring master oscillators remain phase stable with respect to the linac RF system and, finally, that the beam be delivered to the storage ring within 0.3 nsec of the requested time at pulse rates of 10-60 Hz. Within our scheme, for initial operation with a minimal impact on fill times, the linac is operated with only one bunch at a time since fully interlaced multibunch operation would require phase shifting the beam in the damping rings in order to maintain synchronization with the storage rings and the 360 Hz line frequency. The damping times are maintained to be a fixed number of damping ring revolutions so that the damping rings can be treated as delay lines allowing the damping times to be adjusted to match 360 Hz zero-crossing time intervals.

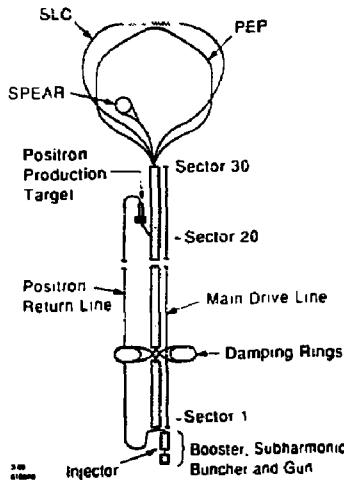

For PEP/SPEAR filling, we operate the front two-thirds of the linac as closely as possible to SLC operation. Following Fig. 1, a timing reference signal is sent from the storage rings to the Injector where the CW RF system controlling the Subharmonic Buncher (SHB) and Damping Rings is phase-shifted and a linac fiducial is generated. About 1 msec later, the gun is fired at a fixed phase of the SHB by Trigger Gate and Synchronized (TGAS) module to produce electrons and store them in the electron damping ring. At a subsequent power line cycle, the electrons are extracted, accelerated, and delivered for electron filling or targeted at Sector 20 to produce positrons which are then returned to the positron damping rings for

Fig. 1. Schematic layout of the SLAC accelerator complex showing the SLC linac systems including the Damping Rings and off-axis Positron Source, and the PEP and SPEAR storage rings in addition to the SLC AHC's and Final Focus.

positron filling; a tertiary trigger extracts and delivers the positrons at a later 360 Hz zero-crossing.

The upgrades, divided into four major subsystems associated with phase-locking the storage rings, the RF distribution, the fiducial generation and RF synchronization using GaAs digital IC, are described below. A detailed description of the GaAs microstrip circuits has been published<sup>3</sup> and is only reviewed briefly in this paper.

### 3.1 Phase-Locking the PEP and SPEAR Master Oscillators

The storage ring master oscillators must be stable with respect to the linac RF system to maintain subnanosecond timing over a period of tens of milliseconds while the beam is stored in the damping rings. We have chosen a scheme by which the CW RF system is phase-shifted on a pulse-to-pulse basis allowing fill rates of 30 Hz and higher for simultaneous filling of PEP and SPEAR. In order to maintain timing accuracy during the damping period, the storage ring master oscillators are phase locked to the linac RF to obtain stability of one part in  $10^9$ .

In order to lock the PEP and SPEAR RF, a subharmonic in common with the linac Master Oscillator needed to be found. The division ratios were determined by requiring that the locked storage ring RF differ by less than a few hundred Hz from the nominal design frequencies. This leads to the following division schemes:

| Storage Ring | Frequency / Divisor | Common Subharmonic | Linear RF / Divisor |

|--------------|---------------------|--------------------|---------------------|

| PEP          | 353.2102 MHz / 233  | 1.5159 MHz         | 476 MHz / 314       |

| SPEAR        | 358.540 MHz / 873   | 410.7 kHz          | 476 MHz / 1159      |

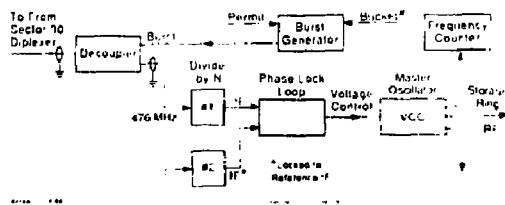

A block diagram of the Phase-Lock electronics is shown in Fig. 2. The linac 476 MHz reference and storage ring RF signals are divided by a programmable "Divide-by-N" circuit to their common intermediate frequency (IF). The Phase-Locked Loop (PLL) circuit uses a digital phase detector to compare the storage ring and linac intermediate frequencies and then applies an error voltage to the storage ring Voltage Controlled Oscillator (VCO) to correct for relative drifts. The control voltage

Fig. 2 PEP/SPEAR Phase Lock electronics block diagram

is the sum of the output voltage of a 12-bit DAC and of the phase/frequency comparator output of a MC4044 phase detector amplified by an active filter. During locked operation the programming of the DAC is continuously controlled in order to keep the DC component of the active filter output voltage equal to zero to minimize unlocking transients. Control circuits are used in the PLL to allow an operator to unlock/ relock the storage ring oscillator. When unlocked, the operator is allowed to ramp the frequency up or down at a rate of less than 100 Hz, see for chromaticity measurements, and to relock for normal storage ring operation without losing beams.

### 3.2 RF Distribution System

We transmit the linac RF reference from the linac Master Oscillator to both the PEP and SPEAR rings. Referring back to Fig. 1, the linac 476 MHz reference and fiducial is carried on the Main Drive Line from the Injector to a "Sector 30 Diplexer" unit at the downstream end of the linac. The Diplexer, a bidirectional coupler between the MDL and the storage rings, picks off, amplifies, and sends the composite signal down a 3/4-inch Heliax cable to PEP and SPEAR. At the storage ring end, a "PEP/SPEAR Decoupler" unit separates the 476 MHz and fiducial signals from the composite signal and amplifies them for phase-locking and diagnostic use. Using the same Heliax cable, the Decoupler transmits the "Burst" timing reference in the opposite direction to Sector 30 through a tandem 90° hybrid circuit arrangement.<sup>4</sup> At Sector 30, the Diplexer amplifies and couples the Burst signal onto the MDL for transmission upstream to the Injector fiducial generator and RF synchronization electronics.

### 3.3. Fiducial Generation

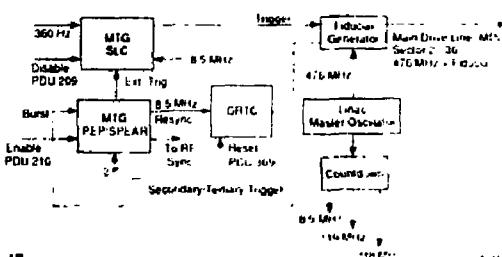

The linac Timing System is driven by the Master Trigger Generator (MTG) and the Fiducial Generator in the Injector alcove. A block diagram of the fiducial generation system is shown in Fig. 3. The MTG generates a timing pulse on an edge of the 8.5 MHz clock for SLC operation.

Fig. 3. Image Fiducial Generation System block diagram

For PEP/SPEAR filling, the SLC MTG was modified to allow disabling by the SLC control system, and a new PEP/SPEAR MTG was built which generates a timing pulse at a chosen zero crossing of the storage ring burst. The timing

Fig. 4. RF Synchronization electronics block diagram.

pulse is required to be at a fixed phase of the 360 Hz power line zero crossing for both SLC operation and storage ring filling.

The new PEP/SPEAR MTG uses a 360 Hz gate from the SLC MTG and the storage ring Burst to generate linac primary fiducials required to produce and store electrons. Using the 476 MHz reference, the PEP/SPEAR MTG generates an additional 8.5 MHz signal resynchronized to the storage ring reference for use by a Damping Ring Turn Counter (DRTC) module (a PDU<sup>2</sup> modified to operate at 8.5 MHz). The DRTC counts the number of damping ring revolutions with the resynchronized 8.5 MHz clock and then generates a secondary fiducial to either deliver electrons to the storage ring or produce positrons, depending on the accelerator beam code. The DRTC generates a tertiary fiducial for positron filling after a second fixed delay measured by the 8.5 MHz clock.

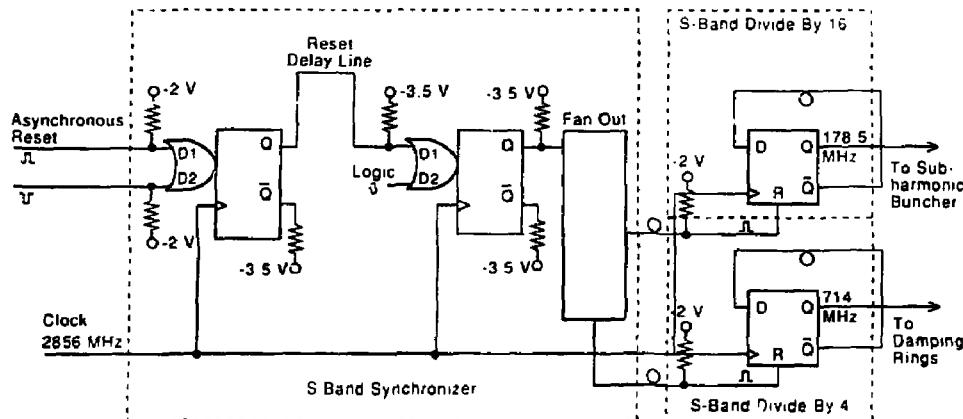

#### 3.4 Linac/Damping Ring RF Synchronization

Precise control of the linac CW-RF system is required for filling the storage rings since the timing and bunching of the beam are controlled by the RF system and not by the triggers from the Fiducial Generation system. Although the PEP and SPEAR Master Oscillators were phase locked to the linac Master Oscillator, phase shifting of the CW-RF is required for high repetition-rate filling at a fixed phase of the 360 Hz power line. A block diagram of the RF synchronization system, which allows phase-shifting of the CW devices to the nearest S-Band bucket for PEP/SPEAR filling, is shown in Fig. 4.

Using recently developed GaAs Master/Slave D-Type Flip-Flops, we have built<sup>3</sup> resettable frequency divider circuits operating at the linac Klystron RF frequency (2.856 GHz) which divide the clock frequency by 4 or 16 to generate the 714 MHz and 178.5 MHz needed for driving the Damping Ring (DR) RF and the Subharmonic Buncher (SHB), respectively. A separate GaAs unit synchronizes the burst timing reference from the storage rings to the 2856 MHz clock before it is distributed as a react to the DR and SHB dividers to insure synchronous resetting, as shown in Fig 4. The synchronizer effectively selects the linac RF bucket that matches the beam timing required for filling, and then resets both GaAs dividers to phase shift the CW-RF systems to the same RF bucket, thus maintaining synchronous operation within the linac accelerator systems. When PEP and SPEAR filling has been completed, a trigger signal from the linac synchronous timing system is used to reset the RF system for normal SLC operation.

#### 4. OPERATIONAL EXPERIENCE

We have successfully used the upgraded timing system to fill both the PEP and SPEAR storage rings using bunched beams

from the SLC Damping Rings. Using the GaAs digital circuits, the CW RF for the Subharmonic Buncher and the Damping Rings were phase-shifted to the chosen S-Band RF bucket with a relative one-bucket, phase shift error rate between the SHB and DR RF of less than a few percent. Several different beams were routinely run in parallel to allow interleaved filling of PEP and SPEAR.

The PEP and SPEAR Master Oscillators, were successfully phase-locked to the linac Master Oscillator to provide long term stability of  $10^{-9}$  without interfering with colliding beam operation. Beam position monitor displays of the stored beams verified that the correct RF bucket of the rings was being filled. The measured accuracy of the delivered beams is close to the expected 350 psec spread due to the linac 2.856 GHz RF system.

#### ACKNOWLEDGMENTS

The conceptual design of the Timing System upgrades for filling the PEP and SPEAR storage rings was defined by the authors and J. Fox, R. Hettel, J. Judkins, A. Odian, and H. Schwarz. We acknowledge the efforts of E. Plouviez for the design of the prototype phase-lock circuitry and R. Hettel for help in selecting microwave components for the RF distribution system. We would like to thank E. Bloom, V. Brown, R. Cassell, E. Paterson, J. Sodja and W. Toki for encouragement and help in installing, testing and commissioning the various electronics systems. In the electronics design, we have benefited from useful discussions with M. Birk, K. Crook, R. Larsen, E. Linstadt, L. Paffrath, J.-L. Pellegrin and H. Schwarz.

#### REFERENCES

1. L. Paffrath *et al.*, "A New Timing System for the Stanford Linear Collider," *IEEE Trans. Nucl. Sci.* NS-32, No. 1, 84 (1985).

2. E. Linstadt, "A Programmable Delay Unit Incorporating a Semi-Custom Integrated Circuit," *IEEE Trans. Nucl. Sci.* NS 32, No. 5, 2112 (1985).

3. M. T. Ronan, K. L. Lee, P. Corredoura and J. G. Judkins, "Gallium Arsenide Digital Integrated Circuits for Controlling SLAC CW RF Systems," *IEEE Trans. Nucl. Sci.* NS 36, No. 1, 662 (1989).

4. Microwave Component catalog, No. 17A, *RF/IF Diplexer circuit*, Anaren Microwave, Inc., 6635 Kirkville Road, E. Syracuse, N. Y. 13057.

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.