27

10-15-99

240715

240715

ORNL/TM-6922

MASTER

## An Intelligent CAMAC I/O Module Based on the Signetics 8X300 Microcontroller

G. W. Turner

R. W. Hendricks

OAK RIDGE NATIONAL LABORATORY

OPERATED BY UNION CARBIDE CORPORATION · FOR THE DEPARTMENT OF ENERGY

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

Printed in the United States of America. Available from

National Technical Information Service

U.S. Department of Commerce

5285 Port Royal Road, Springfield, Virginia 22161

NTIS price codes—Printed Copy: A04 Microfiche A01

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States nor any agency thereof, nor any of their employees, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for any third party's use or the results of such use of any information, apparatus, product or process disclosed in this report, or represents that its use by such third party would not infringe privately owned rights.

# MASTER

ORNL/TM-6922

Contract No. W-7405-eng-26

Solid State Division

AN INTELLIGENT CAMAC I/O MODULE BASED ON THE ~~SIGNETICS~~ 8X300 MICROCONTROLLER\*

G. W. Turner

Instrumentation and Controls Division

and

R. W. Hendricks

Metals and Ceramics Division

National Center for Small-Angle Scattering Research\*\*

Oak Ridge National Laboratory

Oak Ridge, Tennessee 37830

Date Published: September 1979

**NOTICE**

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

\*Research sponsored by National Science Foundation, Grant No. DMR-77-244-58 under Interagency Agreement No. 40-637-77 with the Department of Energy.

\*\*Operated by Union Carbide Corporation under contract W-7405-eng-26 with the U. S. Department of Energy.

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

## CONTENTS

|                                                              | <u>Page</u> |

|--------------------------------------------------------------|-------------|

| Abstract . . . . .                                           | 1           |

| I. Introduction . . . . .                                    | 2           |

| II. The 8X300 Microcontroller . . . . .                      | 4           |

| III. Introduction to CAMAC . . . . .                         | 8           |

| IV. Overview of the Module . . . . .                         | 9           |

| V. Detailed Description . . . . .                            | 18          |

| A. Block Diagram . . . . .                                   | 18          |

| B. LAM/Status Logic . . . . .                                | 21          |

| C. Read Group 1/Group 2 and Function Decode . . . . .        | 23          |

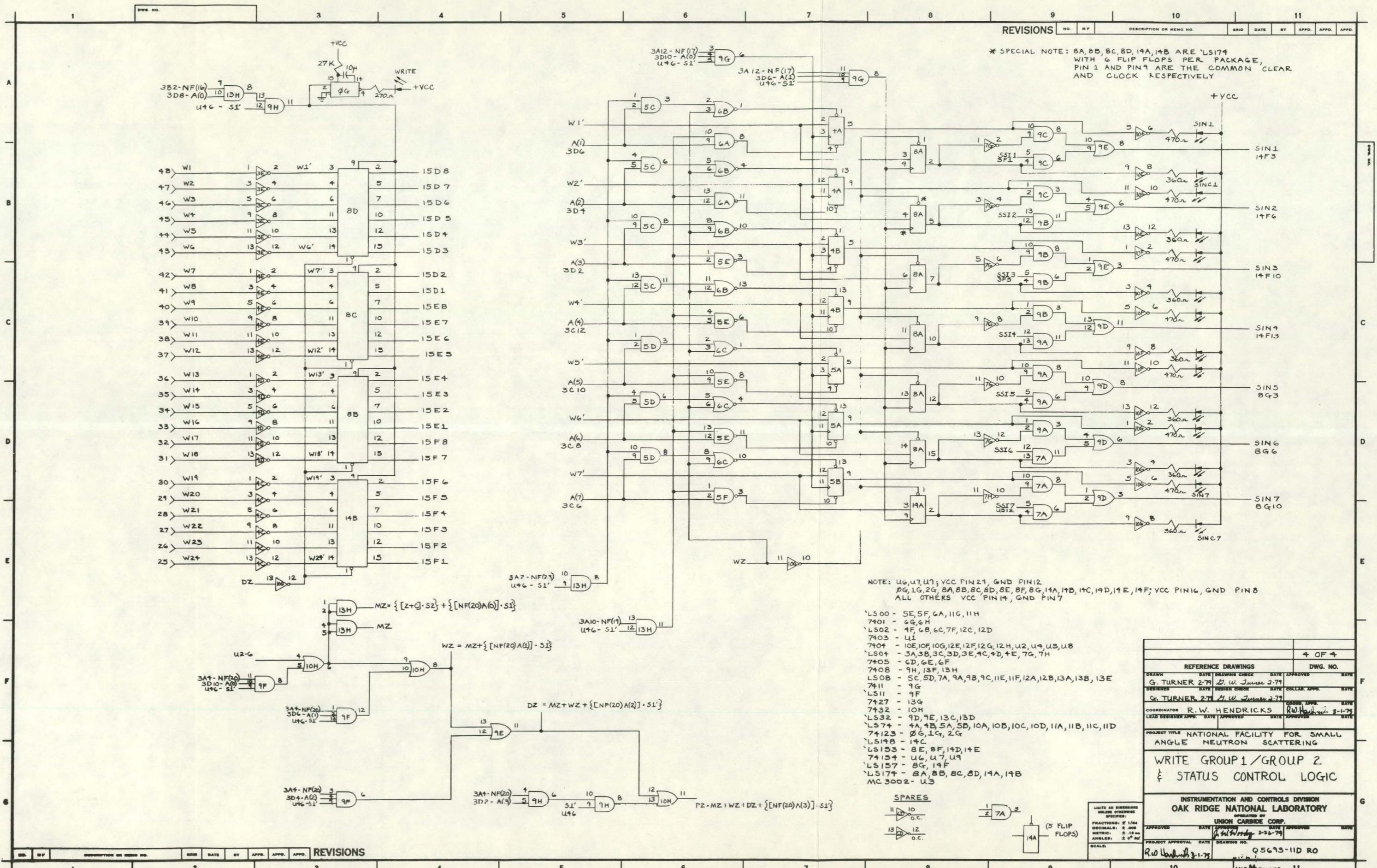

| D. Write Group 1/Group 2 and Status Control Logic . . . . .  | 26          |

| VI. Diagnostic Software . . . . .                            | 29          |

| VII. Acknowledgments . . . . .                               | 30          |

| VIII. References . . . . .                                   | 31          |

| IX. Appendices . . . . .                                     | 33          |

| A. Detailed Chip Coordinate Layout for Interface Board . . . | 35          |

| B. 8x300 Microcontroller Diagnostic Software . . . . .       | 37          |

| C. Host Computer Diagnostic Software . . . . .               | 41          |

| D. Circuit Diagrams . . . . .                                | 51          |

# AN INTELLIGENT CAMAC I/O MODULE BASED ON THE SIGNETICS 8X300 MICROCONTROLLER

G. W. Turner\* and R. W. Hendricks\*\*

Oak Ridge National Laboratory

Oak Ridge, Tennessee 37830

## ABSTRACT

An intelligent CAMAC I/O module based on the Signetics 8X300 microcontroller has been developed. Sixteen 8-bit I/O ports have been utilized; eight are dedicated for data transfers with external devices and/or processes and eight are dedicated to communication with the CAMAC dataway. Separate status and data registers are provided. The input status port (SIN) can receive up to seven individual signals from external devices or the host computer while the output status port (SOUT) can be used to provide up to seven internally graded LAMs and one bit can be used to generate a Q-response for termination of block transfers. Diagnostic software has been developed to operate on the host computer which fully tests all implemented instructions. In our application the device is used in a high-speed memory mapping scheme for data acquisition with a two-dimensional position-sensitive detector system.

---

\*Instrumentation and Controls Division

\*\*Metals and Ceramics Division

## I. INTRODUCTION

The past decade has brought rapid and profound changes to digital electronics and as a result to the procedures and techniques of data acquisition and manipulation in experimental research. The instrument described in this report, an intelligent CAMAC I/O module based on the Signetics 8X300 microcontroller, was developed for use in mapping two-parameter data gathered with a two-dimensional position-sensitive neutron proportional counter into the memory space of a general purpose 16-bit minicomputer. However, we have attempted to keep the design of the module completely general in order that it be able to serve as wide a range of applications as possible.

The Signetics<sup>1</sup> 8X300 microcontroller is the only 8-bit microprocessor built from bipolar technology, and allows 16-bit instructions to be fetched, decoded and executed in 250 ns. It has a repertoire of 8 instructions which are designed for testing status lines, setting or resetting control lines and performing high-speed I/O. With some of its 8-bit I/O ports dedicated to external use and some utilized for interfacing the CAMAC dataway, this unit is ideally suited for high speed, programmable bit-oriented data manipulation.

Our initial experience with the 8X300 was in the development of the ORNL 10-m small-angle x-ray scattering camera as described by Hendricks.<sup>2,3</sup> Here the microcontroller, as implemented by Scientific MicroSystems<sup>4</sup> in their SMS 300 series microcontrollers, was interfaced directly to the I/O bus of a ModComp II 16-bit general purpose minicomputer using standard model 4801 general purpose controllers. Details of the interface are given elsewhere.<sup>5,6</sup> In this application, the 8X300 microcontroller serves

several functions. First, it assumes control of all data flow from the ADC's of a two-dimensional position-sensitive detector system to the computer memory by monitoring a variety of flags such as ADC DATA READY, MODCOMP BUSY, HALT DATA AQUISITION, etc. Second, it performs the necessary manipulations to take various bit patterns presented by the ADC's, map them into a linear memory space, and add an origin offset to account for the fact that the origin of the data acquisition array may be at various absolute memory locations of the host computer depending on experimental conditions. With such an arrangement, it is easy to code various software routines in the 8X300 to map different data acquisition arrays (e.g., 64x64, 128x128, 128x32, 256x16, etc.). All handshaking between the MODCOMP and the 8X300 is performed interactively via a 4801 controller. High speed transfers of the assembled address to the ModComp for memory increment are handled via a second 4801 controller which is coupled to a custom memory increment instruction loop which has been installed in the ModComp. 5,6

The present application, which arose during the development of the NSF-ORNL 30-meter small-angle neutron scattering facility, is almost identical to that of the 10-m x-ray facility. However, with the availability of a fast-response CAMAC crate controller for the ModComp computer<sup>7</sup> it was desirable to interface the 8X300 microcontroller status and control functions to the host computer via the CAMAC dataway instead of through a general purpose controller as was done earlier. The problem was thus to develop hardware which would serve as the interface between the standardized CAMAC bus (dataway) and the input/output ports of the 8x300. The dataway contains a 24 bit read bus and a 24 bit write bus as well as

various control lines. A means of accessing all of these lines by the 8X300 was needed, both for input as well as output. As will be seen, we have dedicated eight 8-bit 8X300 I/O ports to this task; three for data input on the CAMAC write lines (24 bits); three for data output on the CAMAC read lines (24 bits); one for status and control input (8 bits); and one for status and control output (8 bits). The status in (SIN) and status out (SOUT) control allow a wide variety of connections to the dataway look-at-me (LAM), Q-response, and I/O lines as well as to external devices such as ADC's and ModComp transfer initiate lines. Finally, packaging had to be considered. The 8X300 is a very high-speed (250 nsec cycle time) processor and thus cable lengths had to be minimized. The following paragraphs described our development of a general purpose CAMAC module which meets these needs.

## II. THE 8X300 MICROCONTROLLER

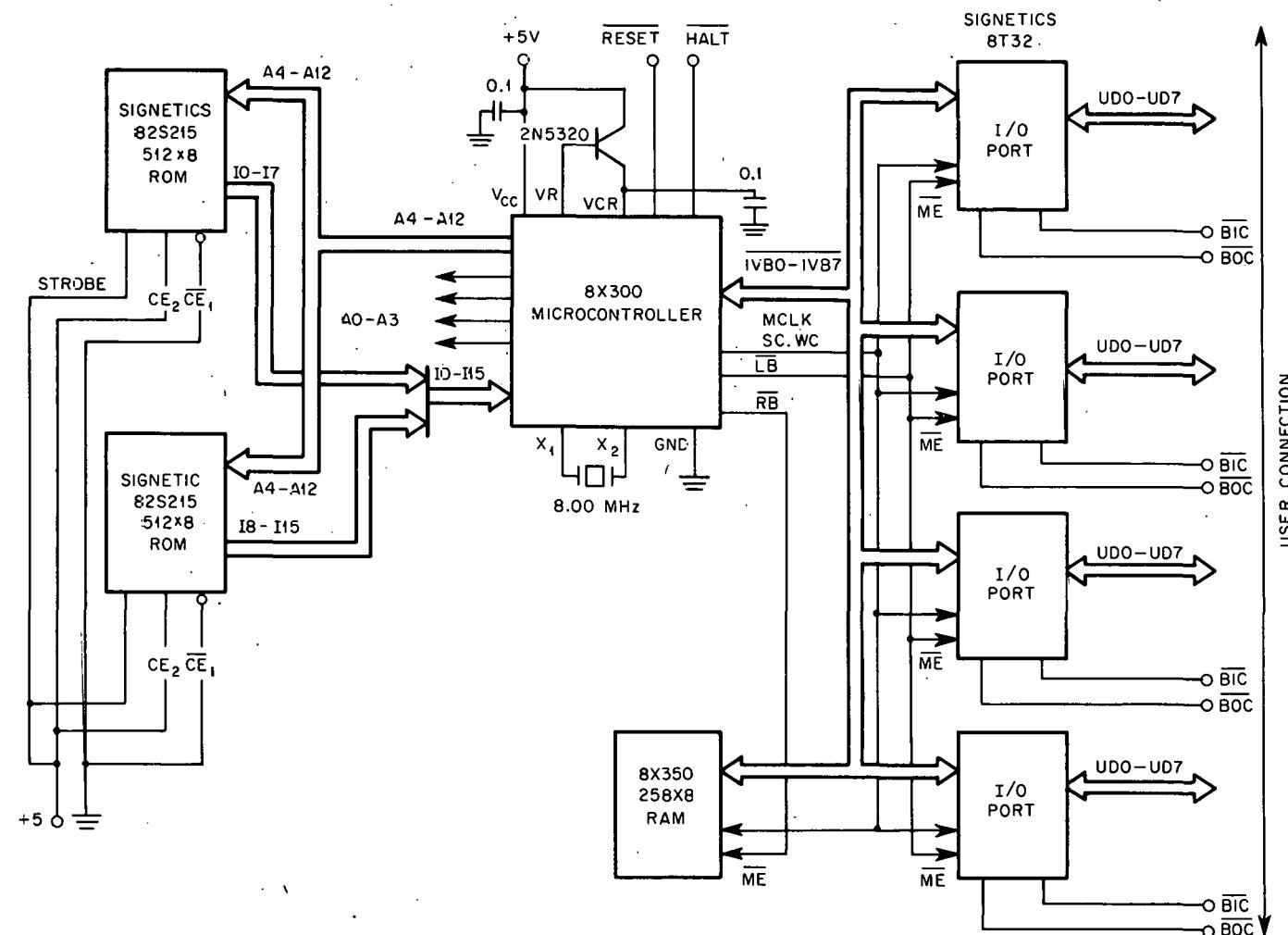

The Signetics 8X300 microcontroller is an 8-bit microprocessor built from bipolar technology. The device has separate instruction address, instruction, and I/O buses. Sixteen bit instructions can be addressed in up to 8192 words of program storage (13 bits), fetched, decoded and executed in only 250 nsec. A block diagram of a typical system is shown in Figure 1. The device used in our application, an SMS 300-140 microcontroller, has 4K of program storage, 1K of read/write data storage, and 16 I/O ports or Interface Vector (IV) bytes.

The 8X300 processor chip has eight internal 8-bit registers and two address registers. The theory applied which makes such a fast instruction cycle time possible is to access program memory and data on the same machine cycle. Normally an instruction is decoded, data read, manipulated and stored

Figure 1. Block diagram of the data flow in the 8X300 microcontroller system (by permission from Ref. 9).

and the next instruction address generated in one machine cycle. The 16 bit instruction word contains the operation code, source, destination and bit field length or rotation of data.

The 8X300 has a repertoire of eight instructions. These include bit manipulation (MOVE, ADD, AND, XOR), control (XEC, NZT, JMP) and data transfer (XMIT). A summary of each instruction is given in Table I. A unique feature is that data on the various IV bytes are treated the same as data in the internal registers.

Data I/O is handled over the Interface Vector (IV) bus. These IV bytes are organized as 8-bit wide bidirectional ports with latch tristate outputs. (Signetics 8T32 I/O ports). Each I/O port has an on-board 8 bit address burned in and a byte input and byte output control (BIC and BOC). The select control/write control (SC/WC) lines are used to determine whether the data on the I/O bus are an I/O port select address (SC high; WC low) or are data address to the last selected port (SC low; WC high). In the I/O port select mode, the port whose internal address matches the address on the I/O bus is enabled and remains enabled until the next I/O select command. All other ports are disabled. The I/O ports have the option of being bidirectional if BIC and BOC are under program control from a different output IV byte. However, in our application we have chosen to dedicate certain I/O ports to input and others to output by hard-wiring BIC and BOC. This procedure eliminates instructions and thus reduces the execution time of certain very fast loops which are necessary for our data handling software.

For further details concerning the 8X300 the reader is referred to the review by Lau,<sup>9</sup> the 8X300 Reference<sup>10</sup> and Programming<sup>11</sup> Manuals, the

Table I

SUMMARY

8X300 INSTRUCTION SET<sup>8</sup>

| <u>INSTRUCTION</u> | <u>OP CODE</u> | <u>DESCRIPTION</u>                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVE               | 0              | Data from the source register or IV bus is moved to the destination register or IV bus. The data may be rotated any number of places and/or masked to any length during the MOVE operation. The source data field remains unchanged after the operation.                                                                                                                                    |

| ADD                | 1              | Data from the source register or IV bus is added to the contents of the AUX register in ALU and the result is placed in the destination register or IV bus. The data may be rotated and/or masked during the operation. The source data field and the AUX register remain unchanged unless one is also the destination.                                                                     |

| AND                | 2              | Data from the source register or IV bus is ANDed with the contents of the AUX register and the result is placed in the destination register or IV bus. The data may be rotated and/or masked during the operation. The source data field and AUX register remain unchanged unless one of those is also the destination.                                                                     |

| XOR                | 3              | Data from the source register or IV bus undergoes an EXCLUSIVE OR comparison with the contents of the AUX register. The result is placed in the destination register or IV bus. Data may be rotated and/or masked during the operation. The source data field and AUX register remain unchanged unless one of those is also the destination.                                                |

| XEC                | 4              | Causes execution of the instruction at the address formed by replacing the least significant bits of the last address with the sum of the I field and the data in the source register or IV byte. After execution of the instruction at the specified address, instruction execution continues at the address following the XEC instruction, unless the executed instruction caused a jump. |

| NZT                | 5              | The least significant bits of the instruction address are replaced by the I field data if the register or IV bus specified by the source field has nonzero contents. The tested data field remains unchanged.                                                                                                                                                                               |

| XMIT               | 6              | The data in the I field is placed in the register or IV bus specified as the destination.                                                                                                                                                                                                                                                                                                   |

| JMP                | 7              | The address of the next instruction to be executed is changed to that specified by the 13-bit A field of the instruction.                                                                                                                                                                                                                                                                   |

SMS 300 data sheets<sup>12</sup> and the Microcontroller Application Guide<sup>13</sup> and System Description.<sup>14</sup> To assist the user with 8X300 applications there are also available an SMS microcontroller monitor<sup>15</sup> which provides display and control of the SMS 300 implementations of the 8X300, and an SMS microcontroller simulator<sup>16</sup> which provides capability for *in situ* development and testing of microcontroller software before the instruction ROMs are burned. We have found the latter device to be indispensable in our prototype work. Finally, there is a FORTRAN IV cross assembler program<sup>17</sup> which executes on a large computer and which generates symbolic listings and object modules. The resulting object modules can then be loaded and tested with the simulator before committing the program to ROM coder.

### III. INTRODUCTION TO CAMAC

CAMAC (Computer Automated Measurement and Control) is an internationally defined system by which various modules, manufactured by different firms and designed to perform a wide variety of data acquisition and control functions, can be interfaced to general-purpose digital computers. An excellent overview of the CAMAC system is given in Reference 18, while the actual standards are given in Reference 19. The standard includes the definition of a crate, which is the box into which all the modules fit, and a backplane dataway which contains all power, control, and data lines. A crate contains 25 physically identical slots or stations. However only 24 can be used for general purpose modules; the twenty-fifth is the master or crate controller position. Modules may occupy any integral member of stations. The module described in this report occupies four stations. Each station has identical access

to the dataway whose signals are described below. Two lines in the dataway, the address (N) line and the look-at-me (LAM) or interrupt line, are unique to each station and are connected from a given station directly to the master control station (N = 25). All other dataway signals are available to every station. Thus modules can be uniquely addressed by slot and generate interrupts to the crate controller independent of the type of module in the slot, and there is no need for on-board address decoding or source identification generation within the modules.

Control and status signals are generated by the crate controller to provide the necessary communications between it and a given station. These include N (station number), A<sub>0</sub>-A<sub>15</sub> (subaddress within a module), F<sub>0</sub>-F<sub>31</sub> (function code), B (dataway busy), Z (initialize, set all modules to a defined state), C (clear all modules), and I (inhibit operation). Module responses to various dataway operations are Q (indicates module status and depends on NAF command) and X (instruction accepted). Of the 32 function (F) codes, 18 are used for defined operations (read, write, test LAM, clear, etc.). An additional 6 are reserved for future expansion of the system and the remainder are nonstandard for the designer to implement his own functions. All data communication is via a 24 bit read bus and a separate 24 bit write bus. Two strobe clocks (S<sub>1</sub>, S<sub>2</sub>) are generated by the crate controller for synchronization.

#### IV. OVERVIEW OF THE MODULE

We set three criteria for our implementation of the 8X300 in a CAMAC module: (i) the device must be self-contained and occupy a minimum

number of CAMAC stations; (ii) it must meet all of the specifications of the IEEE-583 and following standards,<sup>19</sup> and (iii) it should be as general purpose a module as possible and yet perform our primary mission without compromise. The Scientific MicroSystems SMS 300-140 module contains the 8X300 microprocessor, 4K of program storage, 1K of RAM data storage and 16 IV bytes on a single board which will fit in a single CAMAC slot. Of the 16 I/O ports, it was determined that one each should be dedicated to a status in (SIN) and a status out (SOUT) word. These control words provide the necessary signals for the 8X300 software to handle a variety of handshaking tasks between external devices and the CAMAC dataway. In addition, we decided that the CAMAC read and write lines should be interfaced to the 8X300 through separate IV bytes.\* We thus utilize a total of six bytes for data I/O and two more for status and control. The remaining eight IV bytes may be used for connections to external devices.

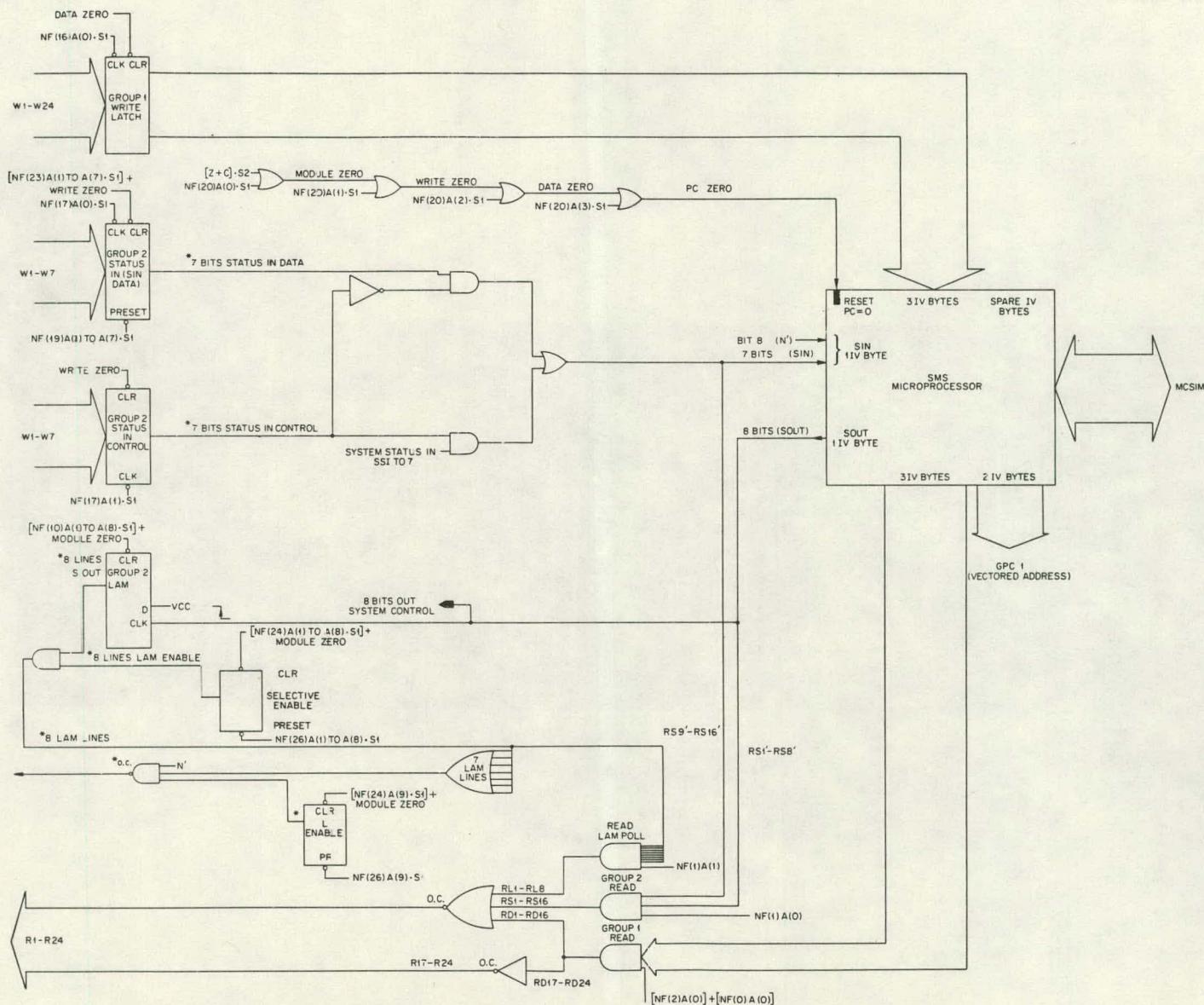

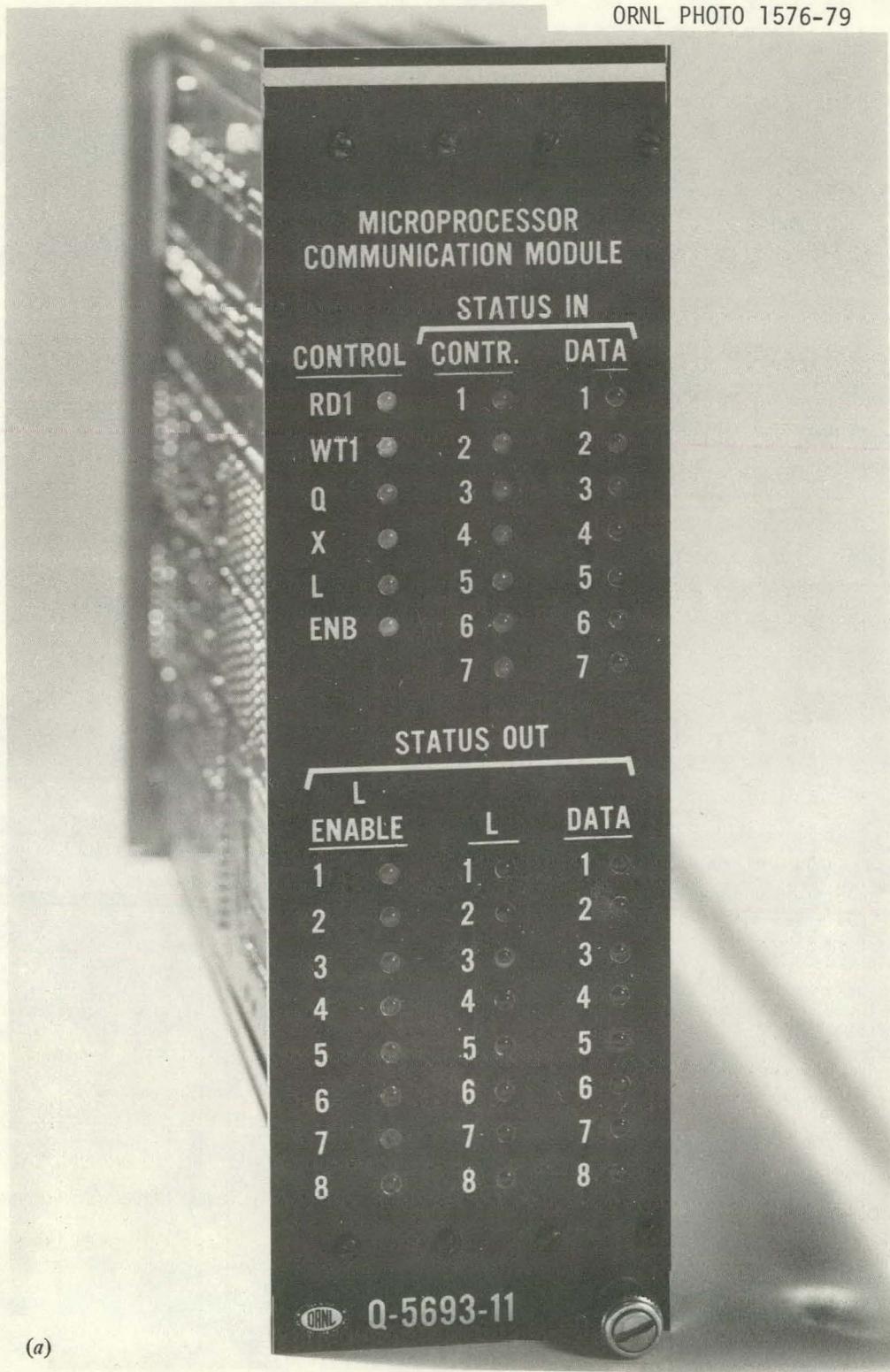

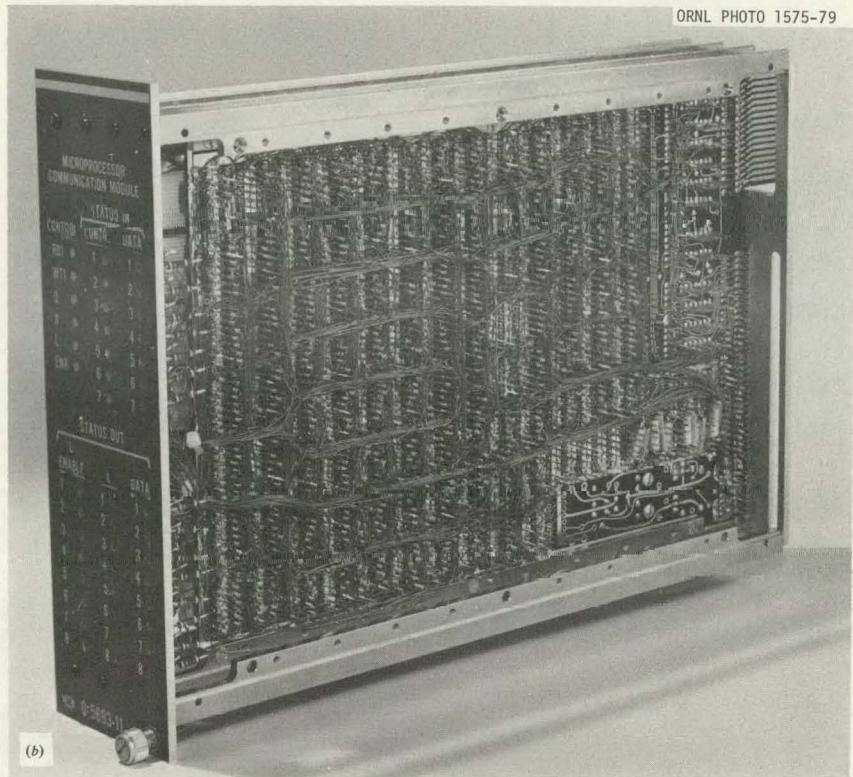

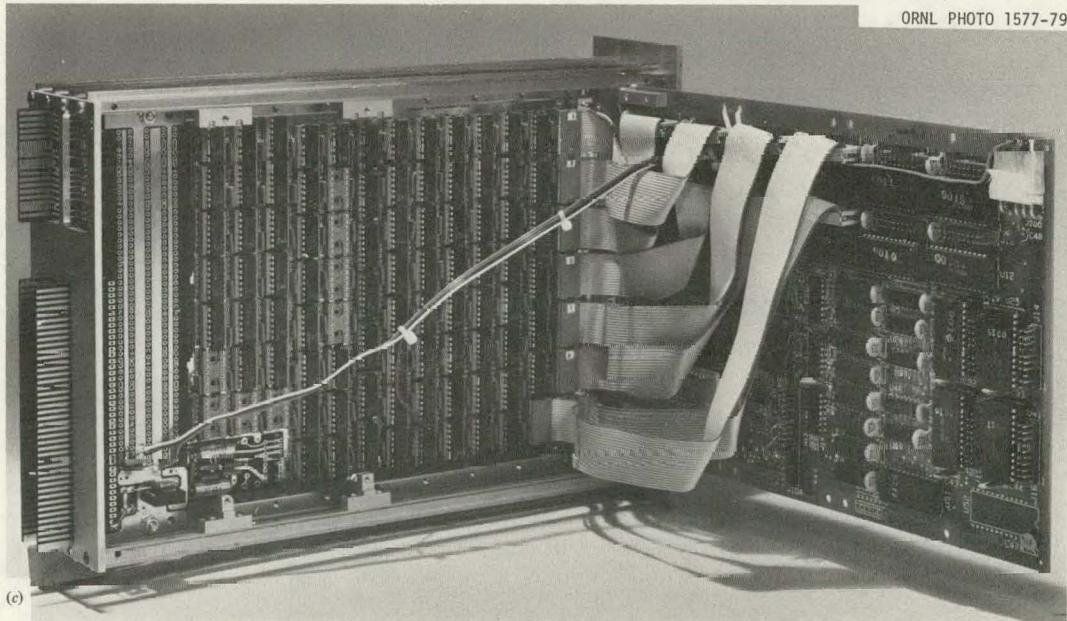

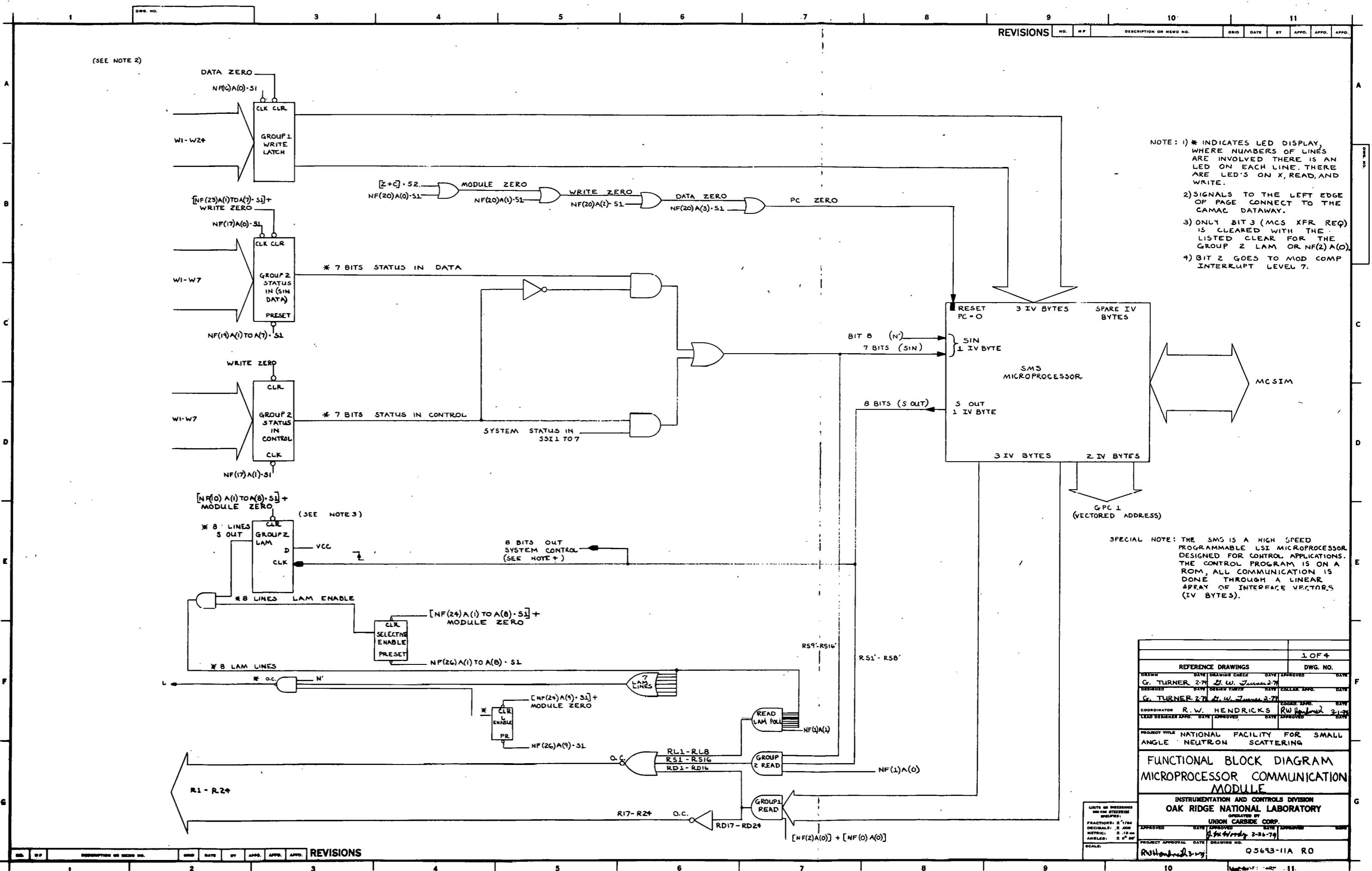

A block diagram of our implementation is given in Figure 2, and photographs of the completed assembly are shown in Figure 3. The CAMAC functions for which there is a module response are given in Table II. The module produces an X-response to every N which addresses the station in which the interface card is mounted. The addresses of the 8X300 interface vector I/O ports and their corresponding dataway connections are given in Table III.

Our module occupies four CAMAC stations (N through N+3) and has two card connectors to the dataway. One of these (N+1) is used exclusively to

---

\*It is possible to use only three IV bytes for I/O by using an SOUT bit to control the I/O BIC and BOC lines. However, such a procedure forces the programmer to use two instructions to address an IV byte; one for IV byte select and a second for I/O direction. We choose to use an additional three IV bytes to gain speed and flexibility.

Figure 2. Block diagram of the 8X300 CAMAC interface implementation.

ORNL PHOTO 1576-79

Figure 3. The 8X300 CAMAC module. (a) front panel; (b) interface board wire-wrap side; (c) open module with interface board (left) and SMS300-140 (right) swung open for access.

ORNL PHOTO 1577-79

TABLE II

CAMAC FUNCTION CODES

| Command    | Function Mnemonic | Q | Action                                                                                                                                              |

|------------|-------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| F(0)•A(0)  | RD1               | 0 | Strobe IV2, IV5, and IV4 to R1-R24                                                                                                                  |

| F(1)•A(0)  | RD2               | 0 | Strobe SOUT (IV6) to R1-R8 and SIN (IV7) to R9-R16                                                                                                  |

| F(1)•A(1)  | RD2               | 0 | Strobe LAM status to R1-R8                                                                                                                          |

| F(2)•A(0)  | RC1               | 0 | Strobe IV2, IV5, and IV4 to R1-R24; clear SOUT(3)                                                                                                   |

| F(8)•A(0)  | ILM               | 1 | Test LAM, Q=1 if set                                                                                                                                |

| F(8)•A(1)  | TLM               | 1 | Test block transfer response SOUT (8); Q=1 if set                                                                                                   |

| F(10)•A(n) | CLM               | 0 | Selective clear SOUT(n); n=1,2...7                                                                                                                  |

| F(10)•A(8) | CLM               | 0 | Selective clear SOUT(8) for Q response                                                                                                              |

| F(16)•A(0) | WT1               | 0 | Latch W1-W24 to IV1, IV3, and IV20                                                                                                                  |

| F(17)•A(0) | WT2               | 0 | Latch W1-W7 to SIN (IV7)                                                                                                                            |

| F(17)•A(1) | WT2               | 0 | Latch W1-W7 to select external device or computer for input to SIN (IV7) register; 0 selects computer, 1 selects external device.                   |

| F(19)•A(n) | SS2               | 0 | Selective set SIN(n) latch; n=1,2,...7                                                                                                              |

| F(20)•A(0) | MZ                | 0 | MODULE ZERO. Disable LAM's; clear individual LAM's; disable all SOUT bits for LAM; perform all functions of F(20)•A(1), F(20)•A(2), and F(20)•A(3). |

| F(20)•A(1) | WZ                | 0 | WRITE ZERO. Clear SIN register and SIN control register; perform all functions of F(20)•A(2) and F(20)•A(3).                                        |

| F(20)•A(2) | DZ                | 0 | DATA ZERO. Clear input write registers; perform functions of F(20)•A(3).                                                                            |

| F(20)•A(3) | PZ                | 0 | PROCESSOR ZERO. Reset microcontroller program counter to zero.                                                                                      |

| F(23)•A(n) | SC2               | 0 | Selective clear SIN(n); n=1,2,...7                                                                                                                  |

| F(24)•A(n) | DIS               | 0 | Selective Disable SOUT(n) for LAM; n=1,2,...7                                                                                                       |

| F(24)•A(8) | DIS               | 0 | Selective disable SOUT(8) for Q-response                                                                                                            |

| F(24)•A(9) | DIS               | 0 | Disable LAM                                                                                                                                         |

TABLE II (Cont'd)

| Command    | Function Mnemonic | Q | Action                                  |

|------------|-------------------|---|-----------------------------------------|

| F(26)•A(n) | ENB               | 0 | Selective enable SOUT(n) for LAM        |

| F(26)•A(8) | ENB               | 0 | Selective enable SOUT(8) for Q-response |

| F(26)•A(9) | ENB               | 0 | Enable LAM                              |

| Z          |                   | 0 | MODULE ZERO [same as F(20)•A(0)]        |

| I          |                   | 0 | NO ACTION                               |

| C          |                   | 0 | MODULE ZERO [same as F(20)•A(0)]        |

TABLE III

8X300 INTERFACE VECTOR CONNECTIONS

| <u>CAMAC</u> | <u>INPUT</u><br><u>IV Byte</u> | <u>CAMAC</u> | <u>INPUT</u><br><u>IV Byte</u> |

|--------------|--------------------------------|--------------|--------------------------------|

| W1-W8        | 208                            | R1-R8        | 1                              |

| W9-W16       | 5                              | R9-R16       | 3                              |

| W17-W24      | 4                              | R17-R24      | 2                              |

| SIN          | 7                              | SOUT         | 6                              |

obtain power for the SMS 300 microcontroller (2.0 A; 5V). All of the CAMAC dataway interface is on a single Standard Engineering<sup>20</sup> wire-wrap kludge card (WW04) which is mounted in slot N+2. For ease of servicing, we have mounted the microcontroller on hinges in such a manner that it can be easily swung open to gain access to the component sides of both boards (Fig. 3c).

Throughout we have used low power Schottky (LS) TTL logic wherever possible in order to minimize power consumption. Still the interface board draws 2.0 amps at 5 volts, thus making the total module power requirement 4.0 amps at 5 volts. A layout of the various integrated circuit chips is given in Appendix A.

Several features of the module should be pointed out. Each SIN bit may be externally selected to be connected either to latches on the dataway or to an external device. The choice is determined by loading a 7 bit word onto W1-W7 with a 0 implying computer control and a 1 external control. Thus, it is possible to have status information available to the microcontroller from both the computer or an external device and to be sure that a given bit is connected to only one device at a time. Note also that this arrangement allows an external device to be connected but be ineffective by setting its control bit to zero. Finally, bit 8 of SIN is connected directly to the dataway N line in order to make that signal available to the 8X300. The mode in which a given SIN bit is utilized is displayed on the front panel as Status in Control (see Fig. 3a); an illuminated LED indicates external source while a dark LED indicates computer source. The state of each SIN bit is displayed in the second column of LED's (Status In Data) and can be read directly on to the dataway R-lines (R9-R16). This gives the host computer access to the external device status lines. There

is no LED display for the standard read/write lines as this information is readily available with commercial dataway display modules.

The SOUT IV byte is more complex. First, each bit can be read directly to the dataway R-lines (R1-R8). More importantly, bits 1-7 can be used to generate structured LAM's, with the enable and disable for each bit under selective control. Bit 8 can be used to generate a Q-response. This is essential to implement certain modes of CAMAC block data transfers.<sup>21</sup> The status of the individual LAMs can be determined from the response to a test LAM command. Front panel LED's indicate the state of the SOUT IV byte, whether a given bit is selected for LAM, and whether that LAM is set.

The various sub-LAM's described above are OR'ed to produce a single module LAM which may also be separately enabled or disabled. Front panel LED's indicate whether or not the module LAM is enabled and whether or not it is set. In addition, N, X, and Q are displayed.

## V. DETAILED DESCRIPTION

### A. Block Diagram

The following description provides details for which the reader should reference the schematic drawings found in Appendix D. In this section reference is made to drawing Q5693-11A Functional Block Diagram Microprocessor Communications Module.

The dataway write lines (W1-W24) are strobed at S1 into a 24 bit latch register with N•A(0)•F(16) and may be accessed by three 8X300 IV bytes (Table 3). This register (called the group 1 write latch) can be cleared with the data zero (DZ), the crate clear (C), or the crate zero (Z) commands.

The status in (SIN) register consists of 7 bits of user controllable information plus the module select (N) which is tied to bit 8. The status information may come either from the CAMAC write lines (W1-W7) or from external inputs. In order that a SIN bit can be used with either source without the need for removing cables, a 7 bit steering register was installed to select one or the other input. This register, the group 2 status input control, is loaded from W1-W7 with an N•A(1)•F(17) command. A zero on write line n selects SIN(n) for CAMAC input; a one selects it for external input. The virtue of this control is that it can be latched and then not reset until it is necessary to change data paths. The group 2 status control register is cleared with a write zero (WZ), C, or Z. Once the status control register has been loaded, the status bits connected to the dataway can be latched from W1-W7 into the group 2 status input data register with an N•A(0)•F(17). In addition, this register has a network of discrete flip-flops which allows any bit to be individually cleared or set with the commands N•A(n)•F(19) or N•A(n)•F(23) respectively. In addition, the WZ, C, and Z commands also clear the group 2 status input data register. The purpose of the individual clear/set operations is to provide the programmer with the capability of operating on a single bit during handshaking operations. (Single bit operations are implemented in the 8X300 instructions as described in Section II.) The status input data, regardless of the data path through which it enters the module, can be read back into the dataway as will be described below.

The final input signal to be described is processor zero (PZ). This signal resets the 8X300 program counter (PC) to zero, and is derived from N•A(3)•F(20).

The data from the microcontroller out to the dataway read lines (R1-R24) are set up in a 24 bit wide bus. Since the 8X300 IV bytes are tristate latched output, it was necessary only to gate these signals with the appropriate CAMAC command and put them through open collector drivers. The data on R1-R24 can represent numerous microcontroller functions:  $N \cdot A(0) \cdot F(0)$  or  $N \cdot A(0) \cdot F(2)$  (group 1 read) place the data in the three dedicated IV bytes (Table III) on R1-R24;  $N \cdot A(1) \cdot F(0)$  is a group 2 status read and places the SOUT IV byte on R1-R8 and the SIN IV byte on R9-R16; and  $N \cdot A(1) \cdot F(1)$  is a LAM status poll. These functions will be discussed in detail.

The group 1 read [ $N \cdot A(0) \cdot F(0)$ ] is a simple read which strobes the data IV bytes onto R1-R24. The group 1 read and clear [ $N \cdot A(0) \cdot F(2)$ ] performs as  $N \cdot A(0) \cdot F(0)$  but in addition automatically clears SOUT(3). This operation is equivalent to  $N \cdot A(0) \cdot F(0)$  followed by  $N \cdot A(3) \cdot F(23)$ , and increases the speed of I/O mode CAMAC-host computer data transfers by eliminating the need for the second instruction.

The LASL fast-response CAMAC crate controller<sup>7</sup> is capable of performing hardware controlled DMP block transfers to the host computer in which the Q-response is used as the block terminator.<sup>5,18</sup> It was therefore decided to implement one status control bit [SOUT(8)] such that the 8X300 could generate a Q-response during high speed data transfers out of its own working storage ROMS. The remaining SOUT bits can be used to generate LAM's or be routed to external devices for control purposes. When setting up the logic surrounding the LAM interrupts, we wanted the ability to selectively enable or disable each bit for LAM (or Q) generation individually as well as the ability to clear the entire register simultaneously in order to have the greatest versatility and dataway control. Thus, the edge triggered group 2 LAM register

is cleared with  $N \cdot A(1) \cdot F(10)$  through  $N \cdot A(8) \cdot F(10)$ . The output of this register is ANDed with the outputs of the selective enable/disable register, an operation which determines if the output of the group 2 LAM register is allowed to advance to the LAM request circuit. Each bit of the selective enable register is enabled with  $N \cdot A(1) \cdot F(26)$  through  $N \cdot A(8) \cdot F(26)$  and selectively disabled with  $N \cdot A(1) \cdot F(24)$  through  $N \cdot A(8) \cdot F(24)$ . Module Zero (MZ) disables all bits simultaneously. The seven enabled LAM requests are ORed onto a single line which is then gated with the module LAM enable [ $N \cdot A(9) \cdot F(26)$ ] or disable [ $N \cdot A(9) \cdot F(24)$ ] signal and  $N$ . The eighth bit is connected directly to the  $Q$  line and has no additional control. The presence of a LAM may be tested with  $N \cdot A(0) \cdot F(8)$  which produces  $Q=1$  (LAM) or  $Q=0$  (no LAM). The  $Q$ -response bit can be tested with  $N \cdot A(1) \cdot F(8)$  which results in  $Q=1$  if  $SOUT(8)$  is both enabled and set. Otherwise  $Q=0$ .

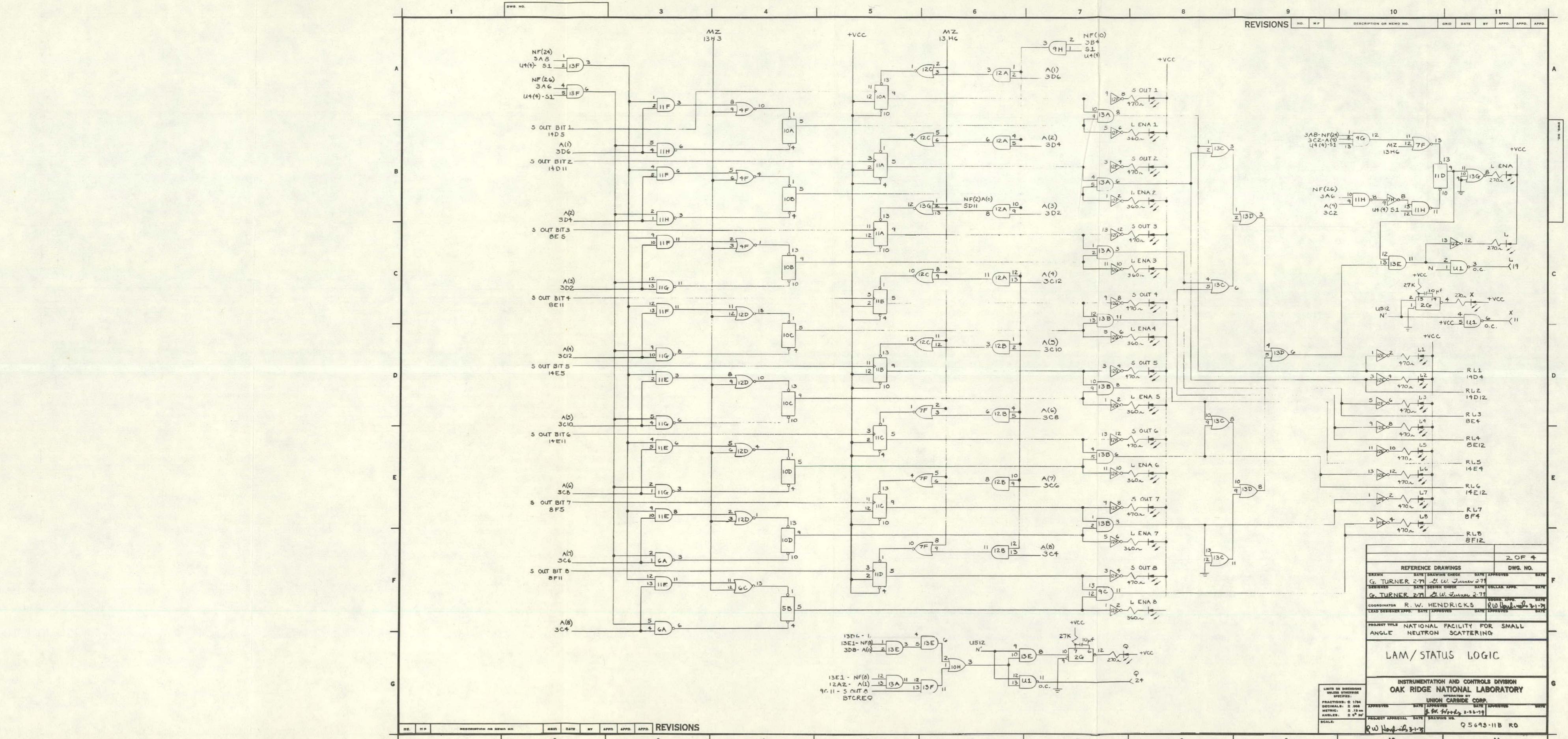

#### B. LAM/Status Logic

This section describes the logic on drawing Q5693-11B. The basic block is the status out registers, the LAM enable registers, the LAM bus, and the logic associated with  $L$ ,  $Q$ , and  $X$ .

The status out ( $SOUT$ ) bits 1-8 are paralleled off the inputs to the 74LS153's 14D, 8E, 14E, and 8F (Group 1/group 2 read and function decode). These inputs are used as the clock input to a bank of eight D flip-flops (10A, 11A, 11B, 11C, 11D) which make up the status out register. The D input is tied to  $V_{CC}$ ; thus any positive transition will be latched in these registers. The  $Q$  outputs of these registers are called  $SOUT(1-8)$  and are displayed on the front panel. The signals are run through a hex inverter and a  $360\Omega$  current limiting resistor and then to the LED. The status out

registers may be cleared as a group or individually. The signal that clears all of them is MZ (module zero).\* The registers may be individually cleared with  $N \cdot A(1) \cdot F(10)$  through  $N \cdot A(8) \cdot F(10)$ . This is accomplished by taking the AND of  $N \cdot F(10)$  and S1 then ANDing this with the appropriate A signal. For reasons associated with our particular application, we chose SOUT(3) to be the status flag for a SMS-ModComp data transfer request. Because of this, SOUT(3) can be cleared with one additional signal,  $N \cdot A(0) \cdot F(2)$ . The  $N \cdot A(0) \cdot F(2)$  is NOR'ed with the standard clearing signal  $N \cdot A(3) \cdot F(24)$  only on bit 3.

The other major register on this sheet is the LAM enable register which is also implemented with D flip-flops. The individual bits of the register are cleared with  $N \cdot A(1) \cdot F(24)$  to  $N \cdot A(8) \cdot F(24)$ .  $N \cdot F(24)$  is ANDed with S1 and this signal is ANDed with the appropriate A signal. These are then NORed with MZ which is used to clear all registers. To set a bit in the LAM register,  $N \cdot A(1) \cdot F(26)$  to  $N \cdot A(8) \cdot F(26)$  are used. The AND of  $N \cdot F(24)$  and S1 is NANDed with the appropriate A signal. Thus, when the output of one of these gates (10A, 10B, 10C, 10D, 5B) goes low the corresponding register FF is preset (set Q=1). These functions enable the programmer to choose any combination of SOUT bits to be seen on the CAMAC dataway as LAMs.

The output of these L enable registers is displayed on the front panel through the same type circuitry as the SOUT signals. These two latched outputs are ANDed to give read LAM (RL1-RL8). This eight bit group of signals is then put back into the input of the read selectors (74LS153's on group 1/group 2 read and function decode), and are displayed on the front panel on LED's. The RL signals are also all ORed to one signal at 13D(6).

---

\*This signal also clears all registers in this module.

Thus when any LAM goes high 13D(6) goes high. This signal is gated with a latched L enable flag. L is enabled with N·A(9)·F(26) which is obtained by ANDing N·F(26), A(9) and S1. When this signal goes low we preset the enable flip-flop, priming the gate 13E(12) and enable the signal at 13D(6) to be transmitted to the L line on the dataway. N·A(9)·F(24), gated with S1, is used to clear the enable flip-flop. As can be seen in Fig. 3(a), L and L ENABLE are displayed on the front panel. To produce X we simply turn N around and also display it on the front panel.

The Q response is used to indicate the status of two functions. In testing the L status N·A(0)·F(8) is used to gate L at 13D(6) onto the Q line. Q is, of course, ANDed with N'. The Q response is also used during a block transfer control (BTC) operation. To initialize the BTC N·A(1)·F(8) is gated with SOUT(8) which is used as a BTC request. SOUT(8) is derived just as the other SOUT signals except that it cannot generate an L. When a BTC operation is desired SOUT(8) is set to 1, and N·A(1)·F(8) is generated to enable the Q output and then Q is monitored by the crate controller. Since Q is not latched, a one shot 27K $\Omega$ /19 $\mu$ F (70 ms) pulse stretcher is used to display it on the front panel.

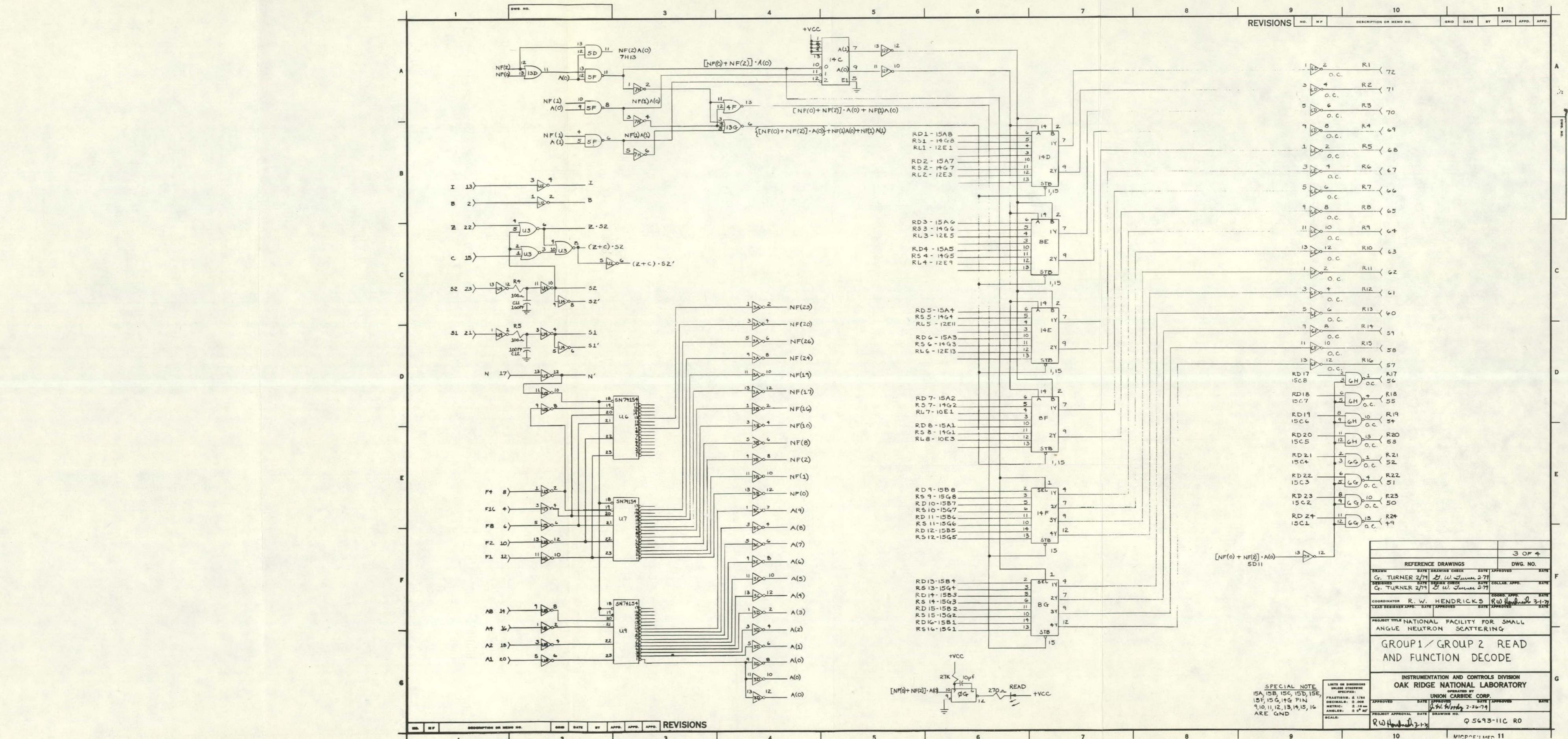

### C. Read Group 1/Group 2 and Function Decode

This section describes the logic referenced to drawing Q5693-11C. First, consider the decode logic at the left side of the drawing. Since the CAMAC dataway is a negative true bus, while positive true logic is used throughout our module, all signals are inverted as they are either buffered or gated onto the interface. Inhibit (I) and busy (B) are brought onto the board but are not used. The two bus strobes S1 and S2 are inverted and put through a 100 $\Omega$ /100 $\mu$ F filter network. Initialize (Z) and clear (C) are

individually ANDed with S2 to give Z S2 and C S2 and are ORed to produce (Z+C)·S2. The module select (N) is used to strobe the function and subaddress inputs into the 74154 4-to-16 line decoder/multiplexer chips. Two chips are used to decode the dataway signals F1, F2, F4, F8 and F16 into N·F(0) to N·F(31), while a third is used to decode A1, A2, A4, and A8 into A(0) to A(15).

The remaining sections of this drawing show the logic for access to the dataway control and read lines (R1-R24) as shown schematically in quadrants G6/G7 of Q5693-11A. RD1-RD24 are the "read data" lines from the three SMS IV data bytes. Each byte has a unique 3M\* cable connector to the interface board, the location of which may be found from Appendix A and Table III. The BOC signal is grounded on these bytes to make them output only bytes. The RS1-RS16 lines are the 16-bit "read status" bus. RS1-RS8 are the lines from the SOUT byte while RS9-RS16 are the lines from the SIN byte. In this case the SOUT IV byte has BOC grounded while SIN has BIC grounded. RL1-RL8 are the "read LAM" lines and come from the LAM logic. They are used in addition to the master LAM (L) line to allow the programmer to set up a priority interrupt scheme for servicing of the LAM.

The hardware used to implement these operations is a series of 74LS153 and 74LS157 two- and three-input multiplexers. The control for selecting which enable is decoded is a 74LS148 priority encoder. Follow now the operation of accessing RD1-RD24. The 24 data lines are already latched on the 8X300 IV byte so it is unnecessary to latch them again. RD1-RD8 are made available to the four 74LS153 chips in 14D, 8E, 14E and 8F. These 'LS153's are dual four-to-one line data selectors. RD9-RD16 are available

---

\*3M Company, St. Paul, MN.

at the inputs of the 74LS157's in 14F and 8G. These 'LS157's are quadruple two-to-one data selectors. Since RD17-RD24 are not multiplexed they simply go through a bank of open collector NAND gates to the dataway. The signals are inverted for the negative true CAMAC logic and open collectors are used to prevent loading of the bus. These gates are strobed with  $[N \cdot F(0) + N \cdot F(2)] \cdot A(0)$ . This signal is also OR'ed with  $N \cdot A(1) \cdot F(1)$  and, when low, is used to strobe 14F and 8G.  $[N \cdot F(0) + N \cdot F(2)] \cdot A(0)$  is used as the 0 input to a 74LS148 eight-to-three line priority encoder in 14C which is utilized as a three-to-two line encoder. Thus, a low signal on 0 with 1 and 2 high gives a high on both A(0) and A(1). These signals are used as the A and B inputs respectively to the data selectors 14D, 8E, 14E, and 8F and allow the RD inputs (C0) to appear on the Y output when pins 1 and 15 are strobed low. This signal is also used to take select low on 14F and 8G thus allowing the RD input (A) to appear on the Y output. All the Y outputs of the 'LS153's and 'LS157's go through 7405 inverters to get to a negative true state and open collector output before going to the dataway bus.

RS1-RS16 access is handled in the same manner as the RD lines. Here, an  $N \cdot A(0) \cdot F(1)$  is generated by ANDing  $N \cdot F(1)$  and  $A(0)$ . This signal is used as the "1" input for the 'LS148. When this input goes low the output on A(0) and A(1) will be 0 and 1 respectively. These data are put on the A and B inputs of the 'LS153's (14D, 8E, 14E, 8F) allowing the RS signals through the multiplexer to the Y outputs. It should be noted that these chips are strobed by any of the functions which are OR'ed at 13G(6) to go low when  $[N \cdot F(0) + N \cdot F(2)] \cdot A(0) + N \cdot F(1) \cdot A(1)$  is present. The 'LS157's carrying RS9-RS16 (14F and 8G) are strobed from 4F(13) going low because  $N \cdot F(1) \cdot A(0)$  is OR'ed with  $[N \cdot F(0) + N \cdot F(2)] \cdot A(0)$ . If the select line is high the RS inputs (B input) will appear on the Y outputs.

RL1-RL8, the read LAM lines, are accessed with an  $N \cdot A(1) \cdot F(1)$ . This signal is derived by ANDing  $N \cdot F(1)$  and  $A(1)$ . When this signal goes low it puts a low on the (2) input of the 'LS148 which gives an output code of 1 and 0 on  $A(0)$  and  $A(1)$  respectively. This code, when applied to the A and B inputs of the 'LS153's, enables the RS inputs (C2) to appear on the Y outputs.

The circuit in 1G is a pulse stretcher to display the read data on an LED indicator. The  $27\text{ k}\Omega/10\mu\text{F}$  arrangement on this one-shot produces a 70 ms delay. These pulse stretchers are used everywhere an indicator is desired on a pulsed output. This particular circuit is active with a high on pin 10 from a  $[N \cdot F(0) + N \cdot F(2)] \cdot A(0)$ .

#### D. Write Group 1/Group 2 and Status Control Logic

This section describes the logic on drawing Q5693-11D. The main parts of the logic are the group 1 write buffer register, the status input select and control logic, and the module initialization and zero logic.

The write buffer is the logic used to control the input of the 24 CAMAC write lines W1-W24. These lines are negative true and are inverted for our positive true logic. They are then put into the group one write registers (74LS174's in 8B, 8C, 8D and 14B). These chips contain six D flip-flops to a package and have a common clear and common clock. Only the Q output is available. These registers are needed as a buffer between the CAMAC dataway and the 8X300 because W1-W24 are available for only 600 nsec (during one dataway cycle) and because the 8X300 operates asynchronously with the dataway and thus may not be ready to accept the data at the time they are available directly from the dataway. The data from W1-W24 are latched with the command  $N \cdot A(0) \cdot F(16)$  and are strobed with S1. When a high,

obtained by ANDing N.F(16), A(0), and S1, is asserted on pin Q of the 'LS174's the data present on the inputs will appear on the outputs. This write command (WT1) is also displayed on the front panel via a pulse stretcher. The output data go directly to the 8X300 input IV bytes (see Table 3 and Appendix A for detailed connections). However, the 24 data lines are not displayed (because of power consumption and an already high chip count). To clear the registers, a data zero (DZ) may be generated. This signal, when low and applied on pin 1 of the 'LS174's, will clear the register. How the zero pulses are derived will be discussed at the end of this section.

The status input select and control logic performs two functions. The first is to present the seven bits of status information to the SIN input IV byte. The second is to provide, under program control, the ability to select whether a bit comes from outside the module system or from the dataway.

Consider first the status select operation. The command N·A(1)·F(17), when strobed with S1, gives a high on pin 9 of the 74LS174 control registers in 8A and 14B and their input is transferred to the Q output. A zero on this output will enable the gate at 9C(9), for example, and because of the inverter 7G will disable the gate at 9C(4). Thus, the 8X300 SIN byte sees the input from the CAMAC dataway line W1' at 3E(2). However, we see that the inputs to the status select registers (8A, 14A) are also derived from W1'-W7'. Thus, a 0 on W1'-W7' selects dataway input to SIN while a 1 selects external sources of data SSI1-SSI7. Since the registers in 8A, 14A are latched, the entire status bus is set up with a single N·A(1)·F(17) command in which the choice of input source is determined by the bit pattern on the W1-W7 lines. The front panel LED's for STATUS IN CONTROL are illuminated if the CAMAC dataway is selected for input, while the STATUS IN

DATA LED's are illuminated if the source (either dataway or external source) is high.

The discussion above indicates how the sources of the SIN data are selected in a single CAMAC dataway cycle. However, in the bit manipulation, handshaking kind of software operations for which the 8X300 is so powerful, it is essential to be able to set or clear a given status bit without affecting any of the other status lines. This was accomplished with the registers in 4A, 4B, 5A, 5B. These are 'LS74 RS flip-flops. To set the flip-flop, the commands N•A(1)•F(19) through N•A(7)•F(19) were used. Each "A" is gated to the appropriate logic. In the case of W1, when N•A(1)•F(19)•S1 is asserted 6A(8) goes low presetting the flip-flop and gives a one on 4A(5). Note that this bit has been set to a one without disturbing or checking the other bits. These bits are cleared in the same manner with N•A(1)•F(23) to N•A(7)•F(23). In the case of W1, N•F(23)•A(1)•S1' is ORed with WZ to give a low at 4A(1) to clear the flip-flop. WZ is OR'ed with the discrete clear lines so that the entire register can be cleared with a single command (WZ also clears the status input control group 2 register).

The zero or clear logic is the other function implemented on Q5693-11D. The basic concept is to generate a controlled clearing signal which would, (i) respond to crate clear; (ii) clear only the registers and logic on our module; or (iii) clear discrete segments with specified signals. The logic is shown at the bottom of the drawing. A dataway Z or C clear the entire module and resets the 8X300 program counter (PC) to zero. These signals may also be generated exclusively in this module with a module zero (MZ) command N•A(0)•F(20). MZ is OR'ed with Z and C. A less drastic operation is the write zero (WZ) command N•A(1)•F(20) which clears the dataway group 1 write buffers (8B, 8C, 8D, 14B), the group 2 status register (4A, 4B, 5A, 5B)

and the group 2 status control register (8A, 14A). In addition, the 8x300 PC is reset. The data zero command  $N \cdot A(2) \cdot F(20)$  clears only the group 1 write buffer and the PC, while the program counter zero (PZ) command  $N \cdot A(3) \cdot F(20)$  resets only the PC. WZ is obtained by ANDing  $[N \cdot A(1) \cdot F(20)] \cdot S1$  and ORing it with MZ. Thus, at 10H(8) the signal is  $WZ = MZ + [N \cdot A(1) \cdot F(20)] \cdot S1$ . Data zero (DZ) is produced with a  $[N \cdot F(20) \cdot A(2)] \cdot S1$ . The signal at 9E(11) is  $DZ = MZ + WZ + [N \cdot F(20) \cdot A(2)] \cdot S1$ . Program counter zero (PZ) is derived with a  $[N \cdot F(20) \cdot A(3)] \cdot S1$  to produce at 10H(11)  $PZ = MZ + WZ + DZ + [N \cdot F(23) \cdot A(30)] \cdot S1$ . This command sequence provides a very versatile clearing arrangement which allows certain segments or combinations thereof to be asserted without clearing others.

## VI. DIAGNOSTIC SOFTWARE

Early in the development of the module it became clear that it would not be possible to manually verify the correct operation of all functions under all conditions because of the very large number of allowable operations. Therefore we have developed diagnostic software for both the host computer and the 8X300 module which test all of the implemented functions under all possible combinations of input data and control functions.

The concept of the diagnostic procedure is simple. A code for the 8X300 was written (Appendix B) which simulates a direct connection of the input data and status IV bytes to their corresponding output IV bytes. The code is written in 8X300 machine language described elsewhere,<sup>11,13</sup> and can be implemented using the SMS3000 microcontroller simulator.<sup>16</sup> The loop contains 17 instructions and executes in 4.25  $\mu$ sec. This time is sufficiently short compared to the execution time of our register I/O CAMAC subroutine CFSA so that the 8X300 input and output IV bytes can be considered to be hardwired together on a bit by bit basis.

The host computer diagnostic program (Appendix C), written in top-down structured FORTRAN<sup>22</sup> and compiled with the SFORTAN precompiler,<sup>23</sup> tests for correct operation of the module by setting up appropriate CAMAC functions (NAF) and outputting known data patterns to the various IV bytes. All CAMAC I/O is performed through the subroutine CFSA which has been written in assembly language specifically for our fast-response crate controllers which were obtained from Los Alamos Scientific Laboratory.<sup>7</sup> This routine meets the proposed specifications for CAMAC FORTRAN subroutines.<sup>24</sup> The 8X300 code (Appendix B) transfers the data from the four input IV bytes to their corresponding output IV byte and the resultant data are read back into the host. The expected pattern and the pattern received are compared; disagreement indicates a module fault.

Logically, the implemented CAMAC functions are tested in an order such that each operation which relies on another CAMAC function is tested only after the prerequisite function has been tested. The order of testing is: Read/Write lines; Status In/Status out data lines; LAM enable/disable; and Q-response.

## VII. ACKNOWLEDGMENTS

We are indebted to R. T. Roseberry, P. A. Seeger and J. W. Woody, Jr. for valuable discussions in designing and implementing the microprocessor control module, and to Sharon P. King for help in developing the diagnostic software.

VIII. REFERENCES

1. Signetics Corp., 811 East Arques Ave., Sunnyvale, CA 94086

2. Hendricks, R. W., Trans. Am. Crystallogr. Assoc. 12, 103-146 (1976).

3. Hendricks, R. W., J. Appl. Crystallogr. 11, 15-30 (1978).

4. Scientific MicroSystems Inc., 520 Clyde Ave., Mountain View, CA 94043

5. Twichell, J. C. and Hendricks, R. W., (1978) Proceedings of Second Annual ModComp Users' Exchange, held in Ft. Lauderdale, FA. 6-8 December 1976 (Published by Modular Computer Systems, Inc., Ft. Lauderdale, FA).

6. Twichell, J. C. and Hendricks, R. W., (1979) to be published.

7. Seeger, P. A. (1976) "A Fast-Response CAMAC Crate Controller" Los Alamos Scientific Laboratory Report LA-6605-M, Los Alamos, NM 87545.

8. Taken (with permission) from Signetics 8X300 Programming Manual, p. 15.

9. Lau, S. Y. (1979) Electronic Design 4 (Feb. 15), 128-139.

10. Signetics 8X300 Reference Manual, Signetics Corp. Sunnyvale, CA.

11. Signetics 8X300 Programming Manual, Signetics Corp., Sunnyvale, CA.

12. SMS 300 Series Data Sheets, Scientific MicroSystems Inc., Mt. View, CA.

13. The Microcontroller Application Guide, Scientific MicroSystems, Inc., Mt. View, CA.

14. The Microcontroller System Description, Scientific MicroSystems Inc., Mt. View, CA.

15. MS 3300 Microcontroller Monitor, Scientific MicroSystem, Inc., Mt. View, CA.

16. MS 3000 Microcontroller Simulator, Scientific MicroSystems, Inc., Mt. View, CA.

17. Signetics Microcontroller Cross Assembly Program, Signetics Corp., Sunnyvale, CA.

18. U. S. NIM Committee (1976), CAMAC Tutorial Articles, Energy Research and Development Administration report TID-26618, Washington, D.C. 20545.

19. CAMAC Instrumentation and Interface Standards: Modular Instrumentation and Digital Interface System (CAMAC) IEEE Std. 583-1975; Serial Highway Interface System (CAMAC) IEEE Std. 595-1976; Parallel Highway Interface System (CAMAC) IEEE Std. 596-1976; Block Transfers in CAMAC System IEEE Std. 683-1976, The Institute of Electrical and Electronic Engineers, Inc. (New York, NY).

20. Standard Engineering Corp., 44800 Industrial Drive, Freemont, CA 94538.

21. Reference 18, page 85; Reference 19, IEEE Std. 683-1976.

22. Yourdon, E. (1975) Techniques of Program Structure and Design (Prentice Hall: Englewood Cliffs, NJ).

23. SFORTRAN was developed by Lars G. Mossberg of Volvo Flygmotor, AB, Trollhattan, Sweden and is distributed in the United States by Software Consulting Services, 901 Whittier Dr., Allentown, PA 18103

24. Reference 18, p. 75.

APPENDIX A

DETAILED CHIP COORDINATE LAYOUT FOR INTERFACE BOARD

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

ORNL-DWG 79-12934

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

A

B

C

D

E

F

G

H

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

APPENDIX B

8X300 MICROCONTROLLER DIAGNOSTIC SOFTWARE

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

APPENDIX B

8X300 DIAGNOSTICS HANDLER

| <u>PC</u> | <u>CODE</u> |                      |

|-----------|-------------|----------------------|

| 00        | 607007      | SELECT SIN (IV7)     |

| 01        | 027001      | (IV7)→R1             |

| 02        | 607006      | SELECT SOUT (IV6)    |

| 03        | 001027      | (R1)→IV6             |

| 04        | 607020      | SELECT W1-W8 (IV20)  |

| 05        | 027001      | (IV20)→R1            |

| 06        | 607001      | SELECT R1-R8 (IV1)   |

| 07        | 001027      | (R1)→IV1             |

| 10        | 607005      | SELECT W9-W16 (IV5)  |

| 11        | 027001      | (IV5)→R1             |

| 12        | 607003      | SELECT R9-R16 (IV3)  |

| 13        | 001027      | (R1)→IV3             |

| 14        | 607004      | SELECT W17-W24 (IV4) |

| 15        | 027001      | (IV4)→R1             |

| 16        | 607002      | SELECT R17-R24 (IV2) |

| 17        | 002027      | (R1)→IV2             |

| 20        | 700000      | BRU START            |

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

APPENDIX C

HOST COMPUTER DIAGNOSTIC SOFTWARE

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

```

1   1      PROGRAM SMS

1   2  C*** VERSION B.00 *** FEB 19,1979

1   3      DIMENSION JDATA(2),KDATA(2),LDATA(2)

1   4      LOGICAL ID,IS,BIT,TESTB,REPEAT,BIT1

1   5      INTEGER CDREGF,BOOL,LAM,ANS,YES

1   6      INTEGER RD1,RD2,RC1,TLM,CLM,WT1,WT2,SS2,F20,SC2,DIS,ENB

1   7      DATA RD1/0/,RD2/1/,RC1/2/,TLM/8/,CLM/10/,WT1/16/,WT2/17/,

1   8      SS2/19/,F20/20/,SC2/23/,DIS/24/,ENB/26/

1   9      DATA YES/'YE'/

1  10      DATA LDATA/2#0/

1  11 C...

1  12 C... INNITIALIZE CRATE

1  13 C...

1  14      ID=.FALSE.

1  15      IS=.FALSE.

1  16      REPEAT=.TRUE.

1  17      IB=0

1  18      WRITE(6,8001)

1  19      READ(5,8002) N

1  20      CALL CMCFNC('Z',ID,IS)

1  21 C...

1  22 C... TEST READ/WRITE LINES

1  23 C...

1  24      IA=0

1  25      LREG=CDREGF(IB,N,IA)

1  26      WHILE(REPEAT) DO

1  27          IERR=0

1  28          JDATA(1)=0

1  29          JDATA(2)=-32767

1  30          WHILE(JDATA(2).LE.32766) DO

1  31              IF(JDATA(1).GE.256) JDATA(1)=1

1  32              CALL CFSA(WT1,LREG,JDATA,ISTAT,JERR)

1  33              IF(JERR.NE.0) WRITE(6,8000) ISTAT

1  34              CALL CFSA(RD1,LREG,KDATA,ISTAT,JERR)

1  35              IF(JERR.NE.0) WRITE(6,8000) ISTAT

1  36              IF((JDATA(1).NE.KDATA(1)).OR.

1  37              (JDATA(2).NE.KDATA(2))) THEN

1  38                  WRITE(6,8010) J,JDATA,KDATA

1  39                  IERR=IERR+1

1  40          ENDIF

1  41          JDATA(1)=JDATA(1)+1

1  42          JDATA(2)=JDATA(2)+1

1  43      ENDDO

1  44      IF(IERR.EQ.0) THEN

1  45          WRITE(6,8015)

1  46      ELSE

1  47          WRITE(6,8020) IERR

1  48      ENDIF

1  49      WRITE(6,8005)

1  50      READ(5,8006) ANS

1  51      IF(ANS.EQ.YES) THEN

1  52          REPEAT=.TRUE.

1  53      ELSE

1  54          REPEAT=.FALSE.

1  55      ENDIF

1  56      ENDDO

1  57      REPEAT=.TRUE.

1  58 C...

1  59 C... TEST STATUS CONTROL FUNCTIONS (PHASE 1)

1  60 C... LOAD SIN REGISTER

```

```

1 61 C...

1 62     IA=1

1 63     LREG2=CDREGF(IB,N,IA)

1 64     WHILE(REPEAT) DO

1 65         JDATA(1)=0

1 66         JDATA(2)=0

1 67         CALL CFSA(WT2,LREG2,JDATA,ISTAT,JERR)

1 68         IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 69         IERR=0

1 70         J=1

1 71         WHILE(J.LE.128) DO

1 72             CALL CFSA(WT2,LREG,JDATA,ISTAT,JERR)

1 73             IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 74             CALL CFSA(RD2,LREG,KDATA,ISTAT,JERR)

1 75             IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 76             CALL SETBT(KDATA(2),1)

1 77             CALL SETBT(KDATA(2),9)

1 78             ITRANS=JCHFT(KDATA(2),-8)

1 79             K=2

1 80             WHILE(K.LE.8) DO

1 81                 CALL SETBT(KDATA(2),K)

1 82                 K=K+1

1 83             ENDDO

1 84             IREC=KDATA(2)

1 85             IF(TRANS.NE.IREC.OR.IREC.NE.JDATA(2)) THEN

1 86                 WRITE(6,8030) JDATA(2),TRANS,IREC

1 87                 IERR=IERR+1

1 88             ENDIF

1 89             JDATA(2)=JDATA(2)+1

1 90             J=J+1

1 91         ENDDO

1 92         IF(IERR.EQ.0) THEN

1 93             WRITE(6,8035)

1 94         ELSE

1 95             WRITE(6,8020) IERR

1 96         ENDIF

1 97         WRITE(6,8005)

1 98         READ(5,8006) ANS

1 99         IF(ANS.EQ.YES) THEN

1 100             REPEAT=.TRUE.

1 101         ELSE

1 102             REPEAT=.FALSE.

1 103         ENDIF

1 104     ENDDO

1 105     REPEAT=.TRUE.

1 106 C...

1 107 C... TEST STATUS CONTROL FUNCTIONS (PHASE 2)

1 108 C... SELECTIVE INPUT FUNCTIONS

1 109 C...

1 110     WHILE(REPEAT) DO

1 111         JDATA(2)=0

1 112         CALL CFSA(WT2,LREG,JDATA,ISTAT,JERR)

1 113         IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 114         IERR=0

1 115         J=1

1 116         WHILE(J.LE.127) DO

1 117             K=1

1 118             WHILE(K.LE.7) DO

1 119                 LREG1=CDREGF(IB,N,K)

1 120                 KTST=17-K

1 121                 BIT=TESTB(J,KTST)

1 122                 IF(BIT) THEN

1 123                     CALL CFSA(SC2,LREG1,JDATA,ISTAT,JERR)

1 124                     IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 125                 ELSE

1 126                     CALL CFSA(SS2,LREG1,JDATA,ISTAT,JERR)

```

```

1 127      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 128      ENDIF

1 129      K=K+1

1 130      ENDDO

1 131      CALL CFSA(RD2,LREG,KDATA,ISTAT,JERR)

1 132      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 133      CALL SETBT(KDATA(2),1)

1 134      CALL SETBT(KDATA(2),9)

1 135      ITRANS=ISHFT(KDATA(2),-8)

1 136      L=2

1 137      WHILE(L.LE.8) DO

1 138          CALL SETBT(KDATA(2),L)

1 139          L=L+1

1 140      ENDDO

1 141      IREC=KDATA(2)

1 142      IF(J.NE.IREC.OR.J.NE.ITRANS) THEN

1 143          IERR=IERR+1

1 144          WRITE(6,8040) J,ITRANS,IREC

1 145      ENDIF

1 146      J=J+1

1 147      ENDDO

1 148      IF(IERR.EQ.0) THEN

1 149          WRITE(6,8045)

1 150      ELSE

1 151          WRITE(6,8020) IERR

1 152      ENDIF

1 153      WRITE(6,8005)

1 154      READ(5,8006) ANS

1 155      IF(ANS.EQ.YES) THEN

1 156          REPEAT=.TRUE.

1 157      ELSE

1 158          REPEAT=.FALSE.

1 159      ENDIF

1 160      ENDDO

1 161      REPEAT=.TRUE.

1 162 C...

1 163 C... TEST LAMS (PHASE 1)

1 164 C... SELECTIVE LAM ENABLES

1 165 C...

1 166      WHILE(REPEAT) DO

1 167          IERR=0

1 168          JDATA(2)=0

1 169          J=0

1 170          WHILE(J.LE.127) DO

1 171              K=1

1 172              WHILE(K.LE.7) DO

1 173                  LREG1=CDREGF(IB,N,K)

1 174                  KTST=17-K

1 175                  BIT=TESTB(J,KTST)

1 176                  IF(BIT) THEN

1 177                      CALL CFSA(DIS,LREG1,JDATA,ISTAT,JERR)

1 178                      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 179                  ELSE

1 180                      CALL CFSA(ENB,LREG1,JDATA,ISTAT,JERR)

1 181                      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 182                  ENDIF

1 183                  K=K+1

1 184              ENDDO

1 185              JDATA(2)=0

1 186              K=0

1 187              WHILE(K.LE.127) DO

1 188                  CALL CFSA(WT2,LREG,JDATA,ISTAT,JERR)

1 189                  IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 190                  CALL CFSA(RD2,LREG2,KDATA,ISTAT,JERR)

1 191                  IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 192                  ICOHP=BOOL(J,K,8,16)

```

```

1 193      IF (ICOMP.NE.KDATA(2)) THEN

1 194          WRITE(6,8050) J,JDATA(2),KDATA(2),ICOMP

1 195          IERR=IERR+1

1 196      ENDIF

1 197      CALL CFSA(WT2,LREG,LDATA,ISTAT,JERR)

1 198      IF (JERR.NE.0) WRITE(6,8000) ISTAT

1 199      L=1

1 200      WHILE (L.LE.7) DO

1 201          LREG1=CDREGF(IB,N,L)

1 202          CALL CFSA(CLW,LREG1,LDATA,ISTAT,JERR)

1 203          IF (JERR.NE.0) WRITE(6,8000) ISTAT

1 204          L=L+1

1 205      ENDDO

1 206      JDATA(2)=JDATA(2)+1

1 207      K=K+1

1 208      ENDDO

1 209      J=J+1

1 210      ENDDO

1 211      IF (IERR.EQ.0) THEN

1 212          WRITE(6,8055)

1 213      ELSE

1 214          WRITE(6,8020) IERR

1 215      ENDIF

1 216      WRITE(6,8005)

1 217      READ(5,8006) ANS

1 218      IF (ANS.EQ.YES) THEN

1 219          REPEAT=.TRUE.

1 220      ELSE

1 221          REPEAT=.FALSE.

1 222      ENDIF

1 223      ENDDO

1 224      REPEAT=.TRUE.

1 225  C...

1 226  C...  TEST LAMS (PHASE 2)

1 227  C...  SELECTIVE CLEAR SOUT

1 228  C...

1 229      WHILE (REPEAT) DO

1 230          JDATA(2)=0

1 231          J=1

1 232          WHILE (J.LE.7) DO

1 233              LREG1=CDREGF(IB,N,J)

1 234              CALL CFSA(ENB,LREG1,JDATA,ISTAT,JERR)

1 235              IF (JERR.NE.0) WRITE(6,8000) ISTAT

1 236              J=J+1

1 237          ENDDO

1 238          IERR=0

1 239          J=0

1 240          WHILE (J.LE.127) DO

1 241              JDATA(2)=0

1 242              CALL CFSA(WT2,LREG,JDATA,ISTAT,JERR)

1 243              IF (JERR.NE.0) WRITE(6,8000) ISTAT

1 244              K=1

1 245              WHILE (K.LE.7) DO

1 246                  LREG1=CDREGF(IB,N,K)

1 247                  CALL CFSA(CLW,LREG1,JDATA,ISTAT,JERR)

1 248                  IF (JERR.NE.0) WRITE(6,8000) ISTAT

1 249                  K=K+1

1 250          ENDDO

1 251          JDATA(2)=127

1 252          CALL CFSA(WT2,LREG,JDATA,ISTAT,JERR)

1 253          IF (JERR.NE.0) WRITE(6,8000) ISTAT

1 254          K=1

1 255          WHILE (K.LE.7) DO

1 256              LREG1=CDREGF(IB,N,K)

1 257              KTST=17-K

1 258              BIT=TESTB(J,KTST)

```

```

1 259      IF(BIT) THEN

1 260          CALL CFSAL(LREG1,JDATA,ISTAT,JERR)

1 261          IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 262      ENDIF

1 263      K=K+1

1 264  ENDDO

1 265      CALL CFSAR(LREG2,KDATA,ISTAT,JERR)

1 266      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 267      CALL SETBT(KDATA(2),9)

1 268      IF(J.NE.KDATA(2)) THEN

1 269          IERR=IERR+1

1 270          WRITE(6,8060) J,KDATA(2)

1 271      ENDIF

1 272      J=J+1

1 273  ENDDO

1 274      IF(IERR.EQ.0) THEN

1 275          WRITE(6,8065)

1 276      ELSE

1 277          WRITE(6,8020) IERR

1 278      ENDIF

1 279      WRITE(6,8005)

1 280      READ(5,8006) ANS

1 281      IF(ANS.EQ.YES) THEN

1 282          REPEAT=.TRUE.

1 283      ELSE

1 284          REPEAT=.FALSE.

1 285      ENDIF

1 286  ENDDO

1 287      REPEAT=.TRUE.

1 288  C...

1 289  C... TEST LAMS (PHASE 3)

1 290  C... Q-RESPONSE MODE

1 291  C...

1 292      CALL CMCFNC('RI',ID,IS)

1 293      WHILE(REPEAT) DO

1 294          IERR=0

1 295          JDATA(2)=0

1 296          J=0

1 297          WHILE(J.LE.127) DO

1 298              K=1

1 299              WHILE(K.LE.7) DO

1 300                  LREG1=CDREGF(IB,N,K)

1 301                  KTST=17-K

1 302                  BIT=TESTB(J,KTST)

1 303                  IF(BIT) THEN

1 304                      CALL CFSAL(LREG1,JDATA,ISTAT,JERR)

1 305                      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 306                  ELSE

1 307                      CALL CFSAR(LREG1,JDATA,ISTAT,JERR)

1 308                      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 309                  ENDIF

1 310                  K=K+1

1 311  ENDDO

1 312          JDATA(2)=0

1 313          K=0

1 314          WHILE(K.LE.127) DO

1 315              CALL CFSAR(WT2,LREG,JDATA,ISTAT,JERR)

1 316              IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 317              CALL CFSACTL(LREG,KDATA,ISTAT,JERR)

1 318              IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 319              BIT=TESTB(ISTAT,11)

1 320              ICOMP=BOUL(J,K,8,16)

1 321              IF(((ICOMP.EQ.0).AND.BIT).OR.

1 322              ((ICOMP.NE.0).AND..NOT.BIT)) THEN

1 323                  WRITE(6,8070) J,K,ISTAT,ICOMP

1 324              IERR=IERR+1

```

```

1 325      ENDIF

1 326      CALL CFSA(WT2,LREG,LDATA,ISTAT,JERR)

1 327      IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 328      L=1

1 329      WHILE(L.LE.7) DO

1 330          LREG1=CDREGF(IB,N,L)

1 331          CALL CFSA(CLW,LREG1,LDATA,ISTAT,JERR)

1 332          IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 333          L=L+1

1 334      ENDDO

1 335      JDATA(2)=JDATA(2)+1

1 336      K=K+1

1 337      ENDDO

1 338      J=J+1

1 339      ENDDO

1 340      IF(IERR.EQ.0) THEN

1 341          WRITE(6,8075)

1 342      ELSE

1 343          WRITE(6,8020) IERR

1 344      ENDIF

1 345      WRITE(6,8005)

1 346      READ(5,8006) ANS

1 347      IF(ANS.EQ.YES) THEN

1 348          REPEAT=.TRUE.

1 349      ELSE

1 350          REPEAT=.FALSE.

1 351      ENDIF

1 352      ENDDO

1 353      REPEAT=.TRUE.

1 354 C...

1 355 C... TEST SOUT Q-RESPONSE

1 356 C...

1 357      IA=8

1 358      LREG1=CDREGF(IB,N,IA)

1 359      WHILE(REPEAT) DO

1 360          JDATA(2)=0

1 361          CALL CFSA(ENB,LREG1,JDATA,ISTAT,JERR)

1 362          IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 363          IERR=0

1 364          J=0

1 365          WHILE(J.LE.255) DO

1 366              CALL CFSA(WT2,LREG,JDATA,ISTAT,JERR)

1 367              IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 368              CALL CFSA(TLM,LREG2,JDATA,ISTAT,JERR)

1 369              IF(JERR.NE.0) WRITE(6,8000) ISTAT

1 370              BIT=TESTB(ISTAT,11)

1 371              BIT1=TESTB(J,9)

1 372              IF((BIT.AND.BIT1).OR.,(.NOT.BIT.AND..NOT.BIT1)) THEN

1 373                  WRITE(6,8080) J,JDATA(2),ISTAT

1 374                  IERR=IERR+1

1 375              ENDIF

1 376              JDATA(2)=JDATA(2)+1

1 377              J=J+1

1 378          ENDDO

1 379          IF(IERR.EQ.0) THEN

1 380              WRITE(6,8075)

1 381          ELSE

1 382              WRITE(6,8020) IERR

1 383          ENDIF

1 384          WRITE(6,8005)

1 385          READ(5,8006) ANS

1 386          IF(ANS.EQ.YES) THEN

1 387              REPEAT=.TRUE.

1 388          ELSE

1 389              REPEAT=.FALSE.

1 390          ENDIF

```

```

1 391      ENDDO

1 392      REPEAT=.TRUE.

1 393      STOP

1 394      8000 FORMAT(1H , 'CAMAC STATUS ERROR'/1H ,2Z4)

1 395      8001 FORMAT(1H , 'WHERE IS SMS? (I2)')

1 396      8002 FORMAT(I2)

1 397      8005 FORMAT(1H , 'REPEAT?')

1 398      8006 FORMAT(A2)

1 399      8010 FORMAT(1H , 'I/O ERROR'/1H ,3(2Z4,2X))

1 400      8015 FORMAT(1H , 'I/O PHASE ERROR FREE')

1 401      8020 FORMAT(1H ,15,2X,'ERRORS DETECTED')

1 402      8025 FORMAT(1H , 'SIN CONTROL ERROR',1H ,2Z4)

1 403      8030 FORMAT(1H , 'SIN LOAD ERROR'/1H ,3(2Z4,2X))

1 404      8035 FORMAT(1H , 'STATUS CONTROL FUNCTIONS (PHASE 1) ERROR FREE')

1 405      8040 FORMAT(1H , 'STATUS SELECTIVI. SET ERROR'/1H ,3(2Z4,2X))

1 406      8045 FORMAT(1H , 'STATUS CONTROL FUNCTIONS (PHASE 2) ERROR-FREE')

1 407      8050 FORMAT(1H , 'LAM ERROR (PHASE 1)'/1H ,4(2Z4,2X))

1 408      8055 FORMAT(1H , 'LAM TEST (PHASE 1) ERROR-FREE')

1 409      8060 FORMAT(1H , 'SOUT SELECTIVE CLEAR ERROR'/1H ,2(2Z4,2X))

1 410      8065 FORMAT(1H , 'LAM TEST (PHASE 2) ERROR-FREE')

1 411      8070 FORMAT(1H , 'LAM ERROR (PHASE 3)'/1H ,4(2Z4,2X))

1 412      8075 FORMAT(1H , 'LAM TEST (PHASE 3) ERROR-FREE')

1 413      8080 FORMAT(1H , 'SOUT Q-RESPONSE ERROR'/1H ,3(2Z4,2X))

1 414      8085 FORMAT(1H , 'SOUT Q-RESPONSE ERROR-FREE')

1 415      END

```

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

APPENDIX D

CIRCUIT DIAGRAMS

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

INTERNAL DISTRIBUTION

- 1-2. Central Research Library

- 3. Document Reference Section

- 4-5. Laboratory Records Department

- 6. Laboratory Records, ORNL - RC

- 7. ORNL Patent Office

- 8. J. A. Biggerstaff

- 9. B. S. Borie

- 10. H. R. Child

- 11-61. R. W. Hendricks

- 62. D. Hensley

- 63. H. N. Hill

- 64. M. R. Hill

- 65. J. A. Keathley

- 66. S. P. King

- 67. W. C. Koehler

- 68. M. K. Kopp

- 69. J. S. Lin

- 70. J. L. Lovvorn

- 71. C. J. McHargue

- 72. E. Madden

- 73. C. D. Martin

- 74. H. Postma

- 75. R. T. Roseberry

- 76. C. T. Stansberry

- 77. C. J. Sparks

- 78. J. O. Stiegler

- 79. D. B. Trauger

- 80-90. G. W. Turner

- 91. R. G. Upton

- 92. J. R. Weir, Jr.

- 93. G. D. Wignall

- 94. M. K. Wilkinson

- 95. J. W. Woody

- 96. H. L. Yakel

- 97. R. E. Zedler

- 98. A. Zucker

EXTERNAL DISTRIBUTION

- 99. B. W. Batterman, Division of Applied Physics, Cornell University, Ithaca, NY 14853

- 100. G. Bauer, Institut für Festkörperforschung der Kernforschungsanlage, 517 Jülich, West Germany

- 101. H. Brumberger, Department of Chemistry, Syracuse University, Syracuse, NY 13200

- 102. P. J. Flory, Department of Chemistry, Stanford University, Stanford, CA 11973

103. T. Hashimoto, Department of Polymer Chemistry, Kyoto University, Kyoto 606, Japan

104. L. C. Ianniello, Department of Materials Sciences, Department of Energy, Washington, DC 20545

105. R. Kurz, Institut für Elektronik, Kernforschungsanlage Jülich, 517 Jülich, West Germany

106. S. Y. Lau, Signetics Corp., Sunnyvale, CA 94086

107. M. Liccardo, Scientific MicroSystems Inc., 520 Clyde Ave., Mountain View, CA 94043

108. D. McMillan, P-9, Los Alamos Scientific Laboratory, Los Alamos, NM 87545

109. D. L. Mitchell, National Science Foundation, 1800 G Street, N.W., Washington, DC 20550

110. L. H. Nosanow, National Science Foundation, 1800 G Street, N.W., Washington, DC 20550

111. J. Schelten, Institut für Festkörperforschung der Kerntorschungsanlage, Jülich, 517 Jülich, Germany

112. B. P. Schoenborn, Biology Division, Brookhaven National Laboratory, Upton, NY 11973

113. C. G. Shull, Massachusetts Institute of Technology, Cambridge, MA 02139

114. P. A. Seeger, P-8, Los Alamos Scientific Laboratory, Los Alamos, NM 87545

115. D. K. Stevens, Division of Materials Sciences, Department of Energy, Washington, DC 20545

116. J. West, Daresbury Laboratory, Keckwick Lane, Warrington WAY 4AD, England

- 117-143. Technical Information Center