Courant Mathematics and

Computing Laboratory

U.S. Department of Energy

MASTER

The Optimization of Horizontal Microcode

Within and Beyond Basic Blocks:

An Application of Processor Scheduling with Resources

Joseph A. Fisher

U.S. Department of Energy Report

Prepared under Contract EY-76-C-02-3077

with the Office of Energy Research

Mathematics and Computing

October 1979

New York University

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

UNCLASSIFIED

Courant Mathematics and Computing Laboratory

New York University

Mathematics and Computing

COO-3077-161

THE OPTIMIZATION OF HORIZONTAL MICROCODE

WITHIN AND BEYOND BASIC BLOCKS:

AN APPLICATION OF PROCESSOR SCHEDULING WITH RESOURCES

Joseph A. Fisher

October 1979

DISCLAIMER

This book was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

U. S. Department of Energy

Contract EY-76-C-02-3077

UNCLASSIFIED

RGH

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

© 1979 Joseph A. Fisher

TABLE OF CONTENTS

|                                                          |    |

|----------------------------------------------------------|----|

| 1. Abstract and Summary                                  | 1  |

| 2. Introduction to the Problem                           | 3  |

| Why This is Important                                    |    |

| 3. Previous Investigations of This Problem               | 6  |

| Optimal Solutions                                        |    |

| Approximate Solutions                                    |    |

| Beyond Block Optimization                                |    |

| 4. Practical Results in Processor Scheduling Theory      | 14 |

| Processor Scheduling                                     |    |

| Approximately Optimal Solutions and List Scheduling      |    |

| Resource Constrained Problems                            |    |

| 5. Optimizing Basic Blocks of Microcode                  | 26 |

| Formal Identification Between Optimizing and Scheduling  |    |

| An Example                                               |    |

| Resource Constraints                                     |    |

| A Note on Efficiency                                     |    |

| 6. A Lower Bound and Its Uses                            | 42 |

| The Fernandez-Bussel Lower Bound                         |    |

| and How it Works                                         |    |

| Finding the Bound                                        |    |

| How the Bound Loses Accuracy                             |    |

| Our Work On and Suggested Uses of the Bound              |    |

| Efficient Calculation of the Bound                       |    |

| 7. Experimentally Obtained Measures of the Effectiveness | 54 |

| of Several Basic Block Optimizing Strategies             |    |

| Introduction and General Conclusions                     |    |

| The Model                                                |    |

| Limitations of the Model                                 |    |

| The Strategies Tested                                    |    |

| Other Suggested Basic Block Methods                      |    |

| The Experiments                                          |    |

| 8. A Unified Approach to Interblock Optimization         | 83 |

| Our Method of Interblock Optimization                    |    |

| Scheduling the Remainder of the Path                     |    |

| Code Containing a Single Loop                            |    |

| Code With a General Flow Structure                       |    |

| Definitions for the Interblock Optimization Problem      |    |

| Calling Sequence                                         |    |

| Comments on the Optimizing Routines                      |    |

| Detailed Algorithms for Interblock Optimization          |    |

| A Detailed Example                                       |    |

| Two Examples From the PUMA 6600 Emulator                 |    |

9. Extensions for More General Models of Microprogramming 158

- Non-conforming Models

- Compatible Uses of Resources

- The Left and Right Resource Bit String

- Resources with Non-unit Availability

- Testing for Compatible Resources

- Many-cycle MOPs

- Polyphase MOPs

- Variable Instruction Formats

- Necessarily Simultaneous MOPs

- Special Case Precedence

- Flow Control Extensions and Restrictions

Annotated Bibliography

170

## FIGURES, TABLES AND EXAMPLES

### Chapter 4

|                                                                   |    |

|-------------------------------------------------------------------|----|

| Figure 4.1 A Formal Description of Task Scheduling With Resources | 16 |

| 4.2 Directed Graph Definitions                                    | 17 |

### Chapter 5

|                                                                                                      |    |

|------------------------------------------------------------------------------------------------------|----|

| Figure 5.1 Formal Identification Between Processor Scheduling and Basic Block Microcode Optimization | 27 |

| 5.2 Rules for the Formation of a Partial Order on Micro-operations                                   | 28 |

| 5.3 Alterations of List Scheduling to Account for "= Edges"                                          | 36 |

| 5.4 $E \in O( T )$ in Data-Precedence Graphs                                                         | 39 |

| Example 5.1 Short Basic Block Optimized in Detail                                                    | 33 |

| 5.2 The Optimization of a PUMA Basic Block                                                           | 41 |

### Chapter 6

|                                             |    |

|---------------------------------------------|----|

| Figure 6.1 The Fernandez-Bussel Lower Bound | 44 |

|---------------------------------------------|----|

### Chapter 7

|                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------|----|

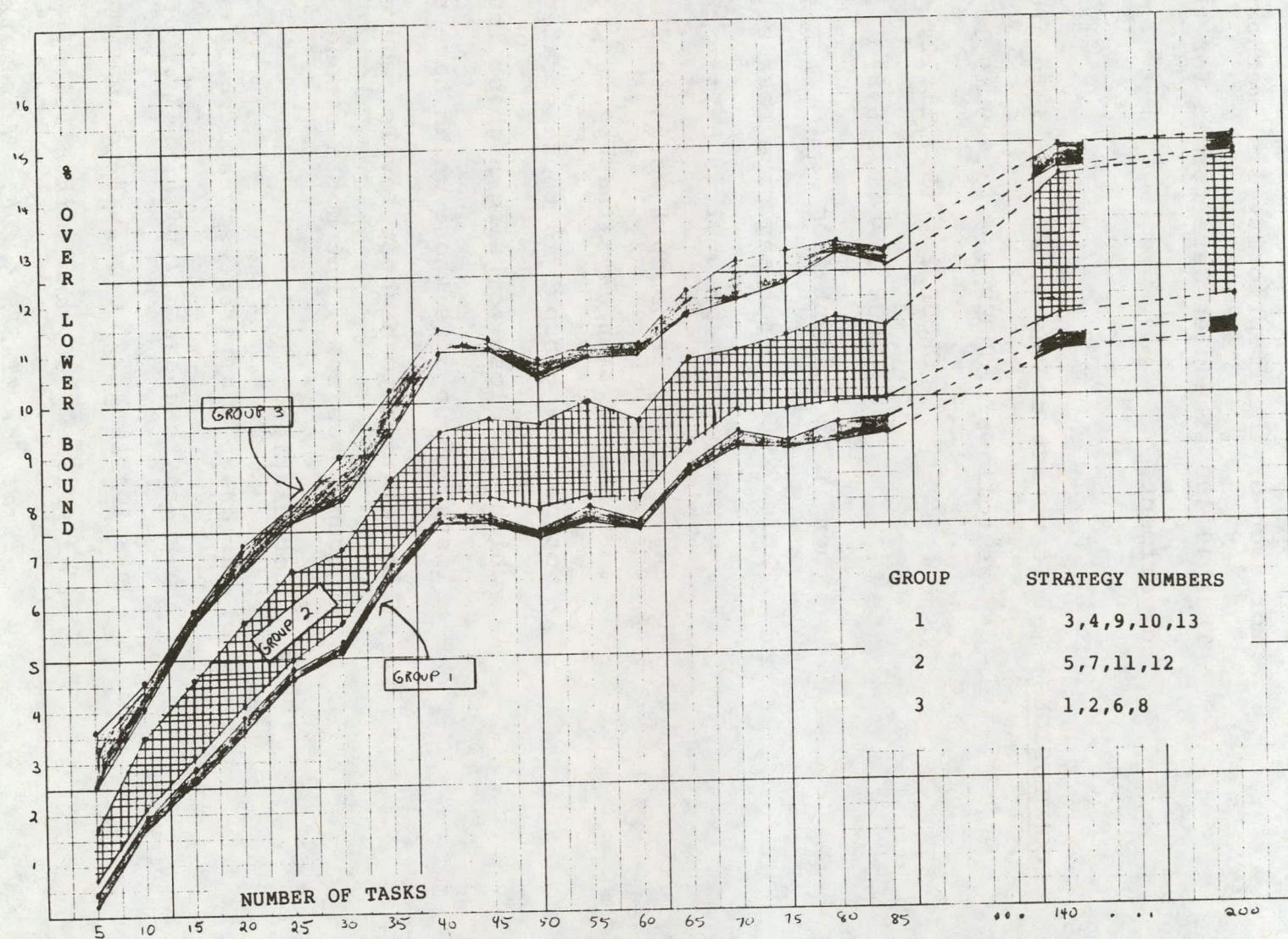

| Figure 7.1 The Performance of the Three List Scheduling Strategy Groups                                          | 66 |

| Table 7.1 Lengths of list schedules for the PUMA-like model and varying size task sets.                          | 67 |

| 7.2 Times to form data-precedence graph, priority lists, lower bounds, and schedules for various task set sizes. | 71 |

| 7.3 The varying parameters for Experiment 2, with number of tasks fixed at 40.                                   | 73 |

| 7.4 Lengths of list schedules for the models of Table 7.3.                                                       | 74 |

| 7.5 Rankings of performances of list schedules for the models of Table 7.3.                                      | 75 |

Table 7.6 Lengths of schedules produced by YAU's

algorithm using various weights; list sche-

dules for same weights given for comparison. 79

Chapter 8

|             |                                                           |     |

|-------------|-----------------------------------------------------------|-----|

| Figure 8.1  | Catalog of Interblock MOP Motions                         | 84  |

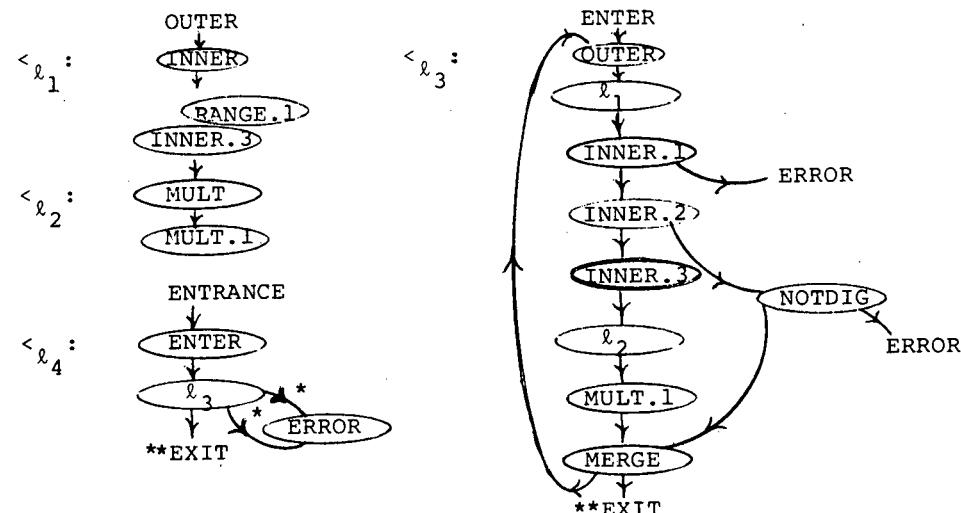

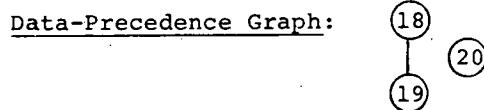

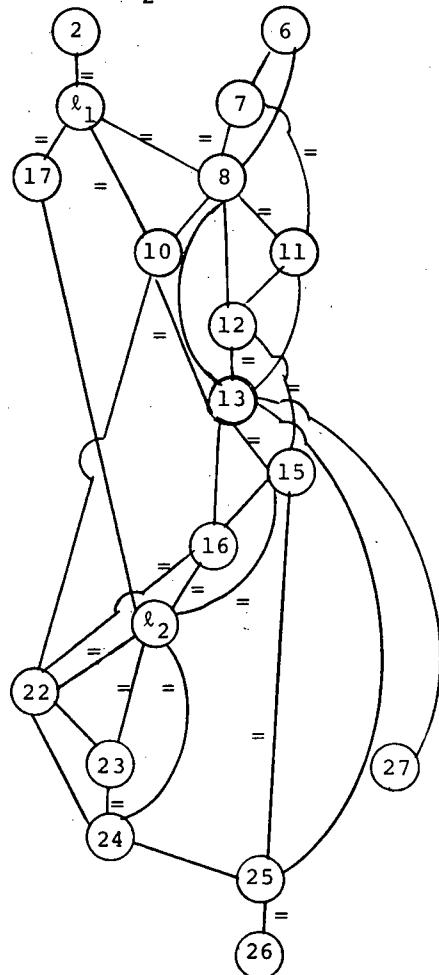

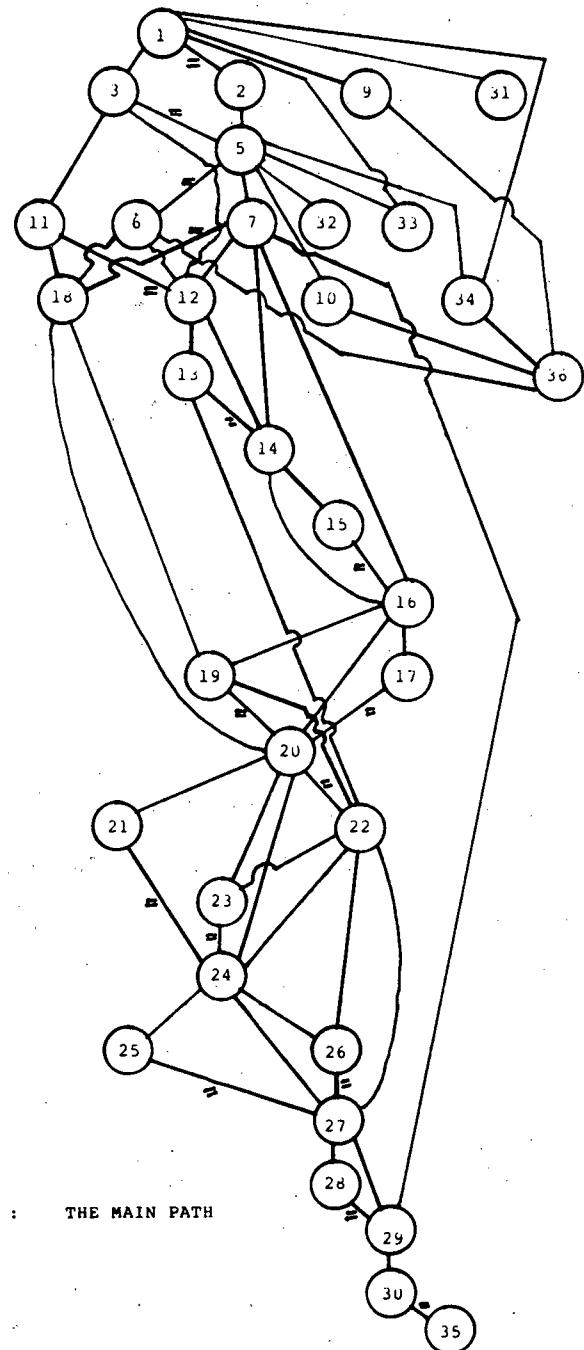

| Example 8.1 | An Example Using the PUMA                                 | 143 |

| 8.2         | The Multiply Set-Up From the PUMA 6600<br>Emulator        | 153 |

| 8.3         | The Normalize (OP CODE 24) From the PUMA<br>6600 Emulator | 156 |

## 1. Abstract and Summary

Microprogram optimization is the rearrangement of microcode written vertically, with one operation issued per step, into legal horizontal microinstructions, in which several operations are issued each instruction cycle. The rearrangement is to be done in a way that approximately minimizes the running time of the code.

We identify this problem with the problem of processor scheduling with resource constraints. As a result of this identification, the problem of optimizing basic blocks of microcode can be seen to be np-complete; however, we are able to use approximate methods for basic blocks which have good records in other, similar, scheduling environments. We use a method of scheduling called "priority list scheduling" in which the tasks are ordered according to some evaluation function, and then schedules are found by repeated scans of the list. Several evaluation functions are shown to perform very well on large samples of various classes of random data-precedence graphs with characteristics similar to those derived from microprograms. An evaluation function we produced is sensitive to both the data-precedence graph and the resource constraints; it performed best of those tested, though the differences among the four best functions, while statistically significant, were small.

A method of spotting resource bottlenecks in the derived data-precedence graph is adapted from a lower bound suggested by Fernandez and Bussel [FERN73]. This method permits us to produce the above-mentioned "resource considerate" evaluation

function, in which tasks which contribute directly to or precede bottlenecks have their priorities raised. We were also able to greatly reduce the complexity of the calculations necessary to compute the lower bound, thus making the above strategy more practical. The lower bound is further used to bound the percentage differences between the lengths of schedules produced and the optimal.

A method is suggested for optimizing beyond basic blocks. We treat groups of basic blocks as if they were one block, encoding the information necessary to control the motion of tasks between blocks as data-precedence constraints on the conditional tasks. We are thus able to optimize long paths of code, with no back branches, using the same methods used for basic blocks. These methods are efficient (order  $n^2$ ), and are capable of handling the long blocks obtained this way quite well. When loops are encountered, the contents of the loop are optimized, and then the loop is treated as a unit, with its own data-precedence constraints, permitting other tasks to move past, ahead of, or into the loop, as is appropriate. The code obtained seems as optimized as, and remarkably similar to, that obtained by hand.

## 2. Introduction to the Problem

Microprograms are sequences of microoperations (MOPs) which control the most fundamental resources of the computer. A MOP might, for example, control whether a register is written into during a particular clock cycle, or select which of several possible data paths might be fed into an adder. In many microprogrammable computers, the fact that several different parts of the hardware can operate simultaneously may be taken advantage of in the microprogram, and a collection of MOPs may be specified for a single microprogram cycle, rather than just one. Such microprograms are said to be horizontal (rather than vertical) and a collection of MOPs specified for a single cycle is called a microinstruction.

This is an investigation into the practicality of taking a sequential microprogram written for a horizontal machine and gathering the MOPs into microinstructions in a way that approximately optimizes the running time of the microprogram. Within basic blocks (no transfers of control), this corresponds to gathering the MOPs into as few microinstructions as possible; subject to, of course, the data-precedence requirements on the MOPs and the resource usage constraints, which will prohibit certain combinations of MOPs from being specified in the same microinstructions. Beyond basic blocks dynamic considerations apply and we

can no longer guarantee that improvements that shorten some branches of code at the expense of others will improve running time. We investigate such improvements at length but, as is the case with some compiler optimizations, it is difficult to measure their effectiveness except empirically. We remark here that the problem at hand does not otherwise bear much resemblance to compiler optimization, except in the use of some flow graph techniques. Indeed, we assume that all ordinary compiler optimizations have already been applied to the vertical code before the gathering into microinstructions.

The reader is invited to look at the source and object codes in the examples presented in Chapters 5 and 8. The code is written for the Courant Institute PUMA System, and, with proper documentation, the source code could be easily understood, having the flavor of assembly language level code. The corresponding horizontal code, however, is usually quite obscure.

#### Why This Is Important

After extensive experience with the highly horizontal PUMA microcode, it is clear that this aspect of microprogramming, producing parallel code, is most unpleasant, very time consuming, and very error prone. Furthermore, those not very familiar with the techniques would seem

essentially prevented from producing any practical microcode at all. Even for a skilled programmer, writing a large interpreter would be a most formidable task without automatic parallelization.

The same consideration appears to be true when one is compiling high level languages (machine dependent or independent) into horizontal microcode. While most compilation tasks involve the same concepts as compilation into machine language, it is essential that the compiler be able to make reasonably full use of the machine's resources. If user microprogramming of horizontal machines is going to become somewhat common, and this appears likely, it seems clear that the techniques investigated herein will be important. It is often mentioned in the literature that automatic parallelization is a necessary and missing systems aid; however, it is also felt that finding practical methods of parallelizing is a difficult problem toward which little progress has been made [AGER76], and is regarded as "next to impossible" [ROSS75].

### CHAPTER 3. Previous Investigations of This Problem

Fortunately, an excellent survey of methods of optimizing microprograms exists, Agerwala [AGER 76]. That survey, updated in March 1976, refers to the gathering of MOPs into microinstructions as "word dimension reduction" and generally considers it to be the most promising area of optimization. Nonetheless, the first paragraph of the conclusions section states

"Most of the important work to date on microprogram optimization has been surveyed in this paper and, unfortunately, the results are disappointing. Very few techniques exist that can be profitably applied in any practical environment."

The survey presented here supports that conclusion. It seems to be unknown whether any of the work done to date can provide enough help to the microprogramming systems designer to enable the writing of large programs using sequential code.

We now survey all the parallelization methods we were able to find. The main reduction algorithms are presented in some detail and an annotated bibliography contains all relevant references. The references are generally from two sources: the IEEE Computer Society Transactions on Computers and the SIGMICRO Yearly Workshop preprints. The SIGMICRO papers, unfortunately, are very loosely edited, and the algorithms are often imprecise. Despite that, they are the best source of current information.

In our descriptions of the algorithms we will use terminology from processor scheduling theory; indeed, in Chapter 5 we will formalize an identification between optimizing microcode and scheduling processors. Most terms should be clear enough from their contexts to provide a general understanding of the algorithms, but all terms used are defined carefully in the next chapter. For the time being, we may think of the MOPs as having a data-dependency relation upon them; that is, some MOPs will have to be placed in earlier microinstructions than others to preserve data validity. Using this relation, we form the data dependency graph referred to below. The tasks referred to in the following chapter definitions (Fig. 4.1) will be representing the MOPs, as we will explain in Chapter 5.

### Optimal Solutions

We can break the work done into two categories, algorithms which always find the optimal solution, and those which might not. We consider the former first; though none of them seems useful in a practical environment. Evidently, the first algorithm was proposed by Astopas and Plukas [ASTO 71]. They consider all possible gatherings of MOPs (partitionings) which don't violate the data dependencies; they then accept the shortest one which doesn't violate the resource conflict criterion.

An improvement upon this algorithm is made by Yau, et al. [YAU 74]. They generate only valid microinstruction partitionings, and not all of those; they then select the shortest, or stop if they obtain one which is provably minimal. Unfortunately, this still seems to use far too much time to be of much use. Of interest in that paper, though, is the fact that they use heuristics to guide the order in which the operations are grouped, stopping if they reach a provably minimal partition. Since they then present a not necessarily minimal algorithm which uses much the same heuristics, this paper is referred to later in this section.

Finally, an algorithm is given by Tabandah and Ramamoorthy [TABA74]. It is considered in the context of the SIMPL compiler (see the next reference) and is similar in style to the nonoptimal algorithm of Ramamoorthy and Tsuchiya, which is presented next. Again, this algorithm requires immense amounts of time and space and is not suggested as a practical solution.

#### Approximate Solutions

We now consider algorithms which produce suboptimal results but are possibly practical. The most important work seems to be that connected with the SIMPL compiler, Ramamoorthy and Tsuchiya [RAMA74]. SIMPL is a high level microprogramming language using the rather restrictive

single identity principle, in which variables may be assigned values only once. It is first compiled into sequential microcode and is then parallelized. Briefly, their parallelizing algorithm is as follows:

Ignoring resource constraints, they identify critical MOPs as those on the critical path(s), which are paths of maximal length on the data-precedence graph. The natural partitioning of these MOPs is taken, in which MOPs the same distance from the top are in the same partition. Each of these is then split up into the minimum number necessary to avoid resource conflict. (Here a potentially large loss of optimality is evident, as data and resource independent MOPs from adjacent partitions are never placed in the same new intermediate partition.) Finally the non-critical MOPs are placed in this scheme from earliest to latest; occasionally a new partition is formed for one of them when it would delay its successors too much to place it legally in an existing partition.

The next algorithm we consider is that of Tsuchiya and Gonzalez [TSUC74], also developed in relation to the SIMPL compiler and meant to be an improvement over the one given above. Briefly, they do the following:

The latest partitioning is formed, in which MOPs are placed as late as possible without increasing the number of partitions over the minimum, and with no regard paid to resource conflict. Individual partitions are then considered earliest

to latest. If no resource conflicts exist, as many MOPs as can be brought in legally from later partitions are and this becomes a permanent microinstruction. If conflicts do exist, all possible MOPs whose data dependencies will allow are brought into the partition and a choice of a permanent set of MOPs for this microinstruction is made. The remaining MOPs are pushed into the next partition, where they may have a ripple effect on their successors, possibly causing new instructions after what had been the last.

Unfortunately, the algorithm was not given in enough detail for us to resolve conflicts between the criteria given for choosing which MOPs to delay, and those actually delayed in a rather detailed example.

Next we consider the previously mentioned algorithm of Yau, Schowe, and Tsuchiya [YAU74]. This is rather different in spirit from the previous two in that it constructs microinstructions an instruction at a time, rather than starting with a more global partitioning and then altering it. Their algorithm is essentially:

The weight of a MOP is defined as its number of descendants (not necessarily direct descendants), and the weight of a microinstruction as the sum of the weights of its constituent MOPs. Microinstructions are formed one at a time, from the earliest to the latest, by considering every possible legal micro-

instruction producable from the MOPs not yet used and selecting the one with the greatest weight. We remark that only microinstructions which cannot have another MOP legally added to them need be considered for maximal weight.

As will be explained in more detail later, we found this the most interesting of the algorithms here, and investigated it in some detail.

Dasgupta and Tartar [DASG76] present an algorithm which they claimed to be optimal; however, it simply considers MOPs in their source order and places them each as early as possible without violating resource and data-dependency rules. Its nonoptimality is evident from very short examples [DASG78], but it is difficult to ascertain that from the algorithm, which is quite complex due to their handling of "poly-phase" microinstructions (which we will briefly discuss in Chapter 9, and which we feel would not present a great deal of difficulty in an implementation).

Finally, we consider the work of Tokoro et al. [TOKO77]. Just as was the case in [DASG76], they have a somewhat more general model, involving "microtemplates", which deals with many more options in microprogrammed machine design than we are considering here. As such, the optimization algorithm, as we would consider it, is somewhat obscured.

When projected down to our environment, however, their algorithm is the same as that in [YAU74], with the exception that they select the microinstruction at each level which has the most MOPs whose longest path distance to the bottom of the data dependency graph is greatest among the remaining MOPs. Ties are broken by simply picking the instruction with the most MOPs.

#### Beyond Block Optimization

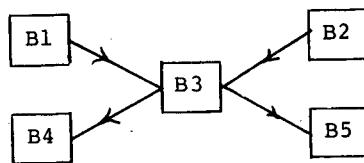

We were only able to find two references to optimization beyond basic blocks, a subject about which we will have much to say in Chapter 8.

The first, again an algorithm of Dasgupta [DASG77], only looks for pairs of basic blocks,  $(B_i, B_j)$ , with the property that  $B_j$  is executed during a run of the code if and only if  $B_i$  is. (For basic block definitions, see Chapter 8.) The earlier block,  $B_i$ , is parallelized, using the nonoptimal algorithm in [DASG76]. Then MOPs in  $B_j$  whose data dependencies allow are moved up into  $B_i$ , if they can be fitted into holes in the already existing optimization of  $B_i$ . (That is, without lengthening  $B_i$ .) Otherwise, they are scheduled in  $B_j$  according to the basic block algorithm.

The other reference to beyond basic block optimization, that of Tokoro et al. [TOKO78], is considerably more ambitious. Although a great many details are omitted, we can describe the spirit of their methods. They produce a

small catalog of the types of MOP motions from one block to another, such as moving a MOP from a block into all of the blocks that must follow it. (We have a catalog of that sort in Chapter 8.) They then proceed in an upward direction, moving MOPs into holes in already optimized blocks. Finally, the same thing is attempted in a downward direction.

## CHAPTER 4: Practical Results in Processor Scheduling Theory

Our approach to this problem has been to identify the main aspects of it with special cases of the processor scheduling problem with resource constraints. Processor scheduling theory has received wide study (e.g. see [COFF76]), and we have been able to use some of the results and methods of attack used for the more general problem.

### Processor Scheduling

The processor scheduling problem we are interested in can be described as follows: we are given a set of tasks to be processed,  $t_1, t_2, \dots, t_s$  and an acyclic partial order on those tasks (the partial order specifies a time precedence on the tasks, i.e. if  $t_i < t_j$ , then  $t_i$  must be completed before  $t_j$  begins). Each task takes some length of time to be processed, and we have  $m$  identical processors,  $P_1, \dots, P_m$  with which to process these tasks. Furthermore, there is a set  $R = \{r_1, r_2, \dots, r_n\}$  of resources and a function  $U$  where  $U(t_i, r_j)$  is between 0 and 1 and specifies the proportion of resource  $j$  which is used by task  $t_i$  in one time unit. In fact, we will restrict ourselves to tasks with identical times (or unit execution time - UET scheduling), but will in later sections make reference to situations in which tasks take longer than 1 unit (e.g.

the PUMA's 2 cycle add).

A schedule is an assignment of the tasks to discrete time units (this assignment is called partitioning; the time units, partitions) such that:

- (1) No more than  $m$  tasks are assigned to any time unit, corresponding to the  $m$  processors available to process them

- (2) If  $t_i < t_j$ ,  $t_i$  is assigned to an earlier time unit than  $t_j$

- (3) Given any resource,  $r$ , and any time unit, the sum of the  $U(t, r)$  for all  $t$ 's assigned to the time unit is less than 1; that is, we don't use up more of a resource than there is.

We are generally interested in finding schedules in which the number of time units used (the "length of the schedule") is near optimally small. Finding the actual minimum is np-complete; indeed it's np-complete under the restriction that there are but 2 processors, and one resource which tasks use either completely or not at all (see Ullman's paper in [COFF76]), and under other, similar restrictions [GARE74].

Our formal definitions for scheduling theory, given in Figure 4.1, make no mention of processors. Indeed, if we had an  $m$ -processor system, we could define a resource  $r_p$  such that  $U(t_i, r_p) = 1/m$  for all  $i$ , and  $r_p$  would completely

Figure 4.1

A Formal Description of Task Scheduling with Resources

**A. Schedule Definitions.**

1. We have a *set of tasks*  $T = \{t_1, t_2, \dots, t_s\}$  of size  $s$

(intuitively, the tasks are jobs which we are going to process).

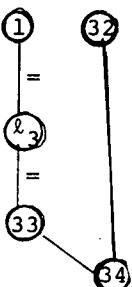

2. We have a *partial order*  $<$  on the tasks, and, thus an associated dag. We distinguish some of the edges by writing  $\leq$  rather than simply  $<$ , and in any picture we draw of the dag we place an " $=$ " next to any edge distinguished by a  $\leq$ .

(Intuitively,  $t_i < t_j$  means that we are required to process  $t_i$  before  $t_j$ .  $t_i \leq t_j$  means that we are required to process  $t_i$  no later than  $t_j$ .)

3. We have a *set of resources*  $R = \{r_1, r_2, \dots, r_u\}$  of size  $u$ .

(Intuitively, the  $r_i$ 's are things used in the processing of the tasks. We think of them as being present in limited amounts and we think of the tasks as competing for their use.)

4. We have a *map*  $U: \{T \times R\} \rightarrow [0,1]$  specifying the percentage of each resource used by each task

(i.e.  $U(t_3, r_7) = .125$  means that task 3 uses  $1/8$  of the available amount of resource 7).

5. We define a *partition* as any subset of  $T$ , and a *partitioning* as an ordered tuple of partitions which are mutually disjoint and exhaustive. That is, if for each  $i$ ,  $P_i \subseteq T$ , the  $P_i$ 's are partitions. If  $P = (P_1, \dots, P_k)$  such that  $P_j \cap P_i = \emptyset$ , unless  $i = j$ , and such that  $\bigcup P_i = T$ , then  $P$  is a partitioning.

Note that the partitioning is determined not only by the  $P_i$ 's, but also their order.

When we refer to a specific partitioning  $P = (P_1, \dots, P_k)$ , we say a task  $t$  is at level  $n$  when  $t \in P_n$ ; we also may refer to  $P_n$  as a *level* or *level n*, and call  $P_n$  a *cycle*.

6. We further say a partitioning  $P$  is a *legal partitioning* if both of the following hold:

- (a) Given any  $t$  and  $t' \in T$  such that  $t < t'$  with  $t$  at level  $n$  and  $t'$  at level  $m$ , then  $n < m$ . Similarly, if  $t \leq t'$ , then  $n \leq m$ .

- (b) Given any partition  $P_j$  in  $P$ , and any resource  $r_i \in R$ ,

$$\sum_{t_k \in P_j} U(t_k, r_i) \leq 1.$$

A legal partitioning is more commonly called a *schedule*.

(Intuitively, we think of our tasks as each taking one time unit to process. Each partition, then, is one time unit, and the tasks belonging to that partition are all thought of as being done in parallel in that time unit. Condition (a) then assures that the specified task precedence is not violated. Condition (b) assures that in no time unit is more than the available amount of any resource used.)

Figure 4.2

B. Directed Graph Definitions (used in describing algorithms):

1. If  $t_i < t_j$  or  $t_i \leq t_j$  we say that  $t_i$  is a predecessor of  $t_j$  and that  $t_j$  is a successor of  $t_i$ . When we wish to distinguish between the two types of precedence, we sometimes use the terms *strict predecessor* and *equal predecessor* with the obvious meanings. Similarly for successor.

2. We formally define the *height* of a task,  $\text{HEIGHT}(t)$ , as follows:

- (a) If a task has no successors, its height is 1.

- (b) Otherwise, find the successors of the task whose height is the largest, say height  $h$ . If one of those tasks is a strict successor, then the given task has height  $h + 1$ . Otherwise the given task has height  $h$ .

(The height may be thought of as the smallest number of time units required from the time processing starts on the given task to the end of the shortest possible schedule, given infinite resources.)

3. A *critical task* is any sequence of tasks such that:

- (a) each task is a predecessor of the following task.

- (b) the first task has no predecessors and is of the highest height in  $T$

- (c) the last task has no successors

We will refer to  $C$ , the "critical path length" in a graph, which is the height referred to in (b). Note that a critical path may have more than  $C$  tasks along it, due to  $=$  edges. Note also that  $C$  is a theoretical lower bound on any schedule, and that the bound would be achieved given infinite resources.

Any task which belongs to any critical path is called a *critical task*.

4. We define the *depth* of a task,  $\text{DEPTH}(t)$ , precisely as height was defined, with the word predecessor substituted for successor throughout.

5. The *earliest partitioning* is that in which the level of each task is its depth. The *latest partitioning* is that in which each task is at level  $(C - \text{height}) + 1$ , which we call  $\text{LATEST}(t)$ . Note that each of these partitionings has exactly  $C$  partitions.

(In the earliest partitioning, every task is done as early as possible, with no regard for resource usage. In the latest, each task is done as late as possible, without adding a level, with no regard for resource usage.)

6. Given a particular partitioning  $P$ , we say that task  $t$  is *data ready at level  $l$*  if all of its strict predecessors are contained in levels  $1, 2, \dots, l-1$  and all of its equal predecessors in levels  $1, 2, \dots, l$ .

describe the processor constraint. Since the systems we will be investigating do not in general have anything corresponding to the processor set, we left it out of the definitions. Also note that some partial order edges are distinguished by equals signs in our definitions. We will need the full generality of those edges later, for the purposes of this discussion, however, we may ignore the " $=$  edges".

#### Approximately Optimal Solutions and List Scheduling

We were not able to find anything in the literature but the roughest upper bounds on approximate algorithms for the full problem we are interested in. If one eliminates the resources, however, or eliminates the precedence relation, experiments have been done to rank some suggested strategies. In the case of no resources, a paper by Adam, Chandy and Dickson [ADAM74] studied various "list scheduling" strategies. List scheduling, which is summarized more formally in the last section of this chapter, basically involves choosing a heuristic function to assign a priority value to each task. The first partition is scheduled by choosing tasks, in order of their priorities, from those that are data-ready. Each task is examined to see if it can be placed in the time unit without any resources being used above capacity, and it is so placed, if possible. The partition is fixed when either no more data ready tasks

exist or all of the processors have been used up. Following partitions are then filled in the same way; scheduling is finished when no tasks remain. It is clear that a legal schedule is formed in this manner.

The attractions of list scheduling include:

- (1) It is fast and straightforward; in particular, no scheduled task is ever moved by a later step.

- (2) The heuristic portion of it is totally isolated from the scheduling aspects.

- (3) It has a record of good performance in some environments.

Adam et al. studied the list schedules produced by five strategies, namely:

- (1) The priority is the length of the largest chain from the given task to the exit. Since their model included nonunit task times, the priority is the total length of all tasks on the chain. They referred to this as HLFET (Highest levels first, estimated times); in our definitions (Fig. 4.2) we have referred to this as the height of a task, for UET scheduling.

- (2) As above, except ignoring tasks times, referred to as HLFNET (no estimated times).

- (3) Random priorities.

- (4) The priority is the closeness to the entrance of the graph, referred to as SCFET (Shortest co-levels). For UET scheduling, we could use -DEPTH to get the same ordering.

(5) As above, with no tasks times - SCFNET.

These strategies were used to produce list schedules for hundreds of precedence graphs, some containing hundreds of edges or nodes; some of the graphs were randomly produced, some culled from real programs. In all cases (and also when the same thing was done for tasks with stochastic task times), the results were in the same order: HLFET, HLFNET, SCFNET, RANDOM, SCFET with HLFET being the superior. What's more, the best known lower bound for this case, that of Fernandez-Bussel [FERN73], was rarely exceeded by HLFET in any class tested by more than 0.2 percent, even for very large graphs (one case was 16 percent worse, one 4, the rest under 2, and a great many hit the lower bound). As we will discuss in Chapters 6 and 7, we were able to put the ideas in [FERN73] to several good uses, but, for the moment, we note that these results demonstrate both the effectiveness of highest-level priorities and the tightness of the bound in this environment. The good performance of the highest level first strategies is not a great surprise; it has been in the folklore for some time that that's the right way. The CDC FTN Fortran compiler optimizes basic blocks this way, as does an optimizer for the CRAY-1 written by Richard Sites, and for some restricted classes of problems, optimal schedules can be formed using highest level type lists (see, e.g., [COFF72]).

## Resource Constrained Problems

Naturally, such strategies could be applied directly to resource constrained problems, but they would be what we have dubbed "resource inconsiderate". It is certainly true that one is often faced with a resource bottleneck that indicates priorities opposed to what would be suggested by a level heuristic; we shall see examples of that shortly. There is, as we have mentioned, a study [ECKE78] which has compared two resource considerate strategies, but in an environment in which the precedence relation was empty. Under such conditions, the problem is called "generalized bin packing" and the heuristics used generalize bin packing strategies. We refer to the two strategies tested as RMAX and NEIGHBORHOOD:

- (1) RMAX: the priority of a task is the maximum component in its resource usage vector, that is,

$$\text{PRIORITY}(t_i) = \max_j \{U(t_i, r_j)\}.$$

- (2) NEIGHBORHOOD: we define a relation CLOSE as:

two tasks,  $t_i$  and  $t_j$ , are close if they could ever be scheduled together without a resource being overused, i.e. for all  $k$ ,  $U(t_i, r_k) + U(t_j, r_k) \leq 1$ . Then the priority of a task is the number of tasks it is CLOSE to.

Eckert chose his simulation parameters in such a way that RMAX would seem to be favored, since individual resources are not often pairwise overused. Nonetheless, the NEIGHBORHOOD

strategy did noticeably, though not decisively, better.

Our concern is with the full problem. In the next two chapters the ideas of [ADAM74] and [ECKE78] are combined and extended, and many other ideas along similar and dissimilar lines are suggested and tested.

We close this chapter with a formal description of list scheduling.

#### A Formal Description of List Scheduling

In the absence of  $=$  edges, we have what is called, in the scheduling theory literature: *unit execution time (UET) scheduling with resources*. The quality of schedules is measured by the number of levels produced, and an aim of scheduling theory is the derivation of methods which produce short schedules.

We now present a method of UET scheduling called *list scheduling*, the desirable properties of which have been outlined in the accompanying text. This will later be modified to include  $=$  edges.

#### Algorithm: List Scheduling

Input:  $T, R, U, <$  given as in Figures 4.1 and 4.2, with accompanying definitions.

Uses: A separate routine — PRIORITYSET — forms a function  $PRI: T \rightarrow$  real numbers.  $PRI(t_i)$  is thought of as the *priority* that task  $t_i$  be scheduled early.

An ordered list of tasks, READY.

A set of tasks, NOT READY. NOT-READY  $\subset T$ .

Output: A schedule, namely a legal partitioning

$$P = \{P_1, P_2, \dots, P_\ell\}.$$

Method: We use a list called READY, the data-ready list, which initially contains all tasks without predecessors and which is sorted by priority.

The first level is formed by considering the tasks on the list in order and placing each one in that level if it does not cause any resource to be overused. A task so placed is deleted from the data ready list. After no more tasks can be placed, the data ready list is updated to contain all tasks which will, as a result of their predecessors' being scheduled, be ready at the next level. The next and following levels are scheduled in the same way.

Algorithm:

1. Call PRIORITYSET, defining  $PRI(t_i)$  for each task  $t_i \in T$ .

2.  $c = 1$ , READY = empty, NOT-READY =  $T$ ,  $P_1 = \emptyset$

3. For each task  $t_i \in$  NOT-READY which is now data ready, do:

- Place  $t_i$  on READY in order of  $PRI(t_i)$

- Delete  $t_i$  from NOT-READY

End.

4. Scan the READY list top to bottom (i.e. in order of priority). For each  $t_i$  on READY, if

for all  $k$ ,  $\sum_{t_j \in P_C} U(t_j, r_k) + U(t_i, r_k) \leq 1$

then do:

Place  $t_i$  in  $P_C$

Delete  $t_i$  from READY

End.

5. If tasks remain on READY or NOT-READY,

then do:

$c = c + 1$

$P_C = \emptyset$

go to step 3

end.

Otherwise, STOP. A schedule has been formed

from  $P_1, P_2, \dots, P_C$ .

Note: The above algorithm was chosen for clarity. It appears to require that  $|T|^2$  elements be scanned at step 4 in a total run of the algorithm, and this seems unlikely to be improvable. In practical terms, however, it is probably a significant constant factor faster to:

1. Keep a count of the predecessors of each task

2. Whenever a task is scheduled, decrement each of its successor's counts by 1

3. Whenever a task's count reaches 0 during the scheduling of some level, put the task on an ALMOST-READY list.

4. After scheduling is completed for some level, insert the the ALMOST-READY tasks onto the READY list.

Indeed, our implementation does this.

It is also worth noting that a sophisticated PRIORITYSET routine is apt to dominate the efficiency considerations.

## 5. Optimizing Basic Blocks of Microcode

### Formal Identification between Optimizing and Scheduling

We now do what we have been alluding to all along, that is, we recast our problem as one of processor scheduling with resource constraints. To make our formal identification, we will need to specify what our tasks are, how the partial order is defined, and what the resource mapping is to be.

Suppose we are given a basic block of sequential microcode (which will be defined carefully in Chapter 8, but which we informally say has no jumps out of the block, except at the end, and no jumps in, except at the beginning). We define as our tasks the individual MOPs. The resource usages of each MOP will be completely machine dependent, but will involve such resources as busses, ALU's, multiplexers, etc.

Our algorithm for determining the partial order on the MOPs is given in Figure 5.2. The algorithm presupposes that the registers read and written by each MOP are known and from those sets determines  $<$ , with some edges distinguished by an  $=$ , as explained earlier.

Formal Identification between Processor Scheduling

and Basic Block Microcode Optimization

| <u>Processor Scheduling</u>                               | <u>Microcode</u>                                                         |

|-----------------------------------------------------------|--------------------------------------------------------------------------|

| Set of tasks                                              | Micro operations                                                         |

| Acyclic partial order                                     | Data precedence relation<br>preserving data validity<br>(see Figure 5.2) |

| Resources                                                 | Hardware resources in<br>computer (e.g., ALU,<br>BUSES)                  |

| One time unit in a task<br>processor resource<br>schedule | A horizontal microinstruction                                            |

Figure 5.1

Rules for Formation of Partial Order on Micro-operations

Given:

1. A set of MOPs  $T = \{t_1, t_2, \dots, t_s\}$ , where  $T$  represents, with subscript order equal to source order, a basic block of MOPs.

2. A set of registers  $A = \{A_1, A_2, \dots, A_v\}$

3. For each  $t_i$ , two sets,  $\text{READ}(t_i)$  and  $\text{WRITE}(t_i) \subseteq A$ , not necessarily disjoint.

We produce a partial order  $<$  on  $T$ , with some edges distinguished by writing  $\leq$ , as follows:

For each pair of MOPs  $t_i, t_j$  with  $i < j$  (i.e.  $t_i$  comes before  $t_j$  in the source code):

1. If  $\text{READ}(t_i) \cap \text{WRITE}(t_j) \neq \emptyset$ , then  $t_i \leq t_j$  unless for each  $a \in \text{READ}(t_i) \cap \text{WRITE}(t_j)$  there is a  $k$  such that  $i < k < j$  and  $a \in \text{WRITE}(t_k)$ .

2. If  $\text{WRITE}(t_i) \cap \text{READ}(t_j) \neq \emptyset$ , then  $t_i < t_j$ , unless for each  $a \in \text{WRITE}(t_i) \cap \text{READ}(t_j)$  there is a  $k$  such that  $i < k < j$  and  $a \in \text{WRITE}(t_k)$ .

3. If  $\text{WRITE}(t_i) \cap \text{WRITE}(t_j) \neq \emptyset$ , then  $t_i < t_j$ . Unless for each  $a \in \text{WRITE}(t_i) \cap \text{WRITE}(t_j)$  there is a  $k$  such that  $i < k < j$  and  $a \in \text{WRITE}(t_k)$ .

4. If by the above rules, both  $t_i < t_j$  and  $t_i \leq t_j$ , then we write  $t_i < t_j$ .

Figure 5.2

Algorithm for the above:

Input:  $T, A, \text{READ}, \text{WRITE}$  as above, except  $T$  is augmented with a dummy task,  $t_0$ .

Uses: A function  $\text{LASTWRITE}: A \rightarrow T$  initially into a dummy task  $t_0$ .

A function  $\text{READS\_SINCE\_WRITE}: A \rightarrow \text{subsets of } T$ , initially into the empty set.

Output: A function  $\text{STRICTPRED}: T \rightarrow \text{subsets of } T$  and  $\text{EQUALPRED}: T \rightarrow \text{subsets of } T$ .

$t_j \in \text{STRICTPRED}(t_i)$  will mean that  $t_j < t_i$ , while  $t_j \in \text{EQUALPRED}(t_i)$  will mean that  $t_j \leq t_i$ .

Method: We consider the tasks in source order. For each task  $t_i$  we look at the set  $\text{READ}(t_i)$ . For each element  $a_j \in \text{READ}(t_i)$ , that is for each register that  $t_i$  reads, we put the last task to write  $a_j$ , (that is,  $\text{LASTWRITE}(a_j)$ ), in the set  $\text{STRICTPRED}(t_i)$ . We then add  $t_i$  to  $\text{READS\_SINCE\_WRITE}(a_j)$ .

Similarly, we consider each register  $a_k \in \text{WRITE}(t_i)$ . For each we put all the tasks belonging to  $\text{READS\_SINCE\_WRITE}(a_k)$  on  $\text{EQUALPRED}(t_i)$ . If  $\text{READS\_SINCE\_WRITE}(a_k)$  is empty, we put  $\text{LASTWRITE}(a_k)$  on  $\text{STRICTPRED}(t_i)$ . (If we did so even when  $\text{READS\_SINCE\_WRITE}(a_k)$  was not empty, it would still be correctly following rule 3 above, but would produce a redundant ("transitive") edge.) Finally

Figure 5.2

(Continued)

we set  $\text{READ\_SINCE\_WRITE}(a_k) = \emptyset$  and we set

$\text{LASTWRITE}(a_k) = t_i$ .

After processing each task, we "cleanup" by removing all edges from  $t_0$ , by removing all duplicate edges (resolving contentions in favor of  $\text{STRICTPRED}$ ), and removing all edges from a task to itself.

Algorithm:

INITIALIZE:

1.  $\text{STRICTPRED}(t_i)$ ,  $\text{EQUALPRED}(t_i)$  empty, for all  $t_i \in T$ .

2.  $\text{READS\_SINCE\_WRITE}(a_k) = \emptyset$ ,

$\text{LASTWRITE}(a_k) = 0$ , for all  $a_k \in A$ .

FORM EDGES:

3. For  $i = 1$  to  $s$  DO:

4. DO for each  $a_k \in \text{READ}(t_i)$ :

5.  $\text{STRICTPRED}(t_i) = \text{STRICTPRED}(t_i) \cup \{\text{LASTWRITE}(a_k)\}$

6.  $\text{READS\_SINCE\_WRITE}(a_k) = \text{READS\_SINCE\_WRITE}(a_k) \cup \{t_i\}$

7. END 4

8. DO FOR EACH  $a_k \in \text{WRITE}(t_i)$ :

9. IF  $\text{READS\_SINCE\_WRITE}(a_k) = \emptyset$  THEN

$\text{STRICTPRED}(t_i) = \text{STRICTPRED}(t_i) \cup \{\text{LASTWRITE}(a_k)\}$

10. ELSE DO:

Figure 5.2

(Continued)

11.  $\text{EQUALPRED}(t_i) = \text{EQUALPRED}(t_i) \cup \text{READS\_SINCE\_WRITE}(a_k)$

12.  $\text{READS\_SINCE\_WRITE}(a_k) = \text{empty}$

13. END 10

14.  $\text{LASTWRITE}(a_k) = t_i$

15. END 8

CLEANUP:

16.  $\text{STRICTPRED}(t_i) = \text{STRICTPRED}(t_i) - \{t_0\}$

17.  $\text{EQUALPRED}(t_i) = (\text{EQUALPRED}(t_i) - \text{STRICTPRED}(t_i)) - \{t_0, t_i\}$

18. END 3

NOTE: As implemented, the above avoids doing  $O(|T|^2)$  of any operation, the order of the most frequently executed steps being  $O(E)$ , the number of edges in the graph being formed. This required that for the  $t_i$  under consideration in steps 3 through 18, an array  $\text{ALREADY}(t_j)$  kept the status of the edge  $(t_j, t_i)$ , which was zero if no precedence was found, 1 if only equal precedence was found, and 2 if strict (or both) precedence(s) were found.  $(t_j, t_j)$  was set back to zero after  $\text{ALREADY}$  was built. All  $t_j \in \text{STRICTPRED}(t_i) \cup \text{EQUALPRED}(t_i)$  were then scanned, and a "cleaned-up" predecessor set was built from that information, with that step also taking  $O(E)$  steps. As Figure 5.4 shows,  $E$  is  $O(|T|)$  in this type of graph.

Figure 5.2

(Continued)

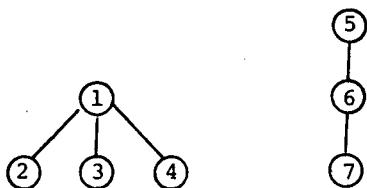

### An Example

We have provided an example, so that the application of scheduling theory, and particularly list scheduling, may be easily followed. Example 5.1a contains a short sequence of MOPs, written for the PUMA. We first identify the individual MOPs as the tasks; there are 7 of them, which we can refer to as  $t_1, t_2, \dots, t_7$ . Our goal is to bunch them into microinstructions, which we think of as the discrete partitions of a schedule. Corresponding to the precedence relation on the tasks we have data-prededence requirements on the MOPs, from the register usages in example 5.1b. The data-prededence requirements simply assure that no MOP reads a register before it is valid or after it has been erased, and we see in example 5.1c the data-prededence graph on  $t_1, \dots, t_7$ . Note that we use the term register rather loosely here. For example, since we are unlikely to be capable of a range analysis, we consider all of main memory to be one register, and we say that any MOP which reads any memory location must follow any (earlier source) MOP which writes any memory location and that two memory writes may not be permuted. This is not likely to be serious if the code being optimized is a microcoded emulator, since the memory references will strongly depend upon the algorithm being interpreted, rather than that in the microcode, and a range analysis is unlikely to provide much help. This is, however, a potentially serious deficiency when a given

|     | <u>SEQUENTIAL<br/>CODE</u> | <u>REGISTER (S)<br/>READ</u> | <u>REGISTER (S)<br/>WRITTEN</u> | <u>RESOURCE (S)<br/>USED *</u> |

|-----|----------------------------|------------------------------|---------------------------------|--------------------------------|

| (1) | AC = BUF                   | BUF                          | AC                              | ALU (1 unit)                   |

| (2) | YO = AC                    | AC                           | YO                              | XYRGBUS (1)                    |

| (3) | Y1 = AC                    | AC                           | Y1                              | XYRGBUS (1)                    |

| (4) | Y2 = AC                    | AC                           | Y2                              | XYRGBUS (1)                    |

| (5) | MQ = -BUF                  | BUF                          | MQ                              | ALU (1)                        |

| (6) | MQ = SHIFT(MQ,L1)          | MQ                           | MQ                              | SHIFTER (1)                    |

| (7) | MQ = SHIFT(MQ,L1)          | MQ                           | MQ                              | SHIFTER (1)                    |

5.1 a

5.1 b

5.1 d

\* We have one unit of each of these resources available.

5.1 c

Using PRIORITY( $t$ ) = HEIGHT( $t$ )

PRIORITY LIST: 5 1 6 2 3 4 7

Schedule:

```

5           MQ = -BUF

1 6         AC = BUF; MQ = SHIFT(MQ,L1)

2 7         YO = AC; MQ = SHIFT(MQ,L1)

3           Y1 = AC

4           Y2 = AC

```

5.1 e

Using PRIORITY LIST: 1 5 6 2 3 4 7

Schedule:

```

1

5 2

6 3

7 4

```

5.1 f

EXAMPLE 5.1 a-f

applications program is compiled into microcode. The programmer, or a smart compiler, may very well know that references differ and that no data-dependency is implied.

Example 5.1 has been chosen to have obvious data-dependencies. It is worthwhile to note that one of the characteristics of the microprogram level of a machine is that it tends to have many hidden and surprising register usages, reflecting some of the subtle aspects of the machine's design. While this complicates all aspects of microcode generation, it can make hand optimizing particularly difficult, especially when there has been a time lapse between the production and optimizing — as in debugging. This presents little difficulty to the automated optimizer, however.

Note that we mark some edges on our graph with an equals sign; this indicates that the following task can be done no earlier than the preceding one, but they may be done simultaneously. In many machines, PUMA included, master-slave flip-flops permit the valid reading of a register up to the time that the register writes occur. Thus a write to a register following a read of that register may be done in the same cycle as the read, but no earlier. Because of "= edges", a task may become data-ready in the course of scheduling a microinstruction if all of its remaining unscheduled predecessors had "= edges" to it at the start of the formation of the microinstruction

and all were scheduled in the microinstruction. Figure 5.3 specifies the changes necessary to our list scheduling algorithm, given at the end of Chapter 4, to allow for "= edges".

### Resource Constraints

We finally need to consider the resource constraints on MOPs. In the PUMA, and we suspect in most machines, the full generality of the resource usage function is never used. In most cases, each MOP uses a set of resources, usually one or two, and each resource it uses, it uses completely. Thus we would expect function values of all zeros, except for a few ones. A somewhat different form of resource conflict occurs when one considers hardware which has mode settings. That is, an arithmetic-logic unit might be able to operate in any of  $2^k$  modes, depending on the values of some lines. Two MOPs which require the ALU to operate in the same mode might not conflict, yet they both use the ALU, and would conflict with other MOPs using the ALU in different modes. A similar situation occurs when a multiplexer selects data onto a data path; two MOPs might select the same data, and we would say they have compatible use of the resource. The possibility of compatible usage makes efficient determination of whether a MOP conflicts with already placed MOPs more difficult. An interesting and efficient way of dealing with this is discussed elsewhere.

Alterations of List Scheduling to Account for "= Edges"

In the algorithm for list scheduling at the end of Chapter 4, replace step 4 with:

- 4a.  $\text{NEXT-READY} = \emptyset$

- 4b. Find the highest priority task on the READY list, call it  $t_i$ .

If  $\text{READY} = \emptyset$ , then do:

$\text{READY} = \text{NEXT-READY}$

GO TO STEP 5

end

- 4c. If for all  $k$ ,  $\sum_{t_j \in P_c} U(t_j, r_k) + U(t_i, r_k) \leq 1$

then do:

Place  $t_i$  in  $P_c$ .

For each equal successor  $t_j$  of  $t_i$  on the data precedence graph,

if: (i) All of  $t_j$ 's strict predecessors were scheduled in  $P_{c-1}$  or earlier

and (ii) All of  $t_j$ 's equal predecessors were scheduled in  $P_c$  or earlier

then do: remove  $t_j$  from NOT-READY

place  $t_j$  on READY

end

else Place  $t_i$  on NEXT-READY

- 4d. remove  $t_i$  from READY; go to step 4b.

Figure 5.3

In example 5.1d, we see that it is sufficient to consider only three resources to determine the conflict relations among the tasks — all other resources have been left out for simplicity. If we ignore these resources in forming our priorities and schedule using a highest level first list, as in example 5.1e, we see that five microinstructions are generated. With a little reflection, though, we can see that  $t_2$ ,  $t_3$ , and  $t_4$  all form a resource bottleneck, and  $t_1$  must be given priority over  $t_5$  to get through this bottleneck quickly, even though  $t_5$  has a higher level. It isn't just resource inconsiderate strategies which are unable to deal with this, though. Neither RMAX nor NEIGHBORHOOD would distinguish between  $t_1$  and  $t_5$ , since they both have precisely the same resource usages. Even a strategy like taking the sum of a task resource priority and level priority would fail here, since  $t_5$  would still have priority over  $t_1$ , and, as example 5.1f shows, putting  $t_1$  ahead of  $t_5$  would generate only four microinstructions.

Naturally, one can invent a clever example which will make any efficient strategy look bad and we were quite curious about whether this is a common situation. In Chapter 7 we report on experiments we have done to test many strategies for the production of list priorities.

### A. Note on Efficiency

List scheduling seems to be an  $n^2$  (in the number of tasks) time complexity algorithm, but when coded efficiently appeared to run linearly. After examination, a possible explanation occurred to us; namely, the code seemed linear in the number of edges in the data-precedence graph. While, normally, the edges of a dag grow as  $n^2$ , the number of edges derived according to the rules in Figure 5.2 is limited in one dimension by the number of registers used, which would not grow with the number of tasks (unless, possibly, if the memory locations were thought of as individual registers and a range analysis were done, which does not seem relevant to these optimizations). Thus the number of edges, and the algorithms used, grow linearly with the number of tasks. The argument that the number of edges grows as the product of the number of tasks and the number of registers is presented in Figure 5.4.

In summary, then, we see that the basic block problem is very little different from the scheduling problem presented in Section 4, but that the methods used on restrictions of the problem are possibly not effective enough on the full problem, even when combined.

Before presenting the results of our experiments we, in the next chapter, concern ourselves with a lower bound which will help us interpret the results of our experiments and will provide a basis for some of the strategies tested.

$E$  is  $o(|T|)$  in Data Precedence Graph:

We show here that the number of edges in the data dependency graph of a set of MOPs grows linearly in the number of MOPs, despite the fact that the in-degree and out-degree of any single MOP may itself grow linearly with the number of MOPs.

We are given a set of MOPs of size  $s$ , and a set of  $v$  registers, as in Figure 5.2.

According to Figure 5.2, there are three sources for edges  $(t_i, t_j)$  defined on the MOPs:

1. where  $t_i$  reads a register which is next written by  $t_j$ ,

2. where  $t_i$  writes a register which is read by  $t_j$ , before any other writes to the register

3. where  $t_i$  writes a register which is written by  $t_j$ , before any other reads or writes to the register (we say that  $t_i$  is an unreferenced write).

We claim that each of the above contributes at most  $v * s$  edges to the graph. For edges of type 1, we maintain that at most  $v$  edges could leave any task, since for each of the  $v$  registers that  $t_i$  reads, there will be at most one MOP which next writes that register. Thus each of  $s$  MOPs could follow  $t_i$  via a type 1 edge, and only  $v * s$  of them could exist.

Similarly, if  $t_j$  reads a register, then only one  $t_i$  could be the immediately preceding write of that register, and only  $v$  type 2 edges could have  $t_j$  as their target. Thus only  $v * s$  edges of type 2 could exist.

Finally, for each of the up to  $v$  registers that  $t_j$  writes, only one unreferred write could immediately precede it, and again only  $v * s$  edges could exist.

We see, then, that fewer than  $3 * v * s$  edges could be generated, and the number of edges is  $o(s)$ . This is somewhat surprising in light of the fact that one MOP could have in-degree of  $v * (s-1)/2$  and out-degree of  $v * (s-1)/2$ . This would happen, for example, if all MOPs read all registers, the middle MOP was the only one to write any register, and it wrote them all.

For a given machine,  $v$  is a small constant, but  $s$ , while possessing a theoretical upper bound, can grow large enough that algorithms requiring  $o(s^2)$  operations or space can take significantly longer than those requiring  $o(s)$ .

Figure 5.4

### A More Complex Example

We close this chapter with an actual example from the PUMA's existing, hand-optimized, microcode; the code is part of the emulation of the CDC 6600 central exchange jump. The example is of interest because, although it is not a frequently executed portion of code, much attention was paid to the hand optimization of the whole emulator. Most list schedules would produce code which requires eight cycles instead of the nine cycles found in the PUMA. Upon investigation, it is clear that the hand optimization was defeated by the intricacies of MOP compatibility, rather than data-dependency. It is also of interest to note that this is the only block in the PUMA code which wasn't done in obvious minimum time, and it seems that any reasonable strategy would produce minimum length code for every PUMA block. We'll have more to say about the implications of this in Chapters 7 and 8.

The exchange jump example is presented briefly and without comment as Example 5.2. Note that it includes two-cycle MOPs, which we consider in Chapter 9, and a jump MOP, which we force to the end, but which we consider at length in Chapter 8.

SOURCE CODE (AS PARALLELIZED IN PUMA):

```

CLEAR; AC = MQ; BUF = Y0

Y2 = AC; AC = AC & ~BUF

BM = AC; MQ = 0

BUF = Y2

AC = SHIFT(BUF:MQ, R16)

AC = SHIFT(AC:MQ, R1)

AC = SHIFT(AC:MQ, R1); BUF = Y0

Y2 = AC; AC = AC & ~BUF; P = P+1

AM = AC; = 7 + E1; IF EALUPOUT-

THEN XJEXTP

```

TASKS:

|    |   |    |   |    |                          |

|----|---|----|---|----|--------------------------|

| 1  | ; | 2  | ; | 3  | (i.e. 1 ≡ CLEAR<br>etc.) |

| 4  | ; | 5  |   |    |                          |

| 6  | ; | 7  |   |    |                          |

| 8  |   |    |   |    |                          |

| 9  |   |    |   |    |                          |

| 10 |   |    |   |    |                          |

| 11 | ; | 12 |   |    |                          |

| 13 | ; | 14 | ; | 15 |                          |

| 16 | ; | 17 |   |    |                          |

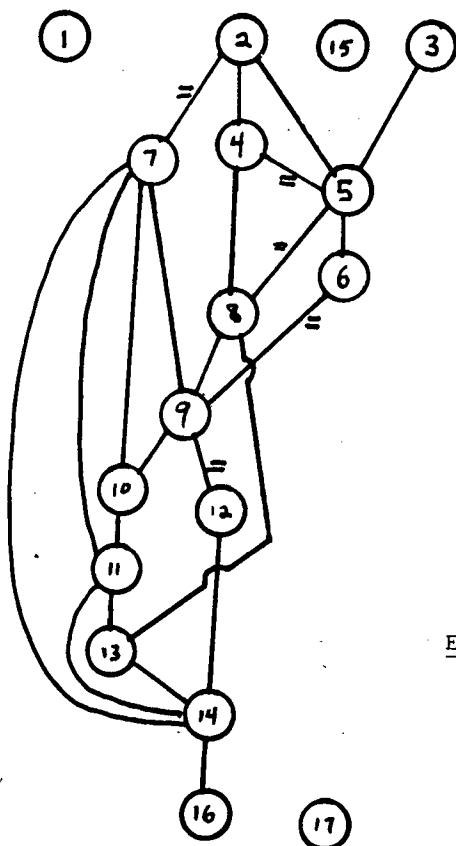

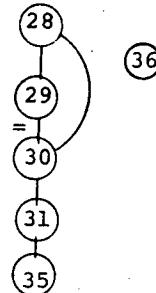

DATA-PRECEDENCE GRAPH

PRIORITY LIST:

|   |    |    |    |    |    |   |

|---|----|----|----|----|----|---|

| 2 | 3  | 4  | 5  | 7  | 8  | 6 |

| 9 | 10 | 11 | 12 | 13 | 14 |   |

| 1 | 15 | 16 | 17 |    |    |   |

(using  $\text{PRIORITY}(t) = \text{HEIGHT}(t)$ )

SCHEDULE:

|    |   |    |   |   |   |   |   |    |

|----|---|----|---|---|---|---|---|----|

| 1  | ; | 2  | ; | 3 | ; | 7 | ; | 15 |

| 4  | ; | 5  |   |   |   |   |   |    |

| 8  |   |    |   |   |   |   |   |    |

| 6  | ; | 9  |   |   |   |   |   |    |

| 10 | ; | 12 |   |   |   |   |   |    |

| 11 |   |    |   |   |   |   |   |    |

| 13 | ; | 14 |   |   |   |   |   |    |

| 16 | ; | 17 |   |   |   |   |   |    |

EXAMPLE 5.2

## 6. A Lower Bound and its Uses

### The Fernandez-Bussel Lower Bound and How It Works

Fernandez and Bussel [FERN73] have produced a lower bound on the number of cycles needed to schedule a set of tasks, given data-precedence, but no resource constraints. This bound was used in [ADAM74] to bound the distance of various list schedules from the optimal; the fact that any schedule is an upper bound on the length of an optimal schedule, and that the derived schedules were very near the bound, show that the bound was very tight in that environment. We have extended their bound, greatly reduced the computation necessary to calculate it, and have some suggested uses for it, beyond the obvious use as an experimental measure of the optimality of derived schedules.

Before explaining how the lower bound is found, we note that in [FERN73] the bound is given for systems that include tasks with arbitrary task times. Everything we do could be similarly presented, but we are primarily interested in unit execution time systems, and will, for clarity, restrict our presentation to such systems.

### Finding the Bound

Given  $m$  processors, we look at all intervals  $(i, j)$ ,  $1 \leq i \leq j \leq C$ , where  $i$  and  $j$  are integers, and  $C$  is the length of a critical path in the data-precedence graph.

For any such interval, say  $(i_0, j_0)$ , we consider the set of tasks  $t$  with the property that  $\text{DEPTH}(t)$  is  $i_0$  or later, and  $\text{LATEST}(t)$  is  $j_0$  or sooner. (For definitions, see Figure 4-2). Those tasks could not, by the definitions of  $\text{DEPTH}$  and  $\text{LATEST}$ , be scheduled any earlier than time  $i_0$  in a schedule of length  $C$ , nor any later than time  $j_0$ . Thus if an optimal schedule were to be only  $C$  units long, all of these tasks would have to be scheduled in  $i_0 - j_0 + 1$  time units. But if there are  $T$  such tasks, then it will take at least  $T/m$  time units, and  $(T/m) - (i_0 - j_0 + 1)$  extra units above  $C$  will be required. We look at all intervals to find the one that contributes the greatest number of extra cycles,  $E$ . The shortest possible schedule will then be  $\geq (C+E)$  units long. We thus have the formula presented in Figure 6-1 for our bound, which has been extended to include resources, as explained in 1, below.

#### How the Bound Loses Accuracy

The Fernandez-Bussel bound is excellent at finding local bottlenecks. Unfortunately, we can only be sure that the number of extra cycles is the largest number found for any one interval. That is, if intervals  $(i, j)$  and  $(i', j')$ , with  $i < j < i' < j'$  each contributed three extra cycles, one cannot, in general, be sure whether three, six, or some intermediate number of extra cycles would

The Fernandez-Bussel Lower Bound:

Given:  $R$  the set of resources,  $C$  the length of a critical path

EARLY, LATEST:  $T \rightarrow$  integers  $[1, C]$

USAGE:  $T \times R \rightarrow [0, 1]$

all as defined previously.

then if

$$E = \max_{\substack{1 \leq j \leq C \\ 1 \leq i \leq j \\ r \in R}} \left\{ \left( \sum_{t \text{ such that} \atop i \leq \text{DEPTH}(t)} \text{USAGE}(t, r) \right) - (j+1-i) \right\}$$

Then  $\neq$  the length of an optimal schedule  $L_{\text{OPT}}$  is

$$L_{\text{OPT}} \geq C + E .$$

Figure 6-1 .

suffice to relieve both bottlenecks. We searched rather hard for a set of criteria to help measure that number, but were unsuccessful. It is our belief that the number is generally the sum of the two disjoint bottlenecks, especially when the graph has many edges. As a result, the greater the length of the critical path, the less accurate the bound is likely to be. In Chapter 7 our experimental results will speak to that point.

#### Our Work On and Suggested Uses of the Bound

We have done the following in relation to this bound:

1. Extension to processor scheduling with resource constraints. It is possible, in the obvious way, to consider each resource separately and to calculate the usage of each resource in each interval. (In fact, the processors themselves can be considered a resource of which each task uses  $1/m$ .) The resource-interval which contributes the most extra cycles will determine the lower bound. Unfortunately, the interaction of a set of tasks restricted to a certain interval will generally involve several resources and, in practice, the bound seems to miss the heavy resource bottlenecks. If, however, the tasks tend to use only one resource apiece, that is, if the tasks form equivalence classes with respect to which resources they use, then we are much more likely to find the worst

bottleneck. Microoperations seem to have approximately this property; the relation of clashing is generally transitive and is certainly reflexive. Some insight into the utility of this extension may be gained from the results of the experiments reported on in Section 7.

2. Efficient computation of the bound. The computational methods suggested in [FERN73] require looking at all  $\Theta(|T|^2)$  intervals and doing a set formation of complexity at least  $\Theta(|T|)$  for each interval. Thus their methods require  $\Theta(|T|^3)$  operations, at least. Our methods, presented at the end of this chapter, do a constant amount of work for each of the  $\Theta(|T|^2)$  intervals, thus requiring  $\Theta(|T|^2)$  operations.

We report on the actual computation time used by an implementation of our algorithm in Chapter 7.

3. Use of the bound as a guide to places to invest more time. Although it is true that when a derived schedule is significantly longer than the bound the fault may lie with either, such cases give some indication that an investment of more time may be worthwhile. In particular, finding spots in the list schedule where a data-ready task was delayed due only to resource constraints and trying again with a different task delayed may pay off. It may be worthwhile, in view of the reason for the loss of accuracy

of the bound, to sum up the extra cycles yielded by some set of disjoint intervals. If that sum were significantly less than the derived schedule length, further search would be indicated.

4. Resource considerate heuristics. Were it not for the data-precedence graph, scheduling with resources would be a generalization of bin-packing to weight-vectors, rather than simple weights. Various heuristics have been suggested for the generalized bin-packing problem [ECKE78], but it is not clear how to apply these heuristics to tasks on a data-precedence graph. We have attempted to use the bottlenecks found by the bound as an aid in the production of resource considerate schedules. Our method was successful, in that it consistently produced the shortest schedules of any method we tested, and could probably be "fine tuned" to do even better. Whether it offers enough improvement over simpler strategies is environment dependent; Chapter 7 contains an experimental measurement of that improvement.

Our method involves altering highest level priorities to compensate for resource bottlenecks. Rather than use the lower bound to spot only the worst bottleneck, we consider all resource-interval pairs which need extra cycles. For each such interval, we note which tasks contributed to the resource bottleneck, and we boost their priorities (and those of their

predecessors) beyond what is obtained from strictly data-precedence considerations. This would seem intuitively, to zero in more firmly on the resource constraints than strategies which permit the measurement, for example, of the resource contentions of tasks which would be unlikely to compete for scheduled places. Again, Section 7 contains a precise statement of the heuristics used, as well as a summary of experiments done.

#### Efficient Calculation of the Bound

Algorithm: Efficient calculation of Fernandez-Bussel Lower Bound, extended to resources.

Input:  $T$ , set of tasks

LATEST, DEPTH functions:  $T \rightarrow$  integers  $[0, C]$

$U$  function:  $T \times R \rightarrow [0, 1]$

$C$  length of critical path of dag defined on  $T$

all as previously defined

Output:  $E$  where  $C + E$  is a lower bound on the length of a schedule for  $T$

Uses: LPTR function: integers  $[1, C] \rightarrow$  subsets of  $T$

where  $LPTR(i)$  is  $\{t_j \in T \text{ such that } LATEST(t_j) = i\}$

SUME, SUML functions: integers  $[0, 1] \times R \rightarrow$  real numbers where, initially,

$$SUME(i, r_k) = \sum_{\substack{t_j \text{ s.t.} \\ DEPTH(t_j) = i}} U(t_j, r_k)$$

That is,  $SUME(i, r_k)$  is the amount of  $r_k$  used by all tasks whose "earliest issue time" (DEPTH) is  $i$ .

SUML is the same, with LATEST replacing DEPTH

TOTAL USAGE function:  $R \rightarrow$  real numbers where

$$\text{TOTALUSAGE}(r_k) = \sum_{t \in T} U(t, r_k)$$

B fixed right endpoint of the major and minor intervals

A varying left endpoint of the minor intervals

MAJOREXCESS the amount of the resource currently under consideration which is used by tasks constrained to the major interval under consideration, in excess of the amount that interval could process.

MINOREXCESS Same as MAJOREXCESS, for minor intervals

MAXEXCESS the maximum of the MINOREXCESSes.

METHOD: For each resource, we consider all of the  $O(C^2)$  intervals  $[i, j]$ , with  $1 \leq i \leq j \leq C$ , called the minor intervals. For each minor interval we determine what the excess resource requirement is, that is, how much of a resource,  $r_k$ , is used by tasks "critically constrained" (see below) to  $[i, j]$ , above the  $j+1-i$  units of  $r_k$  which could be processed in  $[i, j]$  with no additional cycles. A task  $t$  is critically constrained to  $[i, j]$  if  $i \leq \text{DEPTH}(t) \leq \text{LATEST}(t) \leq j$ . We call those excesses the MINOREXCESSes, and, from Figure 6-1, we are looking for the largest such

excess. We will gather the minor intervals into C chains in such a way that the excess for any interval is the excess of its predecessor minus some already known value. The first interval on each chain is referred to as the major interval, and the chains are arranged as follows:

| <u>Major Intervals</u> | <u>Minor Intervals</u>                                                                            |

|------------------------|---------------------------------------------------------------------------------------------------|

| $[1, C]$               | $\rightarrow [2, C] \rightarrow [3, C] \rightarrow \dots \rightarrow [C-1, C] \rightarrow [C, C]$ |

| $[1, C-1]$             | $\rightarrow [2, C-1] \rightarrow \dots \rightarrow [C-1, C-1]$                                   |

| .                      | .                                                                                                 |

| .                      | .                                                                                                 |

| $[1, 2]$               | $\rightarrow [2, 2]$                                                                              |

| $[1, 1]$               |                                                                                                   |

To process the minor intervals, we set up a nested loop. The outer loop iterates through the major intervals from  $[1, C]$  to  $[1, 1]$ . The inner loop processes the chain headed by the major interval.

Consider the first chain. The MINOREXCESS of  $[1, C]$  is TOTALUSAGE - C. For  $[2, C]$  we need to eliminate the tasks which are critically constrained to  $[1, C]$  (which all tasks are) but whose DEPTH is 1. These tasks, however, have a total resource usage of  $SUME(1, r_k)$ , and so we need only subtract  $SUME(1, r_k)$  from MINOREXCESS, and then add 1 because we are losing one cycle and can process one unit less of  $r_k$ . We continue this way, subtracting SUME and

adding 1 until we do  $[C, C]$ .

We now consider the second chain.  $[1, C-1]$  has the same excess as  $[1, C]$  had, minus  $SUML(C, r_k)$ , plus 1, by the same reasoning as above. A problem arises, however, on the transition from  $[1, C-1]$  to  $[2, C-1]$ . This transition cannot be done by subtracting  $SUME(1, r_k)$  because some of the tasks which contributed to  $SUME(1, r_k)$  had LATEST of  $C$ , and thus were not critically constrained to  $[1, C-1]$  and were not included in the excess. Thus, after we chop off an end point to go from one major interval to the next, we must update all of the  $SUME$  function values affected. This is straightforward enough; when we go from  $[1, C]$  to  $[1, C-1]$ , we take all tasks  $t$  in  $LPTR(C)$  and, for each, subtract its usage from  $SUME(DEPTH(t), r_k)$ .

The formal algorithm:

1. In one pass through  $T$ , Form  $LPTR$ ,  $SUME$ ,  $SUML$ ,  $TOTALUSAGE$

2.  $MAXEXCESS=0$

3. Do for each  $r_k \in R$

4.  $MAJOREXCESS = TOTALUSAGE(r_k) - C$

*/\* MAJOREXCESS is likely to start negative \*/*

5. Do  $B=C$  to 1 BY -1

6.  $MINOREXCESS = MAJOREXCESS$

7. DO  $A=1$  TO  $B$

8.  $MAXEXCESS = MAX(MAXEXCESS, MINOREXCESS)$

9.  $MINOREXCESS=MINOREXCESS + 1 - SUME(A, r_k)$

10. END 7

11.  $MAJOREXCESS=MAJOREXCESS + 1 - SUML(B, r_k)$

```

12. /* Update the SUME's to reflect new B */