235

10/7/77

# MASTER

## PHASE I OF THE AUTOMATED ARRAY ASSEMBLY TASK OF THE LOW COST SILICON SOLAR ARRAY PROJECT

Motorola Report No. 2258/4

Annual Technical Report

M. G. Coleman

R. A. Pryor

L. A. Grenon

I. A. Lesk

Date Published—February 1977

Work Performed Under Contract No. NAS-7-100-954363

Motorola Incorporated

Semiconductor Group

5005 East McDowell Road

Phoenix, Arizona 85008

**ENERGY RESEARCH AND DEVELOPMENT ADMINISTRATION**

**Division of Solar Energy**

## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.**

## **DISCLAIMER**

**Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.**

## NOTICE

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Energy Research and Development Administration, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

This report has been reproduced directly from the best available copy.

Available from the National Technical Information Service, U. S. Department of Commerce, Springfield, Virginia 22161

650

Price: Paper Copy \$5.50 (domestic)

\$8.00 (foreign) 13.00

Microfiche \$3.00 (domestic)

\$4.50 (foreign)

PHASE I OF THE AUTOMATED ARRAY ASSEMBLY TASK

OF THE LOW COST SILICON SOLAR ARRAY PROJECT

MOTOROLA REPORT NO. 2258/4

## ANNUAL TECHNICAL REPORT

FEBRUARY, 1977

**NOTICE**

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Energy Research and Development Administration, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

JPL CONTRACT NO. 954363

BY

M. G. COLEMAN, R. A. PRYOR, L. A. GRENON, and I. A. LESK

PREPARED BY

MOTOROLA INC. SEMICONDUCTOR GROUP

5005 EAST McDOWELL ROAD

PHOENIX, ARIZONA 85008

This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, under NASA Contract NAS7-100 for the U. S. Energy Research and Development Administration, Division of Solar Energy.

The JPL Low-Cost Silicon Solar Array Project is funded by ERDA and forms part of the ERDA Photovoltaic Conversion Program to initiate a major effort toward the development of low-cost solar arrays.

88

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

**THIS PAGE

WAS INTENTIONALLY

LEFT BLANK**

## TABLE OF CONTENTS

| <u>SECTION</u> | <u>TITLE</u>                                | <u>PAGE</u> |

|----------------|---------------------------------------------|-------------|

| 1.0            | Summary                                     | 1           |

| 2.0            | Introduction                                | 2           |

| 3.0            | Technical Discussion                        | 3           |

| 3.1            | Design Improvements                         | 3           |

| 3.1.1          | Baseline Design Model Considerations        | 3           |

| 3.1.1.1        | Antireflection Coating                      | 3           |

| 3.1.1.2        | Front Surface                               | 4           |

| 3.1.1.3        | Junction Region                             | 4           |

| 3.1.1.4        | Substrate                                   | 5           |

| 3.1.1.5        | Back Surface                                | 6           |

| 3.1.1.6        | Metallizations                              | 7           |

| 3.1.2          | Textured Surface                            | 7           |

| 3.1.3          | Schottky Barrier Solar Cells                | 15          |

| 3.1.3.1        | Schottky Barrier Solar Cell Bibliography    | 17          |

| 3.1.4          | Front Surface Metallization                 | 18          |

| 3.1.5          | Back Surface Metallization                  | 20          |

| 3.1.6          | Metallization Test Pattern                  | 23          |

| 3.2            | Process Adaptation                          | 26          |

| 3.2.1          | Evaluation Criteria                         | 27          |

| 3.2.2          | Technology Assessment Categories            | 28          |

| 3.2.3          | Starting Condition of Silicon Surface       | 29          |

| 3.2.3.1        | Sawed Surface (Category 1)                  | 29          |

| 3.2.3.2        | Sawed and Etched Surface (Category 4)       | 30          |

| 3.2.3.3        | Lapped and/or Polished Surface (Category 1) | 30          |

TABLE OF CONTENTS

| <u>SECTION</u> | <u>TITLE</u>                                       | <u>PAGE</u> |

|----------------|----------------------------------------------------|-------------|

| 3.2.3.4        | Cleaved Surface (Category 2)                       | 31          |

| 3.2.3.5        | As-Grown Sheet Surface (Category 2)                | 31          |

| 3.2.3.6        | Texture-Etched Surface (Category 4)                | 32          |

| 3.2.4          | In-Process Surface Cleaning or Etching             | 33          |

| 3.2.4.1        | Wet Chemical Cleaning or Etching (Category 4)      | 33          |

| 3.2.4.2        | Plasma Cleaning or Etching (Category 4)            | 33          |

| 3.2.4.3        | Vacuum Baking and Reverse Sputtering (Category 1)  | 35          |

| 3.2.4.4        | Texture-Etching (Category 4)                       | 35          |

| 3.2.4.5        | Cleaning by Scrubbing (Category 4)                 | 35          |

| 3.2.4.6        | Gas Stream Drying (Category 4)                     | 36          |

| 3.2.4.7        | Gravity (Centrifuge) Drying (Category 4)           | 36          |

| 3.2.5          | Lifetime Enhancement and Preservation (Category 3) | 36          |

| 3.2.5.1        | Literature Survey of Gettering                     | 37          |

| 3.1.5.2        | Gettering Bibliography                             | 39          |

| 3.2.6          | Junction Formation                                 | 41          |

| 3.2.6.1        | Epitaxy (Category 1)                               | 41          |

| 3.2.6.2        | Diffusion (Category 4)                             | 41          |

| 3.2.6.3        | Ion Implantation (Category 4)                      | 44          |

| 3.2.6.4        | Alloy (Category 1)                                 | 45          |

| 3.2.7          | Contact Metallization                              | 45          |

| 3.2.7.1        | Vacuum Deposition (Category 1)                     | 46          |

| 3.2.7.2        | Plating (Category 4)                               | 47          |

| 3.2.7.3        | Chemical Vapor Deposition (Category 1)             | 47          |

| 3.2.7.4        | Printing (Silk Screening) (Category 4)             | 47          |

TABLE OF CONTENTS

| <u>SECTION</u> | <u>TITLE</u>                                                                                                                | <u>PAGE</u> |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|

| 3.2.7.5        | Lamination (Category 2)                                                                                                     | 51          |

| 3.2.7.6        | Solder Coating (Category 4)                                                                                                 | 51          |

| 3.2.8          | Antireflection (AR) Coating                                                                                                 | 51          |

| 3.2.8.1        | Vacuum Deposition (Category 4)                                                                                              | 51          |

| 3.2.8.2        | Chemical Vapor Deposition (Category 4)                                                                                      | 52          |

| 3.2.8.3        | Direct Growth ( $\text{SiO}_2$ ) (Category 1)                                                                               | 53          |

| 3.2.8.4        | Plasma Deposition (Category 2)                                                                                              | 53          |

| 3.2.8.5        | Spin-On or Spray-On Deposition (Category 3)                                                                                 | 53          |

| 3.2.9          | Annealing                                                                                                                   | 54          |

| 3.2.9.1        | Resistance Furnace Heating (Category 4)                                                                                     | 54          |

| 3.2.9.2        | Direct Radiant Heating:<br>High Temperatures (Category 2)<br>Low Temperatures (Category 4)                                  | 55          |

| 3.2.9.3        | Laser and Electron-Beam Heating (Category 3)                                                                                | 55          |

| 3.2.9.4        | RF Heating (Category 1)                                                                                                     | 55          |

| 3.2.10         | Patterning                                                                                                                  | 56          |

| 3.2.10.1       | Photolithography (Category 4)                                                                                               | 56          |

| 3.2.10.2       | Shadow Masking:<br>Vacuum Metallization (Category 1)<br>Printed Metallization (Category 4)<br>Ion Implantation (Category 4) | 56          |

| 3.2.11         | Interconnection                                                                                                             | 57          |

| 3.2.11.1       | Solder Reflow (Category 4)                                                                                                  | 57          |

| 3.2.11.2       | Thermal Compression and Ultrasonic Lead<br>Bonding (Category 1)                                                             | 57          |

## TABLE OF CONTENTS

| <u>SECTION</u> | <u>TITLE</u>                                                               | <u>PAGE</u> |

|----------------|----------------------------------------------------------------------------|-------------|

| 3.2.11.3       | Welding (Category 3)                                                       | 58          |

| 3.2.11.4       | Filled Adhesives (Category 2)                                              | 58          |

| 3.2.11.5       | Clamped Connectors (Category 1)                                            | 58          |

| 3.2.12         | Category 4 Processes                                                       | 65          |

| 3.3            | Process Sequencing Optimization and Solar Cell Fabrication                 | 66          |

| 3.3.1          | Textured Surface-Photoresist Interactions                                  | 66          |

| 3.3.2          | Process Sequence Selection                                                 | 67          |

| 3.3.2.1        | Ion Implantation/Diffusion Process Sequence                                | 69          |

| 3.3.2.2        | Diffusion Process Sequences                                                | 69          |

| 3.3.3          | Solar Cell Fabrication                                                     | 71          |

| 3.4            | Interconnection and Encapsulation                                          | 72          |

| 3.4.1          | Interconnection                                                            | 73          |

| 3.4.2          | Module Materials and Encapsulation                                         | 74          |

| 3.4.3          | Protective Coatings for Metal Encapsulant Parts                            | 74          |

| 3.4.4          | Moisture Ingression                                                        | 75          |

| 3.5            | Cost Analysis                                                              | 76          |

| 3.5.1          | General and Specific Cost Assumptions                                      | 78          |

| 3.5.2          | Process Step Costs                                                         | 92          |

| 3.6            | Process Sequence Choice                                                    | 96          |

| 3.7            | Cost Limits, Projections, and Process Areas Requiring Advanced Development | 104         |

| 3.7.1          | Development of Automation and Scale-Up Concepts                            | 105         |

| 4.0            | Conclusions                                                                | 106         |

| 5.0            | Recommendations                                                            | 107         |

## TABLE OF CONTENTS

| <u>SECTION</u> | <u>TITLE</u>         | <u>PAGE</u> |

|----------------|----------------------|-------------|

| 6.0            | Current Problems     | 107         |

| 7.0            | Work Plan Status     | 107         |

| 8.0            | List of Action Items | 107         |

## LIST OF FIGURES

| <u>FIGURE</u> | <u>TITLE</u>                                                                                                                                                                                                                                                                                                    | <u>PAGE</u> |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

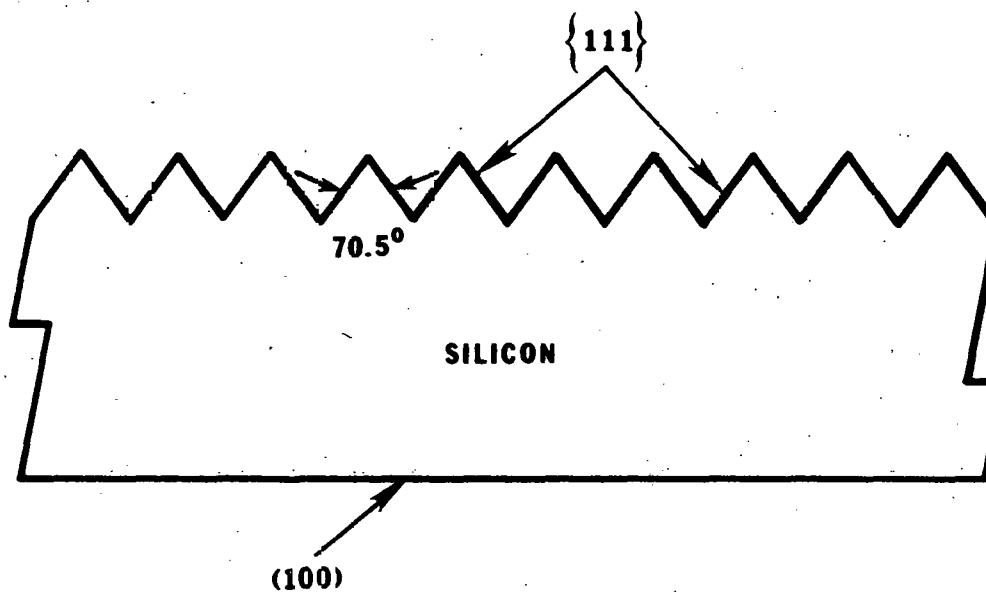

| 3-1           | Cross-sectional diagram of silicon (100) wafer showing geometry of textured surface having {111} faceted pyramids.                                                                                                                                                                                              | 8           |

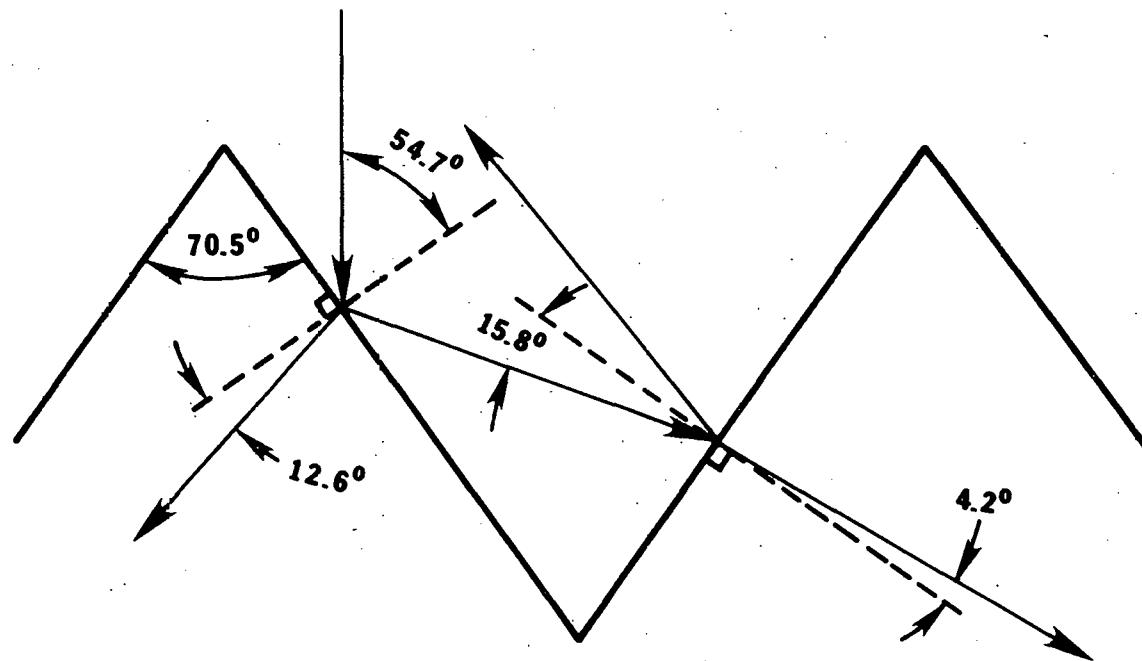

| 3-2           | Diagram of reflected and refracted ray traces and angular relations for light normally incident to the substrate (100) plane of a textured surface solar cell.                                                                                                                                                  | 9           |

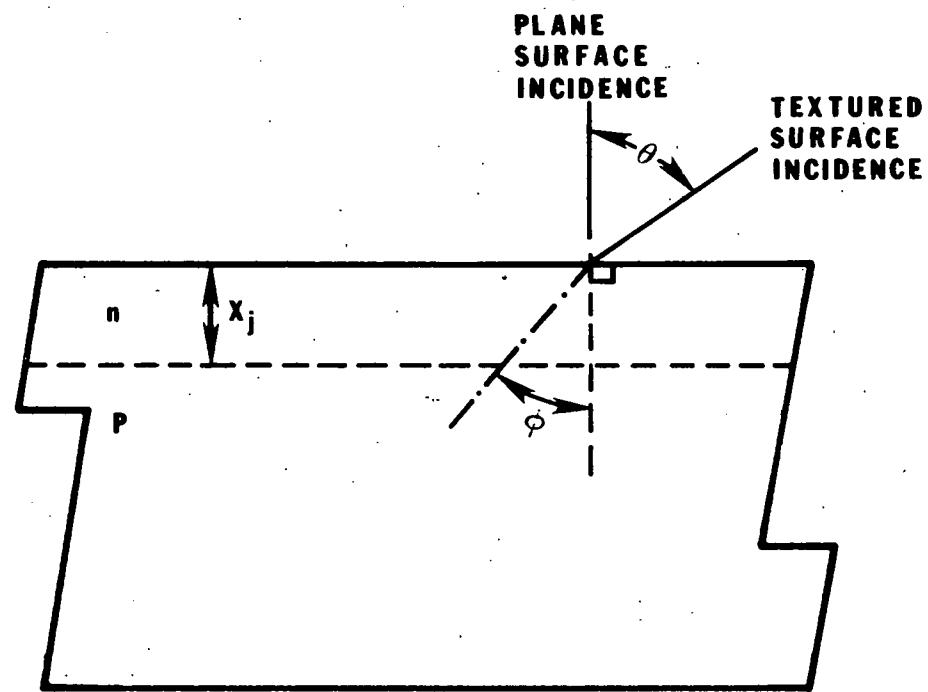

| 3-3           | Representation of increased absorption path length of textured surface and light ray trace compared to trace normal to a plane surface.                                                                                                                                                                         | 11          |

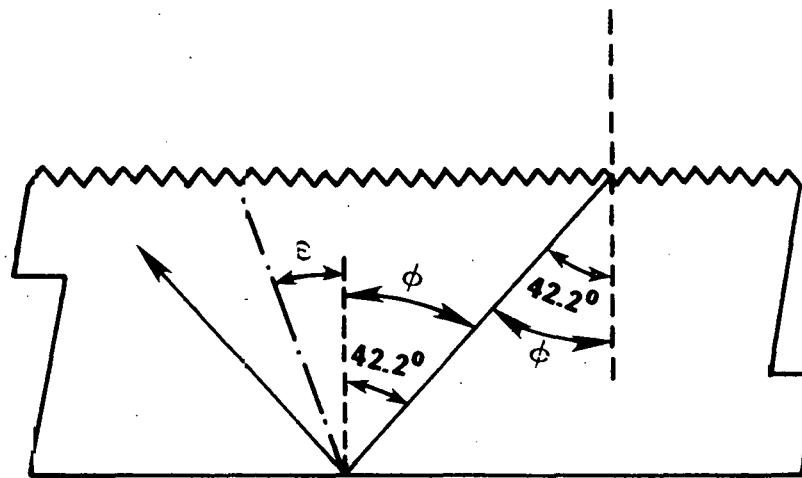

| 3-4           | Path of beam refracted from textured surface illustrating total internal reflection from back surface if the brewster angle $\epsilon < 42.2^\circ$ .                                                                                                                                                           | 13          |

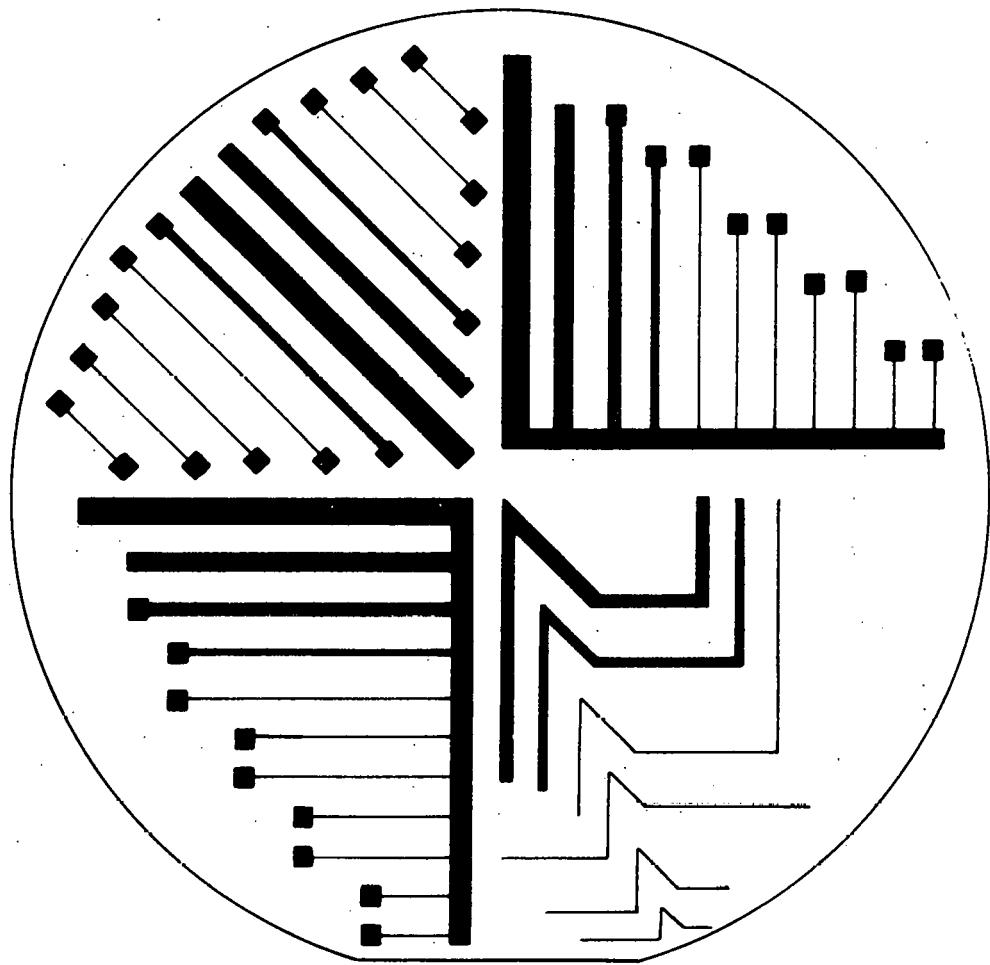

| 3-5           | Metallization and solder test pattern. The pattern contains linewidths ranging from 0.0003 inch to 0.0500 inch. Pattern is designed such that lines are withdrawn from solder coating at horizontal, vertical, and angular directions. In addition, the pattern contains included angles of 45°, 90°, and 135°. | 24          |

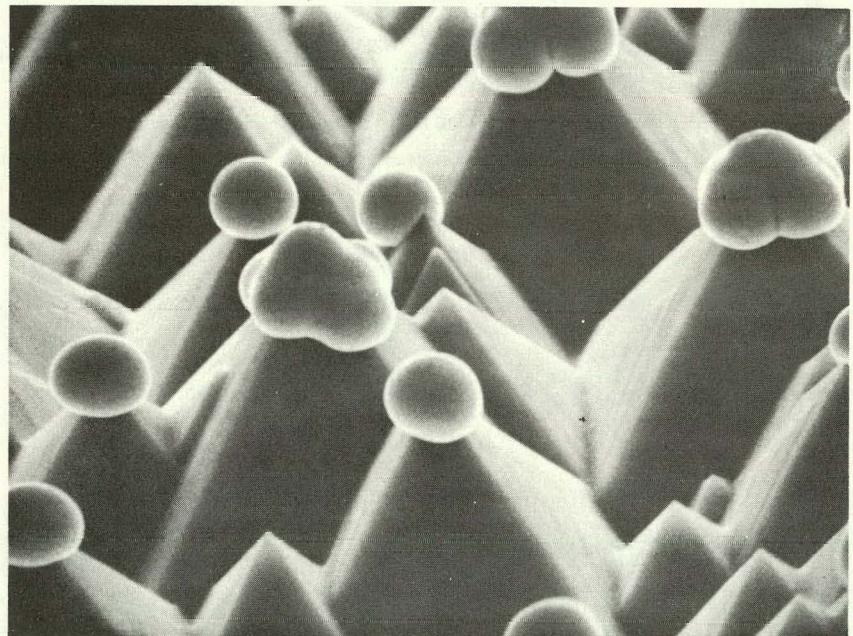

| 3-6           | SEM photomicrograph of electroless nickel plated surfaces of unprotected pyramid peaks, 5000X, 60° tilt.                                                                                                                                                                                                        | 68          |

## 1.0 SUMMARY

This annual report is a critical review and compilation of work performed to analyze, both technically and economically, the state of technology readiness for the automated production of solar cells and modules. The long-term objective solar module characteristics include a selling price of less than \$.50/peak watt and a mean-time-before-failure (MTBF) of 20 years in any terrestrial environment. While efficiency is important to attaining the cost goal, it is a most significant factor in array economics; accordingly, this program has stressed high efficiency, with a suggested cell goal of 15%.

The analysis emphasized technical evaluation of individual process steps first, and then concentrated upon process sequences for making solar cells and modules. Further analysis was performed to yield a detailed cost study of individual process steps; this was applied to the cost analysis of potential process sequences. Potentially economical process sequences formed from process steps deemed to have high technical merit were then identified. Potentially promising technologies needing further development to achieve satisfactory maturity were then identified. It is the conclusion of this study that, while specific areas of technology need advanced development and the source of silicon needs definition, no fundamentally new technology needs to be developed to permit manufacture of solar cells which will meet the 1985 LSSA Program cost goals.

## 2.0 INTRODUCTION

Phase I of the Automated Array Assembly Task, LSSA Program, is concerned with a comprehensive assessment of the improvements in existing technology that will be needed to develop, within a period of no more than 10 years, an industrial capability for low cost, mass production of very durable, efficient silicon solar photovoltaic modules and arrays.

This program was organized to incorporate solar cell design, process adaptation, process sequencing optimization, technology assessment, solar cell fabrication, interconnection and encapsulation, and cost analysis in an interrelated way such that the final choices for particular process sequences would be realistic and have a high probability for success. Out of the study would also come the identification of areas of technology that could contribute significantly to the long term objectives dependent upon the successful conclusion of additional, specific R&D effort.

There have been interactions and heavy interdependence upon other Tasks of the LSSA Program, especially upon the tasks responsible for development of a process to supply silicon sheet for solar cell fabrication, and encapsulation of solar cell panels. This interdependence has required, in some instances, assumptions about future results in order to permit progression toward meaningful conclusions in the time frame of this program.

## 3.0 TECHNICAL DISCUSSION

### 3.1 DESIGN IMPROVEMENTS

In order to effectively evaluate processes and process sequences, it was first necessary to establish minimum, or baseline, design considerations for the solar cell and its constituent elements. It has been Motorola's contention throughout this contract that it is necessary to develop a solar cell design model (or design models) which effectively characterize the highest efficiency silicon solar cell capable of being produced utilizing current or anticipated semiconductor processing techniques, subject to the major constraint that the estimated cost in dollars per watt of the final assembled and installed array of silicon solar cells be minimized. Any process sequence, thus, must be based on a solar cell design model which reflects current state-of-the-art practices as well as additional concepts not currently incorporated in solar cells but envisioned as likely to contribute to future solar cell improvement. The following sections first treat basic design considerations, and then discuss specific solar cell design features.

#### 3.1.1 BASELINE DESIGN MODEL CONSIDERATIONS

A solar cell can be considered as a co-operative group of individual elements, including an antireflection coating, the front surface, a junction region, a substrate, a back surface, and front and back metallizations. Each element can be characterized with a list of desirable properties.

##### 3.1.1.1 ANTIREFLECTION COATING

Desirable features of an antireflection coating on a solar cell include those which:

- (i) optimize the transmission of incident photons into the silicon material;

- (ii) promote the lowest concentration of surface-state recombination centers at the coating-silicon interface;

- (iii) aid in establishing an electric field within the silicon (near the surface) which retards minority carrier flow toward the front surface and recombination at the front surface; and

- (iv) passivate and isolate the P-N junction perimeter.

### 3.1.1.2 FRONT SURFACE

The silicon solar cell should possess a silicon front surface condition which:

- (i) minimizes surface defects and maximizes minority carrier life-time near the silicon surface;

- (ii) minimizes surface recombination velocities;

- (iii) maximizes the absorption of incident photons by the silicon, complementing the antireflection coating;

- (iv) refracts the incident light to optically enhance the possible photon path lengths through the silicon substrate;

- (v) promotes the adhesion of metal ohmic contacts.

The surface may be that of an as-grown sheet of silicon, or it may be polished or etched. When the orientation allows, as discussed Section 3.1.2, texture etching can provide a highly controllable, cost-effective way of obtaining most of the properties listed above while accruing additional benefits for solar cell design. A model for a textured front surface is discussed in further detail in Section 3.1.2 of this report.

### 3.1.1.3 JUNCTION REGION

A study performed on this contract, and included in Section 3.1.3, has concluded that Schottky barrier cells are less favorable than those utilizing P-N junctions. Accordingly, we consider in our baseline design model only the

silicon P-N junction solar cell, which must have a thin, front surface region with an electrical conductivity opposite that of the substrate (e.g., N type surface region on a P type substrate) which:

- (i) forms a metallurgical P-N junction;

- (ii) is amenable to formation of an ohmic contact without significant degradation of solar cell performance;

- (iii) has a low surface recombination velocity, or is designed to effectively minimize surface recombination effects (e.g., has a large built-in drift field);

- (iv) has sufficiently high minority carrier lifetime;

- (v) has a sufficiently low value of sheet resistance; and

- (vi) maximizes the collection efficiency for short wavelength photons.

Property (vi) implies that the P-N junction depth below the front surface be as shallow as can be allowed, subject to satisfying the other five requirements. Traditionally, only junction depths of about 0.5 micron or less have been used, and the best (violet-type) cells have junction depths closer to 0.1 micron. This requirement makes attainment of property (v) more difficult.

#### 3.1.1.4 SUBSTRATE

The solar cell must have a silicon substrate which:

- (i) has high minority carrier lifetime for a maximum photo-current generation;

- (ii) has a sufficiently high impurity doping level to obtain high open circuit voltage and low electrical resistance;

- (iii) is optically thick enough to efficiently absorb an appreciable fraction of incident long wavelength photons but is mechanically

thin enough to conserve silicon; and

- (iv) has a low minority carrier recombination velocity at the back surface, or is designed to have a large drift field to effectively minimize back surface recombination effects.

Minority carrier lifetime is of extreme importance to efficient silicon solar cell performance; however, lifetime values practically obtainable may eventually be dictated by economical silicon purification processes. Under more immediate control, and of particular interest insofar as a design model is concerned, is the optical thickness of the silicon substrate. The optical thickness may be enhanced (for a given mechanical thickness) by forcing absorption paths to be other than perpendicular to the cell plane (or P-N junction), and additionally through multiple internal reflections.

### 3.1.1.5 BACK SURFACE

The solar cell should have a silicon back surface condition which:

- (i) minimizes surface defects and maximizes minority carrier lifetime near the silicon surface;

- (ii) minimizes surface recombination velocity; and

- (iii) reflects unabsorbed incident radiation which passes through the substrate and reaches the back surface.

By reflecting photons reaching the back surface, the optical thickness of the substrate can be at least twice as great as the physical thickness. Moreover, unusable infrared wavelength photons can be re-radiated from the front of the solar cell rather than absorbed at (or near) the back surface.

### 3.1.1.6 METALLIZATIONS

The solar cell must have metallization contacts to both front and back surfaces which:

- (i) provide ohmic electrical contact to the opposite sides of the P-N junction;

- (ii) allow reliable, low-loss interconnection with other solar cells and with external circuits;

- (iii) minimize solar cell internal series resistance;

- (iv) cover (and therefore shadow) a minimum of the cell front surface area; and

- (v) allow optical reflection from as large a fraction as possible of the back surface area; and

- (vi) are corrosion resistant.

### 3.1.2 TEXTURED SURFACE

A textured surface, consisting of a uniform distribution of minute pyramids as shown schematically in Figure 3-1, causes light reflected from the first impingement on the solar cell surface to strike the solar cell at least a second time (assuming initial normal incidence). This second impingement increases the amount of light absorbed in the solar cell, improving cell efficiency by reducing the total amount of light reflected from the cell. Incoming, reflected, and refracted ray traces of light normally incident to the overall solar cell, Figure 3-2, show the multiple reflection features of this surface topography.

Another major effect of front surface texturing is that, since light is refracted into the silicon at an angle to the normal of the overall solar cell plane, more light is absorbed within a given thickness of silicon than would occur with normally incident sunlight on a smooth-surfaced solar cell. This

ω

FIGURE 3-1: Cross-sectional diagram of silicon (100) wafer showing geometry of textured surface having {111} faceted pyramids.

FIGURE 3-2: Diagram of reflected and refracted ray traces and angular relations for light normally incident to the substrate (100) plane of a textured surface solar cell.

property can be separated into its effects in two regions: a microscopic region involving the volumes immediately adjacent to the p-n junction, and a more macroscopic region involving the bulk of the silicon below the junction.

In the microscopic region near the junction, it is first assumed that the surface relief of the pyramidal structures is large (averaging greater than  $10\mu$ ) compared to the p-n junction depth (less than  $0.5\mu$ ). Light normally incident to a textured surface solar cell strikes the surface facets at an angle near  $55^\circ$ . Figure 3-3 diagrammatically demonstrates the refracted paths of a normal incidence light beam on a smooth surface cell and also in an analogous fashion on a textured surface facet. The optical path length of the refracted beam within the region of the junction is greater than the normal path length by a factor of  $\frac{1}{\cos\phi}$  in the case of the textured surface. This increased path length has an effect equivalent to increasing the absorption coefficient of light in the silicon by the same factor (over the smooth cell normal incidence beam). Thus, within the region near the junction, more light is absorbed, creating more carriers, and increasing cell efficiency for very shallow junctions. Assuming that the index of refraction of silicon is 3.75, the angle  $\phi$  is approximately  $12.6^\circ$  and  $\frac{1}{\cos\phi}$  is approximately 1.025. While this near surface (microscopic) phenomenon is effective throughout the solar spectrum, it is most significant in the short wavelength end of the solar spectrum where the silicon absorption coefficient is greatest. The phenomenon is, thus, expected to enhance somewhat the blue response of the solar cell.

A larger effect is seen in the macroscopic region within the bulk of the cell below the microscopic junction region. Light incident normal to the plane of the overall cell is refracted by the textured surface through an angle of  $12.6^\circ$  from the normal to the facet. (Figure 3.2). This is equivalent to an angle of  $42.2^\circ$  from the normal of the overall cell, i.e.,  $\phi=42.2^\circ$ , Figure 3-3, so that the path length through the bulk is increased

FIGURE 3-3: Representation of increased absorption path length of textured surface light ray trace compared to trace normal to a plane surface.

by a factor of  $\frac{1}{\cos 42.2^\circ}$ , equal to 1.35. This is the equivalent of increasing the path length through the bulk by 35%, making each three units of solar cell thickness look like four units of thickness. Restated, the number of carriers created in an optical path length of four thickness units is generated within three mechanical thickness units of the front surface and the p-n junction. This makes the cell far more responsive to the longer wavelengths of incident sunlight, which have smaller absorption coefficients in silicon than the short wavelengths.

A further effect of the angle of travel of the refracted beam through the bulk occurs at the back surface of the cell. If the back surface of the cell is not textured and is a plane, all light refracted through the front textured surface can be shown to strike the back surface of the cell at an angle exceeding a critical angle, resulting in total reflection from the back surface toward the front surface. (The condition for total internal reflection

$$n_{Si} \sin \epsilon = n_{ext}$$

yields angles of about  $15.5^\circ$  for air and near  $24^\circ$  for most plastics and  $SiO_2$ .) Total internal reflection occurs when the angle  $\phi$  exceeds the angle  $\epsilon$ , Figure 3-4. The angle  $\phi$  for normal incidence on the textured front surface is  $42.2^\circ$ , thus satisfying the condition for total internal reflection. Non-normal incidence will produce different values for the angle  $\phi$ , but the angle  $\phi$  will always satisfy total internal reflection conditions.

Total internal reflection from the back surface can be advantageous, utilized in one of two ways. First, the internally reflected beam will be further absorbed on its second pass through the material, again creating more carriers and increasing cell efficiency. Alternately, a thinner cell (conserving silicon) could be made to display the same efficiency as a thicker standard cell. The magnitude of the effect of the second pass absorption will be, of

FIGURE 3-4: Path of beam refracted from textured surface illustrating total internal reflection from back surface if the brewster angle  $\epsilon < 42.2^\circ$ .

course, a function of the total cell thickness and the minority carrier lifetime of the cell substrate.

More subtle advantages also occur with a textured surface. The textured surface, formed by etching, leaves a surface which is relatively free of work damage. A plane surface, on the other hand is often achieved by polishing, leaving a finite degree of work damage in the crystal surface layer. Such damage is known to adversely affect both carrier lifetimes and surface recombination velocity; it can propagate during high temperature processing, aggravating the damage. This additional advantage of textured surface etching will not apply to solar cells fabricated from silicon ribbon (if it is directly grown to have smooth, damage-free surfaces), or from chem-etched wafers.

For any unit area in the plane of the substrate, the (100) plane, the corresponding area of the textured surface described above will be a factor of  $\sqrt{3}$  times larger. When ohmic metal contacts are applied, this increased surface area will serve to reduce the magnitude of the contact resistance. Furthermore, the textured surface itself can promote better metal adhesion to the silicon surface.

Finally, the mechanism causing reduced reflection of incident light discussed at the outset of this section will also lessen the requirements on antireflection coatings chosen for the solar cell surface. For example, the differences in total reflection obtained when using a perfectly matched antireflection coating and when using a somewhat less than perfect one will be much less pronounced, perhaps allowing coatings to be chosen for increased cost-effectiveness and convenience of processing.

### 3.1.3 SCHOTTKY BARRIER SOLAR CELLS

Silicon solar cells can be broadly classified as either Schottky barrier solar cells or P-N junction solar cells. Either, in theory, could meet the goals of the LSSA Project. In order to obtain the LSSA Project goal of silicon solar cell modules which operate with at least 10% efficiency, it is necessary that the individual cells operate at greater than 10% efficiency. This is required since module optical transmission losses, thermal resistance, cell packing density, and space utilization will lower the overall efficiency.

A survey of the recent literature on Schottky-type cells has been performed, and a list of references in chronological order appears at the end of this section. No reference has been found which reports large area silicon Schottky-type solar cells which exhibit greater than a 9.5% efficiency.<sup>9</sup> (Schottky-type cells with 15% efficiency have been reported on GaAs.<sup>15</sup>) Recent professional society conferences have given no indication that a breakthrough in the present state-of-the-art of silicon Schottky cell technology is imminent, although studies are continuing. In fact, although theoretical computations have been mentioned in the literature claiming that the upper limit on conversion efficiency is slightly better for the Schottky barrier cell than for a P-N junction cell,<sup>7</sup> the state of the technology is quite the opposite.

Metal-semiconductor solar cells reported to date exhibit inherently low output voltages. This effect is a consequence of high diode "saturation" (dark) currents and low metal-semiconductor barrier heights. Thus, the possible high photo-generation current densities theoretically available with Schottky cells are offset by low output voltages.

Metal-oxide-semiconductor solar cells<sup>5,12</sup> have been fabricated, exhibiting open circuit voltages as high as 0.52 volts.<sup>18</sup> In such cells, current flow

requires tunneling through the interfacial layer. The best such cells have shown only an 8% conversion efficiency,<sup>8,16</sup> indicating reduced current collection efficiency (through the interfacial layer) compared to the metal-semiconductor cells.

No experimental results have been shown to give credence to the possibility of obtaining increased Schottky cell voltages while maintaining high currents. On the other hand, the high generation current possibilities ascribed to such cells can be approached by P-N junction cells. In fact, high generation current densities along with high open circuit voltages have been reported for P-N junction solar cell structures fabricated incorporating violet-cell and textured surface techniques.

It is often stated (or implied) that Schottky cells are easily fabricated, giving an inherent processing simplicity (and cost) advantage over junction cells. This is a major misconception. Schottky cells require precise control of metal depositions in the thickness ranges of less than 100Å in order to optimize trade-offs between conductivity and reflectance. Such control is difficult by evaporation, and more controllable sputtering techniques have resulted in lower open circuit voltages, presumably due to penetration of sputtered atoms through the interfacial layer into the silicon.<sup>19</sup> Yield, efficiency, and cost problems can be expected to continually plague this fabrication step. Schottky-type solar cells require the same highly conductive metal collection grid and anti-reflection coating deposition as do P-N junction cells. Rather than being simpler, the fabrication complexity for a good silicon Schottky solar cell would be about the same that of a good silicon P-N junction solar cell. It is Motorola's conclusion that the technological uncertainties that must be resolved in order to demonstrate the (slight) theoretical advantages of the silicon Schottky solar cell are much too great to permit considering it as a serious contender at this time.

### 3.1.3.1 SCHOTTKY BARRIER SOLAR CELL BIBLIOGRAPHY

1. S.S. Li, F.A. Lindholm, and C.T. Wang, "Quantum Yield of Metal-Semiconductor Photodiodes", *J. Appl. Phys.*, 43, 4123, (1972).

2. W.A. Anderson and A.E. Delahoy, "Schottky Barrier Diodes for Solar Energy Conversion", *Proc. IEEE*, 60, 1457 - 1458, (1972).

3. E.J. Charlson, A.B. Shah, and J. C. Lien, "A New Silicon Schottky Photovoltaic Energy Converter", *IEEE Electron Devices Meeting*, (1972).

4. R. J. Stirn and Y.C.M. Yeh, "Solar and Laser Energy Conversion with Schottky Barrier Solar Cells", *IEEE Photovoltaic Specialists Conference*, 10, 15, (1973).

5. M.A. Green, F.D. King, and J. Schewchren, "Minority Carrier MIS Tunnel Diodes and Their Application to Electron and Photo-Voltaic Energy Conversion - I. Theory", *Solid State Elec.*, 17, 551 - 561, (1974).

6. J. Schewchun, M.A. Green, and F.D. King "Minority Carrier MIS Tunnel Diodes and Their Application to Electron - and Photo-Voltaic Energy Conversion - II Experiment", *Solid State Elec.*, 17, 563 - 572, (1974).

7. D.L. Pulfrey and R.F. McQuat, "Schottky Barrier Solar-Cell Calculations", *Appl. Phys. Lett.*, 24 (4), 167 - 169, (1974).

8. W. A. Anderson, A.E. Delahoy, and R.A. Milano, "An 8% Efficient Layered Schottky-Barrier Solar Cell", *J. Appl. Phys.*, 45 (9), 3913 - 3915, (1974).

9. W.A. Anderson, R. A. Milano, "I-V Characteristics for Silicon Schottky Solar Cells", *Proc. IEEE*, 63, (1), 206 - 208, (1975).

10. S.J. Fonash, "The Role of the Interfacial Layer in Metal-Semiconductor Solar Cells", *J. Appl. Phys.*, 46 (3), 1286 - 1289, (1975).

11. R.F. McQuat and D.L. Pulfrey, "Analysis of Silicon Schottky Barrier Solar Cells", *IEEE Photovoltaic Specialists Conf.*, 11, 371 - 375, (1975).

12. S.J. Fonash, "Metal-Thin Film Insulator-Semiconductor Solar Cells", *IEEE Photovoltaic Specialists Conf.*, 11, 376 - 380, (1975).

13. Y.C.M. Yeh and R.J. Stirn, "Improved Schottky Barrier Solar Cells", IEEE Photovoltaic Specialists Conf., 11, 391 - 397, (1975).

14. R. J. Stirn and Y.C.M. Yeh, "The AMOS Cell-An Improved Metal-Semiconductor Solar Cell", IEEE Photovoltaic Specialists Conf., 11, 437 - 438, (1975).

15. R.J. Stirn and Y.C.M. Yeh, "A 15% Efficient Antireflection-Coated Metal-Oxide-Semiconductor Solar Cell", Appl. Phys. Lett., 27, (2), 95 - 98, (1975).

16. E.J. Charlson and J.C. Lien, "An Al p-Silicon MOS Photovoltaic Cell", J. Appl. Phys., 46, (9), 3982 - 3987, (1975).

17. S. Shevenock, S. Fonash, and J. Geneczko, "Studies of MIS Type Solar Cells Fabricated on Silicon", IEEE Electron Devices Meeting, 211 - 212, (1975).

18. M. Peckerar, H.C. Lin, and R.L. Kocher, "Open Circuit Voltage of MIS Schottky Diode Solar Cells", IEEE Electron Devices Meeting, 213 - 216, (1975).

19. W.A. Anderson, S.M. Vernon, A.E. Delahoy, K.K. Ng, P. Mathe, and T. Poon, "Variables Which Influence Silicon Schottky Solar Cell Performance", IEEE Electron Devices Meeting, 217 - 219, (1975).

20. W.A. Anderson, "Silicon Schottky Photovoltaic Diodes for Solar Energy Conversion", Quarterly Progress Report, NSF/RANN/SE/AER73-03197/PR/75/3, PB-246-154, (1975).

### 3.1.4 FRONT SURFACE METALLIZATION

Metal coverage and series resistance tradeoffs are major limiting design considerations on the shape and maximum useful size of solar cells, and the concomitant material process for producing silicon sheet. A critical evaluation of existing metallization geometries has revealed that efficiency may suffer if these designs are extended to large area ribbon or sheet cells. Accordingly, improved contact metallization designs were investigated. Designs which show

the greatest promise over existing designs for improved cell performance have multiple contacts; hence the interconnect and packaging systems should consider the possible need for multiple-contacts-per-wafer. Also, efficient design seems to favor long, narrow rectangular ribbons rather than large area square or round sheet solar cells.

In particular, the front surface metal pattern of a silicon solar cell will influence the performance of both solar cells and modules because of three requirements: 1) the pattern must provide area for an interface point (or points) for electrical connection to other cells; 2) the pattern must provide sufficient area for efficient (low resistance) flow of current, since the metal pattern itself (as well as the cell below) will have an internal series resistance; and 3) the pattern should shadow the least possible area to maximize current generation. Some preliminary conclusions regarding constraints on metal pattern design and on solar cell size can be drawn quickly by considering interactions of these three requirements.

Assume that a silicon solar cell is available with any desired surface area or shape but is constrained to have a fixed, minimum value of surface sheet resistance above the P-N junction. Series resistance of the cell will then depend on the thickness of metal used for a particular front ohmic contact pattern and the resistivity of that metal. If the metal pattern coverage is limited to a reasonable percentage of the front surface area (say, 5 to 10%) and a particular metal system and thickness are adopted (defining sheet resistance), then series resistance depends on pattern topology. The metal "current collection" fingers on the cell surface may contribute appreciably to series resistance. For a single contact region solar cell, as the cell surface area becomes larger (and the metal current-conducting paths become longer) a point will be reached where series resistance has increased beyond an acceptable value. In effect, the permissible surface area of the solar cell has been limited.

This is not true if more than one external electrical contact can be made to the cell. In this case, only one lateral dimension of the solar cell surface needs to be limited. For example, a solar cell fabricated on a rectangular ribbon substrate may be infinitely long if electrical contacts are made along its edges at small intervals, but there must be a practical limit on the width of the cell if acceptably low internal voltage loss (i.e., series resistance) is to be maintained. Calculations have shown that as ribbon widths surpass 10cm, loss of efficiency increases so rapidly that such cells are no longer cost effective. The same principle holds for circular solar cells. Constrained to a fixed area of front surface metal, a circular cell may require multiple contact points around the perimeter to maintain a low series resistance. A larger diameter cell would require more contacts than a smaller diameter cell; and in the limit, as cell diameter becomes still larger, overall cell efficiency must suffer.

The net effect of using multiple electrical contacts at the perimeter of a solar cell is to shift some of the burden of summing the photo-current generated by the active surface of the cell away from the metal pattern on the cell surface to external electrical busses. When such a solar cell is assembled in an array of cells, an additional benefit accrued is increased reliability achieved through partial redundancy of the multiple cell contacts.

### 3.1.5 BACK SURFACE METALLIZATION

The physical configuration of the back surface of a solar cell will influence its optical properties. It is important from a design standpoint to know, as a function of wavelength, the degree of light absorption, reflection, and transmission at the cell back surface, since these factors will influence cell efficiency as a function of thickness (multiple light pass from reflection) and heating effects (absorption at the back surface).

Another variable affecting optical performance at the back surface is the configuration of the front surface. If the front surface is texture-

etched and the back surface is non-absorbing, for example, total internal reflection from the back surface should always occur.

Experiments have been performed to measure, as a function of wavelength, the reflection of light from the back surface of a silicon wafer with various front surface and back surface configurations. The purpose of these experiments was to determine if any cell performance advantages can exist with a patterned back metal. Samples with both polished (or isotropically etch-polished) and texture-etched front surfaces were utilized for each back surface configuration.

Test wafers were prepared from 0.8 - 1.2Ωcm p-type silicon wafers. The starting wafers were isotropically etched on one side and polished on the other. Some of the test wafers utilized the polished side as the back surface, and others used the etched side as the back surface. The front surfaces of all test wafers were prepared such that one-half of the wafer was texture-etched. The entire front surface of each test wafer was then coated with 700A of silicon nitride to serve as an antireflection coating.

Half of the back surface of each test wafer was similarly coated with 700A of silicon nitride while the other half was covered with a thick metal film. The back was configured in such a way as to divide the entire test wafer into four classes of front/back surface condition combinations:

1. textured front/dielectric back;

2. textured front/metal back;

3. smooth front/dielectric back;

4. smooth front/metal back.

Integrated sphere reflection tests were then performed. Data were taken over wavelengths from 0.35μm to 2.0um to determine the reflectance characteristics of the interface at the test wafer back surface.

In each case where the back surface was covered with metal (which had been sintered) the empirical reflectance curves agreed perfectly with theoretical curves for reflectance from the front surface of the silicon wafers. The smooth front surface reflectance approached a value of 30% at  $2.0\mu\text{m}$ , and the textured front surface reflectance approached a value of 10% at  $2.0\mu\text{m}$ . In both cases where the test wafer back surface was covered with dielectric (and, during the measurements, backed by an extremely efficient absorber) a back surface reflectance effect was observed. For wavelengths below  $1.1\mu\text{m}$  where the silicon wafer absorption is good, reflectance curve shapes are identical for both dielectric-covered and metal-covered back surface wafers. (The wafers utilized in these measurements were sufficiently thick to totally absorb any light in this wavelength range reflected from the back surface.) However, for wavelengths longer than  $1.1\mu\text{m}$ , where silicon becomes transparent, an additional reflectance component was observed for wafers with dielectric coated backs. The smooth front surface test wafer reflectance approached 50% at  $2.0\mu\text{m}$ , and the textured front surface test wafer approached 50% reflectance at  $2.0\mu\text{m}$ . Therefore, in going from a metal backed cell to a dielectric backed cell, the smooth front surface wafer shows a 33% increase in reflectance while the textured front surface wafer shows a 400% increase in reflectance. This large increase in reflectance for textured surface wafers is a result of the total internal reflection condition inherent to textured wafers.

The possibility of patterning the back surface metal in order to utilize reflection of the longer wavelength portions of the solar spectrum back toward the front surface has ramifications other than increased absorption of useful light. For example, infrared wavelengths longer than 1.2 micrometers can be reflected from the back surface and ultimately out of the module, reducing cell and module operating temperature and increasing module efficiency. Additionally, a cost trade-off occurs between the additional cost of patterning the back

surface metal, the cost savings of decreased metal consumption, and the effective cost reduction brought about through increased cell efficiency.

### 3.1.6 METALLIZATION TEST PATTERN

As discussed in the two previous sections, a major factor in determining solar cell performance is the metallization pattern. The metallization must efficiently collect current while shadowing the minimum active area. In achieving optimum designs, thus, it is necessary to determine allowable contact metallization line widths, both from an achievable fabrication feasibility standpoint and from a series resistance standpoint.

The limitations of metal contact pattern linewidths will vary with the surface flatness of the silicon. Accordingly, two types of surfaces were studied: polished and textured etched. These two types of surfaces represent extremes in surface microscopic smoothness. Both, however, are on macroscopically plane surfaces and will not necessarily present the effects of surface warp or ripple possible from sheet or ribbon growth. The effects of these latter parameters must be evaluated when sufficient representative ribbon samples become available.

A test pattern photoresist mask, Figure 3.5, was designed with linewidths ranging from 0.0003 inch to 0.0500 inch. Dielectrics (or metals) can be patterned on the desired surfaces by standard photolithographic techniques.

The evaluation technique, on both polished and textured test wafers, included the formation on the surface of a dielectric, either silicon dioxide or silicon nitride, and patterning the dielectric with the test pattern. The patterns were visually inspected and evaluated. The patterned wafers were then electroless nickel plated and solder coated. Optical inspections indicated minimum linewidth limitations due to photoresist procedures, and

FIGURE 3-5: Metallization and solder test pattern. The pattern contains linewidths ranging from 0.0003 inch to 0.0500 inch. Pattern is designed such that lines are withdrawn from solder coating at horizontal, vertical, and angular directions. In addition, the pattern contains included angles of 45°, 90°, and 135°.

electrical continuity measurements determined line resistance after soldering.

Sheet resistance versus metal linewidth was tabulated for both textured and polished surfaces to determine the relative ohmic properties of a small number of wide lines versus a large number of narrow lines for solar cell current-collecting patterns.

Results to date indicated that there is no problem in obtaining the smallest (0.0003 inch) line width on polished wafer surfaces using our standard photolithographic techniques and equipment. To the contrary, textured surfaces present a special problem. In order to maintain the integrity of the dielectric covering the peaks of the textured surface pyramids in areas where no preohmic pattern is to appear, a much more viscous photoresist must be used, as discussed in a later section. Application of this viscous resist produces a much thicker layer in the "troughs" of the textured surface. and this, in combination with the optical properties of the textured surface itself, seems to set a practical lower limit on preohmic line width resolution. Patterns were formed by contact printing from the mask. Inspection has shown that line widths smaller than 0.001 inch have not been clearly and consistently opened. Textured surface pyramids may have base widths on the order of 10 microns; therefore linewidths of 0.0005 inch (12.7 microns) may encompass only a single pyramid. Pyramid heights on the order of 10 microns prevent true contact printing. Thus, light scattering among the pyramids contributes to an inherent limit of line width resolution. Exposing with more collimated light source, such as is used with projection or proximity printing, should help to minimize these effects.

Wafers used for photolithographic studies, as well as a comparable set of polished test wafers, were plated with nickel and solder-dipped to obtain maximum metal build-up for a given line width. These lines were then measured for sheet conductance/resistance.

Experiments have been performed with textured surface wafers coated with silicon dioxide and prepared using standard viscosity (44 cp) photoresist to allow formation of soldered metal lines with widths between 0.0003 inch and 0.0500 inch. For line widths less than or equal to 20 mils, soldered line sheet resistance  $\rho$  (in  $\Omega/\text{sq.}$ ) is given by

$$\log \rho = -1.09 - 0.75 \log W,$$

where  $W$  is the line width in mils. This means  $\rho$  is proportional to  $W^{-3/4}$ . (If the solder bead build-up were hemicylindrical, then  $\rho$  would be proportional to  $W^{-1}$ .) For line widths greater than 20 mils the capillary effect of fine lines tends to become suppressed and the sheet resistance tends to become independent of line width, indicating a constant thickness at the larger widths.

The relation between sheet resistance and line width (given above) for lines less than 20 mils wide implies that, for a given area of metal line coverage, one wide contact finger will introduce more series resistance than two contact fingers distributed over the same active cell area, but each finger being half as wide. Thus, for soldered contact systems of equal total area, many narrow fingers are more efficient than fewer wide fingers, as long as the thinnest lines are at least 0.001 inch wide to preserve physical and electrical continuity.

### 3.2 PROCESS ADAPTATION

A major portion of the contractual effort involved a technical assessment of potential process steps for manufacturing silicon solar cells. First, a matrix of possible processing steps was assembled. Second, a group of evaluation criteria was defined to allow a technical evaluation of the usefulness of each individual process step when examined as an isolated step for manufacturing solar cells. Most of the individual process steps were then evaluated, either directly in the laboratory or through indirect methods such as literature

surveys, vendor contacts, and detailed discussions with process engineers in the Motorola manufacturing and research areas (for both discrete and integrated circuit products). This technical evaluation process resulted in the categorization of these individual process steps to reflect both technical readiness and an estimation of future technical utility. This section identifies the various process steps, their evaluation, and their technical categorization.

### 3.2.1 EVALUATION CRITERIA

Evaluation criteria were established to consider both the individual process step itself and also effects on properties of a solar cell resulting from its incorporation in the cell manufacturing sequence. Among the evaluation criteria were:

- Cost

- Labor

- Material

- Capital

- Expense Items

- Performance

- Controllability

- Amenability to automation

- State of readiness

- Reliability considerations

- Amenability to future sheet (ribbon) geometries.

Whenever applicable, each of these criteria was applied to both the process itself and to properties of the resulting solar cell. A poor rating in either case would result in an overall unsatisfactory rating. Performance of surface lapping silicon, for example, is judged favorably as an isolated process step,

but lapped silicon is rated poorly as a starting surface when considering its effects on solar cell performance. It must be understood that process steps do not stand on their merits as individuals, but on their ability to contribute synergistically to a process sequence. Each step must, then, be evaluated first, by itself, and second, as a member of a process sequence.

In this technical evaluation phase, cost criteria were applied in only a qualitative manner, reflecting only estimated and relative costs of competing processes. A detailed process step cost study was subsequently performed, and is reported in a later section.

The only other criterion which may not be self-explanatory is that involving sheet geometries. This requires an evaluation of a process step's suitability for application to a sheet which may have an irregular shape and also may be non-planar in nature. The sheet may, for example, be a ribbon which varies in edge shape, has surface ripples, and is warped. Some processes are relatively insensitive to these factors, while others become virtually useless. As-grown sheet is considered as having more severe geometrical problems than large area sliced sheets, which may also be utilized and must be considered as potential long-range substrates.

### 3.2.2 TECHNOLOGY ASSESSMENT CATEGORIES

A set of initial technology assessment categories was established at the beginning of the program. During the course of detailed process step evaluation, the set of categories was modified to reflect more accurately the requirements for evaluation of projected usefulness. The updated categories were as follows:

Category 1: Processes which are judged unlikely to be utilized in any recommended process sequence.

Category 2: Processes which appear to require a major technological advancement to ensure usefulness. Technology in these areas

must be continually monitored to assess future applicability.

Category 3: Processes which appear potentially promising, but which have required evaluations or equipment not available during the time-frame of this contract. Additional efforts should be expended on these processes.

Category 4: Proven processes which have a high chance of successful incorporation into future process sequences.

### 3.2.3 STARTING CONDITION OF SILICON SURFACE

The starting condition of the silicon surface plays a critical role in subsequent processing steps and in cell efficiency.

#### 3.2.3.1 SAWED SURFACE (CATEGORY 1)

It is unlikely that silicon will be utilized in the as-cut condition. Although this form of silicon is the cheapest available today, near-surface damage (and possible contamination from the saw blade and coolant) can badly degrade the crystal properties upon subsequent processing. Heating of the sawed surface can result in polyganization or recrystallization, converting the area in which the p-n junction is to be formed into a polycrystalline region. Heating may also propagate surface damage far into the bulk, resulting in a heavily dislocated, low lifetime material. All of these factors can degrade efficiency in a severe, uncontrolled manner.

One possible exception to this conclusion exists, however. Severe surface damage may be utilized to getter undesirable impurities from the bulk silicon below. High temperature annealing of a sawed surface may produce this desirable result. Subsequent to annealing, an undamaged silicon surface could be revealed by etching the sawed surface, hopefully removing both the

damage and the impurities. There is at this time insufficient information available to draw conclusions; additional studies should be undertaken.

### 3.2.3.2 SAWED AND ETCHED SURFACE (CATEGORY 4)

This is the best candidate broadly available today. Etching is utilized to remove the sawing damage and contamination. Etching wafers can leave surfaces that contain only gradual undulations of a magnitude so small that no pattern having linewidths of interest to solar cell production should experience any masking difficulties because of surface non-planarity. Thus, apart from the future realization of direct sheet growth, this combination produces the cheapest material suitable for solar cells and has indeed been used to manufacture solar cells. Sawing kerf loss, and material removed by etching, are major drawbacks, however, to this being the most economical approach for long range utilization.

### 3.2.3.3 LAPPED AND/OR POLISHED SURFACE (CATEGORY 1)

Lapping produces a matte appearing surface on a silicon wafer. It will be a flat surface, and, if done carefully, both sides of a wafer can be made plane and parallel by lapping them both. Lapping doesn't necessarily produce a surface having less damage than careful sawing, but a sawed surface will not be as flat as a lapped surface. This process is slow, batch orientated, and labor intensive, and hence is too expensive for ultimate solar cell use.

Polishing is a process like lapping, in which successively finer grit media are used to end up with a mirror-flat scratch-free surface. This degree of smoothness is necessary in order to obtain, by photographic means, the very fine line geometries utilized on many semiconductor devices and integrated circuits. However, solar cell geometries are about an order of magnitude coarser, so polished surfaces are not required for solar cell processing even

where patterning is done photographically. Furthermore, polished surfaces typically contain more mechanical crystal damage than etched surfaces, making them potentially less satisfactory for solar cell use.

Both lapping and polishing are too costly for incorporation into a process sequence to make inexpensive solar cells.

#### 3.2.3.4 CLEAVED SURFACE (CATEGORY 2)

Direct cleaving of silicon wafers or sheets from crystals would eliminate kerf losses, and could possibly produce smooth surfaces directly. To date, however, no process has been developed for cleaving wafers from a boule with anything approaching a satisfactory yield. If a major breakthrough in this area could be realized, it would be very cost competitive. No work appears to be currently underway in this area, however.

#### 3.2.3.5 AS-GROWN SHEET SURFACE (CATEGORY 2)

This is the responsibility of several contractors in the LSSA Program Task II. Breakthroughs in technology are still required to make as-grown sheet practical in the large scale necessary. However, judging by the progress made to date, and the potentialities of the process, it must be assumed that the probability of success is high. The various processes being studied all have the possibility of providing as-grown surfaces suitable for efficient solar cell processing.

The geometrical variations in silicon sheet, however, can greatly influence the usefulness of some solar cell processing, fabrication, and encapsulation choices. It must be made clear that two separate philosophies may be pursued. The first simply states that the large area sheet must conform to certain geometrical limits in order to allow solar cell processing and encapsulation to be performed by essentially conventional silicon wafer processing methods.

The second, the converse of the first, states that whatever the shape that results from the sheet growth method, it will be used, forcing solar cell processing and encapsulation to conform to the delivered geometry.

The most likely ultimate choice, of course, will be a compromise between the two extreme philosophies in order to achieve cost effectiveness. The compromise may, however, provide non-planar, rough surfaced sheets as compared to today's surface texture and flatness standards for wafers. Accordingly, later processes which are recommended under this Task IV study must have the flexibility of handling such future material, or must be clearly labeled as applicable only to optimum surfaces.

### 3.2.3.6 TEXTURE-ETCHED SURFACE (CATEGORY 4)

Texture-etching has been shown to be a repeatable and uniform process on (100) oriented silicon surfaces. Texture-etching can be performed on any of the previously discussed silicon surface conditions. Costs of texture-etching are equal to, or less than, those for other techniques for silicon etching, producing silicon costs only marginally above those of present sawed and etched wafers. For this additional cost, a surface with distinct optical advantages (and attendant efficiency increases) is produced. The textured surface is dramatically different in nature from polished or etched surfaces now used widely in the semiconductor industry. This requires certain modifications of other steps in a process sequence utilizing textured surfaces. These modifications are easily achieved.

The main caveat which must be kept in mind is that texture-etched surfaces currently require (100) oriented surfaces. If future sheet processes cannot produce (100) surfaces, texture-etching development must be attempted for other silicon orientations. If, in the future, a choice must be made between two

sheet growth processes of otherwise similar properties, the advantage will lie with the sheet process which can be texture-etched.

### 3.2.4 IN-PROCESS SURFACE CLEANING OR ETCHING

Any solar cell manufacturing process will require cleaning steps at some stages. Further, most manufacturing sequences will require etching steps.

#### 3.2.4.1 WET CHEMICAL CLEANING OR ETCHING (CATEGORY 4)

Processes in this category are widely utilized in the semiconductor industry with a high degree of success. Several major concerns exist at this time, however. First, it is possible to have unwanted contamination from wet chemicals. For any given process sequence and for each different manufacturing area, control limits will have to be defined for possible contaminants. At this time, no difficulties are seen in this area. Second, the use of wet chemicals limits the level of future cost reductions to the cost of those chemicals consumed, a serious limit if large quantities of chemicals are required. (This must include D.I. water which is consumed in rinsing after wet chemistry steps.) A third consideration is the disposal of waste chemicals. This can contribute additional materials and facilities costs to the utilization of wet chemistry. Nevertheless, because of its current strong position in the semiconductor industry, wet chemistry must still be considered a major possibility for future use.

#### 3.2.4.2 PLASMA CLEANING OR ETCHING (CATEGORY 4)

This is a dry process incorporating an RF field to excite a plasma. The energetic plasma is then used to remove material from the surface, either

through bombardment by inert energetic plasma ions, or by reactive ions liberated from molecules injected into the plasma. Based on their increasing acceptance by the semiconductor industry, plasma etching and cleaning steps have a high likelihood of supplanting at least some of the more traditional wet chemistry process steps.

A silicon nitride film for example, may be patterned utilizing a plasma etching process with excellent results. The plasma etching process, when compared to the wet chemistry process for etching, is less complicated and less time consuming. After application, alignment, and development of a photoresist film, etching of the exposed dielectric requires the following steps for the plasma and wet chemistry processes:

| <u>PLASMA</u>        | <u>WET CHEMISTRY</u>           |

|----------------------|--------------------------------|

| Load in etch carrier | Load in etch carrier           |

| Etch in plasma       | Etch in solution               |

| Remove photoresist   | Rinse in D.I. H <sub>2</sub> O |

|                      | Dry                            |

|                      | Remove photoresist             |

Not only is the plasma step simpler, it consumes only a small amount of material (etching gas) as compared to consumed acid and D.I. water for wet chemistry etching.

Plasma removal of photoresist ("ashing") has a similar appeal for process simplicity and consumed materials. Photoresist materials have notoriously contained metallic contaminants which, if left on the wafer surface and heated in subsequent process steps, could migrate into the silicon and degrade minority carrier lifetime. It is possible that photoresist removal by plasma techniques alone could leave such metallic impurities on the wafer surface. Evaluation of this aspect of plasma processing for solar cell fabrication, where high lifetime must be maintained, must be performed at a future date.

### 3.2.4.3 VACUUM BAKING AND REVERSE SPUTTERING (CATEGORY 1)

While results are reportedly adequate, the comparative capital costs are prohibitive for further consideration.

### 3.2.4.4 TEXTURE-ETCHING (CATEGORY 4)

Rather than texture-etching as a pre-processing step, it can be incorporated within a process sequence. The previous discussion is applicable here.

### 3.2.4.5 CLEANING BY SCRUBBING (CATEGORY 4)

A technique relatively new to the semiconductor industry is cleaning of silicon wafers by the mechanical scrubbing of their surfaces with brushes. Until recently, such scrubbing was avoided to eliminate possible mechanical damage to the silicon surface. Studies have shown, however, that removal of tightly adhering (and otherwise difficult to remove) dirt particles can be achieved through scrubbing without silicon damage. The removal of these particulates is seen to improve process control, device quality and performance, and overall process yield.

Mechanical scrubbing, however, may not be possible on warped or rippled surfaces such as may be forthcoming from future large area sheet production, or on textured surfaces which may house impurities in valleys too tiny to be effectively reached by brush bristles. Manufacturers have recently indicated, however, that cleaning equivalent to mechanical scrubbing may be accomplished hydraulically with a pressurized spray of water.

Numerous vendors now have automatic and semi-automatic scrubbing equipment of both types available. Yield increases of several semiconductor lines within Motorola (precise data is considered proprietary) indicate that scrubbing is technically advantageous.

#### 3.2.4.6 GAS STREAM DRYING (CATEGORY 4)

Wet chemistry steps require a subsequent drying operation. Drying by exposure to a (hot) gas flow has been one of the standards in the industry. It is forgiving of shape and is the prime contender for sheet geometries.

#### 3.2.4.7 GRAVITY (CENTRIFUGE) DRYING (CATEGORY 4)

For round wafers, centrifuge or "spin" drying has become another of the semiconductor industry standards. In that industry, wafers are thicker and smaller than those likely to be utilized for future solar cells. This technique may require special adaptation for very large area, thin solar cell substrates such as long ribbons.

#### 3.2.5 LIFETIME ENHANCEMENT AND PRESERVATION (CATEGORY 3)

Solar cell processing may require minority carrier lifetime improvement of the starting material, and must incorporate special precautions (and possibly specific techniques) to preserve lifetime during processing. Such processes fall into four general categories of lifetime enhancement: Complexing and removal of impurities, temperature-time profiling, leaching, and precipitation of impurities on damage sites or defects.

A literature survey on gettering of impurities in silicon has been performed; initial observations are that a variety of gettering processes has been investigated, and that the technology of impurity gettering is complex and far from developed to its full potential. In short, these processes all fall precisely within the definition of Category 3. Future efforts must be directed toward this area. A brief review of gettering is given here, followed by a bibliography of gettering references.

### 3.2.5.1 LITERATURE SURVEY OF GETTERING

In original investigations<sup>1</sup> into the removal of metallic impurities from silicon, the basic approach was to grow (or deposit) some type of oxide layer onto the surface of the silicon. The basic idea was that at high temperatures, the metallic impurities would diffuse to the surface and become trapped in the oxide layer. Various oxides, including phosphorus -, boron -, vanadium -, and lead - silicon oxides, were used. It was found that phosphorus glass did the best job.

Since then, studies<sup>3,10,13</sup> have shown that the metallic impurities are not gettered into the phosphorus glass, but instead are gettered to the heavily doped silicon under the glass. Apparently, the mechanism is one of increased solubility of metallic impurities in the phosphorus-doped silicon. Removal of impurities from the silicon, thus, requires removal of not only the oxide layer, but also the surface layer of silicon itself.

Normally, in bipolar processing, phosphorus gettering is used to transport metallic impurities away from active device areas to an unused portion of the wafer (i.e., the isolation diffusion or the back of the wafer). In MOS processing, a phosphorus glass is deposited on top of the passivation oxide to getter sodium impurities from the gate oxide<sup>11</sup>; this glass, however, appears to do little gettering of metallic impurities from the bulk of the silicon.

It has also been shown that a preoxidation gettering of the backside of the wafer will reduce the generation of oxide-induced stacking faults<sup>14</sup> (OISF). It is believed that OISF act to precipitate metallic impurities and thus degrade device characteristics. It is also believed that OISF are sites of enhanced phosphorus diffusion, and thus cause emitter-collector piping defects in bipolar devices.

It has been found that the use of various chlorine compounds during oxidation will getter both metallic impurities from the bulk silicon<sup>4,7,8</sup> and sodium impurities from the oxides that are grown<sup>5,6,9,12</sup>. Chlorine gettering can be used only during oxidation because it could otherwise cause extreme etching and pitting of the silicon<sup>4</sup>. Chlorine gas has been used with some success, but it may cause etching of the silicon. Hydrogen chloride has been the most successful gettering compound.

The chlorine gettering mechanism is believed to be diffusion of metallic impurities to the surface, followed by formation at the surface of volatile metallic chlorides which are then carried away by the gas flow. The gettering effect improves with increasing temperature (especially above 1000°C) and increasing amounts of HCl. The limit to the amount of HCl used occurs when significant etching of the silicon begins, or condensation of hydrochloric acid droplets takes place in the cooler portions of the furnace tube. The optimum mixture of HCl is about 5 - 10% HCl by volume in dry O<sub>2</sub>.

It has also been discovered that the use of HCl will clean the furnace tube of metallic impurities, and thus reduce contamination from that source to virtually nil<sup>6</sup>. The process used is 10% HCl in dry oxygen at 1150°C for 6 hours.

It should be noted that the use of HCl with steam instead of dry O<sub>2</sub> will still getter Na and the oxides thus grown, but will not as effectively getter the metallic impurities from the bulk. It is believed that the accelerated oxidation of metallic impurities in steam inhibits the formation of volatile metal chlorides.

It is well known that various types of crystallographic defects in silicon will tend to precipitate metallic impurities. This principle has been used to getter impurities by deliberately introducing defects in the back of the wafer, using them to trap metallic impurities migrating from the active device

regions. It should be emphasized that this method does not remove metallic impurities from the wafer, but merely moves them around. Methods of introducing defects include mechanical abrasion and ion implantation of Ar, O, P, Si, As, or B. As was suggested earlier, sawing damage may also be an appropriate starting point.

Boron diffusions have been used to getter metallic impurities from silicon, but are not as effective as phosphorus<sup>3</sup>. The mechanism is apparently the formation of metal precipitates, rather than any increased solubility of pairing.