# Seventh Workshop on The Role of Impurities and Defects in Silicon Device Processing

## Extended Abstracts and Papers

*August 11-13, 1997

Vail, Colorado*

Workshop Chairman: B.L. Sopori

Program Committee:

*R. Sinton, T. Tan, J. Kalejs, J. Gee,

L. Jastrzebski, T. Saitoh, B. Sopori*

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

National Renewable Energy Laboratory

1617 Cole Boulevard

Golden, Colorado 80401-3393

A national laboratory of

the U.S. Department of Energy

Managed by Midwest Research Institute

for the U.S. Department of Energy

under Contract No. DE-AC36-83CH10093

*kg*

#### **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, make any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

**Seventh Workshop on

The Role of Impurities and

Defects in Silicon Device Processing**

**TABLE OF CONTENTS**

| Title/author(s):                                                                                                                                                                    | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>WORKSHOP THEME: <i>R&amp;D Issues for Crystalline Silicon to Support<br/>GW/Yr Goal by the Year 2010</i></b> .....                                                               | 1    |

| Bhushan Sopori                                                                                                                                                                      |      |

| <br><i>A Study of the Manufacture at 500 MWp p.a. of Crystalline Silicon Photovoltaic<br/>Modules</i> .....                                                                         | 3    |

| W. Wettling, T. M. Bruton, G. Luthardt, K. D. Rasch, K. Roy, I. A. Dorrity,<br>B. Garrard, L. Teale, J. Alonso, U. Ugalde, K. Declerq, J. Nijs, J. Slufcik, A. Räuber<br>A. Valléra |      |

| <br><i>Grown-In Defects in FZ and C Z Silicon Crystals</i> .....                                                                                                                    | 7    |

| Takao Abe                                                                                                                                                                           |      |

| <br><i>Origins and Reduction of Dislocations in Semiconducting Crystals</i> .....                                                                                                   | 16   |

| Subash Mahajan                                                                                                                                                                      |      |

| <br><i>The Role of Dislocations and Associated Defects in Determining Minority<br/>Carrier Lifetime</i> .....                                                                       | 27   |

| L. C. Kimerling                                                                                                                                                                     |      |

| <br><i>Transition Metals and Lifetime in PV Silicon</i> .....                                                                                                                       | 31   |

| Eicke Weber, A. A. Istratov                                                                                                                                                         |      |

| <br><i>Oxygen Precipitation in Polycrystalline Ingot and Ribbon Solar Silicon</i> .....                                                                                             | 41   |

| H. J. Möller, Li Long, S. Riedel, M. Rinio, D. Yang                                                                                                                                 |      |

| <br><i>Analysis of Iron Precipitation in Silicon Using Minority Carrier<br/>Lifetime Measurement</i> .....                                                                          | 51   |

| Worth Henley, Deepok Ramappa                                                                                                                                                        |      |

| <br><i>Generation and Influence of Deep Levels in N<sub>2</sub> Diffused Si</i> .....                                                                                               | 55   |

| Yukio Takano, Katsunori Kakumoto                                                                                                                                                    |      |

| <br><i>Hydrogen in Crystalline Si: A Survey of Recent Results</i> .....                                                                                                             | 63   |

| Michael Stavola                                                                                                                                                                     |      |

|                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <i>Solar Cell Passivation and Selective-Emitter Processes</i> .....                                                                                     | 78  |

| Ron Sinton                                                                                                                                              |     |

| <i>A Summary of the Research Under NREL Silicon Materials Research Program</i> .....                                                                    | 84  |

| Bhushan Sopori                                                                                                                                          |     |

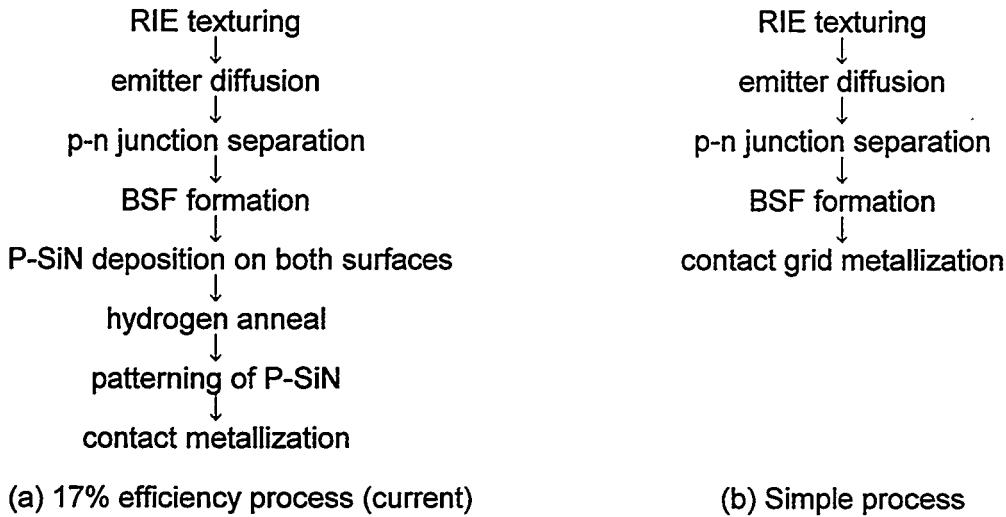

| <i>Possibility of Lower Cost Multicrystalline Silicon Solar Cell Toward<br/>GW Production</i> .....                                                     | 90  |

| Katsuhiko Shirasawa                                                                                                                                     |     |

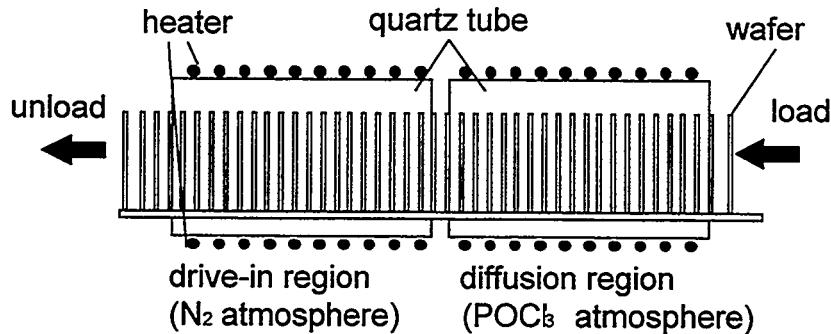

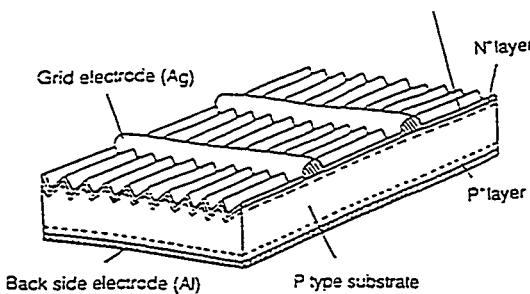

| <i>Low Cost Production Technologies for Polycrystalline Silicon Solar Cells</i> .....                                                                   | 97  |

| Tohru Nunoi, T. Machida, A. Miyazawa, Y. Yokasawa, H. Nakaya, S. Tanaka,<br>T. Tomita, H. Kumada, M. Murakami                                           |     |

| <i>Rapid Thermal Chemical Vapor Deposition: Example Processes and<br/>Their Applications</i> .....                                                      | 102 |

| Mehmet Öztürk                                                                                                                                           |     |

| <i>A Survey of Material Options and Issues for Thin Film Silicon Solar Cells</i> .....                                                                  | 108 |

| Z. Shi, M. A. Green                                                                                                                                     |     |

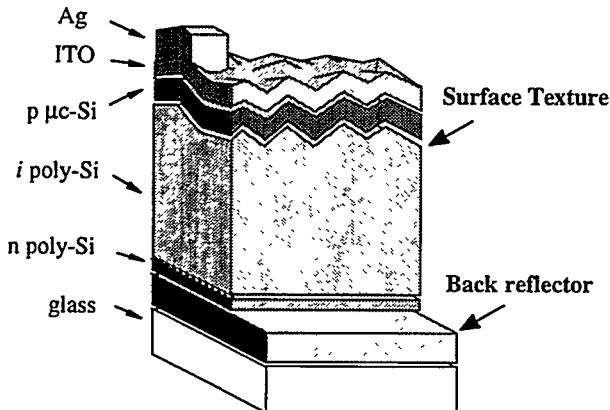

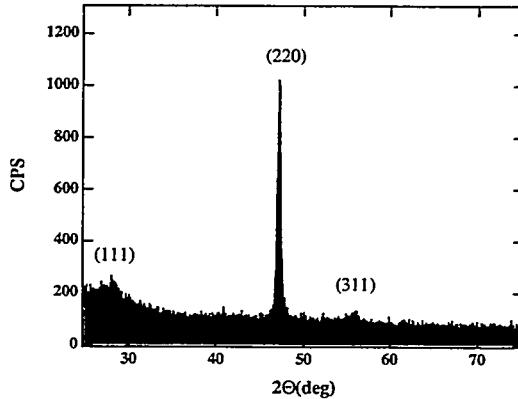

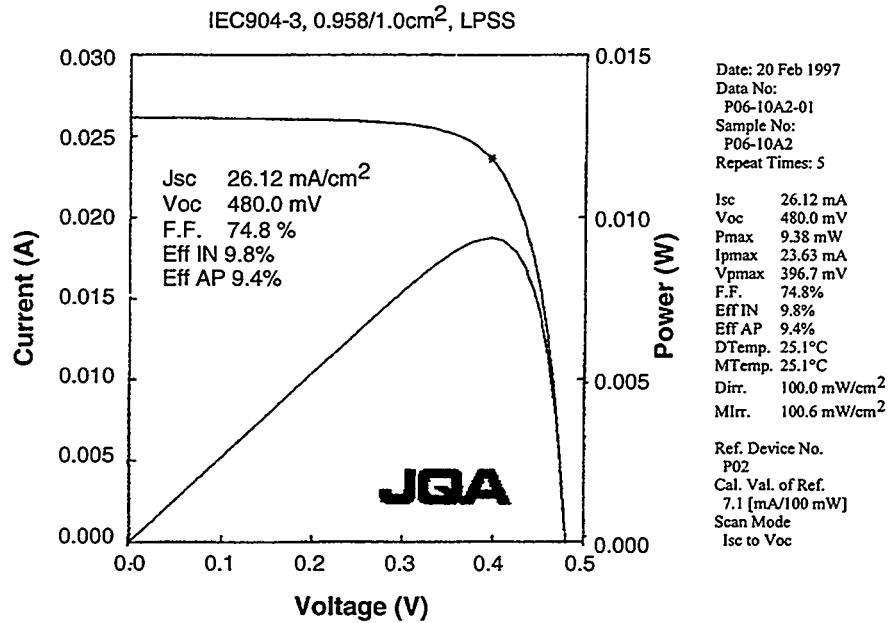

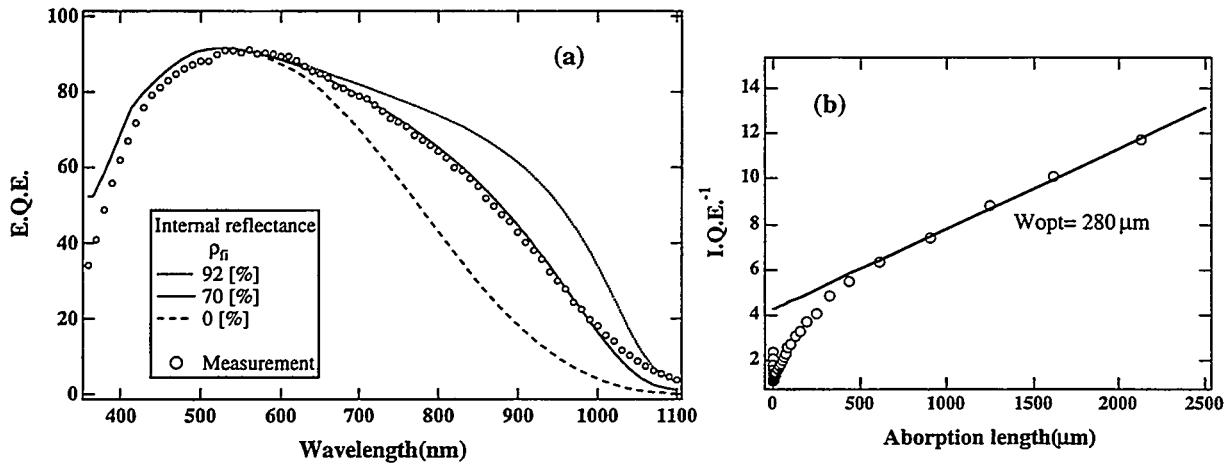

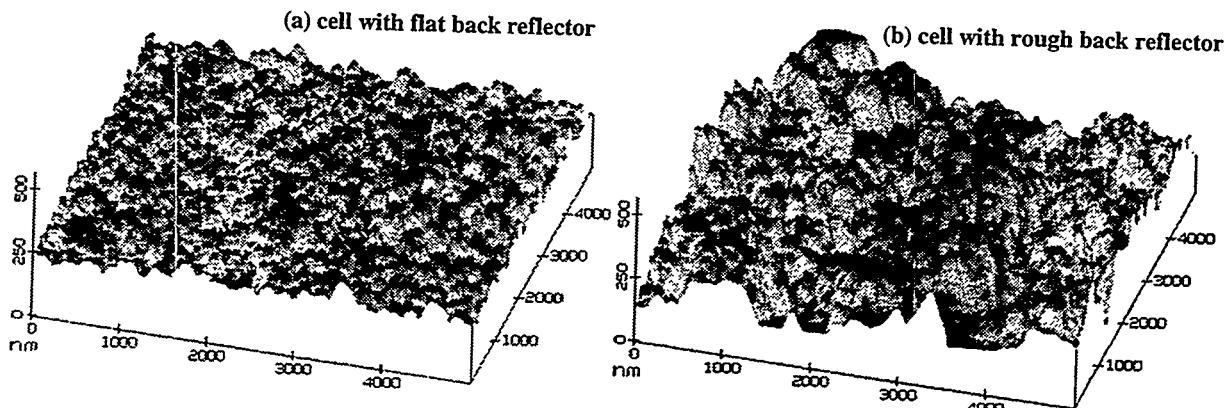

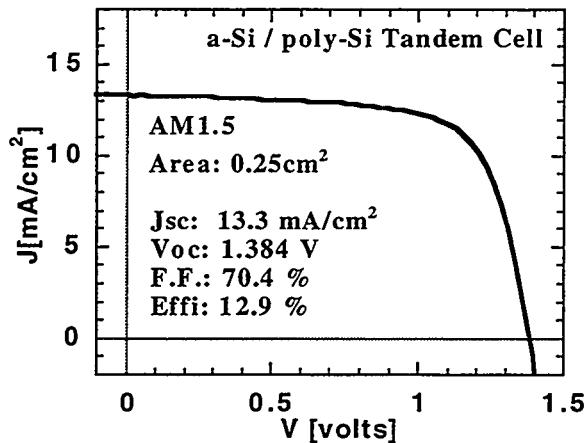

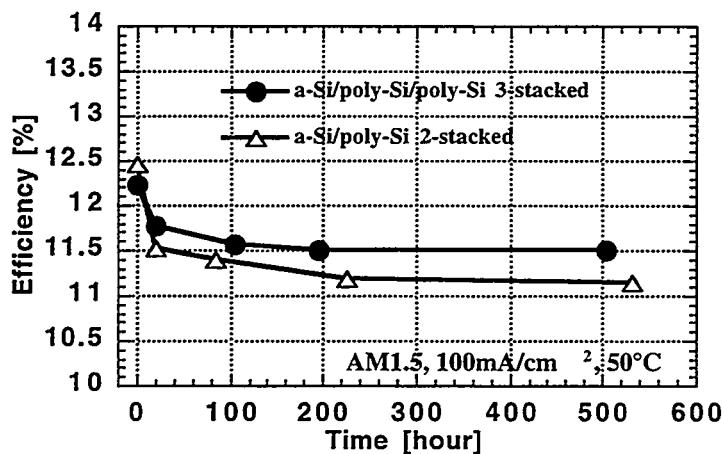

| <i>Optical Confinement Effect for Below 5 <math>\mu</math>m Thin Film Poly-Si Solar Cell on<br/>Glass Substrate Fabricated at Low Temperature</i> ..... | 120 |

| Kenji Yamamoto, Takayuki Suzuki, Masashi Yoshimi, Yoshifumi Okamoto,<br>Yuko Tawada, Akihiko Nakajima                                                   |     |

| <i>Technologies for Thin Film Poly-Si Solar Cells</i> .....                                                                                             | 127 |

| Steve Fonash and Bhushan Sopori                                                                                                                         |     |

| <i>High-Efficiency Solar Cell Development at the Fraunhofer ISE</i> .....                                                                               | 136 |

| W. Wetling, J. Knoblock, S. W. Glunz                                                                                                                    |     |

| <i>Review of the 4-Year R&amp;D Project on Crystalline Solar Materials and Devices<br/>in the New Sunshine Program</i> .....                            | 140 |

| Tadashi Saitoh                                                                                                                                          |     |

| <i>Getting to a Gigawatt</i> .....                                                                                                                      | 148 |

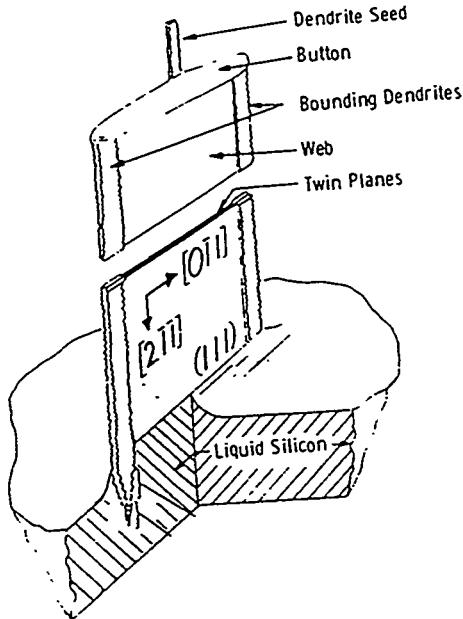

| J. I. Hanoka                                                                                                                                            |     |

| <i>Status of EBARA Solar, Inc.</i> .....                                                                                                                | 151 |

| D. L. Meier                                                                                                                                             |     |

## Poster Papers

|                                                                                                                                                       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <i>Recent Results on Growth and Handling of 125 <math>\mu</math>m String Ribbon Silicon.....</i>                                                      | 152 |

| R. L. Wallace, A. M. Gabor, X. F. Ma, and J. I. Hanoka                                                                                                |     |

| <i>Termination of Web Silicon Growth Due to Polyformation.....</i>                                                                                    | 153 |

| B. Ingram, B. Bathey, D. Meier and S. Mahajan                                                                                                         |     |

| <i>Potential Influence of the Recombination of Minority Carriers on Interstitial and Precipitated Copper in Silicon on Solar Cell Efficiency.....</i> | 158 |

| A. A. Istratov, H. Hieslmair, T. Heiser, C. Flink, E. R. Weber, W. Seifer, M. Kittler                                                                 |     |

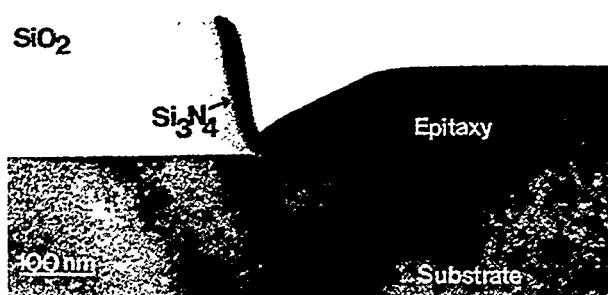

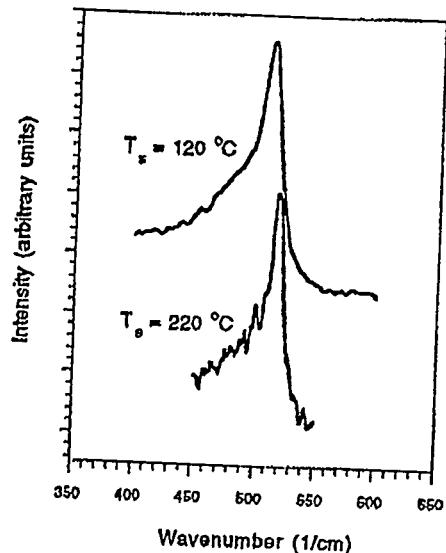

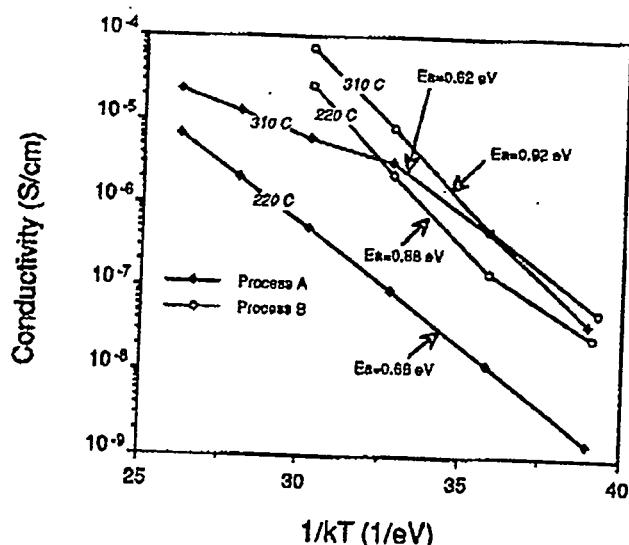

| <i>Selective Nucleation and Solid Phase Epitaxy Process for Si Thin Film Photovoltaics.....</i>                                                       | 162 |

| Claudine M. Chen and Harry A. Atwater                                                                                                                 |     |

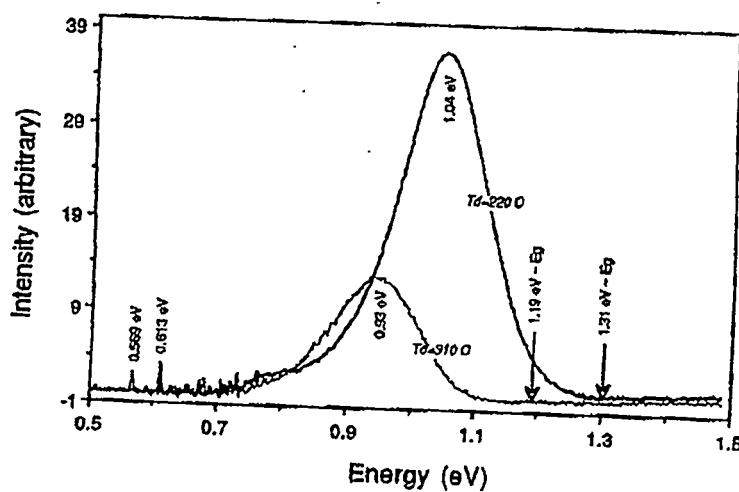

| <i>Relationships Between Room Temperature Photoluminescence and Electronic Quality in Microcystalline Silicon.....</i>                                | 166 |

| J. Koshka, S. Ostapenko, J. Cao and J. P. Kalejs                                                                                                      |     |

| <i>Modeling of Void Nucleation and Growth in Silicon.....</i>                                                                                         | 170 |

| P. S. Plekhanov, U. M. Gösele and T. Y. Tan                                                                                                           |     |

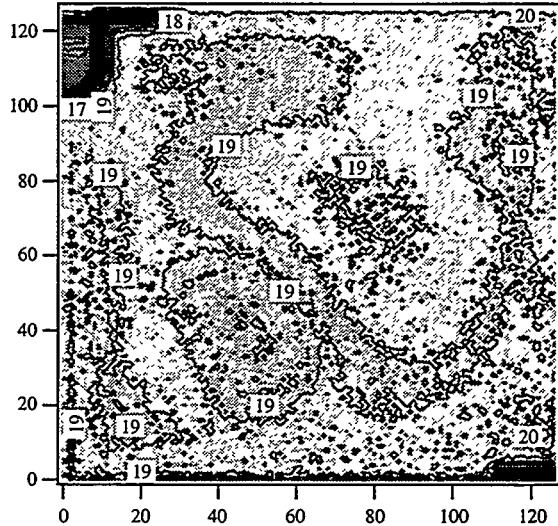

| <i>Recent Improvements on the PVSCAN5000.....</i>                                                                                                     | 174 |

| Bhushan Sopori, Chris Gaylord, Karen Nemire, Jamal Madjdpor, Marta Symko                                                                              |     |

| <i>Radiative Properties of Silicon.....</i>                                                                                                           | 179 |

| N. M. Ravindra, S. Abedrabbo, W. Chen, F. M. Tong, O. H. Gokce, Ray Eby, B. L. Sopori                                                                 |     |

| <i>Precipitation of Iron in Silicon.....</i>                                                                                                          | 187 |

| H. Hieslmair, A. Istratov, S. A. McHugo, C. Flink, E. R. Weber                                                                                        |     |

| <i>The Effects of Rapid Pre-Getter Anneal Treatments on the Performance of Cast mc-Si Solar Cells.....</i>                                            | 191 |

| S. Narasimha and A. Rohatgi                                                                                                                           |     |

| <i>The Reaction Kinetics of Iron at Silicon Surfaces and Interfaces.....</i>                                                                          | 195 |

| Aimee L. Smith, Sang H.I Ahn, Song Zhao, Lynn L. Chalfoun, Gerd Norga, Lionel C. Kimerling<br>(Paper unavailable at time of printing)                 |     |

| <i>EFG Manufacturing Line Technical Progress and Module Cost Reductions Under the PVMaT Program.....</i>                                              | 196 |

| J. Cao, R. Gonsiorawski, M. Kardauskas, J. Kalejs, C. O'Brien, M. Prince and E. Tornstrom                                                             |     |

|                                                                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| <i>Boron Gettering of Si Substrates and the Effect on Cell Performance</i> .....                                         | 198 |

| T. Saitoh, S. Ishikawa, N. Ohe, Y. Takano and T. Warabisako                                                              |     |

| <i>Aluminum Gettering of Gold in Single-Crystal Silicon</i> .....                                                        | 202 |

| Subhash M. Joshi, Ulrich M. Gösele, and Teh Y. Tan                                                                       |     |

| <i>Response of Silicon-Film<sup>TM</sup> Polycrystalline Silicon to Post-Growth Quality Enhancement Treatments</i> ..... | 206 |

| Yibin Bai, David H. Ford, James A. Rand, Robert B. Hall and Allen M. Barnett                                             |     |

| <i>Magnetic Field Topography for Current Distribution Measurements in Solar Cells</i> .....                              | 211 |

| J. Kabs and H. J. Möller                                                                                                 |     |

| <i>The Effect of Gettering on Areal Inhomogeneities in Large-Area Multicrystalline-Silicon Solar Cells</i> .....         | 215 |

| James M. Gee and Bhushan L. Sopori                                                                                       |     |

| <i>Boron-Doped Back-Surface Fields Using an Aluminum-Alloy Process</i> .....                                             | 219 |

| James M. Gee, Michel Bode and Beverly Silva                                                                              |     |

| <i>Industrial Process for Bulk and Surface Passivation of Multicrystalline Silicon Solar Cells</i> .....                 | 223 |

| F. Duerinckx, R. Einhaus, E. Van Kerschaver, J. Szlufcik, J. Nijs, R. Mertens                                            |     |

| <i>Epilift Silicon Solar Cells</i> .....                                                                                 | 227 |

| Andrew Blakers, Klaus Weber and Kylie Catchpole                                                                          |     |

| <i>PV Optics: Cell and Module Design</i> .....                                                                           | 231 |

| Bhushan L. Sopori, Jamal Madjdpour, Chris Gaylord                                                                        |     |

| <i>Low Level CU Contamination Studied by Transient Ion Drift</i> .....                                                   | 233 |

| T. Heiser, S. McHugo, H. Hieslmair, C. Flink, A. Istratov, and E. R. Weber                                               |     |

## R&D Issues for Crystalline Silicon to Support GW/Yr. Goal by the Year 2010

Bhushan Sopori

National Renewable Energy Laboratory

1617 Cole Boulevard

Golden, CO 80401

The demand for photovoltaic (PV) energy has been increasing at a rapid pace during the last few years. The silicon technology is continuing to meet this need with improved solar cell/module efficiency and cost. It is expected that this demand will continue to grow, and that by the year 2010 it will exceed 1GW/yr. Other factors such as the "Million Solar Roofs" Program, if successful, can further enhance this demand. To date, nearly 90% of the PV demand is satisfied by crystalline silicon technology, with the balance using a-Si and other thin-film technologies. Although it is expected that newer technologies such as CIS and CdTe will be launched into commercial production, silicon is expected to continue to have a dominant role. This is based on the fact that the price for silicon modules has already come down, and further cost reductions, approaching \$2/W, are being contemplated. Increased productions that can raise the factory output levels to 25 MW/yr. can further reduce the module cost to \$1.78/W.

Clearly, silicon is facing challenges, both on the absolute terms of lowering the module costs and with the advent of potentially lower-cost thin film technologies. There are concerns as to how Si can meet these challenges, continue as the leading technology in the future, and meet the heavy demands in the future. The flip side of this argument is that the newer technologies have to compete with the performance, reliability, and cost of crystalline silicon technologies.

The previous workshops have addressed some issues on high demands and cost reduction by improving the cell performance and the cell cost. This workshop is aimed at raising the awareness of these issues and initiating planning activities. At the outset, a workshop on the role of impurities and defects in silicon device processing may appear out of place for discussion of such issues. However, because a major impact on the production can occur precisely by improving the material quality and fabrication procedures, this workshop is a valuable opportunity to address these issues. Some of these issues are related to:

- Silicon feedstock: availability/cost/quality

- Improved material quality through improved crystal growth, and post-growth gettering and defect passivation

- Further understanding the performance-limiting factors and the approaches to resolve them

- The use (handling, device processing, encapsulation) of thinner wafers

- Higher efficiency device fabrication

- Higher throughput processes

- "PV" oriented equipment

- Monitoring techniques

In addition to current “wafer-based” devices, it is expected that a major effort will be devoted to the development of thin silicon solar cells. New understanding of the mechanisms of nucleation and growth, grain enhancement processes, thin film stress control, low-temperature gettering, and defect passivation are all a testament to the success of this emerging approach.

\* There are additional issues related to module fabrication, and system design and development, that will not be directly discussed in this workshop.

# A Study of the Manufacture at 500 MWp p.a. of Crystalline Silicon Photovoltaic Modules

T.M. Bruton (BP Solar), G. Luthardt, K.D. Rasch, K. Roy (ASE), I.A. Dorrity, B. Garrard, L. Teale (Crystalox), J. Alonso, U. Ugalde (IES-UPM), K. Declerq, J. Nijs, J. Slufcik (IMEC), A. Räuber, W. Wetling (FhG-ISE), A. Valléra (ICAT)

In the framework of the EU programme APAS a study was performed by eight companies and research institutions with the task to determine if 500 MWp per year could be successfully manufactured using crystalline silicon technology. The result of the study showed that module costs of 1 ECU/Wp using multicrystalline wafers with screen printed contacts are achievable. Further extension of the ribbon silicon technology by the EFG process could lower costs further to 0.7 ECU/Wp. It was confirmed that it is market size which is a key driver in cost reduction.

Annual production of silicon PV modules is presently around 60 MWp p.a. This is very small compared to the market for PV demanded by such schemes as „PV power for the world“, the ALTENER study and the Madrid Conference on a „Renewable Energy Strategy for Europe“ where an annual production rate of 500 MWp to 1 GWp was required. This study was a multi-institution study carried out under the APAS programme of the European Commission [1] to determine if manufacture at the scale of 500 MWp p.a. is possible with crystalline silicon technology. The study also examined the potential to reduce the costs by increased volume with the target of 1 ECU/Wp for factory gate module costs.

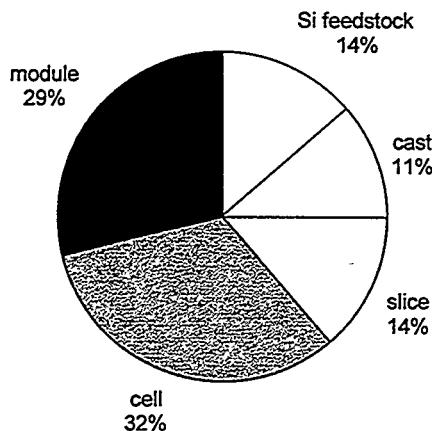

The silicon PV module manufacturing process can be sub-divided into five stages:

(1) Feedstock production, (2) crystallisation, (3) wafering, (4) solar cell processing and (5) module fabrication. A group was appointed to study each of these stages as a task.

Approximate calculations of product costs were carried out at the task level but the detailed costing was done by the IES group in Madrid using a commercially available computer costing package, STAMPP (task 6). Here a population weighted and over several European countries averaged labor rate of 14.4 ECU/hr was used which included all social costs.

(1) Concerning the silicon feedstock it was assumed that the demand of 5000 tons p.a. should be provided by a new production facility that is producing silicon only for PV applications. After investigating several other technical paths it was concluded that a somewhat relaxed Siemens process could be used for this feedstock fabrication and that the polysilicon costs would be about 20 ECU/kg, a number which is higher than todays feedstock price which is based on „heads and tails“ of the microelectronic industry.

(2) Three possible options to convert the silicon feedstock into a crystalline form appropriate for wafer production were taken into account in the study: (i) directional solidification of multicrystalline ingots (DS), (ii) Czochralski growth of monocrystalline boules (CZ) and (iii) direct crystallization as silicon foil (EFG). For each method costs were evaluated together with producers assuming the most advanced technique available.

(3) Wafering was assumed to be performed by multiwire saws (MWS) with little technological improvement above present day practice. Wafer dimensions were assumed as 125x 125x 0.2 mm<sup>3</sup> and the kerf loss as 230 µm.

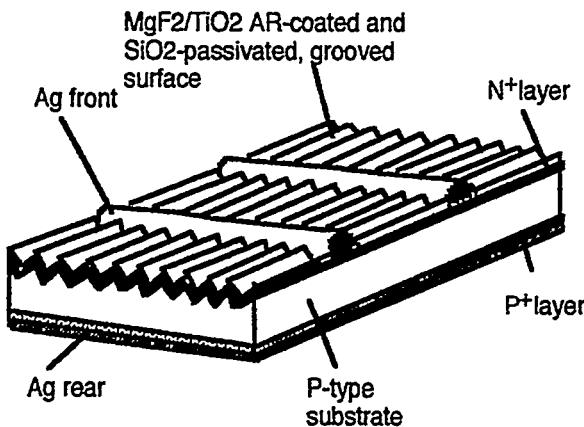

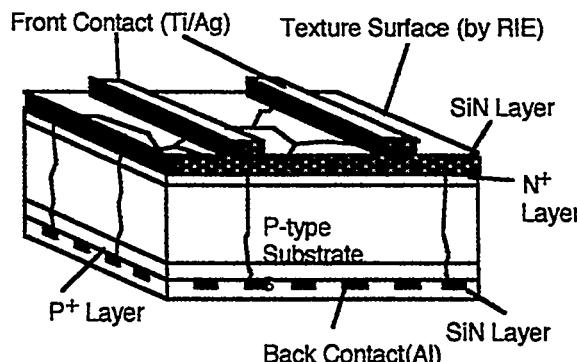

(4) Five solar cell processing schemes were considered in the study:

- Screen printing solar cells [2] which is the predominant present day manufacturing process (SP). This is the assumed process also for EFG material although the exact process details of the present EFG solar cell process are confidential.

- Laser grooving of buried grid (LGBG) cells. This is a high-efficiency process which has been in operation at BP Solar España since 1991 [3].

- MIS contacting to diffused solar cells which is developed at ASE and which has demonstrated reproducibly high-efficiency solar cells [4].

- A simplified localized back surface field (LBSF) process for solar cells. The LBSF process which is similar to the PERL process of UNSW, (the world record holding process) has demonstrated near world record efficiencies with float zone wafers at Fraunhofer ISE [5].

It was necessary to set solar cell efficiencies and wafer size and thickness giving full consideration to data inputs from wafering and module fabrication studies. Table 1 shows the efficiencies for the various technologies as assumed for the cost calculations.

**Table 1.** Assumed efficiencies versus wafer type and size for different cell processing technologies.

| Cell Technology | 125x125 mm <sup>2</sup> , mono | 125x125 mm <sup>2</sup> , multi | 150x150 mm <sup>2</sup> , multi |

|-----------------|--------------------------------|---------------------------------|---------------------------------|

| Screen printed  | 16                             | 15                              | 14                              |

| LGBG            | 18                             | 16                              | 16                              |

| MIS-Diffused    | 17                             | 15                              | 13                              |

| EFG             | n/a                            | 14.4                            | n/a                             |

| LBSF            | 20                             | n/a                             | n/a                             |

(5) Two module technologies were investigated in the study:

- Reflow soldering for the tabbing process and vacuum lamination using EVA, (S/L)

- Ultrasonic welding for the tabbing process and resin in-fill between glass plates, (USW/RF).

Two high capacity highly automated module lines were assumed for this task.

(6) For the detailed cost calculations seven alternative scenarios have been costed [6]. They are summarized in Table 2.

**Table 2.** Scenarios for costing of different crystalline silicon manufacturing technologies. The abbreviations used are explained in the above text.

| Process    | Crystallization | Wafering | Solar Cell Proc. | Module Assemb. |

|------------|-----------------|----------|------------------|----------------|

| Scenario 1 | DS              | MWS      | SP               | S/L            |

| Scenario 2 | CZ              | MWS      | SP               | S/L            |

| Scenario 3 | CZ              | MWS      | LGBG             | S/L            |

| Scenario 4 | CZ              | MWS      | MIS              | S/L            |

| Scenario 5 | CZ              | MWS      | MIS              | USW/RF         |

| Scenario 6 | CZ              | MWS      | LBSF             | S/L            |

| Scenario 7 | EFG             | n/a      | SP               | S/L            |

The costs as specified for the five processing tasks are given in Table 3.

**Table 3.** Factory cost in ECU/Wp for different crystalline manufacturing scenarios at 500 MWp p.a. manufacture by process step.

| Process    | Crystalliz. | Wafering | Solar Cell | Module assembly | Module power(Wp) | Cost ECU/Wp |

|------------|-------------|----------|------------|-----------------|------------------|-------------|

| Scenario 1 | 0.28        | 0.22     | 0.11       | 0.30            | 86.9             | 0.91        |

| Scenario 2 | 0.62        | 0.21     | 0.12       | 0.31            | 85.6             | 1.25        |

| Scenario 3 | 0.55        | 0.18     | 0.14       | 0.28            | 96.3             | 1.15        |

| Scenario 4 | 0.59        | 0.21     | 0.18       | 0.30            | 90.9             | 1.28        |

| Scenario 5 | 0.59        | 0.21     | 0.18       | 0.36            | 90.9             | 1.34        |

| Scenario 6 | 0.50        | 0.18     | 0.83       | 0.27            | 107.0            | 1.78        |

| Scenario 7 | 0.28        | 0        | 0.11       | 0.32            | 81.5             | 0.71        |

In Table 4 the cost for the seven scenarios are specified with respect to the main cost categories as labour, materials, maintenance, depreciation and overhead. All costs are given in ECU/Wp.

**Table 4.** Factory cost in ECU/Wp for different manufacturing scenarios broken down into the main cost categories at 500 MWp p.a. manufacture.

| Process    | Labour | Materials | Maintenan. | Depreciat. | Overhead | Cost ECU/Wp |

|------------|--------|-----------|------------|------------|----------|-------------|

| Scenario 1 | 0.10   | 0.66      | 0.03       | 0.07       | 0.05     | 0.91        |

| Scenario 2 | 0.13   | 0.85      | 0.07       | 0.12       | 0.07     | 1.25        |

| Scenario 3 | 0.13   | 0.78      | 0.06       | 0.12       | 0.06     | 1.15        |

| Scenario 4 | 0.13   | 0.88      | 0.09       | 0.17       | 0.06     | 1.28        |

| Scenario 5 | 0.13   | 0.88      | 0.09       | 0.17       | 0.07     | 1.34        |

| Scenario 6 | 0.32   | 0.94      | 0.14       | 0.27       | 0.11     | 1.78        |

| Scenario 7 | 0.13   | 0.40      | 0.04       | 0.07       | 0.07     | 0.71        |

These results show that the avoidance of the wafering step in the EFG process produces the lowest module cost. The well proven route for screen printed cells on wafers made by directional solidification and wire sawing gives the next lowest cost and is at 0.91 ECU/Wp below the 1 ECU/Wp target. The technology improvements required to achieve this scenario are modest and all the individual parameters of ingot size, wafer thickness and cell efficiencies have been demonstrated. All the processes based on CZ wafers show higher costs because of the high wafer cost. However it can be seen that the LGBG process, with the highest efficiency, produces the lowest cost on monocrystalline wafers.

The other new processes require further improvement to be cost effective and the study has shown which areas must be addressed to achieve cost competitiveness. In particular the LBSF process which demands by far the highest labour and investment costs in this study is not optimized and requires more detailed study and process experience to fully specify the lowest cost production route. The balance of systems benefit of very high efficiency should also be noted.

The study has shown, subject to appropriate investment, that there are no barriers to achieving 500 MWp p.a. production of photovoltaic modules using crystalline silicon. Costs below or near 1 ECU/Wp are projected for a number of crystalline silicon manufacturing technologies. Investment costs are in the region of 1 ECU/Wp of installed production capacity and around 3000 jobs would be created in a 500 MWp p.a. manufacturing plant.

This study has clearly confirmed the widely held view that by increasing the market size, the prize of PV modules will fall. Indeed the study shows that it is market size which is one of the most significant factors in achieving cost reduction.

## References

- [1] APAS Contract RENA-CT94-0008 „MUSIC FM“

- [2] J. Nijs et al., Proc. 24th IEEE PVSC (1994) p.1242

- [3] T.M. Bruton, et al Proc. 12th E.C. Photovoltaic Solar Energy Conf. (1995) p. 761

- [4] K. Jaeger-Hezel et al., Proc. 13th E.C. Photovoltaic Solar Energy Conf. (1995) p. 1515

- [5] J. Knobloch et al., Proc. 13th E.C. Photovoltaic Solar Energy Conf. (1995) p. 9

- [6] U. Ugalde, J. Alonso et al., Proc. 14th E.C. Photovoltaic Solar Energy Conf. (1997), to be published

This is a shortened version of a paper presented at the 14th E.C. Photovoltaic Energy Conference in Barcelona, July 1997. A preprint of the full paper will be available at the conference.

## Addresses of the participants of the study

T.M. Bruton

BP Solar International

PO Box 191

Sunbury on Thames

Middlesex TW16 7XA, UK

G. Luthardt, K.D. Rasch, K. Roy

ASE GmbH

Industriestraße 13

D-63755 Alzenau, Germany

I.A. Dorrity, B. Garrard, L. Teale

Crystalox Ltd.

1 Limborough Rd.

Wantage, Oxon OX12 9AJ, UK

J. Alonso, U. Ugalde

Instituto Energia Solar

E.T.S.I. de Telecomunicaciones

Ciudad Universitaria

E-28040 Madrid, Spain

K. Declerq, J. Nijs, J. Slufcik

IMEC

Kapeldreef 75

B-3001 Leuven, Belgium

A. Räuber, W. Wetling

Fraunhofer Institute for Solar Energy Systems

Oltmannsstrasse 5

D-79100 Freiburg, Germany

A. Vallêra

ICAT

Univ. de Lisboa

Edif C1, Campo Grande

P-1700 Lisboa, Portugal

# Grown-In Defects in FZ and CZ Silicon Crystals

Takao ABE

Isobe R&D Center, Shin - Etsu Handotai

2-13-1 Isobe, Annaka - Shi, Gunma - ken 379-01

## ABSTRACT

Six silicon ingots of different diameters (200, 150, 125, 100, 75 and 50 mm) were grown from a single crystal puller under identical crucible and growth conditions. Each crystal included a region containing a junction between high and low growth rates. The distributions of SEP (Secco etch pit) defects and FP (flow pattern) defects were observed using longitudinal cut surfaces (110) along the growth direction <100>. Only the SEP defects were observed in the 50 mm crystal, and this was in the region in and around the time of slow growth rate. For the 75 and 100 mm crystals, a similar but smaller region of SEP defects was seen in the area of low growth rate. However, FP defects were also observed in the high growth rate regions of these crystals. For the crystals of 125 mm diameter and larger, both defects were found coexisting throughout the crystals. An effect on the defect density is still seen when the crystal growth was slowed. The behavior of the SEP and FP defects are exactly the same as that of A and D defects in FZ crystals, respectively. From the results presented here, it is confirmed that the species of intrinsic point defects is determined not by growth rate, but by the thermal gradient at the growth interface in CZ crystal growth. This has been demonstrated in the past for FZ crystal growth.

## INTRODUCTION

As integrated circuits such as D-RAMs go to finer design rules, smaller grown-in defects have an opportunity to affect the device performance. Therefore, since traditional IG (internal gettering) treatment [1] may not be enough, a high temperature hydrogen annealing has been proposed for denuding [2]. Moreover, epitaxial wafers which can be made free of grown-in defects have been used for high performance microprocessors and may be used in the future D-RAM generations. Finally, as the age of 300 mm wafers comes, it is anticipated that SOI may be utilized for all advanced devices. The behavior of grown-in defects during the bonded SOI process has been recently reported [3].

On the other hand, concerning R-OSF (ring like distributed oxidation induced stacking faults) the generation and annihilation conditions have been clearly demonstrated by Dornberger et al [4]. The nuclei of these stacking faults come from one of the grown-in defects discussed in this paper. However, with regard to COP (crystal originated particle) [5] and FP defects, the generation mechanism has not been discussed. The GOI (gate oxide integrity) clearly depends on the density of FP defects [6] but little has been reported (except one paper [7]) showing FP defects to affect the real device characteristics. This may be true due to the fact that actual device processes include a high temperature oxidation before the gate oxidation. Annihilation of the FP defects in such a process has been demonstrated by Yamagishi et al. [6]. It should be remembered, however, that if processing temperatures are reduced in the future, a serious effect from the FP defects may result.

Whereas the FP defects are associated with excess vacancies, it is shown in this paper that the SEP defects arise from secondary defects formed by excess silicon interstitials. The SEP defects may, therefore, be more important than the FP defects. Many researchers tend to connect the growth rate of the crystal with the formation of grown-in defects, but it is shown here that this concept is not true and the Voronkov theory [8] is not complete.

## EXPERIMENTS

A conventional CZ furnace was charged with 70 kg and used for pulling 6 different diameter silicon crystals (200, 150, 125, 100, 75 and 50 mm). First, the 200 mm crystal was grown and then poly crystal with the same weight as the 200 mm crystal was recharged into the puller. This process was repeated as crystals of progressively smaller diameters were grown. The crystals used here are summarized in Table 1.

| Diameter (mm) | 200  | 150  | 125  | 100 | 75  | 50  |

|---------------|------|------|------|-----|-----|-----|

| Weight (kg)   | 39.3 | 18.6 | 12.4 | 8.0 | 4.6 | 2.5 |

Table 1 Crystal weights (= recharged weights) of each diameter crystal.

Each crystal was grown to about 30 cm in length. The growth rate through most of the crystal was fixed at 1.0 mm / min. At the middle of the crystal (approximately 15 cm position) the growth rate was suddenly changed to 0.2 mm / min and held for 30 min (6 mm in length). To avoid the diameter increasing as the growth rate was decreased, the input power was changed just prior to slowing the growth (to add 14% for 200 mm and 2.5% for 50 mm). Before returning to the 1.0 mm / min growth rate, the input power was decreased. Seed rotation was 15 rpm and the crucible was counter-rotated at 1.5 rpm.

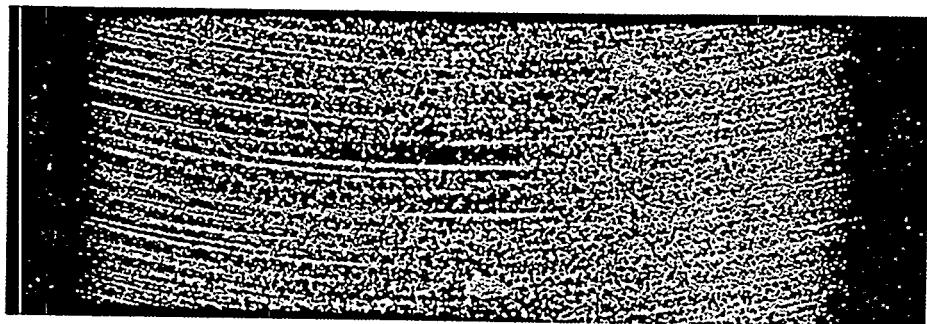

The crystals are <100> orientation and p type 10 - 20 Ωcm. Each crystal was cut perpendicularly to growth direction with the length of 15 cm as including the low growth rate region at center and then cut longitudinally to growth direction with (110) surface. Each wafer was polished with 700 μm in thickness. These wafers were deposited vertically in Secco etch solution for 1 hr. to observe the SEP and FP defects. In order to observe the R-OSF distribution and the growth interface shape which was influenced by low growth rate, these wafers were annealed at 1100 C, 1 hr in wet oxygen and observed by conventional x-ray diffraction topography. The distributions of oxygen and carbon concentration were measured along the growth direction centerlines by IR absorption using the measurement area of 4 mm in diameter. For the analysis of the defect distributions a wafer lifetime (WLT) method was applied using SEMILAB WT-85. In the FP defect annihilation experiment, PROTECH RTPF-850 as a rapid thermal annealer was used.

## RESULTS

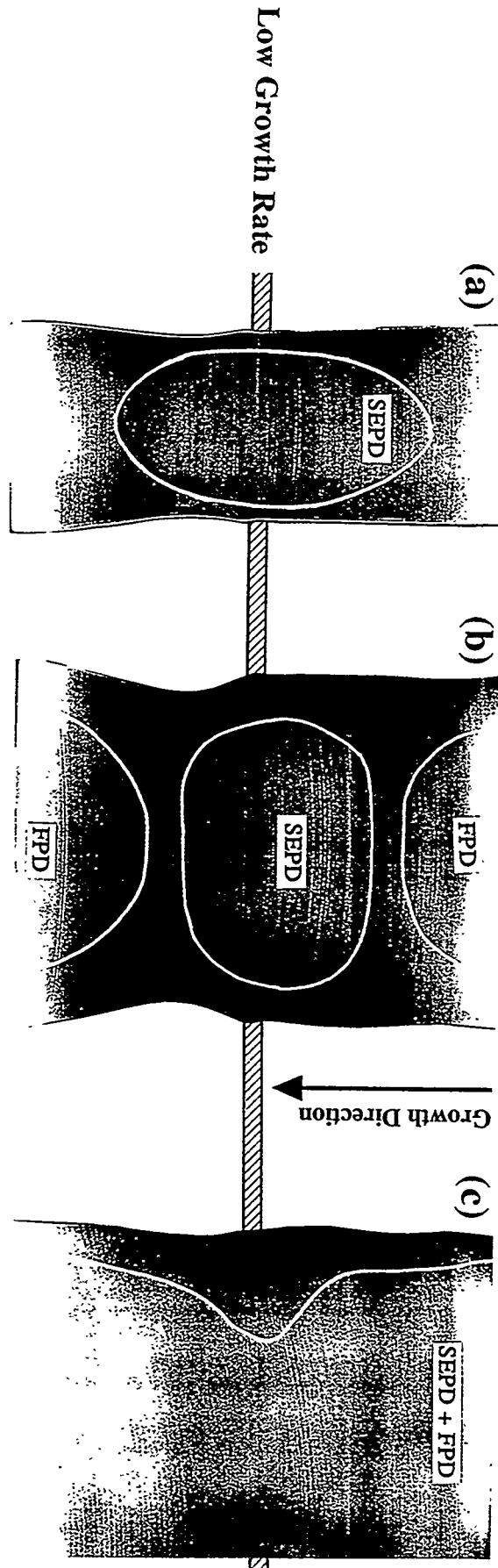

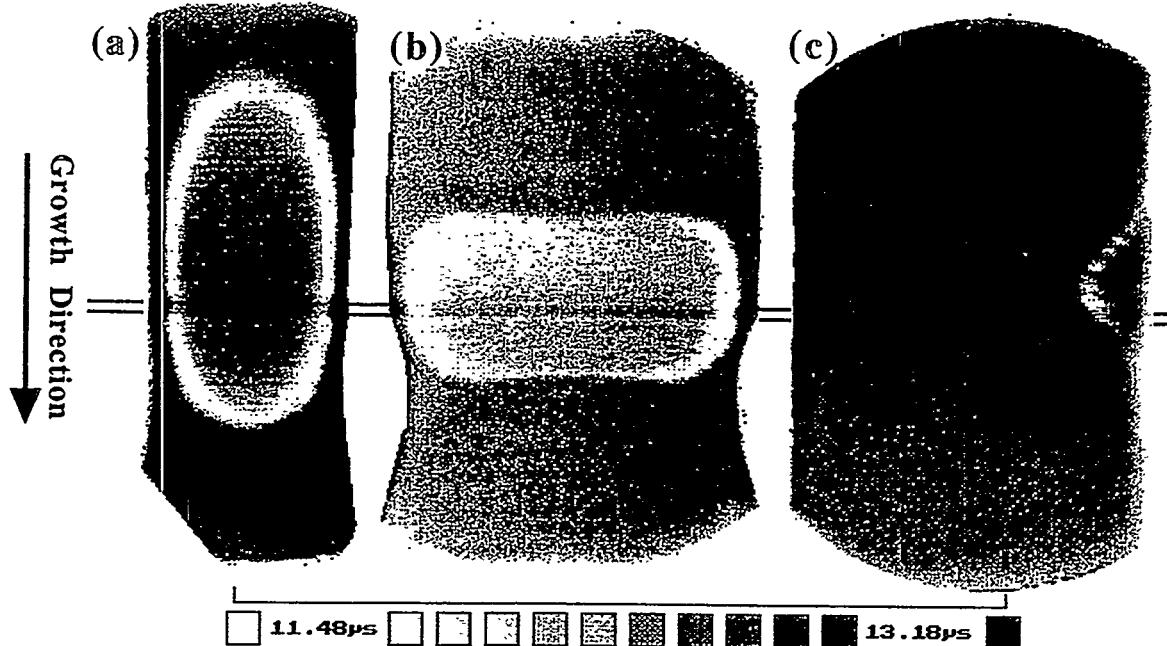

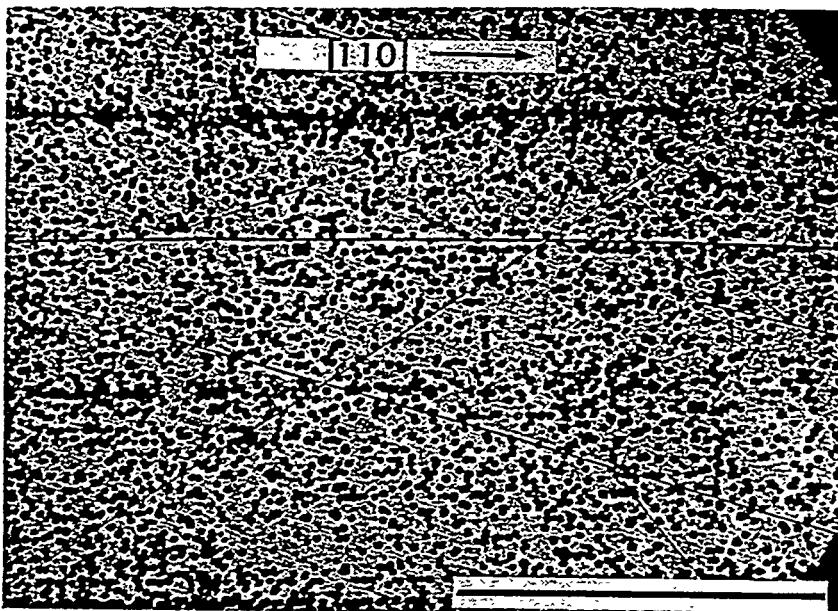

Figure 1 shows the x-ray topographs of the wafers annealed for the R-OSF observations, but contrast of R-OSF was not clearly seen. The temperature fluctuations induced by the operation at low growth rates caused the noted diameter changes in all cases. The growth interfaces as revealed by oxygen striations are varied by the low growth rate, but much less so for the larger diameter.

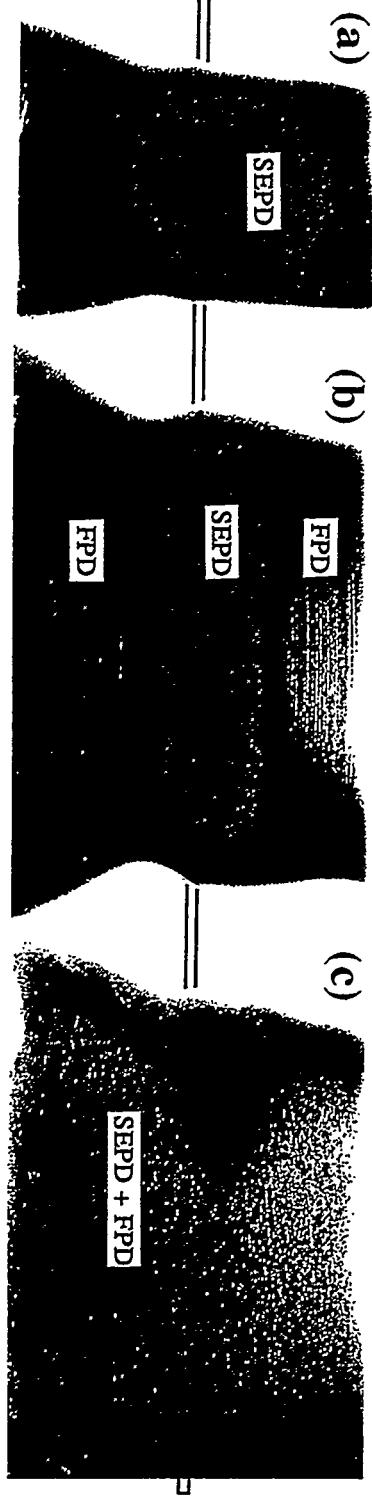

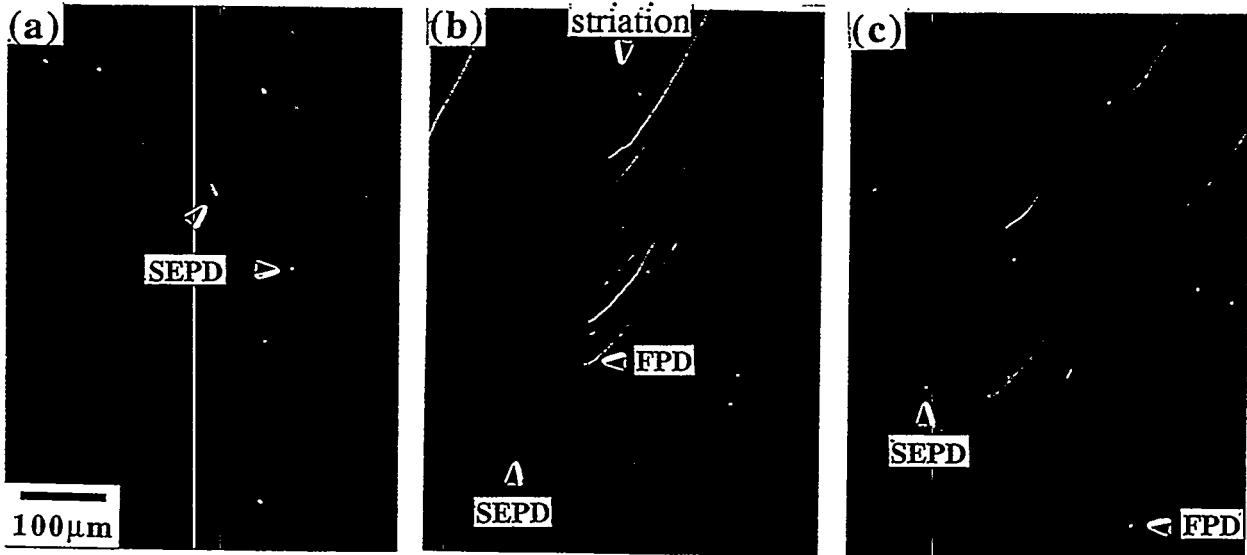

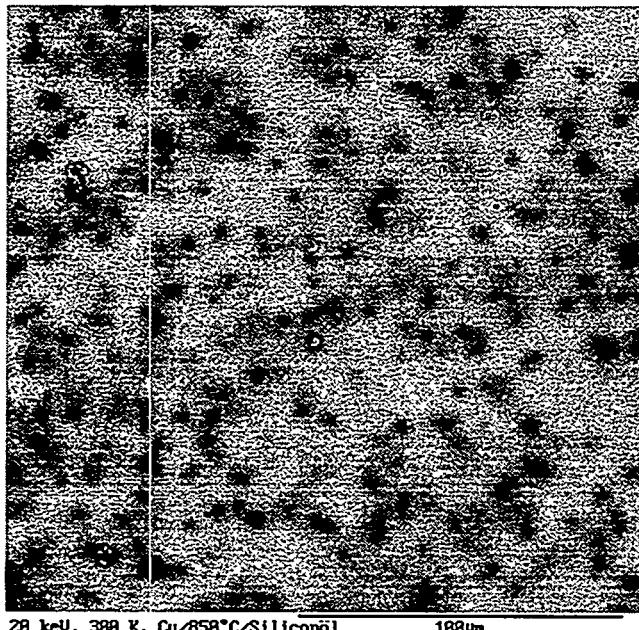

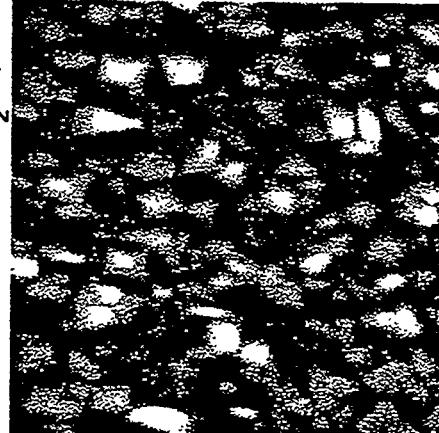

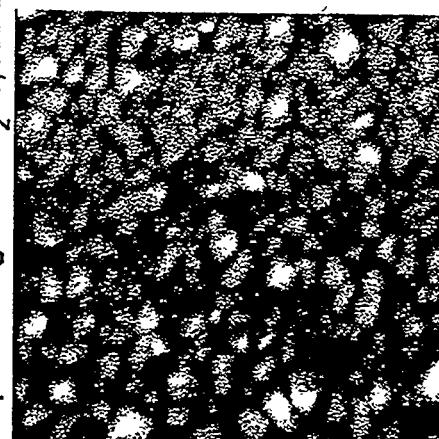

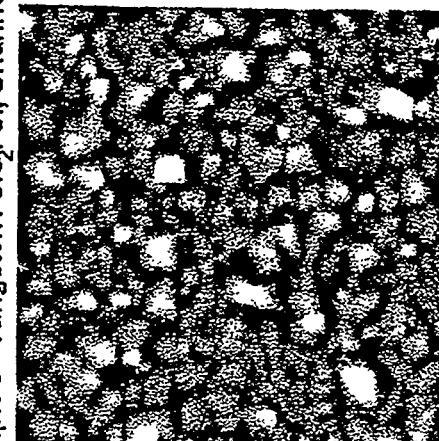

Figure 2 shows dark-field photographs using oblique lights after Secco etching. Macroscopic distributions of etch pits can be seen. In Fig. 2 (a) the 50 mm wafer is shown. There is a wide area before and after the low-growth section where SEP are generated. A part of this area was delineated by Nomalski optical microscopy and is shown in Fig. 3 (a). Various etch pits of different shapes and sizes are seen. The area before and after the slow growth shows SEP defects. Next, in Fig. 2 (b), the 100 mm wafer is seen. The area before and after the slow growth shows only SEP defects similar to the 50 mm sample, but in the outer high growth regions, FP and SEP defects are noted. The size of the core pit of the FP defect is extremely small compared to the SEP defects as seen in Fig. 3 (a). Nevertheless the size and density of the FP defects are small, we can easily observe their distributions as shown in Fig. 2 (b) owing to the extending flow patterns. The 200 mm wafer is shown in Fig. 2 (c). Here the effect of the slow growth on defect generation is only seen in the peripheral region. As can be seen in Fig. 3 (c), the defect area consists of both SEP and FP defects.

Figure 1 shows a sketch with the three types of defect regions superimposed : mainly

Fig. 2. Dark field photographs. 50mm (a), 100mm (b) and 200mm wafers in diameter (c).

Fig. 1. X-ray topographs of the longitudinal cut wafers with 50 mm (a), 100 mm (b) and 200 mm in diameter (c) annealed with 1100 C, 2hrs in wet. White lines showing the SEP and FP defect regions are superimposed by sketching from the dark field photographs as seen in Fig. 2.

Fig. 3. Microphotographs (a), (b) and (c) which are obtained in center area in Fig. 1 (a) the upper area of Fig. 1 (b) and the middle area of Fig. 1 (c), respectively.

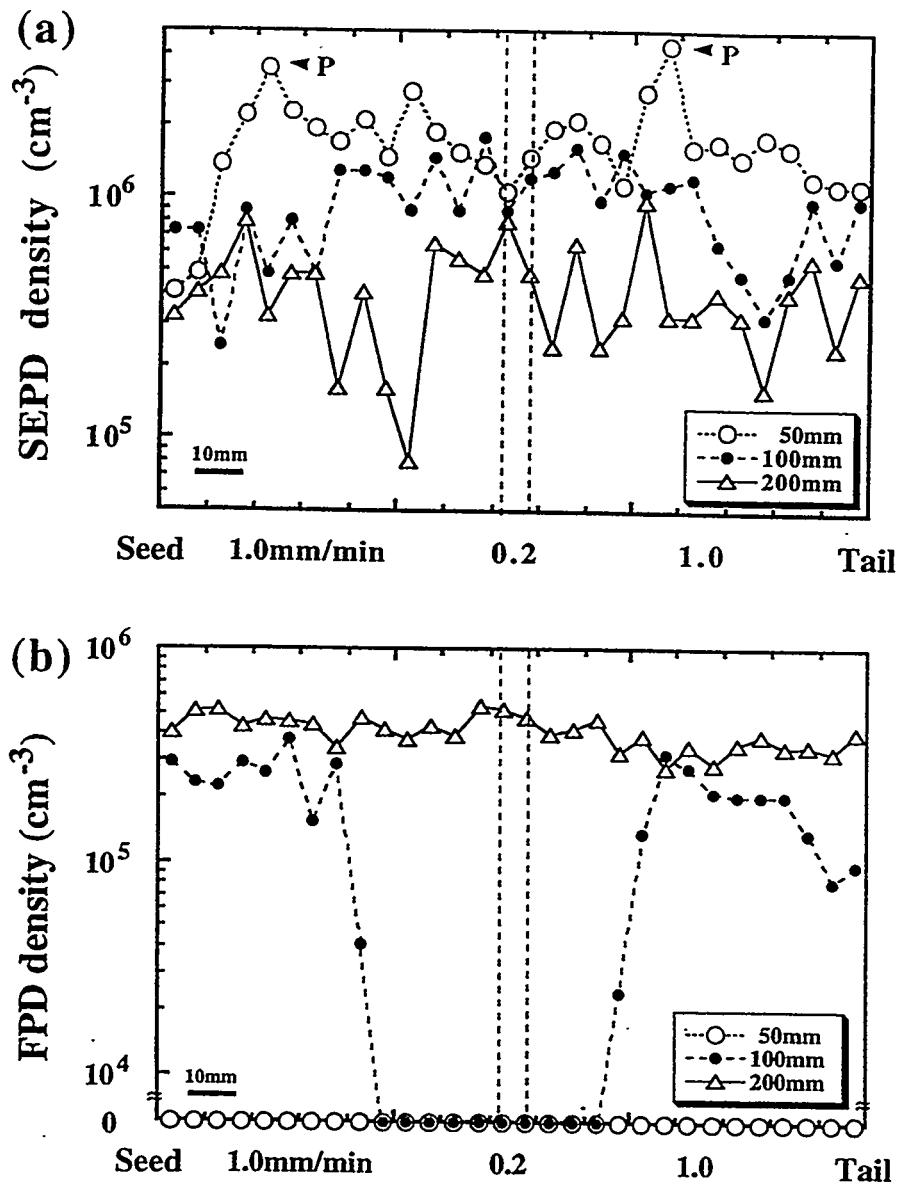

SEP, mainly FP on growth striations, and a combination of FP and SEP. The SEP are the main defects for small diameter crystals, while FP defects increase with larger diameters until finally the mixed defects form. Figure 4 (a) and (b) give an analysis of the density of SEP and FP defects along the growth direction centerlines for the 50, 100 and 200 mm wafers. The counting volumes of each defect are  $0.1 \text{ mm} \times 5 \text{ mm} \times 24.4 \mu\text{m}$  for the SEP and  $1.0 \text{ mm} \times 5 \text{ mm} \times 24.4 \mu\text{m}$  for the FP defects, respectively. These distributions are not always in accord with the pattern distributions of Fig. 2. This is because Fig. 2 gives a macroscopic view and Fig. 4 is created by counting densities in limited small areas. As seen in Fig. 3 (b), the FP defects are located along growth striations and the SEP defects distribute uniformly. In Fig. 3 (c), both SEP and FP defects are observed randomly. From Figs. 4 (a) and (b), it can be understood that as the crystal diameter increases, the SEP defects decrease and the FP defects increase.

Figure 5 shows a WLT distribution corresponding to Figs. 2 (a), (b) and (c) on the as polished surfaces. The SEP defect regions in Figs. 4 (a) and (b) have the lower WLT compared to the other region where is the lower density of the SEP. The values of the WLT in the mixed region of SEP and FP defects in Fig. 2 (b) do not show any reduction. This may be due to the lower densities of SEP defects. It is noted that the WLT in the periphery of the SEP defect regions in Figs. 2 (a) decreases clearly. This can be related to the peak densities indicated by p in Fig. 4 (a).

Along the so-called R-OSF band in Fig. 4 (c), several points with the low values of WLT are seen. They are probably related to nuclei of the R-OSF and they are generated as the results of interaction with the strong growth striations. In the area after the slow growth rate where is free of the strong growth striation no such contrast is seen.

The outer boundaries of the SEP defect regions in Figs. 1, 2 and 4 coincide to the regions of the lowest WLT values in Fig. 5. These boundary regions probably became to the R-OSF bands when these wafers are annealed at 1100C, 1hr in wet oxygen.

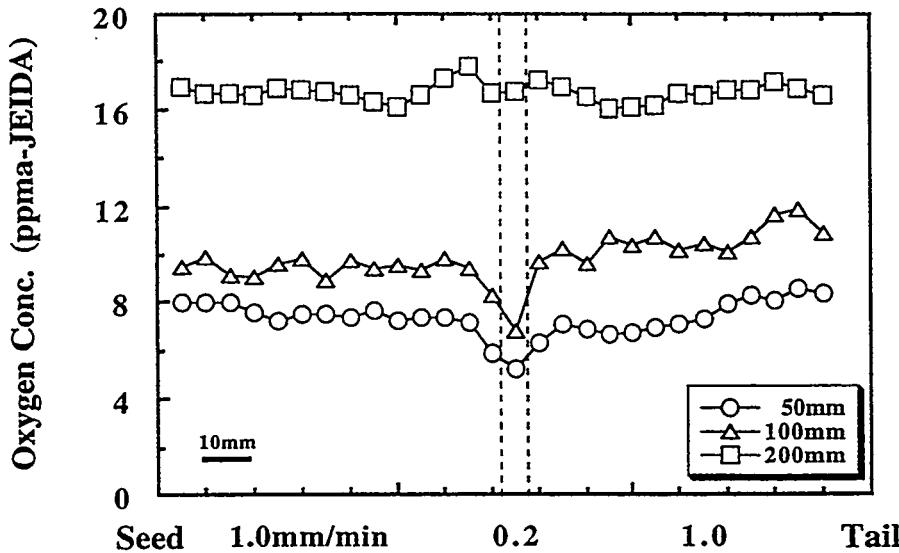

The distributions of oxygen concentrations along the growth direction centerlines are shown in Fig. 6. Carbon concentrations ranged from  $0.05 \sim 0.12 \text{ ppma}$  for all wafers. Due to the slow rotation of the crucible, the oxygen content was not high even for the 200 mm case. For the small diameters, it was extremely low. An anomalous oxygen distribution was seen in the low growth rate region, and will be discussed elsewhere.

Fig. 4. Density distributions of the SEP (a) and FP (b) defects measured along growth direction on center line.

## DISCUSSION

Habu et al [9,10,11] first formulated the behavior of secondary defects induced by intrinsic point defects such as the R-OSF [12] and the AOP [13] (anomalous oxygen precipitation) during CZ crystal growth. They postulated the main species of the intrinsic point defects at growth interface. However, from our experimental results [12,13,14,15], we have reported that there is no universal equilibrium concentration of intrinsic point defects during growth as far as the thermal gradient exists. The predominant point defects, whether excess silicon interstitials or vacancies at the growth interface are determined by the growth condition. This relation was first proposed by Voronkov [8] based on the experimental result obtained by Roksnouer et al. [16]. Recently, Dornberger et al [4] demonstrated that Voronkov's theory clearly agree with their experimental results. When  $V/G > C_{\text{crit}} = 1.3 \times 10^{-3} \text{ cm}^2 \text{ min}^{-1} \text{ K}^{-1}$ , the FP defects generate. On the other hand, when  $V/G < C_{\text{crit}}$ , large defects believed to

Fig. 5. Wafer lifetime maps. 50mm (a), 100mm (b) and 200mm wafers in diameter (c). Relative WLT values are represented by different levels of darkness.

be SEP appear. ( $V$  is the growth rate and  $G$  is the thermal gradient at growth interface.) However, the  $V/G$  relationships only explain that higher growth rate is necessary to compensate for larger thermal gradients and the thermal gradients in large diameter crystals are small compared to the smaller sized crystals.

They did not measure the actual thermal gradients of the growing crystal but employed the theoretical calculation values simulated using the commercially available finite element code FEMAG which include the effects of the shapes of growth furnaces and crystal diameters. The effect of growth rate on thermal gradient was ignored. The higher growth rate on the same diameter introduces the smaller thermal gradient as shown in our experimental results in the FZ crystal growth. The thermal gradient should be a reverse function of the growth rate.

Moreover, if the Voronkov's relation is kept even when the growth rate is zero, excess interstitials should be generated independently of the thermal gradient. However, when a crystal is heated with uniform temperature distribution, the vacancy rich crystal will be realized. It can be said that vacancy is predominant in equilibrium state of silicon in terms of the thermal gradient (when  $G = 0$ ). On the other hand, heating with a strong thermal gradient brings about excess interstitials as shown in the experimental results by Roksnoeur et al. [16]. They demonstrated that the D defect region changes into the A defect region by *in situ* annealing after growth.

We have proposed that the principal parameter determining whether excess silicon interstitials or excess vacancies is only the thermal gradient  $G$  based on results using FZ crystals [14]. In this paper based on CZ crystals, it is again proposed that growth rate is not a controlling parameter.

In these experiments, the growth conditions such as the crystal puller configuration, the initial melt level and especially the growth rate are the same for the 6 crystals of diameters from 50 to 200 mm in diameter. Nevertheless, the FP defects do not generate in the 50 mm crystal at the growth rate of 1.0 mm / min. When the growth rate is reduced to 0.2 mm / min, as seen in Figs. 1 (a), 2 (a), and 4 (a), a high density of SEP appear not only in the low growth region, but also in the sections before and after this part. Such extraordinary effects have been previously reported for FZ crystals [14,15], the fundamental reason for this phenomenon is not fully understood, but we have proposed that the high thermal gradient

Fig. 6. Oxygen concentration distributions along growth direction.

effect extends to the region of the material already grown and continues after the growth rate is restored.

In the 75 and 100 mm crystals grown at 1.0 mm / min, FP defects spread across the whole area except the periphery. However in the low growth section (0.2 mm / min, 30 min) and adjacent areas the FP defects disappear. On the contrary, SEP defects emerge. This fact is exactly the same phenomenon [15] which one of the authors has reported in FZ crystals. There the D defect region changes into an A defect region by stopping the growth of a 40 mm diameter crystal for 2 min. Therefore, it is reasonable to conclude that the origin of the SEP defects is the same as that of the A defects and the origin of the FP defects is the same as that of the D defects in FZ crystals.

For the CZ crystals greater than 125 mm in diameter, the effect of the low growth rate does not show so clearly the replacing of FP defects with SEP defects. This indicates that in the larger crystals, the thermal gradient is relatively small and the heat capacity is large enough to minimize the effect of the low growth rate. However, from the previous discussions, the parameter controlling whether excess interstitials or vacancies is predominant at the growth interfaces is the thermal gradient and not the growth rate. Different lattice strains are induced which allow for excess silicon interstitials or vacancies.

Using the same growth conditions for different diameter crystal brings about differences in melt convection and evaporation of oxygen from the melt. Hence, the oxygen concentration varied widely. However, the behavior of the SEP and FP defects is consistent and independent of the oxygen concentration. Therefore, it appears that the interaction between intrinsic point defects themselves is dominant, rather than the interaction between the intrinsic point defects and oxygen atoms. In the larger crystals, both the SEP and FP defects are mixed in the same regions. There are two possibilities to explain the intrinsic point defect interaction. One is the idea that the interaction between the same kind of defect (interstitials or vacancies) is stronger than the interaction between interstitials and vacancies. (If vacancies interacts with interstitials they are annihilated as they combine.) The second explanation is that the reaction temperatures are different. For instance, the reaction temperature for excess self interstitials may be higher than that for excess vacancies ; possibly over 1200 C for excess interstitials and under 1200 C for excess vacancies as previously reported for FZ crystals [15].

Previously, it has been noted that the FP defect density has a direct relationship with GOI [ 6 ]. So crystals having a lower density of FP have been required. These were created by using an after-heater during the crystal growth process.

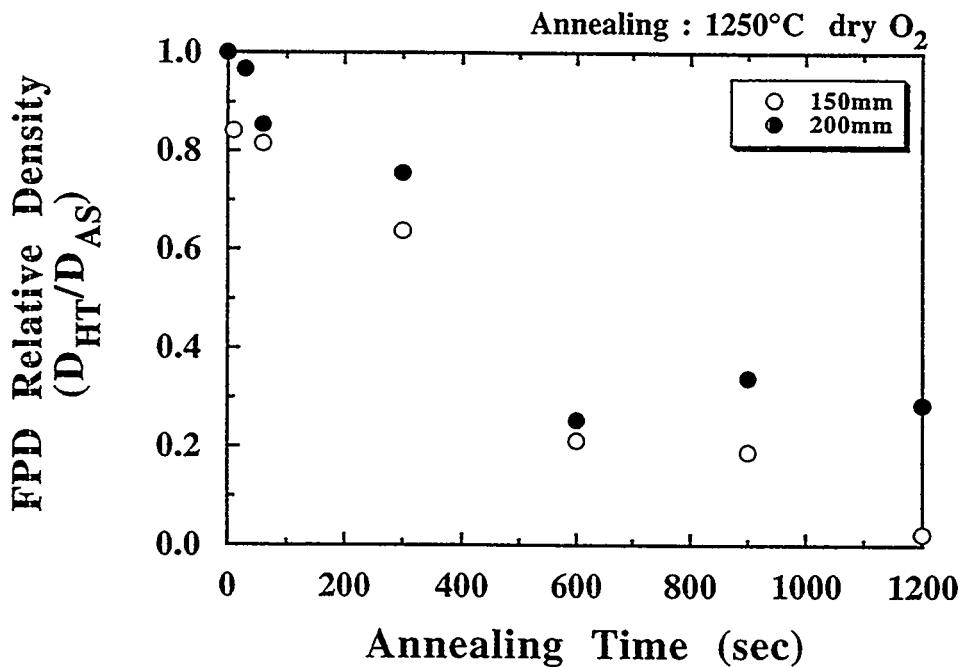

However, as the density of FP defects decrease, their size increases. A solution which

Fig. 7. Annihilation rate of the FP defects normalized with densities in as-grown state on different crystal diameter.

provides a smaller density of larger and more stable defects is not desirable for future device characteristics. Figure 7 shows the results of an annihilation experiment on FP defects using a RTA. The FP defects annihilate quickly when the specimens are thin, as in a wafer. The annealing temperature used was 1250 C in an ambient of dry oxygen. The process was ramped up and down from and to room temperature in 20 sec. Two crystals were examined: one was 150 mm in diameter with a relatively high growth rate of 1.18 mm / min and the other was 200 mm grown at 0.8 mm / min. It can be seen that the FP defects of higher density disappear faster than those of lower density. This may be due to the defects being of a bigger size.

In the future, for crystals of 300 mm and larger, the sizes of FP and SEP defects are expected to be large. In order to prevent these defects, the authors propose that as fast a growth rate as possible be used even though there would be an increase in the density of the FP defects.

## CONCLUSION

When crystals of different diameters are grown from the same growth condition at both high and low growth rates, the SEP defects are generate in the low growth region and the regions adjacent to it in the smaller crystals. In the rest of the high growth regions FP defects appear except near the periphery. For larger crystals, the effect of the low growth rate is small but still exists in the periphery. Both types of defects appear together. From the analogy with FZ crystals, the SEP defects relate to excess silicon interstitials similar to the A defects, and the FP defects are associated with excess vacancies as are the D defects in FZ material. The oxygen in CZ crystals does not significantly disturb the formation of either defect. Finally, it may be concluded that the essential parameter determining the species of intrinsic point defects at the growth interface is not the growth rate, but the thermal gradient. From the viewpoint of perfect crystals, the properties of FP defects are understood to some extent. However, the SEP defects may be more harmful to devices of the future and more fundamental analysis is needed on them.

## ACKNOWLEDGEMENT

The authors deeply thank Y. Yamagishi group (SEH R&D) for growing crystals, Y. Nakazato group (Nagano Denshi) for wafering process and S. Ushio group (SEH R&D) for x-ray topographs and IR measurements.

## REFERENCES

- 1) T.Y.Tan, E.E.Gardner and W.K.Tice : *Appl. Phys. Lett.* 30, (1977) 175.

- 2) H.Kubota, M.Numano, M.Miyashita, S.Samata and Y.Matsushita : *Semiconductor Silicon 1994*, eds. H.R.Huff et al., (Electrochem. Soc. Pennington 1994) p.225.

- 3) T.Abe, K.Sunakawa, K.Hagimoto, and H.Aga : *Semiconductor Wafer Bonding, Science, Technology and Applications III* : eds. C.E.Hunt et al, (Electrochem. Soc. Pennington 1995) p.296.

- 4) E.Dornberger, W.V.Ammon, and H.Oerknug and H.Weidner : *J. Electrochem. Soc.* 143, (1996) 1648.

- 5) J.Ryuta, E.Morita, T.Tanaka and Y.Shimanuki : *Jpn. J. Appl. Phys.*, 29, (1990) L1947.

- 6) H.Yamagishi, I.Fusegawa, N.Fujimaki and M.Katayama : *Semicond. Sci. Technol.*, 7, (1992) A135.

- 7) J-G.Park, H.Kirk, K-C.Cho, H-K.Lee, C-S.Lee, and G.A.Rozgonyi *Semiconductor Silicon 1994*, eds. H. R. Huff et al., (Electrochem. Soc, Pennington 1994), p.370

- 8) V.V.Voronkov, *J. Cryst. Growth* 59, (1982) 625.

- 9) R.Habu, I.Yunoki, T.Saito, and A.Tomiura, : *Jpn. J. Appl. Phys.* 32, (1993) 1740.

- 10) R.Habu, K.Kojima, H.Harada, and A.Tomiura, : *ibid*, 32, (1993) 1754.

- 11) R.Habu, Iwasaki, T., Harada, H. and Tomiura, A. : *ibid*, 33, (1993) 1234.

- 12) T.Abe, K.Kikuchi, S.Shirai, and S.Muraoka : *Semiconductor Silicon 1981*, eds. H.R.Huff, et al., (Electrochem. Soc., Pennington 1981) p.54.

- 13) H.Harada, T.Abe, and J.Chikawa : *Secmicondutor Silicon 1986*, eds. H.R.Huff et al. (Electrochem. Soc., Pennington 1986) p.76.

- 14) T.Abe, H.Harada, and J.Chikawa : *Defects in Semiconductors*, eds. J.W.Corbett et al, Mater. Res. Soc. Symp. Proc. Vol. 14 (Elsevier, NY, 1983) p.1.

- 15) T.Abe, and M.Kimura : *Semiconductor Silicon 1990*, eds. H.R.Huff et al. (Electrochem. Soc., Pennington 1990) p.105.

- 16) P.J.Roksnoer and M.M.B.Van Den Boom : *J. Cryst. Growth* 53, (1981) 563.

ORIGINS AND REDUCTION OF DISLOCATIONS IN

SEMICONDUCTING CRYSTALS

S. Mahajan

Department of Materials Science and Engineering

Carnegie Mellon University

Pittsburgh, PA 15213-3890

ABSTRACT

The supersaturation of point defects occurs in the melt-grown crystals during the cool down. To reduce the supersaturation, the point defects cluster together to form embryonic dislocation sources. In the presence of thermal gradient-induced stresses, these dislocations multiply. Thus, the perfection of the crystal is impaired.

Two approaches have been used to reduce the density of dislocations. First, by binding the point defects with some impurities so that they cannot cluster together to form dislocation sources. Both electronic and size interactions between the point defects and the impurities may be important for this purpose. Second, to strengthen the crystals by the addition of suitable impurities so that the probability of thermal gradient-induced slip is reduced. Examples of the two approaches will be presented.

## 1. INTRODUCTION

That dislocations have deleterious effects on the performance and reliability of the minority carrier devices, such as solar cells, light emitters, photoelectrons, etc., is well documented. Ishida and Kamejima (1979) have shown that dark line defects observed in the degraded regions of GaAlAs/GaAs double heterostructure laser diodes originate from existing dislocations. Dutt et al. (1981) have demonstrated that dislocations and stacking faults in GaAlAs layers, grown on poorly prepared GaAs surfaces, have a marked effect on the performance of light emitting devices.

Meier et al. (1985) have examined the influence of dislocations on the minority carrier diffusion length and the efficiency of silicon solar cells. They have seen that the increase in the density of dislocations lowers the minority carrier diffusion length. This decrease is in turn reflected in the reduced efficiency of the solar cells.

Beam et al. (1990) have shown that during homoepitaxy all the substrate dislocations intersecting the surface are replicated into an epitaxial layer. This observation implies that substrates having low dislocation densities are essential for the growth of high quality epitaxial layers.

It is clear from the above discussion that substrates with low dislocation density are required for reliable minority carrier devices. To achieve this objective, an understanding of the origins of dislocations in as-grown crystals is essential. Then, some schemes must be designed to reduce the density of dislocations. These topics are briefly covered in the present paper.

## 2. ORIGINS OF DISLOCATIONS IN CRYSTALS GROWN FROM THE MELT

The introduction of dislocations during the seeded growth from the melt could result from three different sources. First, dislocations present in seed crystals could propagate into a growing crystals. Second, the supersaturation of point defects could occur during cool down. This supersaturation could be reduced by the clustering of point defects into dislocation loops. Third, dislocation loops in the growing crystal could multiply under the influence of thermal gradient-induced stresses. Since it is possible to grow using dislocated seeds crystals having high perfection, the seed quality does not appear to influence the quality of as-grown crystals (Mahajan et al. 1981). In addition, the incorporation of a necking procedure during growth can also reduce the effects of the seed quality.

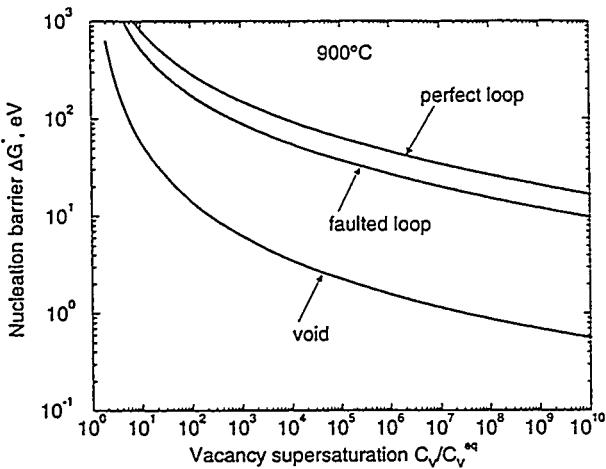

During growth, the non-equilibrium concentrations of point defects are incorporated into the crystals. The free energies of the crystals, crystallizing in the diamond cubic and zinc-blende structures, can be lowered if the excess point defects cluster into embryonic faulted loops on {111} planes. These loops grow by the absorption of either interstitials or vacancies. When the loops reach a critical size, they undergo unfaulting, resulting in perfect dislocation loops. Such loops have been seen in float zone silicon crystals (Föll and Kolbesen 1975, Petroff and de Kock 1975, 1976).

The nucleation of the faulted loops occurs preferentially on dopant atoms and their clusters because of the strain energy considerations.

## 2. ORIGINS OF DISLOCATIONS IN CRYSTALS GROWN FROM THE MELT

The introduction of dislocations during the seeded growth from the melt could result from three different sources. First, dislocations present in seed crystals could propagate into a growing crystals. Second, the supersaturation of point defects could occur during cool down. This supersaturation could be reduced by the clustering of point defects into dislocation loops. Third, dislocation loops in the growing crystal could multiply under the influence of thermal gradient-induced stresses. Since it is possible to grow using dislocated seeds crystals having high perfection, the seed quality does not appear to influence the quality of as-grown crystals (Mahajan et al. 1981). In addition, the incorporation of a necking procedure during growth can also reduce the effects of the seed quality.

During growth, the non-equilibrium concentrations of point defects are incorporated into the crystals. The free energies of the crystals, crystallizing in the diamond cubic and zinc-blende structures, can be lowered if the excess point defects cluster into embryonic faulted loops on {111} planes. These loops grow by the absorption of either interstitials or vacancies. When the loops reach a critical size, they undergo unfaulting, resulting in perfect dislocation loops. Such loops have been seen in float zone silicon crystals (Föll and Kolbesen 1975, Petroff and de Kock 1975, 1976).

The nucleation of the faulted loops occurs preferentially on dopant atoms and their clusters because of the strain energy considerations.

Therefore, the distribution of the loops would tend to follow that of the dopant atoms, i.e., impurity striations. This effect is illustrated in Fig. 1 that shows the distribution of loops in a longitudinal section of a dislocation-free float zone silicon crystal as revealed by x-ray topography (de Kock 1980).

Fig. 1. X-ray topograph of a longitudinal section of a dislocation-free float zone silicon crystal revealing lithium-decorated A swirl defects.

To form faulted loops, two {111} layers of either interstitials or vacancies must be added to the crystal. The situation is a bit more complicated in the case of the III-V crystals. In this case, one of the layers contains group III defect species, whereas group V defect species reside in the second layer.

If thermal gradient-induced stresses are low, the critical resolved shear stress of the crystal may not be exceeded during the cool down. Its ramification is that the crystal will only contain dislocation loops discussed above. As a result, it will be of high quality and will be macroscopically dislocation-free. However, if the critical resolved shear stress is exceeded, then the loops can act as dislocation sources, multiplication occurs by glide

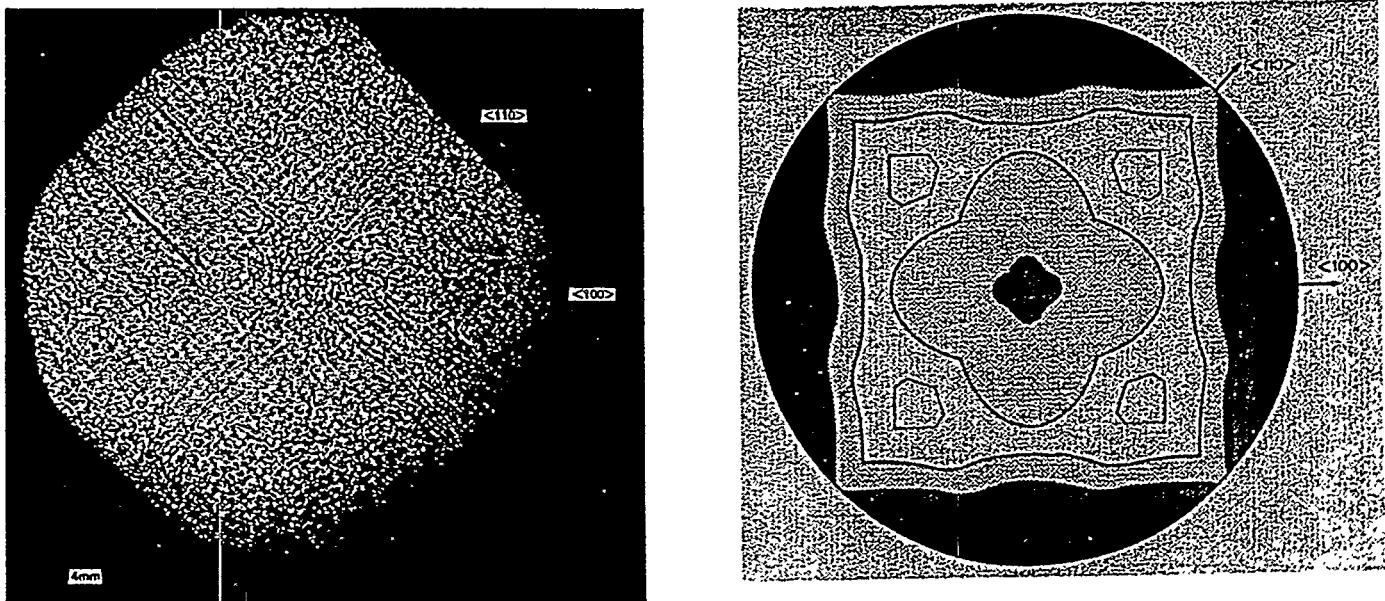

and the dislocation density increases. Since slip occurs on  $\{111\}$  planes of the diamond cubic and zinc-blende structures, the etch pits due glide-induced dislocations are aligned along specific crystallographic directions on a given plane. This effect is illustrated in Fig. 2 that shows the alignment of etch pits along the  $[110]$  direction of a (001) InP wafer that is highly dislocated (Mahajan 1989).

Fig. 2. Typical dislocation etch pit distribution observed on a (001) slice of highly dislocated S-doped InP wafer. Marker represents 0.1mm.

The thermal gradient-induced stresses are the major source of dislocations in II-VI and III-V crystals because they are softer materials. This is elegantly demonstrated in the study of Jordan et al. (1980). In Fig. 3 (left), a photomicrograph obtained from a  $\{001\}$  tellurium-doped GaAs wafer is shown. The key features of the observed dislocation distribution are: (i) its

four fold symmetry, (ii) maximum density at the  $\langle 100 \rangle$  edges, (iii) minimum density midway between the center and  $\langle 110 \rangle$  edge, and (iv) intermediate densities at the center and the  $\langle 110 \rangle$  edges. Jordan et al. (1980) have rationalized the results of Fig. 3 (left) in terms of slip caused by thermal gradient induced stresses. The computed dislocation density contour lines are shown in Fig. 3 (right). It is remarkable that their analysis can predict the salient features of the observed dislocation distribution.

Fig. 3. (left) Photomacrograph obtained from a KOH etched  $\{100\}$  GaAs wafer. The crystal was cut close to the top end of a Te-doped boule grown by the liquid encapsulated Czochralski technique. (right) Constant dislocation density contour lines for the top wafer were obtained from a boule grown along the  $\langle 100 \rangle$  direction.

### 3. REDUCTION OF DISLOCATION DENSITIES

Two approaches have been used to produce crystals with lower dislocation densities. In one of the schemes, point defects are prevented from clustering by binding them with suitable impurities so that embryonic dislocation sources do not form. In the second approach, crystals are strengthened by the addition of suitable impurities. This reduces the probability of thermal gradient-induced slip.

de Kock et al. (1979) have investigated the influence of different dopants on the formation of microdefects, i.e., embryonic dislocation sources, in macroscopically dislocation-free Czocharski silicon crystals. The density of the microdefects is reduced for certain dopants. These results can only be understood if it is invoked that there is binding between the point defects and the dopant atoms. The interaction appears to be electronic in nature and does not depend on the size of the dopant atom.

The efficacy of zinc in reducing the dislocation density in InP crystals is considerably higher than that in the case of GaAs. Tucker and Hooper (1975) have suggested that the zinc atoms form complexes with the vacancies and thus prevent them from clustering into microdefects. On the other hand, the complexes may not develop in GaAs, leading to dislocation sources that can multiply under the influence of thermal gradient-induced stresses. It can also be argued that the above results cannot be explained on the basis of the size differentials between the dopant and host lattice atoms.

The above results imply that point defect-dopant interactions are electronic in nature. Therefore, to select suitable impurities for controlling the dislocation density, information on the electronic properties of the point defects in the host lattice is important.

A number of workers have shown that the perfection of InP crystals, grown by the liquid encapsulated Czochralski technique can be substantially improved by heavy doping (Seki et al. 1976, 1978 and Cockayne et al. 1983). High doping could affect the density of dislocations in two ways. First as discussed previously, the impurities could interact with the point defects and thus prevent them from clustering into potential dislocation sources. Second, hardening of the lattice by the impurities reduces the probability of introducing dislocations by thermal-gradient-induced stresses. Ehrenreich and Hirth (1985) visualize that when some of the Ga atoms on the group III sublattice in GaAs are replaced by In, five-atom  $\text{InAs}_4$  tetrahedral units are produced within the matrix. The volume of the  $\text{InAs}_4$  unit is larger than that of the  $\text{GaAs}_4$  unit because the In-As bond is longer than the Ga-As bond. The strain field associated with the  $\text{InAs}_4$  unit interacts strongly with glide dislocations, leading to strengthening of the GaAs lattice by the addition of In. Ehrenreich and Hirth believe that this solid solution strengthening is responsible for the reduction of dislocation density observed in LEC grown In-substituted GaAs. Extending the Ehrenreich-Hirth approach to S- and Te-doped InP and neglecting the charge transfer-induced size effects, it can be argued that Te should be more potent than S in reducing the dislocation

density. This assessment is not borne out by the experimental observations (Seki et al. 1976, 1978). It is reckoned that in the case of the isoelectronic impurities, the size differentials between the impurities and the host lattice atoms may be responsible for reducing the dislocation density, whereas the point defect-impurity interactions along with the size effects could improve the crystal perfection in the case of electrically active impurities.

In summary there are two sources for the introduction of dislocations in as-grown semiconductor crystals: (i) point defects, and (ii) thermal gradient-induced stresses. The influence of the stresses can be reduced substantially by the addition of suitable impurities to the crystals. These impurities either bind the point defects and prevent them from clustering into embryonic dislocation sources or strengthen the lattice by introducing strain centers in the host lattices.

The support of the above work by the Ebara Corporation is gratefully acknowledged.

#### REFERENCES

Beam, E.A. III, Mahajan, S. and Bonner, W.A. *Mats Sci. Eng.* B7, 83 (1990).

Cockayne, B., Brown, G.T., and MacEwan, W.R., *J. Crystal Growth* 64, 48 (1983).

de Kock, A.J.R., *Handbook of Semiconductors*, Vol. 3, edited by S.P. Keller, North Holland, N.Y. p. 247 (1980).

de Kock, A.J.R., Stacy, W.T., and van de Wijgert, W.M., *Appl. Phys. Lett.* 34, 611 (1979).

Dutt, B.V., Mahajan, S., Roedel, R.J., Schwartz, G.P., Miller, D.C. and Derick, L., *J. Electrochm. Soc.* 128, 1573 (1981).

Ehrenreich, H. and Hirth, J.P., *Appl. Phys. Lett.* 46, 668 (1985).

Föll, H., and Kolbesen, B.O., *Appl. Phys.* 8, 319 (1975).

Ishida, K., and Kamejima, T., *J. Electron Mater.* 8, 57 (1979).

Jordan, A.S., Caruso, R., and von Neida, A.R., *Bell System Tech. J.*, 59, 593 (1980).

Mahajan, S., *Prog. Mats. Sci.* 33, 1 (1989).

Meier, D.L., Greggi, J. Rohatgi, A., O'Keefe, T.W., Rai-Chundhury, P., Campbell, R.B., and Mahajan, S., *Proc. of the 18th IEE Photovoltaic Specialists Conf.* p. 596 (1985).

Petroff, P.M., and de kock, A.J.R., *J. Cryst. Growth* 30, 117 (1975).

Petroff, P.M., and de Kock, A.J.R., *J. Cryst. Growth* 35, 4 (1976).

Seki, Y., Matsui, J., and Watanabe, H., *J. Appl. Phys.* 47, 3374 (1976).

Seki, Y., Watanabe, H., and Matsui, H., *J. Appl. Phys.* 49, 822 (1978).

Tuck, B., and Hooper, A., *J. Phys. D* 8, 1806 (1975).

# The Role of Dislocations and Associated Defects in Determining Minority Carrier Lifetime

Lionel C. Kimerling

Department of Materials Science and Engineering

Massachusetts Institute of Technology

Cambridge, MA 02139

The electrical activity of dislocations as recombination centers is manifested in three primary ways: 1) the intrinsic activity of imperfect bonds on the dislocation line; 2) the activity of point defect debris associated with dislocation glide; and 3) the activity of precipitates and impurity atmospheres in the vicinity of the dislocation line.

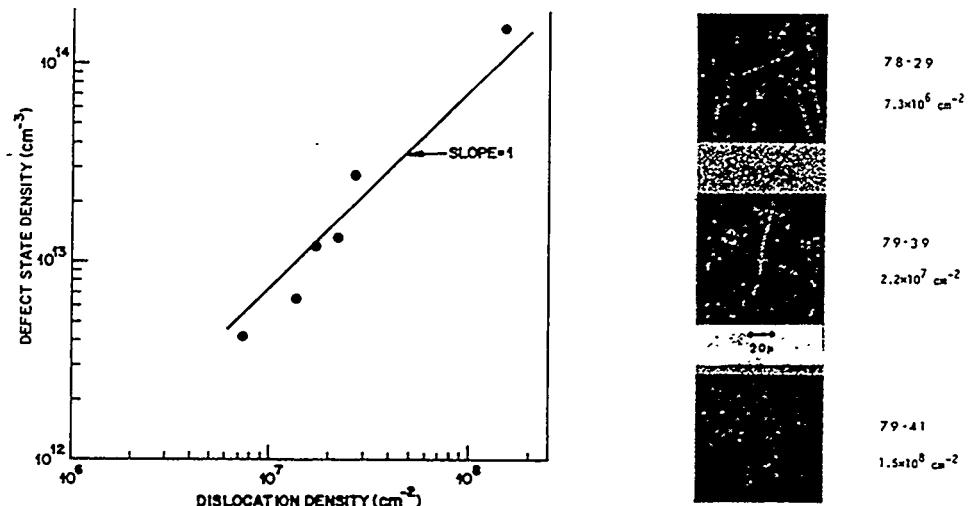

The intrinsic activity of imperfect dislocation bonds depends largely on the kink site density, because the dislocation core dissociates and reconstructs to minimize the density of dangling bonds. For typical silicon materials that have been plastically deformed,  $N_T$  (cm<sup>-3</sup>)  $\sim 10^6 N_d$  (cm<sup>-2</sup>), where  $N_T$  is the density of recombination centers and  $N_d$  is the dislocation density.

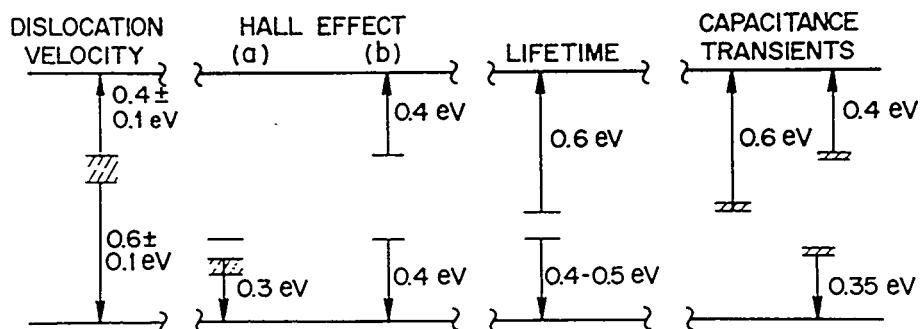

Figure 1 shows the data that enable this conclusion.

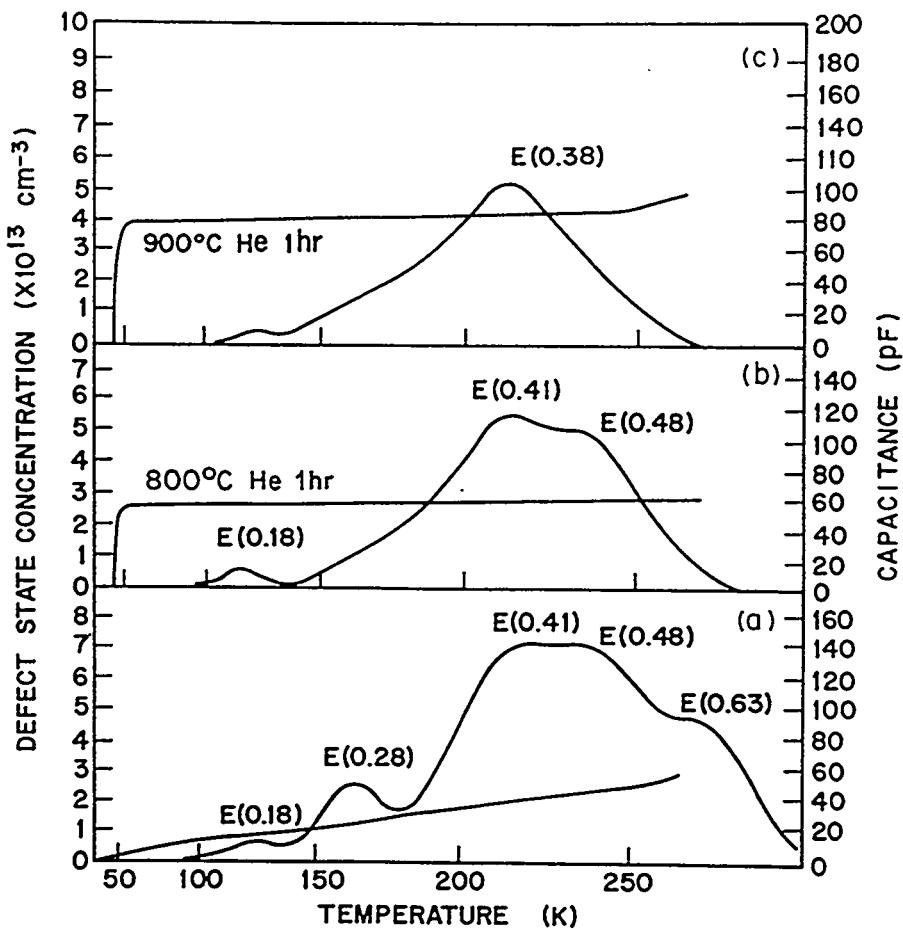

The point defect debris are created by cross slip in concentrations that can be x10 higher than the intrinsic electrical activity. These defects disappear upon annealing at temperatures of 900C or higher. Figure 2 shows evidence of this behavior.

Precipitates act as short circuits in solar cells. Impurity atmospheres enhance the recombination velocity in the dislocation core region. However, dislocations getter metallic impurities from the bulk of the active region. Therefore, dislocations, like grain boundaries, can play a beneficial role when present in controlled numbers. One must engineer the spatial distribution in a way that minimizes the detrimental effect on open circuit voltage.

The energy level structure for intrinsic activity is shown in Figure 3, as observed by several measurement methods. The Fermi level is pinned to produce p-type conduction in heavily dislocated regions.

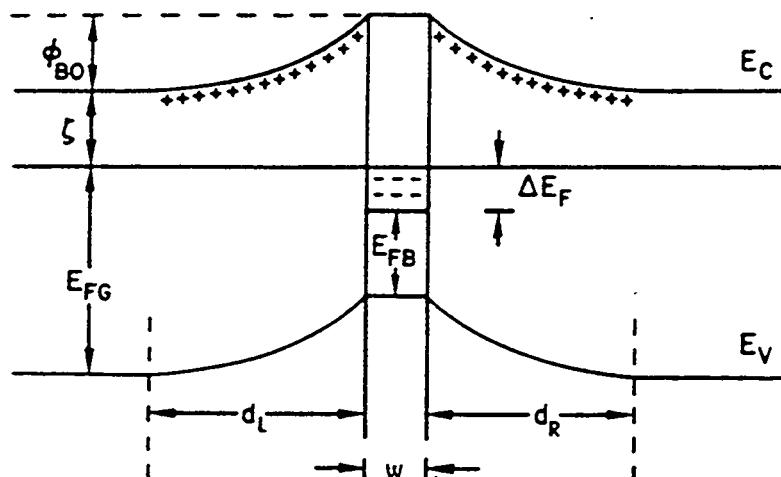

The accumulation of charge in the vicinity of the dislocation core induce band bending as shown in Figure 4. This band bending enhances the capture cross section for minority carriers. It also gives rise to an occupation dependent recombination rate. This, recombination proceeds at a slower rate at high injection levels.

The observations listed above have been reported for SiGe alloys and misfit dislocations produced by heterostructure growth. Hence, they are considered to be generic to dislocations in silicon materials systems.

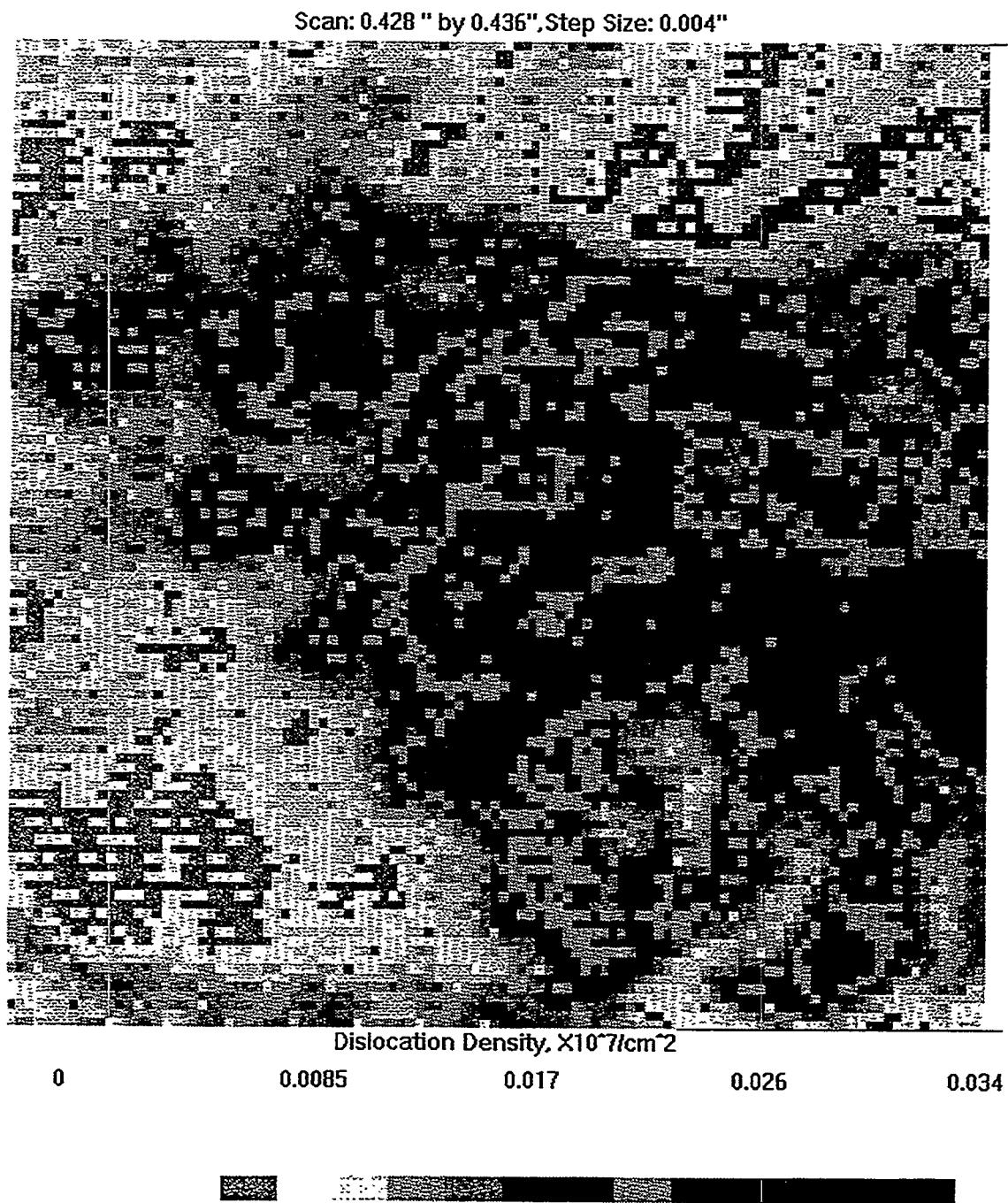

Figure 1 - Defect state concentration as a function of local dislocation density under the Schottky barrier in samples. (EBIC micrographs of samples are also shown).

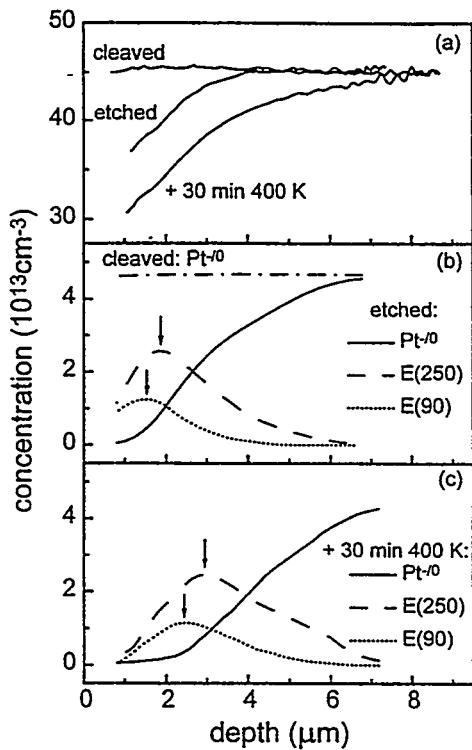

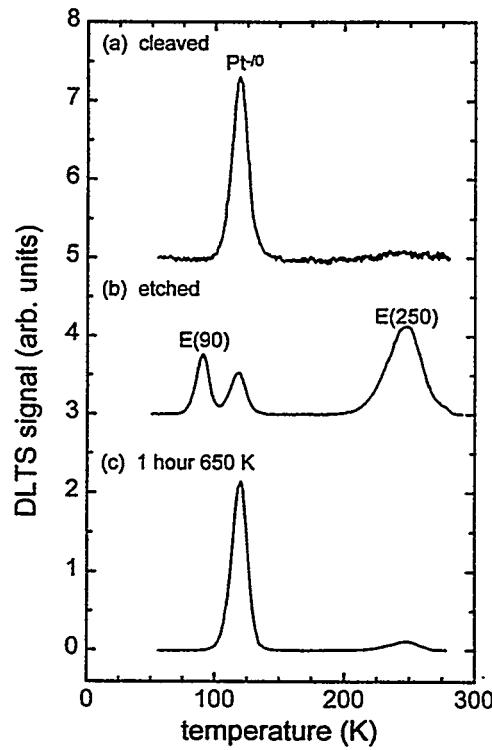

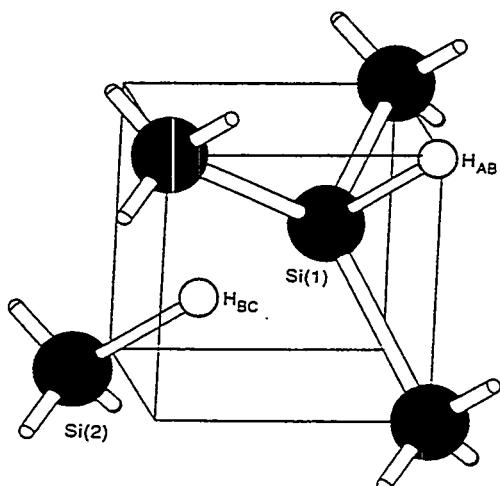

Fig. 2. (a) Defect spectrum produced by deformation at  $T = 770^\circ\text{C}$ ,  $\epsilon = 5\%$ ; annealing at  $700^\circ\text{C}$  1 hr caused little change in the original spectra after deformation. (b) and (c) Stability of the defect spectrum shown after annealing for 1 hr at temperatures shown. The smooth featureless line represents junction capacitance; F.Z. silicon,  $n = 3 \times 10^{15} \text{ cm}^{-3}$ ,  $\tau_t = 6 \text{ ms}$ .

Fig. 3. Schematic comparison of dislocation levels in silicon obtained from a variety of experimental determinations.

Fig. 4. Energy band diagram for two grains and boundary region. Value  $E_{FB}$  is the neutral Fermi level of the boundary before charge transfer from the grains. (From Seager

# Transition metals and lifetime in PV silicon

A.A.Istratov, E.R.Weber.

Department of Materials Science and Mineral Engineering,

University of California at Berkeley,

577 Evans Hall, Berkeley CA 94720-1760, USA

e-mail: [weber@socrates.berkeley.edu](mailto:weber@socrates.berkeley.edu)

## **Introduction.**

One of the most important and critical parameters of photovoltaic (PV) silicon is the diffusion length (lifetime) of minority charge carriers. This parameter determines the effectiveness of solar cells and is significantly lower in PV silicon than in CZ and FZ silicon. In this paper, we discuss the role of precipitates and agglomerates of transition metals in the reduction of lifetime in PV silicon.

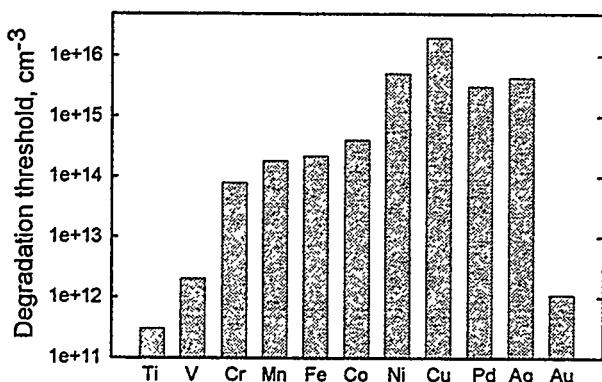

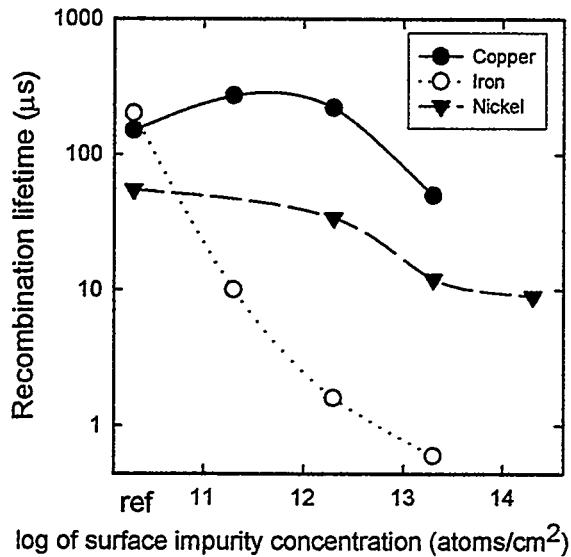

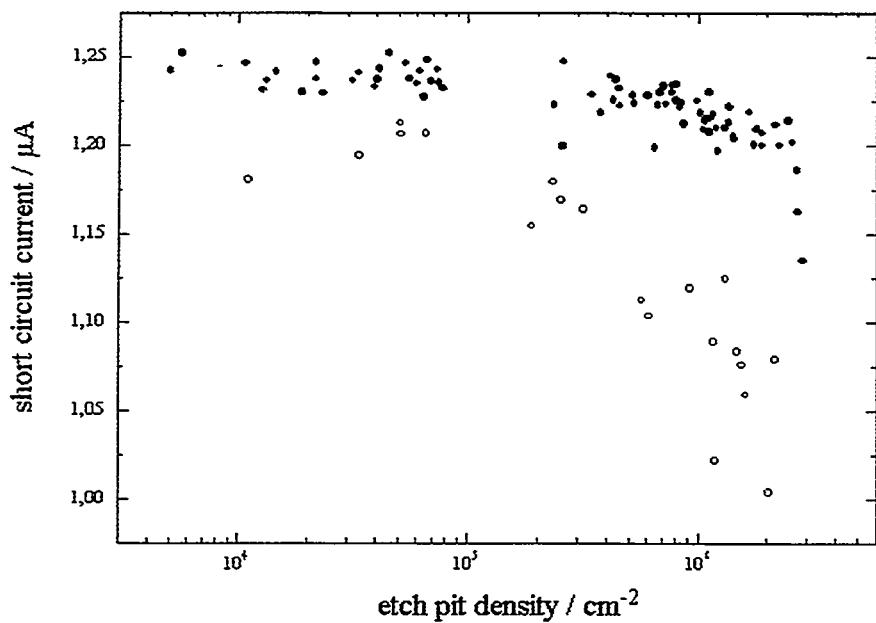

Transition metals form electrically active levels in the bandgap and can act as minority carrier recombination sites, decreasing the lifetime. CZ silicon manufacturers routinely use minority carrier diffusion length measurement (for example, SPV) as indication of the level of contamination by transition metals. The first studies of the effect of transition metals on solar cell efficiency made on CZ silicon, revealed that the critical contamination level, which leads to a substantial decrease in solar cell efficiency, is individual for each metal. The frequently cited results of Hopkins *et al*<sup>1,2</sup> are presented in Fig.1. It is

interesting to note that, according to Ref.1,2, the most critical metals for CZ solar cell performance are Ti, V, Cr and Al, which have a deleterious effect in concentrations  $10^{11}$ - $10^{12}$  cm<sup>-3</sup>. On the contrary, Fe, Co, Ni and Cu, which can be easily incorporated into the volume of the wafer during any heat treatment and are considered the chief metal contaminants in the semiconductor industry are (according to Ref.1,2) tolerable in CZ solar cells in concentrations up to  $10^{14}$ - $10^{16}$  cm<sup>-3</sup>.

Numerous gettering techniques have been developed to decrease the concentration of metals in the critical areas of the wafer. They are based on creation of artificially formed precipitation sites (i.e., oxygen precipitates or dislocations) or regions with

Fig.1. Threshold impurity concentrations for CZ solar cell performance reductions (after Hopkins and Rohatgi<sup>2</sup>)

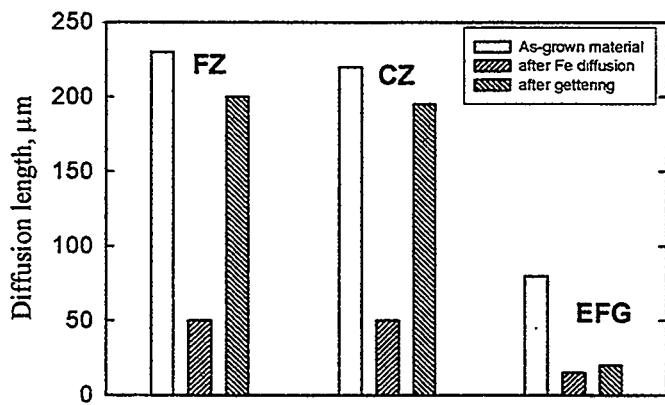

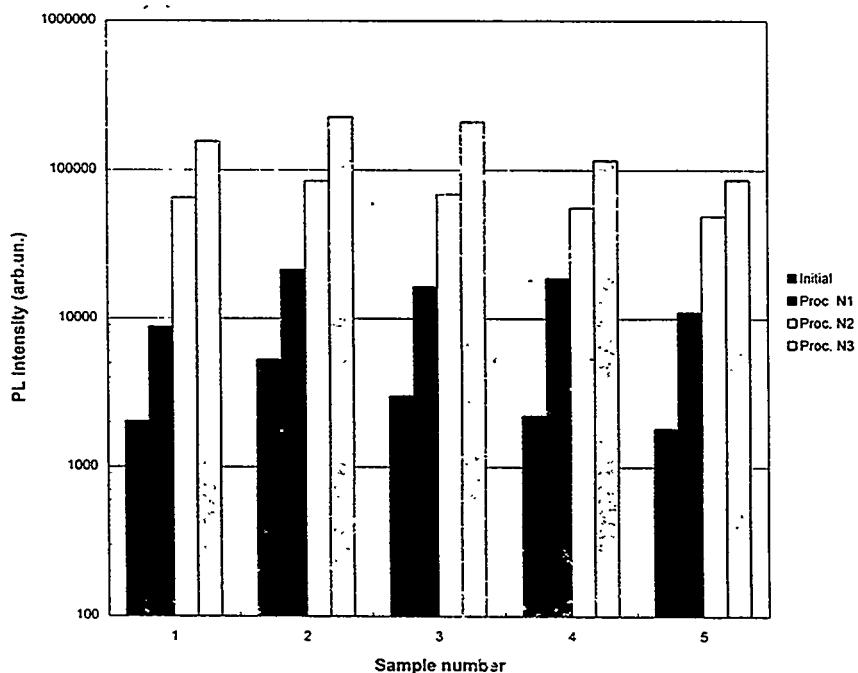

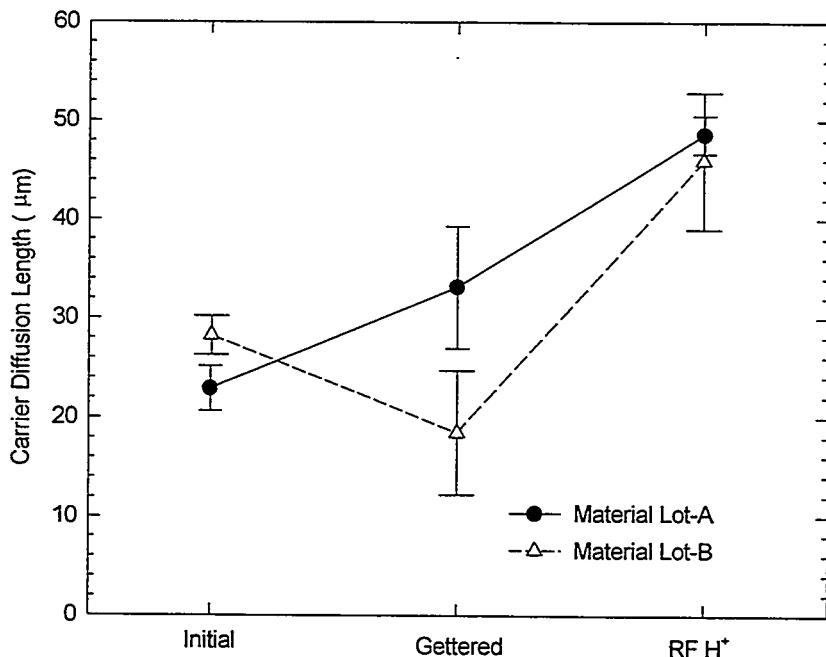

elevated solubility of impurities (backside aluminum layer) in non-critical areas of the wafer. The experiments, made on FZ and CZ material have shown that the diffusion length, drastically decreased after intentional iron contamination, could be restored by a gettering procedure (Fig.2, FZ,CZ). This means that the interstitially dissolved metals could be gettered almost completely. However, the same gettering procedure was found much less efficient on low-cost PV material (Fig.2, EFG).

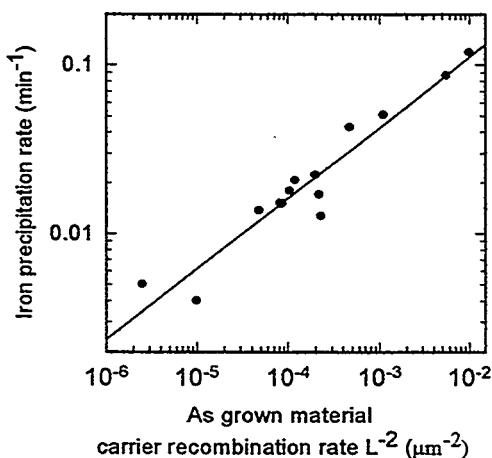

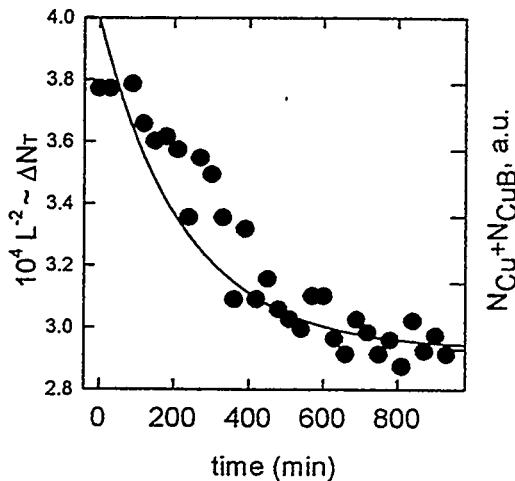

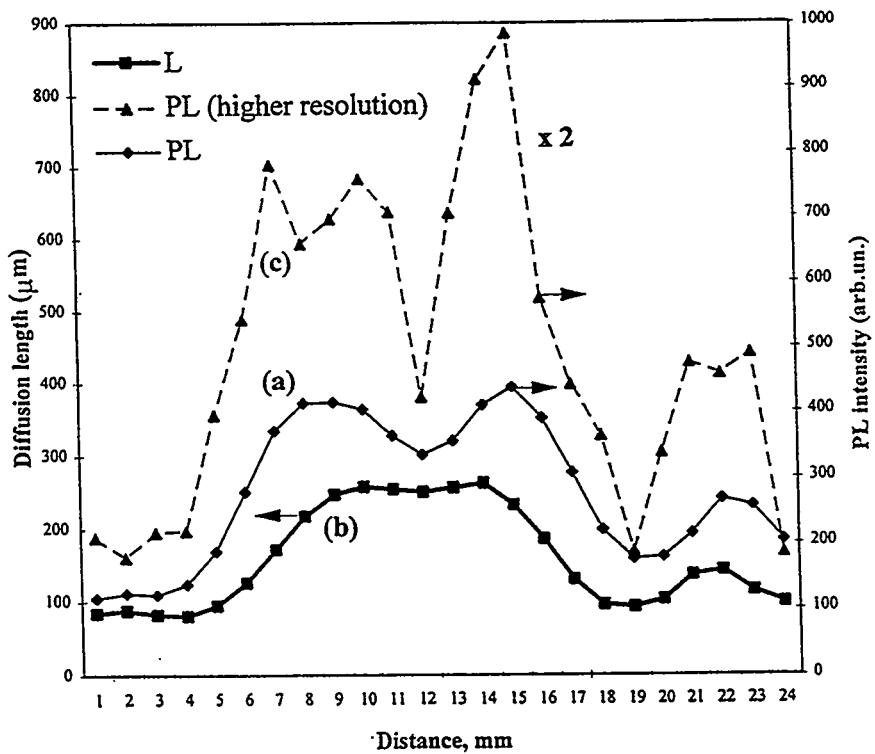

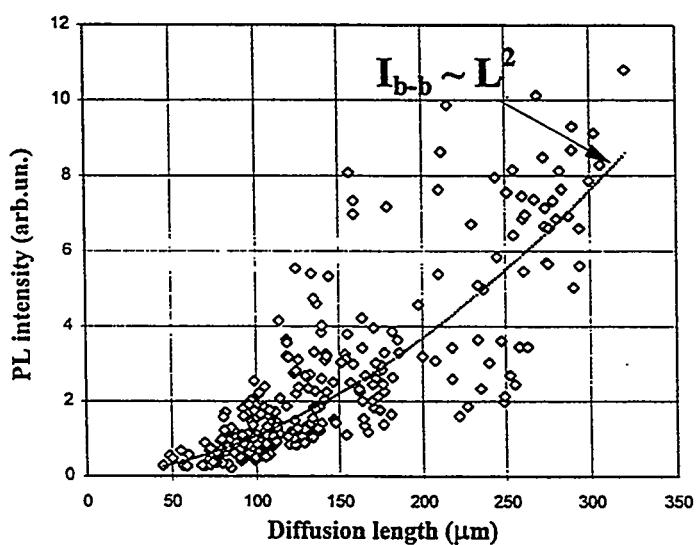

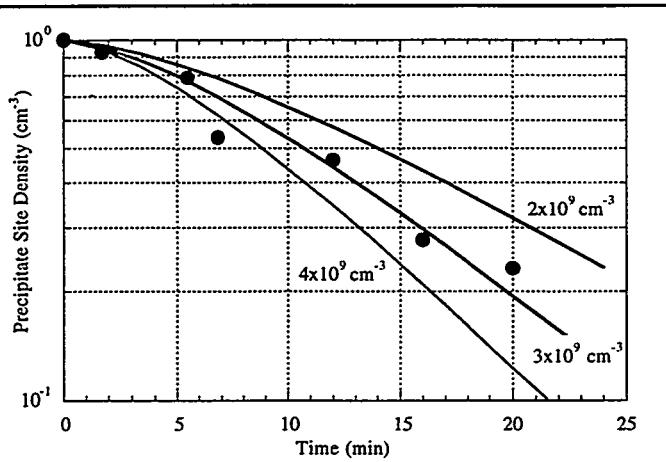

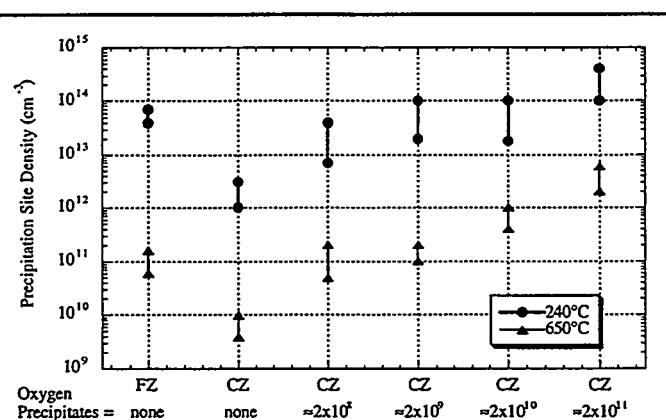

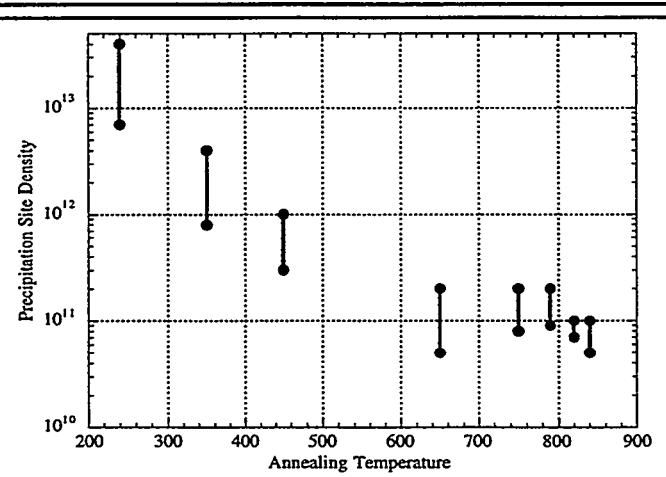

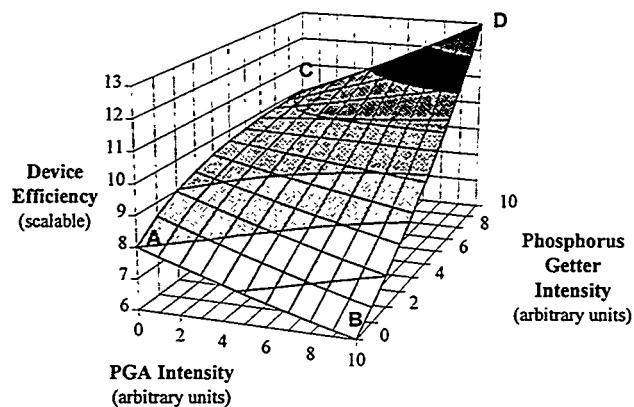

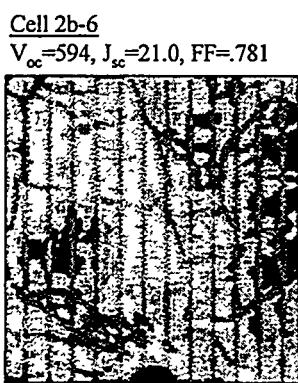

Gettering by precipitation can be analyzed by measuring the precipitation rate, as demonstrated by Gilles<sup>3,4</sup>. The determination of the density of precipitation sites from iron precipitation kinetics is based on Ham's law<sup>5,6</sup>, from which it follows that the precipitation rate is proportional to the density of precipitation sites. Using this approach for various silicon solar cell materials (including FZ, CZ, MCZ, EFG, SOPLIN)<sup>7,8,9,10</sup>, it was revealed that the precipitation rate of iron was proportional to the as-grown minority

Fig.2. Dependence of minority carrier diffusion length in as-grown sample, after iron diffusion and after phosphorus-diffusion gettering for three types of material: float zone (FZ), Chochralski-grown (CZ) and edge-defined film-fed grown silicon for solar cells (Ref.8).

carrier lifetime and inversely proportional to the square of the diffusion length (Fig.3). In other words, in materials with low initial diffusion length iron precipitated very quickly, indicating that the materials with a low lifetime contained a higher concentration of precipitation sites<sup>7,8,9,10</sup>.

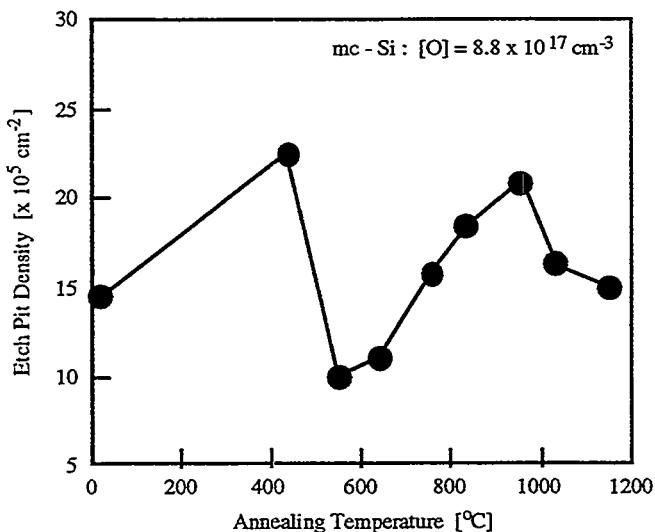

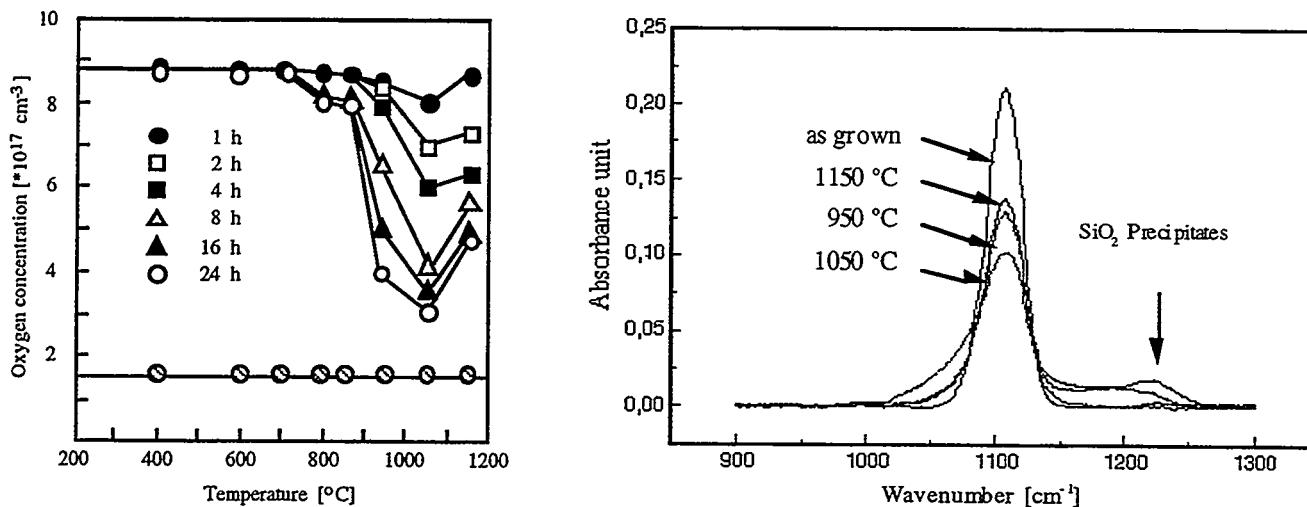

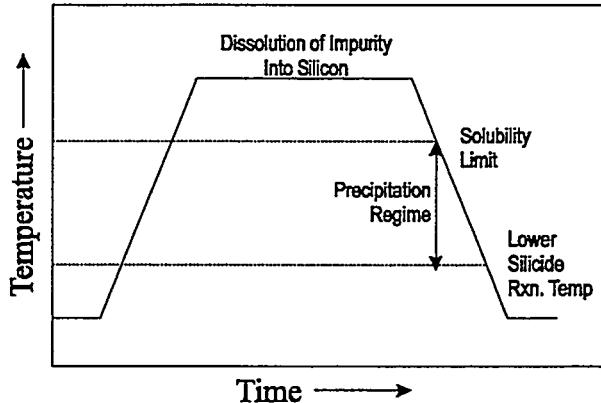

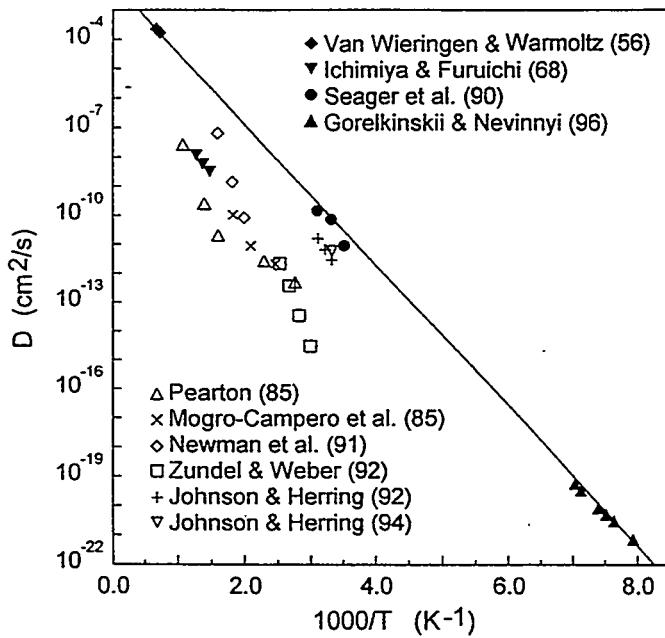

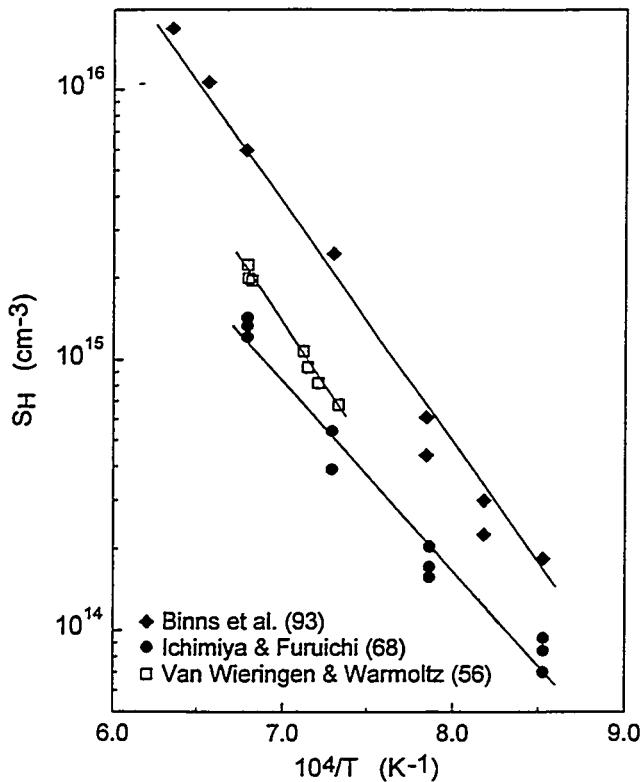

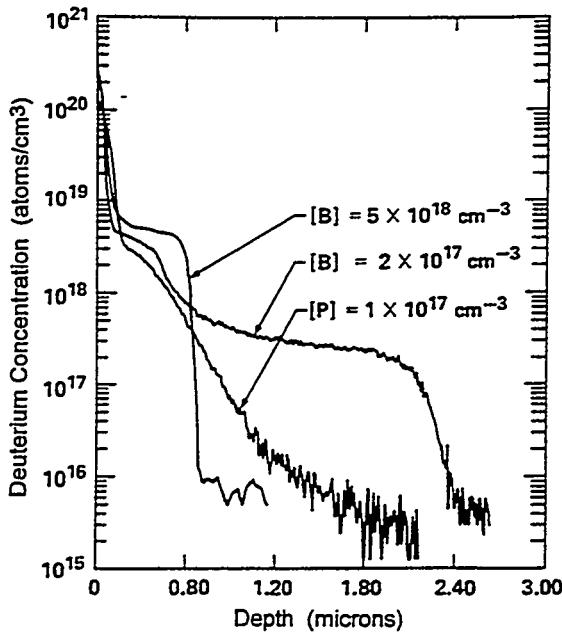

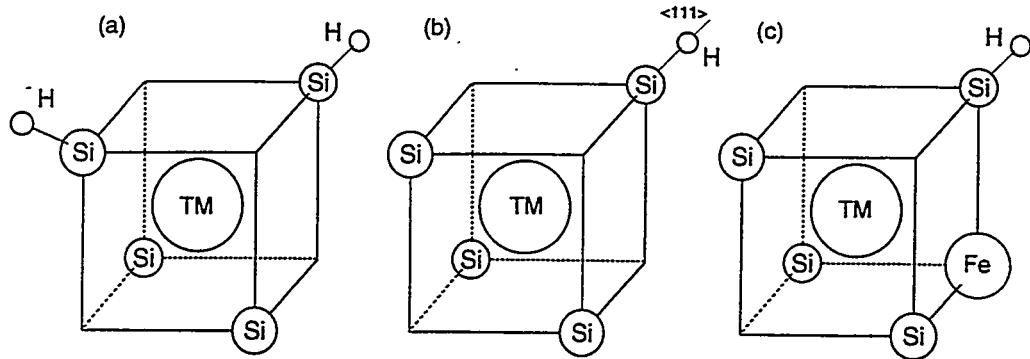

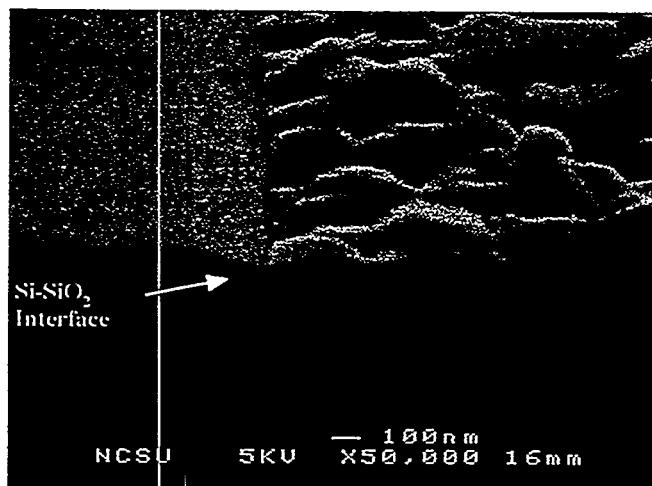

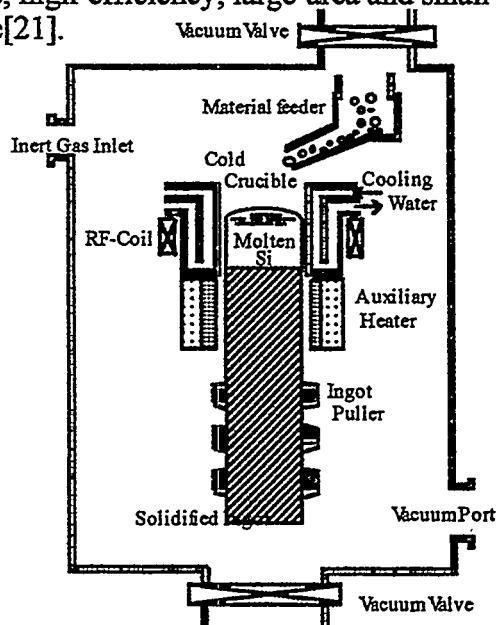

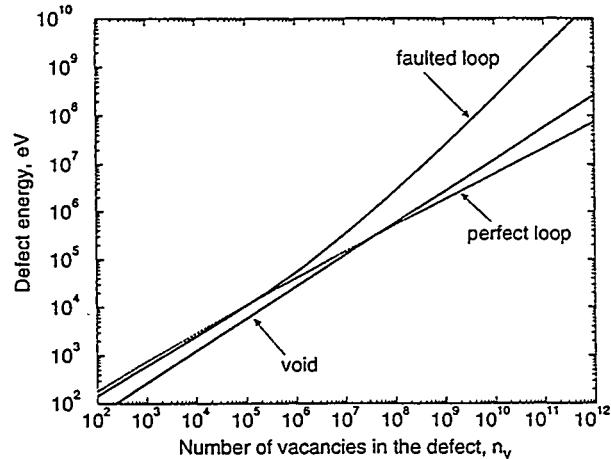

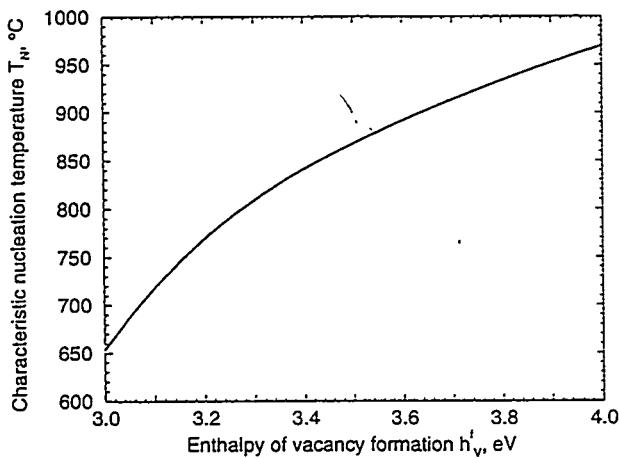

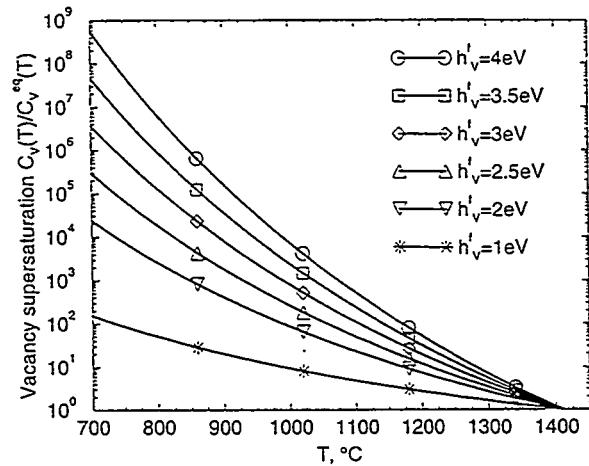

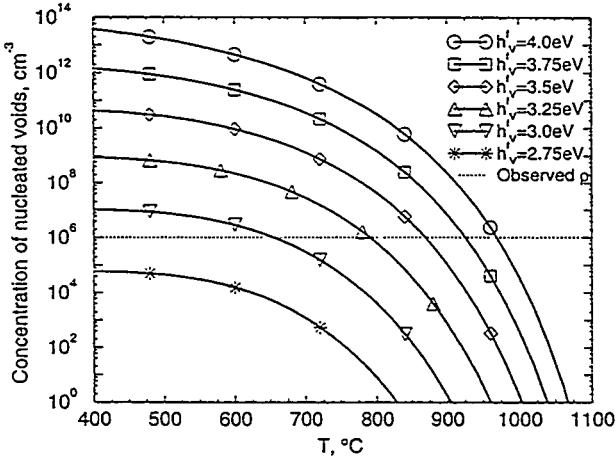

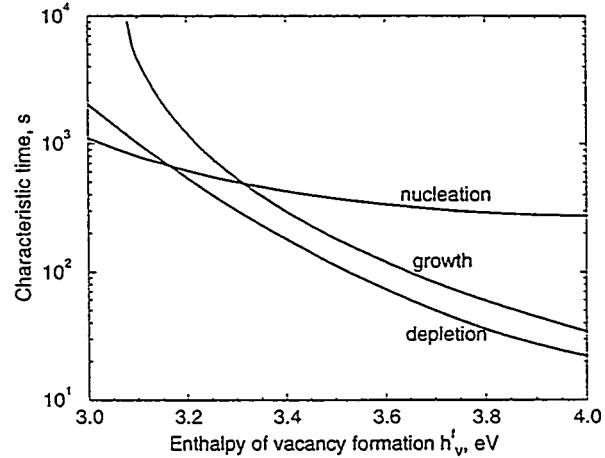

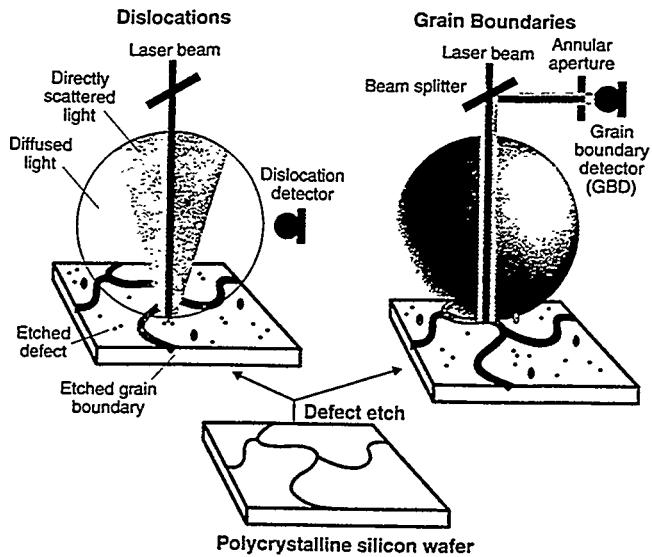

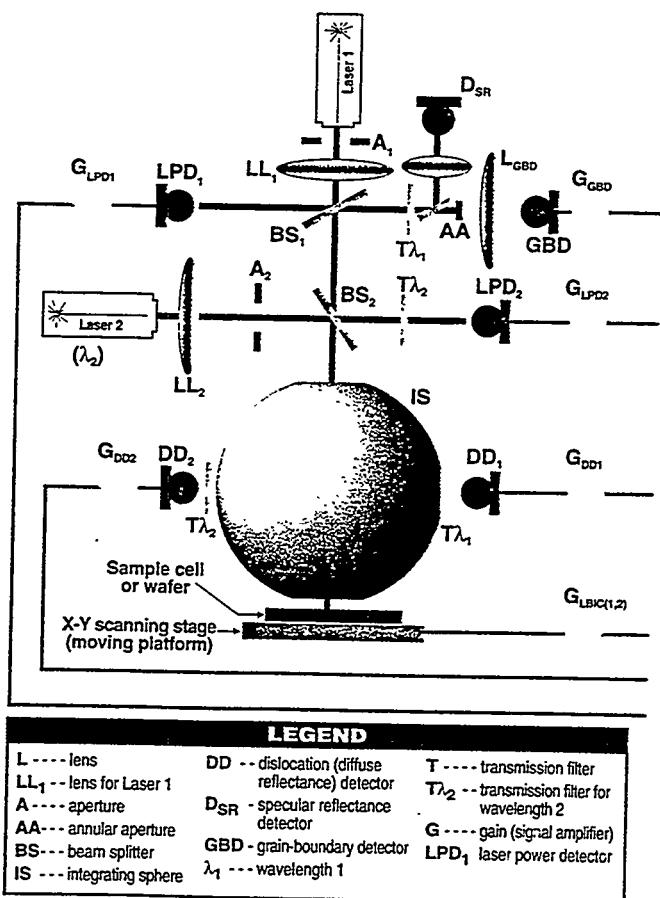

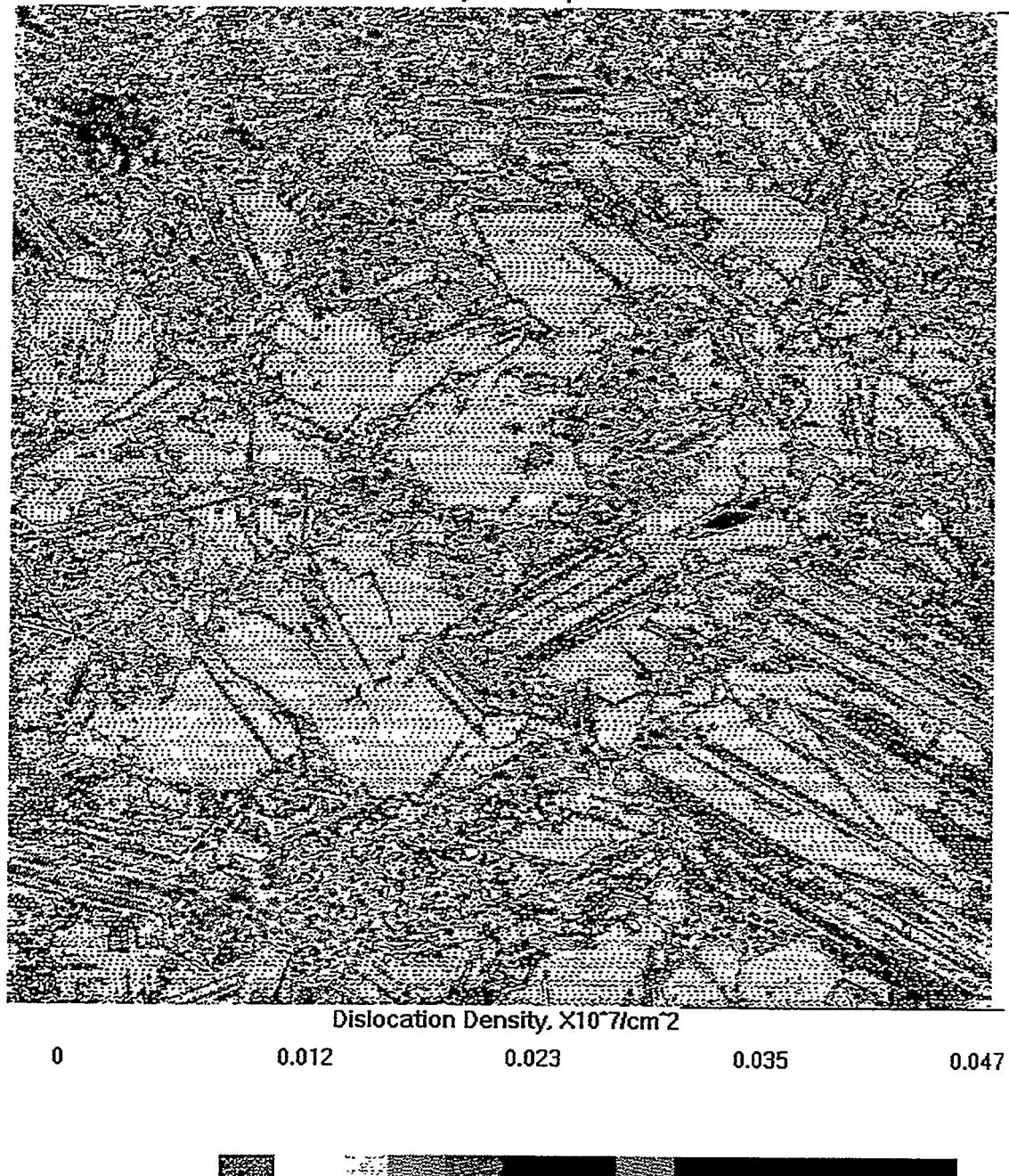

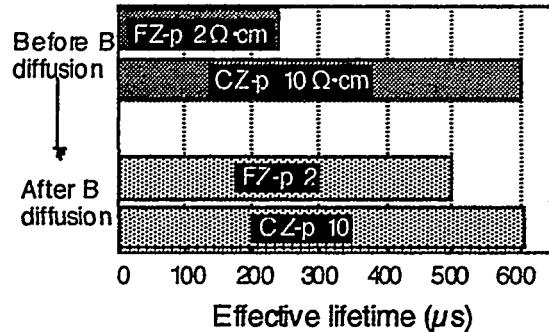

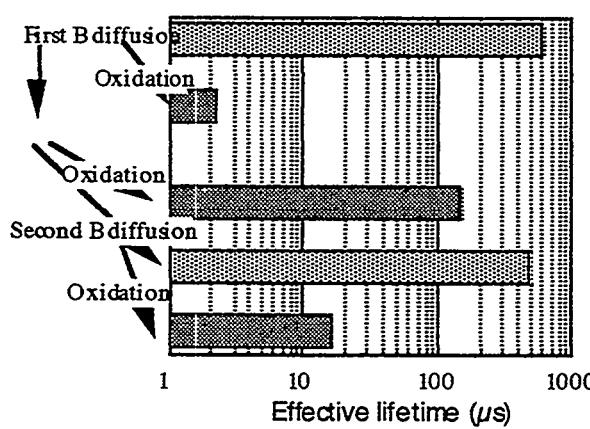

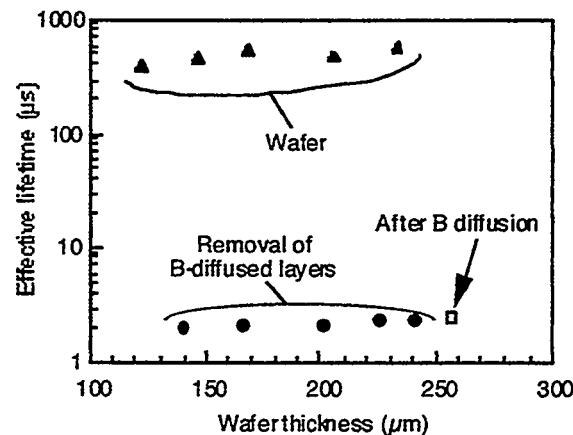

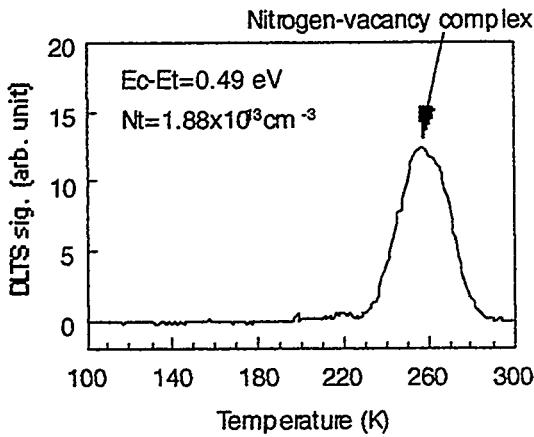

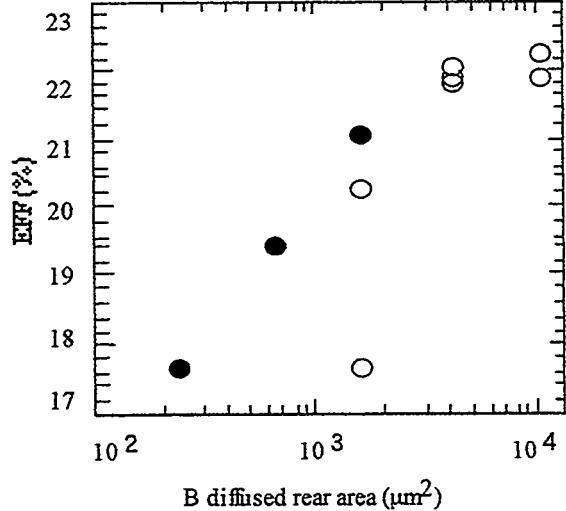

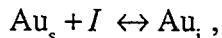

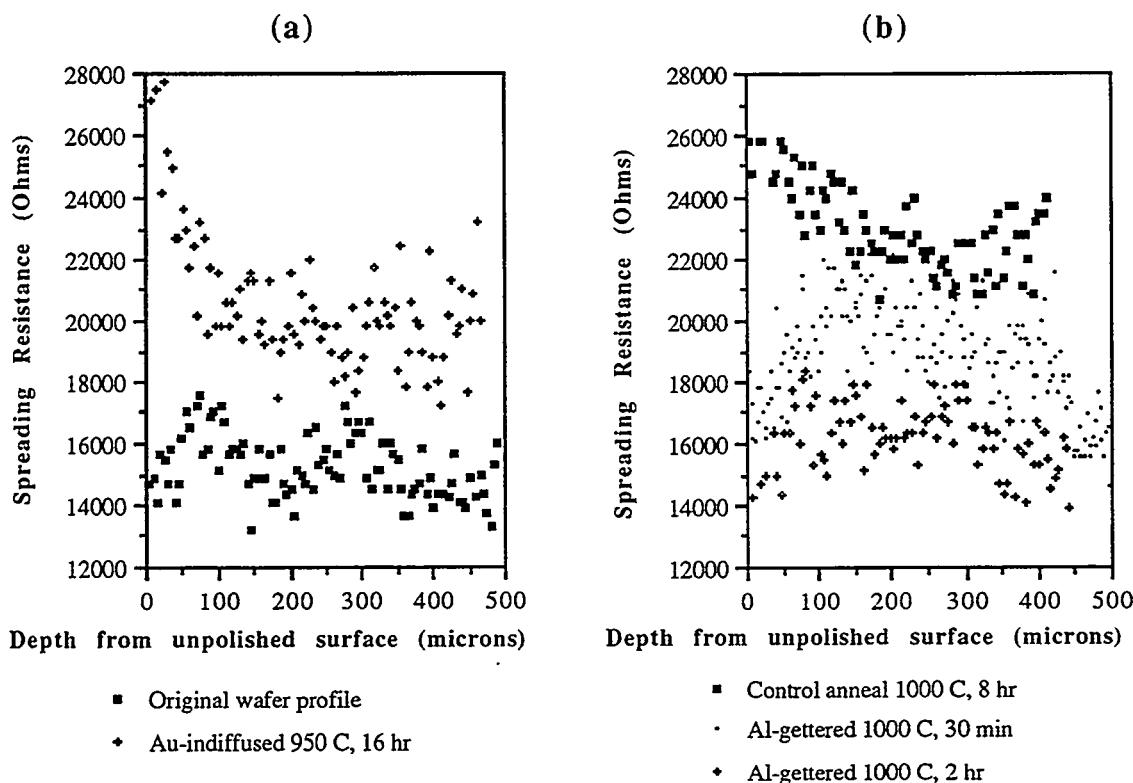

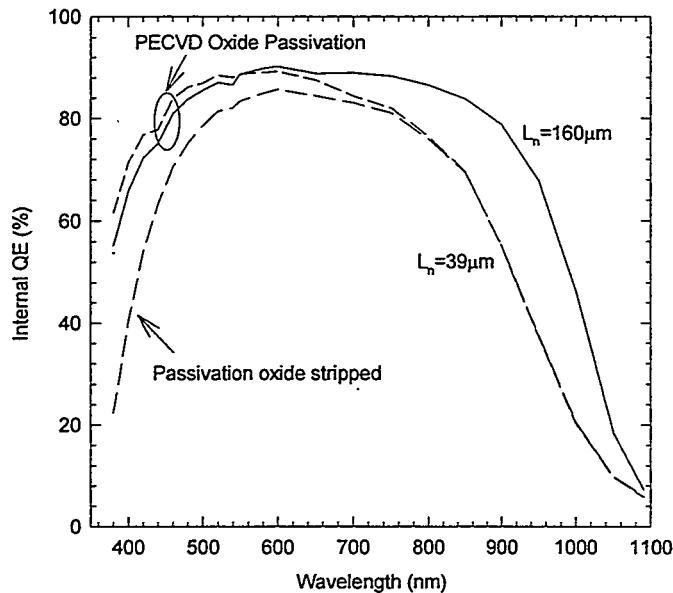

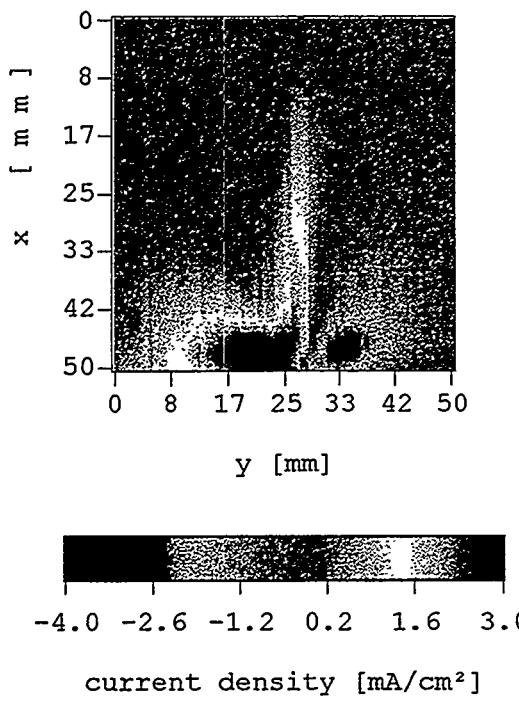

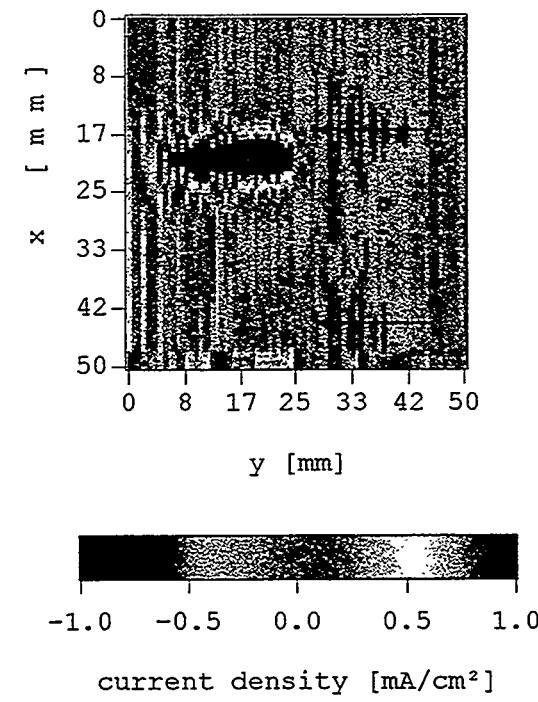

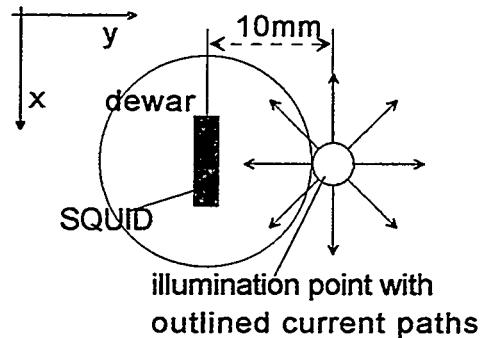

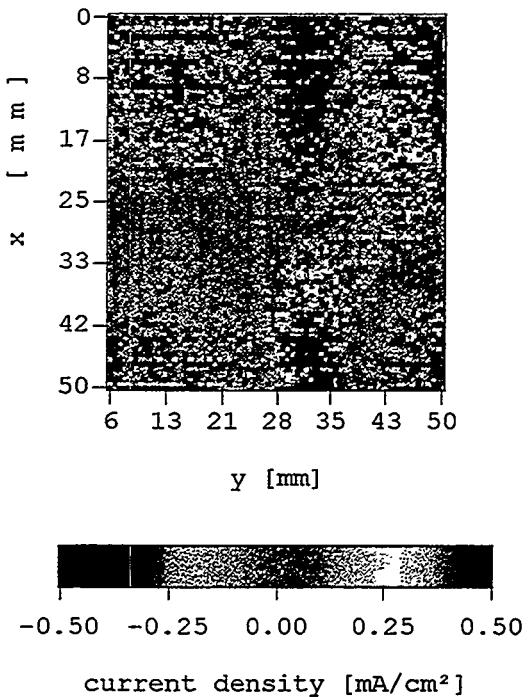

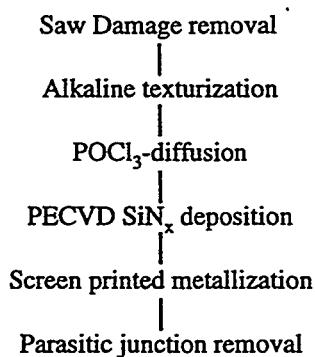

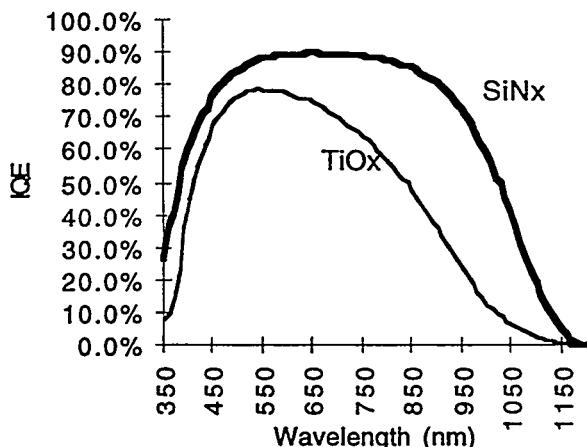

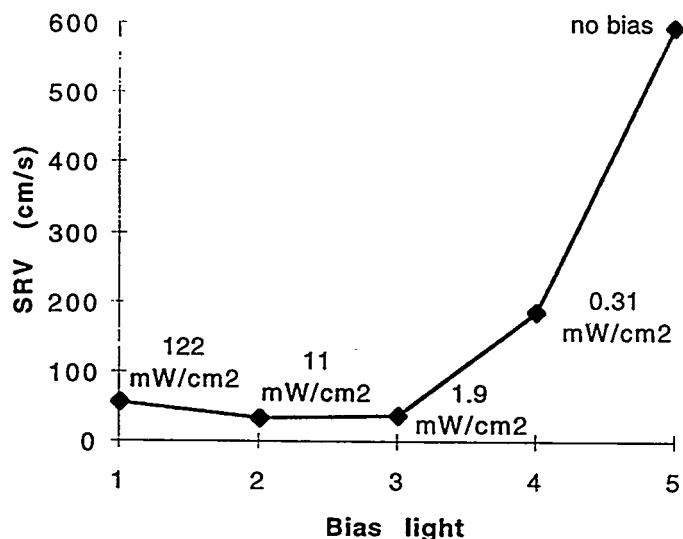

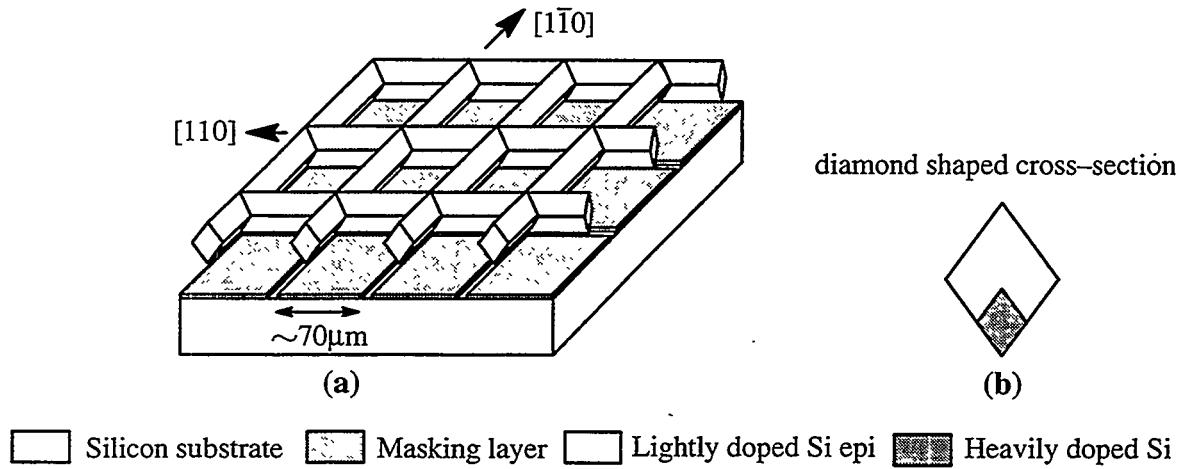

Structural investigations of grains with low diffusion length revealed that they contained high densities of dislocations and intragranular defects. The nature of the latter type of defect is still being investigated. In a recent paper by M. Werner<sup>11</sup> several types of microdefects were reported. In particular, she reported spherical particles and planar defects lying in {111} planes. The size of the defects was below 100 nm. They might contain (or even consist of) precipitated transition metals. The last premise is confirmed by spatially resolved X-ray fluorescence data<sup>12,11</sup>, which indicated that the grains of as-grown multicrystalline silicon with low initial diffusion lengths and high density of precipitation sites contained agglomerations of Fe, Cr and Co in significant concentrations (Cu concentration could not be measured since the sensitivity of the setup to copper was too low). Agglomerates of metals were found both on dislocations and in virtually dislocation-free regions<sup>12</sup>.