SAND--91-0434C

DE92 000981

## ABSTRACT

A series of controlled experiments has been performed in Sandia's Photovoltaic Device Fabrication Laboratory to evaluate the effect of various chemical surface treatments on the recombination lifetime of crystalline silicon wafers subjected to a high-temperature dry oxidation. From this series of experiments we have deduced a relatively simple yet effective cleaning sequence. We have also evaluated the effect of different chemical damage-removal etches for improving the recombination lifetime and surface smoothness of mechanically lapped wafers. This paper presents the methodology used, the experimental results obtained, and our experience with using this process on a continuing basis over a period of many months.

## INTRODUCTION

Sandia's Photovoltaic Device Fabrication Laboratory (PDFL) is funded to facilitate the transfer of laboratory-scale advances in silicon cell design and processing to large-scale processing in industry. Consistency in processing is essential to this mission. To accomplish this, we have established baseline processes which are run on a continuing basis to insure that all equipment is functioning properly and is free of contamination.

This paper describes our development and subsequent experience with a baseline process for the cleaning and dry oxidation of silicon wafers. The primary measurable quantity is the carrier lifetime as measured by microwave-detected photoconductance decay [1]. Maintaining carrier lifetime through high-temperature processes like oxidation is the single most important factor in the fabrication of high-performance solar cells, and it is also the

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## DISCLAIMER

## ABSTRACT

A series of controlled experiments has been performed in Sandia's Photovoltaic Device Fabrication Laboratory to evaluate the effect of various chemical surface treatments on the recombination lifetime of crystalline silicon wafers subjected to a high-temperature dry oxidation. From this series of experiments we have deduced a relatively simple yet effective cleaning sequence. We have also evaluated the effect of different chemical damage-removal etches for improving the recombination lifetime and surface smoothness of mechanically lapped wafers. This paper presents the methodology used, the experimental results obtained, and our experience with using this process on a continuing basis over a period of many months.

## INTRODUCTION

Sandia's Photovoltaic Device Fabrication Laboratory (PDFL) is funded to facilitate the transfer of laboratory-scale advances in silicon cell design and processing to large-scale processing in industry. Consistency in processing is essential to this mission. To accomplish this, we have established baseline processes which are run on a continuing basis to insure that all equipment is functioning properly and is free of contamination.

This paper describes our development and subsequent experience with a baseline process for the cleaning and dry oxidation of silicon wafers. The primary measurable quantity is the carrier lifetime as measured by microwave-detected photoconductance decay [1]. Maintaining carrier lifetime through high-temperature processes like oxidation is the single most important factor in the fabrication of high-performance solar cells, and it is also the most difficult to control. The baseline process we have developed improves the reliability of all PDFL experiments by providing early detection of contamination or mechanical problems in our chemical cleaning baths, deionized water rinses, and high-temperature furnaces.

---

This work supported by the U.S. Department of Energy under contract DE-AC04-76DP00789.

## DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

**MASTER**

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

## MATERIALS

Our goal in the PDFL has been to develop cleaning sequences that are adequate for a wide variety of silicon materials, while maximizing the simplicity, safety, and economy of the process. We have performed experiments using a variety of crystalline and polycrystalline materials from several major photovoltaic production companies. We report here only those results obtained using 300- $\Omega$ cm n-type float-zone (FZ) and 10- $\Omega$ cm p-type Czochralski (Cz) wafers.

The FZ wafers were purchased from Wacker and SEH with mechanically lapped surfaces, and the Cz wafers were purchased from Monsanto and SEH America with the front surface mirror-polished and the back surface chemically etched. The wafers were <100>-oriented, 100-mm diameter, and 500 - 625  $\mu$ m thick.

All of the cleaning solutions used in the PDFL are mixed from concentrated semiconductor-grade liquid chemicals. Our primary suppliers are General Chemical and Ashland Chemical, although we occasionally purchase from other companies. The water used in these solutions is ultrapure 18-M $\Omega$ cm deionized (DI) water produced on-site, continuously circulated through an ultraviolet sterilizer and 0.05- $\mu$ m filter, and cultured monthly for bacteria. This DI water is also used for dump-rinsing the wafers after each step, and in the final rinse/dry, which is performed in an Estek SRD-1000 spinning rinser/dryer.

The baths used for the chemical etching and cleaning solutions are constructed of metal-free materials, ranging from polypropylene for low-temperature processes to Halar<sup>TM</sup> for high-temperature caustic solutions. Several of these baths are equipped with recirculation pumps and active temperature control, which can maintain the solution temperature to within 1°C throughout a

## MATERIALS

Our goal in the PDFL has been to develop cleaning sequences that are adequate for a wide variety of silicon materials while maximizing the simplicity, safety, and economy of the process. We have performed experiments using a variety of crystalline and polycrystalline materials from several major photovoltaic production companies. We report here only those results obtained using 300- $\Omega$ cm n-type float-zone (FZ) and 10- $\Omega$ cm p-type Czochralski (Cz) wafers.

The FZ wafers were purchased from Wacker and SEH with mechanically lapped surfaces, and the Cz wafers were purchased from Monsanto and SEH America with the front surface mirror-polished and the back surface chemically etched. The wafers were <100>-oriented, 100-mm diameter, and 500 - 625  $\mu$ m thick.

All of the cleaning solutions used in the PDFL are mixed from concentrated semiconductor-grade liquid chemicals. Our primary suppliers are General Chemical and Ashland Chemical, although we occasionally purchase from other companies. The water used in these solutions is ultrapure 18-M $\Omega$ cm deionized (DI) water produced on-site, continuously circulated through an ultraviolet sterilizer and 0.05- $\mu$ m filter, and cultured monthly for bacteria. This DI water is also used for dump-rinsing the wafers after each step, and in the final rinse/dry, which is performed in an Estek SRD-1000 spinning rinser/dryer.

The baths used for the chemical etching and cleaning solutions are constructed of metal-free materials, ranging from polypropylene for low-temperature processes to Halar<sup>TM</sup> for high-temperature caustic solutions. Several of these baths are equipped with recirculation pumps and active temperature control, which can maintain the solution temperature to within 1°C throughout a process. A separate quartz bath is used for solutions like sulfuric:peroxide (piranha) which exceed 80°C.

Our quartz single-wall furnace tubes are installed without chemical cleaning, then cleaned overnight at 1100°C using in-situ oxidation of trichloroethane (TCA) to form HCl vapor. One-hour TCA cleans are then implemented on an as-needed basis,

which thus far has been only a few times per year. Silicon carbide paddles are used to transport dedicated quartz boats into the furnace, using digital programming for push, pull, temperature ramp, and gas flow control. Vacuum wands with high-temperature plastic tips are used to load and unload wafers from the furnace boats.

#### MAIN EFFECTS EXPERIMENT

Our initial effort involved a statistically designed main-effects experiment to explore the effects of 18 parameters associated with 8 different chemical treatments: freon-acetone-alcohol (degrease), 7:1 buffered oxide etch (BOE), nitric-hydrofluoric silicon etch, sulfuric-peroxide clean (piranha), caustic choline clean (Summa), hydroxide-peroxide clean (RCA1), hydrofluoric acid dip (HF), and hydrochloric-peroxide clean (RCA2). Four additional parameters were introduced: initial wafer contamination, time delay between cleaning and oxidation, oxidation temperature, and forming-gas anneal temperature. The results of this main-effects experiment have been presented previously [2]. The most important factor that emerged from the main-effect experiment was the inclusion of an HF-dip/rinse/spin-dry as the last step before oxidation. Other potentially beneficial factors were the inclusion of a degrease, nitric:HF, and piranha clean. The effectiveness of nitric:HF in removing metal ions, especially iron, has been reported previously [3]. The nitric:HF also proved beneficial in improving the overnight stability of the lifetime. We found no basis for choosing the relatively complex and expensive RCA process [4].

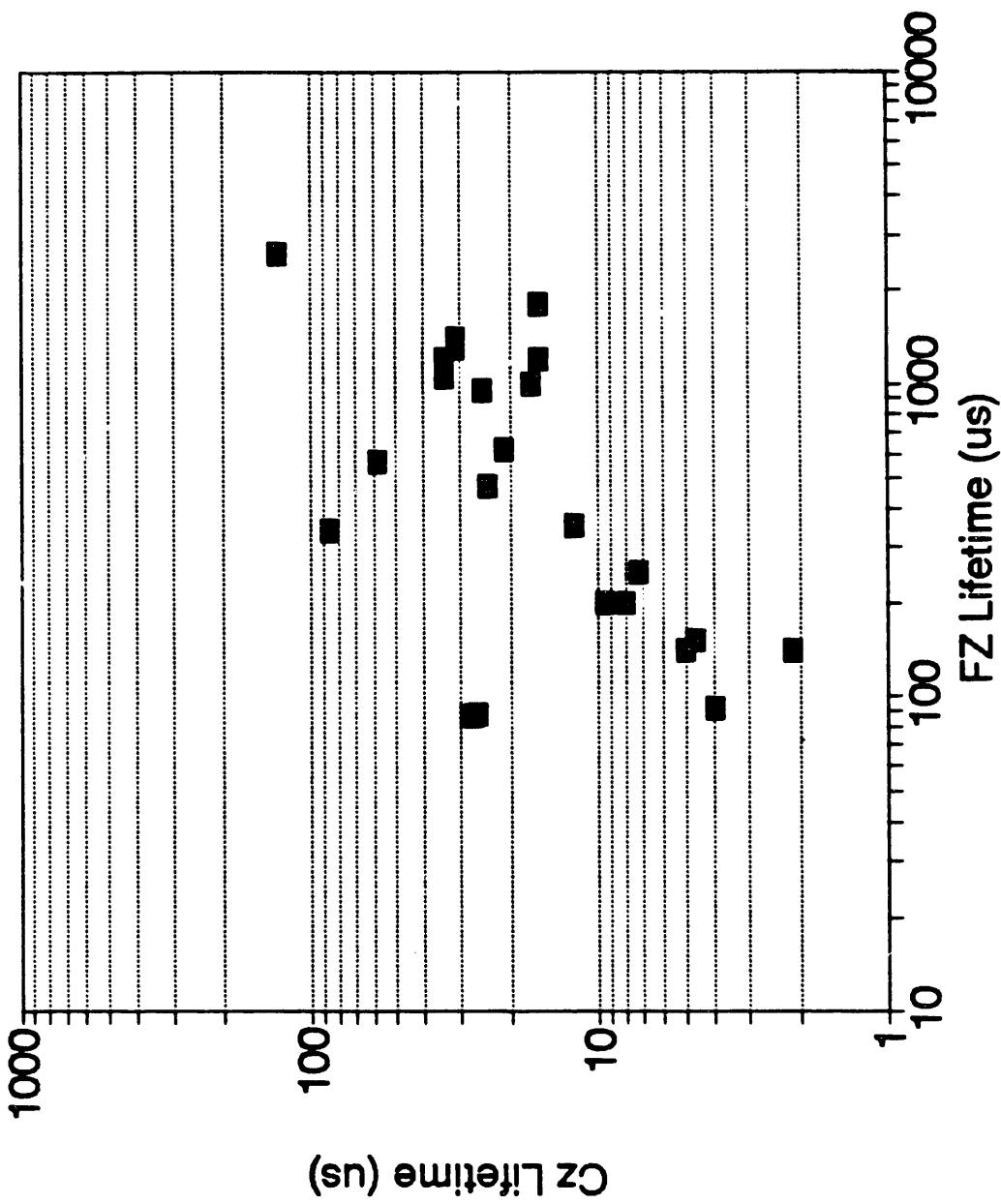

We have recently re-examined the data and found that the recombination lifetimes measured by photoconductance decay in each of the 24 trials for FZ and Cz are well correlated, as illustrated in Fig. 1. This result suggests that each impurity introduced during the cleaning sequence is much more effective as a recombination center in the low-resistivity p-type Cz material than in the high-resistivity n-type FZ material. Even the worst cleaning sequence only introduced enough impurities in the FZ wafers to reduce their lifetime to 100  $\mu$ s. The Cz wafers, with a starting lifetime of about 100  $\mu$ s, should have only been reduced to 50  $\mu$ s if the impurities had the same effect; yet the observed reduction in lifetime is more than an order of magnitude greater.

#### SURFACE DAMAGE REMOVAL

In conjunction with the cleaning optimization, we have also studied two different techniques for removing the surface damage on unpolished wafers. The first used 1:1 potassium-hydrosulfide and water

acetic acid:water), and buffered oxide etch (BOE), nitric-hydrofluoric silicon etch, sulfuric-peroxide clean (piranha), caustic choline clean (Summa), hydroxide-peroxide clean (RCA1), hydrofluoric acid dip (HF), and hydrochloric-peroxide clean (RCA2). Four additional parameters were introduced: initial wafer contamination, time delay between cleaning and oxidation, oxidation temperature, and forming-gas anneal temperature. The results of this main-effects experiment have been presented previously [2]. The most important factor that emerged from the main-effect experiment was the inclusion of an HF-dip/rinse/spin-dry as the last step before oxidation. Other potentially beneficial factors were the inclusion of a degrease, nitric:HF, and piranha clean. The effectiveness of nitric:HF in removing metal ions, especially iron, has been reported previously [3]. The nitric:HF also proved beneficial in improving the overnight stability of the lifetime. We found no basis for choosing the relatively complex and expensive RCA process [4].

We have recently re-examined the data and found that the recombination lifetimes measured by photoconductance decay in each of the 24 trials for FZ and Cz are well correlated, as illustrated in Fig. 1. This result suggests that each impurity introduced during the cleaning sequence is much more effective as a recombination center in the low-resistivity p-type Cz material than in the high-resistivity n-type FZ material. Even the worst cleaning sequence only introduced enough impurities in the FZ wafers to reduce their lifetime to 100  $\mu$ s. The Cz wafers, with a starting lifetime of about 100  $\mu$ s, should have only been reduced to 50  $\mu$ s if the impurities had the same effect; yet the observed reduction in lifetime is more than an order of magnitude greater.

#### SURFACE DAMAGE REMOVAL

In conjunction with the cleaning optimization, we have also studied two different techniques for removing the surface damage on unpolished wafers. We first used 1:1 potassium-hydroxide and water (KOH) at 85°C for 5-10 minutes to remove about 40  $\mu$ m (20  $\mu$ m per side) from the wafers, consistent with published data [5]. This process proved to be rather messy, generating a lot of particulate residue on and around the etch bath because it was necessary to remove the lid to agitate the wafers continuously to insure uniform etching. Even then, the wafer surfaces were rough enough to interfere with fine-line photolithographic alignment and

Fig. 1. Correlation of float-zone and Czochralski wafer recombination lifetimes for a wide variety of preoxidation cleaning sequences.

ellipsometry. The KOH process was used to prepare all of the FZ wafers used in the main-effects experiment.

Attempts to use lower-temperature (50-70°C) KOH etching solutions in a recirculating bath to eliminate the particulate residue were not successful, resulting in very rough wafer surfaces with poor uniformity.

Ten months ago, we switched to a 15:1 nitric:HF room-temperature silicon etch, performed in a recirculating bath. Ten minutes in this solution removes about 60  $\mu\text{m}$  (30  $\mu\text{m}$  per side) of silicon, consistent with published data [6]. This treatment leaves the surfaces fairly smooth. Additional thinning in this solution produces nearly specular surfaces, but tends to feather the wafer edges, making them very fragile. This solution also produces orange nitrogen dioxide fumes that may need to be scrubbed in an industrial setting. Although waste disposal costs for this solution are rather high due to the mixing of an acid and oxidizer, it should be possible to neutralize the solution on-site to produce an effluent that is free of metal ions. We have found that we can reuse the same 12-liter bath of nitric:HF mixture for many wafer batches if we replenish 1.5 ml of HF for every wafer-minute of etching. Otherwise, the silicon etch rate decreases with each use of the solution.

Two months ago, we discovered that a ten-minute etch in a 70°C KOH solution (1:2 KOH:H<sub>2</sub>O) following the nitric:HF polishing etch yields a nearly specular surface and improves the post-oxidation PCD lifetime of high-resistivity float-zone wafers. Table 1 lists the results from two lots in which

Fig. 1. Correlation of float-zone and Czochralski wafer recombination lifetimes for a wide variety of preoxidation cleaning sequences.

ellipsometry. The KOH process was used to prepare all of the FZ wafers used in the main-effects experiment.

Attempts to use lower-temperature (50-70°C) KOH etching solutions in a recirculating bath to eliminate the particulate residue were not successful, resulting in very rough wafer surfaces with poor uniformity.

Ten months ago, we switched to a 15:1 nitric:HF room-temperature silicon etch, performed in a recirculating bath. Ten minutes in this solution removes about 60  $\mu\text{m}$  (30  $\mu\text{m}$  per side) of silicon, consistent with published data [6]. This treatment leaves the surfaces fairly smooth. Additional thinning in this solution produces nearly specular surfaces, but tends to feather the wafer edges, making them very fragile. This solution also produces orange nitrogen dioxide fumes that may need to be scrubbed in an industrial setting. Although waste disposal costs for this solution are rather high due to the mixing of an acid and oxidizer, it should be possible to neutralize the solution on-site to produce an effluent that is free of metal ions. We have found that we can reuse the same 12-liter bath of nitric:HF mixture for many wafer batches if we replenish 1.5 ml of HF for every wafer-minute of etching. Otherwise, the silicon etch rate decreases with each use of the solution.

Two months ago, we discovered that a ten-minute etch in a 70°C KOH solution (1:2 KOH:H<sub>2</sub>O) following the nitric:HF polishing etch yields a nearly specular surface and improves the post-oxidation PCD lifetime of high-resistivity float-zone wafers. Table 1 lists the results from two lots in which the additional KOH step was compared side-by-side with nitric:HF alone. The PCD lifetime measurements were made both with and without a white-light bias, which affects the recombination rate by increasing the excess carrier density in the wafer. The lifetime entries shown in the table are the average of fifteen measurements spread across three wafers. Although we have not attempted to separate bulk and surface effects in

these PCD measurements, we presume that the KOH improvement is due to reduced recombination at the smoother surfaces.

Table 1

Evaluation of KOH after Nitric:HF

Average PCD Lifetime ( $\mu$ s)

95% confidence limits  $\pm 15\%$

| Lot ID | Light Bias | Nitric:HF | Also KOH |

|--------|------------|-----------|----------|

| Life55 | None       | 1909      | 3679     |

| Life55 | 100%       | 475       | 853      |

| Life56 | None       | 2639      | 3316     |

| Life56 | 100%       | 482       | 675      |

#### THE LIFETIME BASELINE

Based on the results of the main-effects and damage-removal experiments, a relatively simple baseline process has been established to monitor contamination in the chemical baths and furnace oxidation tubes. The lifetime baseline process involves damage-removal, cleaning, dry oxidation, annealing, and measurements. The damage-removal process involves HF, nitric:HF, and KOH etches. The cleaning process involves only HF and nitric:HF solutions. Oxidation is at 1000°C, followed by an in-situ inert-gas anneal, then a forming-gas anneal at 450°C. The PCD lifetime is measured both with and without light bias, after waiting at least one hour for the surfaces to stabilize. The oxide and wafer thickness are also measured.

Parameter variations have been explored in an attempt to simplify the process and reduce chemical consumption. After applying a damage-removal etch to any unpolished wafers, the cleaning sequence requires only a 15-second 10:1 H<sub>2</sub>O:HF dip, 10 minutes of 100:1 nitric:HF etch, and a final 50:1 H<sub>2</sub>O:HF dip. All of these chemicals are at room temperature and can be reused, although the final 50:1 HF dip should be replaced frequently to prevent plating contaminants onto the wafers.

The baseline oxidation is performed with the wafers split between two different furnace tubes so that contamination can be traced to either the chemical baths or one of the furnace tubes. Tube 2 is normally used for phosphorus diffusion, and tube 3 is normally used for dry oxidation. Two clean baffle wafers are placed on each end of the wafers in the furnace boat, to minimize end effects. The wafers for each tube are pushed at 800°C in a nitrogen ambient. The temperature is ramped to 1000°C at 5°C/min using nitrogen in tube 2 and argon in tube 3. The ambient is then switched to oxygen for 30 minutes. After this time, the ambient reverts to either nitrogen or argon for a

## THE LIFETIME BASELINE

Based on the results of the main-effects and damage-removal experiments, a relatively simple baseline process has been established to monitor contamination in the chemical baths and furnace oxidation tubes. The lifetime baseline process involves damage-removal, cleaning, dry oxidation, annealing, and measurements. The damage-removal process involves HF, nitric:HF, and KOH etches. The cleaning process involves only HF and nitric:HF solutions. Oxidation is at 1000°C, followed by an in-situ inert-gas anneal, then a forming-gas anneal at 450°C. The PCD lifetime is measured both with and without light bias, after waiting at least one hour for the surfaces to stabilize. The oxide and wafer thickness are also measured.

Parameter variations have been explored in an attempt to simplify the process and reduce chemical consumption. After applying a damage-removal etch to any unpolished wafers, the cleaning sequence requires only a 15-second 10:1 H<sub>2</sub>O:HF dip, 10 minutes of 100:1 nitric:HF etch, and a final 50:1 H<sub>2</sub>O:HF dip. All of these chemicals are at room temperature and can be reused, although the final 50:1 HF dip should be replaced frequently to prevent plating contaminants onto the wafers.

The baseline oxidation is performed with the wafers split between two different furnace tubes so that contamination can be traced to either the chemical baths or one of the furnace tubes. Tube 2 is normally used for phosphorus diffusion, and tube 3 is normally used for dry oxidation. Two clean baffle wafers are placed on each end of the wafers in the furnace boat, to minimize end effects. The wafers for each tube are pushed at 800°C in a nitrogen ambient. The temperature is ramped to 1000°C at 5°C/min using nitrogen in tube 2 and argon in tube 3. The ambient is then switched to oxygen for 30 minutes. After this time, the ambient reverts to either nitrogen or argon for a 15-minute in-situ anneal. The temperature is then ramped down to 800°C at 5°C/min and the wafers are pulled in nitrogen. The wafers are then transferred to a different tube, where they receive a 20-minute anneal in 12% hydrogen-argon forming gas at 450°C.

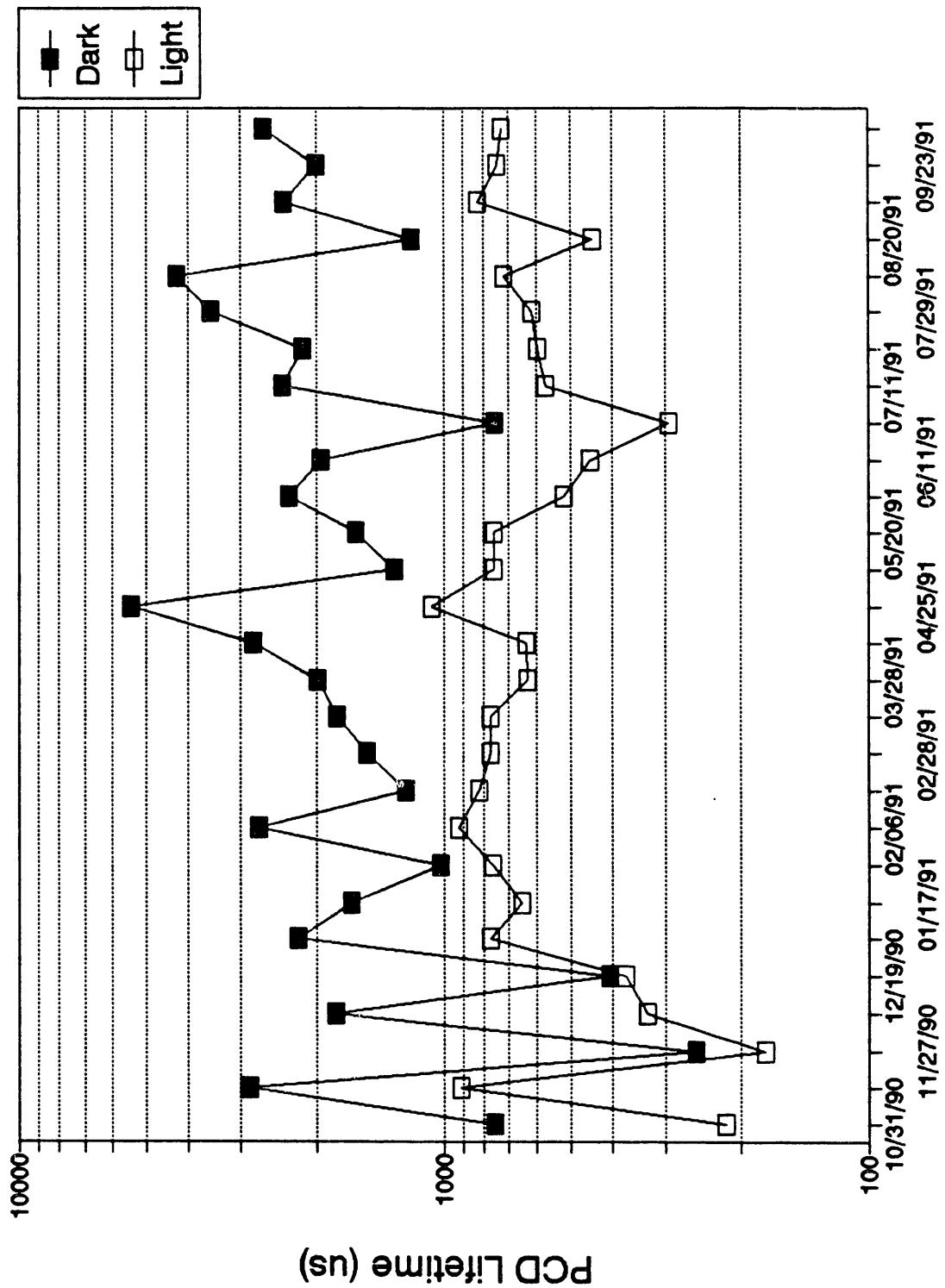

Fig. 2 shows the post-oxidation PCD lifetimes obtained in the PDFL over the past year using the baseline cleaning process on high-resistivity n-type FZ wafers. Lifetimes are shown both with and without light bias, with each value representing the average of 30 measurements spread across six wafers from both furnace tubes. Although the light and dark results tend to follow one another, there are some significant deviations that have been traced to variations in the damage-removal etch, to be discussed at the end of this section.

Fig. 2. PDFL lifetime baseline experience using nitric:HF for damage removal and cleaning of high-resistivity n-type float-zone wafers.

With the exception of four lifetime "crashes," the dark PCD lifetime of these wafers has remained above 1 ms. Recovery from the first three of these crashes was obtained by acid-cleaning the chemical baths using HCl. Beginning in February 1991, we started using a fresh solution of 50:1 H<sub>2</sub>O:HF for all lifetime baseline lots, and this has improved the consistency somewhat. The recent lifetime crash in June 1991 was traced to nickel contamination on the plastic-tipped vacuum wand used to load and unload the wafers from the furnace boat. This same wand had been used to load some nickel-plated wafers into the forming-gas anneal tube. Fig. 3 illustrates the lifetime as a function of position for one particular wafer from this lot. The lifetime was adversely affected only in the lower-left portion of the wafer, which is where the wafers were grasped by the vacuum wand.

The lifetime baseline also provides a means to monitor the oxide growth rate as measured by ellipsometry [7] and the surface damage-removal etch rate as measured by a digital micrometer. We have observed that the oxide thickness grown in tube 3 is quite consistent, with a standard deviation from run-to-run of  $\pm 4\%$ . However, a large

Fig. 2. PDFL lifetime baseline experience using nitric:HF for damage removal and cleaning of high-resistivity n-type float-zone wafers.

With the exception of four lifetime "crashes," the dark PCD lifetime of these wafers has remained above 1 ms. Recovery from the first three of these crashes was obtained by acid-cleaning the chemical baths using HCl. Beginning in February 1991, we started using a fresh solution of 50:1 H<sub>2</sub>O:HF for all lifetime baseline lots, and this has improved the consistency somewhat. The recent lifetime crash in June 1991 was traced to nickel contamination on the plastic-tipped vacuum wand used to load and unload the wafers from the furnace boat. This same wand had been used to load some nickel-plated wafers into the forming-gas anneal tube. Fig. 3 illustrates the lifetime as a function of position for one particular wafer from this lot. The lifetime was adversely affected only in the lower-left portion of the wafer, which is where the wafers were grasped by the vacuum wand.

The lifetime baseline also provides a means to monitor the oxide growth rate as measured by ellipsometry [7] and the surface damage-removal etch rate as measured by a digital micrometer. We have observed that the oxide thickness grown in tube 3 is quite consistent, with a standard deviation from run-to-run of  $\pm 4\%$ . However, a large variation is found in tube 2, normally used for phosphorus diffusion. This appears to be related to how recently the tube was used for a phosphine diffusion. The oxidation of phosphine produces water vapor, which significantly increases the oxide growth rate during subsequent oxidations.

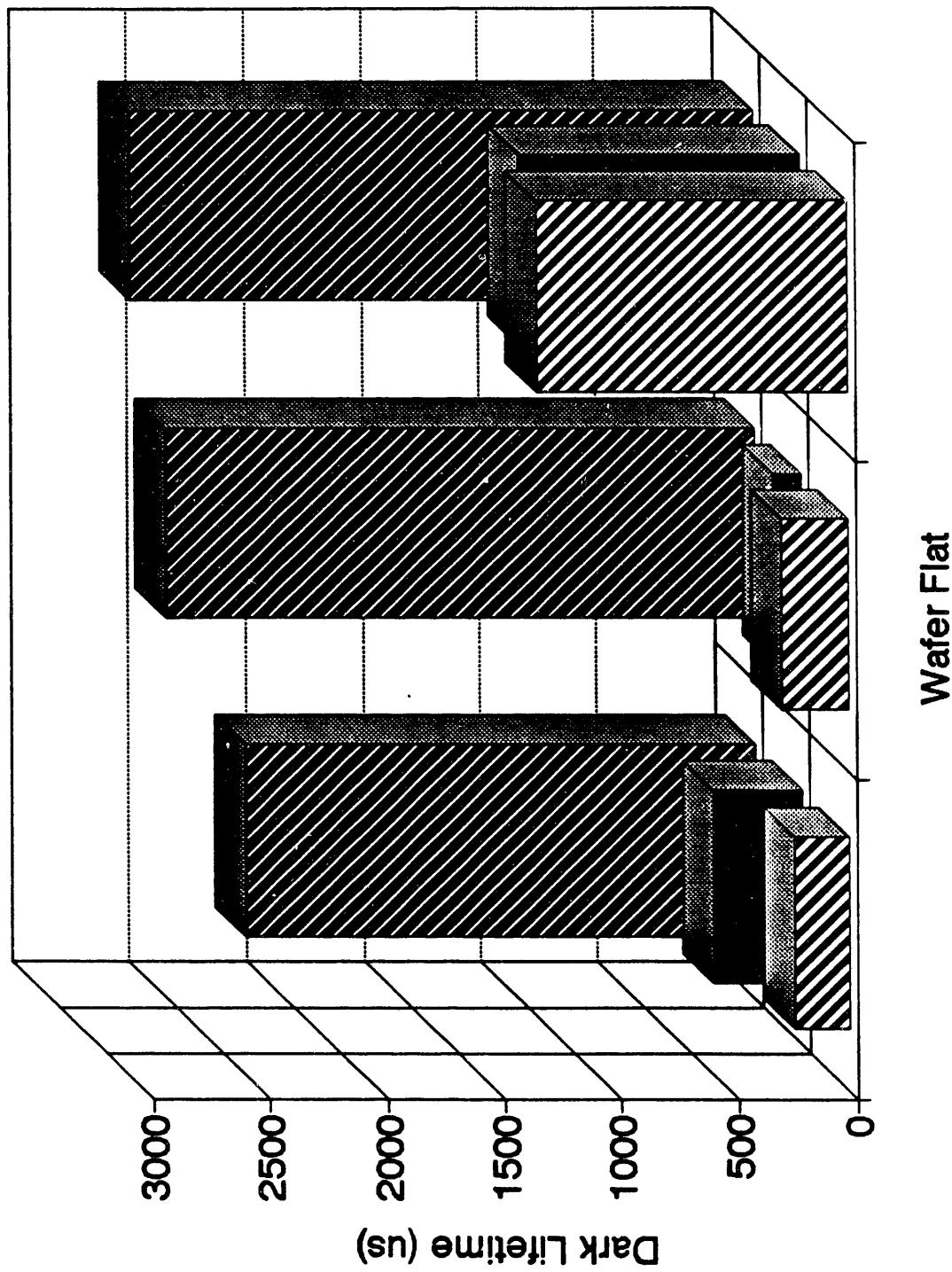

Fig. 3. Lifetime map for one wafer in lot Life52, illustrating contamination restricted to the lower-left corner of the wafer.

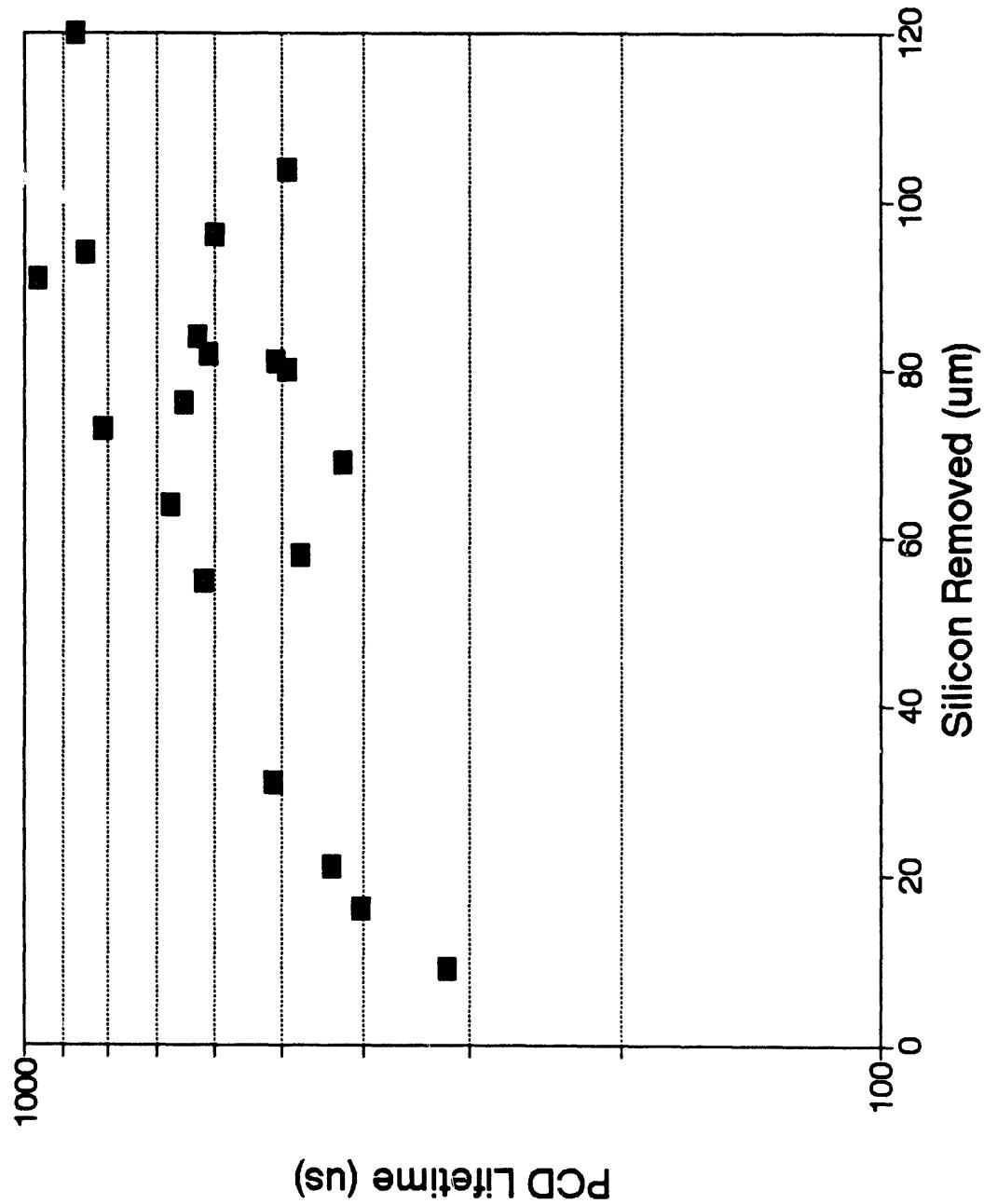

By measuring the wafer thickness at both the start and finish of the baseline process, it is possible to monitor the damage-removal etch rate. We found that the etch rate in the 15:1 nitric:HF solution was very inconsistent, but that it could be stabilized by replenishing the HF after each use. Until this procedure was implemented, the lifetime baseline lots served as an unintended experiment comparing the PCD lifetime against the amount of silicon removed by the etch. Fig. 4 illustrates, the light-biased PCD lifetime obtained for furnace tube 3. The light-biased PCD measurement is used for this purpose because it is more sensitive to the surface condition, presumably because in the absence of light bias there is enough energy-band bending to repel carriers away from the damaged near-surface region.

Fig. 4. Correlation of light-biased PCD lifetime with amount of silicon removed from unpolished

**Fig. 3. Lifetime map for one wafer in lot Life52, illustrating contamination restricted to the lower-left corner of the wafer.**

By measuring the wafer thickness at both the start and finish of the baseline process, it is possible to monitor the damage-removal etch rate. We found that the etch rate in the 15:1 nitric:HF solution was very inconsistent, but that it could be stabilized by replenishing the HF after each use. Until this procedure was implemented, the lifetime baseline lots served as an unintended experiment comparing the PCD lifetime against the amount of silicon removed by the etch. Fig. 4 illustrates the light-biased PCD lifetime obtained for furnace tube 3. The light-biased PCD measurement is used for this purpose because it is more sensitive to the surface condition, presumably because in the absence of light bias there is enough energy-band bending to repel carriers away from the damaged near-surface region.

**Fig. 4. Correlation of light-biased PCD lifetime with amount of silicon removed from unpolished high-resistivity n-type FZ wafers.**

Fig. 4 shows a clear increase in lifetime as silicon is removed, up to about 40  $\mu\text{m}$  (20  $\mu\text{m}$  per side), with somewhat less effect apparent beyond that point. Note that most of these lots used only a nitric:HF polishing etch, but a few of the more recent lots included an additional KOH etch to

produce a smoother surface. The lot that was contaminated by the vacuum wand was excluded from this data set.

### CONCLUSIONS

A series of controlled experiments has been performed in our Photovoltaic Device Fabrication Laboratory to evaluate the effect of various chemical surface treatments on the recombination lifetime of crystalline silicon wafers subjected to a high-temperature dry oxidation. Both float-zone and Czochralski materials were evaluated, and correlations between the two materials were presented. We also evaluated the effect of different chemical damage-removal etches for unpolished wafers and found that a nitric:HF etch followed by a mild KOH etch gives the best lifetime and surface smoothness. From this series of experiments, we deduced a simple preoxidation cleaning sequence based on nitric:HF solutions that yields recombination lifetimes consistently greater than 1 ms in high-resistivity float-zone wafers.

### ACKNOWLEDGEMENTS

The authors wish to thank John McBrayer of Sandia for championing the establishment of baselines for process control in the PDFL. Also Ron Sinton of Stanford (now SunPower) for sharing his experience with nitric:HF etching solutions. And thanks to the few but dedicated members of the PDFL staff for keeping everything running as smoothly as could be expected during the lab's start-up phase.

### REFERENCES

- [1] P. A. Basore and B. R. Hansen, "Microwave-Detected Photoconductance Decay," 21st PVSC, May 1990, pp. 374-379.

- [2] D. King, J. McBrayer, et al., "Experimental Evaluation of Chemical Cleaning Processes for High-Lifetime Silicon Processing," MRCE Monographs on Materials and Processes, Univ. of Texas at El Paso, March 1990.

- [3] R. Takizawa, T. Nakanishi, K. Honda, and A. Ohsawa, "Ultraclean Technique for Silicon Wafer Surfaces with HNO<sub>3</sub>-HF Systems," Jap. Jour. of Applied Physics, 27 (11), November 1988, pp. L2210-L2212.

- [4] W. Kern and D. A. Puotinen, "Cleaning Solutions Based on Hydrogen Peroxide for use in Silicon Semiconductor Technology," RCA Review, June 1970, pp. 187-206.

- [5] H. Seidel et al., "Anisotropic Etching of Crystalline Silicon in Alkaline Solutions," Jour. of the Electrochem. Soc. 137 (11), November 1990, pp. 3612-3632.

- [6] D. R. Turner, "On the Mechanism of Chemically Etching Germanium and Silicon," Jour. of the

presented. We also evaluated the effect of different chemical damage-removal etches for unpolished wafers and found that a nitric:HF etch followed by a mild KOH etch gives the best lifetime and surface smoothness. From this series of experiments, we deduced a simple preoxidation cleaning sequence based on nitric:HF solutions that yields recombination lifetimes consistently greater than 1 ms in high-resistivity float-zone wafers.

#### ACKNOWLEDGEMENTS

The authors wish to thank John McBrayer of Sandia for championing the establishment of baselines for process control in the PDFL. Also Ron Sinton of Stanford (now SunPower) for sharing his experience with nitric:HF etching solutions. And thanks to the few but dedicated members of the PDFL staff for keeping everything running as smoothly as could be expected during the lab's start-up phase.

#### REFERENCES

- [1] P. A. Basore and B. R. Hansen, "Microwave-Detected Photoconductance Decay," 21st PVSC, May 1990, pp. 374-379.

- [2] D. King, J. McBrayer, et al., "Experimental Evaluation of Chemical Cleaning Processes for High-Lifetime Silicon Processing," MRCE Monographs on Materials and Processes, Univ. of Texas at El Paso, March 1990.

- [3] R. Takizawa, T. Nakanishi, K. Honda, and A. Ohsawa, "Ultraclean Technique for Silicon Wafer Surfaces with  $\text{HNO}_3$ -HF Systems," Jap. Jour. of Applied Physics, 27 (11), November 1988, pp. L2210-L2212.

- [4] W. Kern and D. A. Puotinen, "Cleaning Solutions Based on Hydrogen Peroxide for use in Silicon Semiconductor Technology," RCA Review, June 1970, pp. 187-206.

- [5] H. Seidel et al., "Anisotropic Etching of Crystalline Silicon in Alkaline Solutions," Jour. of the Electrochem. Soc. 137 (11), November 1990, pp. 3612-3632.

- [6] D. R. Turner, "On the Mechanism of Chemically Etching Germanium and Silicon," Jour. of the Electrochem. Soc. 107 (10), October 1960, pp. 810-816.

- [7] H. L. Tardy, "ELLIPSE User's Manual and Program Reference", Sandia Report SAND89-0008, March 1989.

PREOXIDATION CLEANING OPTIMIZATION

FOR CRYSTALLINE SILICON

Paul A. Basore and M. Elaine Buck

Sandia National Laboratories

Presented at the 22nd IEEE Photovoltaic Specialists Conference, October 1991. Copyright IEEE 1991.

Report No. 91-10-001

SANDIA NATIONAL LABORATORIES

OCT 21 1991

# Comparison of Cz and FZ Lifetime

# PDFL Lifetime Control

Life52-W1

## Effect of Silicon Etch on Lifetime

4

END

DATE

FILMED

// 122191

II