Ion-Implanted GaAs JFETs with  $f_t > 45$  GHz for Low-Power ElectronicsJ. C. Zolper, A. G. Baca, M. E. Sherwin,<sup>\*</sup> V. M. Hietala, and R. J. Shul

Sandia National Laboratories, Albuquerque, NM 87185-0603<sup>\*</sup>present address: Microwave Signal, 22300 Comsat Dr, Clarksburg, MD 20871

RECEIVED

NOV 06 1996

OSTI

**Abstract** - GaAs Junction Field Effect Transistors (JFETs) are reported with gate lengths down to 0.3  $\mu\text{m}$ . The structure is fully self-aligned and employs all ion implantation doping.  $\text{p}^+$ -gate regions are formed with either Zn or Cd implants along with a P co-implantation to reduce diffusion. The source and drain implants are engineered with Si or SiF implants to minimize short channel effects. 0.3  $\mu\text{m}$  gate length JFETs are demonstrated with a sub-threshold slope of 110 mV/decade along with an intrinsic unity current gain cut-off frequency as high as 52 GHz.

## I. INTRODUCTION

GaAs Junction Field Effect Transistors (JFETs) have attracted renewed attention for low-power, low-voltage electronics [1-3]. JFETs have a significant advantage over MESFETs for low-power operation due to the higher gate barrier of the p/n junction gate which results in less gate leakage. Although some JFET structures suffer a degradation in high-frequency performance due to the added gate-to-source capacitance ( $C_{GS}$ ) of the junction gate and the gate length broadening associated with formation of the  $\text{p}^+$ -gate region, we have previously demonstrated a self-aligned GaAs JFET technology that minimizes  $C_{GS}$  and closely aligns the  $\text{p}^+$ -gate with the gate contact [3].

In our earlier work, JFETs with a 0.7  $\mu\text{m}$  gate length were reported with an  $f_t$  of 26 GHz and  $f_{\max}$  of 42 GHz [4]. These devices have been employed as the n-channel FET in a complementary heterostructure field effect transistor (CHFET) technology with the demonstration of 319 ps loaded gate delays at 8.9 fJ [5]. Furthermore, these JFETs are being applied to low-power microwave circuits. A hybrid amplifier has been reported that operates at 1 mW of DC power with a gain of 10 dB and a

noise figure of less than 2.5 dB at a frequency of 2.15 GHz using 0.7  $\mu\text{m}$  gate lengths JFETs[6].

In this work we present results for all ion implanted GaAs JFETs with gate lengths down to 0.3  $\mu\text{m}$ . Details of the process sequence, particularly those aspects required to reduce short channel effects, are reviewed. Finally, DC and rf device results are presented.

## II. JFET PROCESSING

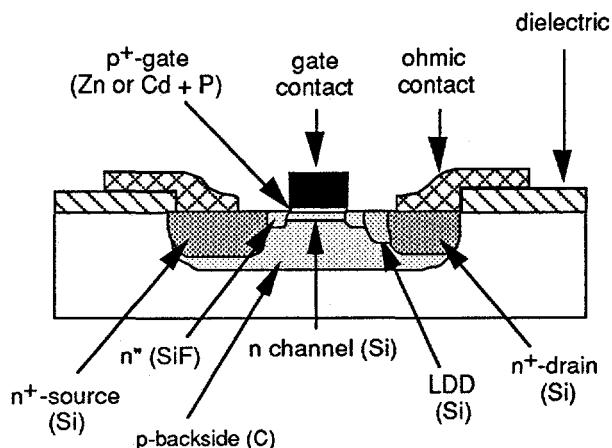

Fig. 1 shows a schematic of the all ion-implanted GaAs JFET with seven different implanted regions. To reduce short channel effects in an all ion implanted device, the doping profiles must be significantly modified as compared to a longer gate transistor. In particular, the depth of the source and drain ( $\text{n}^+$ ) implant must be reduced and the lateral profile must be off-set from the gate contact. Since a Varian 400-10 ion implanter with a minimum operating energy of ~40 keV was used, we employed 40 keV SiF implants next to the gate contact ( $\text{n}''$  implants) to realize an effective Si ion energy of 25 keV which gives a projected range of 26 nm with a lateral straggle of 20 nm. Next, 100 nm  $\text{SiO}_2$  sidewall spacers were

Fig. 1. Schematic of self-aligned GaAs JFET showing the multiple implant areas.

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, make any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

#### **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

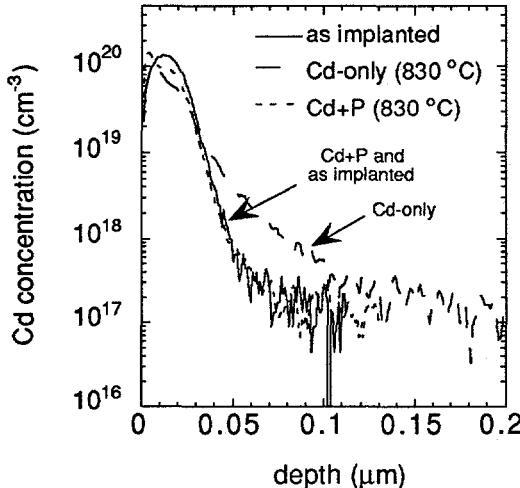

defined by a deposition and etchback process and a lightly-doped drain (LDD or n') region was implanted with 50 keV  $^{29}\text{Si}$  ions self-aligned to the sidewalls. Finally the n<sup>+</sup> source and drain implant is done with a photolithographically defined LDD region. This lateral doping profile is critical to minimizing output conductance and achieving good channel pinch-off characteristics. In addition to the n-type doping profile, the p<sup>+</sup>-gate region has been made extremely shallow by using the heavy acceptor species Zn or Cd implanted at 45 keV to achieve very shallow p<sup>+</sup>-regions as shown in Fig 2 for Cd. Fig 2 also shows the utility of P co-implantation for reducing indiffusion of Cd. This is understood by the P increasing the probability for Cd to occupy the Ga-sublattice and thereby reduce interstitial diffusion [7]. Backside confinement is achieved with carbon implantation (90 keV,  $4 \times 10^{12} \text{ cm}^2$ ) which has been shown to give enhanced high-frequency performance compared to Mg (or Be) implants particularly at higher doses [8]. The gate contact is sputter deposited tungsten defined by electron beam lithography and patterned in a subtractive RIE-based etch [9]. Realization of a near vertical gate profile is critical since the gate contact feature acts as a self-aligning mask for n-type implants in the source and drain regions. All implants are activated in a single rapid thermal anneal at 800 to 850 °C for 15 s. Finally, ohmic contacts (Ge/Au/Ni/Au) are defined by liftoff and alloyed at 400 °C for 15 s.

Fig. 2. SIMS profile of implanted Cd (45 keV,  $3 \times 10^{14} \text{ cm}^{-2}$ ) alone or along with P( $^{62}\text{P}_2$ ; 40 keV,  $3 \times 10^{14} \text{ cm}^{-2}$ ) as implanted or annealed at 830 °C for 15 s.

### III. DEVICE RESULTS

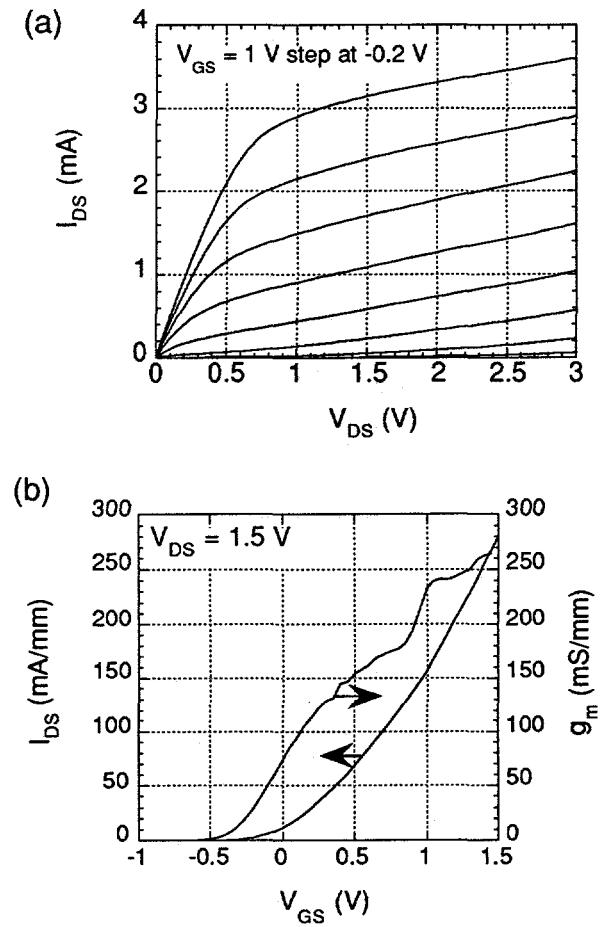

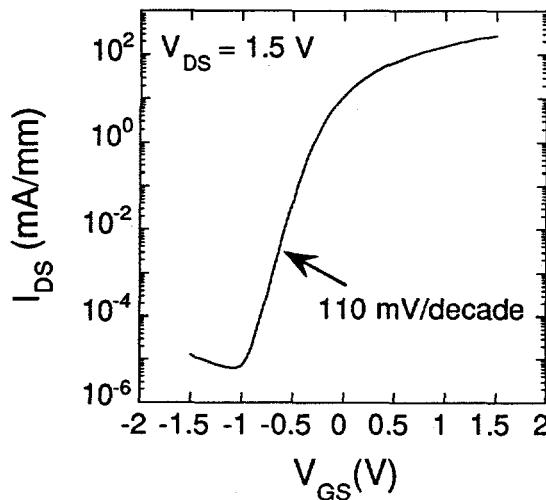

Fig 3 shows DC performance of a 0.3  $\mu\text{m}$   $\times$  20  $\mu\text{m}$  GaAs JFET with a Cd-implanted gate region that demonstrates a transconductance of 230 mS/mm and a saturation current of 160 mA/mm for  $V_{GS} = 1 \text{ V}$  and  $V_{DS} = 1.5 \text{ V}$ . Although this device has a threshold voltage of  $\sim 0.2 \text{ V}$ , this can be shifted to enhancement mode operation by adjusting the channel implant dose. The output conductance ( $g_{DS}$ ) between  $V_{DS} = 1.5$  to 2.5 V is 17 mS/mm and the sub-threshold slope, as seen in Fig. 4, is 110 mV/decade. Both of these values are comparable to previous longer gate length implanted JFETs [4] and are the result of the optimized doping profiles in this device. The gate diode has a forward turn-on voltage at 1 mA/mm of gate current of 1.0 V, allowing the JFET to operate at low power with minimal gate leakage on a 1 V power supply.

Fig. 3. DC performance of a 0.3  $\times$  40  $\mu\text{m}^2$  Cd-gate GaAs JFET.

Fig 4.  $\log I_{DS}$  versus  $V_{GS}$  at  $V_{DS} = 1.5$  V showing a sub-threshold slope of 110 mV/decade.

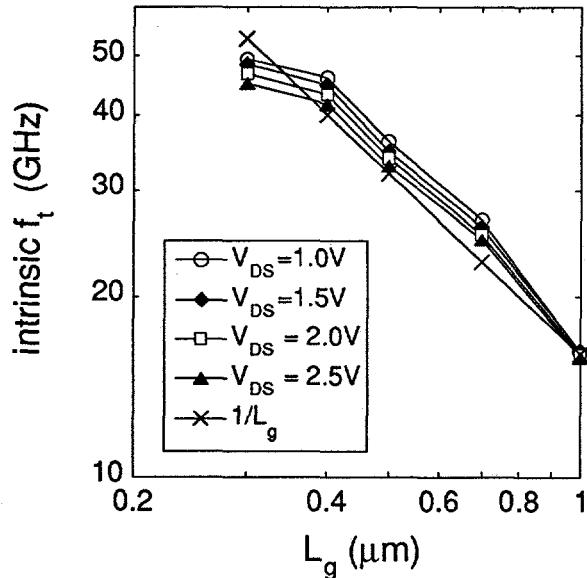

Fig 5 shows the dependence of intrinsic  $f_t$  (corrected for pad capacitance) versus gate length at several values of  $V_{DS}$  for Cd-gate JFETs which follows a  $1/L_g$  dependence down to 0.4  $\mu\text{m}$  before showing some roll-off at the shortest gate length. At increasing drain biases intrinsic  $f_t$  decreases due to the increase in the effective gate length with the increase in the gate/drain depletion region.

Fig. 5.  $f_t$  vs. gate length for various drain biases for 40  $\mu\text{m}$  wide GaAs JFETs at  $V_{GS} = 1.0$  V.

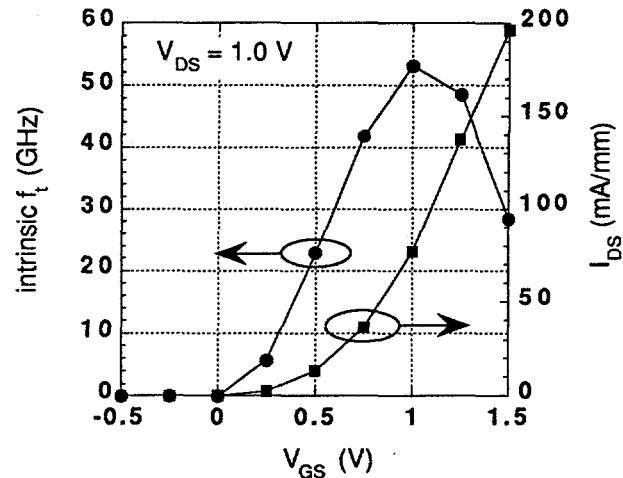

Fig. 6 shows the intrinsic  $f_t$  and  $I_{DS}$  versus gate bias at  $V_{DS} = 1$  V for a  $0.3 \times 40 \mu\text{m}^2$  Zn-gate JFET. This shows the enhancement mode operation of the device as well as the excellent frequency performance for 1 V operation. An intrinsic unity current gain cut-off frequency of 52 was measured for this device. The roll off at higher gate biases was due to increased gate conduction. The maximum oscillation frequency ( $f_{max}$ ) on this device was 48 GHz.  $f_{max}$  was limited by a high ohmic contact resistance on this device (0.27  $\Omega\text{-mm}$ , < 0.1  $\Omega\text{-mm}$  is typically achieved) and the high resistance of the small geometry tungsten gate contact. A gold overlayer will be required to reduce this gate resistance in future devices.

Fig. 6. Intrinsic  $f_t$  and  $I_{DS}$  versus  $V_{GS}$  at  $V_{DS} = 1.0$  V for a  $0.3 \times 40 \mu\text{m}^2$  Zn-gate GaAs JFET.

#### IV. CONCLUSION

In conclusion, we have demonstrated 0.3  $\mu\text{m}$  gate length all ion implanted GaAs JFETs with  $V_{GS(on)} = 1$  V with DC and rf performance comparable to a similar gate length GaAs MESFET with  $V_{GS(on)} \sim 0.6$  V. Since this JFET is based solely on ion implantation it should be readily manufacturable. In addition, this device should be very attractive for low-power, low-voltage, high-frequency operation.

## ACKNOWLEDGMENTS

The authors gratefully acknowledge the excellent technical support of G. Lopez in device processing and M. Housel in rf testing. This work was supported by the Department of Energy under contract #DE-AC04-94AL85000.

## REFERENCES

- [1] M. R. Wilson, D. E. Chasson, B. S. Krongrad, R. W. Rosenberry, N. A. Shah, and B. M. Welch, "Process Optimization of High Performance Ion Implanted GaAs FET's," in *Tech. Dig. 14th Gallium Arsenide IC Symp.*, p. 169 (1992).

- [2] D. Sherrer, J. Kruse, J. Laskar, M. Feng, M. Wada, C. Takano, and J. Kasahara, "Low-power performance of 0.5  $\mu$ m JFET for low-cost MMIC's in personnel communications," *IEEE Elect. Dev. Lett.*, **14**, 428 (1993).

- [3] J. C. Zolper, A. G. Baca, R. J. Shul, A. J. Howard, D. J. Rieger, M. E. Sherwin, M. L. Lovejoy, H. P. Hjalmarson, B. L. Draper, J. F. Klem, and V. M. Hietala, "An all-implanted, self-aligned, GaAs JFET with a non-alloyed W/p<sup>+</sup>-GaAs ohmic gate contact," *IEEE Trans. Elec. Dev.* **41**, 1078 (1994).

- [4] J. C. Zolper, A. G. Baca, M. E. Sherwin, and R. J. Shul, "High-performance GaAs JFET with shallow implanted Cd-gates," *Electron. Letts.* **31**, 923 (1995).

- [5] A. G. Baca, J. C. Zolper, M. E. Sherwin, P. J. Robertson, R. J. Shul, A. J. Howard, D. J. Rieger, and J. F. Klem, "Complementary GaAs junction-gated heterostructure field effect transistor technology," *IEEE GaAs IC Symposium Technical Digest*, pp. 59-62, 1994.

- [6] A. G. Baca, M. E. Sherwin, J. C. Zolper, D. F. Dubbert, V. M. Hietala, R. J. Shul, L. R. Sloan, and M. J. Hafich, "Complementary HFET technology for low-power mixed-mode applications," *Conf. Proceedings of Materials Research Society, Symposium C*, Spring 1996 (Material Research Society, Pittsburgh, PA, in press).

- [7] M. E. Sherwin, J. C. Zolper, A. G. Baca, T. J. Drummond, R. J. Shul, A. J. Howard, D. J. Rieger, R. P. Schneider, and J. F. Klem, "Comparison of Mg and Zn Implants for GaAs n-channel JFETs," *J. Electronic Materials* **23**, 809 (1994).

- [8] J. C. Zolper, M. E. Sherwin, A. G. Baca, R. J. Shul, J. F. Klem, and V. M. Hietala, "Enhanced High Frequency Performance in a GaAs, Self-Aligned, n-JFET Using a Carbon Buried p-Implant," *IEEE Elec. Dev. Lett.*, vol **15** (12) 493 (1994).

- [9] R. J. Shul, M. E. Sherwin, A. G. Baca, and D. J. Rieger, "Etching of sub-0.5  $\mu$ m W/WSi<sub>x</sub> bilayer gates," *Electron. Lett.* **32**, 70 (1996).