A MICROPROCESSOR SAMPLED DATA

PROCESS CONTROLLER

T. A. Seim

Pacific Northwest Laboratories

Richland, Washington 99352

NOVEMBER 1973

Prepared for the U.S. Atomic Energy

Commission under Contract AT(45-1):1830

## NOTICE

The report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Atomic Energy Commission, nor any of their employees nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

PACIFIC NORTHWEST LABORATORY

operated by

BATTELLE

for the

U.S. ATOMIC ENERGY COMMISSION

Under Contract AT(45-1)-1830

Printed in the United States of America

Available from

National Technical Information Service

U.S. Department of Commerce

5285 Port Royal Road

Springfield, Virginia 22151

Price: Printed Copy \$5.45, Microfiche \$1.45

BNWL-1795

3 3679 00062 3001

A MICROPROCESSOR SAMPLED DATA

PROCESS CONTROLLER

by

T. A. Seim

November 1973

BATTELLE

PACIFIC NORTHWEST LABORATORIES

RICHLAND, WASHINGTON

A MICROPROCESSOR SAMPLED DATA

PROCESS CONTROLLER

ABSTRACT

A micro-miniaturized digital processor was utilized in the development of a sampled data process controller. While general purpose in nature, the processor was applied specifically to control temperature. Physically the processor was found to be well suited for industrial environments, as its relatively slow speed and high switching voltage levels made it exceptionally noise immune. Successful application was found to be more dependent on external software development support than anything else. This is because of the very limited nature of the processor in terms of memory and input-output peripherals.

SUMMARY

This report documents the application of an Intel MCS-8 microprocessor to sampled data process control. Microprocessors are small scale digital processors which offer low cost, small size, and high reliability to areas such as process control. The programming and application of microprocessors, however, present problems much different than those associated with minicomputer applications. Hence a major portion of the development was expended solving these problems, most of which centered around software development. It was concluded that software could only be conveniently and inexpensively developed with the use of a larger computer system.

The MCS-8 was found to be a highly reliable unit, and considerably more immune to electrical noise than conventional digital logic. This is due in part to its p-channel MOS construction, and in part to its relatively slow execution speed (higher speed logic is inherently more susceptible to electrical noise).

Because of the low cost of microprocessors, many new application areas will become feasible. But this depends directly on minimizing other development costs as well, notably software development costs. The potential impact of microprocessors on technology and productivity is tremendous if the application problems are known and understood.

CONTENTS

|                                           |    |

|-------------------------------------------|----|

| SUMMARY . . . . .                         | i  |

| ILLUSTRATIONS . . . . .                   | ii |

| INTRODUCTION . . . . .                    | 1  |

| Application Description . . . . .         | 1  |

| Feasibility . . . . .                     | 2  |

| Sampled Data Control Systems . . . . .    | 4  |

| Feedback Control . . . . .                | 5  |

| Development Sequence . . . . .            | 6  |

| CONCLUSIONS AND RECOMMENDATIONS . . . . . | 9  |

| Reliability . . . . .                     | 9  |

| Other Processors . . . . .                | 10 |

| Cost Reduction . . . . .                  | 11 |

| Packaging . . . . .                       | 13 |

| INSTALLATION . . . . .                    | 14 |

| Controller . . . . .                      | 14 |

| Cables . . . . .                          | 14 |

| Stepping Motor . . . . .                  | 14 |

| OPERATING INSTRUCTIONS . . . . .          | 17 |

| Normal Operation . . . . .                | 17 |

| Adjustments . . . . .                     | 17 |

| Control Response Adjustments . . . . .    | 17 |

| Proportional Gain. . . . .                | 19 |

| Integral Gain . . . . .                   | 19 |

| Differential Gain. . . . .                | 20 |

| MAINTENANCE. . . . .                      | 22 |

| Digital Process Simulator . . . . .       | 22 |

| Test Programs . . . . .                   | 22 |

| Calibration . . . . .                     | 27 |

| Oscilloscope Waveforms . . . . .          | 28 |

| Maintaining the Processor . . . . .       | 29 |

| Single Stepping . . . . .                 | 30 |

| ODT . . . . .                             | 30 |

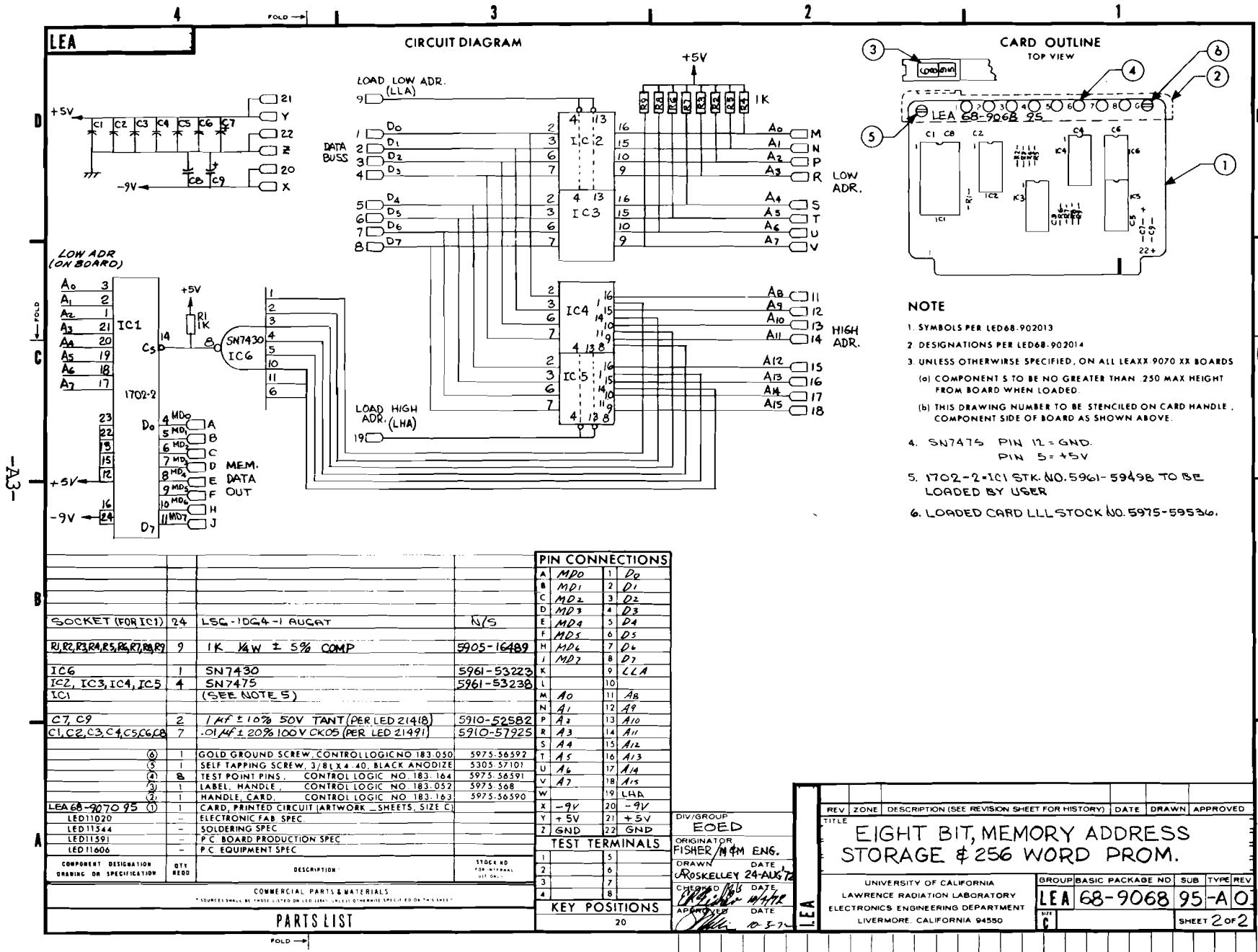

| Memory . . . . .                          | 31 |

## CONTENTS (continued)

|                                    |    |

|------------------------------------|----|

| SOFTWARE . . . . .                 | 34 |

| Octal Debug Technique . . . . .    | 36 |

| MCS-8 Instruction Set . . . . .    | 38 |

| Control Program . . . . .          | 39 |

| Digital Filter. . . . .            | 41 |

| Multiple Precision Data . . . . .  | 43 |

| Control Algorithm . . . . .        | 44 |

| Sequential Control . . . . .       | 46 |

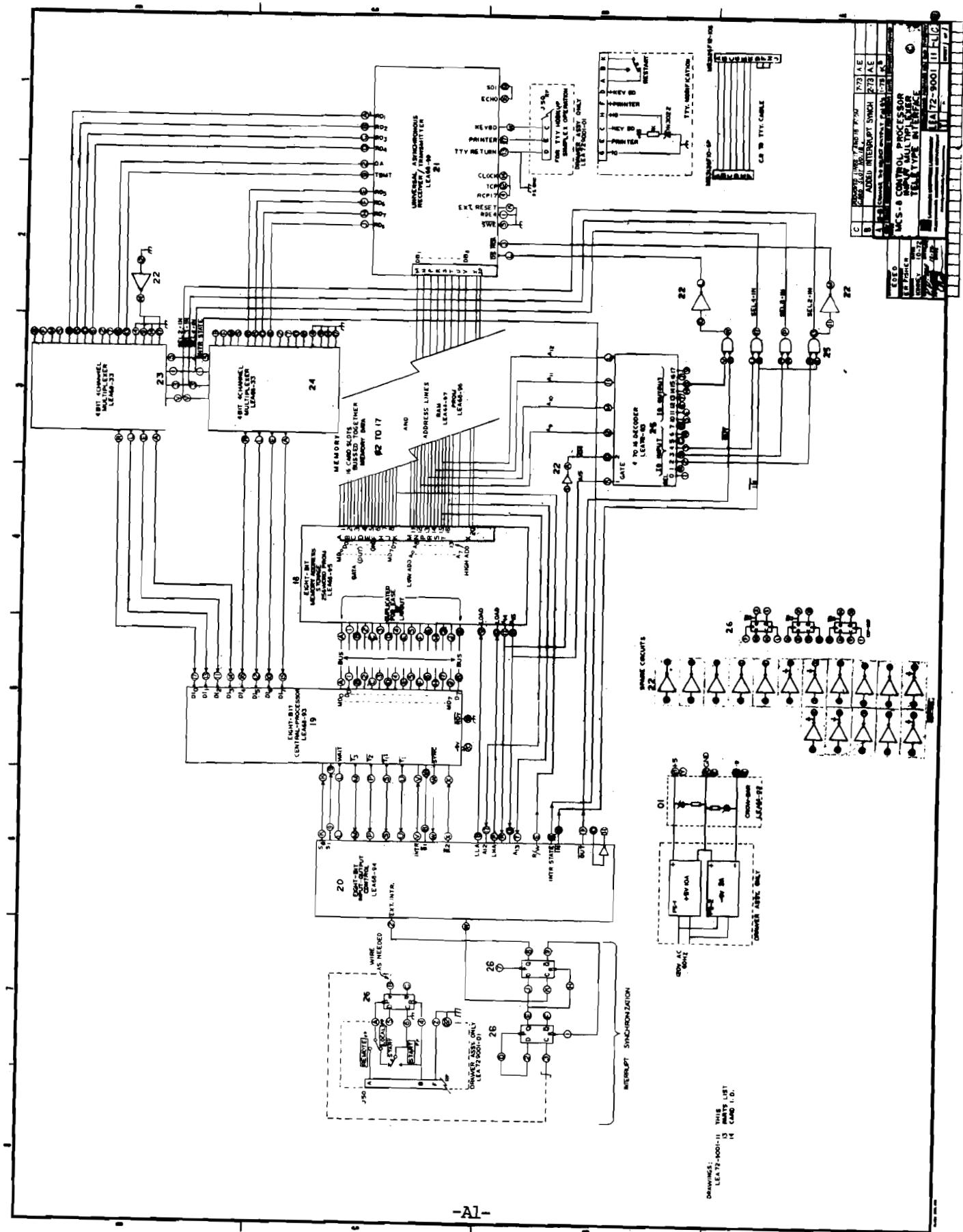

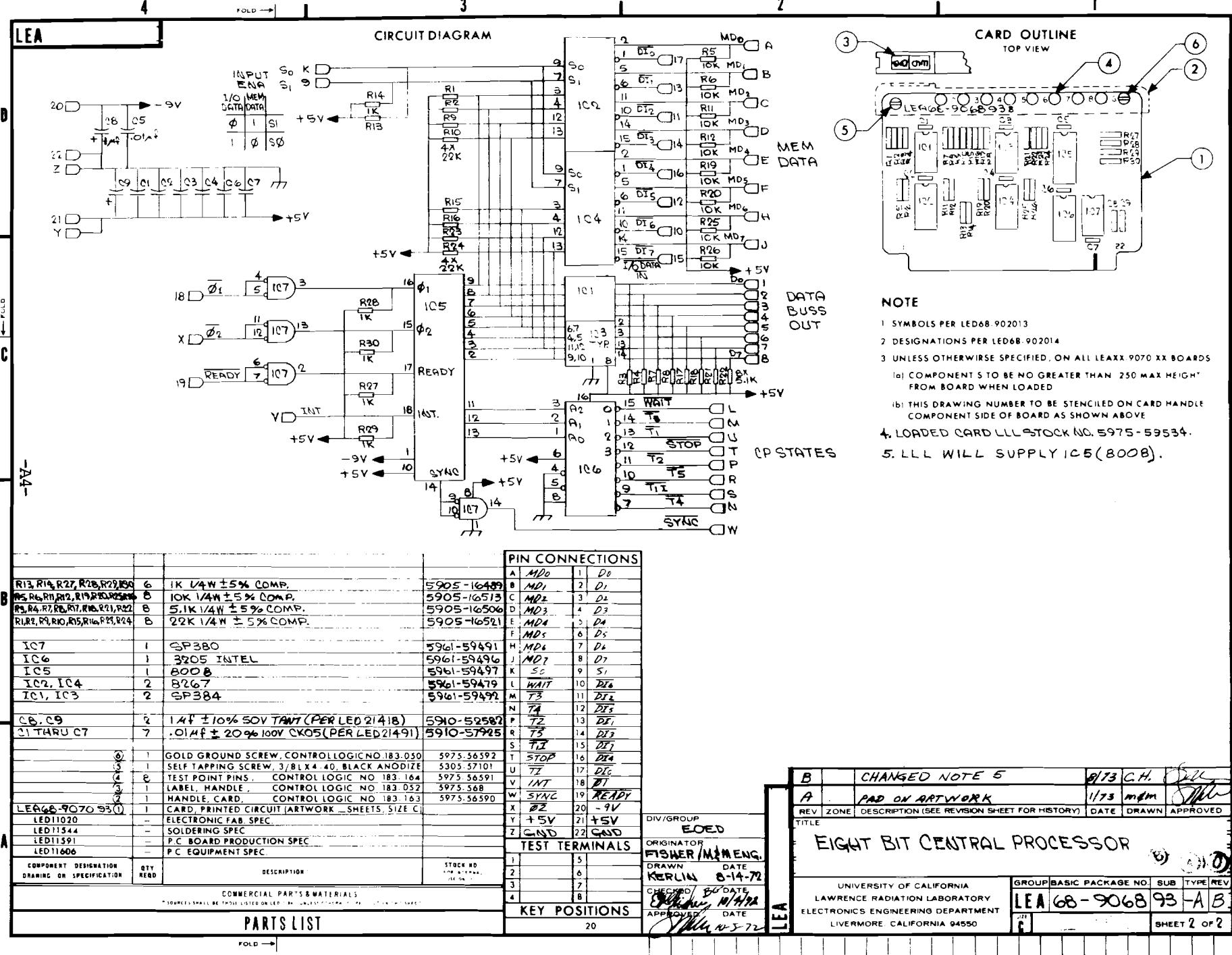

| THEORY OF OPERATION . . . . .      | 48 |

| Intel Micro Computer Set . . . . . | 48 |

| MCS-4 . . . . .                    | 48 |

| MCS-8 . . . . .                    | 51 |

| MCS-8 Basic System . . . . .       | 58 |

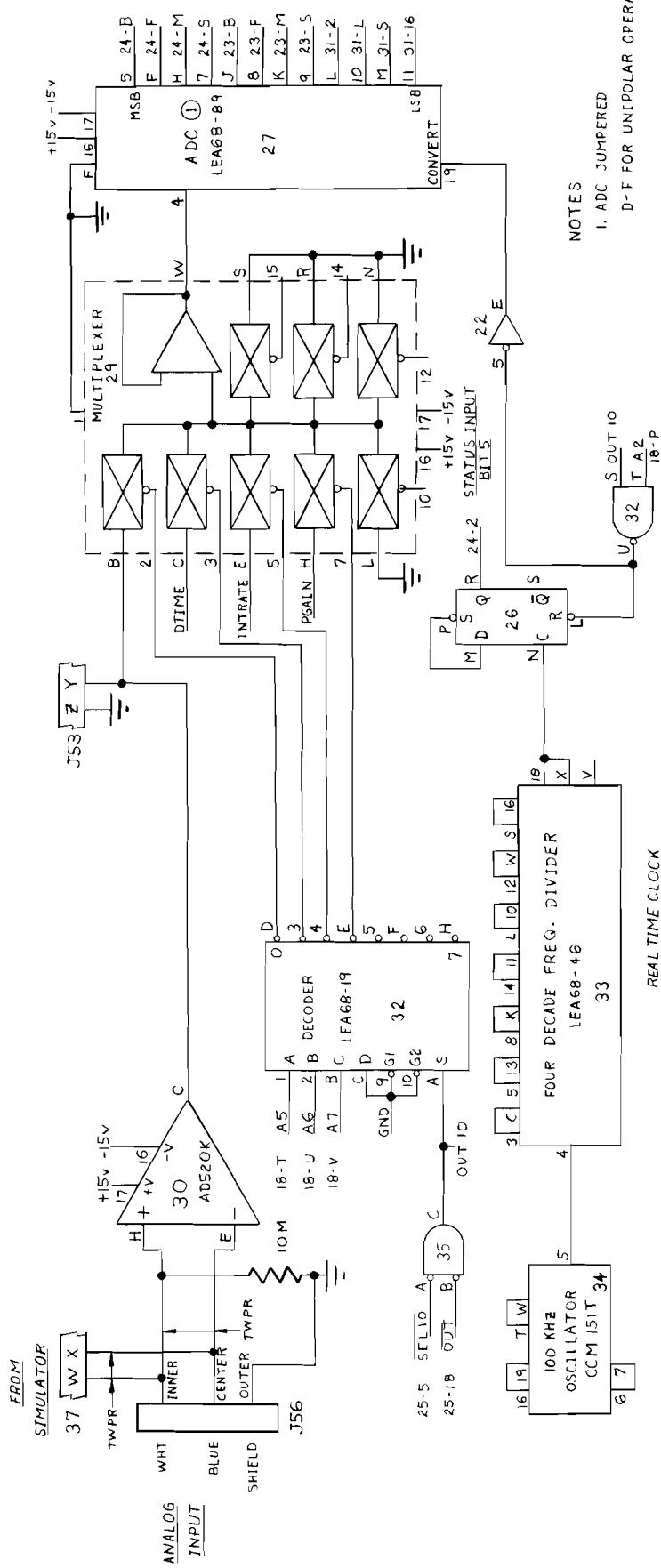

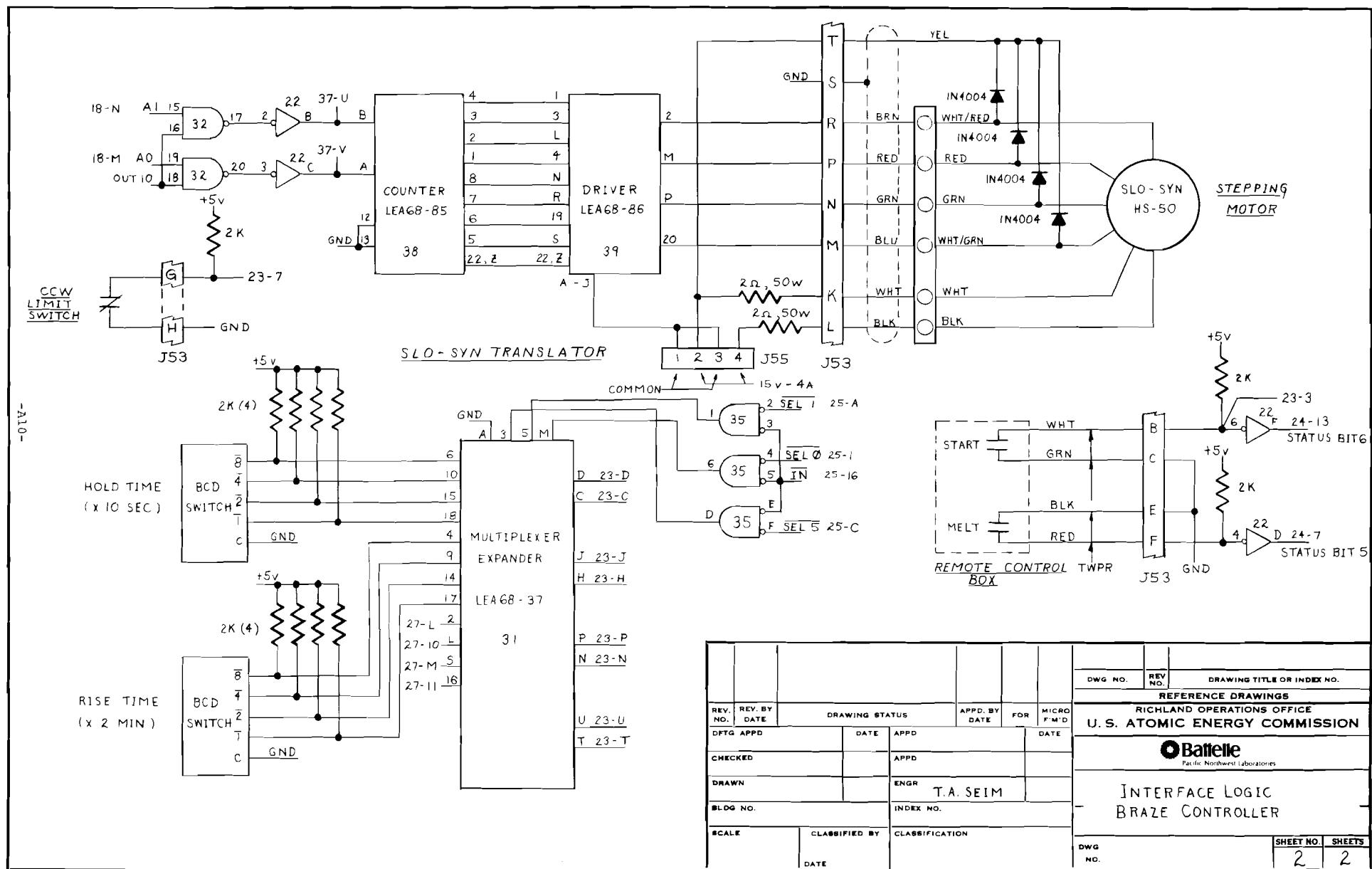

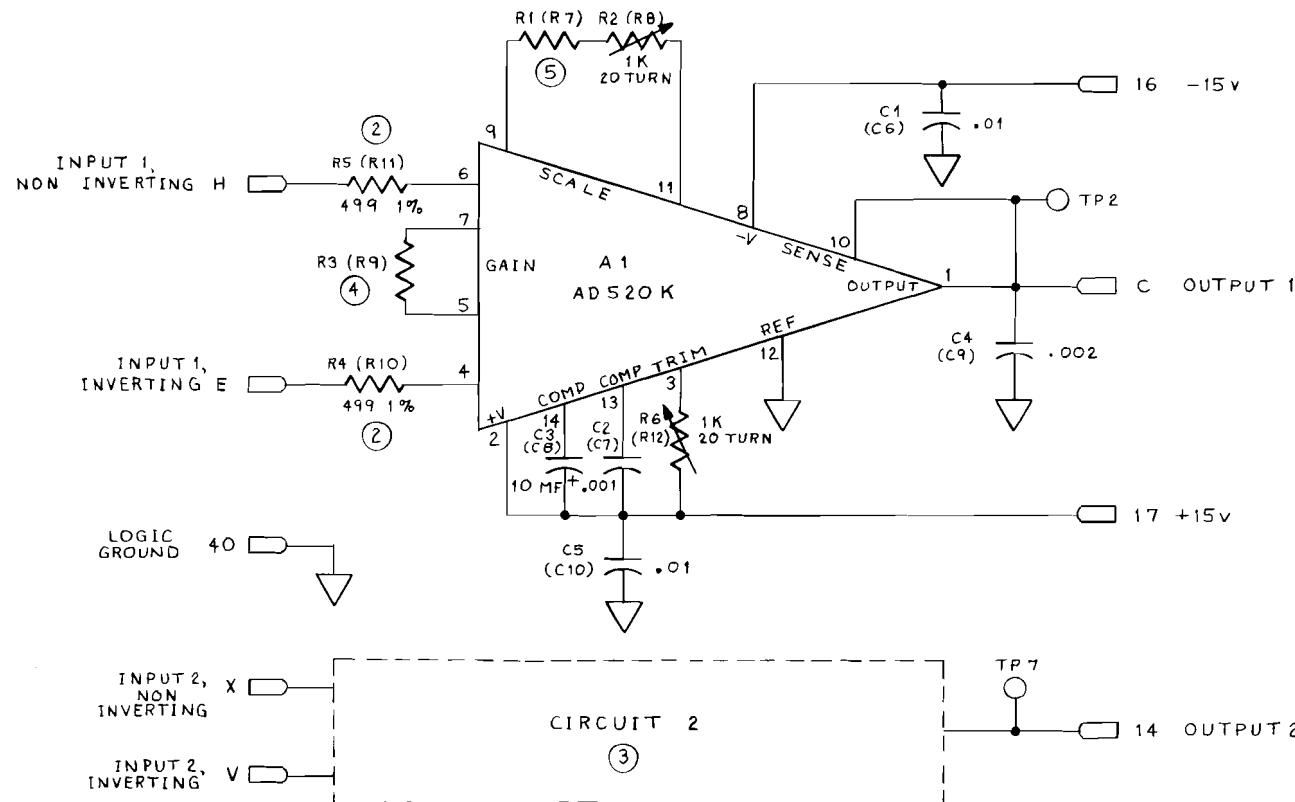

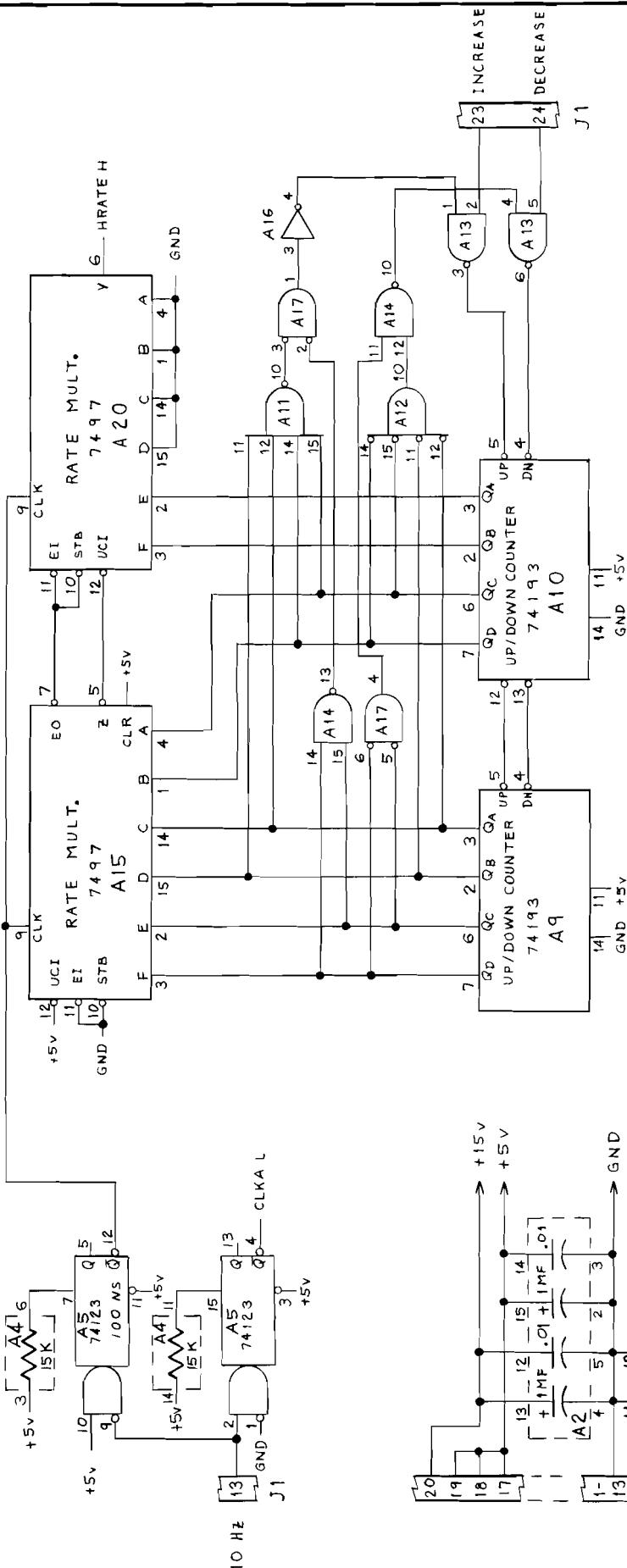

| Interface Logic . . . . .          | 60 |

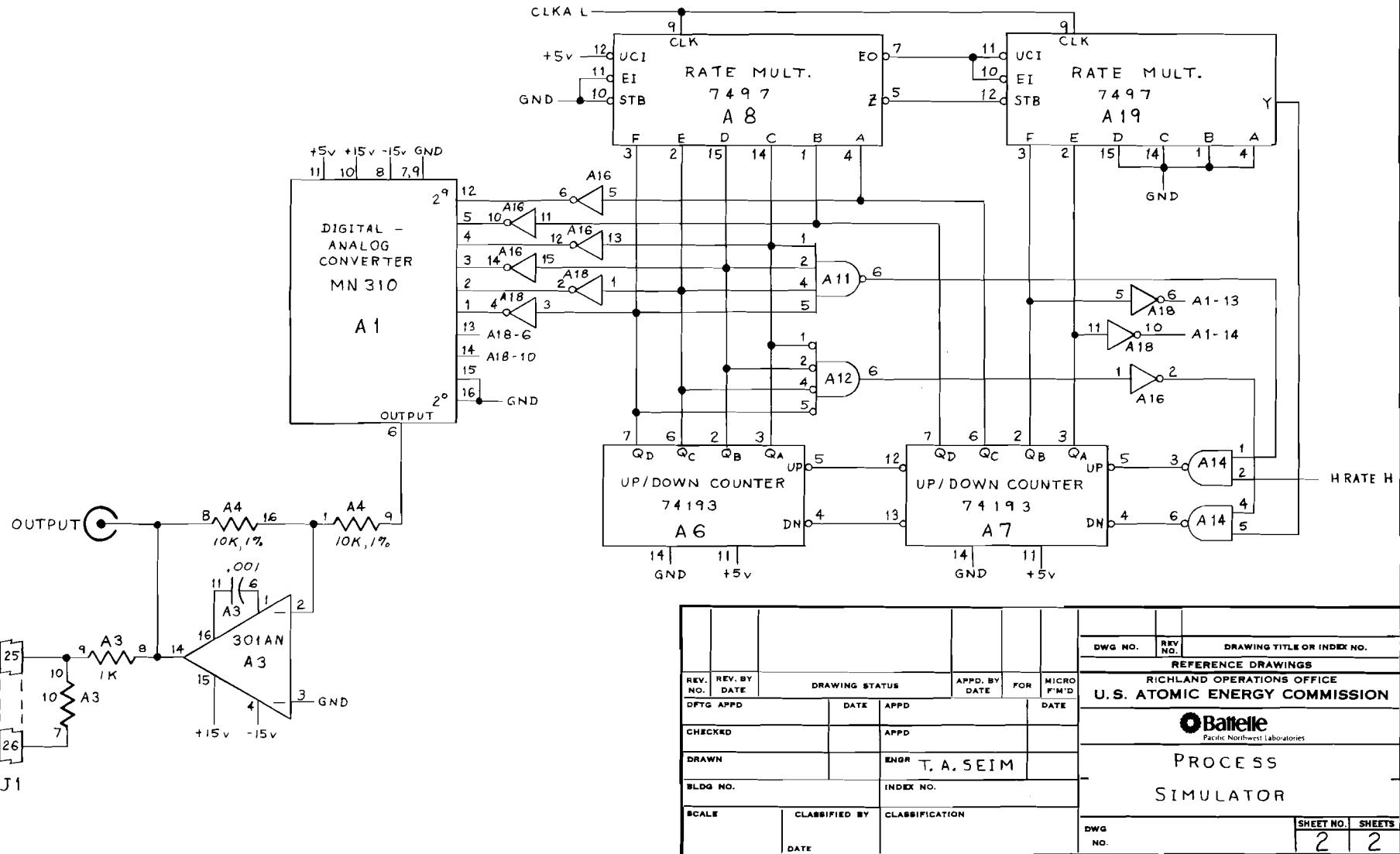

| Digital Simulator . . . . .        | 65 |

| ACKNOWLEDGMENT . . . . .           | 67 |

| BIBLIOGRAPHY . . . . .             | 68 |

| APPENDIX A - WIRING SCHEMATICS     |    |

| APPENDIX B - FABRICATION DOCUMENTS |    |

| APPENDIX C - PROGRAM LISTINGS      |    |

| APPENDIX D - CALIBRATION TABLE     |    |

ILLUSTRATIONS

| <u>Figure</u> | <u>Title</u>                                              |    |

|---------------|-----------------------------------------------------------|----|

| 1             | Signal sampling . . . . .                                 | 4  |

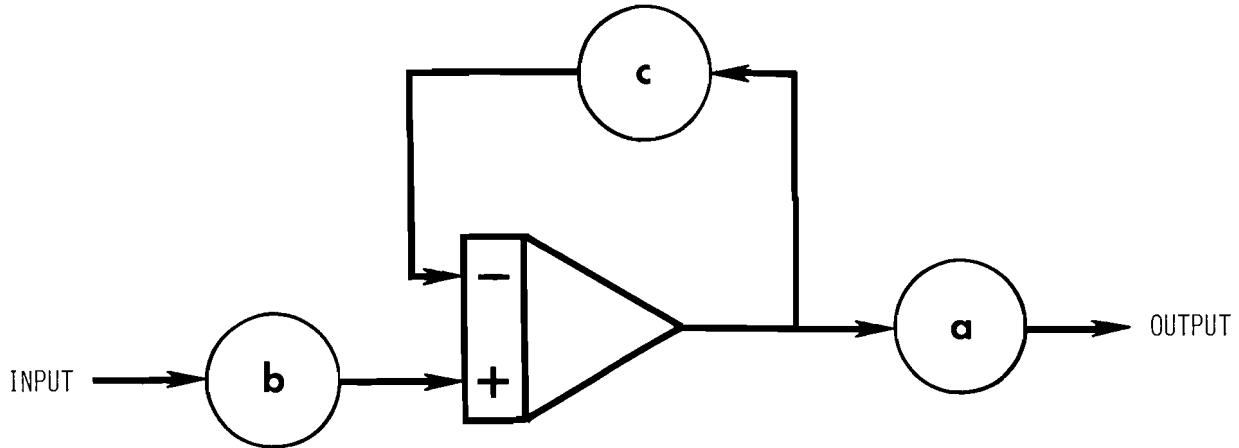

| 2             | Single loop feedback control. . . . .                     | 5  |

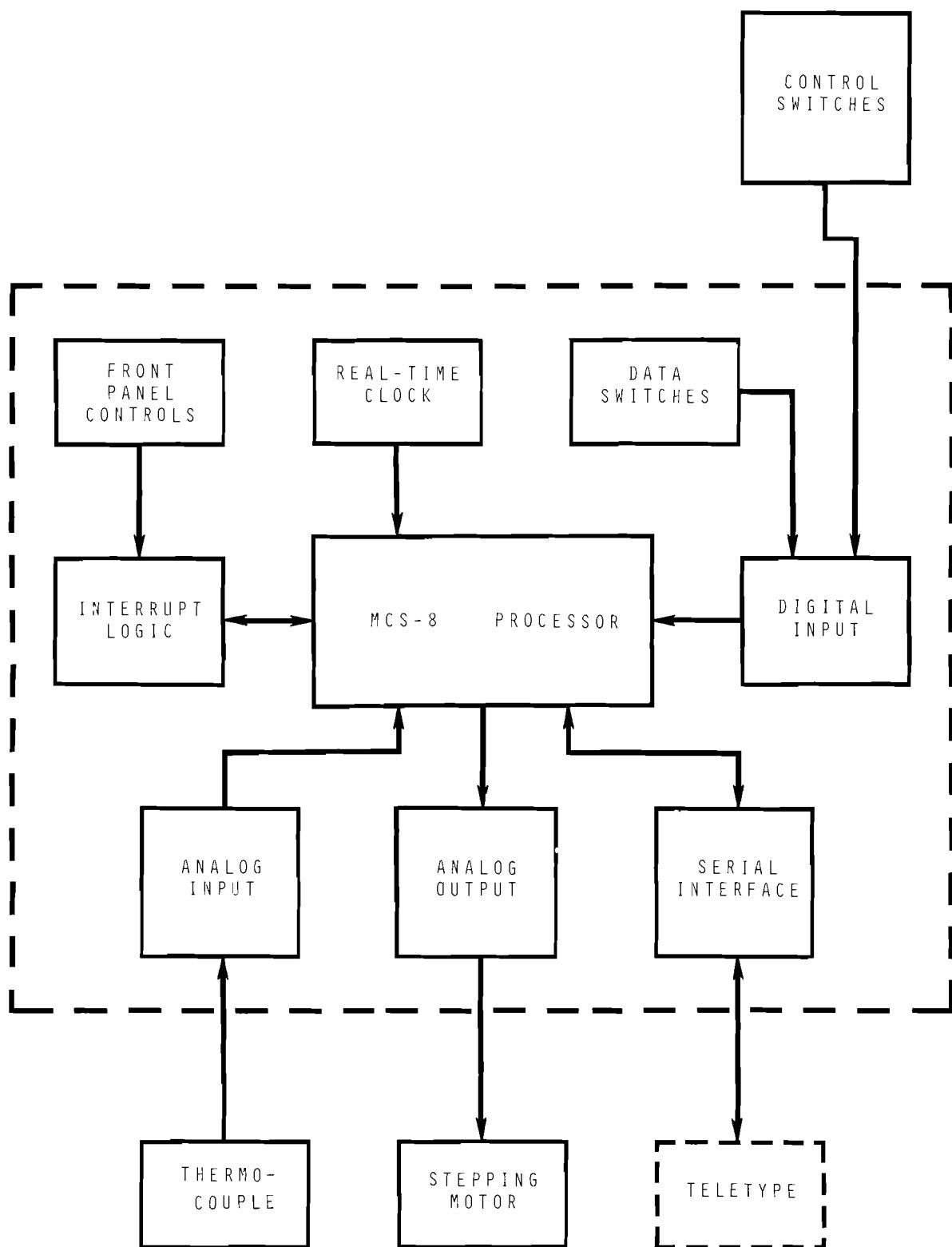

| 3             | Control system block diagram. . . . .                     | 6  |

| 4             | Prototype braze controller . . . . .                      | 8  |

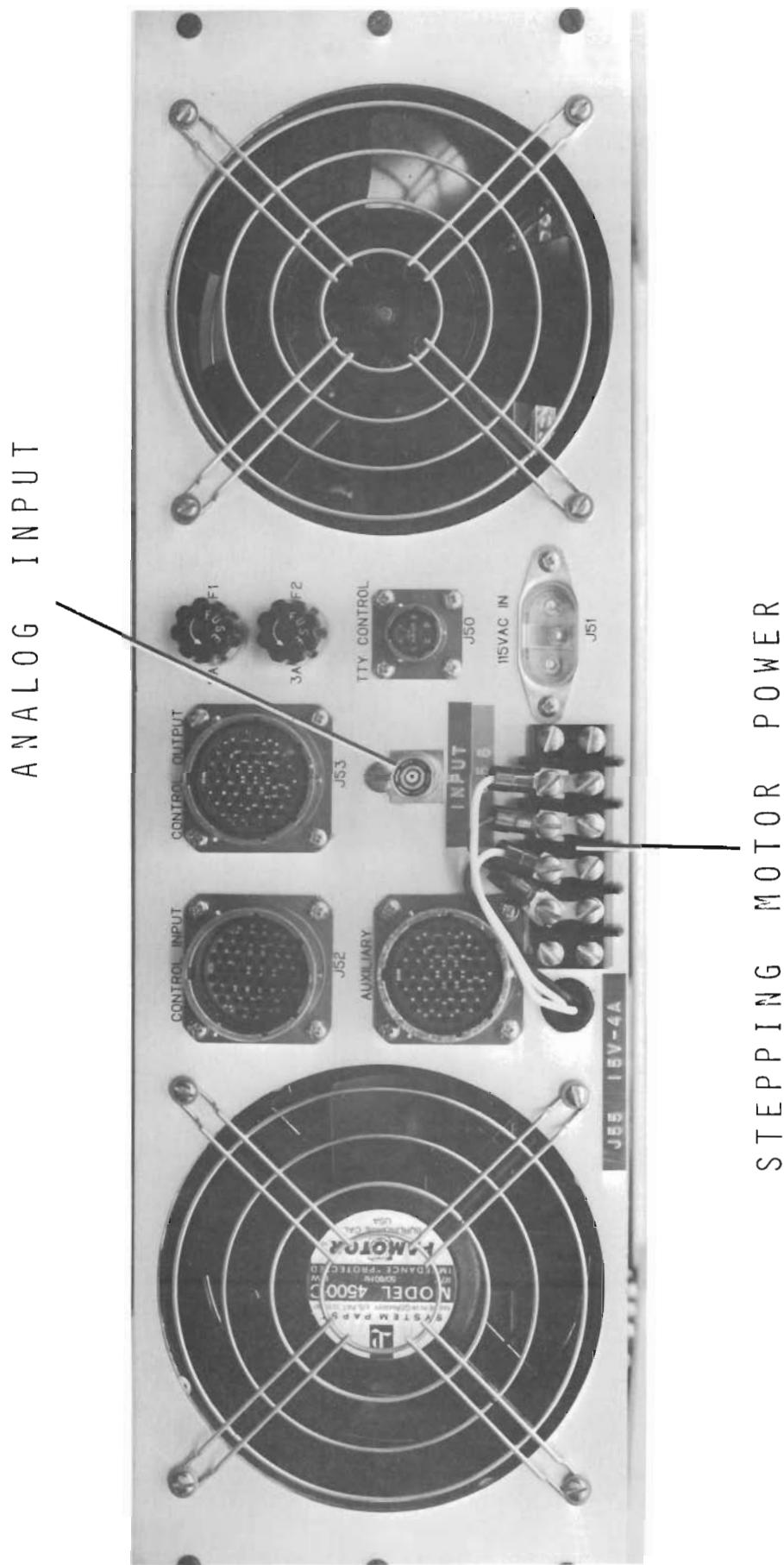

| 5             | Input/output connectors . . . . .                         | 15 |

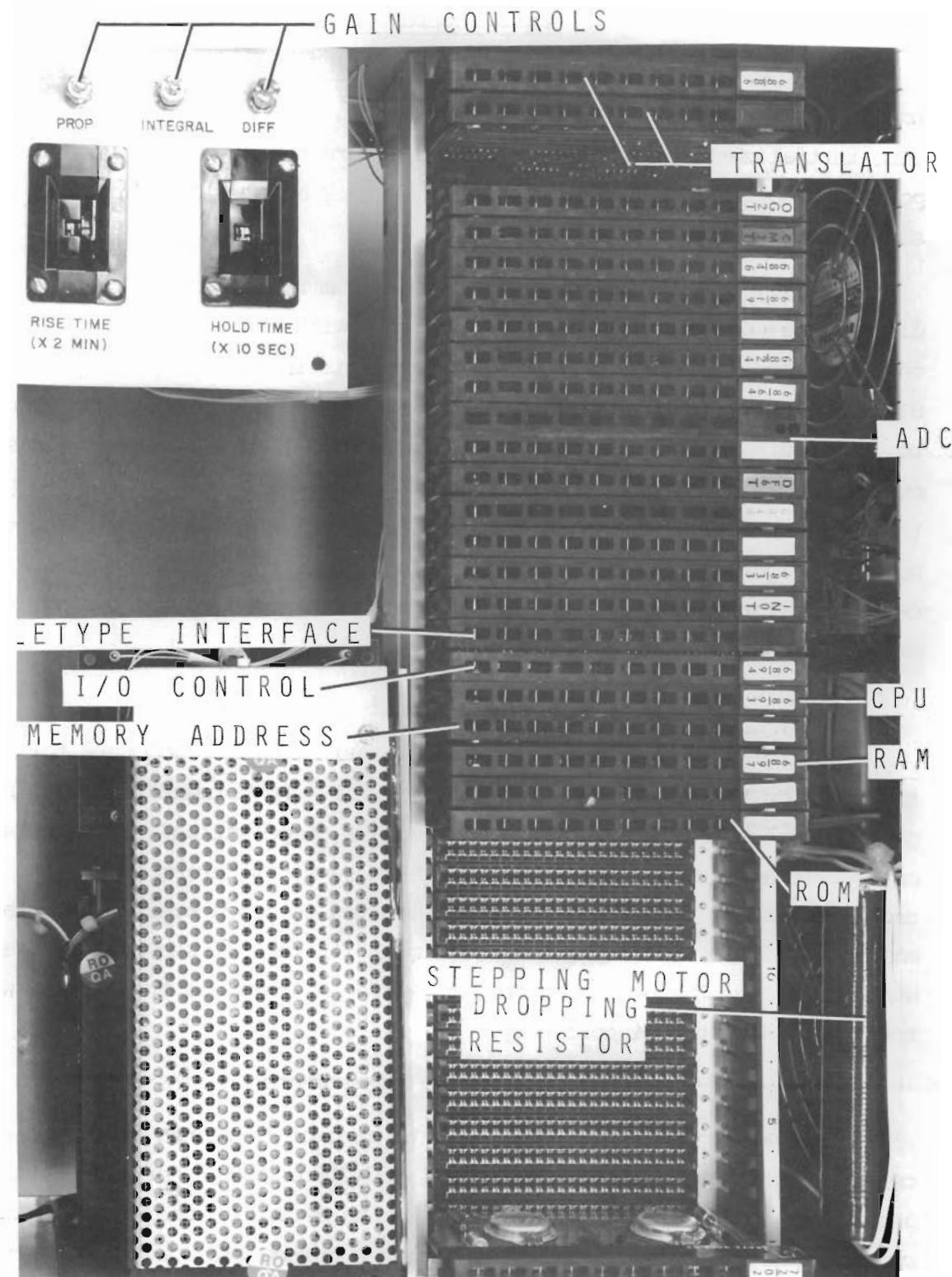

| 6             | Controller internal view. . . . .                         | 18 |

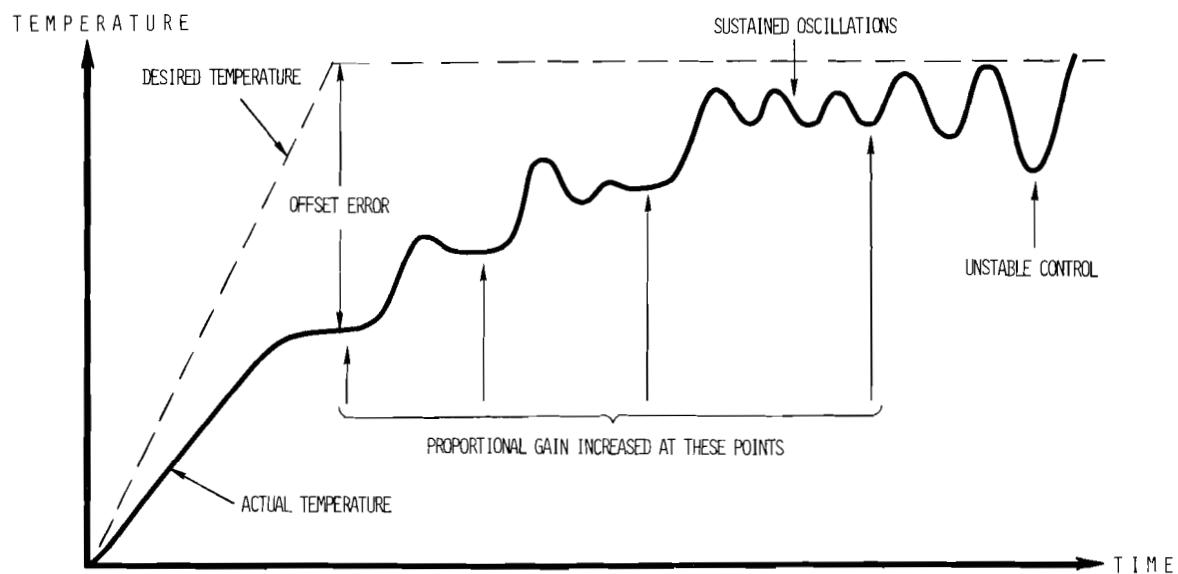

| 7             | Effects of various proportional gain settings . . . . .   | 21 |

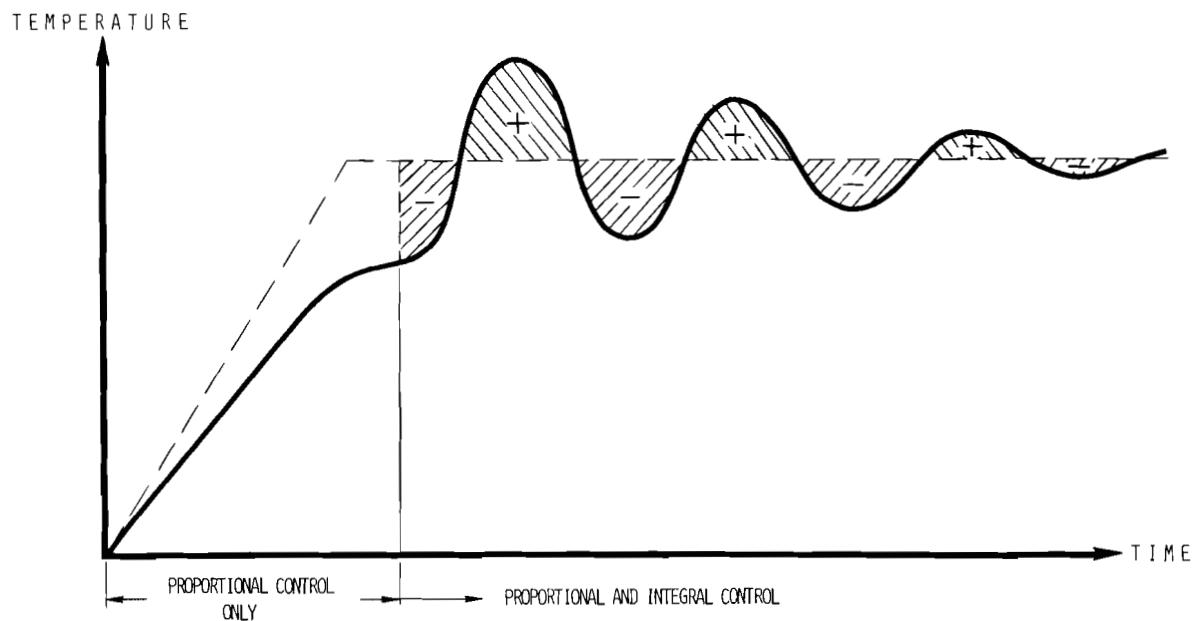

| 8             | Adjusting integral control . . . . .                      | 21 |

| 9             | Process simulator connected to the controller . . . . .   | 23 |

| 10            | Process simulator . . . . .                               | 24 |

| 11            | Controller setup for maintenance and calibration. . . . . | 25 |

| 12            | Real time clock waveforms . . . . .                       | 28 |

| 13            | Data multiplexer waveforms . . . . .                      | 29 |

| 14            | Quantization error . . . . .                              | 41 |

| 15            | 4004 CPU block diagram . . . . .                          | 50 |

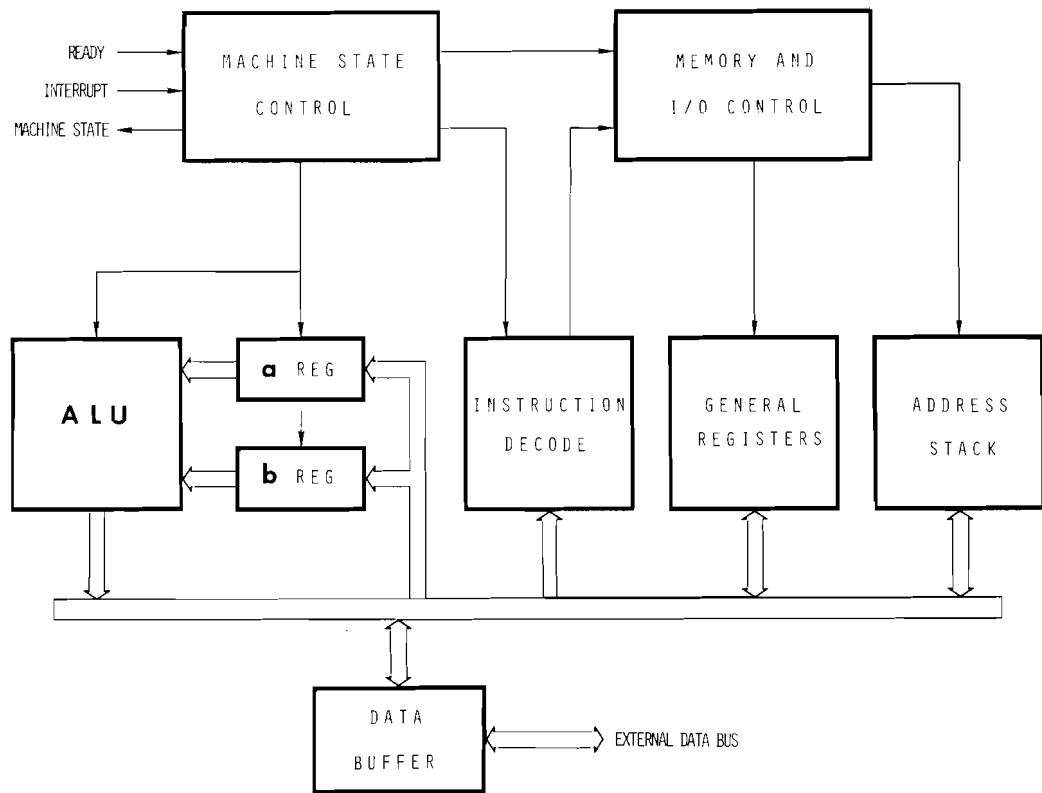

| 16            | 8008 CPU block diagram . . . . .                          | 53 |

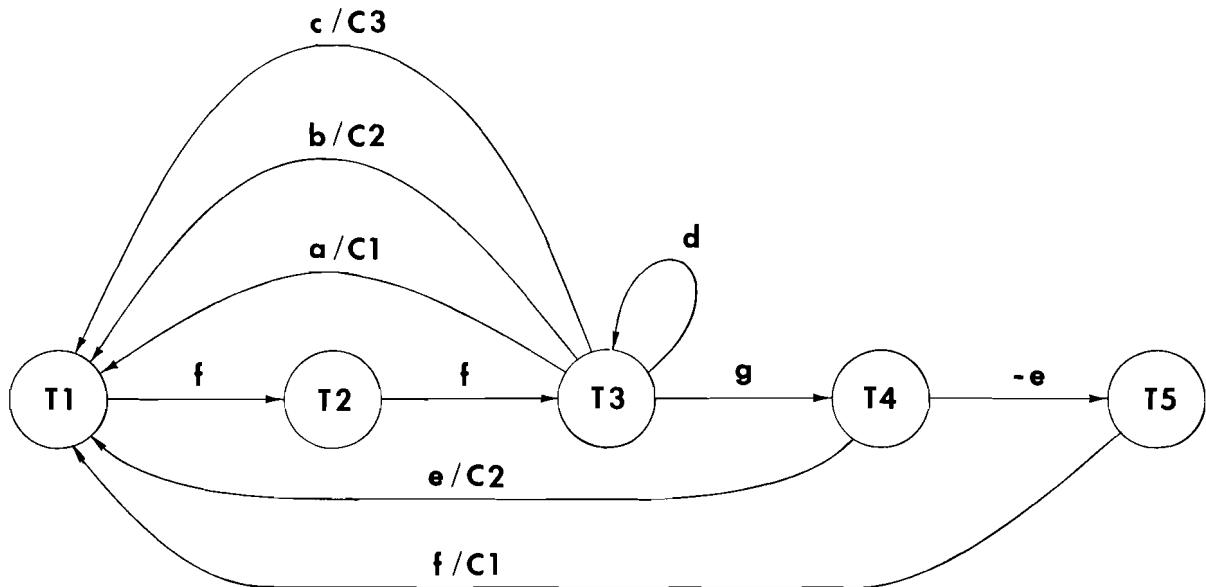

| 17            | MCS-8 state diagram . . . . .                             | 54 |

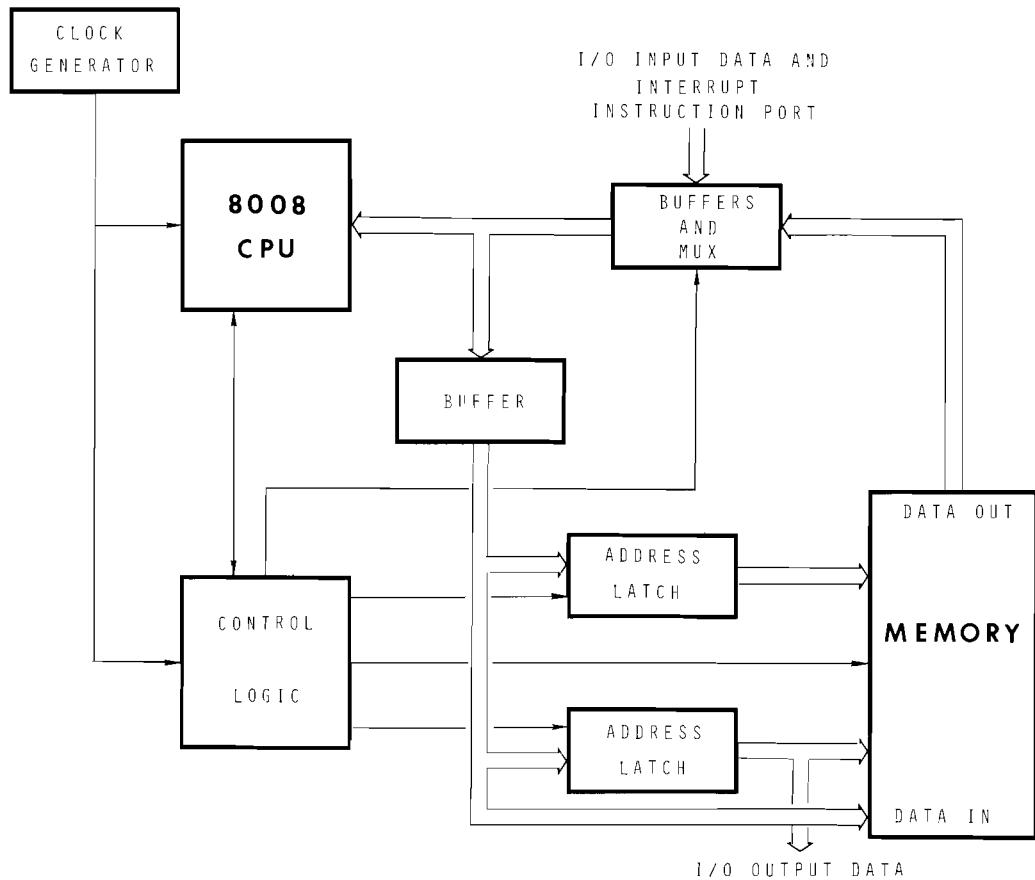

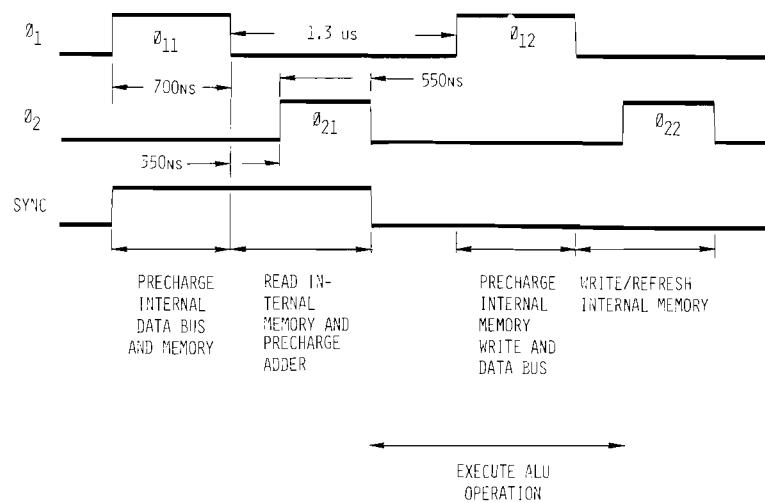

| 18            | MCS-8 system block diagram . . . . .                      | 59 |

| 19            | Clock timing diagram. . . . .                             | 59 |

| 20            | Detailed control system block diagram . . . . .           | 61 |

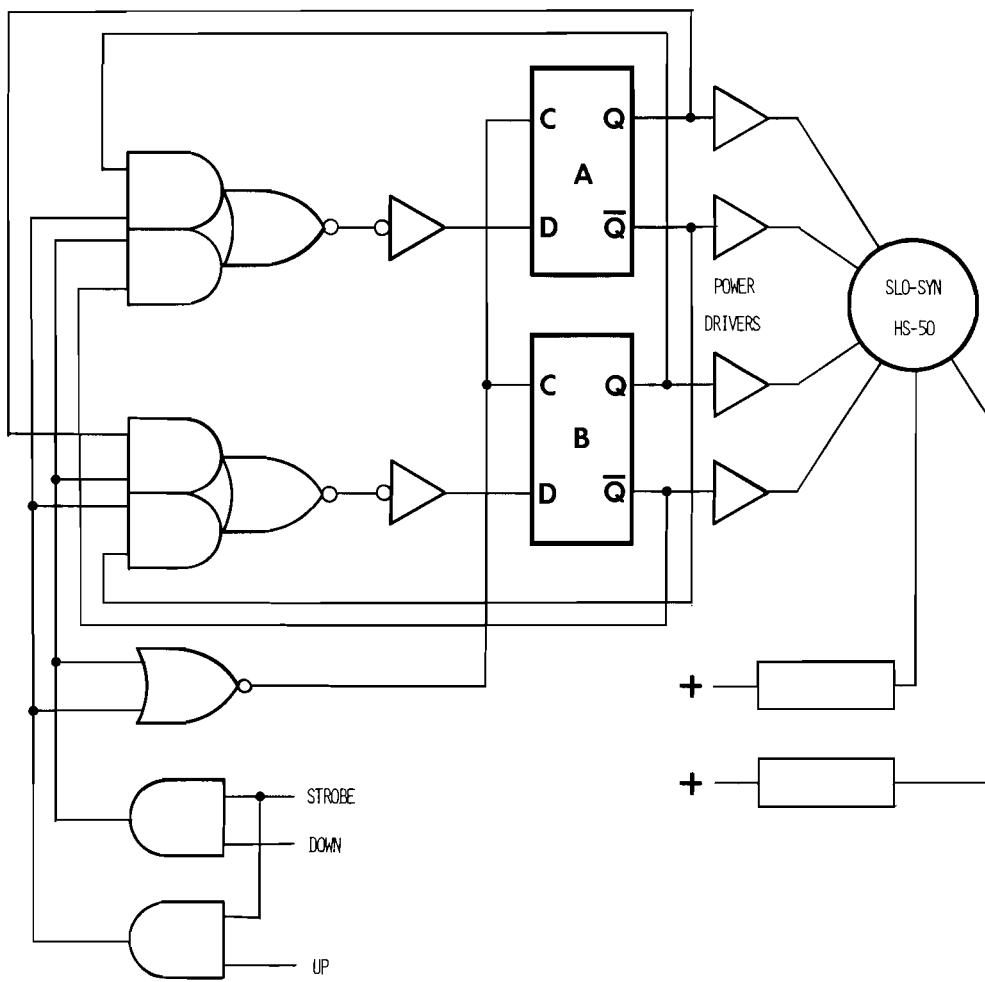

| 21            | Stepping motor translator . . . . .                       | 63 |

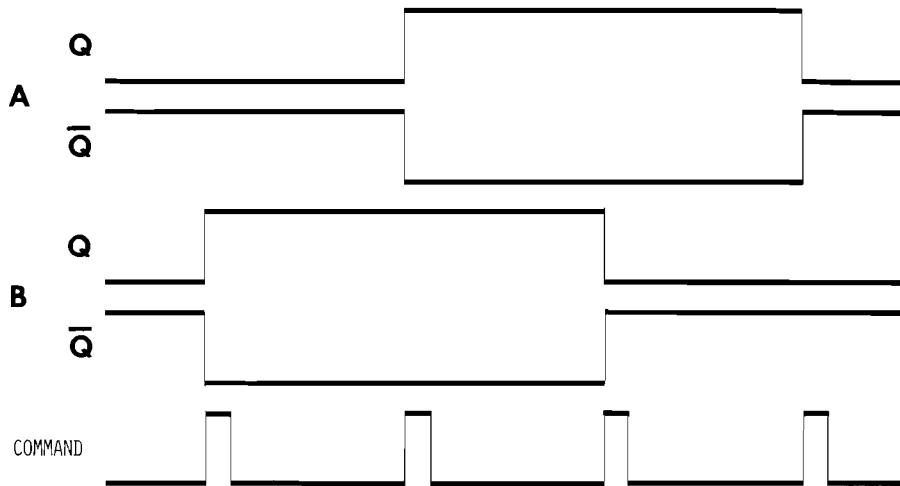

| 22            | Translator output . . . . .                               | 64 |

| 23            | Block diagram of the digital simulator . . . . .          | 66 |

A MICROPROCESSOR SAMPLED DATA

PROCESS CONTROLLER

INTRODUCTION

Under initial funding from Lawrence Livermore Laboratory, Livermore, California, and later by funding from Dow Chemical, Rocky Flats Division, Golden, Colorado, Battelle was directed to undertake two tasks. First, establish the feasibility of using large scale integrated (LSI) circuit computers known as *microprocessors* in industrial environments; and secondly to implement a digital brazing process controller with a microprocessor. This report is concerned primarily with the later task, but discusses topics of the former where pertinent.

Application Description

The wider goal, of which this development was a part, was to upgrade the performance of a brazing process and minimize uncertainties of the joint parameters. This, in turn, would reduce rejects and improve component reliability, and would ease the problems of a component failure analysis.

The braze is done under high vacuum, with heat applied by an inductively coupled coil. The coil is fed by a three phase motor-generator. Heating energy is controlled by the voltage applied to the generator's primary winding. Presently the brazing temperature is uncontrolled, and its rise time varies from part to part, depending upon the degree of coupling between the heating coil and the part. Also the temperature rise, or overshoot, after the braze occurs is unknown. The object of closed loop control is to have repeatable rise time and minimal overshoot. It was also specified that a post-braze temperature hold be maintained for a selectable period of time.

During discussions of this problem at Battelle in March of 1972 it was agreed that a small digital processor with its control program stored in an unchangeable type of media, termed a *read only memory* (ROM)<sup>1</sup>, would satisfy the requirements of the controller for the brazing process. Recent semiconductor developments had made available a digital processing unit in a single integrated circuit (IC), which was ideal for the processor required by the controller. From this base a controller was developed using the microprocessor and analog input and output subsystems. The use of ROM for program storage eliminated the problems of alteration caused by electro-magnetic interference (EMI).<sup>2</sup>

#### Feasibility

The use of microprocessors in industrial applications have been demonstrated to be a viable alternative to conventional control techniques. They offer improvements in reliability, capability, and cost. Further, such advantages as vastly simplified maintenance techniques (the "throw-away" philosophy) will minimize the necessity of employing skilled technicians to keep this equipment in operating order, which is especially inviting at a time when skilled labor is becoming increasingly scarce. But this is the positive outlook, the negative aspects include the fact that digital processors are high technology devices, and require at least an acquaintance with the numerous technologies they touch on. The difficulty is that many of these areas are simply out of the realm of the average control engineer. In other words, some education and re-orientation of one's thinking are in order. For instance, the idea that reliability is a function of the switching function complexity (i.e. the number of relay contacts) does not hold for microprocessors, where reliability is more a function of the number of interconnections. As the complexity of the

1. *The actual memory used could not only be programmed, but could also be erased and reprogrammed indefinitely. It was read only, or unchangeable, in the sense that this operation could not be done under program control, but took a special programming device which applied programming pulses unavailable to the processor.*

2. *Some programmable controllers used core memory for program storage, and had problems because of EMI.*

individual circuits increase the number of interconnections drop significantly, thus yielding a considerable reliability increase.

Obsolescence of the controller is minimized by (a) the universality of the control element, and (b) the ability of the unit to be reprogrammed. The latter feature is especially important with an in-place process which must be updated to some new specifications. Redesign of an existing relay control panel is a costly and time-consuming task, but the alteration of a control program is a far less formidable undertaking. Testimony to this observation is readily available from numerous special purpose controllers now obsolete, while computers procured at the same time are still performing valuable functions.

Apparent contradictions will be the order of the day for some time for those recently introduced to this area. The initial impression one has of microprocessors is that of unbridled complexity. Yet microprocessors represent simplicity itself. Instead of being confronted with a bewildering array of semi-compatible control elements the microprocessor represents a definite move toward standardization. Instead of hundreds or thousands of unique components a control function can be performed by single component, the digital processor. Many functions can be executed by one processor, whose particular character is governed by the control program.

The control engineer who is unacquainted with computer technology is not the only one caught in the tides of change. Engineers already associated with computer applications must accept some radically different theorems of use ("rules of thumb") concerning microprocessors. For the most part the central processor was treated as a scarce resource which must be utilized to the utmost. This is direct result of the cost of the processor and its associated peripherals. Consequently much effort has been expended to make programs as efficient as possible, and to maximize the number of functions performed by the processor (the most irritating sight a programmer can see is a computer which is not being used). This concept is being invalidated by the microprocessor, whose cost is becoming

an insignificant factor. In other words the processor has changed from a scarce resource to an overabundant resource, which can be used almost at will. The impact of this new factor alone is so immense as to defy full consideration.

If the processor is no longer the scarce resource, what is? Unquestionably this is in the domain of invested man-time, which continues to rise and is accelerated by the rapidly changing technology. If savings are to be realized it will be by minimizing the invested man time in each application. Specific recommendations will be made as how to fully use microprocessors, while minimizing the investment in both man-time and equipment. But it must be expected that a greater development of capabilities is required than, say, relay controller design. It is only through the availability of powerful development tools that the full advantage of microprocessors can be gained.

#### Sampled Data Control Systems

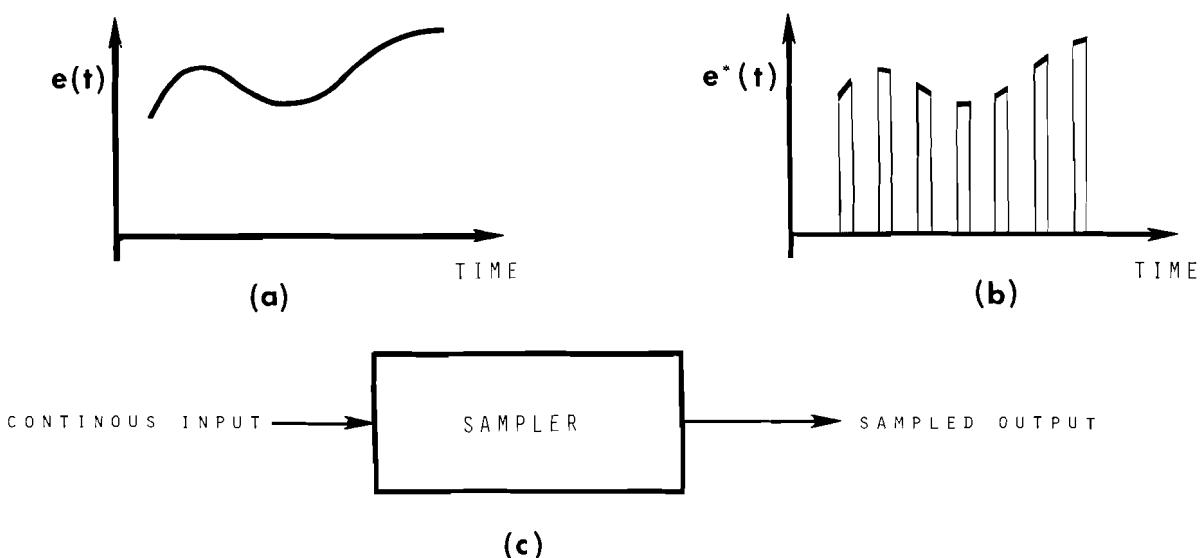

Originally sampled data control systems implied the existence of a sampler in what was otherwise a continuous system. The sampler would measure a continuous signal at discrete points in time for short intervals, thereby approximating the input with a pulse train similar to Fig. 1.

FIGURE 1. *Signal sampling*

While sampled data control systems still are used which contain continuous type components this term is more often applied to digital control systems which, by the very nature, are discrete. Indeed, it was the advent of practical digital control systems that motivated the theoretical development of sampled data control.

Unfortunately until very recently the cost and reliability of a completely digital system had a hard time competing directly with analog controllers economically. The prime use of computers was not in the control loops, but in a supervisory role performing functions which simply could not be done with analog techniques. Now, however, the economics of LSI make it feasible for general digital controllers to compete directly with their analog counterparts, almost on a loop-for-loop basis.

#### Feedback Control

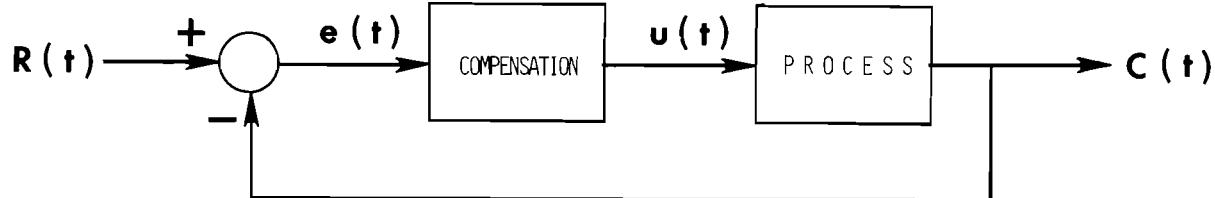

The initial goal was to implement a single feedback control loop as diagrammed in Fig. 2.

FIGURE 2. Single loop feedback control

The target, or desired control point is  $R(t)$ , while  $C(t)$  is the actual process output, in this case temperature. Their difference, the control error  $e(t)$ , is what the controller uses to compute the control action,  $U(t)$ .

As the time functional notation suggests  $R(t)$  is not a constant "setpoint," but is rather a function of time, or a time profile. This allows the temperature to be increased in a controlled manner during a brazing cycle and makes the temperature control more stable.

The feedback control system of Fig. 2 takes on the physical formulation of Fig. 3.

FIGURE 3. Controller internal view

The temperature, which corresponds to  $C(t)$ , is sensed by a thermocouple, and is amplified and converted to digital form by the controller. The control output,  $U(t)$ , is in the form of rotary motion derived from a stepping motor. This is converted to electrical energy by a Variac to ultimately supply power to a heating coil. The independent control variable,  $R(t)$ , is generated internally by the controller from a profile table.

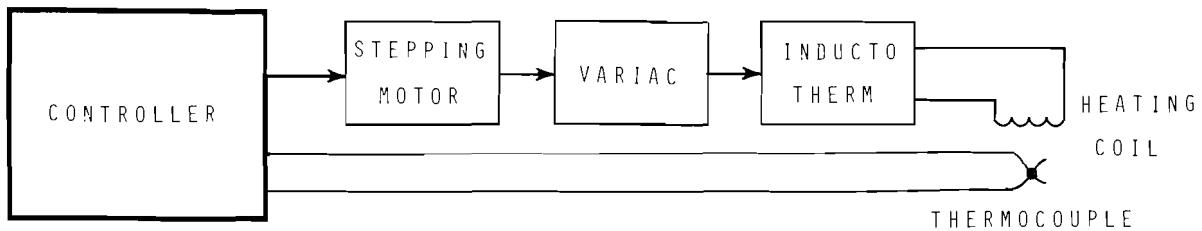

#### Development Sequence

While the end result is most visible in the hardware form the major part of the development effort was in software. This includes not only the control program, but several other programs written for a Battelle-owned SEL 840. The SEL 840 proved to be a convenient vehicle with which to develop the controller software, most of which was designed and operational before any hardware had been received. Part of the SEL 840 software included a simulator for the microprocessor. With this program the SEL 840 simulated the microprocessor in every detail, allowing it to be used to debug software for use on the microprocessor.

Final design of the hardware was not done until the software was completely operational. This resulted in the least number of hardware design changes, and the most efficient software design. Then the hardware was breadboarded using a device designed for this purpose by the manufacturer of the microprocessor. This breadboard was used to find any errors in the control program, and to check out a data link to the SEL 840. This

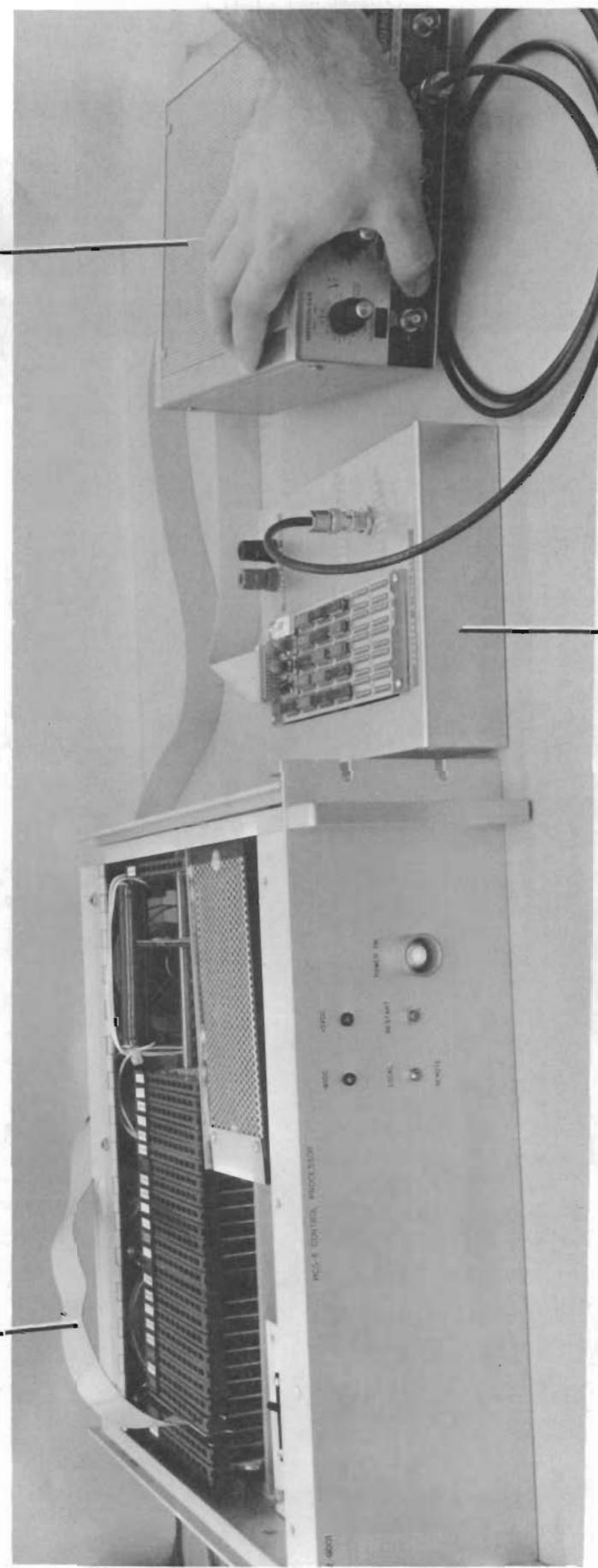

data link was used primarily to load programs into the controller (the programs were stored in volatile memory at this time). Because all of these preparatory steps were taken the main task involved with the prototype were final fabrication details, as most all the design problems had been solved. The prototype controller, remote control box, and stepping motor are pictured in Fig. 4.

FIGURE 4. Prototype braze controller

CONCLUSIONS AND RECOMMENDATIONSReliability

The initial conclusion I have reached based on personal experience with MCS-8 processors at Battelle and other installations is that they are highly reliable and relatively immune to EMI. The only reliability problems I encountered were with the RAM memory units.<sup>1</sup> These exhibited a failure rate which was unusually high (ten percent of exercised units). The sample size, however, was too small (40 IC's) to base a firm judgment on.

The PROM's were never observed to fail when used properly. They are probably a more reliable memory medium than the more common magnetic core memories. The later devices are known to be susceptible to EMI commonly found in industrial environments. The immunity of the PROM's is due to the insulated floating gate on which the data are stored (each integrated circuit has 2048 such gates). This gate is isolated in an extremely high resistance material. Data are stored by avalanche injecting a charge into the gate by relatively high voltage pulses. Since EMI is highly unlikely to duplicate these conditions the only possibility for loss of data is through degradation of the charge stored on the gate by leakage (it can also be erased with a high intensity short wavelength ultraviolet light). This degradation has been measured and found to take years to occur (only about three years data are available, with estimates based on projections past this point). This failure mechanism is considered to be insignificant as annual, or bi-annual, re-programming defeats it.

Reliability of the processor can be further increased by minimizing the digital logic external to the processor. As is explained in the section on the micro computer set, much of this external circuitry is due to the choice of packaging of the MCS-8. The device is pin limited and must multiplex data in and out of the processor. Much of the external circuitry is required to handle this multiplexing.

---

<sup>1</sup> *Volatile storage devices used for storing program variables.*

Other Processors

Intel will soon introduce an improved version of the 8008 processor, numbered 8080, which will eliminate these and other problems with the unit. Furthermore, programs written for the 8008 will run on the 8080 (which is what is called "upwards compatible"). The instruction set will be expanded by about 60 percent more instructions than are available with the 8008, and will execute these instructions several times faster than the 8008.

Future applications should definitely consider other available microprocessors. Currently most semiconductor manufacturers are developing microprocessors, some of which are available. An incomplete list of these companies is:

American Microsystems, Inc.

Computer Automation

Fairchild Semiconductor

National Semiconductor

RCA

Rockwell International

Teledyne

Texas Instruments.

Of these only Computer Automation and Rockwell International have units available, while Teledyne repackages chips manufactured by some other firm (as many as 30 companies are packaging the Intel processors, mostly the MCS-4).

Choice of the processor will increasingly depend less on performance and more on software support. This is a simple result of the generally long time constants found in process control (high performance applications, of course, will be an exception). In other words if a processor can perform a task within specified time constraints the major consideration will be what it costs to build and program it. And since the costs of building the processor are decreasing the major cost will increasingly be programming (high volume applications are the exception here).

Cost Reduction

Software costs can be minimized in at least two ways. The first way is to take advantage of vendor supplied software. This typically consists of programs such as assemblers, compilers, and operating systems. Selection of a processor can in part be based on the software available for it and the cost of that software. Intel offers programs written in Fortran to assemble code for the MCS-8 and simulate the MCS-8, either as an outright sale or from a time sharing service. For us neither of those choices was acceptable due to the high cost. It was more economical to develop the same programs for our own computer system. The reason for that lies in the fact that this type of program, when written in Fortran, becomes machine dependent. The effort involved in adapting the Fortran code for our own system plus the acquisition cost made it more economical to design what we wanted to begin with.

Computer Automation, a minicomputer manufacturer as opposed to a semiconductor manufacturer, based their micro design on a previous minicomputer series. Since the instruction sets were compatible, software developed for the earlier series can be used with the micro series. This presents the tremendous advantage of a large body of existing software. It must be understood that the Computer Automation processor is considerably more powerful than the MCS-8, being comparable to most minicomputers in all respects with the exception of speed. Thus with a reasonable amount of memory (at least 4K words) it is possible to operate an assembler with the unit. The primary disadvantage here is with the lack of high speed peripherals and mass storage. This can be overcome by using it in conjunction with another computer system already possessing those peripherals, communicating by means of a medium speed data link (an asynchronous 9600 baud interface will do nicely).

Another approach to take is to develop a simulator for the target computer, and execute the assembler with simulator on the host computer. This has proven satisfactory in the past, and has the great advantage of not requiring the availability of the target computer. The value of a good simulator, in this and other respects, should not be under-estimated.

Almost all of the software development for this project was done in this fashion, with few changes when run on the actual processor. If this approach had not been taken a delay of between one and two months would have resulted. In addition, program changes can be tested with the simulator before they are installed in the field. If the process operation is critical, or the time to deliver and install a change lengthy, this alone can be justification for the simulator's development.

The other area where software development costs can be saved falls in the category of remote site assistance. Generally the application process will be physically separated from the research and development location, perhaps by thousands of miles. Thus it may be inconvenient, or patently impractical, to make repeated trips to the host computer for program changes and re-assemblies. Yet the use of these facilities is very useful for such purposes as

- Program debug

- Equipment installation

- Program changes

- Process alterations.

The obvious conclusion is some sort of data link between the host computer and the process control site. Where it is infeasible to install a dedicated communications line the telephone lines can be used. This requires a data modulator/demodulator (modem) at each location. The use of switched telephone lines for data transmission involves well known problems. These problems can and have been solved by the use of error checking techniques. The teletype interface can be used to complete the data link from the modem to the MCS-8 processor (the serial data format is compatible with most modems). In this case the Teletype cannot be used while the modem is connected to the processor. A second telephone line would be necessary for the operators at each end to communicate. Another alternative is the addition of an interface dedicated to the modem so that the Teletype would be on-line with the processor while the communications link is established.

The primary use of the data link would be to load programs in writable storage (RAM), but other uses come to mind. For instance, by means of the necessary "operating system" (not to be confused with operating systems developed for larger systems) the system developer could monitor and change program data and parameters during operation. At present this can only be done by stopping the processor and, hence, the process.

Packaging

Packaging and interface hardware can easily dwarf the cost of the microprocessor, its peripheral logic, and memory. And adapting a particular microprocessor to a package configuration consistent with the user's usual electronics packaging can be an expensive proposition. Packaging alone can sway the choice from a lower cost, higher performance processor, merely because the older processor is already available in a desirable package.

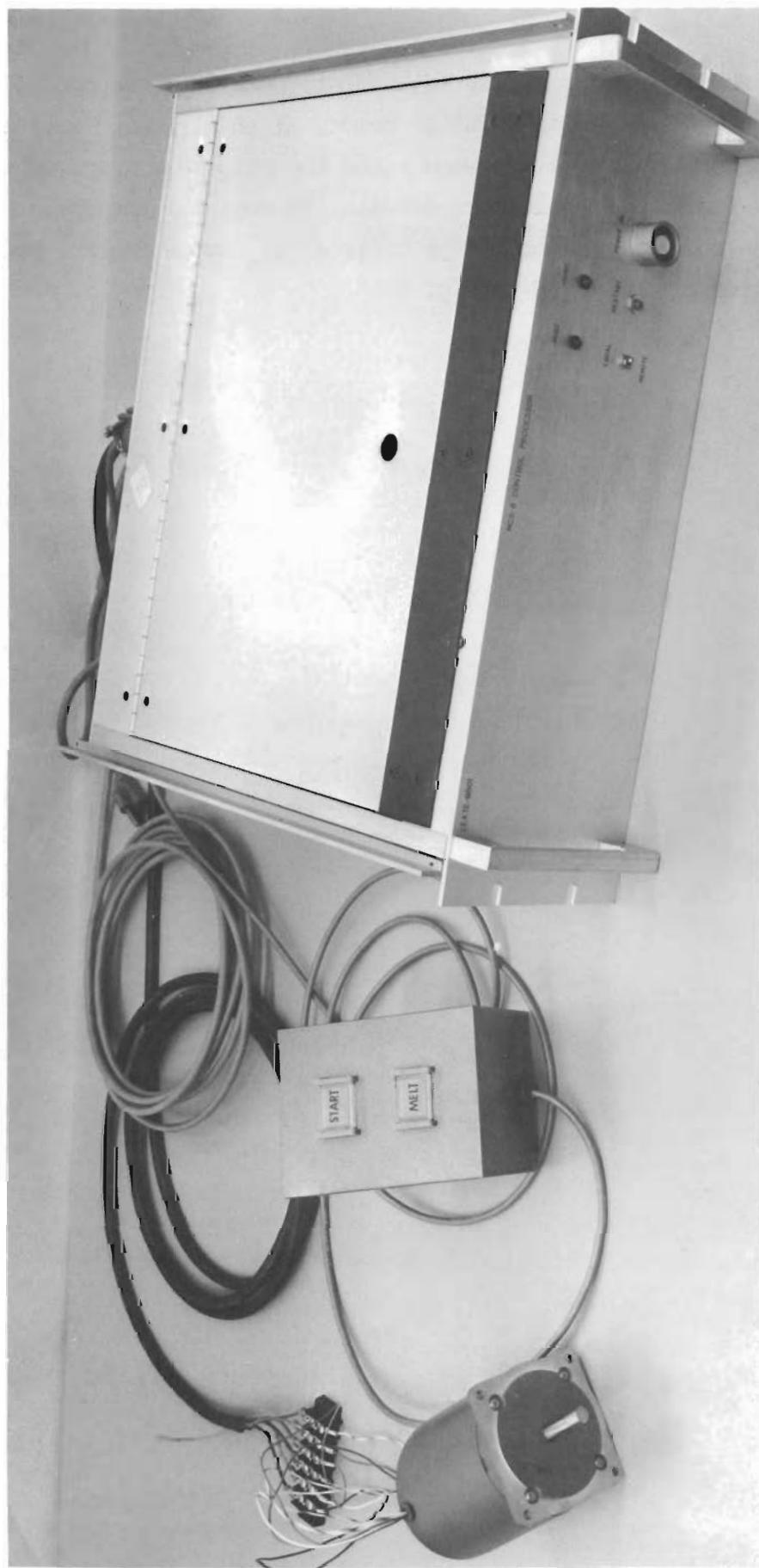

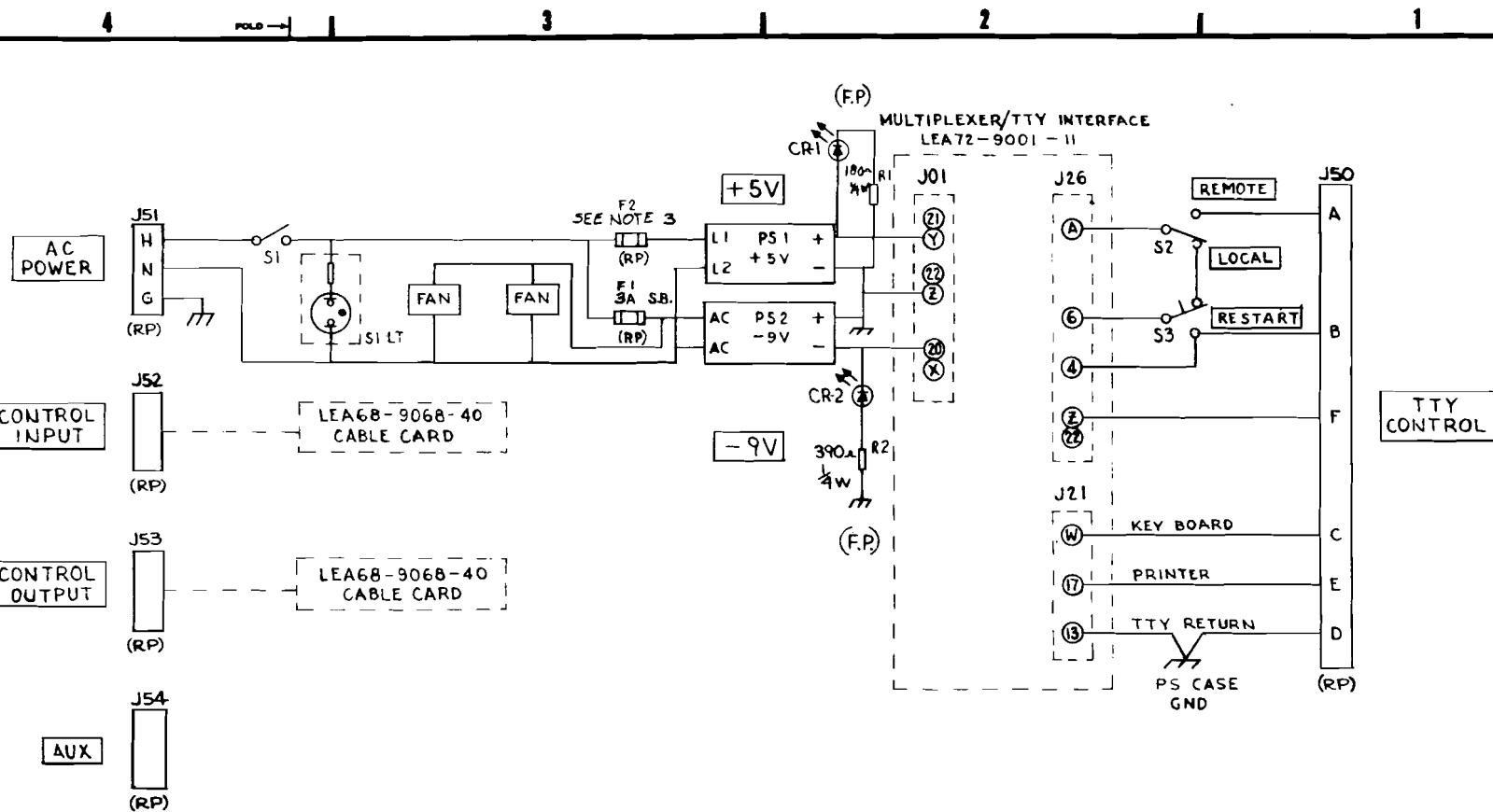

INSTALLATIONController

The controller rack mounts and is equipped with ball bearing slides with a tilt-lock mechanism. Other than physical proximity to the brazing process the only consideration need be given toward placement is the availability of free air flow behind the unit. The box has two fans, one for blowing cool air in and the other for exhausting hot air. The input fan has no filter so if installation is in a dusty area it may be wise to add a filter to this fan.

Cables

The unit has three cables which mate to the controller via two connectors. The analog input uses a special twisted pair shielded cable and three conductor coaxial connector (both manufactured by Trompeter Electronics), J56, for minimal electrical noise pickup (Fig. 5).

The other two cables are for the remote control box and the stepping motor. They both use J53, control output, for mating to the controller, and are both ten feet long.

Stepping Motor

The HS-50 stepping motor requires a 15 volt, 6 amp power supply, connected by terminal strip J55 (Fig. 5). If desired, the power can be provided by two 15 volt, 3 amp supplies. Good regulation of this power is not necessary, and a brute force regulated supply is more than sufficient. Sixteen gauge wire should be used in the power distribution.

The program is designed to have the motor connect directly to a Variac, or equivalent. The control output is limited to 180 degrees maximum rotation for this reason. If the 85 oz-in torque of the motor is insufficient to rotate the shaft, gearing can be added, but this will require a program change.

Because there is no feedback from the stepping motor it is necessary for the program to rotate the motor far enough in CCW direction to reach a travel limit. After this initialization has been accomplished the program

FIGURE 5. Input/output connectors

maintains the motors position by counting all output pulses, until heat is to be shutoff following the braze melt. At this time initialization is repeated to assure no accumulating error. A limit switch is sensed by the program to prevent excessive rotation of the Variac.

OPERATING INSTRUCTIONSNormal Operation

When power is first applied to the controller it will be necessary to restart the unit by pressing the switch on the front panel. This will also initialize the control program and return the stepping motor to home position, so that in the event of an emergency automatic control can be shut off by pushing the restart switch.

Usually power will be on and the program running. Under these conditions the operator need only be concerned with the pushbutton switches on the remote control box. A brazing cycle is initiated by pressing the START switch. This commands the controller to raise the temperature up to the brazing point at a preset rate (see Adjustments section for discussion of this and other control settings). Once at the brazing temperature the controller will hold indefinitely at this temperature until the operator signals that melt has occurred by pressing the MELT switch. This causes the controller to continue holding for a pre-set time period, after which the heat is shut completely off.

Adjustments

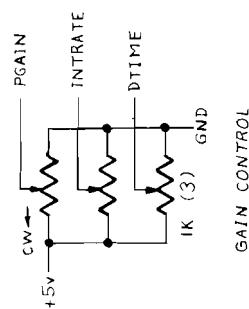

Controller adjustments are located inside of the enclosure towards the front on the right hand side (see Fig. 6). Adjustments include three gain control potentiometers for the feedback compensation and two data entry switches for profile control. The parameters determined by the later two switches set the rate of rise (in minutes to reach brazing temperature) and the hold time following the braze melt (in tens of seconds) before heat shut-off. The hold time may *not* be set at zero, as the program will treat this situation incorrectly.

Control Response Adjustments

The gain constants associated with each of the three different control actions: proportional, integral, and differential, are set by the previously mentioned potentiometers. For satisfactory operation these controls must be set correctly, or either under-control or unstable response will result. Many references in the literature describe techniques

FIGURE 6. Controller internal view.

for setting these controls, but most assume detailed characterization of the controlled process. The method given here anticipates the absence of this knowledge, and only requires a strip chart recorder attached to the temperature feedback signal (full scale should be 50 mv).

One note of caution: the response of any particular brazing setup will be affected by the degree of coupling between the heating coil and the part. The control response should take this into account by being set on the conservative side. Otherwise a test part with adequate coupling may control well when a production part with poorer coupling is partially unstable. Strip chart records of the temperature profile should be maintained for the first few parts following an adjustment for this reason.

Proportional Gain. The bulk of the control response will undoubtedly be proportional, that is the control output (the amount of heat being applied to the part) will be proportional to the difference between the desired profile temperature and the actual (measured) temperature. The important thing to note is that there must be some temperature error to produce any proportional response. Thus for any temperature other than ambient with proportional response only, a steady state temperature offset will exist. Increasing proportional gain will decrease the amount of the offset, but can *never* fully eliminate it. At some point further increases in proportional gain will cause the system to go unstable and oscillate (this is called the ultimate proportional gain). A reasonable proportional gain setting is half this value. Fig. 7 represents the effects of increasing proportional gain. The third adjustment is the ultimate gain setting, and the process is in continuous oscillation at this point.

Integral Gain. The offset error that accompanies proportional-only control can be eliminated by the introduction of integral control. The control output in this mode is proportional to the integral of the control error. Thus even a small offset will integrate over some time period to a sizable control response. In fact, any degree of integral control has infinite gain for dc control errors. The integral gain merely determines the rate at which integral accumulates.

The infinite dc gain of integral (also known as reset) control allows it to reduce the steady state error to zero, but the 90 degree phase lag it adds tends to make the closed loop system more unstable. For this reason it should be used sparingly. After the proportional gain is set and the steady state error is known, the integral gain can be increased to observe its effects. This is illustrated by Fig. 8, where the cycle was allowed to reach the holding temperature before the integral gain was adjusted. This allows for a constant *setpoint* temperature, thus avoiding the introduction of another variable parameter during the adjustment. When the integral gain is first increased it will begin integrating the offset error which presently exists. This will increase the control output, causing the temperature to increase. When the temperature reaches the setpoint of the profile the error has gone to zero, but the integral may have accumulated more than necessary. To reduce the excessive integral the temperature must go *above* the profile to integrate in the opposite direction. The net effect of this is the damped oscillation indicated by Fig. 8. Further increases of integral gain will make the oscillations continuous and, then, unstable. The ideal integral gain (or integration rate) will match the response of the process such that little or no overshoot results from this adjustment.

Differential Gain. This control mode responds to the differential of the control error. Its primary use is to optimize the dynamic performance of the controller to fast changing setpoints and processes. This application does not require such performance so its use may not be necessary. Certainly until more operating experience is gained it should not be used because interaction of a third parameter makes adjustment more difficult. However, because differential control has a 90 degree phase lead it can, to some degree, counteract the instability of the integral control's phase lag, if this is necessary (it probably will not be).

FIGURE 7. Effects of various proportional gain settings.

FIGURE 8. Adjusting integral control.

MAINTENANCE

The only periodic preventive maintenance which the controller requires is occasional oiling of the cooling fans and analog-to-digital converter calibration. All other maintenance will involve either "tuning" the control parameters (detailed in the Operating Instructions) or repairing a failure. Because the controller is considerably more sophisticated than it first appears a comprehensive set of procedures for verifying operating and detecting failures is included.

Digital Process Simulator

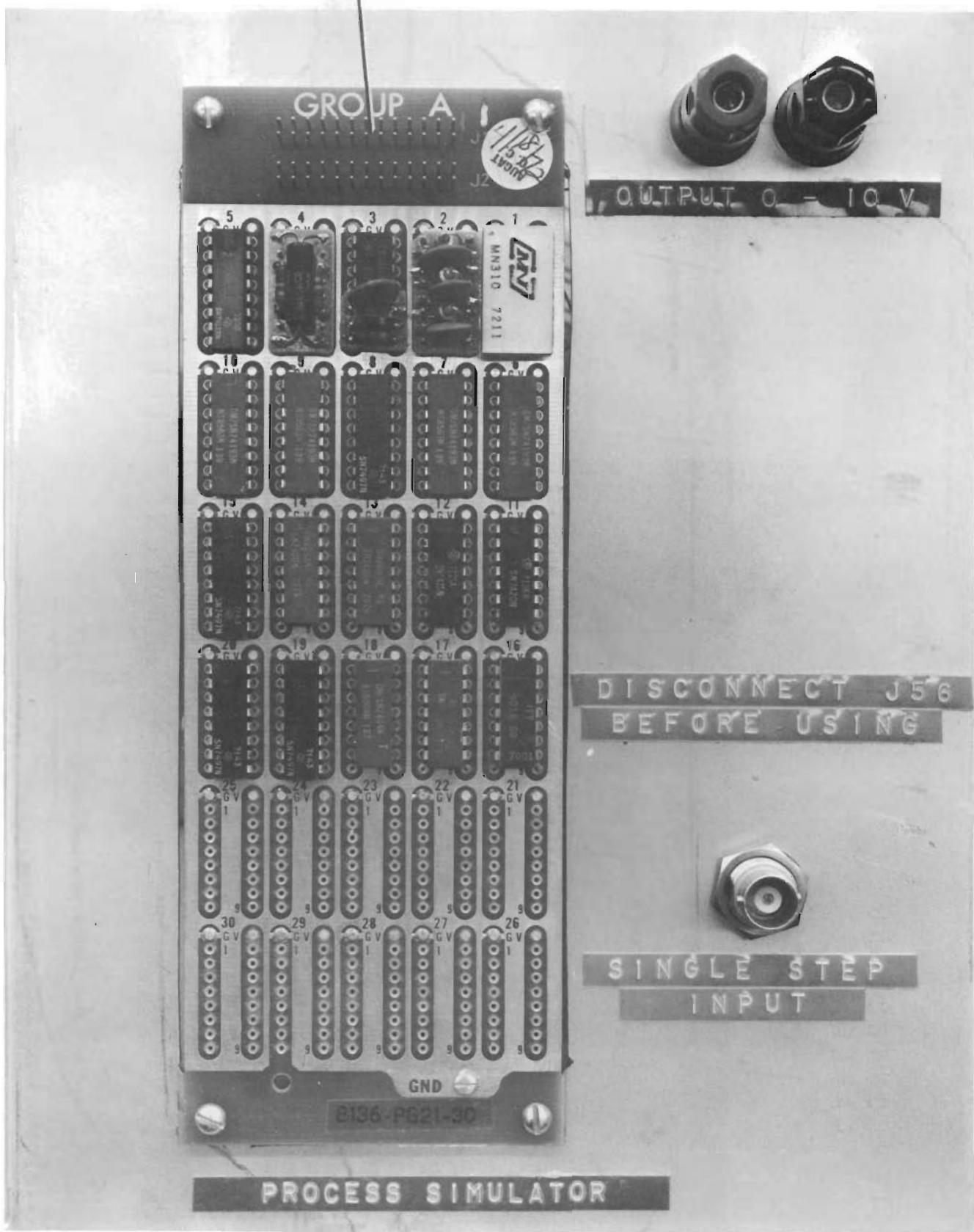

The immediate concern in the event of a malfunction is the positive isolation of the source of the difficulty. For this and other reasons a digital process simulation was designed and fabricated which permits most of the controller functions to be checked out independent of the other components in the system. While not intended to be foolproof, this technique can identify most controller failures.

Connection of the simulator is made through a cable card connector which plugs into card position 37 (Fig. 9) accessed through the top cover. It is necessary to turn the controller power off and disconnect the temperature input cable (J56). *The simulator should never be connected or disconnected with controller power on.* If it is necessary to disable the stepping motor for any reason, do so by turning off the translator power to terminal strip J55, and *not* by disconnecting only the motor.

The analog output (corresponding to temperature) of the simulator is made available by the two terminal posts on the simulator's box (Fig. 10), and varies between 0 and +10 volts. The best method for observing this signal is with a strip chart recorder.

Test Programs

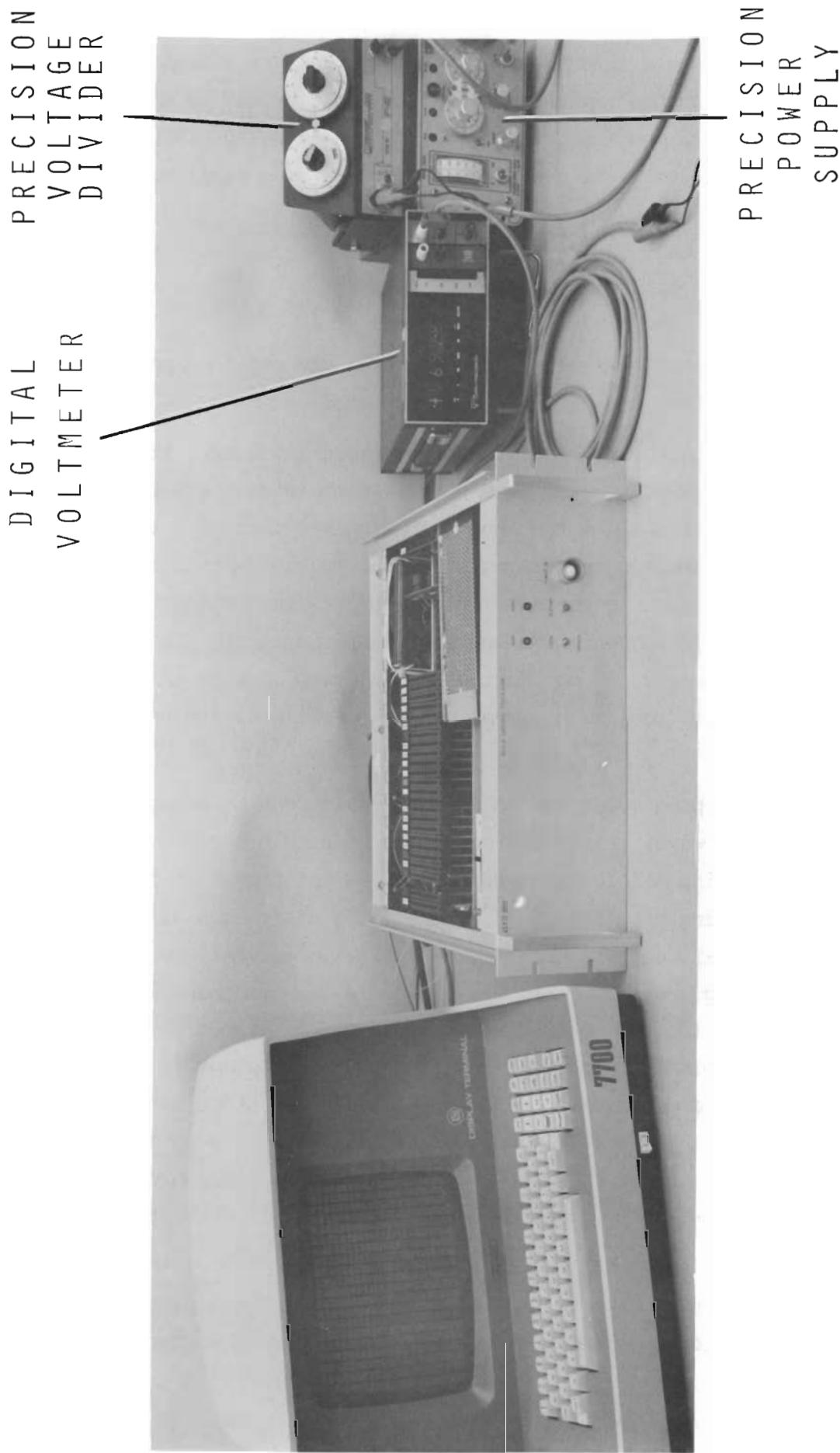

The interface circuitry can be largely checked by utilizing the processor and a Teletype. This is done by using the Octal Debug Technique program (ODT) to enter short test programs into random access memory (RAM) from the Teletype and execute them. Fig. 11 shows the controller connected to a video terminal in place of a Teletype, along with instrumentation used during calibration.

INTERCONNECTING

CABLE

PULSE GENERATOR

PROCESS SIMULATOR

FIGURE 9. Process simulator connected to the controller.

## CABLE CONNECTOR

FIGURE 10. Process simulator.

FIGURE 11. Controller setup for maintenance and calibration.

Testing of the input facilities is eased by use of the octal output routine, OCTALP, contained in the ODT program itself. This routine types a space and the value of the A register as a three digit octal number. It is executed by any subroutine call, such as

```

106      CAL OCTALP

307

000.

```

The BCD and control switches, for instance, are examined merely by inputting their setting and typing it out in octal.

Exercising the MUX-ADC is a little more involved. It requires setting the multiplexer and commanding a conversion. A BCD switch is conveniently used to select the input line (only 0 through 3 are used) by reading its value and outputting it to the multiplexer control register. The real-time clock is tested simultaneously with the ADC by waiting for it to set before commanding a conversion and resetting the clock flip-flop. A Teletype, however, is not fast enough to keep up with the clock rate (10 Hz), but the real time clock must be operational for any output to occur.

The stepping motor has no feedback which can be examined, but can be tested in two ways. First the motor can be single stepped in both directions by pushing "A" for CCW and "B" for CW rotation. It may be convenient to use a masking tape "pointer" on the motor shaft as a single step (1.6 degrees) is difficult to observe. A typical motor failure will involve a single winding (usually the power driver is the component which goes). In this situation the motor may continue to rotate, but in an erratic fashion. Single stepping will reveal this as two steps in one direction, one reversed, and one with no motion at all (four steps are required to complete a full sequence). The motor still turns because the net sum of motion will be in the commanded direction, but at one fourth the correct amount. Speed is also limited so that it may stall when operated at normal speeds.

Continuous motion is best checked with the motor disconnected from the load. Friction clamping can simulate the load's torque requirements,

but will not usually be necessary. The test program reads the Teletype input character (which is available until another is typed) and outputs it as a stepping command. As before an "A" causes CCW motion and a "B" CW motion, a "D" will stop all motion. The stepping rate, 200 Hz, is fixed by a software delay of slightly less than 5 milliseconds.

#### Calibration

To assure an accurate correlation between the thermocouple temperature and the internal digital representation the input amplifier and analog-digital converter need periodic calibration of approximately once a year. This task will require the following pieces of equipment (see Fig. 11):

Reference power supply, 0.01%

Precision divider, 0.01%

Digital voltmeter, 0.01%.

The reference voltage is divided by a suitable factor, such as ten to provide an input to the controller from zero to 40 millivolts in 0.1 millivolt steps. The digital voltmeter verifies the correct gain of the combined amplifiers with calibration data in Appendix D.

The analog input test program, with the amplifier input selected, is used to compare converted values with the above calibration data.

Since the amplifier gain is fixed the use of the digital voltmeter is an optional double check. Small variations from tabulated values can be compensated for by the analog-digital converted (ADC). Larger variations indicated a failure or a drift in a component value. In this case the particular amplifier at fault should be identified (the first amplifier has a gain of 10 and the second a gain of 25) and repaired.

The ADC has two adjustments, one for zero and one for full scale trimming (see LED 69-901184). These adjustments will affect only a few digits change in the data listed in the calibration table (only eight of the unit's twelve bits are tabulated because this is all that is used in the control program). Adjustments which are greater than this range cannot be made by these potentiometers and indicate a gross malfunction which should be repaired. Any adjustments which are made should utilize

the full twelve data bits to afford the longest term calibration (full scale of 42.38 ms can be assumed equal to 377.740<sub>8</sub> for this purpose).

#### Oscilloscope Waveforms

The general status digital and program logic can be determined from a few waveforms. Any oscilloscope with a dual trace feature can check this.

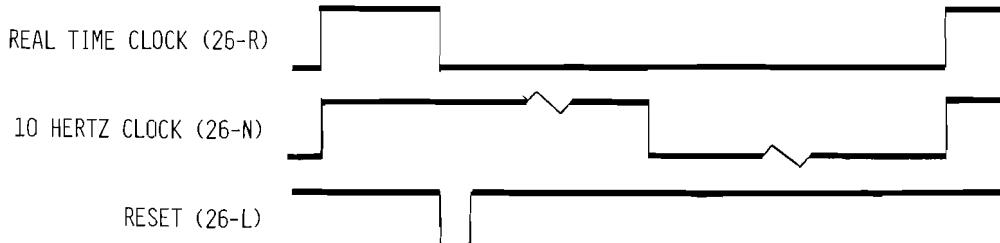

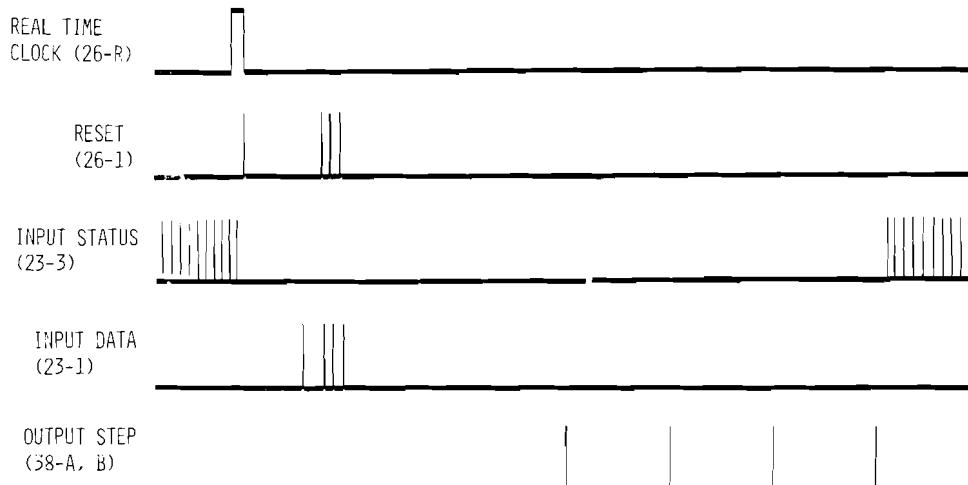

The real-time clock will always be running except for one second after a restart. This signal, at pin 26-R, is triggered by a ten Hertz clock on pin 26-N (see Fig. 12). The processor continually samples this signal, and once it is triggered the processor resets it (pin 26-L).

FIGURE 12. Real Time Clock Waveforms.

Much information about what the processor is doing and when is available from the input multiplexer control signals. To synchronize these signals with a particular point in the program the Real Time Clock signal (26-R) is used to trigger the oscilloscope. The signals in Fig. 13 are typical for a cycle after the push of the START button. About seven milliseconds after the resetting of the Real Time Clock the reset signal will pulse three times. This is the triggering of the ADC for each of the three control parameters for use in calculating the output response. Between 20 to 25 milliseconds after the start of the cycle output pulses to the stepping motor will appear (if there is a change in the control output). These pulses may be CW (38-B) or CCW (38-A) during any cycle, but will never be both. The pulses will be separated by 5 millisecond intervals, and can never exceed 175 total (an unlikely number, with a dozen or less being more typical). Once all output steps have been commanded the processor will resume sampling the Real Time Clock with

the status input signal (23-3). Since this signal is absent during the calculations the execution time during any cycle can be observed from it.

FIGURE 13. Data Multiplexer Waveforms.

#### Maintaining the Processor

Much of the previous maintenance depends upon the processor being operational so that at least the ODT program can be run. In the event that the processor is not operational procedures are needed for diagnosing and repairing the malfunction.

One simple technique is to replace all cards associated with the processor one at a time until the facility card is isolated. The nine cards in positions 18 through 26 are those which must be exchanged. This technique will only work if the failure is on one of these nine cards. If it is on another card, or if it is in the wiring (it is possible for the corner of a wire wrap pin to cut through the insulation of a wire held against it with excessive tension), this technique will only indicate that the problem is *not* on these cards, which is valuable information in itself.

While the particular problem may dictate the nature of the problem it is wise to ascertain the following items

1. Both power supplies, +5 and -9 volts, are within tolerance.

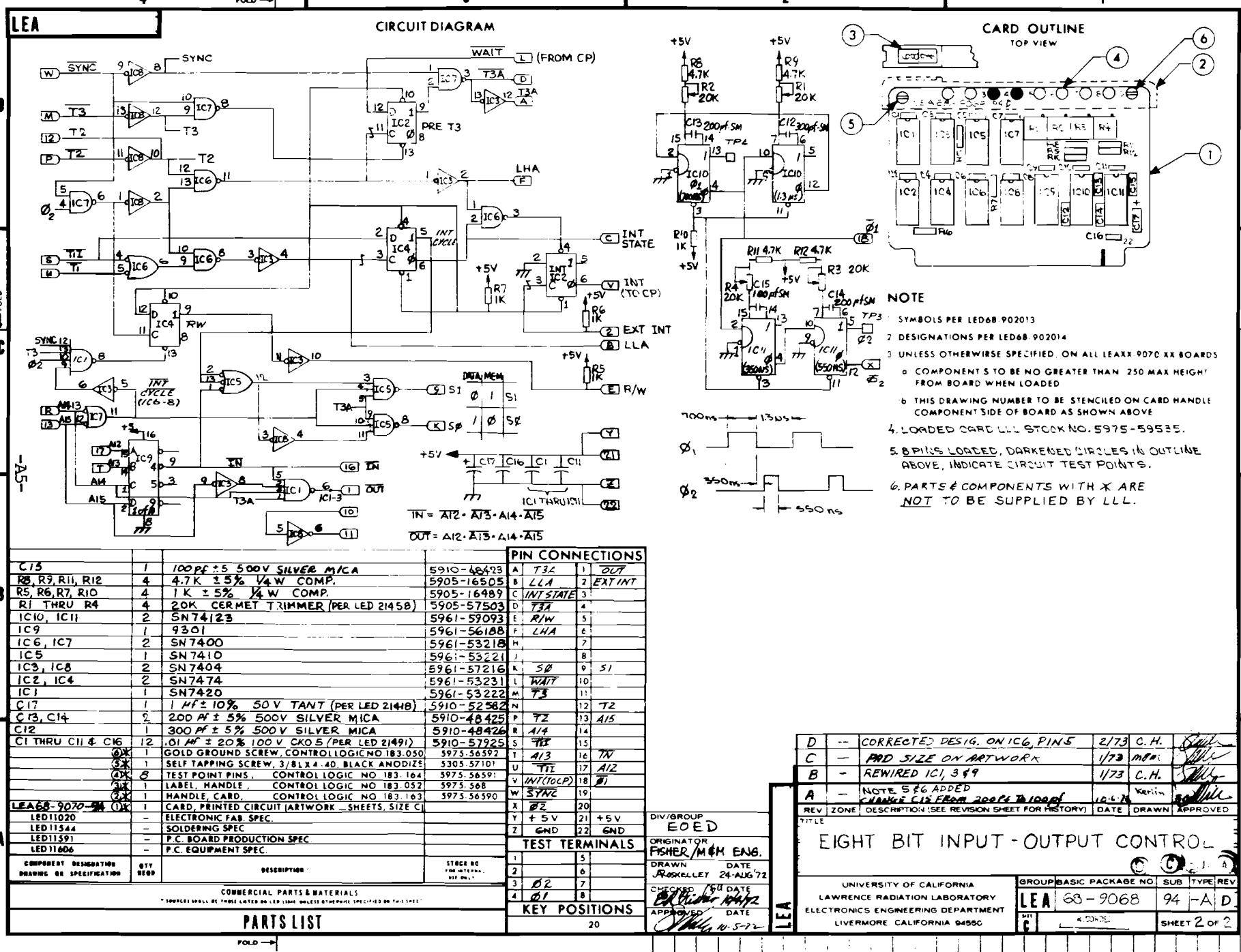

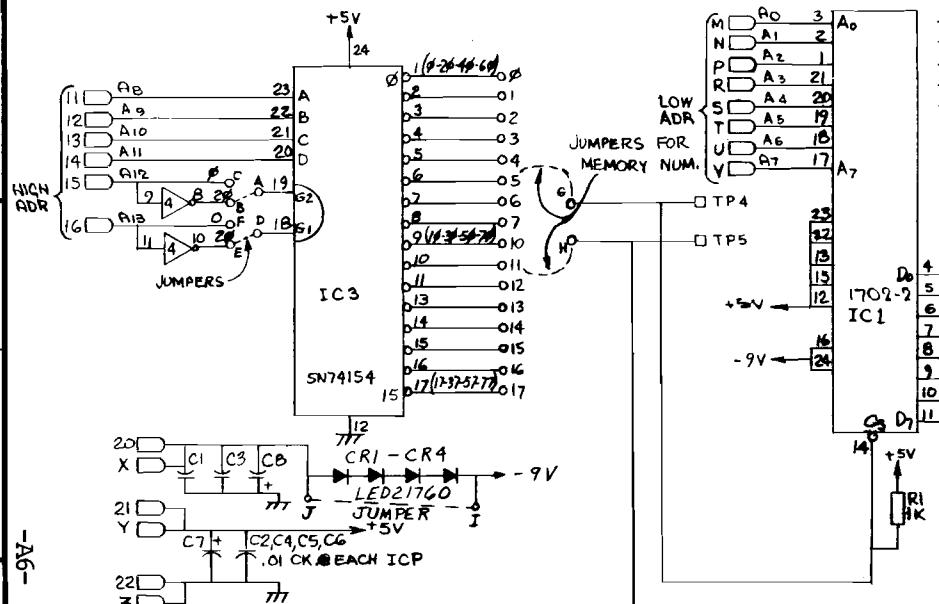

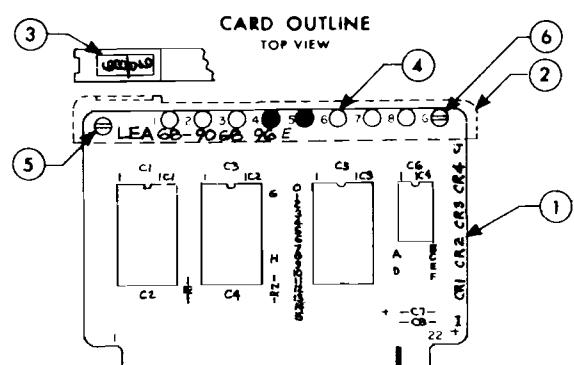

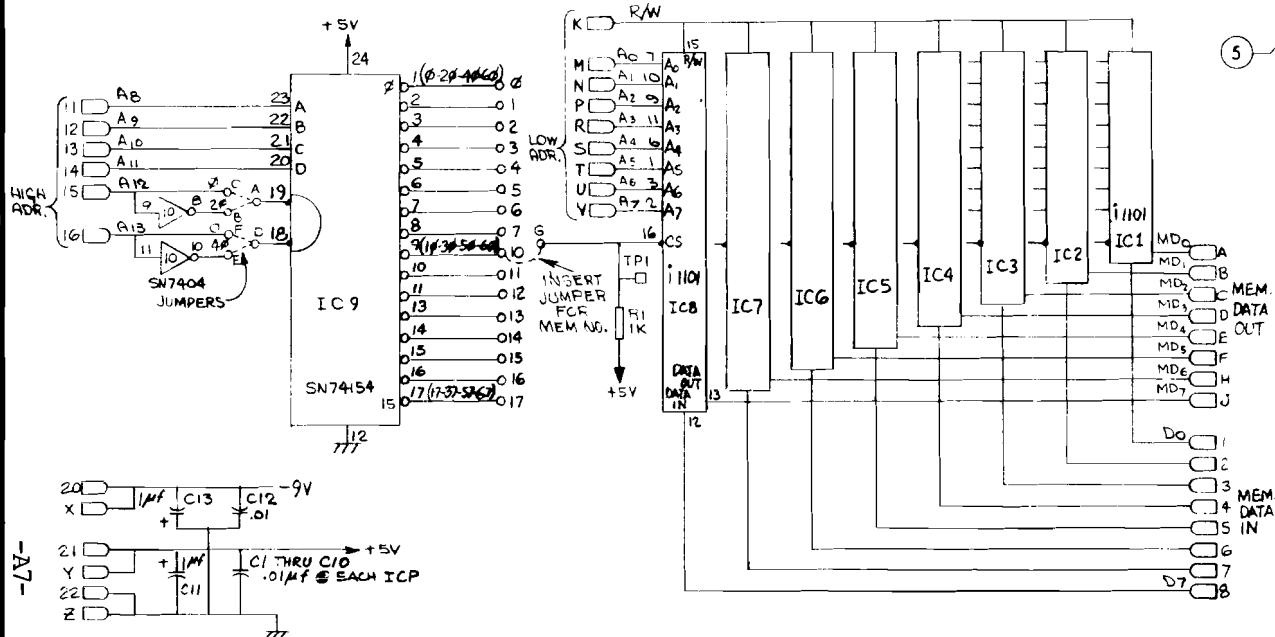

2. The two phase clocks are running and in tolerance (see MCS-8 manual or LEA 68-9068-94D)

3. The Sync signal (19-W) is running after pushing restart

4. The Ready line (19-19) is low.

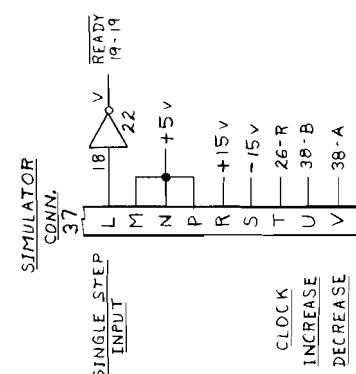

Single Stepping - If the following procedures do not locate the problem it will be necessary to examine operation on a step-by-step basis. The processor can be single stepped by pulsing the READY line (19-19) with a low-true pulse. For this purpose the wire to ground was removed and wired to an inverter at 22-V. With the input disconnected the output will be low and the processor will run normally. With a pulse generator connected to the input on the digital simulator which generates a positive 3 to 5 volt 10 microsecond pulse the processor will execute one instruction cycle for each pulse (see Fig. 9 for the setup of this equipment). If the generator is set for single pulses the processor can be easily single stepped through a program. Also the program can be executed at the repetition rate of the generator. The effect of this is best observed by operating the ODT program at a slow speed with an operational processor.

Single stepping and slow speed execution by themselves are of little value without address and data display. LLL has available a card which plugs into one of the memory slots which displays the address and memory output data with light emitting diodes (LED's). But to be useful this information must be properly interpreted, for which a program listing and an MCS-8 manual are useful.

It must be remembered that the address information serves a multiple purpose. Not only is it used for the instruction address, but it also is used for I-O instruction decode and accumulator output data. Further for multiple cycle instructions data and address fetches may be required. The breakdown of each instruction on a sub-cycle basis is tabulated in the MCS-8 User's Manual. An instruction set summary is on the inside rear cover.

ODT - If the ODT program does not respond to input usually either the asynchronous receiver/transmitter is not functioning (card 21) or the input

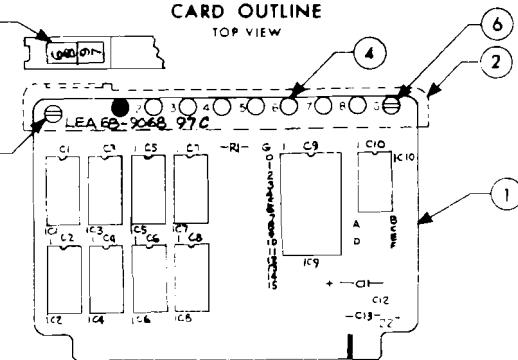

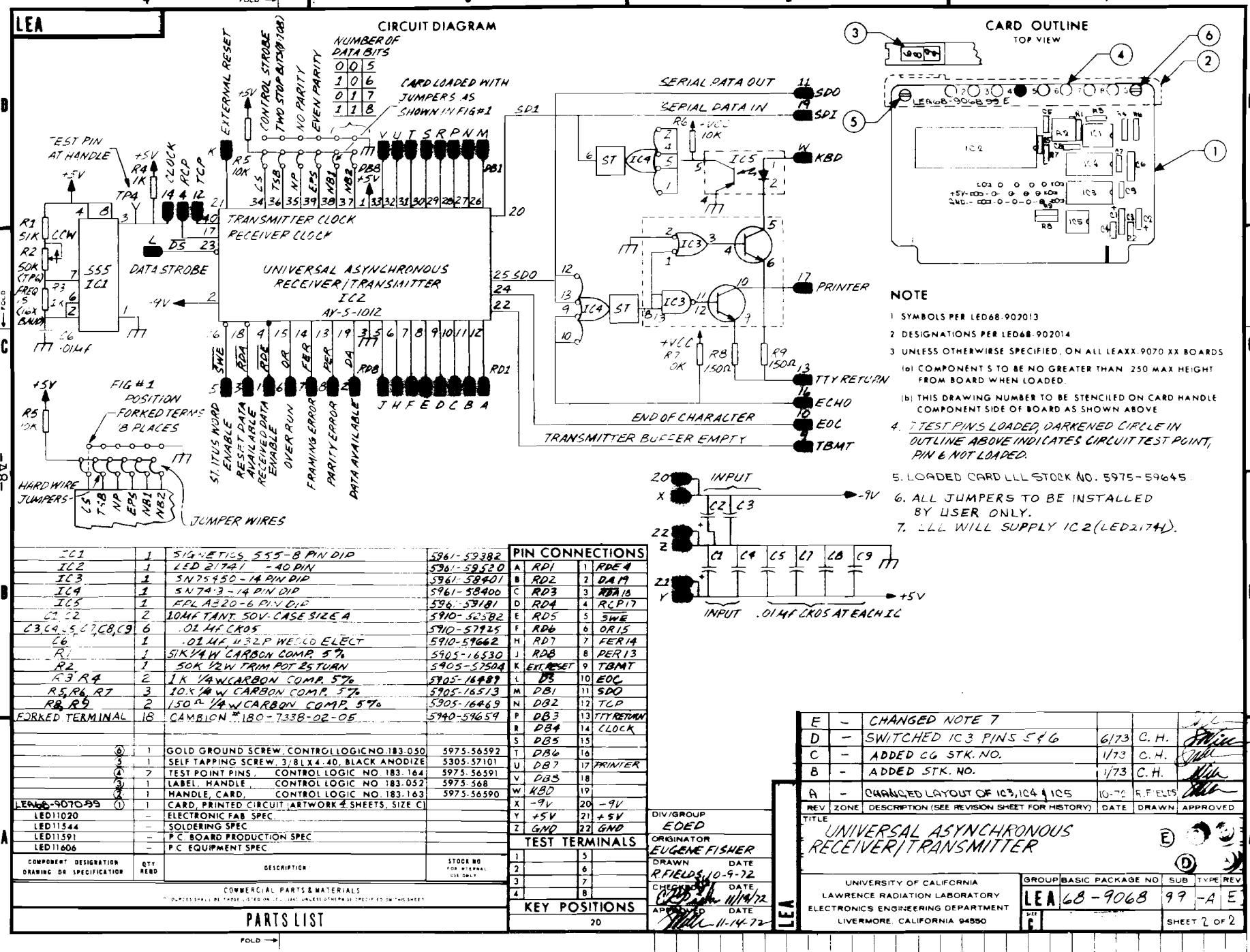

multiplexer is not properly inputting status (card 23). If data available (21-2) do not go high after pushing a Teletype key check that serial data are actually being sent by examining both 21-W and 21-19 (refer to LEA 68-9068-99C). If the ODT program does not properly recognize the character check to see that the clock on 21-14 is 1760 Hz. If the clock rate is right, one of the data lines, either between the UART and the multiplexer or the multiplexer and processor, has been damaged. ODT may recognize some characters and not others, which will point to a particular data bit (for instance an open line will have the effect of a high signal, which will work for these characters that agree in this bit position).

Memory - If ODT, the processor, and the interface equipment function properly but the temperature control program fails in some manner the memory may be at fault. Memory consists of both random access (RAM) and programmable read-only (PROM) memory, so each must be checked separately.

RAM is checked easiest by replacing it (be sure that the three jumpers of the replacement are identical to the original). If this does not solve the problem, yet the RAM is known to be the problem (as can be determined by a test program which must be entered in *another* RAM), the next step is to check the address bits and the read-write control line. The latter must pulse high to write data, but also must stay low at all other times.

The PROM presents a more difficult situation, but has also demonstrated to be more reliable from the admittedly small sample size with which we have worked. The difficulty is that spare PROM's written with the control program (it takes four) may not be available for replacement. Assuming this to be the case, one of two techniques may be used to check the PROM out.

If a computer is available with a synchronous interface of suitable speed (at least 600 baud) a program in the host computer can do a word-for-word compare of the PROM to a program tape using ODT. Such a program has not been developed for this project, but one designed to link the MCS-8 to an SEL 840A could be readily adapted for this purpose.

If this is not practical, the slow speed execution technique may be used to detect hard program failures ('hard' is used to describe those changes in the program which cause a complete stoppage of execution, such as a jump to an unused page of memory). By restarting the program and allowing it to approach the point of failure slowly the approximate address of the failure can be determined. Although it is only necessary to determine the page in which the memory change is located the exact location can be deduced by close examination with ODT.

A 'soft' program failure is more difficult to identify since full operation is not defeated. Further it may be erratic since only certain number sizes may be affected, for example. The best bet here is to start execution and stop it periodically to examine the program variables in RAM with ODT. The program must be manually restarted at  $4415_8$  to avoid program initialization each time. Only experience and a thorough knowledge of the control program make this feasible, however, as these variables are only the effects, and not the causes, of the failure.

SPECIFICATIONSDimensions

|                          |                |

|--------------------------|----------------|

| Controller               | 7 x 19 x 15 in |

| Remote control box cable | 10 ft          |

| Stepping motor cable     | 10 ft          |

| Analog input cable       | 15 ft          |

Power

A.C.: 120 v @

D.C.: 15 v @ 6 a

Analog Input

|                     |                 |

|---------------------|-----------------|

| Bandwidth:          | 1 KHz           |

| Impedance:          | 300 MΩ          |

| CMRR:               | 100 db          |

| Full scale Voltage: | 42.38 mV        |

| Connector:          | Trumpeter PL-72 |

Stepping Motor

|                   |                         |

|-------------------|-------------------------|

| Type:             | Superior Electric HS-50 |

| Torque:           | 85 oz-in                |

| Steps/revolution: | 200                     |

| Control range:    | 180 degrees             |

| Mounting:         | Any position            |

| Thermal:          | 55° C rise              |

Control Program

|                     |                                                         |

|---------------------|---------------------------------------------------------|

| Control modes:      | Proportional, integral, and differential                |

| Digitation accuracy | +0.012%                                                 |

| Sampling rate:      | 10 Hz                                                   |

| Output resolution   |                                                         |

| Nominal:            | 0.6%                                                    |

| Maximum:            | 0.0015%                                                 |

| Temperature profile |                                                         |

| Number of points:   | 256                                                     |

| Accuracy:           | +0.012%                                                 |

| Advancement Rate:   | Selectable, 0.6 to 5.4 sec/point,<br>0.6 sec increments |

| Hold delay:         | Selectable, 1 to 9 min.                                 |

Teletypewriter Interface

|        |                            |

|--------|----------------------------|

| Type:  | Asynchronous, current loop |

| Level: | 8                          |

| Code:  | ASCII                      |

| Rate:  | 110 baud                   |

SOFTWARE

As mentioned in the Introduction the largest effort in the controller development was software. Obviously the success or failure of a microprocessor application will depend greatly on the continuity and strength of all associated software. The general approach of using the same system to develop software which it will eventually run on, and relying on vendor supplied system software, will not be viable for microprocessors. For even if the system software exists, the microprocessor, by nature a small dedicated purpose machine, will not be adequate for this use. The software development, then, must be done on a larger system with the necessary hardware and software to support the development.

Support is of several different types. First, facilities must be available to assist in the conversion of a symbolically coded microprocessor program to the machine code of the microprocessor. This will consist of means of preparing the symbolic code, such as on punched cards, editing it, and storing it on a mass storage device such as magnetic tape. This code then must be converted to machine code by what the current programming jargon calls a "cross assembler." The designation "cross" refers to the generation of code for one type of machine on another. The assembler generates both the machine code (termed the "object code") and a program listing with both the machine code and the symbolic or "source" code.

An assembler is a mandatory aid in the software development. The only alternative to an assembler is to "hand" assemble the program. This is a lengthy and error prone procedure for a reasonably sized program, and must be repeated each time the program is changed (which, during development, is often).

The second type of system support is a *hardware simulator* program. The simulator must be capable of performing every function of the microprocessor. It executes the identical program code which the microprocessor executes. It also provides the operator with sophisticated debugging aids unavailable on the microprocessor. The use of the simulator speeds program development by a factor several times the rate using the

microprocessor alone. Further the simulator could be used to check out program changes before they are applied to an actual process. This is done by simulating the process as well as the microprocessor.

It should be stressed that the sole value of a simulator is the information it supplies the designer. For this reason the simulator must be highly interactive with the user, providing all pertinent information and full control of execution. Also, because information can be voluminous, the simulator should be capable of condensing it down to a useful form.

The third type of support involves mating the microprocessor to the larger system. With a data link between the two, the larger computer can assist in such tasks as program loading, program debugging, memory check-out, and microprocessor exercising.

Program loading is a typical chore during development. Because re-programming of several ROM's can be time consuming, much time can be lost making simple program changes. If RAM is used during this stage instead of ROM this time can be cut drastically. The key to the method is using the data link to pass the program code from the large computer to the microprocessor.

The data link itself is the RS232C serial asynchronous convention which is relatively commonplace. The controller is equipped with such an interface, but is designed for a Teletype at 110 baud (data elements per second). Each character requires eleven bits, which sets the character rate at ten per second. This is not satisfactory for an inter-computer link, since both devices can operate at a much higher rate, which necessitates modification of the interface for higher speeds (a straight-forward modification).

The host computer can be used for debugging by capturing information during program execution. The host will have facilities for storing, condensing, and outputting this information. Exercising the microprocessor can be written to return control to the host computer after execution. However the data link is used, for program loading or controller checkout,

there must exist a service routine in the controller to support its end of the data link. Such a program has been written for this purpose.

#### Octal Debug Technique

The octal debug technique (ODT) allows the operator to examine and change memory from a terminal such as a Teletype. Lawrence Livermore Lab's document LER 72-103402 describes the use of ODT for the purpose. The program given in the document has been modified in minor ways. Primarily the program loading command was altered to a more efficient binary format.

The host computer uses ODT by minimizing the operator's interaction, but at a much higher speed. Through ODT the host computer can examine and change memory, and transfer control to some other program. The capabilities of the MCS-8 ODT should not be confused with powerful debug programs written for the larger minicomputers. ODT, for practical reasons, is limited to 256 words (one page) of memory.

The program starts by typing a question mark and waiting for input. As each character is typed it is examined as to its type: command terminator, or digit. Legal octal digits are accumulated to form a number up to 255, anything greater is an error. The number typed is interpreted by ODT when a terminating command is entered, such as G for go. For example, 377G.

The terminator is decoded by successively subtracting the numerical difference between legal terminating characters. For instance, the difference between a line feed and a carriage return is 3. The program first subtracts octal 212 (the line feed code) from the terminator. If the result is not zero the character was not a line feed. It then subtracts 3 (for a total of octal 215, the carriage return code) and again tests for zero. In like manner all other legal terminators are tested.

Memory addressing must be done in two separate steps. The memory page is set by entering the page number in octal followed by S. The ODT page is selected by typing

ØS,

and the RAM page with

10S.

It must be remembered that the assembled address, as outputted in the program listing, is a complete octal number which is not separated by page numbers. Consequently page  $10_8$ , word 0 is equivalent to address  $4000_8$ .

Once the page has been set a particular location within that page can be examined by typing the octal word number (0 to  $377_8$ ), followed by a slask. ODT will respond by typing the contents of that location. If this location is in RAM the contents can be changed by typing the desired quantity followed by a line feed or carriage return. The contents are unchanged if no number is typed, or the location is a part of ROM.

A line feed automatically displays the next sequential location in the selected page. This command uses an output routine which converts an eight bit octal number to three octal digits preceded by a space. First typed is the page number, followed by the word number, completed with the contents of that address typed as three octal digits. It is up to the operator to interpret this octal number as either instruction code or program data. As with the slash terminator, the contents can be altered if a one to three digit octal number is typed by the operator.

Control can be transferred to another program from ODT by entering the starting address followed by G. The page number, as before, must have been set by the S command. ODT constructs a jump command in the last three words of page  $10_8$  (375, 376, and 377). For this reason these locations should not be used except as temporaries. It also requires a page of RAM at this page number.

A "bootstrap loader" is executed by the R command. It is not intended to be operated from the Teletype in as all data is in binary format (the host computer takes over at this point, having itself issued the "R" to begin program load). The program is loaded into RAM in contiguous pages, whether or not the program uses all of the pages for code. Load parameters consist of the starting page and the number of pages. The starting page is typed in octal preceding the R command. The first data

following the R are the number of pages to be loaded, beginning at word Ø of the starting page. The number of pages and the program code is in binary.

#### MCS-8 Instruction Set

The MCS-8 instruction set is divided into five classes:

- I. Index register instructions

- II. Accumulator group instructions

- III. Program counter and stack control instructions

- IV. Input-output instructions

- V. Halt instruction.

Index register instructions allow for the loading of registers from memory and other registers (a NOP is performed when an index register is loaded from itself). Also any register, except for A, can be incremented or decremented by one.

Accumulator group instructions use the A register as one of the operands for an arithmetic or logical operation. The source of the second operand, which can be an index register, memory, or data in the program code (immediate data), subdivides the accumulator group class three ways. A carry flip-flop provides the mechanism for propagating carries during multiple precision arithmetic operations.

In the third class of instructions are program jumps, and subroutine calls and returns. This class allows use of conditional testing where the programmer can specify which of the status flip-flops must be true or false for the instruction to be executed. While being quite useful it is also the only way in which the status flip-flops can be examined. Because the programmer has no access to the return address during a subroutine call, arguments must be passed via the general registers or predetermined memory locations.

Input-output instructions are the sole source of communication with the external world. Both use the A register for the destination and source of the transferred data, respectively.

The halt instruction is, literally, in a class by itself. Because of the dedicated type of application to which microprocessors will be put,

this instruction is not expected to be normally used in program code. It can catch the gross error of a jump to a memory address with no actual memory (the structure of the memory generates the code of a halt instruction if no valid decode occurs).

A serious deficiency of the MCS-8 instruction set is the lack of provisions for signed arithmetic. For instance there is no direct means to detect a signed overflow. If A and B are the operands and R is the condition for overflow is

$$\overline{(A_S + B)} \cdot (A_S + R_S)$$

Clearly this calculation by software means would be costly, so much so that it is as fast to do double precision arithmetic and not check overflow. This, in fact, is what the control program does. Enough dynamic range is allocated to contain a worst case set of inputs. The output of the program is limited to the maximum range of the controlled variable after the calculations have been done.

#### Control Program

The control program executes a discrete version of the three mode control algorithm and a first order digital filter. The term three mode refers to the three types of responses available with the controller: proportional, integral, and differential. The time response of this controller is

$$U(t) = k_1 e(t) + k_2 \int_0^t e(t) dt + k_3 de(t)/dt.$$

It also controls analog conversion, checks control limits, and generates a temperature profile. This code occupies four 256 word memory pages, with the profile requiring one of those pages.

Temperature profile data are stored in the table as eight bit unsigned integers, of the format

|       |       |       |       |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| $2^7$ | $2^6$ | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|

This permits a resolution of 1 part in 256, or about  $\pm 0.0125\%$ . The value, or weight, assigned to the least significant bit is not in units of temperature and must be converted by multiplying by a constant. A correlation to temperature requires two conversions; first the temperature--voltage function of the thermocouple must be known, and second the voltage--digital factor of the analog-digital converter must be known. For a cromel-alumel thermocouple a temperature of  $810^\circ \text{ C}$  produces a voltage of 32.91 mv corrected to an ambient temperature of  $20^\circ \text{ C}$ . For this voltage the output of the converter is 305.34<sub>8</sub> (see Appendix for an ADC calibration data and a temperature-digital conversion table). This calculates to be approximately  $4.09^\circ \text{ C}$  least significant bit (LSB) weight.

The control program is not aware of this factor. It merely compares converted input data to profile data, both of which are in the same units and need not be converted any further. The difference between the table entry and the measured temperature is known as the control error,  $e(t)$ . The control response calculation is based on this error.

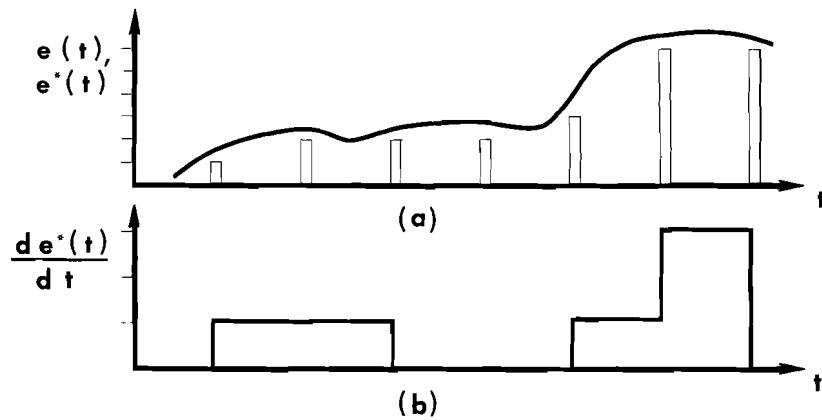

Prior to making this calculation, however, the temperature data are operated on by a recursive digital filter. This filter has two purposes: first it reduces any signal noise that may be present, and secondly it minimizes the truncation effect of digitization (quantization). Both of these problems tend to be very disruptive to the derivative action. Even if noise were not a problem, quantization, or truncation error, would be. Quantization error is illustrated by Fig. 14, where continuous signals must be approximated both by sampling and by discrete levels. Although the continuous signal can usually be approximated adequately for most applications by quantizing, the computation of the derivative may not. If only two data are used it is easy enough to show that for any frequency the sampling rate can be increased to the point where the derivative is either one or zero. The addition of noise at this point greater than the quantization level will mean that the signal to noise ratio will be less than one, a disastrous control situation. The use of programmed filters, however, can circumvent this problem.

FIGURE 14. Quantization error. (a) Approximation of a continuous signal. (b) Discrete derivative.

### Digital Filter

If the input to the filter is  $X$  and the output  $X'$ , the output at step  $n$  is

$$X'_n = aX_n + bX'_{n-1}.$$

The fact that  $X'$  appears on both sides of the equation makes it recursive, that is the result of any successive calculation depends upon all previous calculations. The output,  $X'_n$ , can be written as an infinite series

$$X'_n = a[X_n + bX_{n-1} + b^2X_{n-2} + \dots + b^k X_{n-k}]$$

It is evident from this that  $X'_n$  is a function of all previous inputs,  $X_n$ . If the difference is taken between two successive outputs,  $X'_n$  and  $X'_{n-1}$  (as the derivative does), the result will also contain differences between all successive inputs, as can be seen from

$$\begin{aligned} X'_n - X'_{n-1} = & a[(X_n - X_{n-1}) + b(X_{n-1} - X_{n-2}) + \\ & \dots + b^k(X_{n-k} - X_{n-k-1})] \end{aligned}$$

Control Algorithm

The error thus calculated is used as the input to the three mode control algorithm. The control response derived by this algorithm is calculated as follows:

$$U_n = P e_n + I \sum_{i=0}^n e_i + D (e_n - e_{n-1})$$

where  $U_n$  is the control output at sampling interval  $n$

$e_n$  is the control error at sampling interval  $n$

$P$  is the proportional gain

$I$  is the integral gain

$D$  is the differential gain.

The proportional calculation uses the single precision value of the control error (which is scaled back down to regain the original weight). This is multiplied by the proportional gain, measured from a potentiometer, which is also a single precision number. If no further operation is done on the result choices of proportional gain would be limited to integral values. Since this would be insufficient resolution the proportional output is scaled down by a factor of one-sixteenth. This allows a proportional gain range of 0 to 7 15/16 units in 1/16 unit steps (1 part in 127).

The integral control is calculated in two steps: first the current control error is summed to the error integral, and then the integral is multiplied by the integral gain. If the integral were allowed to accumulate at 10 summations per second, the sampling rate of the controller, the integral would rapidly saturate if a significant error were present (even though the integral is maintained in double precision). Prescaling the error prior to summation is undesirable in as this creates a deadband for errors less than the minimum resolution of the scaled error. For instance, say the control error is scaled by four, then errors in the range of one to three units (approximately 4°C to 12°C) would appear as zero after scaling. Since this is the type of error which the integral response is to eliminate this is an unacceptable technique. A second approach is

to integrate at a slower rate, such as one-tenth the sampling frequency. This has the effect of scaling the integral by one-tenth without introducing deadband. It does, however, reduce the bandwidth of integral control and increases phase lag at frequencies near and greater than the summation rate. This is accomplished in the program via a timeout variable which is initialized to ten and is decremented at each calculation loop. Summation occurs only if it is zero, otherwise the control response is calculated from the previous integral without summing the current error. To do this the single precision equivalent is found from the double precision integrand, which is multiplied by the integral gain and then scaled down for the same reasons outlined in the proportional response discussion.

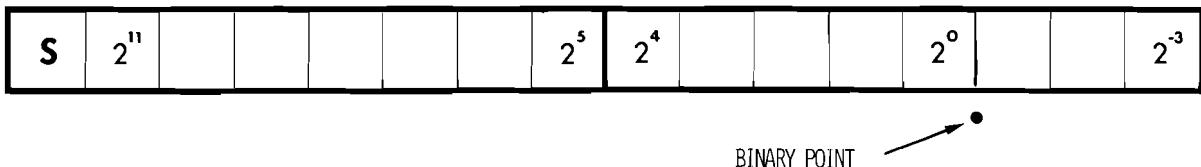

Differential response is found by differencing two successive control errors, and multiplying the difference by the differential gain. To avoid the truncation problem mentioned earlier the scaled double precision error is used in the difference calculation. These data have the two word format

It is mandatory, however, that the multiplication routine be entered with two single precision numbers. Thus if the greater resolution ( $2^{-3}$ ) is to be maintained some magnitude restrictions on the error difference must be made. What this means is that the largest positive error difference recordable is  $7\frac{5}{8}$  units and the negative bound is -8 units. This would only happen if the set point changed by an amount greater than this in two successive steps, which it does not. As before, the double precision value generated by multiplication is scaled down.

After all three control responses have been calculated a signed double precision value represents the control variable. This must be translated to some physical quantity capable of controlling the process. This is the purpose of the stepping motor, which, when connected to some suitable device as a Variac, can regulate the energy inputted to the process. Some limitations are applied to the control variable. First

only positive energy is meaningful so all negative control values are limited to zero. Secondly, the Variac has a travel limit which must not be exceeded. Since the motor is directly coupled to the Variac shaft, and the motor makes one revolution with 200 steps, maximum clockwise actuation is limited to 185 steps (310 degrees). The program keeps the motor position equal to the control variable by stepping it in the appropriate direction (clockwise for positive differences and counterclockwise for negative) one step for each unit difference up to the travel limit (0 and 175). Because there is no position feedback from the stepping motor the controller keeps track of it by storing its current position in memory. Further, the motor has certain dynamic restrictions which limit the maximum synchronous stepping rate. A delay variable in the output stepping program loop sets this rate at 200 Hz.

#### Sequential Control

The remainder of the control program is related to sequence control. Facets of the program which come under this category are program initialization, cycle start, temperature ramping, braze melt, and cycle completion. The decision logic of this part of the program is regulated by a table controlled routine known as a *finite state automation* (FSA). Process control is exercised by which of the several states the FSA is in. It advances from one state to the next on the basis of control inputs and the particular state it happens to be in at the time. The FSA for the control program has four states, which have the following functions:

1. Initialization - Reset stepping motor position, input data switches and initialize other control variables.

2. Wait - Wait for the start of a cycle.

3. Cycle - Advance process through a temperature cycle.

4. Melt - Hold process at plateau temperature for specified delay, then return to initialization.

Inputs to the FSA include the two control pushbuttons and an internally generated advance and reset command. The decision of what the next state the process will transfer to is made by a table containing all the possible

combinations of possible states and inputs (4 states x 4 inputs = 16 entries). An example is if the FSA is in state 2 and the Start button is pressed the FSA is advanced to state 3. If the Melt pushbutton is pressed in state 2 the next state is also state 2. In effect the Melt pushbutton is ignored at this time. If it is pushed when the FSA is in state 3, however, the FSA will change to state 4.

The switches are scanned at the sampling rate, 10 times per second, to test for activation. If one is pushed the FSA is executed to determine the next state, otherwise the current state is decoded in order to execute the appropriate routine. The other two inputs are generated by the program itself, as in the initialization routine which is to be executed only once. It causes the FSA to advance to state 2, the Wait state. The other instance is in the Melt state following the hold delay, at which time the FSA is to be triggered into the Initialization state to shut power off and re-initialize.

The Cycle state executes the three mode control algorithm, and advances a pointer through the temperature profile table. The table contains 256 entries, which are sequenced at a rate of 0.6 second times the rise time setting per entry. For instance, if the switch is set at one (for a two minute rise time) the pointer will be incremented once every six program loops. The pointer will reach the two hundredth entry after 120 seconds, or two minutes. The profile stored in the table is set such that the brazing temperature is reached at this entry. The remaining 56 entries also are this value, which corresponds to the temperature plateau. If the cycle is not completed by the end of the table the program automatically halts advancing the pointer at the last entry.

The Melt routine decrements the hold time out, which is the setting of the hold delay switch times 60 seconds. Since the loop is executed at 10 Hz the setting is multiplied by 600. The hold delay switch is read during initialization, so if it is changed *after* initialization the processor must be restarted to reflect that change for the next cycle. All the time the hold delay is being executed the three mode control algorithm is being executed to maintain temperature control right up to the moment when the power is shut off.

THEORY OF OPERATION

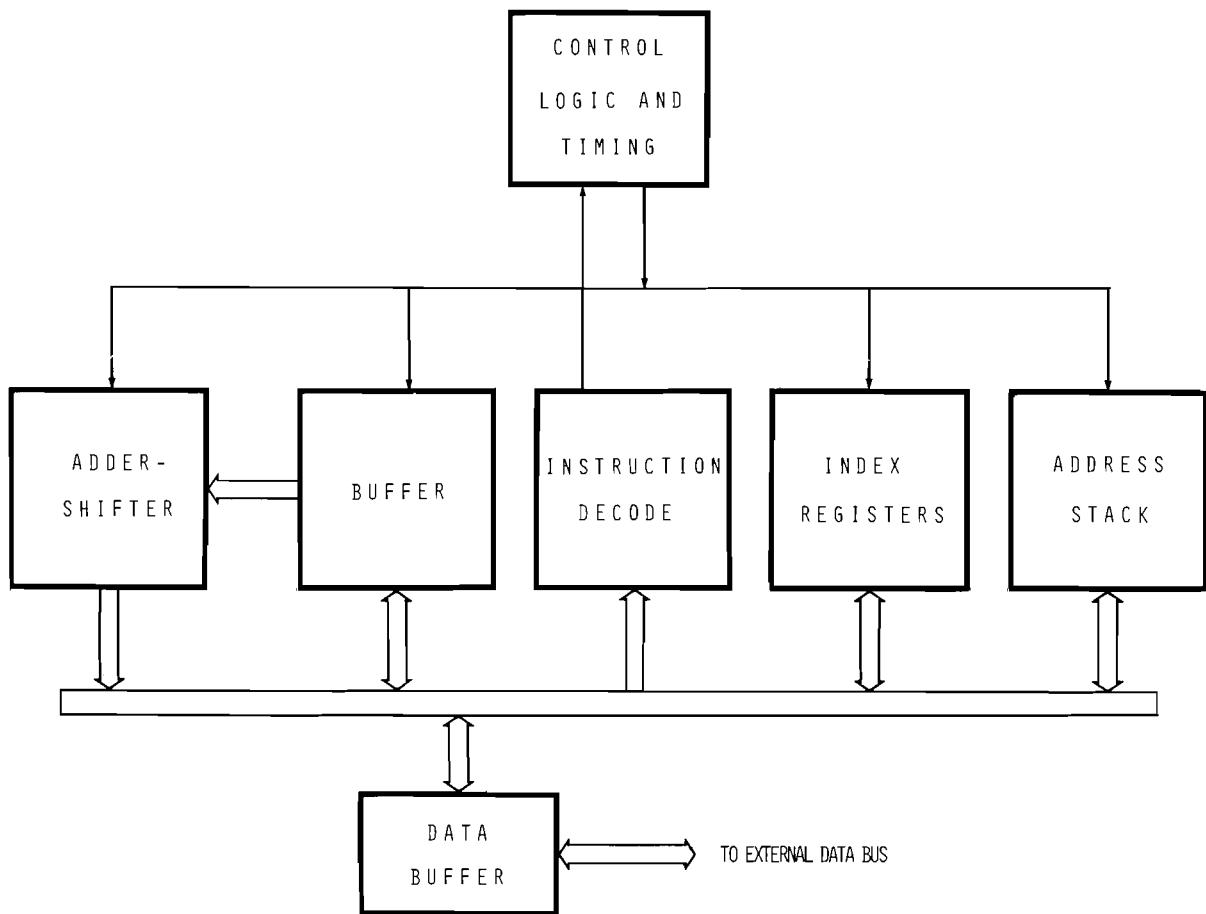

The hardware discussion is separated into two sections. The first section deals with the processor itself and compares it with the MCS-4. Explained are both the internal and external organization of the MCS-8. The second section goes into the interface equipment and its theory of operation.

Intel Micro Computer Set