# The Effects of Threshold Voltage and Number of Fins per Transistor on the TID Response of GF 12LP Technology

Aldo I. Vidana<sup>1</sup>, Nathaniel A. Dodds<sup>1</sup>, R. Nathan Nowlin<sup>1</sup>, Trace M. Wallace<sup>1,2</sup>, Phil J. Oldiges<sup>1</sup>, Brian M. Dodd<sup>1</sup>, Jenny Xiong<sup>1</sup>, Rick M. Cadena<sup>1</sup>, James Trippe<sup>1</sup>, Hugh J. Barnaby<sup>2</sup>, Jeffrey S. Kauppila<sup>3</sup>, and Lloyd W. Massengill<sup>3</sup>

Sandia

National

Laboratories

<sup>1</sup>Sandia National Laboratories, Albuquerque, NM, USA, <sup>2</sup>Arizona State University, Tempe, AZ, USA, <sup>3</sup>Reliable MicroSystems, Franklin, TN, USA

## ABSTRACT

We present experimental total ionizing dose data on GlobalFoundries 12LP 12nm FinFET technology. The TID response depends on both the transistor threshold voltage and on the number of fins per transistor.

## MOTIVATION & OBJECTIVE

- GlobalFoundries (GF) 12LP 12nm bulk FinFET technology is being studied for many rad-hard programs

- As a state-of-the-art technology, 12LP offers significant performance and density advantages over older technologies.

- We report the first TID results on 12LP covering all four of the core threshold voltage variants, as well as a wide range of number of fins per transistor, both gate oxide thicknesses, and nFETs and pFETs.

- These results show designers how to maximize TID hardness in their 12LP designs.

## EXPERIMENTAL DETAILS

| Transistor Test Structures |             |                        |                        |               |                        |

|----------------------------|-------------|------------------------|------------------------|---------------|------------------------|

| Type                       | Gate Length | Threshold Voltage (VT) | $n_{Fins}$             | $n_{FinFETs}$ | $n_{Fins\_Total}$      |

| nFET                       | $L_{Gmin}$  | Super-Low (SLVT)       | 1, 2, 3, 4, 12, 20, 40 | 1             | 1, 2, 3, 4, 12, 20, 40 |

| nFET                       | $L_{Gmin}$  | Low (LVT)              | 1, 2, 3, 4, 12, 20, 40 | 1             | 1, 2, 3, 4, 12, 20, 40 |

| nFET                       | $L_{Gmin}$  | Regular (RVT)          | 1, 2, 3, 4, 12, 20, 40 | 1             | 1, 2, 3, 4, 12, 20, 40 |

| nFET                       | $L_{Gmin}$  | High (HVT)             | 1, 2, 3, 4, 12, 20, 40 | 1             | 1, 2, 3, 4, 12, 20, 40 |

| nFET & pFET                | $L_{Gmin}$  | Super-Low (SLVT)       | 4                      | 10            | 40                     |

| nFET & pFET                | $L_{Gmin}$  | Low (LVT)              | 4                      | 10            | 40                     |

| nFET & pFET                | $L_{Gmin}$  | Regular (RVT)          | 4                      | 10            | 40                     |

| nFET & pFET                | $L_{Gmin}$  | High (HVT)             | 4                      | 10            | 40                     |

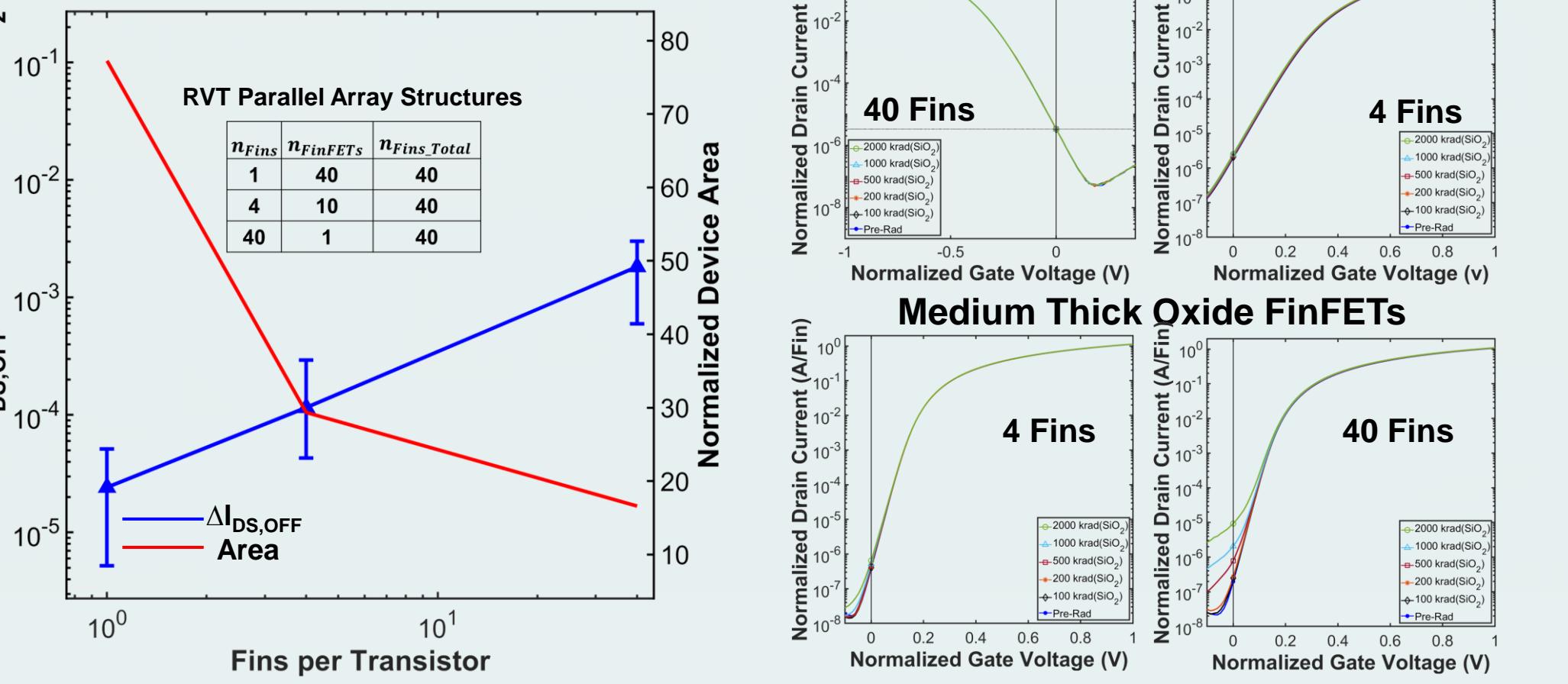

| nFET & pFET                | $L_{Gmin}$  | Regular (RVT)          | 1, 4, 40               | 10, 1         | 40                     |

| Type                       | Gate Length | Gate Oxide Thickness   | $n_{Fins}$             | $n_{FinFETs}$ | $n_{Fins\_Total}$      |

| nFET                       | $L_{Gmin}$  | Medium Thick           | 4, 10, 40              | 10, 4, 1      | 40                     |

- 1) nFET Single Transistor Structures with different number of fins per transistor ( $n_{Fins}$ )

- 2) nFET and pFET Parallel Array Structures with 1, 10, and 40  $n_{FinFETs}$  with different number of fins per transistor ( $n_{Fins}$ ) connected in parallel for total of 40 fins each

- 3) Medium Thick Oxide nFET Parallel Array Structures with 1, 4, and 10  $n_{FinFETs}$  with different number of fins per transistor ( $n_{Fins}$ ) connected in parallel for total of 40 fins each

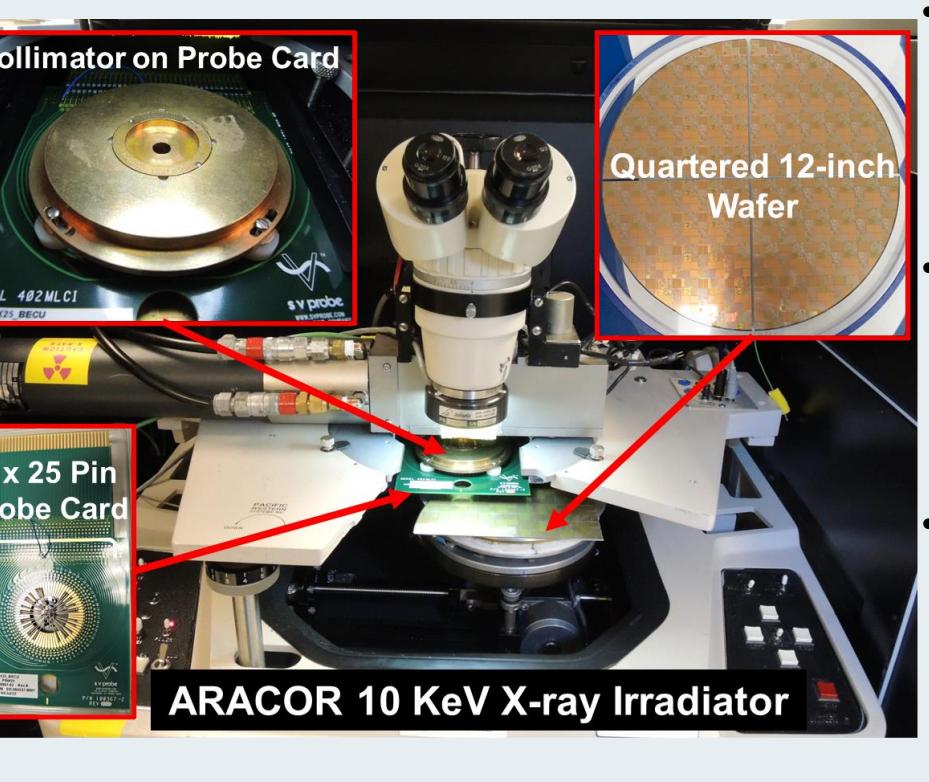

### Experimental Set-Up

### TID induced leakage currents dependence on process threshold voltage (VT)

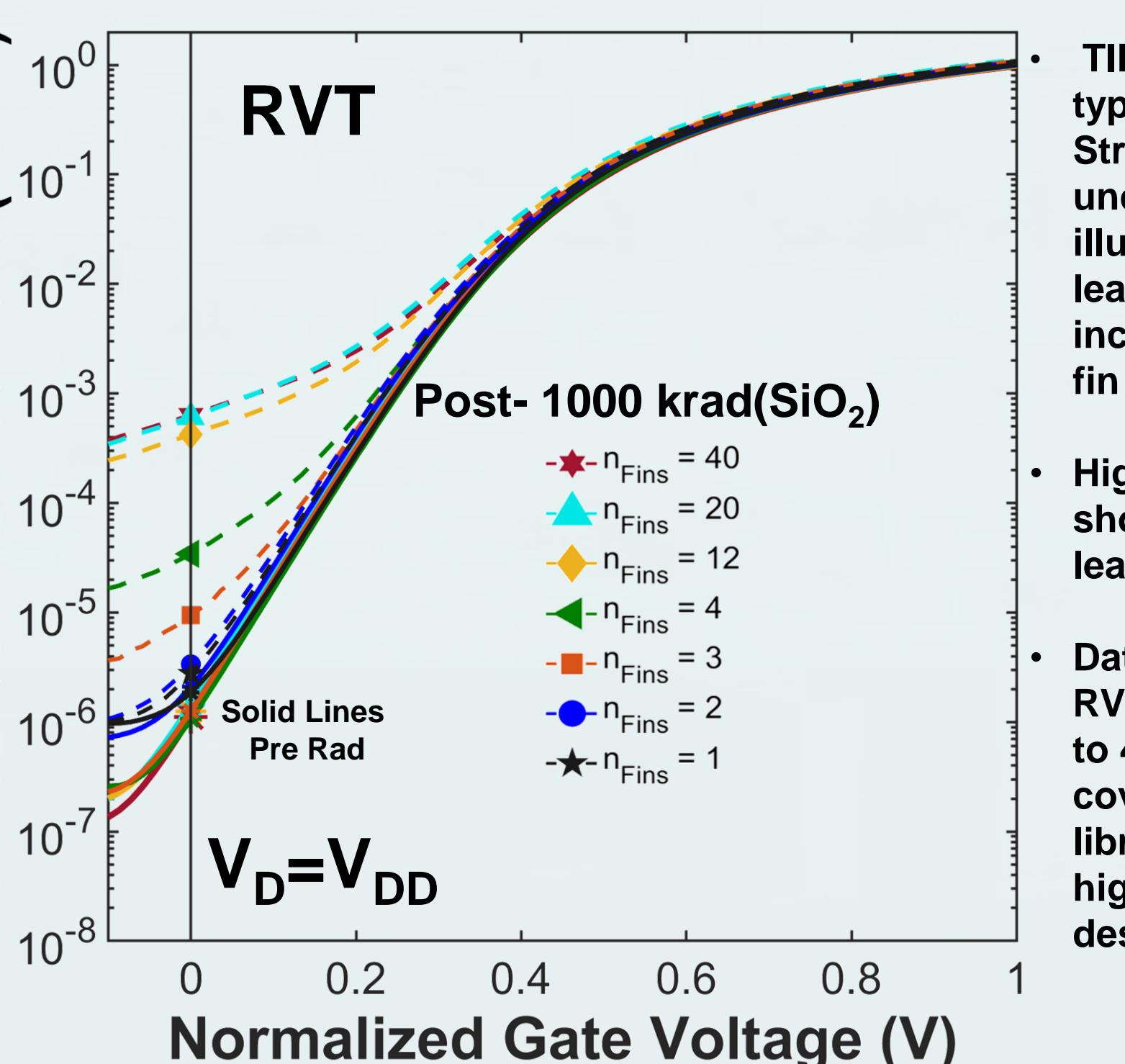

### TID induced leakage currents dependence on number of fins per transistor

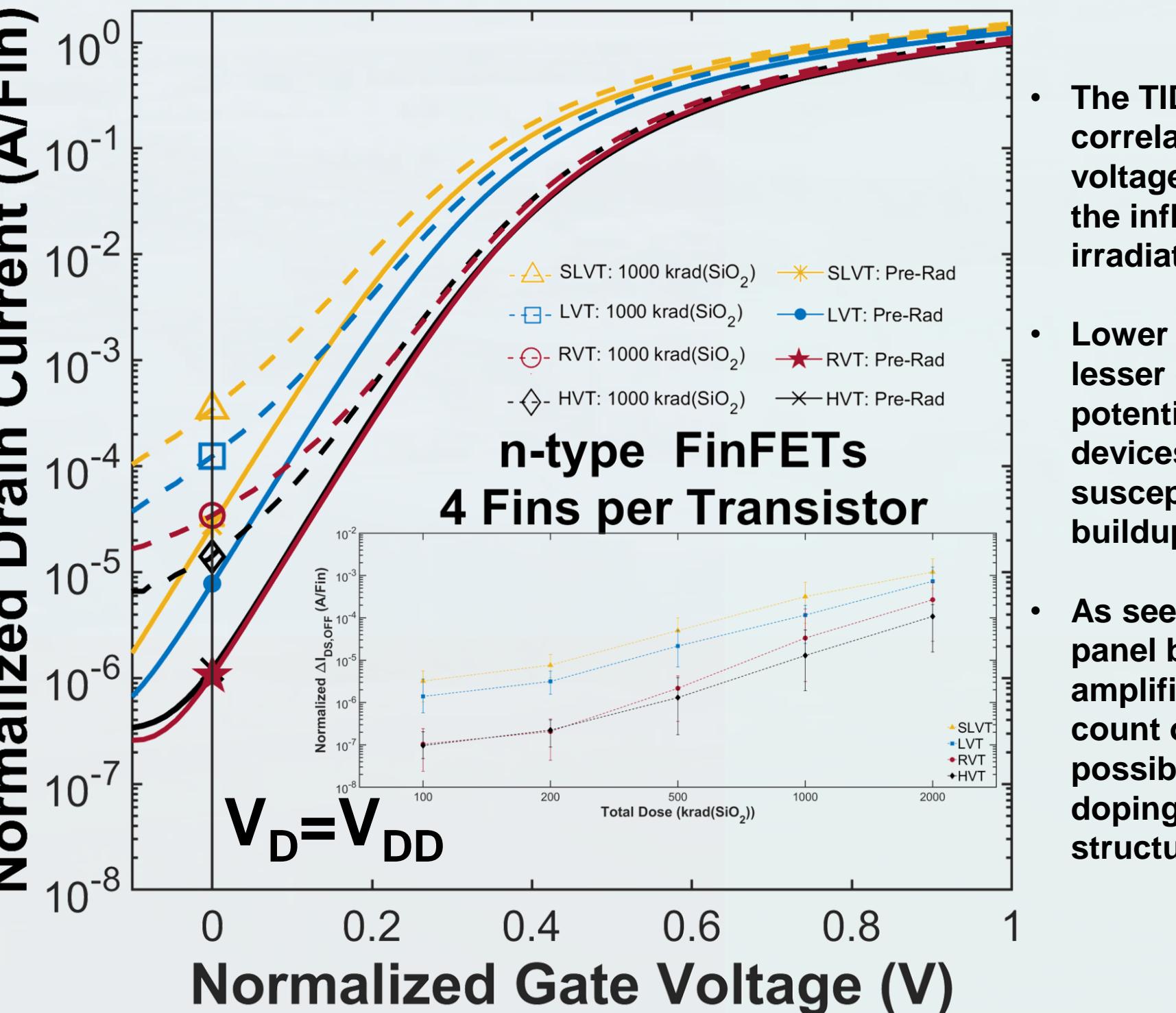

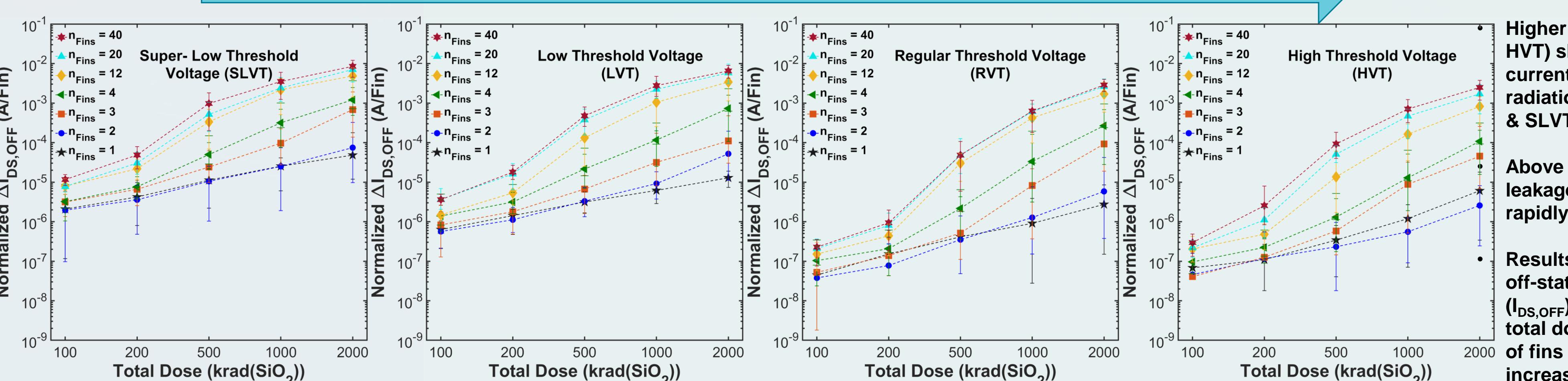

- The TID response strongly correlates with threshold voltage type, underscoring the influence of VT on post-irradiation sub-fin leakage.

- Lower VTs might suggest lesser doping in the sub-fin, potentially causing these devices to be more susceptible to oxide trap buildup.

- As seen in the figures in the panel below, increasing VT amplifies the impact of fin count on TID sensitivity, possibly due to more varied doping distribution across fin structures.

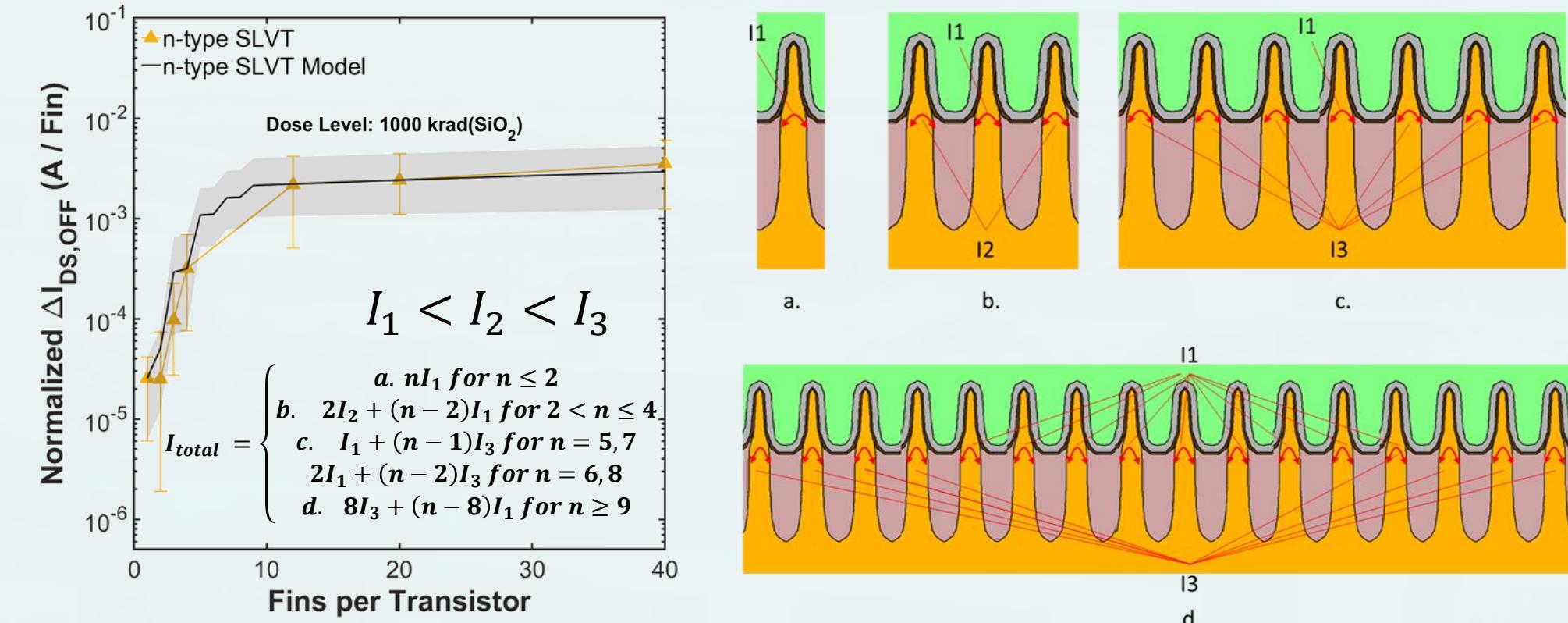

## MODEL RESULTS

- Variability in STI stress across a multi-fin transistor may lead to different trapping precursor densities or local electrical field which may cause variations in trapped charge build-up.

- A mathematical model was created to account for the potential strain-induced variability.

## ADDITIONAL TEST RESULTS

### TID Performance vs Device Area

- P-type device across all VTs and RVT nfins1, 40 showed no negligible TID degradation.

- The longer gate lengths tested were more tolerant to TID.

- Medium thick oxide FETs had negligible response to TID, except when using many fins in one transistor.

- Best way to minimize TID induced leakage is to use fewer fins per transistor, which comes with some area trade-off.

## CONCLUSIONS

- TID response in n-channel transistors varies with threshold voltage (VT) and number of fins per transistor.

- High VT (RVT and HVT) transistors showed greater robustness to TID degradation.

- Fewer fins per transistor enhance TID resistance, making these configurations more radiation-tolerant.

- p-Channel structures across all VT variants displayed significant resistance to TID damage up to 2000 krad(SiO2).

### Major Findings: The TID-induced increase in off-state leakage current is strongly affected by both the process threshold voltage (VT) and by the number of fins per transistor ( $n_{Fins}$ )

#### 12LP core transistor threshold voltage (VT) increases

Average off-state drain-source leakage ( $I_{DS, OFF}$ ) current at 0, 100, 200, 500, 1000, and 2000 krad(SiO<sub>2</sub>) of individual n-type transistors with 1, 2, 3, 4, 12, 20, and 40 fins per transistor for SLVT, LVT, RVT, and HVT threshold voltages. Error bars represent the min and max values.