BNL-65754

Informal Report

**TOWARDS A MORE ACCURATE EXTRACTION OF THE

SPICE NETLIST FROM MAGIC BASED LAYOUTS\***

Gianluigi De Geronimo

Brookhaven National Laboratory

Upton, NY 11973-5000

**RECEIVED**

NOV 05 1998

**OSTI**

August, 1998

*Just Master*

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

\*This research was supported under Contract No. DE-AC02-98CH10886.

#### **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, not any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency, contractor, or subcontractor thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency, contractor or subcontractor thereof.

Printed in the United States of America

Available from

National Technical Information Service

U.S. Department of Commerce

5285 Port Royal Road

Springfield, VA 22161

## **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

# **Index**

|                                                                                 |          |

|---------------------------------------------------------------------------------|----------|

| <b>Introduction.....</b>                                                        | <b>2</b> |

| <b>Step 1 - From the Layout to the .EXT file .....</b>                          | <b>2</b> |

| The information contained in the .EXT file .....                                | 2        |

| The errors contained in the .EXT file.....                                      | 2        |

| A solution which globally corrects all the type 1 and type 2 errors.....        | 2        |

| <b>Step 2 - From the .EXT file to the .CIR file (Ext2spice) .....</b>           | <b>2</b> |

| The Ext2spice program .....                                                     | 2        |

| Capacitor Extraction .....                                                      | 2        |

| FET Extraction.....                                                             | 2        |

| Resistor Extraction.....                                                        | 2        |

| <b>Step 3 - Corrections and Improvements (ext2spice.corr) .....</b>             | <b>2</b> |

| Ext2spice.corr .....                                                            | 2        |

| Improvements in the extraction of the Resistors .....                           | 2        |

| Improvements in the extraction of the FETs .....                                | 2        |

| Improvements in the extraction of the Linear Capacitors.....                    | 2        |

| Extraction of the resistance of the Metal lines .....                           | 2        |

| <b>Conclusions.....</b>                                                         | <b>2</b> |

| <b>Appendix A - Connect and extract sections.....</b>                           | <b>2</b> |

| <b>Appendix B - Linear capacitor fringing capacitance.....</b>                  | <b>2</b> |

| <b>Appendix C - Introduction of the additional plane and layer.....</b>         | <b>2</b> |

| <b>Appendix D - Ext2spice Manual (by Lloyd Clonts) .....</b>                    | <b>2</b> |

| <b>Appendix E - Ext.defs support file for Ext2spice (by Lloyd Clonts) .....</b> | <b>2</b> |

| <b>Appendix F - Ext2spice.corr code.....</b>                                    | <b>2</b> |

| <b>Appendix G - Technology File: Summary of Replacements and Additions.....</b> | <b>2</b> |

## ***Introduction***

The extraction of the SPICE netlist from MAGIC based layouts is investigated. It is assumed that the layout is fully coherent with the corresponding mask representation<sup>1</sup>.

The process of the extraction can be made in three steps:

- step 1: extraction of .EXT file from layout, through MAGIC command *extract*

- step 2: extraction of the netlist from .EXT file through *ext2spice* extractor

- step 3: correction of the netlist through *ext2spice.corr* program.

Each of these steps introduces some approximations, most of which can be optimized, and some errors, most of which can be corrected. Aim of this work is the description of each step, of the approximations and errors on each step, and of the corresponding optimizations and corrections to be made in order to improve the accuracy of the extraction.

The HP AMOS14TB 0.5 $\mu$ m process with linear capacitor and silicide block options and the corresponding SCN3MLC\_SUBM.30.tech27 technology file will be used in the following examples.

This work was supported by the US Department of Energy, Contract No. DE-AC02-98CH10886.

### ***Step 1 - From the Layout to the .EXT file***

The MAGIC command *extract* provides the extraction of the layout according to some information contained in the technology file. The technology file is composed of 17 sections (*tech*, *version*, *planes*, *types*, *contact*, *styles*, *compose*, *connect*, *cifoutput*, *cifinput*, *mzrouter*, *drc*, *extract*, *wiring*, *router*, *plowing*, *plot*) and the sections of interest for the extraction are the 8<sup>th</sup> (*connect*) and the 13<sup>th</sup> (*extract*).

The *connect* and the *extract* sections contained in the SCN3MLC\_SUBM.30.tech27 Technology File are reported in Appendix A. See MAGIC Maintainer's Manual #2 (Technology File Manual) for the formalism used in these sections.

### **The information contained in the .EXT file**

The circuit is always extracted by using three elements: the **node** element, the **capacitance between nodes** element, and the **FET** element.

---

<sup>1</sup> It is good practice to write into cif format (:cif MAGIC command) and to read from the written cif format (:cif read MAGIC command) the layout before the extraction.

### a) Node Element

Each  $\lambda \times \lambda$  tile of the layer is part of a node. The node is determined through the information contained in the *connect* section of the technology file. If each tile is *connected* to the adjacent one, both tiles are part of the same node. To each node element corresponds a line in the .EXT file which looks as follows:

node *nodename* *R C X Y layer a1 p1 a2 p2 a3 p3 .....*

where:

***nodename*** is the label of that node. MAGIC assigns an arbitrary name if there is no label on that node.

***R*** is the resistance of the node and it is calculated according to the formula:

$$\begin{cases} R = \sum_i R_i \\ R_i = \frac{RSQ_i}{2} \left[ \frac{P_i^2}{4A_i} - 2 + \sqrt{\left( \frac{P_i^2}{4A_i} - 2 \right) - 4} \right] \end{cases} \quad (1)$$

where  $RSQ_i$  is the resistance per square of the  $i^{\text{th}}$  layer, and its value in mOhm/square (default=0) is given in the *extract* section under the corresponding keyword *resist* (giving the precedence to the upper plane in case a layer is represented in more than one plane, as it is for the contacts),  $A_i$  and  $P_i$  are respectively the total area and the total perimeter of the  $i^{\text{th}}$  layer. The value of  $R$  is expressed in Ohm and it is approximated to the nearest integer. This formula gives an exact value only for rectangular sections composed of a single layer. The resistance is always calculated along the longest direction of the rectangle. In all other cases  $R$  represents a bad approximation and for this reason  $R$  is ignored during Step 2 of the extraction. As a consequence, the values reported in the *extract* section under the keyword *resist* are not determinant for the extraction.

***C*** is the capacitance between the node and the substrate and it is calculated according to the formula:

$$\begin{cases} C = \sum_i C_i \\ C_i = ACAP_i \times A_i + PCAP_i \times P_i \end{cases} \quad (2)$$

where  $ACAP_i$  and  $PCAP_i$  are respectively the capacitance per  $\lambda^2$  associated to the area and the capacitance per  $\lambda$  associated to the perimeter (fringing) of the  $i^{\text{th}}$  layer, and their values in aF (default=0) are given in the *extract* section respectively under the keywords *areacap* and *perimcap* (see the Manual for the formalism),  $A_i$  and  $P_i$  are respectively the total area and the total perimeter of the  $i^{\text{th}}$  layer. The value of  $C$  is expressed in aF and it is approximated to the nearest integer. In most cases  $C$  represents a good approximation and for this reason it is taken into account dur-

ing Step 2 of the extraction. As a consequence, the values reported in the *extract* section under the keywords *areacap* and *perimcap* are determinant for the final extraction and their value must be accurately verified and updated through the General Process Specifications and the Beta Technology Files and the MOSIS Parametric Test Results.

*X Y* are the coordinates of the node in units of  $\lambda$ . For single layer nodes, the low corner of the most left side is assumed as origin. For multiple layer nodes, the low left corner of the most down among the most left contacts is assumed as origin.

*layer* is the name of one of the layers of the node. For single layer nodes, it is the name of that layer. For multiple layer nodes, it is the name of the contact the corner of which is assumed as origin.

*a1 p1 a2 p2 a3 p3 ...* are respectively the area and the perimeter of the layers of the node which belong to the resist-classes 1, 2, 3 ... where resist-class 1 is the first line with keyword *resist* in the *extract* section, class 2 is the second line with keyword *resist* and so on. In the technology file used here for the examples, there are 6 resist-classes. The values *a1, p1, a2, p2, ...* are used for the evaluation of the resistance of the node but not for the evaluation of its capacitance. As a consequence these values are not determinant for the final extraction.

### *b) Capacitance Element*

If two or more nodes are present in the layout, the capacitance between each couple of nodes (if  $> 0$ ) is extracted, and reported through the capacitance element. The corresponding line in the .EXT file looks as follows:

*cap nodename1 nodename2 C*

where:

*nodename1 nodename2* are the labels of the two nodes; MAGIC uses an the arbitrary names if there is no label.

*C* is the capacitance between the two nodes, in aF.

The capacitance between two nodes is evaluated only in the following cases:

- a layer of one node overlaps a layer of the other node and the two layers belong to different planes; the corresponding keyword in the *extract* section is *overlap* ( $aF/\lambda^2$ ), and includes the possibility of a shield layer between the two layers (see Manual); if this capacitance is extracted for a given area, an equal area is subtracted in the evaluation of the node capacitance to substrate for the layer belonging to the upper plane, which is correct;

- a layer of one node is adjacent to a layer of the other node and the two layers belong to different planes; the corresponding keyword in the *extract* section is *sideoverlap* ( $aF/\lambda$ ) and in-

cludes the possibility of a shield between the two layers; if this capacitance is extracted for a given perimeter, an equal perimeter is subtracted in the evaluation of the node capacitance to substrate for the layer belonging to the upper plane, which is correct;

- a layer of one node is close, but not adjacent, to a layer of the other node and the two layers belong to the same plane; the corresponding keyword in the *extract* section is *sidewall* (aF, and must be calculated by using the factor  $2 \times \lambda_w / \lambda_d$  where  $\lambda_d$  is the distance and  $\lambda_w$  the width); the capacitance is extracted only if the distance between the adjacent layers is below the value reported under the *sidehalo* keyword at the beginning of the *extract* section.

c) *FET Element*

If two nodes are connected through a specific layer, and it exists a corresponding *fet* line with the specified layer indicated in the 2<sup>nd</sup> element under the corresponding keyword *fet* in the *extract* section (see Manual), a FET is extracted, the gate of which is the specific layer. The corresponding line in the .EXT file looks as follows:

```

fet model X Y X+1 Y+1 a p snode gatenodename gatewidth 0 nodename1 width1 jlabel1 node-name2 width2 jlabel2

```

where:

**model** is the name of the model of the FET, as specified in the 5<sup>th</sup> element under the corresponding keyword *fet* in the *extract* section.

**X Y X+1 Y+1** are the Cartesian coordinates and the Cartesian coordinates plus 1 of the low left corner gate layer in units of  $\lambda$ .

**a p** are respectively the area and the perimeter of the gate

**snode** is the label of the node at which the substrate must be considered connected, as specified in the 6<sup>th</sup> element under the corresponding keyword *fet* in the *extract* section. The [7<sup>th</sup>] facultative element under the corresponding keyword *fet* in the *extract* section considers the connection of the body to a well, when the well is superposed to the channel of the FET (see Manual).

**gatenode** is the label of the gate node; **gatewidth** is the width of the gate contact (i.e. the length of the channel of the FET) in units of  $\lambda$ .

**nodename1, nodename2** are respectively the labels of the drain and of the source, the layer (and number) of which are specified in the 3<sup>rd</sup> (and 4<sup>th</sup>) element under the corresponding keyword *fet* in the *extract* section (see the Manual), **width1, width2** are respectively the widths of the drain and of the source (i.e. the lwidth of the channel of the FET) in units of  $\lambda$  and **jlabel1, jlabel2** are respectively the labels at the drain and at the source junction (in the layout these labels must be followed by the "\$" symbol). According to the Magic extraction criteria, during Step 1 the drain junction of each finger is the one at the left or below the gate. This criteria for the choice of the

drain is not determinant for the final extraction because, as it will be discussed, during Step 2 the side with the *jlabel* S\$ is assumed as source and the one with the *jlabel* D\$ is assumed as drain, disregarding the orientation of the gate.

### The errors contained in the .EXT file

Three **errors** are made during Step 1 in the evaluation of the capacitance for the node and capacitance element.

**Type 1 Error.** An over-estimation is made by the extractor when two or more layers of the same node and belonging to different planes are overlapped. The error is due to the fact that the capacitance of the upper layers to the substrate is in most cases added, but its value should be zero because of the shield of the lower layer.

This is the case for example of all the contact layers (pc, ndc, pdc, nsc, psc, cwc), which are characterized by the fact that lie both in the *active* plane and in the *m1* plane (see Manual). In the evaluation of the capacitance of the area to the substrate, both the planes are considered, but only the *active* plane should be considered because the *m1* plane is shielded by the *active* plane.

In the evaluation of the capacitance of the perimeter to the substrate, both the planes are considered, but only the *active* plane should be considered because the *m1* plane is shielded, except when the contact layers are along the perimeter of the node.

Both problems could be corrected by suitably modifying few lines of the *extract* section, as shown. The line<sup>2</sup>

```

areacap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

2.700

```

must be replaced with the line

```

areacap (m1,m2c/m1)/metal1 2.700

```

which means that no capacitance to substrate is calculated for the part of the contact lying in the metal1 plane.

The line

```

perimc (ndc/a,nsc/a,pdc/a,psc/a,pc/a,cwc/a)/active (ndiff,nsd,pdiff,psd,poly,cwnsd)/active

-9.300

```

(note the minus sign) must be added, which means that, if the contact is not along the perimeter of the node, the capacitance of that perimeter to the substrate is adjusted to be zero.

---

<sup>2</sup> Don't be surprised if sometimes the name of a layer is reported more than once in the same group of a line in the Technology File (for example cwc/m1 appears twice in this case). The origin of this redundancy is at the Technology File generation level (ask Anand Kandasamy for details), but it is without consequence for the extraction.

### Example 1

From .EXT file:

node "a\_82\_n45#" 7 136410 82 -45 p 0 0 0 0 15000 600 2500 200 0 0 0 0

resistance from Eq.(1):

$$\frac{\left(\frac{P_1^2}{4 \cdot A_1} - 2\right) + \sqrt{\left(\frac{P_1^2}{4 \cdot A_1} - 2\right)^2 - 4}}{2} \cdot 1.8 + \frac{\left(\frac{P_2^2}{4 \cdot A_2} - 2\right) + \sqrt{\left(\frac{P_2^2}{4 \cdot A_2} - 2\right)^2 - 4}}{2} \cdot 0.07 = 6.788$$

capacitance from Eq.(2):  $A_1 \cdot 7.92 + P_1 \cdot 15 + A_2 \cdot 2.7 + P_2 \cdot 9.3 = 136410$

which is over-estimated. After the modification of the technology file, it results from .EXT file:

node "a\_82\_n45#" 7 128265 82 -45 p 0 0 0 0 15000 600 2500 200 0 0 0 0

capacitance from Eq.(2):  $A_1 \cdot 7.92 + P_1 \cdot 15 + (P_2 - 50 - 50 - 50) \cdot 9.3 = 128265$

and it is a better approximation.

It is worth noting that this is only a partial solution of the problem, and it is subject to errors. For example when a *m1* line connected to the contact flows above the active layer of that contact, its capacitance to the substrate is erroneously added. An alternative solution not subject to errors will be proposed in the next section.

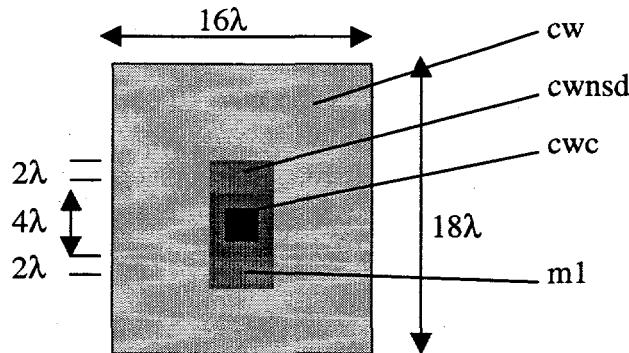

**Type 2 Error.** In the case of *contacts*, *metals* and *poly* which flow over a *well* and are connected to that well (i.e. are parts of the same node), the area and perimeter capacitances to substrate of the metal and poly as well as the part of the perimeter capacitance to substrate of the contact adjacent to the well are added (no overlap or sideoverlap to the well and consequent subtraction occurs, because the well is part of the same node). This is an error because all these layers are shielded by the well.

To give a simple example, the linear capacitors can be considered, where the perimcap capacitance to substrate of *cwc* (the well contact) along the perimeter which is not adjacent to the *cwnsd* (the n-diffusion) as well as the area and perimeter capacitance to substrate of a metal connected to the *cwc* are erroneously added.

In the case of linear capacitors, a partial solution of the problem can be obtained by introducing the following additional changes in the *extract* section.

The line:

```

perimc (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 9.300

```

must be replaced with the line (the layer *cwc/m1* is deleted):

```

perimc (m1,ndc/m1,nsc/m1,pdc/m1,psc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 9.300.

```

The line added to correct the Error 1

```

perimc (ndc/a,nsc/a,pdc/a,psc/a,pc/a,active (ndiff,nsd,pdiff,psd,poly,cwnsd)/active

-9.300

```

must be replaced with the line:

```

perimc (ndc/a,nsc/a,pdc/a,psc/a,pc/a)/active (ndiff,nsd,pdiff,psd,poly)/active -9.300

```

### Example 2

From .EXT file:

```

node "w_246_n38#" 0 2606.88 246 -38 cw 0 0 0 0 0 24 20 0 0 0 0

```

capacitance from Eq.(2):  $A1 \cdot 8.46 + P1 \cdot 0 + A2 \cdot 2.7 + P2 \cdot 9.3 = 2606.88$

which is over-estimated. After the further modification of the technology file, it results from .EXT file:

node "w\_246\_n38#" 0 2532.48 246 -38 cw 0 0 0 0 0 0 24 20 0 0 0 0

capacitance from Eq.(2):  $A1 \cdot 8.46 + P1 \cdot 0 + A2 \cdot 2.7 + (P2 - 4 - 4) \cdot 9.3 = 2532.48$

and it is a better approximation.

It is worth noting that an over-estimating error due to the capacitance of the metal to substrate is still present. The solution proposed in the next section will solve also this problem.

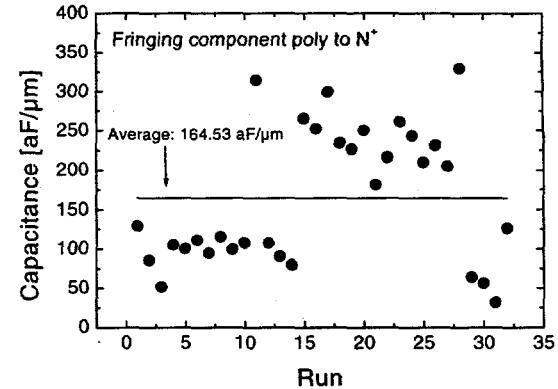

**Type 3 Error.** In the case of linear capacitors, the sideoverlap capacitance between *wcap* (the active area of the capacitor) and *cwnsd* (the diffusion) and the sideoverlap capacitance between *poly* and *capwell* (the well of the capacitor) are considered under the same *sideoverlap* keyword. This is an error because they are characterized by different thickness of the oxide and then subject to two different values of  $aF/\lambda$ . To solve this problem the following changes must be made.

The line:

```

sideoverlap (poly,pres,wcap,pc/a,wcap,pc/a)/active

~(poly,pres,wcap,pc/a,wcap,pc/a)/active ~space/w 15

```

must be replaced with the line:

```

sideoverlap (poly,pres,wcap,pc/a,wcap,pc/a)/active

~(poly,pres,wcap,pc/a,wcap,pc/a,cwnsd)/active ~space/w 15

```

and the line

```

sideoverlap (wcap)/active (cwnsd)/active ~space/w 40

```

must be added, where the value 40  $aF/\lambda$  can be deduced from a simulation, from a suitably equation or from the MOSIS Parametric Test Results (see Appendix B).

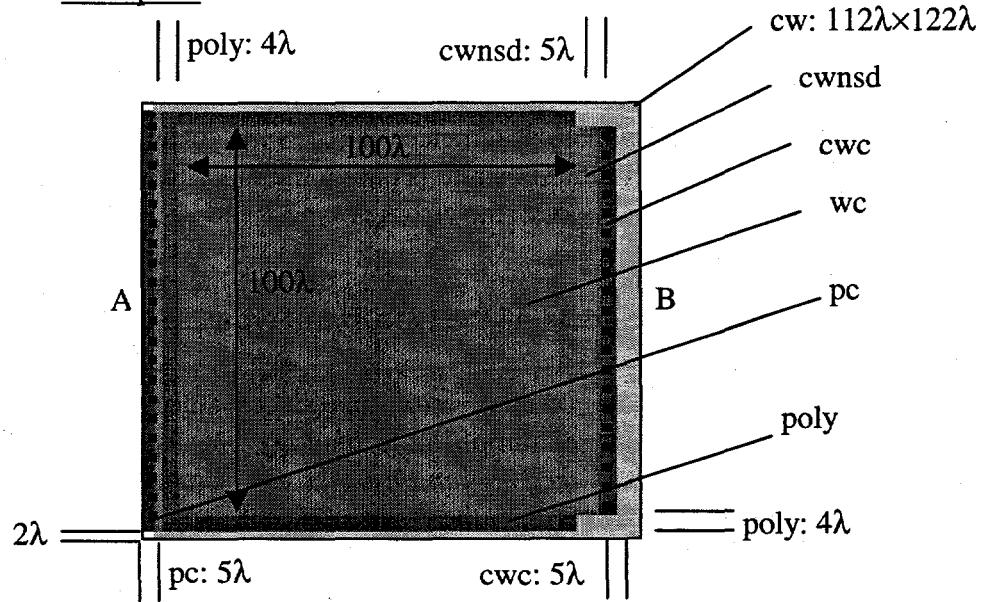

Example 3

From .EXT file:

```

node "A" 3 5336.28 141 -18 pc 0 0 0 0 11772 434 540 226 0 0 0 0

node "B" 1 115597 144 -20 cw 0 0 0 0 0 500 210 0 0 0 0

cap "A" "B" 2.09531e+06

```

Capacitances from Eq.(2):  $A1 \cdot 7.92 + P1 \cdot 15 + P1 \cdot 9.3 = 5336.28$ ,

$A2 \cdot 8.46 = 115597.44$ ,

which are correct.

Internodal capacitance:  $A3 \cdot 207.9 + (A4 - A3) \cdot 7.92 + P4 \cdot 15 + P5 \cdot 9.3 = 2095305.36$ ,

which is under-estimated due to Error 3.

After the further modification of the technology file, it results from the .EXT file:

```

node "A" 3 5336.28 141 -18 pc 0 0 0 0 11772 434 540 226 0 0 0 0

node "B" 1 115597 144 -20 cw 0 0 0 0 0 500 210 0 0 0 0

cap "A" "B" 2.09781e+06

```

Internodal capacitance:

$$A3 \cdot 207.9 + (A4 - A3) \cdot 7.92 + (P4 - 100) \cdot 15 + P5 \cdot 9.3 + 100 \cdot 40 = 2097805.36$$

which is a better (indeed with negligible difference in this case) approximation.

It is worth noting that, in this case, the solution adopted is effective in the correction of the error in the evaluation of the internodal capacitance. On the other hand, the absence of errors in the evaluation of the capacitance to the substrate is due to the modifications introduced in the *extract* section of the technology file to correct the errors of type 1 and 2.

### A solution which globally corrects all the type 1 and type 2 errors

It has been shown that the three types of errors introduced during Step 1 can be partially corrected by modifying the *extract* section of the technology file. Apart from the correction of the error of type 3, which *must be introduced in any case* and it represents a global correction, the other modifications correct only partially the errors of type 1 and 2.

A different approach to globally correct **all** the errors of type 1 and 2 is now discussed. This approach is based on the introduction of an additional plane (we will call it “substrate”) and of an additional layer (we will call it “substrate” or “ss”) which lies in the additional substrate plane. By using this additional layer the capacitances to substrate are now evaluated as *overlap* and *sideoverlap* capacitances, instead of *areacap* and *perimc* capacitances. The main advantage is that the shielding layers (available only with the *overlap* and *sideoverlap* keywords) can now be used for the capacitances to substrate. Another advantage is that the new layer, which must be present in all the layout under extraction, can be divided into areas thus allowing the simulation of the resistance of the substrate from one point to another of the layout. This additional layer must be also invisible at the CIF extraction level. The modifications which must be made in the technology file to introduce and use the additional plane and layer are discussed in the Appendix C. A label SS can be given to the additional node the layer of which is ss.

#### Examples

By applying the modified technology to **Example 1** it follows from the .EXT file:

without the ss layer (note the zero value capacitance)

```

node "a_82_n172#" 7 0 82 -172 p 0 0 0 0 15000 600 2500 200 0 0 0 0

```

With the ss layer (note that the capacitance to substrate is now represented by the capacitance element, while the node elements are ignored during the step 2 of the extraction because their capacitance is zero)

```

node "a_82_n172#" 7 0 82 -172 p 0 0 0 0 15000 600 2500 200 0 0 0 0

node "SS" 0 0 74 -184 ss 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

cap "a_82_n172#" "SS" 128265

```

By applying the modified technology to **Example 2** it follows from the .EXT file:

Without the ss layer (note the zero value capacitance)

```

node "w_246_n38#" 0 0 246 -38 cw 0 0 0 0 0 24 20 0 0 0 0

```

With the ss layer (again note that the capacitance to substrate is now represented by the capacitance element)

```

node "w_246_n38#" 0 0 246 -38 cw 0 0 0 0 0 24 20 0 0 0 0

node "SS" 0 0 245 -39 ss 0 0 0 0 0 0 0 0 0 0 0 0

cap "w_246_n38#" "SS" 2436.48

```

and now the result is now correct:  $A1 \cdot 8.46 = 2436.48$

By applying the modified technology to **Example 3** it follows from the .EXT file:

Without the ss layer (note the zero value capacitance)

```

node "A" 3 0 141 -18 pc 0 0 0 0 11772 434 540 226 0 0 0 0

node "B" 1 0 144 -20 cw 0 0 0 0 0 500 210 0 0 0 0

cap "A" "B" 2.09781e+06

```

With the ss layer (again note that the capacitances to substrate is now represented by the capacitance element)

```

node "A" 3 0 141 -18 pc 0 0 0 0 11772 434 540 226 0 0 0 0

node "B" 1 0 144 -20 cw 0 0 0 0 0 500 210 0 0 0 0

node "SS" 0 0 134 -25 ss 0 0 0 0 0 0 0 0 0 0 0 0

cap "A" "SS" 5336.28

cap "A" "B" 2.09781e+06

cap "B" "SS" 115597

```

## **Step 2 - From the .EXT file to the .CIR file (Ext2spice)**

The Ext2spice program provides the extraction of the Spice netlist from the Magic.EXT file. The Ext2spice program here considered was released by Lloyd Clonts (Oak Ridge National Laboratory) in June 23<sup>rd</sup> 1998<sup>3</sup>.

### **The Ext2spice program**

The Ext2spice program runs with the command line:

```

ext2spice [options] nomofile.ext

```

and the output (-g option) are two files:

|                       |                                                                                                         |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| <i>nomofile.cir</i>   | Spice netlist containing options, sources, library lines and the line<br>.include <i>nomofile.spice</i> |

| <i>nomofile.spice</i> | Spice netlist containing the elements extracted from the .EXT file                                      |

The netlist containing the elements extracted from the .EXT file will be discussed, element by element, in the next sections. Information about the options can be found in the Ext2spice manual (Appendix D). Ext2spice uses a support file called Ext.defs (Appendix E) the role of which will be discussed in the next sections. In the Ext.defs file are also contained the Spice command lines which will appear in the .cir file.

### **Capacitor Extraction**

The capacitors from the node element and from the capacitance element of the .EXT file are reported in the .spice file.

In particular, to each node element in the .EXT file

```

node nodename R C X Y layer a1 p1 a2 p2 a3 p3 .....

```

it corresponds in the .spice file the element

```

Cx newnodename $G_Vsub! C

```

---

<sup>3</sup> In the original release (1QT 1998) some errors were found, which have been corrected by Lloyd under our stimulus, generating the new release here discussed.

where  $C_x$  is an arbitrary name and  $newnodename$  is equal to  $nodename$  if the node has a label or an arbitrary node number (indeed much shorter than the arbitrary node names used by Magic in the .EXT file) if there is no label on that node. The line "Vsubstr \$G\_Vsub! 0 DC 0V" is added by Ext2spice (-D option) to insure the connection of the global substrate node \$G\_Vsub!.

To each capacitance element in the .EXT

```

cap nodename1 nodename2 C

```

it corresponds, in the .spice file, the element

```

Cx newnodename1 newnodename2 C

```

where  $C_x$  is the name of the element according to the general device labeling (see Ext2spice Manual) or an arbitrary name if there is no label on that element;  $newnodename1$  ( $newnodename2$ ) is equal to  $nodename1$  ( $nodename2$ ) if the node has a label or an arbitrary node numbers (much shorter than the arbitrary node name used in the .EXT file) if there is no label on that node.

It is worth pointing out that a capacitance is reported only if it is not floating and if its value is higher than the value indicated with the option  $-c cmin$  (default minimum: 1fF). All the values of these capacitances (linear, parasitics, ...) are reported as well. The accuracy in their value is related to the accuracy of their extraction during Step 1.

## FET Extraction

All the FETs from the fet element of the .EXT file are reported in the .spice file.

In particular, to each fet element in the .EXT file (with some exceptions discussed in the next sections, such as in the case of the extraction of resistors)

```

fet model X Y X+1 Y+1 a p snode gatenodename gatewidth 0 nodename1 width1 jlabel1

nodename2 width2 jlabel2

```

it corresponds in the .spice file the element

```

Mx newdrainnodename newgatenodename newsourcenodename substratenodename

newmodel [M=m] W=w L=l AD=ad PD=pd AS=as PS=ps [NRG=nrg NRD=nrd

NRS=nrs]

```

If the  $-mm$  option is used, multifinger FETs are merged in a single FET by adding the  $M=m$  term, where  $m$  is the number of fingers.

*Mx* is the name of the element according to the general device labeling (see Ext2spice Manual) or an arbitrary name if there is no label on that element;

*newgatenodenname* is equal to *gatenodenname* if the node has a label or an arbitrary node numbers (much shorter than the arbitrary node name used by Magic in the .EXT file) if there is no label on that node.

*newdrainnodename* *newsourcenodenname* respectively the drain (to which the area AD and the perimeter PD are associated) and the source name (to which the area AD and the perimeter PD are associated), are equal to *nodename1* and *nodename2* with a order which, if *jlabel1* and *jlabel2* are zero, depends on the orientation of the FET. The drain node is chosen according to Magic extraction criteria where the drain junction of each finger is the one at the left or below the gate. On the contrary, if one *jlabel1* and/or *jlabel2* is labeled as D (or S) (remember that in the layout these labels must be followed by the "\$" symbol), the corresponding junction will be assumed as drain (or source). Attention must be paid to the fact that, for multifinger FETs, the junction label *jlabel* must lie in the same finger where is placed the label of the device, otherwise it will be ignored !

*substratenodenname* is equal to *snode*

In order to recognize the substrate node used in Ext2spice (\$G\_Vsub!) and to use the additional ss layer, the following changes must be made for n-channel FETs in the *fet* lines of the *extract* section:

```

# REPLACED fet nfet ndiff,ndc 2 nfet Gnd! pwell 15 324

fet nfet ndiff,ndc 2 nfet $$G_Vsub! pwell,ss 15 324

# REPLACED fet nfet ndiff,ndc 1 nfet Gnd! pwell 15 324

fet nfet ndiff,ndc 1 nfet $$G_Vsub! pwell,ss 15 324

```

A problem arises when the body must be connected to pwell. When the MAGIC extractor must choose between ss and pwell, it chooses ss (i.e. the layer with the lower planeorder), which is an error. A way to solve this problem is to delete the layer ss from the areas where nfet and pwell are simultaneously present. On the other hand, for most of the technologies that we use, the connection of the body of an n-channel FET to a pwell different from the p substrate is not allowed (i.e. the body of n-channel FETs is always connected to the substrate).

*newmodel* is equal to the model defined in the Ext.defs file with the lines:

```

def model newmodel M n

def model newmodel M p

```

where *model* is equal to *name* of the *fet* element in the .EXT file (see Tehcnology File Manual) and it is different for n-channel and p-channel devices

*w* is the gate width, ant it is equal to *width1* (= *width2*)

$l$  is the gate length, and it is equal to *gatewidth*

$ad$ ,  $pd$ ,  $as$  and  $ps$  are the areas and perimeters of drain and source respectively, and the layer to be used in this evaluation is the one indicated under the *resistclass* keyword in the extract section of the technology file. In particular:

the drain/source layer for n-channel devices is defined by using the Ext.defs line *nrclass n*, where  $n$  is the  $n^{\text{th}}$  *resistclass* line in the extract section;

the drain/source layer for p-channel devices is defined by using the Ext.defs line *prclass n*, where  $n$  is the  $n^{\text{th}}$  *resistclass* line in the extract section.

Note that, in order to correctly extract the areas and perimeters in our case, the original lines in the Ext.defs file:

```

prclass 1

nrclass 2

nwclass 3

pwclass 4

plrclass 5

```

must be replaced with the lines (we are not interested in the nwclass, pwclass and plrclass):

```

prclass 2

nrclass 1

nwclass 9

pwclass 9

plrclass 9

```

Note that, because the area and perimeter capacitances of the diffusions (*ndiff*, *pdiff*) and of the corresponding contacts (*ndc*, *pdc*) are included the FET model, the corresponding parasitics in the node and capacitance elements of the .EXT file must be set to zero. In order to achieve this result, the layers *ndiff*, *pdiff*, *ndc/a*, *pdc/a*, *ndc/m1* and *pdc/m1* must be deleted from all the *areacap*, *perimcap*, *overlap*, *sideoverlap* (not *sidewall*) lines in the *extract* section which contain these layers.

Note also that, according to the *extract* section lines:

```

resist (ndiff,anres,ndc/a,nsd,nsc/a)/active 1900

resist (pdiff,apres,pdc/a,psd,psc/a)/active 2000

```

the layers *anres*, *nsd*, *nsc/a*, *apres*, *psd*, *psc/a* take part in the calculus of the areas and perimeters. In order to avoid this error (consider for example the case of a FET diffusion connected to a n-well with a *nsc/a* all around it: the area and perimeter calculated will be strongly over-estimated!), the two lines must be replaced with the lines:

resist (ndiff,ndc/a)/active 1900

resist (pdiff,pdc/a)/active 2000

Ext2spice calculates correctly the areas also for multifinger FETs and for FETs which share a diffusion. For equal width FETs sharing a diffusion, it calculates the total area and divides it by the total number of fingers. For different FETs having different width and sharing a diffusion, the calculus is made in order to assign to each finger the same area per unit of width. For example, in the case of two FETs with widths  $W_1$  and  $W_2$  and number of fingers  $NF_1$  and  $NF_2$ , it results for the area per finger  $AF_2$  of the second FET:

$$AF_2 = \frac{Atot \frac{W_2}{W_1 + W_2}}{NF_1 \frac{W_1}{W_1 + W_2} + NF_2 \frac{W_2}{W_1 + W_2}} \quad (3)$$

where  $Atot$  is the total diffusion area. With an analog procedure, the perimeter is correctly calculated for multifinger FETs and for FETs which share a diffusion:

$$PF_2 = \frac{Ptot \frac{W_2}{W_1 + W_2}}{NF_1 \frac{W_1}{W_1 + W_2} + NF_2 \frac{W_2}{W_1 + W_2}} \quad (4)$$

If the *-mn* option is used, the number of squares of the gate NRG, drain NRD and source NRS of the FET are calculated for the evaluation of the corresponding parasitic resistances.

The parameter NRG is calculated only for the FET active area (nfet, pfet) and in the drain to source direction, which can be considered a bad approximation. Moreover, in the case of multifinger FETs, the NRG of a finger is equal to the number of squares of the active area of that finger divided by  $M$ , which is an error. Finally, it must be considered that SPICE uses the same resistance per square of the diffusion to calculate RG, RD and RS, which is another error.

The parameters NRD and NRS are calculated in the drain to source direction by using the drain and source areas and perimeters respectively. This approach introduces an approximation which is strongly dependent on the geometry of the diffusion areas. It introduces also an over-estimation because also the areas of the diffusion contacts are included in the calculus. Moreover, in the case of multifinger FETs, the NRD (NRS) of a finger is equal to the sum of the number of squares of the drain (source) divided by  $M^2$ , which is an error.

It is worth noting that, during the simulation, SPICE considers the RS, RG, RD as values per finger, and it divides these values by  $M$  for the simulation of the overall FET, which is the correct approach.

The Step 3 will provide a more accurate extraction of the parasitic resistances RG, RD and RS, by correcting the errors and by including the resistance of the contact.

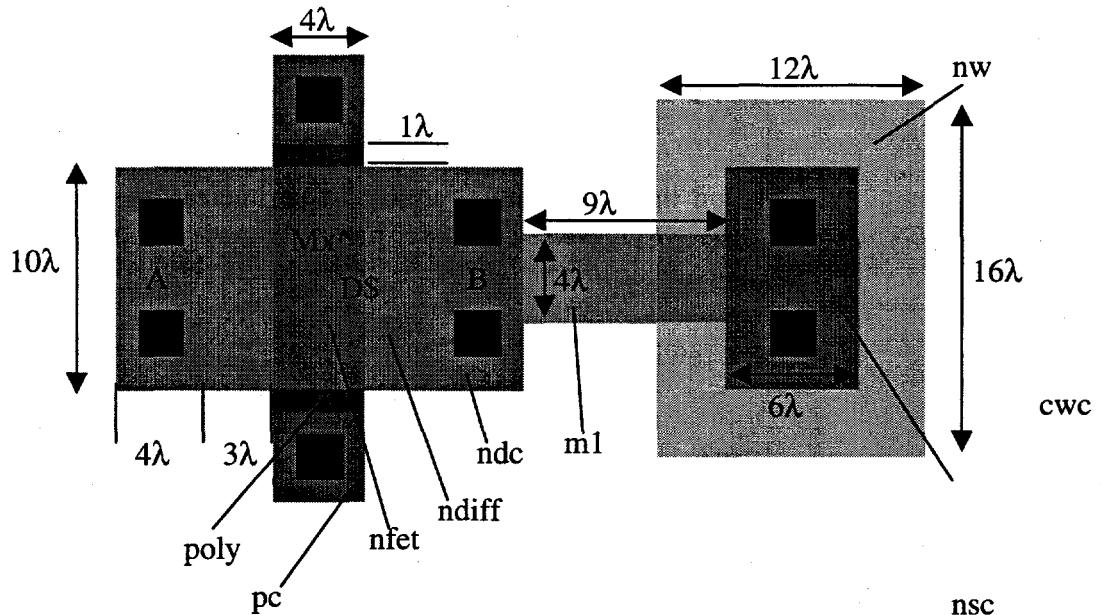

Example 4

From the .EXT file (we use the technology file modified as in Step 1, in its version with the ss layer) it results:

```

node "A" 3 0 59 31 ndc 70 34 0 0 0 0 40 28 0 0 0

node "C" 9 0 66 26 pc 0 0 0 0 80 48 32 32 0 0 0

node "B" 12 0 83 28 nw 130 66 0 0 0 0 136 70 0 0 0

node "SS" 0 0 55 23 ss 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

cap "C" "SS" 1080

cap "A" "SS" 167.4

cap "B" "SS" 1930.92

fet nfet 66 31 67 32 40 28 "Gnd!" "C" 8 "Mx" "A" 10 0 "B" 10 "D"

```

The capacitances of A and B nodes to substrate are over-estimated (for example the capacitance of the A node must be zero, because included in the FET model through the source area and perimeter) and the body of the FET is connected to Gnd! while should be connected to the substrate SS. After the further modifications of the technology file, it results from the .EXT file:

```

node "A" 3 0 59 31 ndc 70 34 0 0 0 0 40 28 0 0 0

node "C" 9 0 66 26 pc 0 0 0 0 80 48 32 32 0 0 0

node "B" 3 0 83 28 nw 70 34 0 0 0 0 136 70 0 0 0

node "SS" 0 0 55 23 ss 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

cap "C" "SS" 1080

cap "B" "SS" 1800.72

fet nfet 66 31 67 32 40 28 "SS" "C" 8 "Mx" "A" 10 0 "B" 10 "D"

```

which is correct both in terms of capacitances and of connections.

Now, from the .spice file (*-mn* option) it results:

```

Mx B C A SS CMOSN W=3.00U L=1.20U AD=6.30P PD=10.20U AS=6.30P PS=10.20U

+ NRG=0.40 NRD=0.70 NRS=0.70

C1 B SS 1.8F

C2 C SS 1.1F

```

and the capacitances, areas and perimeters are correctly extracted, while the NRG, NRD and NRS parameters are affected by the previously discussed errors.

#### Example 5

In this example two n-channel FETs (M1, gate  $10\lambda \times 2\lambda$ , 3fingers and M2, gate  $20\lambda \times 2\lambda$ , 2fingers) share the source.

From the .EXT file (we use the technology file modified as in Step 1 and in Step 2, in its version with the ss layer) it results:

```

node "A2" 7 0 107 31 ndif 120 52 0 0 0 0 80 48 16 16 0 0

node "A" 13 0 61 31 ndc 110 62 0 0 0 0 80 56 88 52 0 0

node "B" 26 0 68 31 ndif 470 164 0 0 0 0 240 152 168 100 0 0

node "C" 61 0 61 24 pc 0 0 0 0 320 212 224 128 0 0 0 0

node "C2" 60 0 100 24 pc 0 0 0 0 264 192 160 96 0 0 0 0

node "SS" 0 0 59 21 ss 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

cap "A" "SS" 243.96

cap "B" "C2" 248.48

cap "C" "SS" 5598

cap "A" "B" 627.33

cap "A2" "SS" 57.6

cap "B" "C" 248.48

```

```

cap "B" "SS" 399.96

cap "C2" "SS" 4075.68

cap "A2" "B" 359.28

cap "A2" "C2" 35.68

cap "A" "C" 248.48

fet nfet 113 31 114 32 40 44 "SS" "C2" 4 "M2" "A2" 20 "D" "B" 20 0

fet nfet 105 31 106 32 40 44 "SS" "C2" 4 0 "B" 20 0 "A2" 20 0

fet nfet 82 31 83 32 20 24 "SS" "C" 4 0 "A" 10 0 "B" 10 0

fet nfet 74 31 75 32 20 24 "SS" "C" 4 0 "B" 10 0 "A" 10 0

fet nfet 66 31 67 32 20 24 "SS" "C" 4 "M1" "A" 10 "D" "B" 10 0

```

Now, from the .spice file (-mm and -mn options) it results:

```

M1 A C B SS CMOSN M=3 W=3.00U L=0.60U AD=3.30P PD=6.20U AS=6.04P PS=7.03U

+ NRG=0.07 NRD=0.12 NRS=0.22

M2 A2 C2 B SS CMOSN M=2 W=6.00U L=0.60U AD=5.40P PD=7.80U AS=12.09P PS=14.06U

+ NRG=0.05 NRD=0.07 NRS=0.17

C1 A C 0.2F

C2 A2 C2 0.0F

C3 A2 B 0.4F

C4 C2 SS 4.1F

C5 B SS 0.4F

C6 B C 0.2F

C7 A2 SS 0.1F

C8 A B 0.6F

C9 C SS 5.6F

C10 B C2 0.2F

C11 A SS 0.2F

```

and the capacitances, areas and perimeters are correctly extracted, while the NRG, NRD and NRS parameters are again affected by errors. Note that in the perimeter calculation, the parts adjacent to the channel are included, which is a reasonable approach.

From Eq.(3) it results for the shared area:

$$\frac{(10.6 + 10.11 + 20.10 + 20.5) \cdot \frac{10}{20+10}}{3 \cdot \frac{10}{10+20} + 2 \cdot \frac{20}{10+20}} \cdot 3 \cdot 3 = 6.043$$

$$\frac{(10.6 + 10.11 + 20.10 + 20.5) \cdot \frac{20}{20+10}}{3 \cdot \frac{10}{10+20} + 2 \cdot \frac{20}{10+20}} \cdot 3 \cdot 3 = 12.086$$

From Eq.(4) it results for the shared perimeter:

$$\frac{(10+5+10+5+10+11+11+10+10+20+20+20+6+6) \cdot \frac{10}{20+10}}{3 \cdot \frac{10}{10+20} + 2 \cdot \frac{20}{10+20}} \cdot 3 = 7.029$$

$$\frac{(10+5+10+5+10+11+11+10+10+20+20+20+20+6+6) \cdot \frac{20}{20+10}}{3 \cdot \frac{10}{10+20} + 2 \cdot \frac{20}{10+20}} \cdot 3 = 14.057$$

## Resistor Extraction

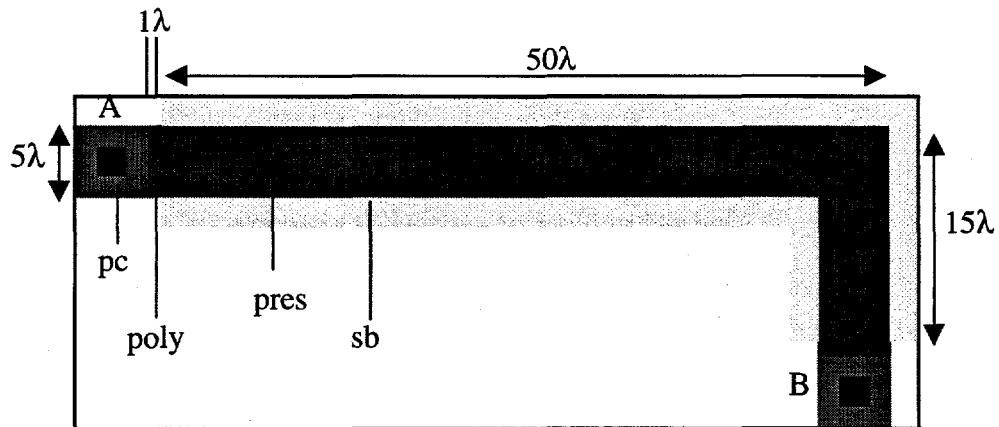

The Magic extractor doesn't have any additional element for the extraction of the resistors. As a consequence, the three basic elements (the *node* element, the *capacitance* element and the *fet* element) must be used for this purpose. A very simple technique for the extraction of the resistors is to extract these devices as particular FETs. This technique will be discussed here and applied to the case of a poly resistors with silicide block (*sb*).

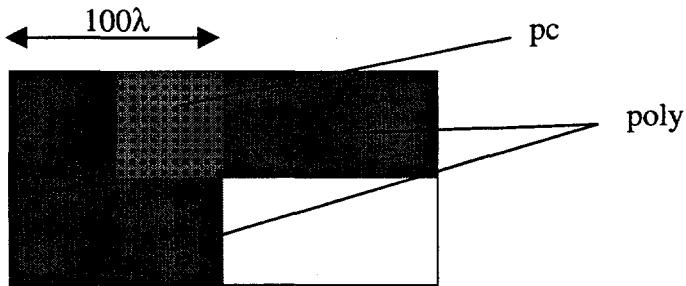

A poly resistor is composed of a polysilicon layer (*poly*) (the great part of which is subject to the silicide block *sb* (*pres*)), and by two polycontacts (*pc*). Till now, when a poly resistor is extracted, the two contacts and the *poly* appears as parts of the same node. The reason is the line:

*poly,pres,wcap,nfet,wcap,pfet,pc/a poly,pres,wcap,nfet,wcap,pfet,pc/a*

which is present in the *connect* section of the technology file and which "tells" the extractor that, when *poly*, *pres* and *pc* are in contact, they it must be considered connected each other (i.e. parts of the same node).

In order to extract the *pres* layer as a FET, this line must be replaced with the line:

*poly, wcap,nfet,wcap,pfet,pc/a poly, wcap,nfet,wcap,pfet,pc/a*

and the line:

*fet pres poly 2 polyres \$\$G\_Vsub! ss,nwell,pwell 0 0*

must be added in the *extract* section.

Ext2spice recognizes this "fet" as a resistance if the Ext.defs file contains the lines:

```

def polyres    RPOLY R r

distrib polyres RSQ 0.000 0 ecapp    SQ

distrib ecapp  CPAR 0.0 0

```

where RSQ is the resistance per square of *pres* ( $90\Omega$  in this technology) and CPAR is the parasitic capacitance (in  $fF/\mu m^2$ ) used in the *distributed model* (-d option, see Ext2spice Manual). The number of squares SQ of the extracted resistance is then calculated by Ext2spice, from the corresponding fet line in the .EXT file, by using the "channel" (*pres*) area and the "channel" width, according to the equation:

$$SQ = \frac{A}{W^2} \quad (5)$$

where W is the minimum between the widths of the "drain" and "source" connections (the *poly* adjacent to *pres* in this case). It turns out that the width of these connections is determinant for the correct extraction of the resistance.

In most cases the extracted SQ represents a good approximation of the value of the resistor. On the other hand, for a more accurate approximation:

- each corner along *pres* must be weighted with a factor 0.55 <sup>4</sup>;

- the real width of *pres* should be used, which is in general smaller than the drawn width;

- in the distributed case, the perimeter component of the parasitic capacitance is not included;

- the resistance of the *poly* near the *pc* should be added;

- the resistance of the *pc* should be added.

The Step 3 will provide a more accurate extraction, by including all these additional terms

#### Example 6

<sup>4</sup> R. L. Geiger, P. E. Allen, N. R. Strader, *VLSI*, McGraw-Hill, 1990, p.80

From the .EXT file (we use the technology file modified as in Step 1, in its version with the ss layer) it results:

```

node "a_n21_31#" 0 0 -21 31 sb 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

node "A" 26 0 -27 33 pc 0 0 0 0 360 154 50 40 0 0 0 0

equiv "A" "B"

node "a_n21_38#" 0 0 -21 38 sb 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

node "SS" 0 0 -35 13 ss 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

cap "A" "SS" 5440.2

```

and the two nodes A and B are "short circuited" (equiv "A" "B").

After the further modifications of the technology file, it results from the .EXT file:

```

node "B" 2 0 24 17 pc 0 0 0 0 30 17 25 20 0 0 0 0

node "a_n21_31#" 0 0 -21 31 sb 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

node "a_n21_33#" 18 0 -21 33 pres 0 0 0 0 300 120 0 0 0 0 0 0 0 0

node "A" 2 0 -27 33 pc 0 0 0 0 30 17 25 20 0 0 0 0

node "a_n21_38#" 0 0 -21 38 sb 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

node "SS" 0 0 -35 13 ss 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

cap "A" "SS" 632.1

cap "B" "SS" 632.1

cap "a_n21_33#" "SS" 4176

fec polyres -21 33 -20 34 300 130 "SS" "a_n21_33#" 0 "R1" "A" 5 0 "B" 5 0

```

and the resistor is extracted as a FET while the parasitic capacitances of the two contacts (from *pc* and *poly*) are correctly extracted.

From the .spice file (-*mm* and -*mn* options) it results:

```

R1 A B RPOLY 12.00

* R1=1080.0 (width=1.50U)

C1 B SS 0.6F

C2 A SS 0.6F

*****

** Model Definitions for PSPICE

*****

.MODEL RPOLY RES (R=90.000)

```

and the number of squares SQ is correctly extracted, apart the factor 0.55 which must be attributed to the corner.

Or, in the distributed case (-*mm*, -*mn* and -*d* options)

```

XR1 A B SS D_RPOLY params: SQ=12.00 A=27.00

* R1=1080.0 (width=1.50U)

C1 B SS 0.6F

C2 A SS 0.6F

.SUBCKT D_RPOLY 1 2 3 params: SQ={SQ} A={A}

```

```

XR1 1 4 3 E_RPOLY params: SQ={SQ/5} A={A/5}

XR2 4 5 3 E_RPOLY params: SQ={SQ/5} A={A/5}

XR3 5 6 3 E_RPOLY params: SQ={SQ/5} A={A/5}

XR4 6 7 3 E_RPOLY params: SQ={SQ/5} A={A/5}

XR5 7 2 3 E_RPOLY params: SQ={SQ/5} A={A/5}

.EDNS

*****

** Unit element model for RPOLY

*****

.SUBCKT E_RPOLY 1 2 3 params: SQ={SQ} A={A}

R1 1 2 RPOLY {SQ}

C1 1 3 CAPP {A/2}

C2 2 3 CAPP {A/2}

.EDNS

*****

** Model Definitions for PSPICE

*****

.MODEL RPOLY RES (R=90.000)

.MODEL CAPP CAP (C=0.088FF)

```

and also the area A of *pres* for the evaluation of the parasitic capacitance associated to *pres* is correctly extracted.

In this example, the limits in the accuracy of the extraction are the ones previously discussed.

### **Step 3 - Corrections and Improvements (*ext2spice.corr*)**

The Ext2spice.corr program provides the correction and improvement of the spice netlist generated by the Ext2spice program. In particular:

- eliminates, if present, all the capacitors the value of which is 0,0F<sup>5</sup>;

- calculates the value of **resistors**, both in the non-distributed and in the distributed case, by including in the evaluation the corners, the resistance of the poly adjacent the contact, the resistance of the contact, the perimeter component of the parasitic capacitance and the difference between the real and the drawn width; for each resistor the result of these calculations is also reported as a comments;

- converts the NRG, NRD and NRS parameters of the FETs into RG, RD and RS parameters, providing also a more accurate approximation, by including the resistance of the contacts and a separate coefficient for the resistance per square of polysilicon, ndiffusion and pdiffusion;

- locates the **linear capacitors** and provides these capacitors with a model that includes their dependence on the voltage and on the temperature.

Finally:

- by the introduction of an additional layer for each metal and by some further modification of the Technology file and of the Ext.defs file, it provide the extraction of the **metal lines as resistors**, including all the related parasitic capacitances.

### **Ext2spice.corr**

The code of the Ext2spice.corr program is reported in the Appendix F. The program can be invoked in cascade to Ext2spice by using the following script:

```

#!/bin/csh

rm -f $1.cir

~ ext2spice -mm -mn -c .001 -g -d -D -S $1

cp $1.spice $1.spice.old

~ ext2spice.corr $1.spice.old > $1.spice

```

The old .spice file is saved as *namefile.spice.old*

---

<sup>5</sup> This function is necessary because in some cases the 0 value capacitors are not filtered by Ext2spice.

## Improvements in the extraction of the Resistors

### *(a) - Corners*

In order to take into account in the calculus of the value of the resistor all the corners present along *pres*, the number of corners of each resistor must be known. This number can be included in the label of each resistor. When Ext2spice.corr finds a resistor with a label *Rxx\_Ln* (the label *Rxx\_Ln^n* must be attached to *pres*), extracts *n* as the number of corners for that resistor. If the term *\_Ln* is omitted from the label, the number of corners of that resistor is assumed to be zero. Ext2spice.corr provides also the necessary modifications in the .spice file in order to take into account this new parameter, both in the case of the non-distributed and distributed model.

### *(b) - Resistance of the contact and of the poly adjacent to the contact*

The resistance of the contact *pc* and of the poly adjacent the contact are included in the calculus. For the adjacent poly, the minimum length  $1\lambda$  is assumed (plus  $1\lambda$  for the distance between the real contact and the poly). The value of the resistance of the poly contact *PC* [Ohm] and of the resistance per square of the poly *RSQPOLY* [Ohm/square] must be given at the beginning of the Ext2spice.corr code. These values can be found in the General Process Specifications, in the Technology File of the Process or in the Mosis Parametric Test Results.

### *(c) - Perimeter component of the parasitic capacitance*

In the case of the distributed model, the parasitic capacitance associated to the resistor is extracted. But Ext2spice provides only the area component of this capacitance. In order to extract also the perimeter component, the .MODEL lines are replaced with .PARAM lines and the capacitance is calculated according to the values of the parameters. The value of the areacap *RA-CAP* [ $F/m^2$ ] and perimcap *RPCAP* [ $F/m$ ] must be given at the beginning of the Ext2spice.corr code. These values can be found in the General Process Specifications, in the Technology File of the Process or in the Mosis Parametric Test Results.

Attention must be paid when the additional *ss* layer is used and *pres* lies in a well, because the parasitic capacitance is calculated from *pres* to the layer *ss* and not from *pres* to the well, which is an error. The problem is that when the MAGIC extractor must choose between *ss* and well, it chooses *ss* (i.e. the layer with the lower planeorder). The solution is to remove the *ss* layer from all the areas where *pres* is overlapped to a well.

### *(d) - Real and drawn width*

Ext2spice.corr provides the correction through the parameter *RDW*, which is the delta-width. The value of *RDW* [m] must be given at the beginning of the Ext2spice.corr code. This value can be found in the General Process Specifications, in the Technology File of the Process or in the Mosis Parametric Test Results.

### *(e) - Calculus of the value of the resistance*

The value of the resistance is finally calculated through the equation:

$$R = 2PC + 2RSQPOLY \frac{2LAMBDA}{W} + \frac{RSQ(SQ - 0.45NL)}{1 - \frac{RDW}{W}} \quad (6)$$

where  $W$  is the width of *pres* and  $NL$  is the number of corners. In the non-distributed case  $W$  is not available and a minimum width  $WMIN$  is assumed.

The values of  $LAMBDA$  [m],  $RSQ$  [Ohm/square] and  $WMIN$  [m] must be given at the beginning of the Ext2spice.corr code. These values can be found in the General Process Specifications, in the Technology File of the Process or in the Mosis Parametric Test Results.

### Example 7

After the relabeling of the resistance of the **Example 6** as  $R1\_L1^A$ , it follows from Ext2spice.corr in the non-distributed case:

```

R100 A B 1056.3

C1 B 1 0.6F

C2 A 1 0.6F

```

and in the distributed case:

```

XR1 A B 1 D_RPOLY params: SQ=12.00 A=27.00 NL=1

* XR1=1056.3 (W=1.5e-06, Weff=1.5e-06, Cpar=6.687e-15)

C1 B 1 0.6F

C2 A 1 0.6F

*****

* Global Node Definitions

*****

Vsubstr $G_Vsub! 0 DC 0V

*****

* Distributed Model Definitions

*****

** Multiple element model for RPOLY

*****

.SUBCKT D_RPOLY 1 2 3 params: SQ={SQ} A={A} NL={NL}

XR1 1 4 3 E_RPOLY params: SQ = {SQ/5} A = {A/5}

XR2 4 5 3 E_RPOLY params: SQ = {SQ/5} A = {A/5}

XR3 5 6 3 E_RPOLY params: SQ = {SQ/5} A = {A/5}

XR4 6 7 3 E_RPOLY params: SQ = {SQ/5} A = {A/5}

XR5 7 2 3 E_RPOLY params: SQ = {SQ/5} A = {A/5}

.ENDS

*****

** Unit element model for RPOLY

*****

.SUBCKT E_RPOLY 1 2 3 params: SQ={SQ} A={A} NL={NL}

R1 1 2 {2*PC+2*RSQPOLY*2*LAMBDA/SQRT(A*1p/SQ)+RSQ*(SQ-NL*0.45)/(1-

RDW/SQRT(A*1p/SQ))}

C1 1 3 {RACAP*A*1p/2+RPCAP/2*2*SQRT(A*1p*SQ)}

C2 2 3 {RACAP*A*1p/2+RPCAP/2*2*SQRT(A*1p*SQ)}

.ENDS

*****

```

```

.PARAM RSQPOLY=3.5 PC=7

*****

.PARAM RSQ=90 RDW=0 SQ=1 A=1p NL=0

.PARAM RACAP=8.5e-05 RPCAP=1.22e-10

```

## Improvements in the extraction of the FETs

In order to give a better approximation of the parasitic resistances, their values are directly calculated by Ext2spice.corr. On each FET line, the new expressions for RG, RD and RS replaces the old expressions for NRG, NRD, NRS.

### (a) - Parasitic resistance RG

The following equation is used for the evaluation of RG:

$$RG = RSQPOLY \left( \frac{1}{M \cdot NRG} + \frac{4LAMBDA}{L} \right) \frac{1}{4} + PC \frac{1}{2} \frac{CLT \cdot LAMBDA}{L} \quad (7)$$

The equation follows by considering the gate of a finger connected at both sides thus giving two resistors (remember that Ext2spice evaluates NRG in the wrong direction and it divides NRG per finger by M) in parallel for each finger. The term  $4\lambda/L$  takes into account the resistance of the poly external to the active area. The last term approximates the contact resistance by using the parameter CLT, which is the number of contacts per lambda. The calculus is subject to the approximation made on the original NRG. The minimum dimension  $1\lambda$  for the *poly* adjacent to the *pc* is assumed. The contact resistance results over-estimated for small W. The value of CLT must be given at the beginning of the Ext2spice.corr code and is set by the design rules.

### (b) - Parasitic resistances RD and RS

The following equations are used to approximate the values of RD and RS.

For single finger n-chennal FETs:

$$RD = NRSQ \left( NRD - \frac{3 \cdot LAMBDA}{W} \right) + NDC \frac{2 \cdot CLT \cdot LAMBDA}{W} \quad (8a)$$

$$RS = NRSQ \left( NRS - \frac{3 \cdot LAMBDA}{W} \right) + NDC \frac{2 \cdot CLT \cdot LAMBDA}{W} \quad (8b)$$

and for single finger p-channel FETs:

$$RD = PRSQ \left( NRS - \frac{3 \cdot LAMBDA}{W} \right) + PDC \frac{2 \cdot CLT \cdot LAMBDA}{W} \quad (8c)$$

$$RS = PRSQ \left( NRS - \frac{3 \cdot \text{LAMBDA}}{W} \right) + PDC \frac{2 \cdot \text{CLT} \cdot \text{LAMBDA}}{W} \quad (8d)$$

For multifinger n-channel FETs:

$$RD = NRSQ \left( NRD \cdot M^2 - \frac{M \cdot \text{LAMBDA}}{W} - \frac{2 \cdot \text{LAMBDA}}{W} \right) \frac{1}{M} + NDC \frac{2 \cdot \text{CLT} \cdot \text{LAMBDA}}{W} \quad (9a)$$

$$RS = NRSQ \left( NRS \cdot M^2 - \frac{M \cdot \text{LAMBDA}}{W} - \frac{2 \cdot \text{LAMBDA}}{W} \right) \frac{1}{M} + NDC \frac{2 \cdot \text{CLT} \cdot \text{LAMBDA}}{W} \quad (9b)$$

and for multifinger p-channel FETs:

$$RD = PRSQ \left( NRS \cdot M^2 - \frac{M \cdot \text{LAMBDA}}{W} - \frac{2 \cdot \text{LAMBDA}}{W} \right) \frac{1}{M} + PDC \frac{2 \cdot \text{CLT} \cdot \text{LAMBDA}}{W} \quad (9c)$$

$$RS = PRSQ \left( NRS \cdot M^2 - \frac{M \cdot \text{LAMBDA}}{W} - \frac{2 \cdot \text{LAMBDA}}{W} \right) \frac{1}{M} + PDC \frac{2 \cdot \text{CLT} \cdot \text{LAMBDA}}{W} \quad (9d)$$

The  $M^* \lambda / W - 2 \cdot \lambda / W$  terms take into account the resistance of the diffusion part of the real contact. The  $XDC / (W \cdot CLT / \lambda)$  term approximates the contact resistance and  $XDC$  must be  $NDC$  for n-channel and  $PDC$  for p-channel. The calculus is subject to the approximation on the original  $NRS$  (or  $NRD$ ). The minimum distance between the channel and  $ndc$  (or  $pdc$ ) is assumed. The contact resistance results overestimated for small  $L$ . Note that, during the simulation, SPICE considers the  $RS$ ,  $RG$ ,  $RD$  as values per finger, dividing these values by  $M$  for the simulation of the overall FET, which is the correct approach.

The values of  $NRSQ$  and  $PRSQ$  [Ohm/square], respectively the resistance per square of the ndiffusion and of the pdiffusion, as well as the values of  $NDC$  and  $PDC$  [Ohm], respectively the resistance of the contacts  $ndc$  and  $pdc$ , must be given at the beginning of the Ext2spice.corr code. These values can be found in the General Process Specifications, in the Technology File of the Process or in the Mosis Parametric Test Results.

### Example 8

For the FET of **Example 4** it follows:

```

Mx B C A SS CMOSN W=3.00U L=1.20U AD=6.30P PD=10.20U AS=6.30P PS=10.20U

+ RG=7.4375 RD=3 RS=3

C1 B SS 1.8F

C2 C SS 1.1F

```

and for the FET of **Example 5** it follows:

```

M1 A C B SS CMOSN M=3 W=3.00U L=0.60U AD=3.30P PD=6.20U AS=6.04P PS=7.03U

```

```

+ RG=14.6667 RD=4.48333 RS=5.23333

M2 A2 C2 B SS CMOSN M=2 W=6.00U L=0.60U AD=5.40P PD=7.80U AS=12.09P PS=14.06U

+ RG=19.25 RD=2.1 RS=2.6

C1 A C 0.2F

C3 A2 B 0.4F

C4 C2 SS 4.1F

C5 B SS 0.4F

C6 B C 0.2F

C7 A2 SS 0.1F

C8 A B 0.6F

C9 C SS 5.6F

C10 B C2 0.2F

C11 A SS 0.2F

```

### Improvements in the extraction of the Linear Capacitors

The improvement in the extraction of the linear capacitors consists in the addition of the dependence of the capacitance on the voltage and on the temperature. In order to achieve this result, all the linear capacitors must be modeled by using a .MODEL statement in the .spice file. Till now it was not possible to distinguish between parasitic and linear capacitors. But adding the following line in the *extract* section of the technology file:

```

fet wcap cwnsd 1 wcap $$G_Vsub! 0 0

```

each linear capacitor will be represented both as *cap* and as *fet* element in the .EXT file.

If the following lines are added in the Ext.defs support file,

```

def wcap    LCAP    C c

distrib wcap    0.475 0.0 0

```

Ext2spice will extract, for each linear capacitor, a "duplicated" capacitor (apart the value) and models each duplicate with LCAP.

Ext2spice.corr deletes, by comparison, all these "duplicates" and models the corresponding original capacitors (the value of which is more accurate) through the model LCAP. The original and correct values of the capacitors are preserved and the .MODEL line for LCAP is added. The values of the voltage parameters *VC1* and *VC2* and of the temperature parameters *TC1* and *TC2* used in the .MODEL statement can be found in the General Process Specifications or in the Mosis Parametric Test Results.

### Example 9

For the linear capacitor of **Example 3** it follows:

```

C2 A B LCAP 2097.8F

```

```

*****

```

\* Global Node Definitions

\*\*\*\*\*

.MODEL LCAP CAP (C=1 VC1=0.001 VC2=0.0005 TC1=0 TC2=0 )

## Extraction of the resistance of the Metal lines

The extraction of the resistance of the metal lines requires that, as in the case of poly resistors, a part or all the line becomes visible as a *fet* to the MAGIC extractor. A possible and effective approach is the introduction of an additional layer for each metal, which must be invisible at the .CIF extraction level and which represents the active area of this "fet". In order to preserve all the parasitic capacitances related to the lines, the active area of the "fet" must be as small as possible, i.e. must be a square along the line. The resistance of the line is then extracted by evaluating the number of squares of the "drain" and of "source" of this "fet" (which equals with good approximation the number of squares of the line). The use of more squares suitably distributed along the line allows a more accurate extraction.

In order to use the additional layers, the following changes must be made in the Technology File.

In the *types* section, three additional layers (*m1res*, *m2res* and *m3res*) for the three metals (*m1*, *m2* and *m3*) must be added:

```

metal1 m1res,m1r

metal2 m2res,m2r

metal3 m3res,m3r

```

In the *styles* section, to "see" the additional layers at the MAGIC layout level; the lines

```

m1res 20

m1res 12

m1res 13

m2res 21

m2res 12

m2res 13

m3res 22

m3res 12

m3res 13

```

must be added.

In the *connect* section, to set the connections, the lines:

```

m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

m2,m2c/m2,m3c/m2,m3c/m2 m2,m2c/m2,m3c/m2,m3c/m2

m3,m3c/m3 m3,m3c/m3

```

must be replaced with the lines:

```

m1,m1res,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

m2,m2res,m2c/m2,m3c/m2,m3c/m2 m2c/m2,m3c/m2,m3c/m2

m3,m3res,m3c/m3 m3c/m3

```

In the *cifoutput* section, to let the layer be invisible at the .CIF level (i.e to let it be "like" the original metal):

```

layer CMF m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

labels m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

layer CMS m2,m2c/m2,m3c/m2,m3c/m2

labels m2,m2c/m2,m3c/m2,m3c/m2

layer CMT m3,m3c/m3

labels m3,m3c/m3

```

must be replaced with the lines:

```

layer CMF m1,m1res,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

labels m1,m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

layer CMS m2,m2res,m2c/m2,m3c/m2,m3c/m2

labels m2,m2,m2c/m2,m3c/m2,m3c/m2

layer CMT m3,m3res,m3c/m3

labels m3,m3,m3c/m3

```

In the *extract* section, to enable the extraction of the "fet" diffusion areas, the *resistclass* lines must be modified as follows (this change does not affect the calculus of the real FET areas, if the Ext.defs support file is modified as described later):

```

# REPLACED resist (ndiff,anres,ndc/a,nsd,nsc/a)/active 1900

resist ((ndiff,ndc/a)/active,(pdifff,pdc/a)/active) 0

# REPLACED resist (pdifff,apres,pdc/a,psd,psc/a)/active 2000

resist (m1/metal1,m2/metal2,m3/metal3) 0

```

while the old *resistclass* lines containing *m1*, *m2* and *m3* must be deleted.

Finally, to enable the "fet" extraction, the following lines

```

fet m1res m1,ndc/m1,nsc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1 2 m1res $$G_Vsub! 0 0

fet m2res m2,m2c/m2,m3c/m2,m3c/m2 2 m2res $$G_Vsub! 0 0

fet m3res m3,m3c/m3 2 m3res $$G_Vsub! 0 0

```

must be added. Note that all the contacts have been included in the evaluation of the areas of the fets for the extraction of the resistances.

In order to extract the new "fet" as a resistance, the following lines must be added in the Ext.defs support file. Basically the idea is to extract the areas of the new "fet" by considering these as p-channel FETs. The areas of the real p-channel FETs is extracted by considering these as n-channel FETs. This approach, relevant only at the Ext2spice level, has no consequence for the final correct extraction of the areas of all real FETs.

The line:

```

def pfet CMOSP M p

```

must be replaced with the line:

```

def pfet CMOSP M n

```

and the lines:

```

def m1res RM1 M p

def m2res RM2 M p

def m3res RM3 M p

```

must be added.

Now Ext2spice.corr provides the accurate extraction of the resistances associated to the metal lines from the "drain" and "source" areas of these "fets".

The values of  $RSQM1$ ,  $RSQM2$ , and  $RSQM3$  [Ohm/square], respectively the resistance per square of  $m1$ ,  $m2$  and  $m3$ , must be given at the beginning of the Ext2spice.corr code. These values can be found in the General Process Specifications, in the Technology File of the Process or in the Mosis Parametric Test Results.

Drawback of this technique is that the line, at the MAGIC layout level, doesn't appear connected so that the check of the connections must be made before this modification, or the lines in the *connect* section must be suitably switched.

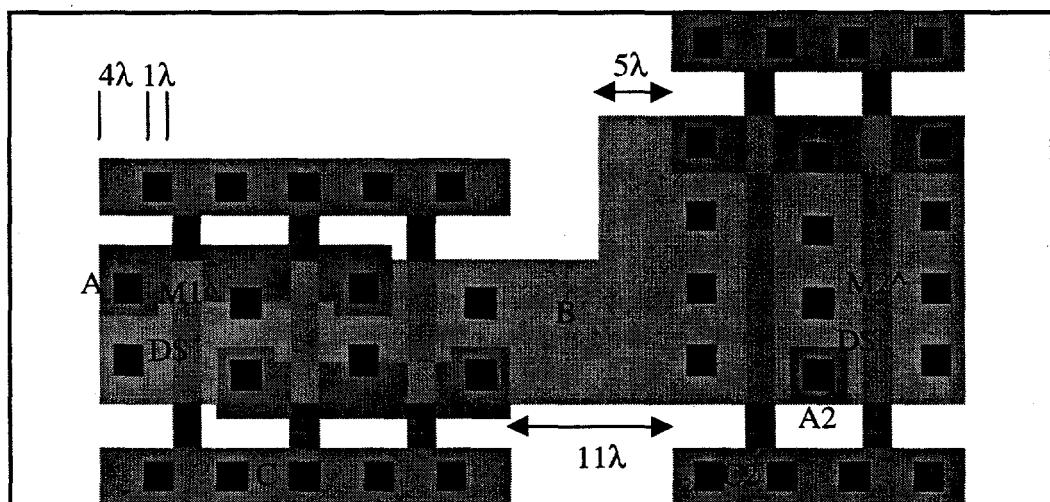

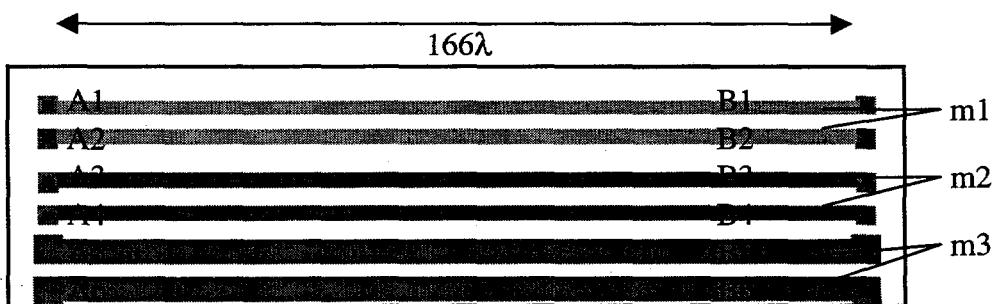

#### Example 10

In this example we have three couples of minimum wide lines in the three different metals ( $m1$ ,  $m2$ ,  $m3$ ). A small square of the correct type (respectively  $m1res$ ,  $m2res$ ,  $m3res$ ) has been introduced in the middle of each line, thus dividing the line in two parts. The square is not visible here be-

cause the picture is extracted from the .CIF file, and, as required, the layers ( $m1res$ ,  $m2res$ ,  $m3res$ ) are not visible at the .CIF level. From Step 2, with regards to the fet elements, it follows:

```

M1 A1 4 B1 $G_Vsub! RM1 W=0.90U L=0.00U AD=21.87P PD=50.40U AS=22.14P PS=51.00U

+ NRG=1.00 NRD=27.00 NRS=27.33

M2 A2 7 B2 $G_Vsub! RM1 W=0.90U L=0.00U AD=21.87P PD=50.40U AS=22.14P PS=51.00U

+ NRG=1.00 NRD=27.00 NRS=27.33

M3 A3 10 B3 $G_Vsub! RM2 W=0.90U L=0.00U AD=21.87P PD=50.40U AS=22.14P PS=51.00U

+ NRG=1.00 NRD=27.00 NRS=27.33

M4 A4 13 B4 $G_Vsub! RM2 W=0.90U L=0.00U AD=21.87P PD=50.40U AS=22.14P PS=51.00U

+ NRG=1.00 NRD=27.00 NRS=27.33

M5 A5 16 B5 $G_Vsub! RM3 W=1.50U L=0.00U AD=34.65P PD=55.80U AS=40.50P PS=63.60U

+ NRG=1.00 NRD=15.40 NRS=18.00

M6 A6 19 B6 $G_Vsub! RM3 W=1.50U L=0.00U AD=34.65P PD=55.80U AS=40.50P PS=63.60U

+ NRG=1.00 NRD=15.40 NRS=18.00

```

And from Step 3:

```

RM1 A1 B1 3.87333

RM2 A2 B2 3.87333

RM3 A3 B3 3.87333

RM4 A4 B4 3.87333

RM5 A5 B5 1.72

RM6 A6 B6 1.72

C2 A6 SS 1.0F

C5 B5 SS 1.1F

C8 A5 SS 1.0F

C9 B2 SS 2.7F

C10 B6 B5 0.8F

C11 B2 B1 0.4F

C13 A2 SS 2.7F

C14 A6 A5 0.7F

C16 B4 SS 1.4F

C19 A2 A1 0.4F

C20 B4 B3 0.4F

C21 A4 SS 1.4F

C22 SS B1 2.2F

C23 B3 SS 1.4F

C24 B6 SS 1.1F

C25 A4 A3 0.4F

C26 A3 SS 1.4F

C28 SS A1 2.2F

```

The accuracy of this evaluation, which includes the parasitic capacitances between the lines lying in the same plane, can be easily verified.

## **Conclusions**

With a relatively simple modification of the Technology File (see Appendix G for a summary of the modifications), and with the use of the Magic Extract function, of the Ext2spice program

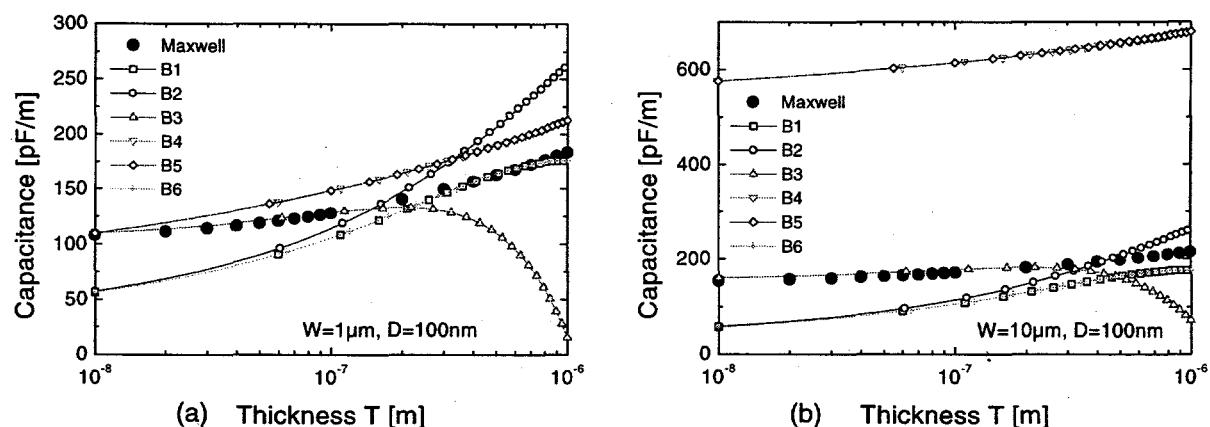

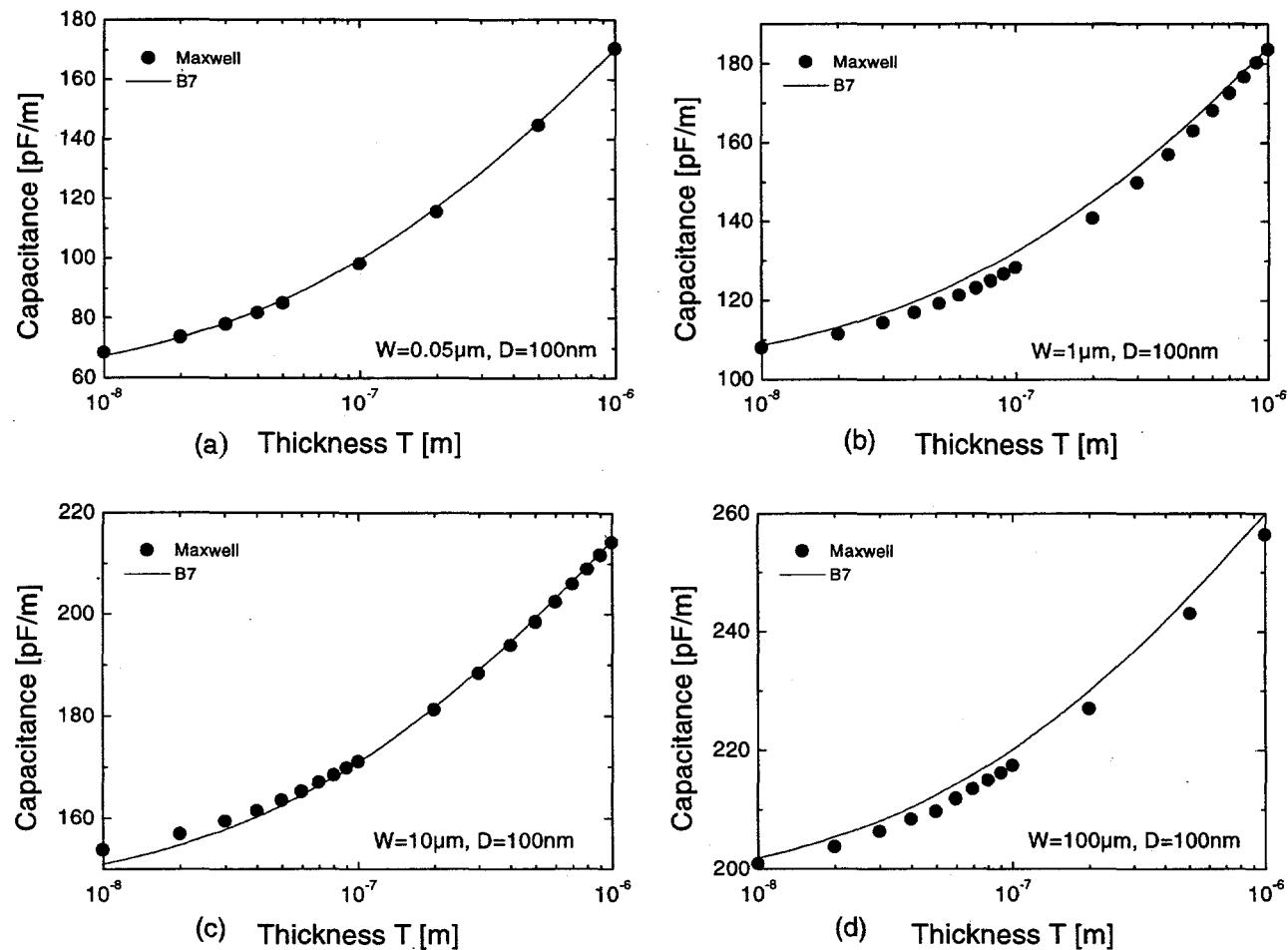

(and its support file Ext.defs) and of the Ext2spice.corr program, it is possible to extract the SPICE netlist from a MAGIC based layout with an improved accuracy. The limit in this approach is that every technology requires the modification of the corresponding Technology File (together with some minor changes in the two programs). The extraction of the capacitances is strongly dependent on the accuracy of the parameters from the Technology File, which must be verified by the simulations (for example by using the Maxwell simulator) and updated by using the beta versions released by MOSIS.

## **Appendix A - Connect and extract sections**

---

```

connect

nwell,cwell,nsc,cwc,nsd,cwnsd,cwc/a  nwell,cwell,nsc,cwc,nsd,cwnsd,cwc/a

pwell,psc,psd  pwell,psc,psd

m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1

m2,m2c/m2,m3c/m2,m3c/m2  m2,m2c/m2,m3c/m2,m3c/m2

m3,m3c/m3  m3,m3c/m3

ndiff,anres,ndc/a  ndiff,anres,ndc/a

pdiff,apres,pdc/a  pdiff,apres,pdc/a

ndiff,anres,nsd  ndc/a,nsc/a,psd,psc/a

pdiff,apres,psd  pdc/a,psc/a,nsd,nsc/a

poly,pres,wcap,nfet,wcap,pfet,pc/a  poly,pres,wcap,nfet,wcap,pfet,pc/a

gc  poly,pres,wcap

gv1  m1,m2

gc  ndiff,anres,pdiff,apres,nsd,psd,m1

m3,m3c/m3  m3,m3c/m3

gv2  m2,m3

pad  m1,m2,m3

end

```

---

```

extract

style HP0.5um(hpcmos14tb)from:N81D

cscale 1

lambda 30

step 100

sidehalo 8

planeorder well 0

planeorder implant 1

planeorder select 2

planeorder active 3

planeorder metal1 4

planeorder metal2 5

planeorder metal3 6

planeorder oxide 7

planeorder xp 8

planeorder comment 9

planeorder contact 10

planeorder via1 11

planeorder via2 12

resist (ndiff,anres,ndc/a,nsd,nsc/a)/active 1900

resist (pdiff,apres,pdc/a,psd,psc/a)/active 2000

resist (poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active 1800

resist (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1,m2c/m1)/metal1 70

resist (m2,m2c/m2,m3c/m2,m3c/m2)/metal2 70

resist (m3,m3c/m3, pad)/metal3 50

contact ndc 4 2000

```

```

contact pdc 4 2000

contact pc 4 1700

contact m2c 4 700

contact m3c 4 360

#wellcap

overlap wcap capwell 207.900

#nwell,cwell,pwell

areacap (nwell,cwell)/well 8.460

areacap (cwell)/well 8.460

#ndiff

areacap (anres)/active 48.330

overlap (anres)/active ~space/w 48.330

perimc (anres)/active ~(anres)/active 67.800

sideoverlap (anres)/active ~(anres)/active ~space/w 67.800

# MODEL HANDLES THIS: areacap (ndiff,anres,ndc/a)/active 48.330

# MODEL HANDLES THIS: overlap (ndiff,anres,ndc/a)/active ~space/w 48.330

# MODEL HANDLES THIS: perimc (ndiff,anres,ndc/a)/active ~(ndiff,anres,ndc/a,nfet,pfet)/active 67.800

# MODEL HANDLES THIS: sideoverlap (ndiff,anres,ndc/a)/active ~(ndiff,anres,ndc/a,nfet,pfet)/active

~space/w 67.800

#pdiff

areacap (apres)/active 84.600

overlap (apres)/active ~space/w 84.600

perimc (apres)/active ~(apres)/active 67.500

sideoverlap (apres)/active ~(apres)/active ~space/w 67.500

# MODEL HANDLES THIS: areacap (pdiff,apres,pdc/a)/active 84.600

# MODEL HANDLES THIS: overlap (pdiff,apres,pdc/a)/active ~space/w 84.600

# MODEL HANDLES THIS: perimc (pdiff,apres,pdc/a)/active ~(pdiff,apres,pdc/a,nfet,pfet)/active 67.500

# MODEL HANDLES THIS: sideoverlap (pdiff,apres,pdc/a)/active ~(pdiff,apres,pdc/a,nfet,pfet)/active

~space/w 67.500

#polycap

#poly

sidewall (poly,pres,wcap,pc/a,wcap,pc/a)/active ~(poly,pres,wcap,pc/a,wcap,pc/a)/active

~(poly,pres,wcap,pc/a,wcap,pc/a)/active (poly,pres,wcap,pc/a,wcap,pc/a)/active 2.136

areacap (poly,pres,wcap,pc/a,wcap,pc/a)/active 7.920

overlap (poly,pres,pc/a,pc/a)/active ~space/w 7.920

perimc (poly,pres,wcap,pc/a,wcap,pc/a)/active ~(poly,pres,wcap,pc/a,wcap,pc/a)/active 15

sideoverlap (poly,pres,wcap,pc/a,wcap,pc/a)/active ~(poly,pres,wcap,pc/a,wcap,pc/a)/active ~space/w 15

# MODEL HANDLES THIS: overlap (nfet)/active (ndiff,anres,ndc/a)/active 324.360

# MODEL HANDLES THIS: sideoverlap (nfet)/active ~(nfet)/active (ndiff,anres,ndc/a)/active 15

# MODEL HANDLES THIS: overlap (pfet)/active (pdiff,apres,pdc/a)/active 308.160

# MODEL HANDLES THIS: sideoverlap (pfet)/active ~(pfet)/active (pdiff,apres,pdc/a)/active 15

#poly2

#metal1

sidewall (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 6.690

```

```

areacap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 2.700

#metal-sub blocked by ~space/a,~space/c

overlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 ~space/w 2.700

~space/a

perimc (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 9.300

sideoverlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 ~space/w

9.300 ~space/a

#metal-diff blocked by ~space/c

overlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(ndiff,anres,ndc/a)/active 2.790

sideoverlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(ndiff,anres,ndc/a)/active 9.300

overlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(pdif,apres,pdc/a)/active 2.790

sideoverlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(pdif,apres,pdc/a)/active 9.300

#metal-polycap blocked by poly

#metal-poly blocked by poly2

overlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active 5.400

sideoverlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

~(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1

(poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active 15

sideoverlap (poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active

~(poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active

(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 15

#metal-poly2 not blocked

#metal2

sidewall (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2

(m2,m2c/m2,m3c/m2)/metal2 9.090

areacap (m2,m3c/m2)/metal2 1.260

#metal2-sub blocked by ~space/a,~space/m1,poly2/polycap

overlap (m2,m3c/m2)/metal2 ~space/w 1.260 ~space/a,~space/m1

perimc (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2 5.100

sideoverlap (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2 ~space/w 5.100

~space/a,~space/m1

overlap (m2,m3c/m2)/metal2 (ndiff,anres,ndc/a)/active 1.260 ~space/m1

sideoverlap (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2 (ndiff,anres,ndc/a)/active

5.100 ~space/m1

overlap (m2,m2c/m2,m3c/m2)/metal2 (pdif,apres,pdc/a)/active 1.260 ~space/m1

sideoverlap (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2 (pdif,apres,pdc/a)/active

5.100 ~space/m1

#metal2-polycap by ~space/m1,poly

```

```

#metal2-poly blocked by ~space/m1,poly2

overlap (m2,m3c/m2)/metal2 (poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active 1.620 ~space/m1

sideoverlap (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2

(poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active 6.300 ~space/m1

sideoverlap (poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active

~(poly,pres,wcap,pc/a,wcap,pc/a,nfet,pfet)/active (m2,m2c/m2,m3c/m2)/metal2 6.300

~space/m1

#metal2-poly2 blocked by ~space/m1

#M2->M1

overlap (m2,m3c/m2)/metal2

(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 4.050

sideoverlap (m2,m2c/m2,m3c/m2)/metal2 ~(m2,m2c/m2,m3c/m2)/metal2

(m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1 11.700

sideoverlap (m1,ndc/m1,nsc/m1,cwc/m1,pdc/m1,psc/m1,cwc/m1,pc/m1,m2c/m1)/metal1