## **DISCLAIMER**

**This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof. Reference herein to any social initiative (including but not limited to Diversity, Equity, and Inclusion (DEI); Community Benefits Plans (CBP); Justice 40; etc.) is made by the Author independent of any current requirement by the United States Government and does not constitute or imply endorsement, recommendation, or support by the United States Government or any agency thereof.**

## Final Scientific/Technical Report

### 20 kV Gallium Nitride pn Diode Electro-Magnetic Pulse Arrestor for Grid Reliability

18/CJ000/10/01

|                                |                                                                                     |

|--------------------------------|-------------------------------------------------------------------------------------|

| <b>Award:</b>                  | 18/CJ000/10/01                                                                      |

| <b>Lead Recipient:</b>         | Sandia National Laboratories                                                        |

| <b>Project Title:</b>          | 20 kV Gallium Nitride pn Diode Electro-Magnetic Pulse Arrestor for Grid Reliability |

| <b>Program Director:</b>       | Isik Kizilyalli                                                                     |

| <b>Principal Investigator:</b> | Bob Kaplar                                                                          |

| <b>Contract Administrator:</b> | Kelly Harper                                                                        |

| <b>Date of Report:</b>         | 11/07/2023                                                                          |

| <b>Reporting Period:</b>       | 07/11/2019-07/10/2023                                                               |

The information, data, or work presented herein was funded by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number 18/CJ000/10/01. The views and opinions of authors expressed herein do not necessarily reflect those of the United States Government or any agency thereof.

Sandia National Laboratories is a multi-mission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

This document contains no protected data.

## Public Executive Summary

This project developed vertical Gallium Nitride (GaN) pn diodes under two main thrusts: (1) A focus on relatively higher-voltage devices for use as fast EMP arrestors to protect the electric grid; and (2) A focus on a Foundry effort to establish the manufacturability of relatively lower-voltage devices. For the first thrust, the aim was to develop devices that go into avalanche breakdown to clamp the voltage across sensitive grid equipment subject to voltage transients induced by electromagnetic pulses (EMPs). Devices with breakdown voltages exceeding 6.5 kV were achieved, and breakdown times shorter than 1 ns were demonstrated, which is sufficiently fast to protect against the fast component of an EMP-induced signal. Key challenges included the epitaxial growth of thick (50 um or more), low-doped (low  $10^{15} \text{ cm}^{-3}$  range) GaN layers comprising the drift regions of the diodes, as well as the design and fabrication of edge termination structures (step-etched junction termination extensions) to prevent premature breakdown. Midway through the project, an additional emphasis was put on large-area, high-current devices, and forward currents of approximately 400 A were achieved in composite devices towards the end of the project. Experimental and theoretical studies of impact ionization and avalanche ruggedness were also conducted. For the second thrust (the Foundry), the focus was primarily on 1.2-kV-class devices, although towards the end of the project outstanding results on 3.3-kV-class devices were also achieved. The aim of the Foundry was to develop a high-yield, reliable, and economic vertical GaN pn diode process. The Foundry conducted characterization of incoming epitaxial material and correlated this information with the yield and performance of fully processed devices. Wafer maps of diode characteristics such as forward and reverse current as well as capacitance-voltage curves were measured using auto-probing. Several mask sets comprising different-area devices as well as multiple edge termination designs (implanted junction termination extensions, guard rings, and combinations thereof) were studied, and machine-learning-based approaches were utilized to analyze the data. Packaging and reliability efforts were also undertaken for the Foundry diodes, which are necessary for a viable commercial process.

## Acknowledgements

The PI would like to thank ARPA-E for supporting this work, especially Isik Kizilyalli, Eric Carlson, and Danny Cunningham. The PI also thanks the outstanding technical team that conducted the work summarized herein: Sandia: Luke Yates, Mary Crawford, Andrew Binder, Jack Flicker, Tony Rice, Brendan Gunning, Andy Allerman, Greg Pickrell, Andy Armstrong, Jeramy Dickerson, Jason Neely, and Paul Sharps; Naval Research Lab: Travis Anderson, Karl Hobart, Alan G. Jacobs, James Gallagher, Mona Ebrish, Andy Koehler, Marko Tadjer, Jennifer Hite, and Matt Porter; Stanford University: Srabanti Chowdhury, Ke Zeng, Rohith Soman, Bhawani Shankar, and Dong Ji (thanks also go to Stanford for providing the cost share for the project); EDYNX: Ozgur Aktas; Sonrisa Research: Jim Cooper; Boston University: Enrico Bellotti.

## Table of Contents

|                                      |    |

|--------------------------------------|----|

| Public Executive Summary .....       | 2  |

| Acknowledgements.....                | 2  |

| Table of Tables .....                | 3  |

| Table of Figures.....                | 3  |

| Accomplishments and Objectives ..... | 6  |

| Project Activities .....             | 13 |

| Project Outputs.....                 | 37 |

| Follow-On Funding.....               | 41 |

## Table of Tables

|                                                |    |

|------------------------------------------------|----|

| Table 1. Key Milestones and Deliverables ..... | 6  |

| Table 2. Follow-On Funding Received.....       | 41 |

## Table of Figures

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

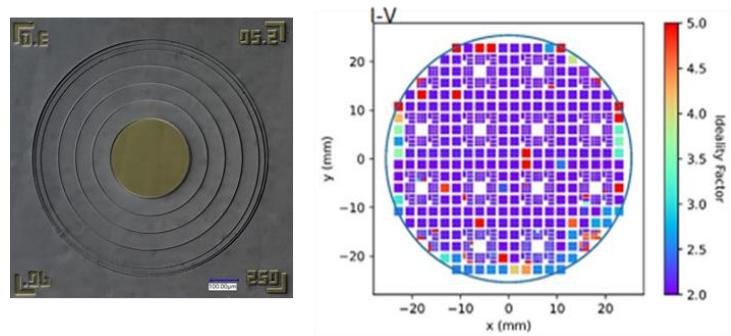

| Figure 1. (left) Nomarski image of 2" HVPE LD-grade GaN wafer with an additional 60 $\mu\text{m}$ epitaxial drift layer grown using Sandia's Veeco MOCVD reactor. (right) Carrier concentration as measured by Hg probe CV for several different drift thicknesses, up to 60 $\mu\text{m}$ . .....                                                                                                                                                                                                                                                                     | 15 |

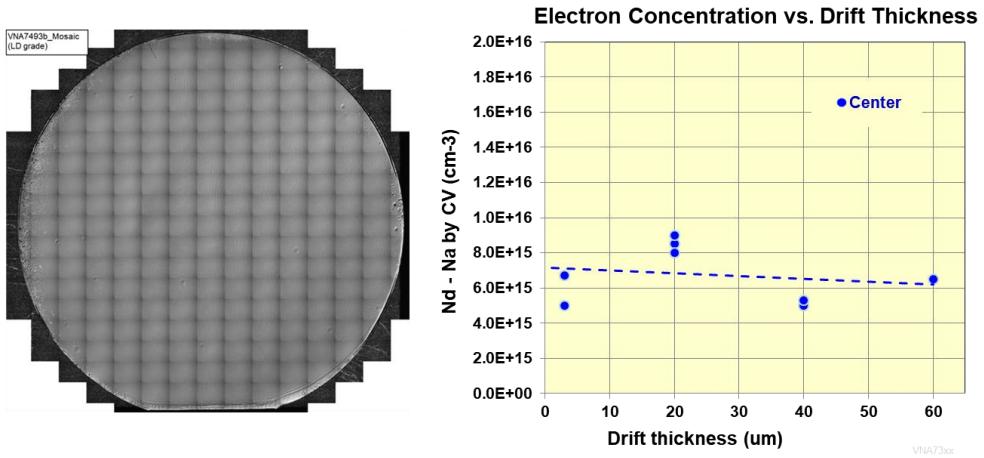

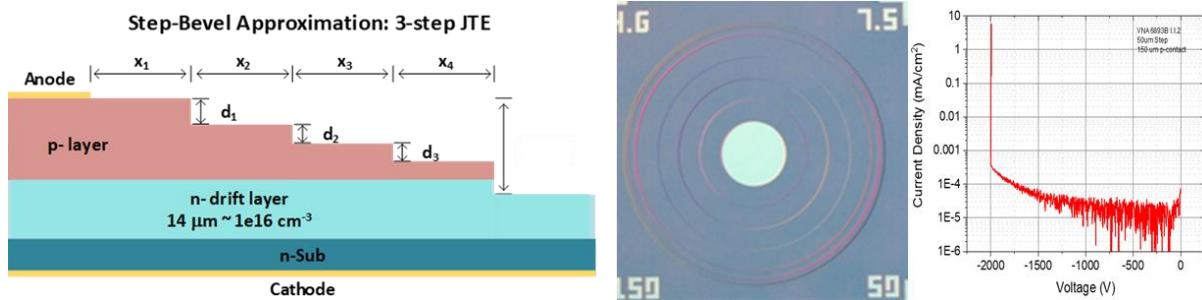

| Figure 2. (left) Axisymmetric diagram of device with included JTE structure. Multiple variations of the x and d dimensions were explored. (middle) Optical image of a fabricated device with a 150 $\mu\text{m}$ diameter anode contact and 50 $\mu\text{m}$ wide JTE steps. (right) Reverse IV characteristic of a typical well-performing device from this design lot. Multiple devices demonstrated noise floor leakage out to 2 kV breakdown. ....                                                                                                                 | 15 |

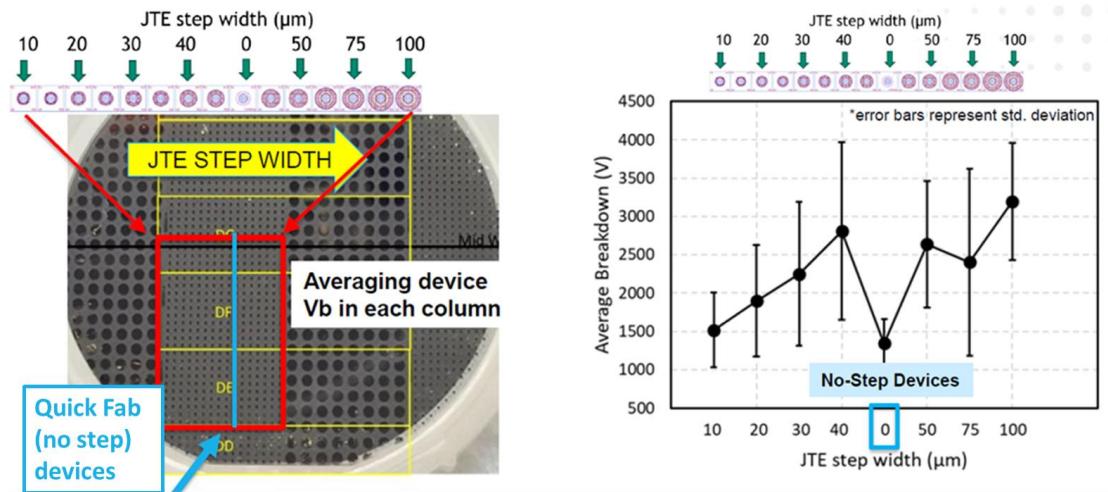

| Figure 3. (left) Annotated optical image of a processed 2" wafer with a 50 $\mu\text{m}$ drift region and varying JTE step widths and anode sizes. (right) Average breakdown of different device columns, each with varying JTE step widths.....                                                                                                                                                                                                                                                                                                                       | 16 |

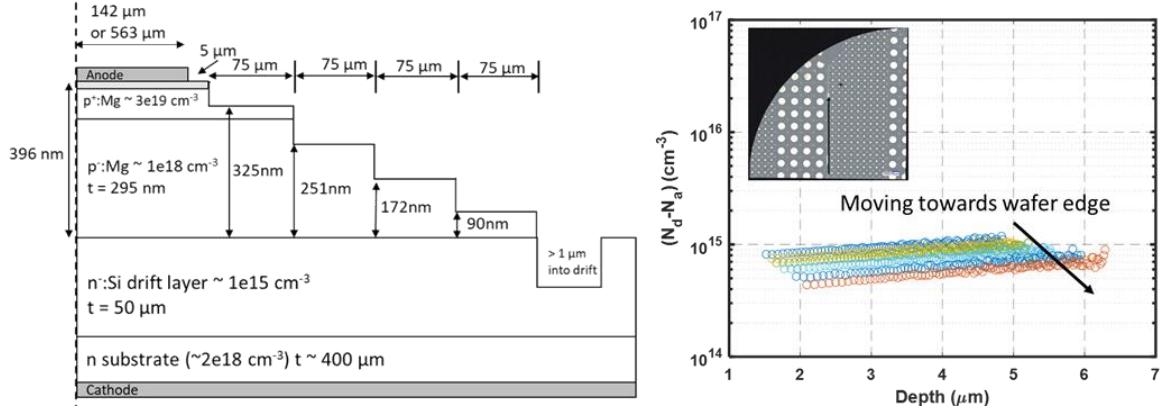

| Figure 4. (left) Axisymmetric schematic of vertical PN diode with four-zone JTE design. (right) Extracted carrier concentration of measured devices in the n-GaN drift layer. A frequency of 1 MHz was used for the CV measurements.....                                                                                                                                                                                                                                                                                                                               | 17 |

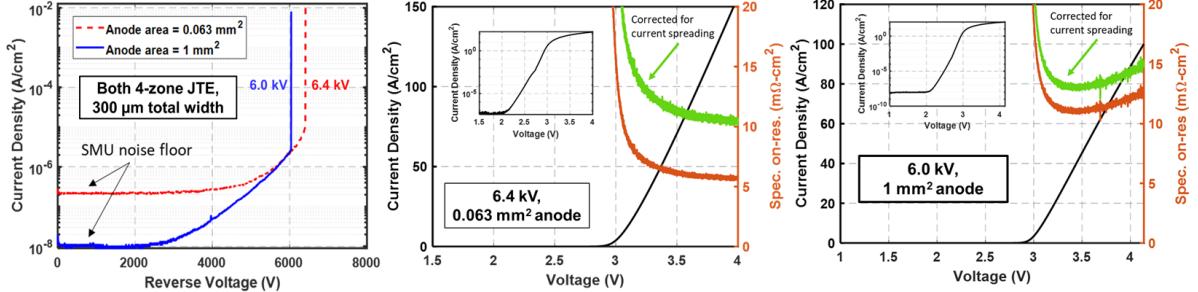

| Figure 5. (left) Reverse I-V characteristics and breakdown voltage of two PN diodes with anode areas of 0.063 $\text{mm}^2$ and 1.0 $\text{mm}^2$ . The noise floor change is a result of different anode areas and not due to the characterization equipment. (middle) Forward I-V characteristics of a 6.4 kV diode with a 0.063 $\text{mm}^2$ anode area. (right) Forward I-V characteristics of a 6.0 kV diode with a 1.0 $\text{mm}^2$ anode area. Both the middle and right figures were taken to a maximum of 1 A DC current, and the specific on-resistance is |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| shown using both the anode area and assuming a 45° current spreading through the drift region. Insets show the forward I-V on a semilogarithmic scale.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 |

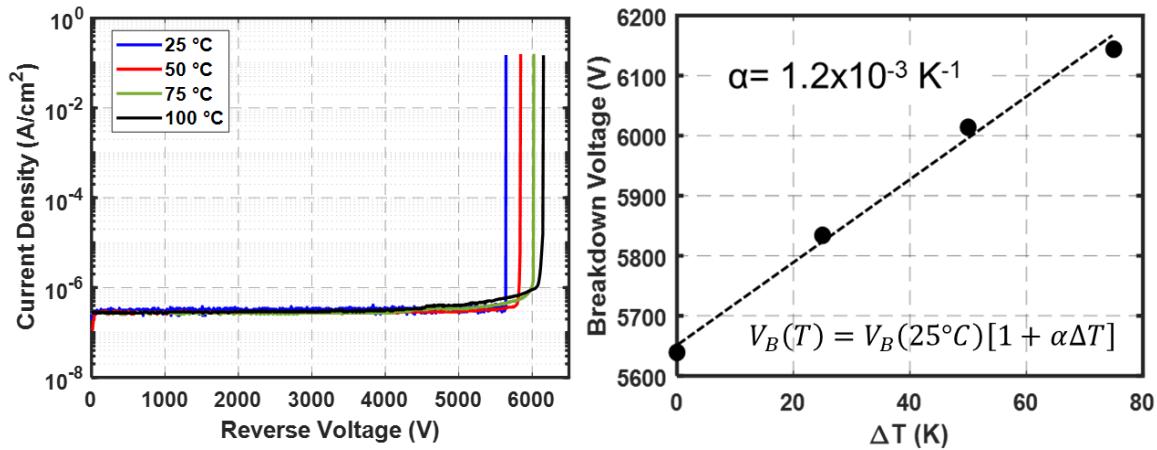

| Figure 6. (left) Temperature dependence of the reverse I-V characteristics of a PN junction diode with an anode area of 0.063 mm <sup>2</sup> . (right) Linear relationship of breakdown with change in temperature as indicated by the inset equation. A temperature coefficient of $1.2 \times 10^{-3}$ K <sup>-1</sup> was fit and is consistent with literature for this doping level. ....                                                                                                                                                                                                                                 | 18 |

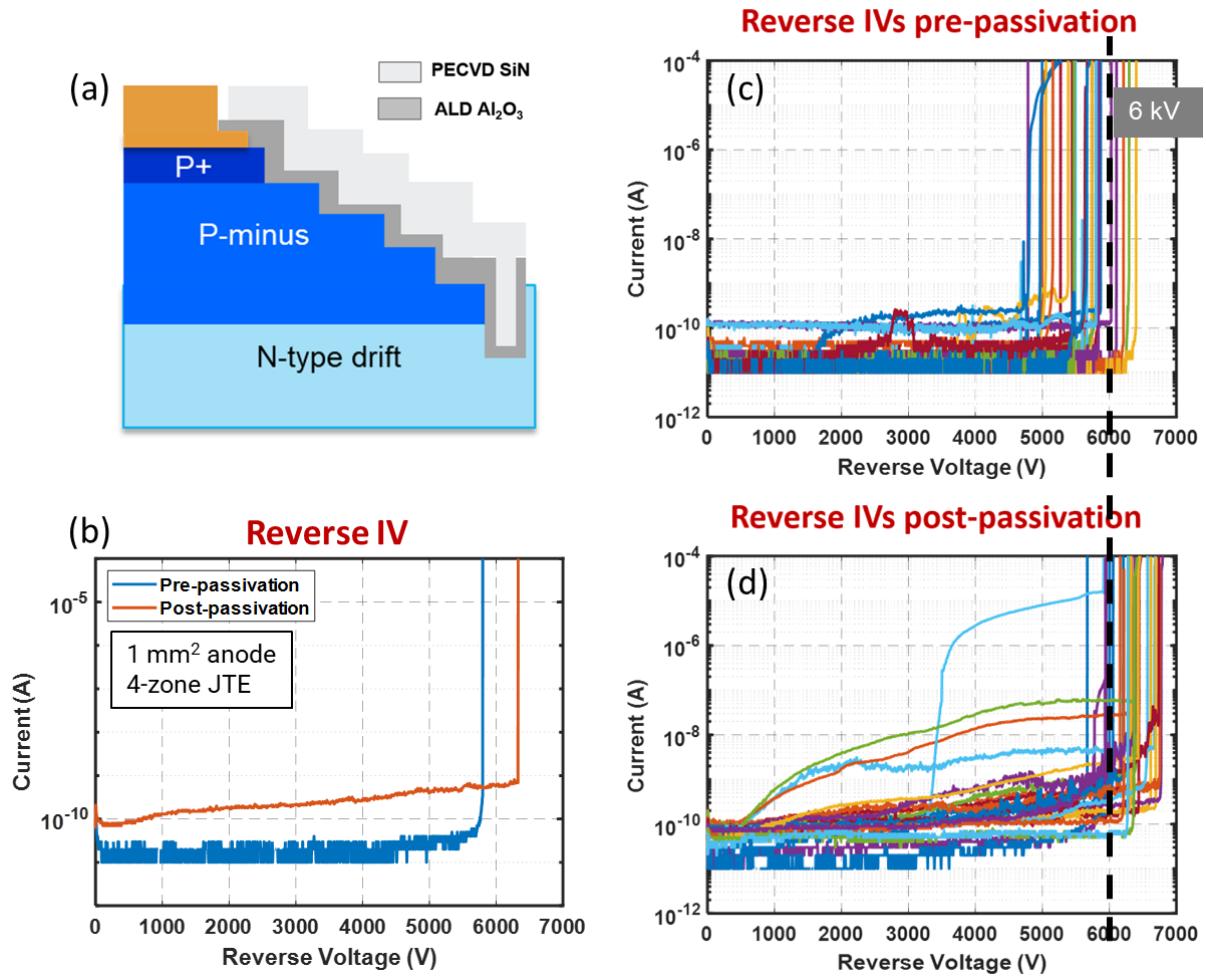

| Figure 7. (a) Schematic of implemented passivation consisting of 100 nm ALD Al <sub>2</sub> O <sub>3</sub> and 2 μm PECVD SiN. (b) Reverse IV characteristics of a PN diode with 1 mm <sup>2</sup> anode contact. A slight increase in leakage current is observed with an almost 10% increase in breakdown voltage. (c) & (d) Comparison of 24 devices with 0.063 mm <sup>2</sup> anode contacts. A total of 20 devices maintained <10 nA leakage current up to 80% of breakdown, with all the devices demonstrating an increase in absolute breakdown voltage. This resulted in multiple devices breaking down at 6.7 kV..... | 19 |

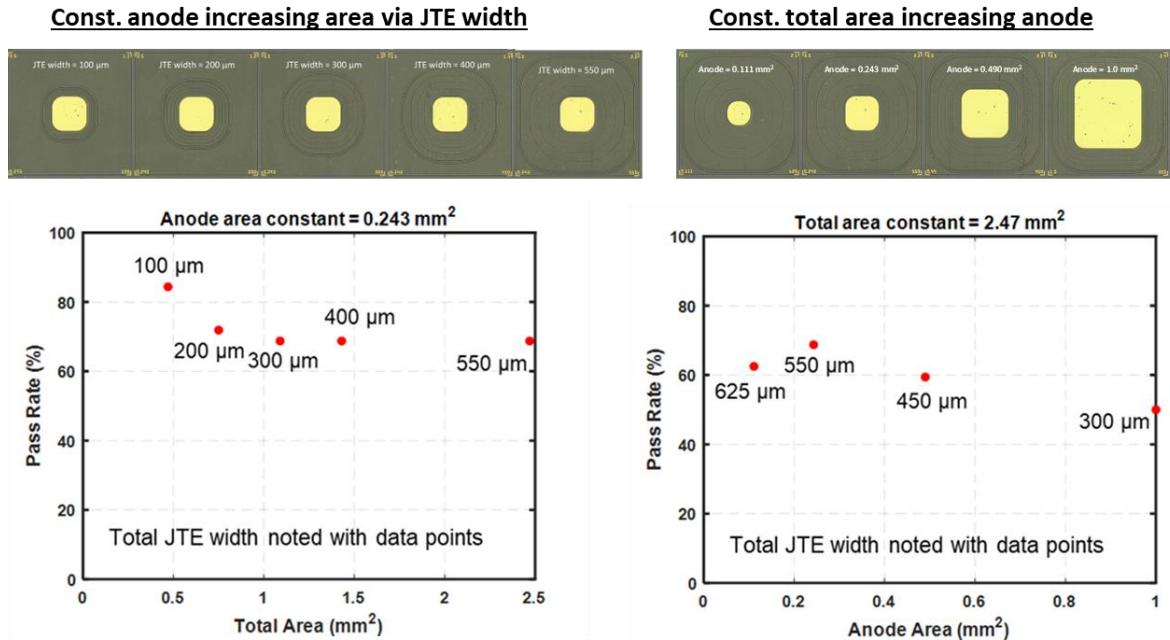

| Figure 8. (left) The pass rate vs. total area for the devices with a constant anode area and increasing JTE width. The JTE width is noted on the data points, and an image of the completed diodes is shown above the plot. (right) The pass rate for devices with a constant total area vs. anode area. An image of the diodes is shown above the plot. Increasing the device total area reduces the pass rate, with a combination of large anode and large total area leading to the lowest yield.....                                                                                                                        | 20 |

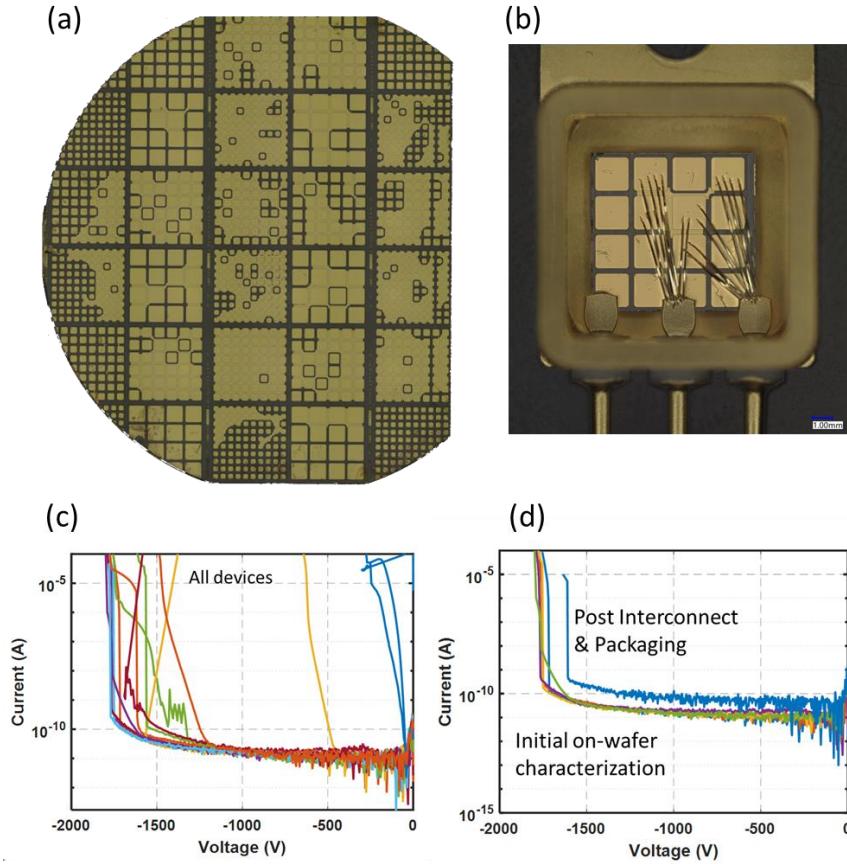

| Figure 9. (a) Completed 2" quad cell wafer post-screening and interconnect metallization. The right edge was diced off prior to interconnect for initial wire/ribbon bonding tests. (b) A 4 x 4 cell with five of the largest 2.77 mm <sup>2</sup> anode devices connected in parallel and ribbon-bonded into a TO-254 package. (c) Initial reverse I-V characterization of the on-wafer devices from the same cell shown in (b). (d) A comparison of the reverse I-V characteristics of the paralleled devices on-wafer and post interconnect and packaging. ....                                                              | 22 |

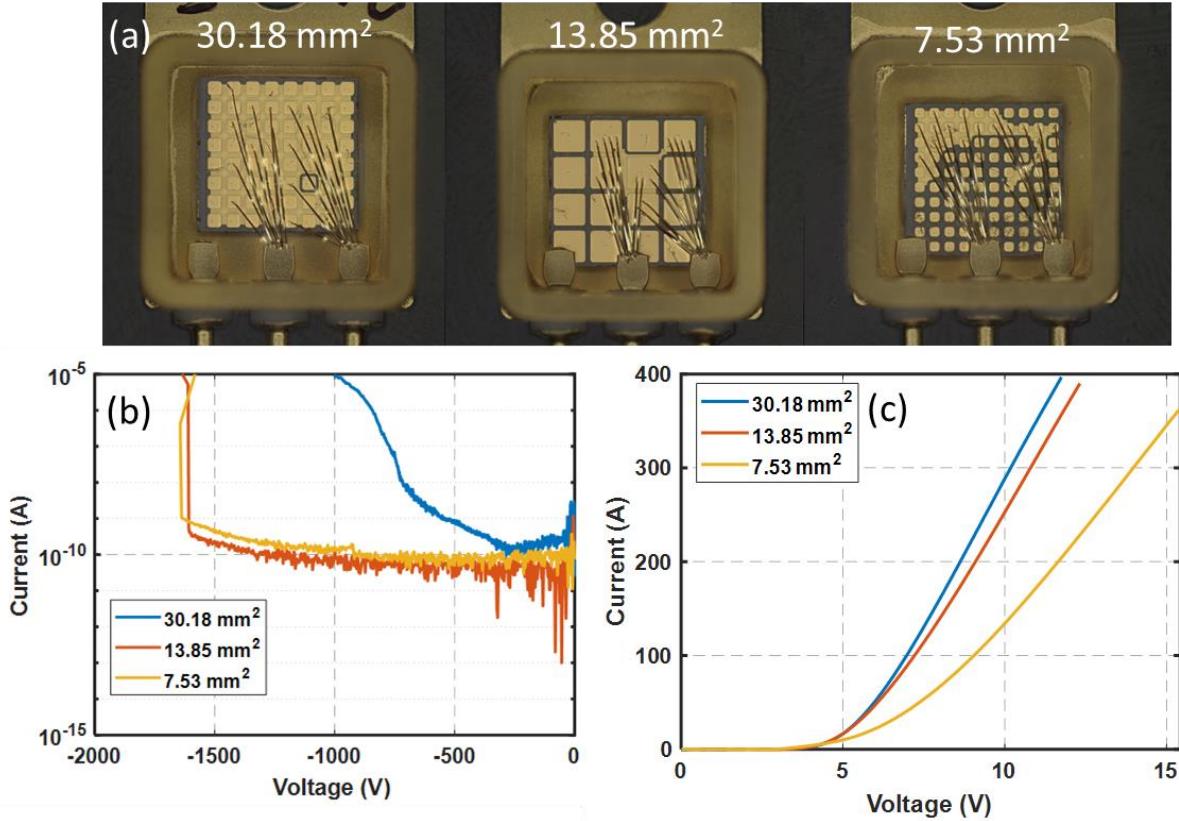

| Figure 10. (a) Optical images of three paralleled packaged diodes of varying individual anode areas. (b) The reverse I-V characteristics of the packaged diodes in (a). The 13.85 and 7.53 mm <sup>2</sup> devices maintained low leakage and 1600 V breakdown, while the largest 30.18 mm <sup>2</sup> device exhibited elevated leakage. (c) The forward I-V characteristics showing a reduction in resistance for the larger paralleled anode contact areas and ~400 A forward current conduction. Testing was performed using a 50 μs pulse width with a 0.1% duty cycle. ....                                              | 23 |

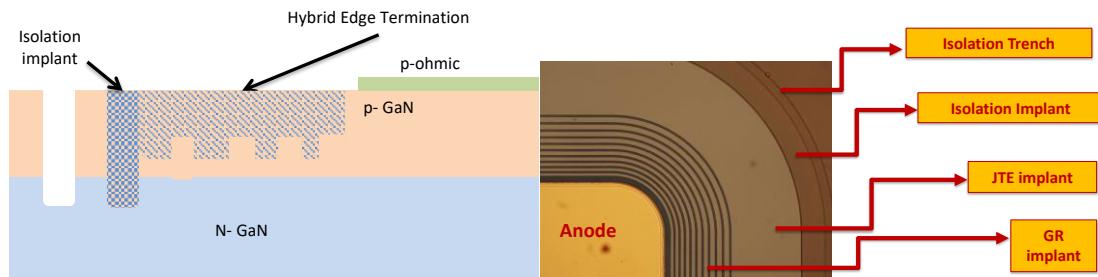

| Figure 11. GaN diode cross-section and optical image.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24 |

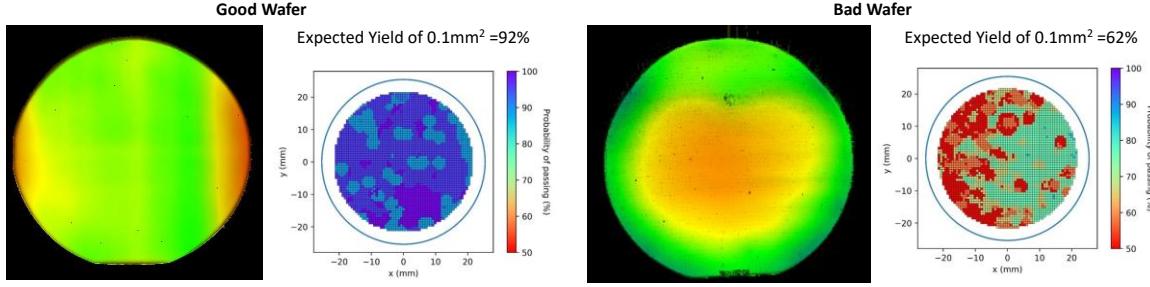

| Figure 12. Optical profilometry image and predicted yield for multiple wafers.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |

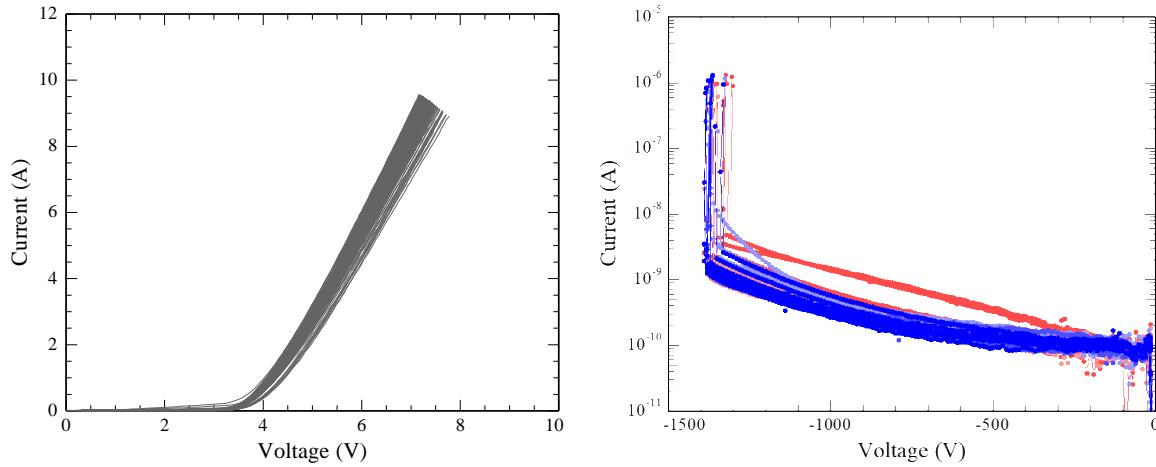

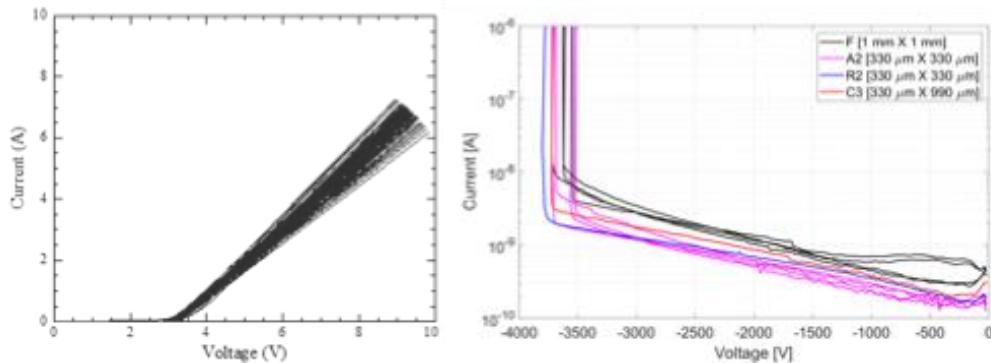

| Figure 13. Typical I-V behavior of 1 mm <sup>2</sup> , 1.2 kV-class Foundry diodes. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25 |

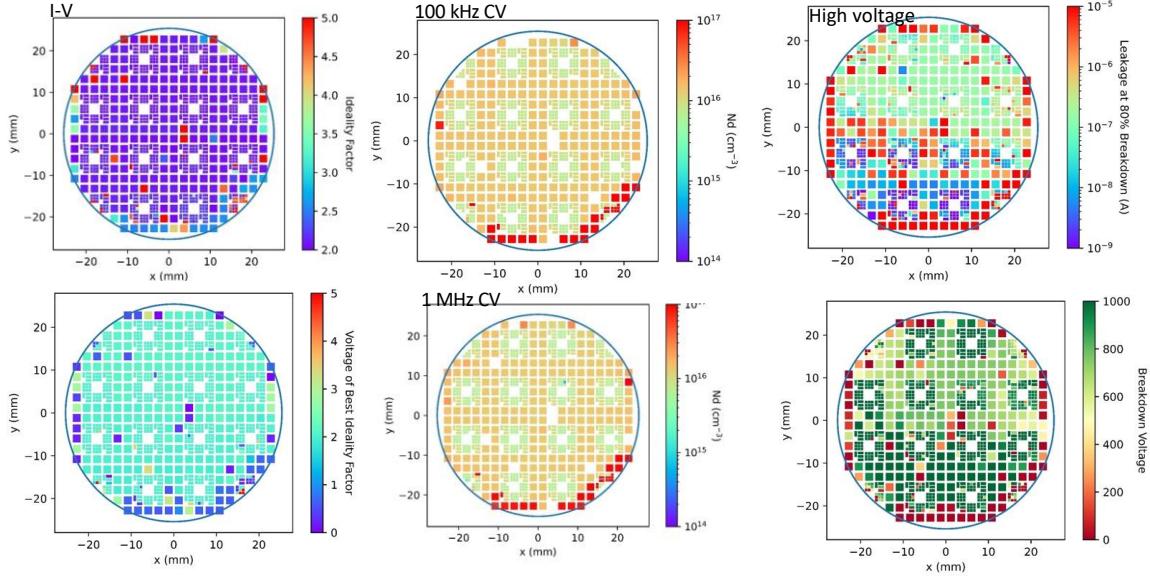

| Figure 14. Typical auto probe map of Foundry wafer. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

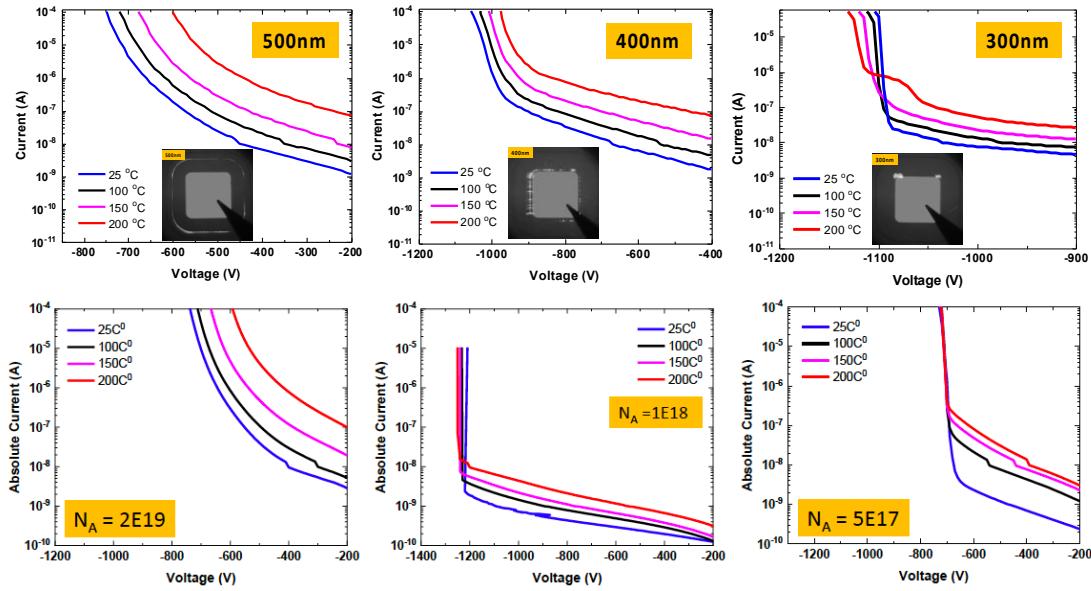

| Figure 15. Temperature-dependent reverse I-V behavior of six different anode designs. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 |

| Figure 16. Typical I-V behavior of 1 mm <sup>2</sup> 3.3 kV-class Foundry diodes. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |

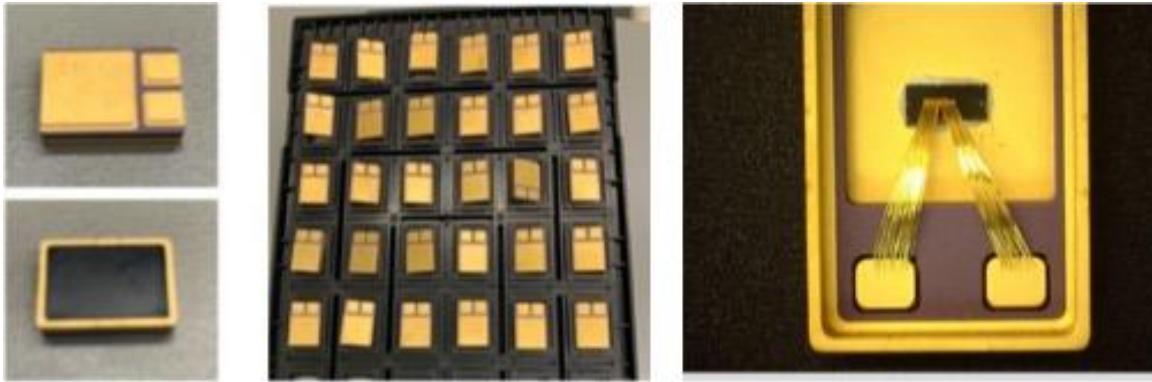

| Figure 17. Optical images of packaged parts from 1.2 kV-class diode wafer. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28 |

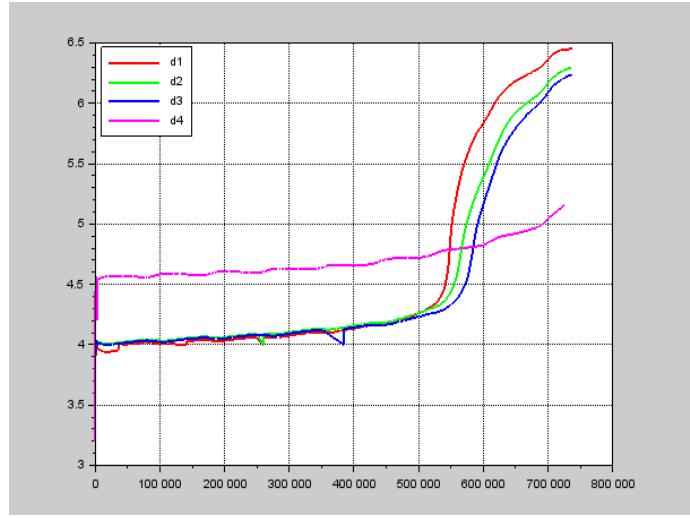

| Figure 18. Forward voltage versus time for four GaN diodes during HTOL testing.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29 |

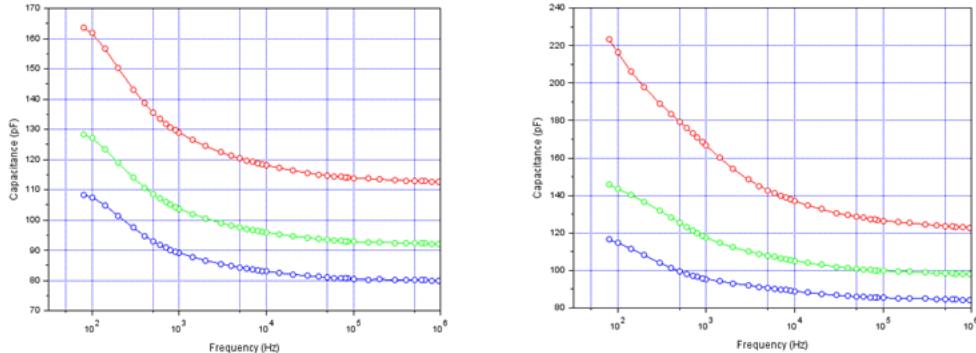

| Figure 19. Capacitance-frequency curves at -1 V (blue), 0 V (green), and 1 V (red) for representative GaN diode at (left) room temperature and (right) 150°C. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 |

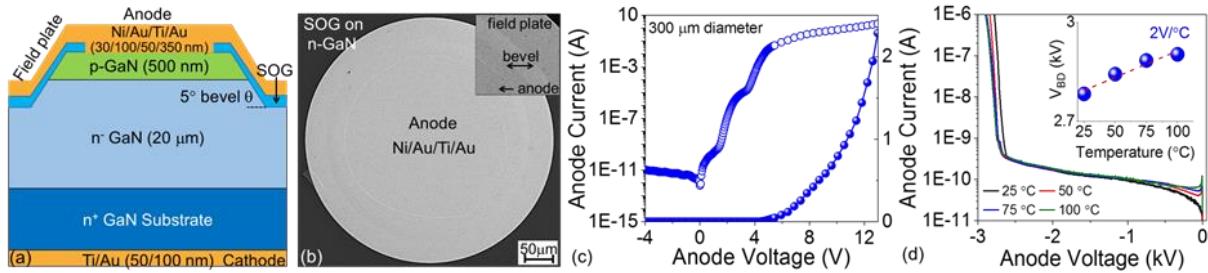

| Figure 20. (a) Cross-sectional schematic of 3 kV GaN vertical PN diode depicting different layers of the device stack. Field plate with 5° bevel was used as edge termination at anode. (b) Top view SEM image                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| of diode, with magnified view of field plate and bevel shown in the inset. (c) I-V characteristics of 3 kV GaN vertical PN diode. (d) Reverse breakdown voltage $V_{BD}$ @ 1 $\mu$ A measured at different temperatures.                                                                                                                                                                                                                      | 30 |

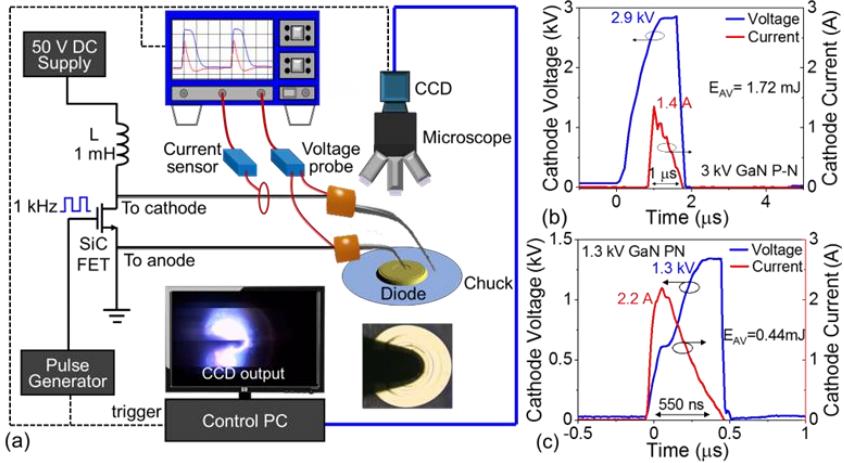

| Figure 21. (a) Experimental setup with integrated CCD for on-wafer UIS testing and avalanche study of GaN vertical PN diodes. The diode is probed on-chuck using thick needle probes and is connected anti-parallel to the MOSFET. (b) Cathode voltage and current waveforms recorded for 3 kV GaN vertical PN diode in a UIS cycle. (c) Cathode voltage and current waveforms recorded for 1.3 kV GaN vertical PN diode in similar test..... | 31 |

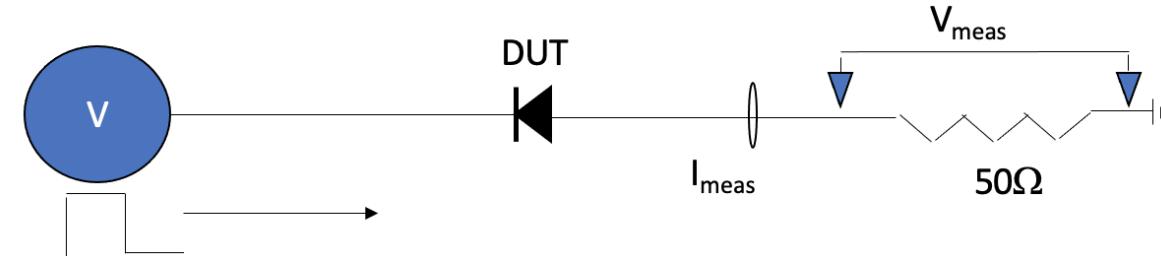

| Figure 22. Pulse Arrested Spark Discharge testing diagram for GaN diode. ....                                                                                                                                                                                                                                                                                                                                                                 | 32 |

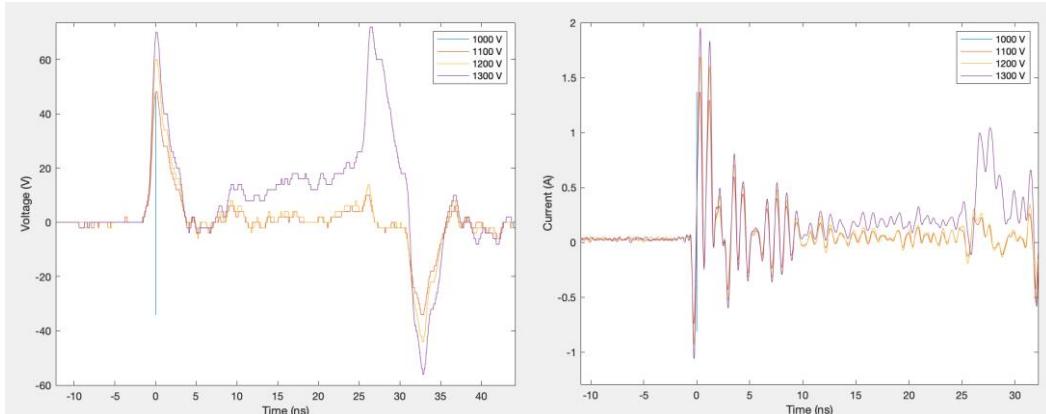

| Figure 23. (left) Voltage profile of the PASD pulser from 1000 V to 1300 V. (right). Current profile of the terminating 50 $\Omega$ resistor of the PASD pulser. ....                                                                                                                                                                                                                                                                         | 32 |

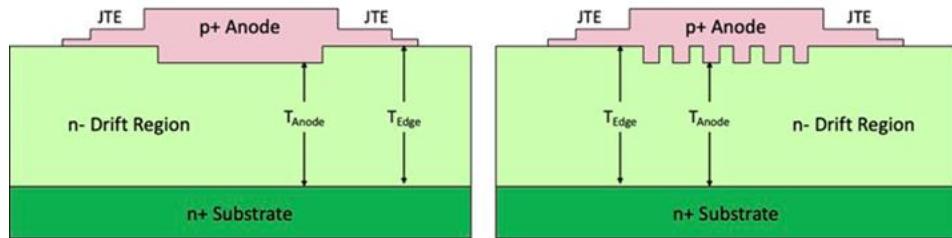

| Figure 24. Two diode structures designed for broad-area avalanche rather than edge breakdown.....                                                                                                                                                                                                                                                                                                                                             | 33 |

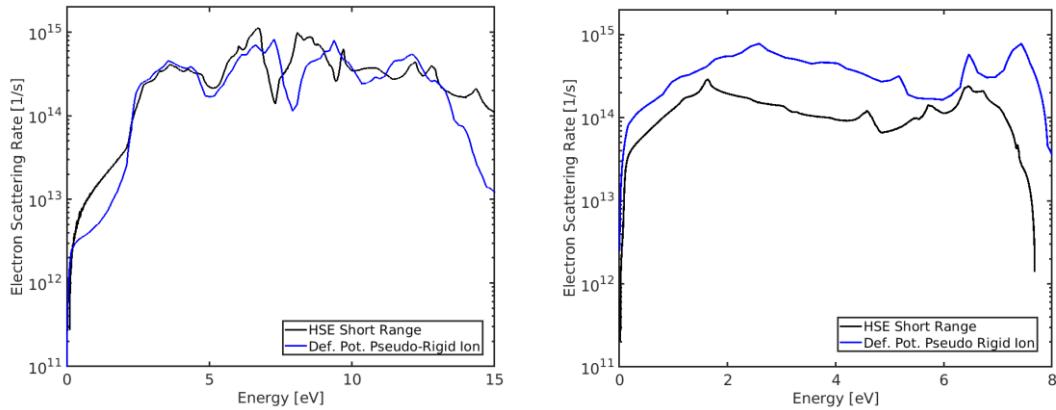

| Figure 25. (left) Comparison between the electron-phonon deformation potential scattering calculated with the pseudo-rigid-ion (blue line) and DFT-HSE (black line) models. (right) Comparison between the hole-phonon deformation potential scattering calculated with the pseudo-rigid-ion (blue line) and DFT-HSE (black line) models.....                                                                                                 | 34 |

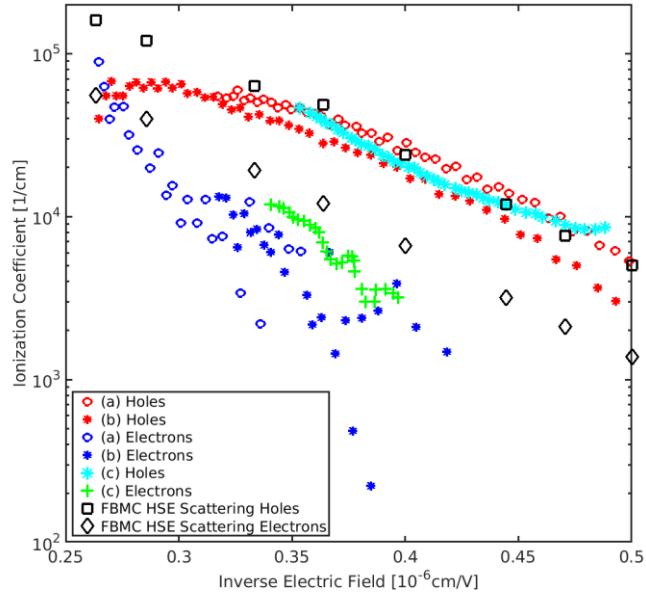

| Figure 26. Comparison between the measured and computed electron and hole ionization coefficients for GaN. The data sets are from: (a) and (b) Cao et al., APL 112, 262103 (2018), (c) Maeda et al., Maeda et al., JAP 129, 185702 (2021). The calculated hole and electron ionization coefficients are represented by open black squares and open black diamonds respectively.....                                                           | 35 |

## Accomplishments and Objectives

A summary of the tasks, milestones, deliverables, and their final status is provided in the table below.

**Table 1. Key Milestones and Deliverables.**

| Tasks                                                                                                                                                                                                                          | Milestones and Deliverables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Task 1: Development of work plan</b><br><br>1.1: Refine tasks and milestones for the work plan                                                                                                                              | <ul style="list-style-type: none"><li>• Development of interim/lower level tasks and milestones. <b>Project Q1</b></li><li>• 1.1: Refine tasks and milestones for the work plan (if applicable). <b>Due project Q1</b><br/><b>Actual Performance:</b> <b>Completed Q1 (FY19Q4).</b> Reviewed and verified milestones at the program kickoff meeting in Philadelphia on June 20, 2019 as well as at the project kickoff meeting in Washington DC on October 7, 2019.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>Task 2: Epitaxial Materials Growth</b><br><br>2.1: (Go/No-Go) Develop growth conditions for 5 kV PN diode<br><br>2.2: Develop growth conditions for 10 kV PN diode<br><br>2.3: Develop growth conditions for 20 kV PN diode | <ul style="list-style-type: none"><li>• The final objective of this project element is to grow epitaxial GaN layers of sufficiently low net doping and sufficiently high thickness to achieve a prototype 20 kV PN diode fabricated at Sandia for the EMP arrestor, and 6.5 kV diodes fabricated with high yield at the NRL/NIST nanofab. <b>Project Q1-Q9</b></li><li>• 2.1: Demonstrate controllable n-type doping <math>&lt;8 \times 10^{15} \text{ cm}^{-3}</math>, evaluated by capacitance-voltage measurements, in a <math>&gt;30\text{-}\mu\text{m}</math>-thick epitaxial GaN layer on a GaN substrate suitable for 5 kV device processing as justified through simulations and edge termination. Perform studies of compensating deep level defects in the GaN layer and correlate to growth conditions. Concurrently develop growth conditions necessary for a 1.2 kV diode to be fabricated at the NRL/NIST nanofab. <b>Due project Q3</b><br/><b>Actual Performance:</b> <b>Completed project Q2 (FY20Q1).</b> Drift layers of thickness <math>&gt;40 \mu\text{m}</math> with doping as low as <math>1-2 \times 10^{15} \text{ cm}^{-3}</math> were achieved.</li><li>• 2.2: Demonstrate controllable n-type doping <math>&lt;4 \times 10^{15} \text{ cm}^{-3}</math>, evaluated by capacitance-voltage measurements, in a <math>&gt;50\text{-}\mu\text{m}</math>-thick epitaxial GaN layer on a GaN substrate suitable for 10 kV device processing as justified through simulations and edge termination. Perform studies of compensating deep level defects in the GaN layer and correlate to growth conditions. Concurrently develop growth conditions necessary for a 3.3 kV diode to be fabricated at the NRL/NIST nanofab. <b>Due project Q6</b><br/><b>Actual Performance:</b> <b>Completed project Q6 (FY21Q1).</b> The team measured carrier concentrations of <math>1-3 \times 10^{15} \text{ cm}^{-3}</math> by CV measurements of fabricated PN diodes with 45- and 50-<math>\mu\text{m}</math>-thick drift layers. Similar carrier concentrations were measured by Hg-probe CV of n-GaN epitaxial calibration layers.</li><li>• 2.3: Demonstrate controllable n-type doping <math>&lt;2 \times 10^{15} \text{ cm}^{-3}</math>, evaluated by capacitance-voltage measurements, in a <math>&gt;100\text{-}\mu\text{m}</math>-thick epitaxial GaN layer on a GaN substrate suitable for 20 kV device processing as justified through simulations and edge termination. Perform studies of compensating deep level defects in the GaN layer and correlate to growth conditions.</li></ul> |

| Tasks                                                                                                                                                                                                                                                                        | Milestones and Deliverables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                              | <p>thick epitaxial GaN layer on a GaN substrate suitable for 20 kV device processing as justified through simulations and edge termination. Perform studies of compensating deep level defects in the GaN layer and correlate to growth conditions. Concurrently develop growth conditions necessary for a 6.5 kV prototype diode to be fabricated with high yield at the NRL/NIST nanofab. <b>Due project Q9</b></p> <p><b>Actual Performance: Estimated to be 50% complete at the end of the project.</b> A trial thick epi run using the TNSC reactor at Sandia was not successful and resulted in severe build-up in the reactor. This prompted the team to re-consider the feasibility of MOCVD for 10- and 20-kV-class epi, and investigations have been on-going regarding the possible use of HVPE growth instead. As a result of this, the focus of the project shifted to large-area (<math>&gt;10 \text{ mm}^2</math>) devices in the 1-5 kV range.</p>                                                                                                                                                                                               |

| <p><b>Task 3: Materials</b></p> <p>3.1: Impact ionization characterization</p>                                                                                                                                                                                               | <ul style="list-style-type: none"> <li>The final objective of this project element is to establish the semiconductor materials understanding necessary to enable a prototype 20 kV GaN PN diode fabricated at Sandia for the EMP arrestor, and a 6.5 kV diode fabricated with high yield at the NRL/NIST nanofab. <b>Project Q1-Q9</b></li> <li>3.1: Determine impact ionization coefficients in GaN based on optically-induced avalanche multiplication experiments at Stanford. Approximately 4 wafers with epi per quarter will be provided by Sandia to Stanford for this task/milestone, plus other processing tasks performed there. Acceptance of an impact ionization characterization report by ARPA-E Program Director. <b>Due project Q8</b></li> </ul> <p><b>Actual Performance: Completed project Q8 (FY21Q3).</b> Measurements of the ionization coefficients were made and compared to processed device breakdown voltage data.</p>                                                                                                                                                                                                               |

| <p><b>Task 4: Device Fabrication</b></p> <p>4.1: Establish baseline high-yield pilot 1.2 kV diode manufacturing line.</p> <p>4.2: Demonstrate 5 kV GaN diode</p> <p>4.3: Establish high-yield pilot 3.3 kV diode production line</p> <p>4.4: Demonstrate 10 kV GaN diode</p> | <ul style="list-style-type: none"> <li>The final objective of this project element is to fabricate a prototype 20 kV GaN PN diode at Sandia for the EMP arrestor, and to establish a 6.5 kV GaN PN diode in a high-yield pilot production line at the NRL/NIST nanofab. <b>Project Q4-Q12</b></li> <li>4.1: Establish a baseline, high-yield pilot manufacturing capability for a 1.2 kV GaN PN diode with avalanche breakdown. Develop back-side ohmic contacts suitable for 1.2, 3.3, and 6.5 kV GaN PN diodes. Develop back-side thinning processes for GaN diodes in support of impact-ionization studies. Demonstrate reliable high-yield production of this diode at the NRL/NIST NanoFab with <math>&gt;50\%</math> yield on at least one wafer per lot, where yield is defined as GaN PN diodes with area <math>&gt;1 \text{ mm}^2</math>, forward current density <math>&gt;500 \text{ A/cm}^2</math>, differential specific on-resistance in the forward direction <math>&lt;1.3 \text{ m}\Omega \text{ cm}^2</math>, turn-on voltage <math>&lt;3.5 \text{ V}</math>, and leakage current density <math>&lt;1 \text{ mA/cm}^2</math> at 80%</li> </ul> |

| Tasks                                                                                                       | Milestones and Deliverables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p>4.5: Establish high-yield pilot 6.5 kV diode production line</p> <p>4.6: Demonstrate 20 kV GaN diode</p> | <p>of rated breakdown voltage. Approximately 12 wafers with epi per quarter will be provided by Sandia to NRL for this task/milestone. Acceptance of a baseline 1.2 kV process report by ARPA-E Program Director. <b>Due project Q5</b></p> <p><b>Actual Performance:</b> <b>Completed project Q7 (FY21Q2).</b> Many of the 1.2-kV-class, 1 mm<sup>2</sup> devices met the yield target for most metrics. However, a problematic issue was the thick metallization, which significantly impacted <math>R_{ON}</math> and was unavailable due to the COVID-imposed closure of the NIST nanofab. The addition of thick Au metallization at NRL enabled an estimated reduction in <math>R_{ON}</math> for the best Foundry devices such that the 1.3 m<math>\Omega</math> cm<sup>2</sup> target was met with the appropriate use of wafer thinning and back-side processing.</p> <ul style="list-style-type: none"> <li>4.2: Fabricate and characterize 5 kV GaN PN diode and verify &gt;5 kV avalanche breakdown. The diode must also have: Area &gt;1 mm<sup>2</sup>, forward current density &gt;330 A/cm<sup>2</sup>, differential specific on-resistance in the forward direction &lt;7.7 m<math>\Omega</math> cm<sup>2</sup>, turn-on voltage &lt;3.5 V, and leakage current density &lt;1 mA/cm<sup>2</sup> at 80% of rated breakdown voltage. <b>Due project Q6</b></li> <li><b>Actual Performance:</b> <b>Completed project Q7 (FY21Q2).</b> As of the previous quarter, all of the metrics had been met except for the forward turn-on criterion, and this final metric was met in project Q7. A detailed investigation of the dependence of the forward characteristics of the device with duty cycle was conducted, which allowed the turn-on metric to be satisfied.</li> <li>4.3: Establish high-yield pilot manufacturing capability for a 3.3 kV GaN PN diode with avalanche breakdown. Demonstrate reliable high-yield production of this diode at the NRL/NIST NanoFab with &gt;30% yield on at least one wafer per lot, where yield is defined as GaN PN diodes with area &gt;1 mm<sup>2</sup>, forward current density &gt;400 A/cm<sup>2</sup>, differential specific on-resistance in the forward direction &lt;3.8 m<math>\Omega</math> cm<sup>2</sup>, turn-on voltage &lt;3.5 V, and leakage current density &lt;1 mA/cm<sup>2</sup> at 80% of rated breakdown voltage. Approximately 12 wafers with epi per quarter will be provided by Sandia to NRL for this task/milestone. Acceptance of a 3.3 kV pilot production process report by ARPA-E Program Director. <b>Due project Q8</b></li> <li><b>Actual Performance:</b> <b>Estimated to be 50% complete at the end of the project.</b> This milestone was not completed primarily due to the closure of the NIST fab. However, good progress was made, particularly towards the end of the project – devices were designed, epi was delivered to NRL, and initial device results were very promising, with breakdown voltages up to 3.8 kV demonstrated.</li> </ul> |

| Tasks                                                                                            | Milestones and Deliverables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                  | <ul style="list-style-type: none"> <li>4.4: Fabricate and characterize 10 kV GaN PN diode and verify &gt;10 kV avalanche breakdown. The diode must also have: Area &gt;1 mm<sup>2</sup>, forward current density &gt;200 A/cm<sup>2</sup>, differential specific on-resistance in the forward direction &lt;28 mΩ cm<sup>2</sup>, turn-on voltage &lt;3.5 V, and leakage current density &lt;1 mA/cm<sup>2</sup> at 80% of rated breakdown voltage. <b>Due project Q9</b><br/> <b>Actual Performance: Estimated to be 50% complete at the end of the project.</b> While progress was made and breakdown voltages &gt;6 kV were achieved, given the reconsideration of the drift region growth mentioned above, the 10 kV device work was delayed as the focus of the project shifted to large-area (&gt;10 mm<sup>2</sup>) 1-5 kV diodes.</li> <li>4.5: Establish high-yield pilot manufacturing capability for a 6.5 kV GaN PN diode with avalanche breakdown. Demonstrate reliable high-yield production of this diode at the NRL/NIST NanoFab with &gt;10% yield on at least one wafer per lot, where yield is defined as GaN PN diodes with area &gt;1 mm<sup>2</sup>, forward current density &gt;280 A/cm<sup>2</sup>, differential specific on-resistance in the forward direction &lt;13 mΩ cm<sup>2</sup>, turn-on voltage &lt;3.5 V, and leakage current density &lt;1 mA/cm<sup>2</sup> at 80% of rated breakdown voltage. Approximately 12 wafers with epi per quarter will be provided by Sandia to NRL for this task/milestone. Acceptance of a 6.5 kV pilot production process report by ARPA-E Program Director. <b>Due project Q11</b><br/> <b>Actual Performance: Estimated to be 0% complete at the end of the project.</b> This milestone was delayed due to the unavailability of 6.5 kV class epi coupled with the closure of the NIST nanofab, resulting in the focus of the Foundry processing efforts on 1.2 and 3.3 kV class device fabrication.</li> <li>4.6: Fabricate and characterize 20 kV GaN PN diode and verify &gt;20 kV avalanche breakdown. The diode must also have: Area &gt;1 mm<sup>2</sup>, forward current density &gt;110 A/cm<sup>2</sup>, differential specific on-resistance in the forward direction &lt;110 mΩ cm<sup>2</sup>, turn-on voltage &lt;3.5 V, and leakage current density &lt;1 mA/cm<sup>2</sup> at 80% of rated breakdown voltage. <b>Due Project Q12</b><br/> <b>Actual Performance: Estimated to be 0% complete at the end of the project.</b> This milestone was delayed due to the unavailability of 20-kV-class epi as discussed above, resulting in a shift in focus of the project to large-area (&gt;10 mm<sup>2</sup>) 1-5 kV diodes.</li> </ul> |

| <b>Task 5: Device Modeling</b><br>5.1: Evaluate edge terminations and down-select to best design | <ul style="list-style-type: none"> <li>The final objective of this project element is to design an edge termination that enables 6.5 kV breakdown in a high-yield GaN PN diode and 20 kV breakdown in a prototype GaN PN diode, without sacrificing switching speed. <b>Project Q1-Q10</b></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Tasks                                                                                                                                                              | Milestones and Deliverables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p>5.2: Finalize edge termination for 3.3 and 10 kV diodes</p> <p>5.3: Finalize edge termination for 6.5 and 20 kV diodes</p> <p>5.4: EMP switching simulation</p> | <ul style="list-style-type: none"> <li>5.1: Evaluate the suitability of different edge termination approaches for high voltage diodes based on numerical simulation and compatibility with processing capability. Down-select to most suitable design and optimize for 1.2 and 5 kV diodes. Acceptance of an edge termination simulation report by ARPA-E Program Director. <b>Due project Q3</b><br/> <b>Actual Performance:</b> <b>Completed project Q4 (FY20Q3).</b> For the Foundry, the primary path was established to use implanted guards/rings and/or JTEs, with a secondary plan to use a bevel termination. Simulations and experiments at Stanford determined that a 1° edge termination is a highly efficient edge termination design. For the high-voltage EMP arrestor diodes, the path was established to utilize a multi-zone JTE implemented either by etching.</li> <li>5.2: Finalize edge termination design for 3.3 and 10 kV diodes using numerical simulation. Acceptance of an edge termination simulation report by ARPA-E Program Director. <b>Due project Q6</b><br/> <b>Actual Performance:</b> <b>Completed project Q6 (FY21Q1).</b> Simulations were performed of both the drift layers and the anodes/edge terminations required for the 10 kV EMP diodes and the 3.3. kV Foundry diodes. The 10 kV diodes will utilize a multi-step JTE, and the 3.3 kV diodes will utilize various combinations of guard rings and JTEs as a primary path, and bevel termination as a secondary path. This follows the approach used for the 5 kV EMP diodes and 1.2 kV Foundry diodes.</li> <li>5.3: Finalize edge termination design for 6.5 and 20 kV diodes using numerical simulation. Acceptance of an edge termination simulation report by ARPA-E Program Director. <b>Due project Q9</b><br/> <b>Actual Performance:</b> <b>Estimated to be 75% complete at the end of the project.</b> While substantial progress on this task was made, it was put on hold due to the thick epi and NIST nanofab challenges described above, and the resulting shift in the project focus to large-area (<math>&gt;10 \text{ mm}^2</math>) 1-5 kV diodes.</li> <li>5.4: Perform simulation studies to ensure that diode design is compatible with switching performance required for use in EMP applications. Acceptance of an EMP switching simulation report by ARPA-E Program Director. <b>Due project Q10</b><br/> <b>Actual Performance:</b> <b>Estimated to be 75% complete at the end of the project.</b> Electro-thermal considerations under high-voltage/high-current avalanche conditions were examined, and TCAD simulations of avalanche structures were also conducted.</li> </ul> |

| Tasks                                                                                                                                                                                                                                                     | Milestones and Deliverables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|