## DER inverter control fault ride through model in accordance with IEEE 1547-2018 Std.

- ▶ Mark Booge

- ▶ Western Michigan University

This material is based upon work supported by the U.S. Department of Energy's Office of Cybersecurity, Energy Security, and Emergency Response (CESER) under Award no. DE-CR0000029. Additional support has been provided by Factory Mutual (FM) Insurance Co. through contract no. 7036430.

**APPLICATIONS & TECHNOLOGY CONFERENCE 2025**

CHICAGO, ILLINOIS, U.S.A.

# Introduction

Equip Distributed Energy Resource (DER) windfarm to comply with IEEE Std. 1547-2018, High Voltage Ride Through (HVRT) and Low Voltage Ride Through (LVRT)

1. IEEE Std. 1547-2018 Background

2. Reconstruct RMS meter

3. Base Model Background

4. Implement Sensing and Timing Control Logic

5. Implement Breaker Control

6. Results of Under and Over Voltages

7. Future Work

8. Questions and Answers

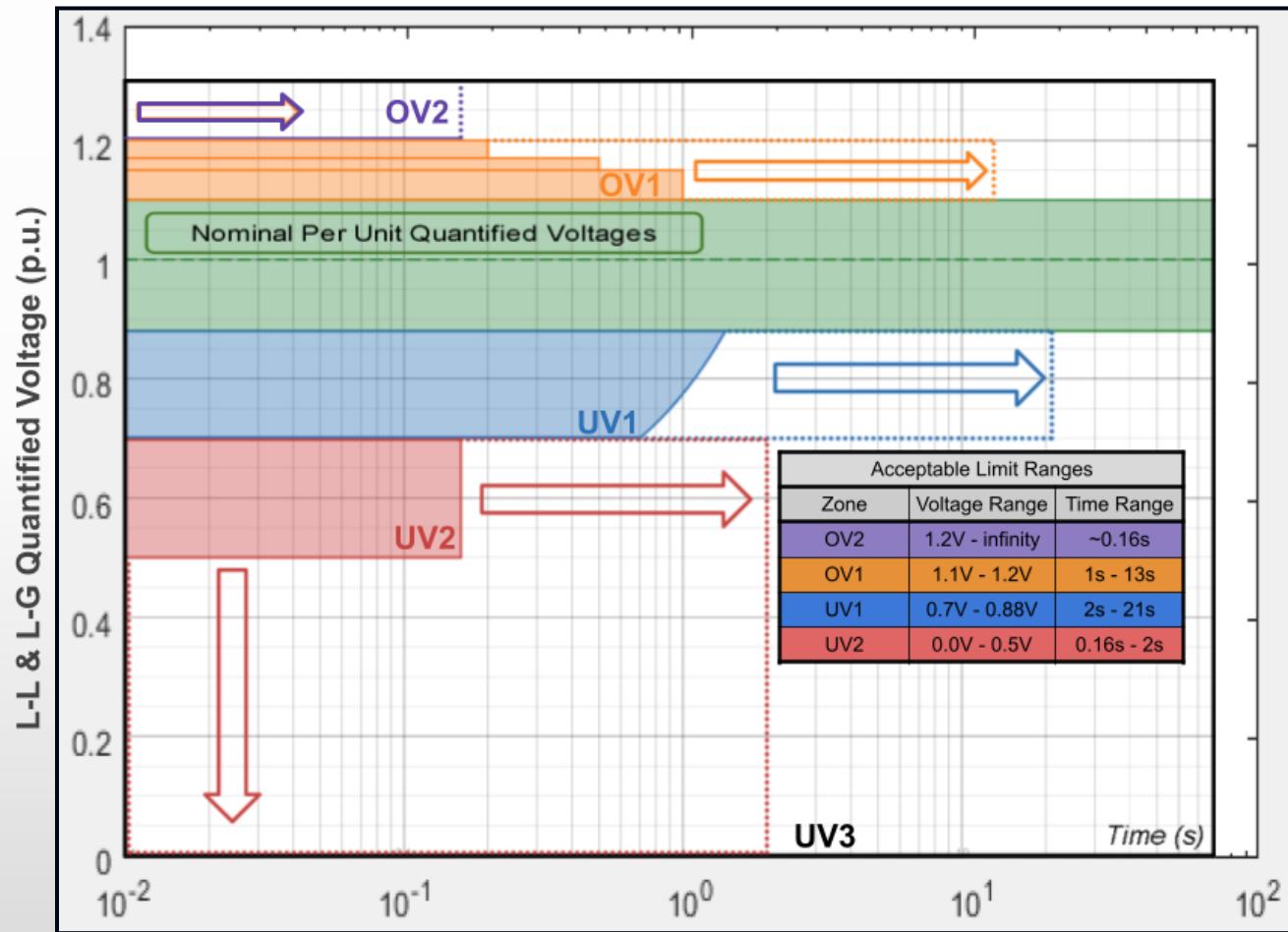

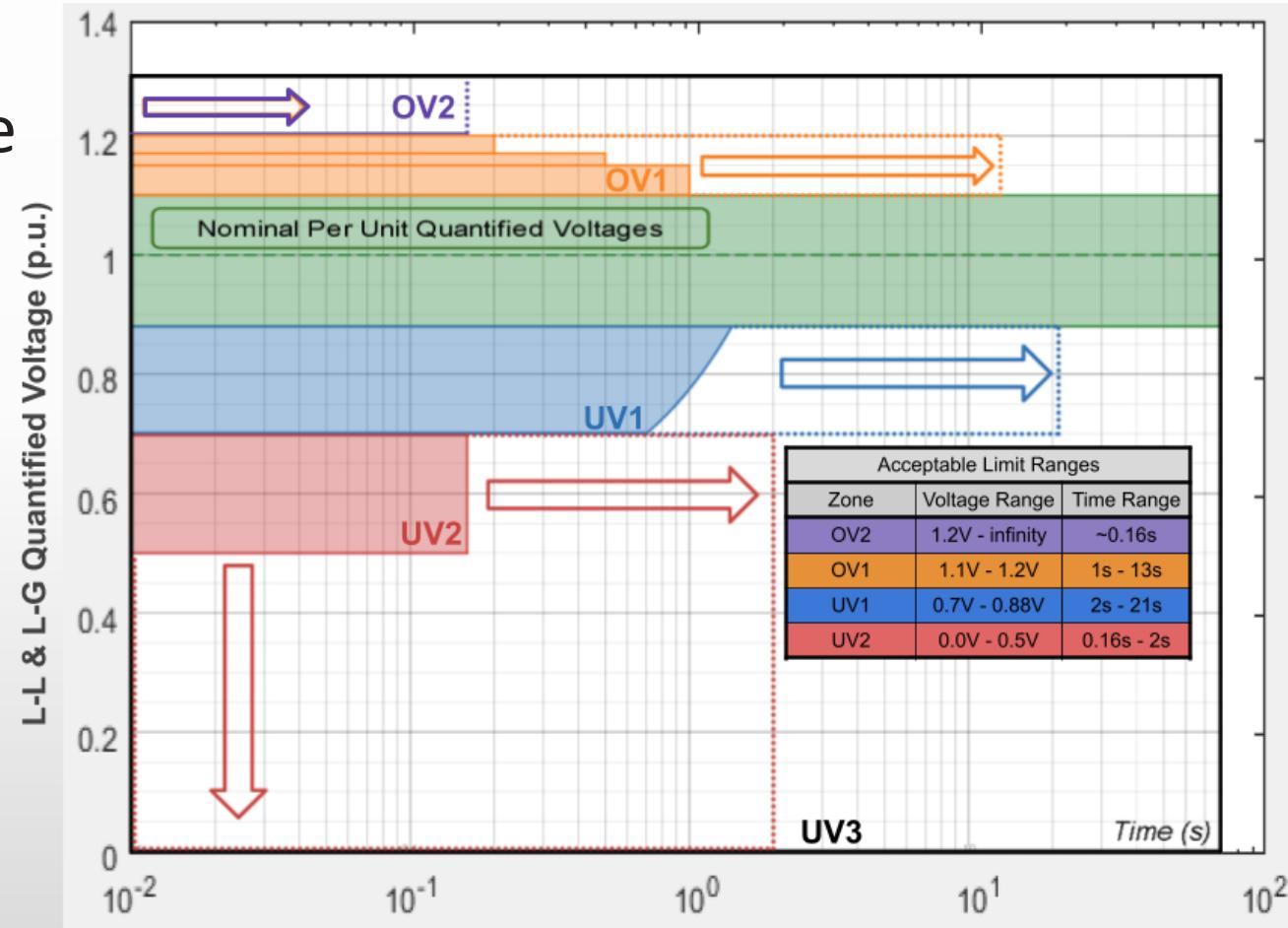

# IEEE Std. 1547-2018 HVRT & LVRT

- Defines the conditions where DER should cease to energize the grid for category 1

- Assigns Applicable Voltages based on grid voltage and phase layout

- Specifies undervoltage and overvoltage zones

- Allows operators to adjust trip zones based on DER needs

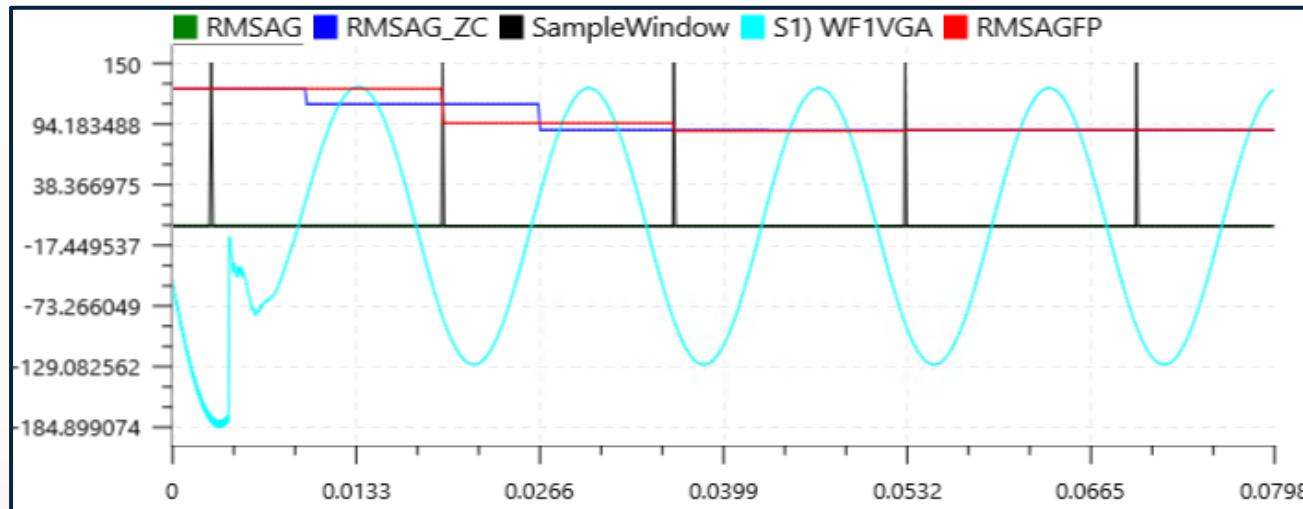

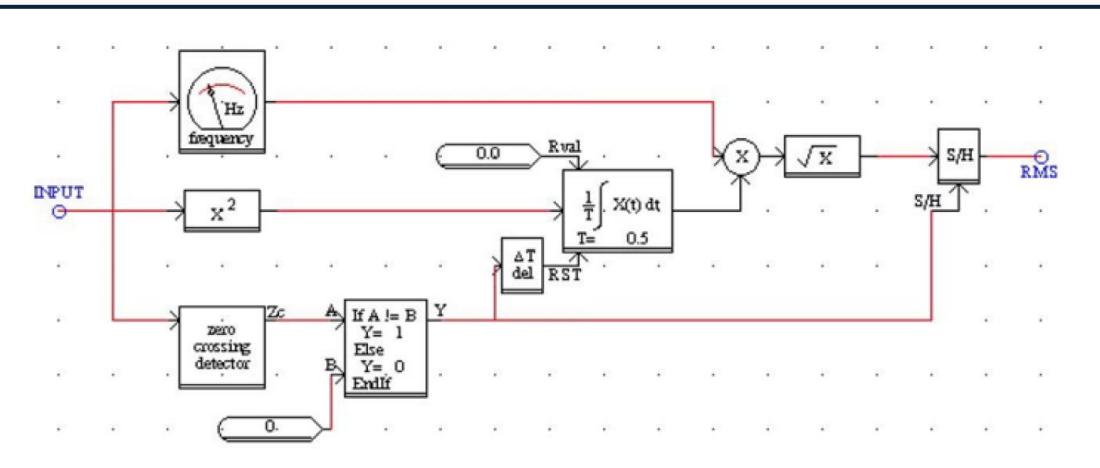

# RMS Measurement

## RSCAD Library RMS Meter:

- Samples RMS every zero crossing

- Fault transients may trigger RMS update

## Standard's Metering Requirement:

- Samples RMS in full period intervals

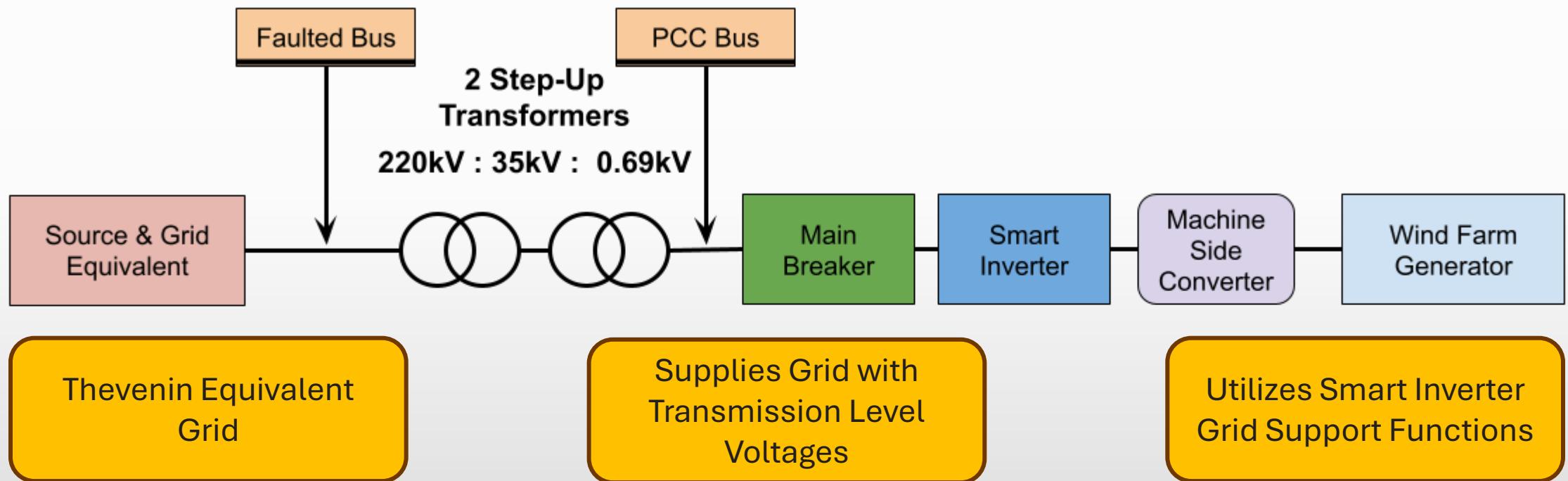

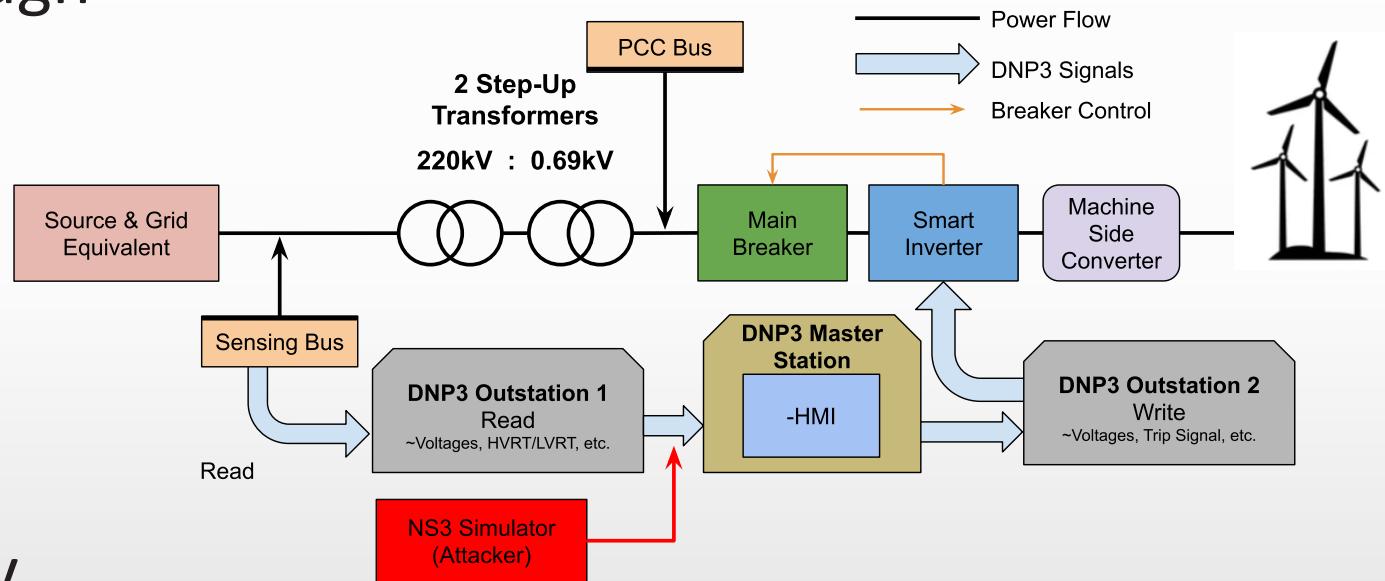

# Model Background

## PMSM LVRT/HVRT Grid-linked Smart Inverter

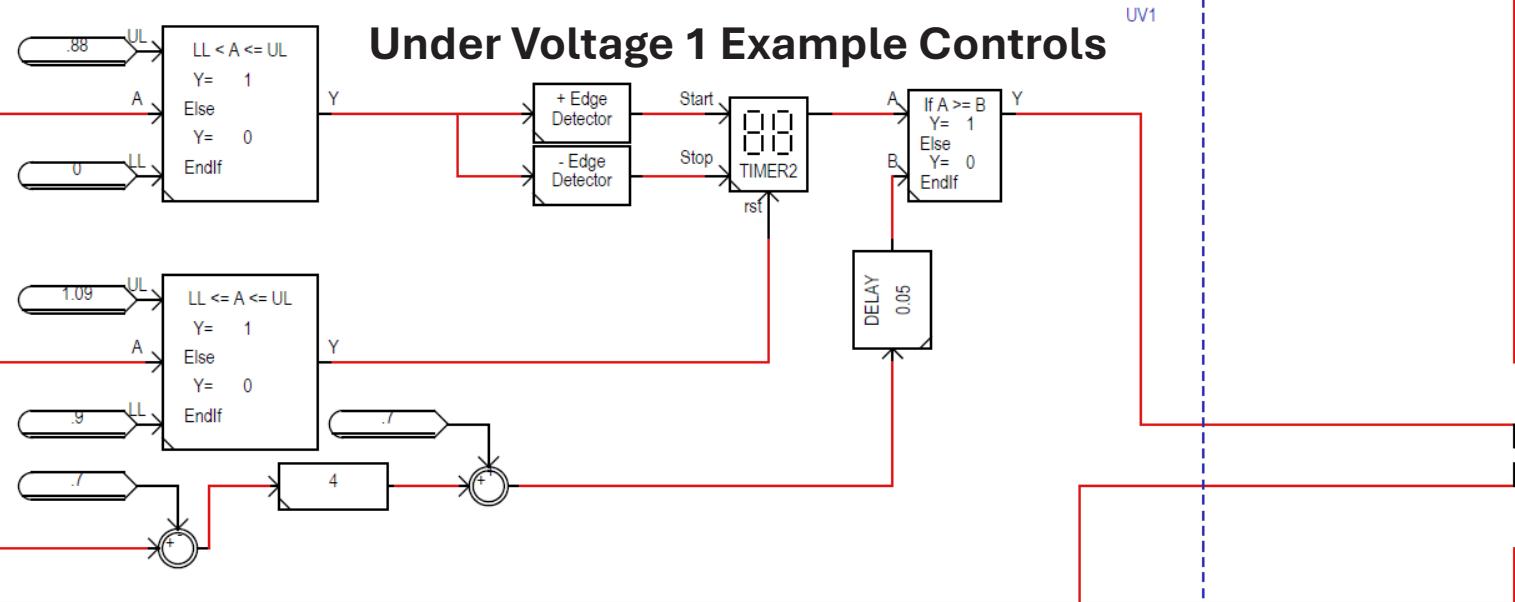

# Ride-Through Control Logic

- “Range Check” component senses voltage zone.

- High output starts the timer

- Low output stops the timer

- “Signal Comparator” component checks whether ride through time has been exceeded

- Timer resets when voltage returns to nominal

$$T_{\text{VRT}} = 0.7 \text{ s} + \frac{4 \text{ s}}{1 \text{ p.u.}} (V - 0.7 \text{ p.u.})$$

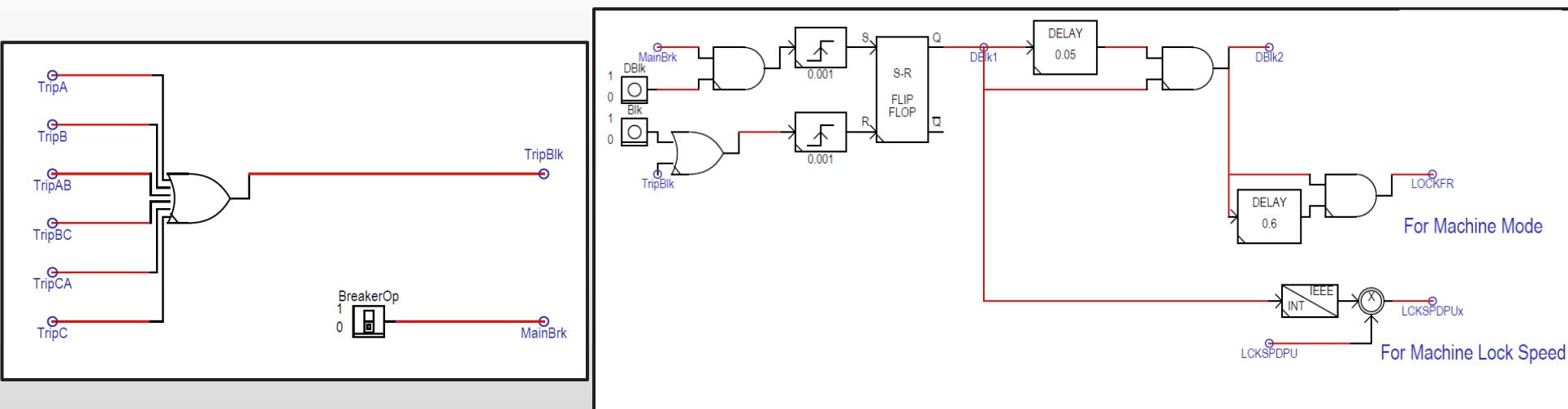

# Tripping Control Logic

- Routes through “OR” gates

- Connects to inverter blocking control scheme

- Implemented breaker open & close switch

# Control Summary

| Voltage range (p.u.)    | Operating mode/response        | Minimum ride-through time (s)<br>(design criteria)                                                                                                       | Maximum response time (s)<br>(design criteria) |

|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| $V > 1.20$              | Cease to Energize <sup>a</sup> | N/A                                                                                                                                                      | 0.16                                           |

| $1.175 < V \leq 1.20$   | Permissive Operation           | 0.2                                                                                                                                                      | N/A                                            |

| $1.15 < V \leq 1.175$   | Permissive Operation           | 0.5                                                                                                                                                      | N/A                                            |

| $1.10 < V \leq 1.15$    | Permissive Operation           | 1                                                                                                                                                        | N/A                                            |

| $0.88 \leq V \leq 1.10$ | Continuous Operation           | Infinite                                                                                                                                                 | N/A                                            |

| $0.70 \leq V < 0.88$    | Mandatory Operation            | Linear slope of 4 s/1 p.u. voltage starting at 0.7 s @ 0.7 p.u.:<br>$T_{VRT} = 0.7 \text{ s} + \frac{4 \text{ s}}{1 \text{ p.u.}}(V - 0.7 \text{ p.u.})$ | N/A                                            |

| $0.50 \leq V < 0.70$    | Permissive Operation           | 0.16                                                                                                                                                     | N/A                                            |

| $V < 0.50$              | Cease to Energize <sup>a</sup> | N/A                                                                                                                                                      | 0.16                                           |

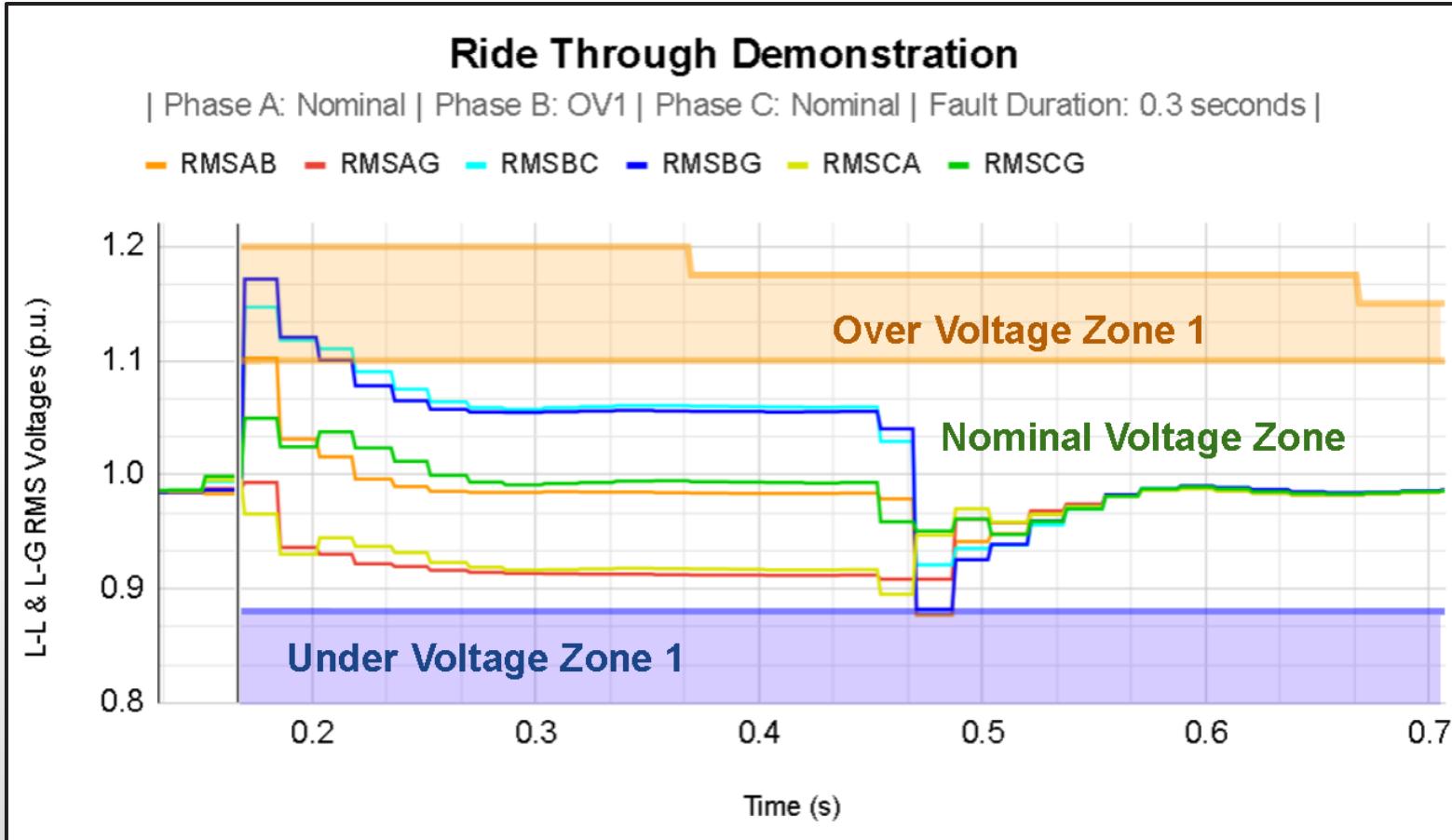

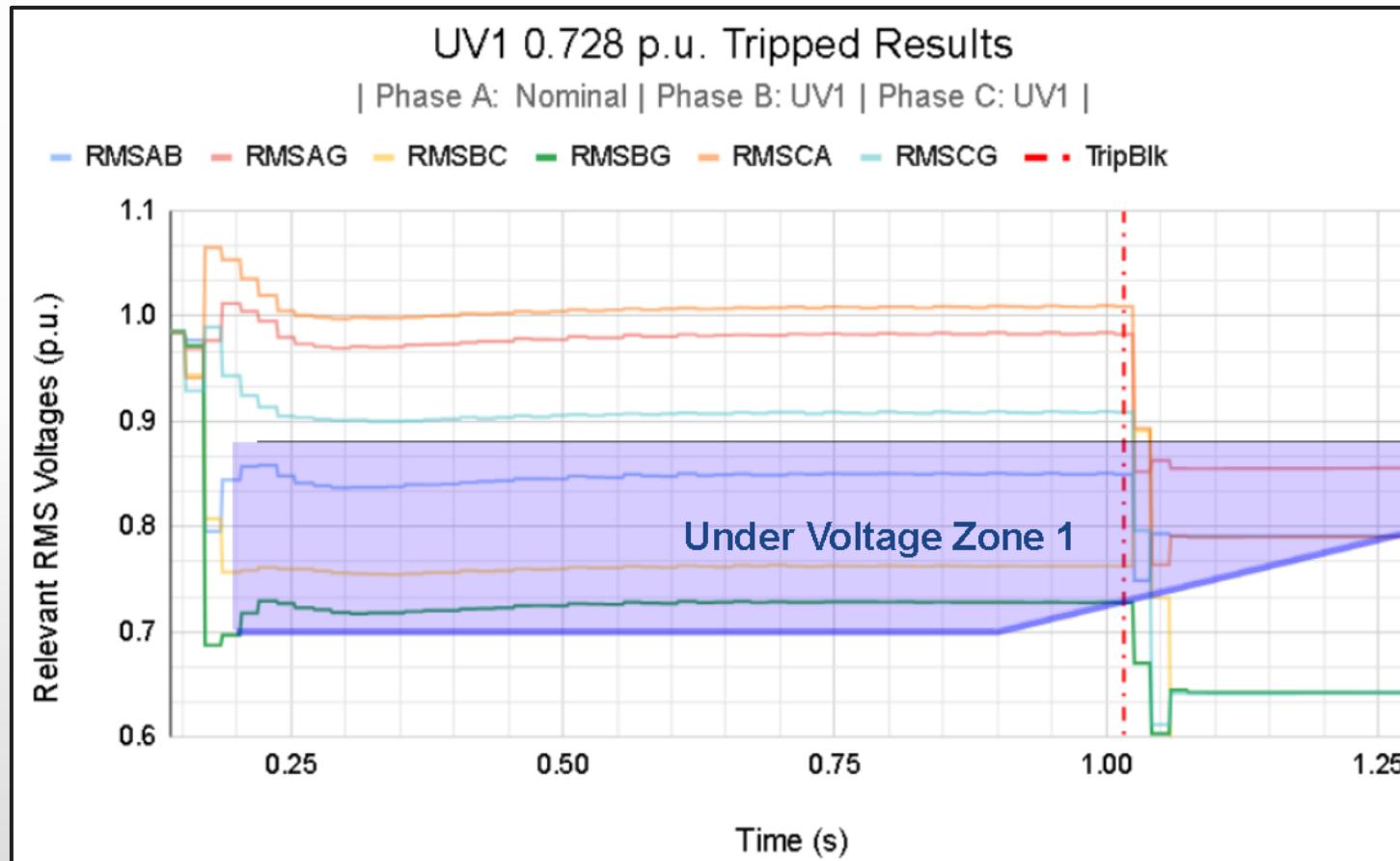

# Demonstration Ride -Through

- Voltages per unit quantity manually set

- Grid support functions allow ride-through

- RMS voltages reach zones **OV1** & **UV1**

# Demonstration

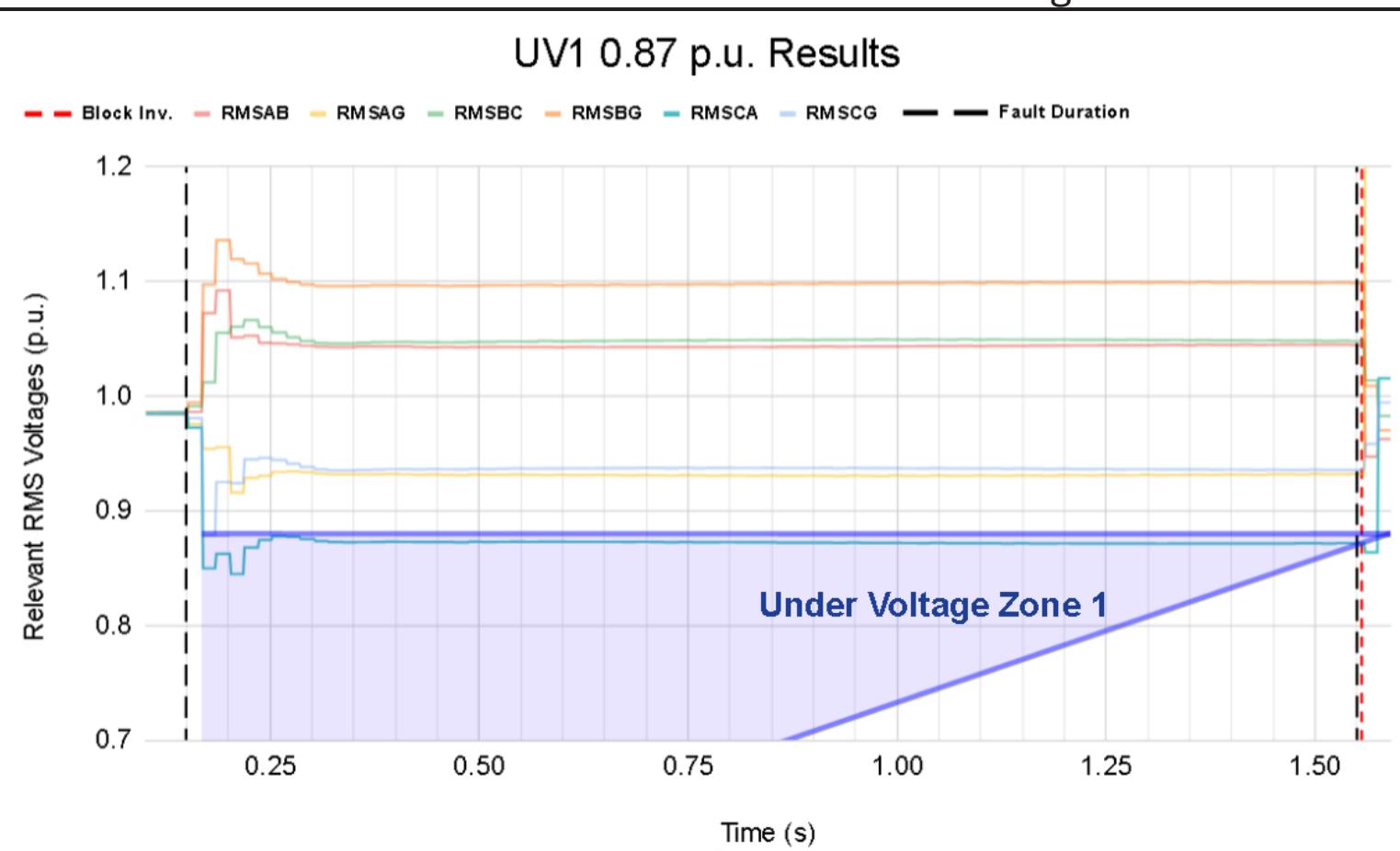

## UV1 Trip

Power Output

Before Blocking

Power Output

After Blocking

- Phase A to ground 1.5s fault

- RMS L-L Voltage A-B is 0.87 p.u.

- Cease to energize in 1.38s

- $1.38s > 1.5s$ : Block Inverter

$$T_{VRT} = 0.7 \text{ s} + \frac{4 \text{ s}}{1 \text{ p.u.}} (V - 0.7 \text{ p.u.})$$

# Demonstration UV1

## Ride -Through

- Simulating a two phase to ground fault

- Lowest Signal is L-L RMS Voltage B-C

- Rides-Through for 812ms

- $$T_{VRT} = 0.7 \text{ s} + \frac{4 \text{ s}}{1 \text{ p.u.}} (V - 0.7 \text{ p.u.})$$

- Grid Support Functions lost after Inverter is Blocked

# Future Work

- Implement frequency ride through and breaker control

- Redesign DER to support a distribution grid

- Design testbed for cybersecurity studies

# Acknowledgements

Thank you to all the people who have helped with this project, whether it was power systems knowledge, financial support, or assistance with the RTDS/RSCAD.

Special thank you to...

- WMU InterEnergy Center, host lab

- Dr. Pablo Gomez: Project Advisor, WMU InterEnergy Center Director, ECE Prof.

- DOE Office of Cybersecurity, Energy Security and Emergency Response (CESER), project sponsor

- Award no. DE-CR0000029

- FM (Factory Mutual Insurance Company), project sponsor

- Dr. Sujit Purushothaman: FM Lead Research Engineer

- RTDS Technologies Inc

- Arunprasanth Sakthivel: RTDS Senior Simulation Engineer

# Question and Answers

## Major Points:

1. IEEE Std. 1547-2018 outlines interconnection and interoperation of DERs with electrical power system

2. Altered RSCAD's RMS meter to better abide by IEEE Std. and counter numerical errors

3. Implemented logic for ride-through grid support functions using RSCAD's built-in library

4. Demonstrated ride-through and cease energization for zones UV1 and OV1