Focus Area: 1

FY23 TRL: 4

FY24 TRL: 4

FY24 Task Goals/Deliverables and status:

- Modelling

- Detector fabrication

- Electronics development

- (deliverable) Detector selection report

PROACTIVE GORs:

**Relevant FA1 topics**

- SNM absence

- Warhead confirmation

- Dismantlement

- (possible) Type identification

- HE absence

- Disposition confirmation

Use Case(s):

**Dismantlement confirmation**

- Confirm warhead presence before

- Confirm warhead absence after

- Confirm SNM separated from HE

**Template initialization**

- Confirm that initial item presented for template measurement is a warhead

**(possible) Type verification**

- Use SNM geometry in a warhead to identify type

**Integration Across PROACTIVE:**

Participation in venture experiments

Development of information-secure readout and analysis techniques

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525

**Technical Objectives**

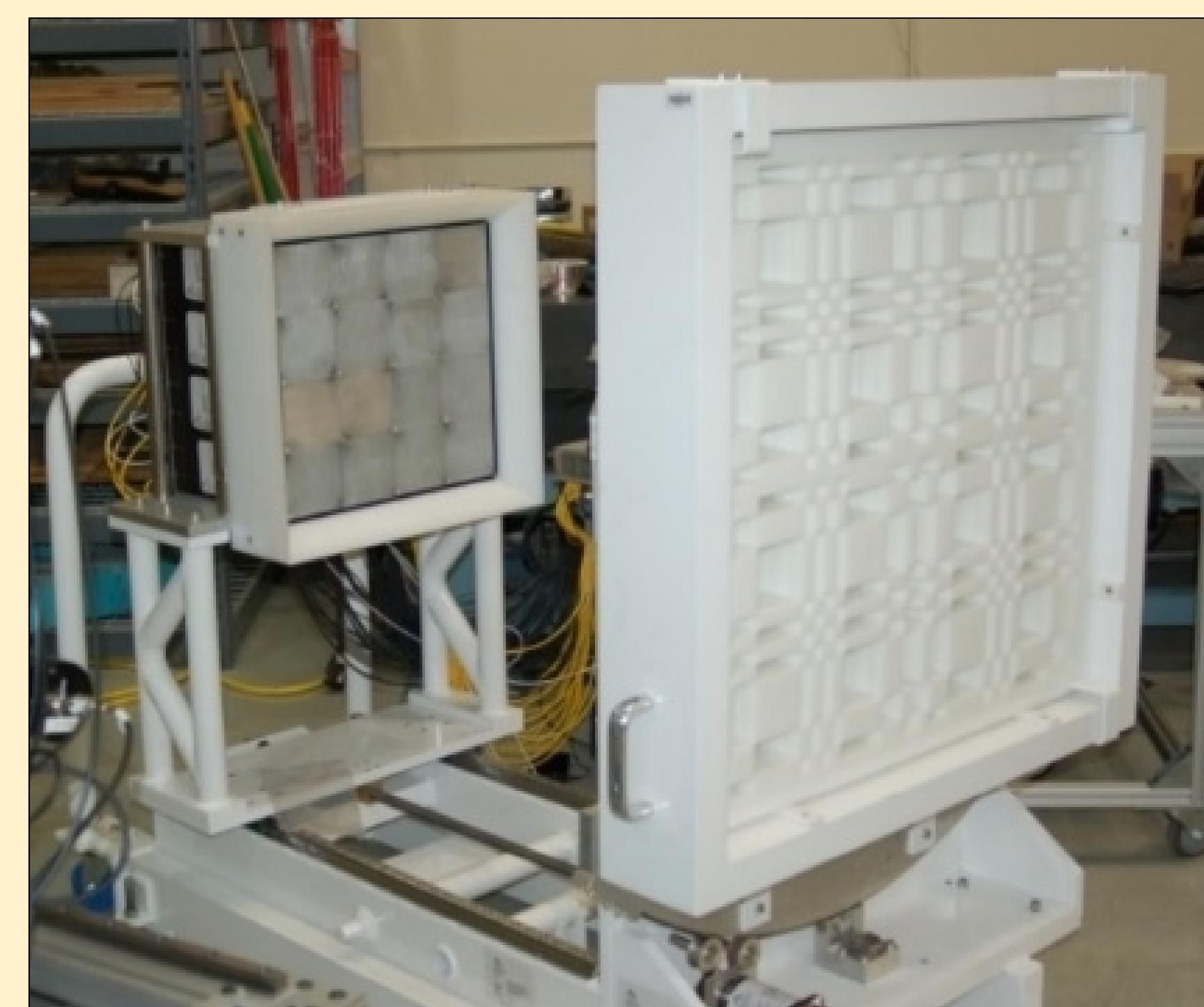

Design, fabricate, commission, and field a coded aperture neutron imager for use in an arms control context.

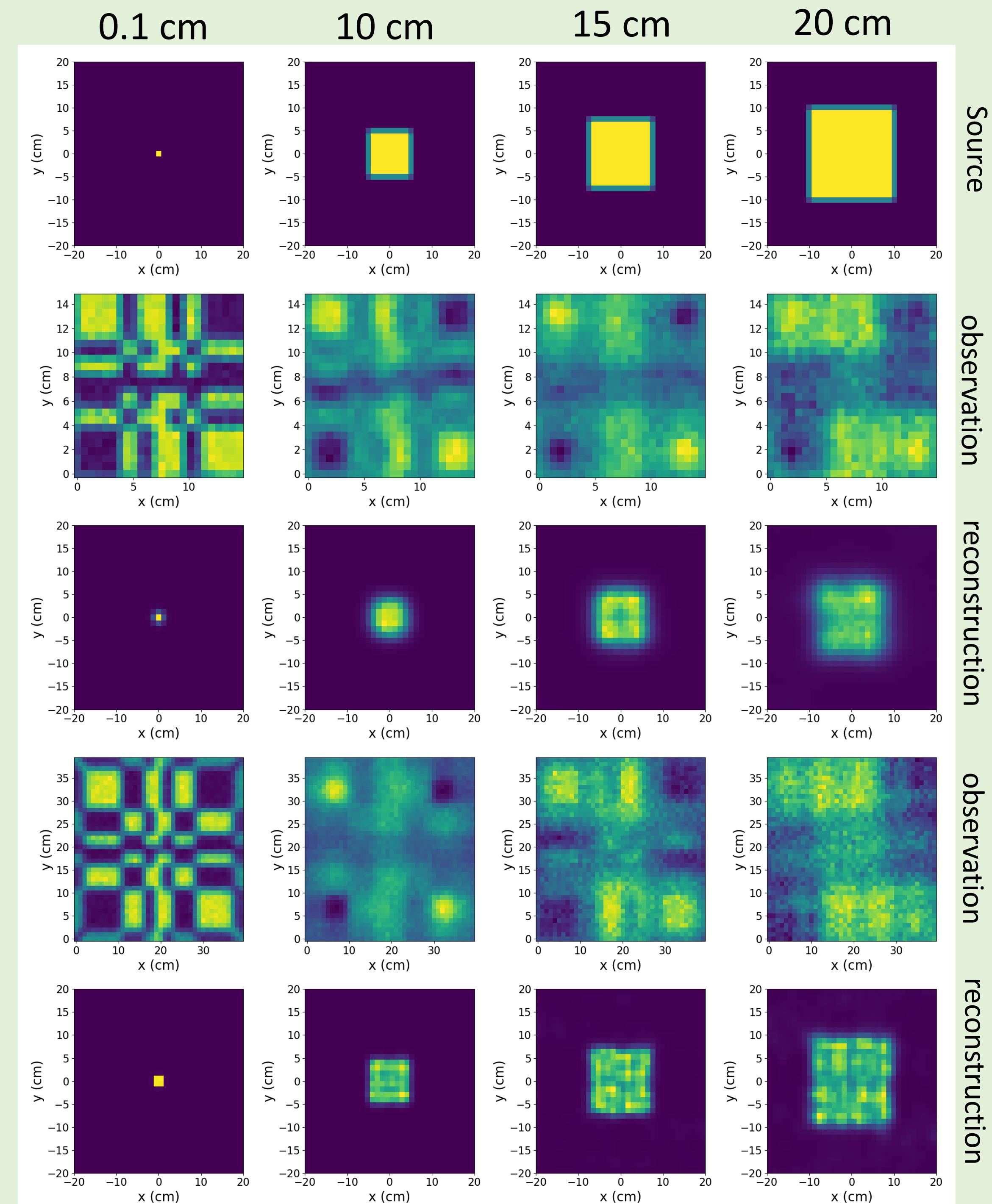

- Modelling to investigate use cases and information at risk

- Production of a 24x24 pixelated neutron detector based on organic glass scintillator and read out by SiPMs

- First-pass electronic readout for participation in venture experiments

- Second-pass electronic readout system for robust information protection

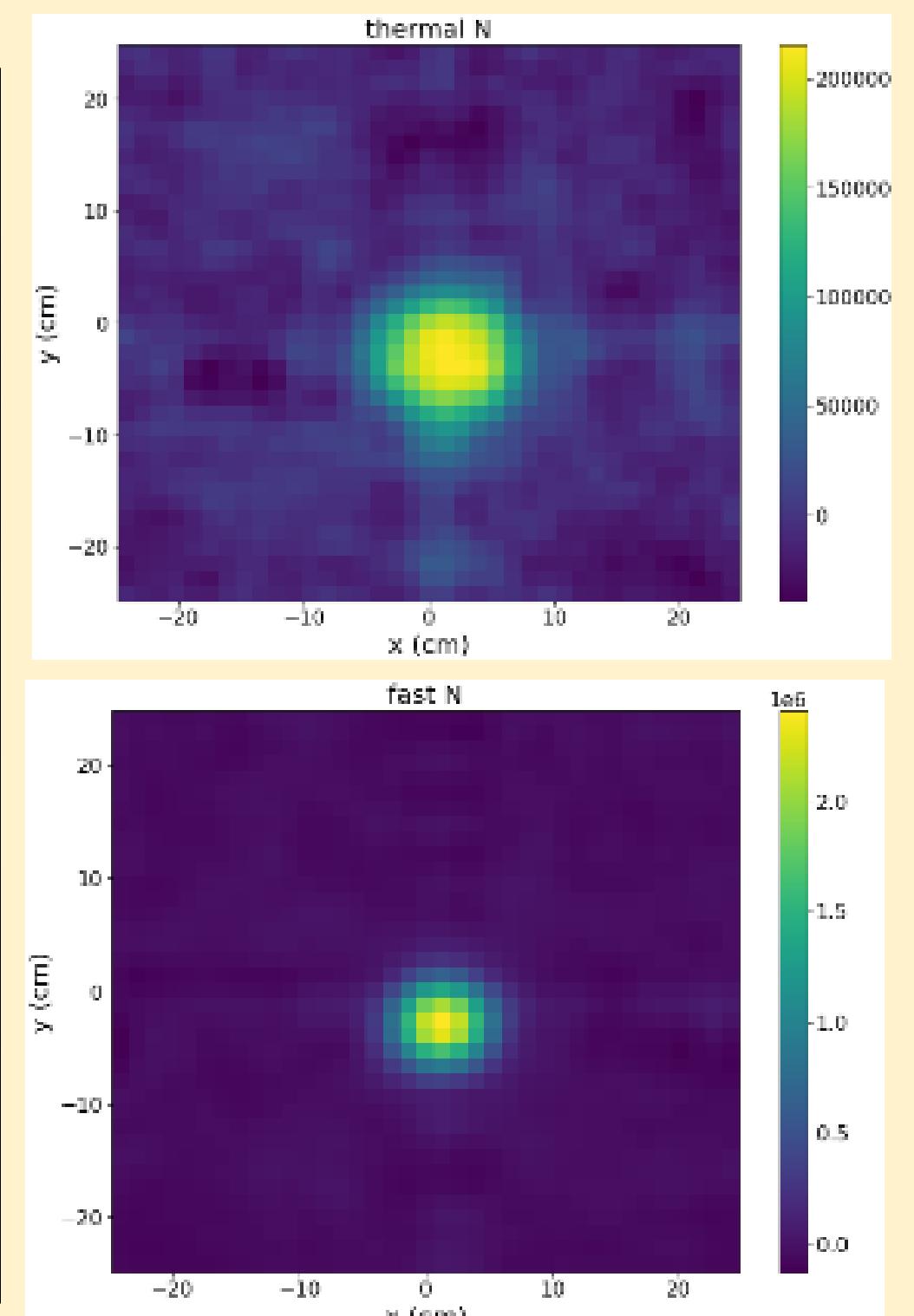

**Modelling**

- Mask based on rank 11 Modified Uniformly Redundant Array (MURA)

- Response map generated via ray-tracing and material dependent attenuation

- Image reconstruction via MLEM

**Scintillator**

- Selected organic glass scintillator (OGS) as fast neutron detector

- Mixed with PVT for subtractive processing

- OGS produced by Patrick Feng at SNL-CA

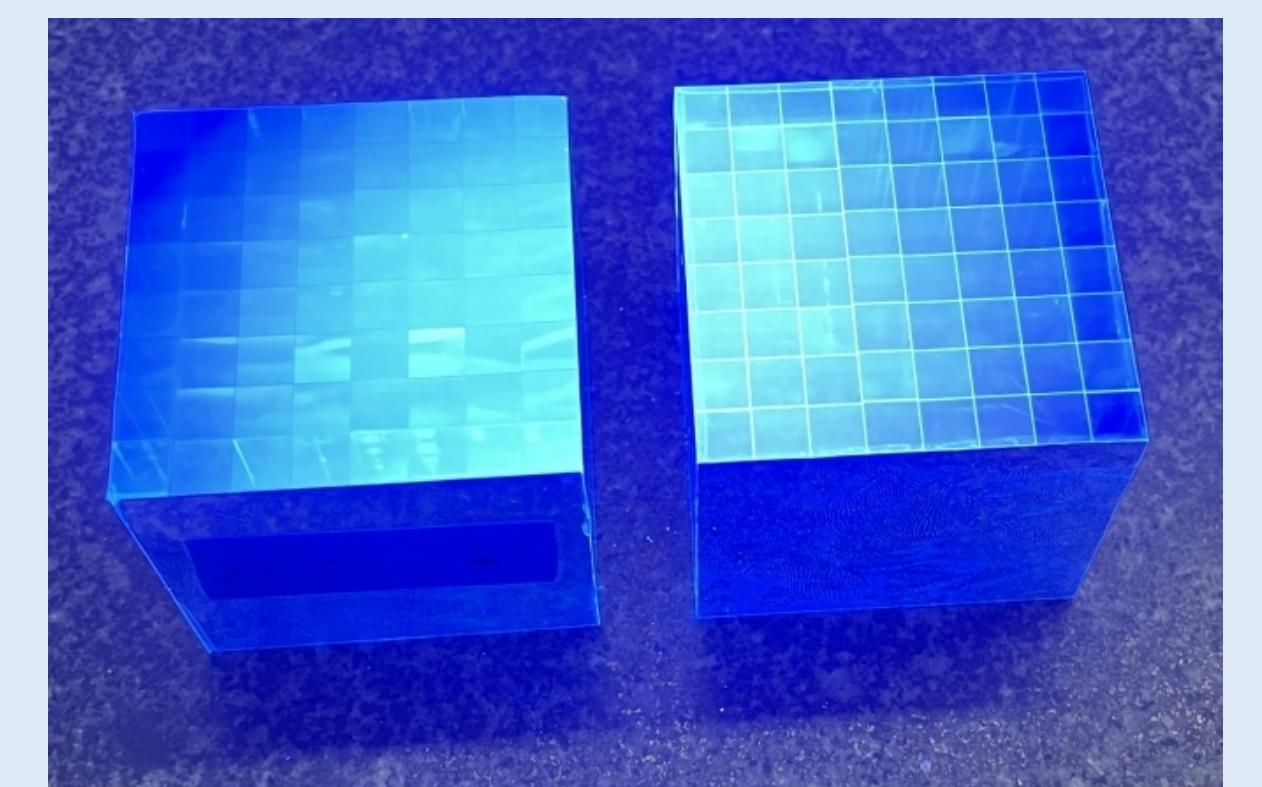

- 8x8 blocks fabricated at ORNL

- Pixels separated with aluminized ESR

- First test blocks with 50% OGS have been assembled

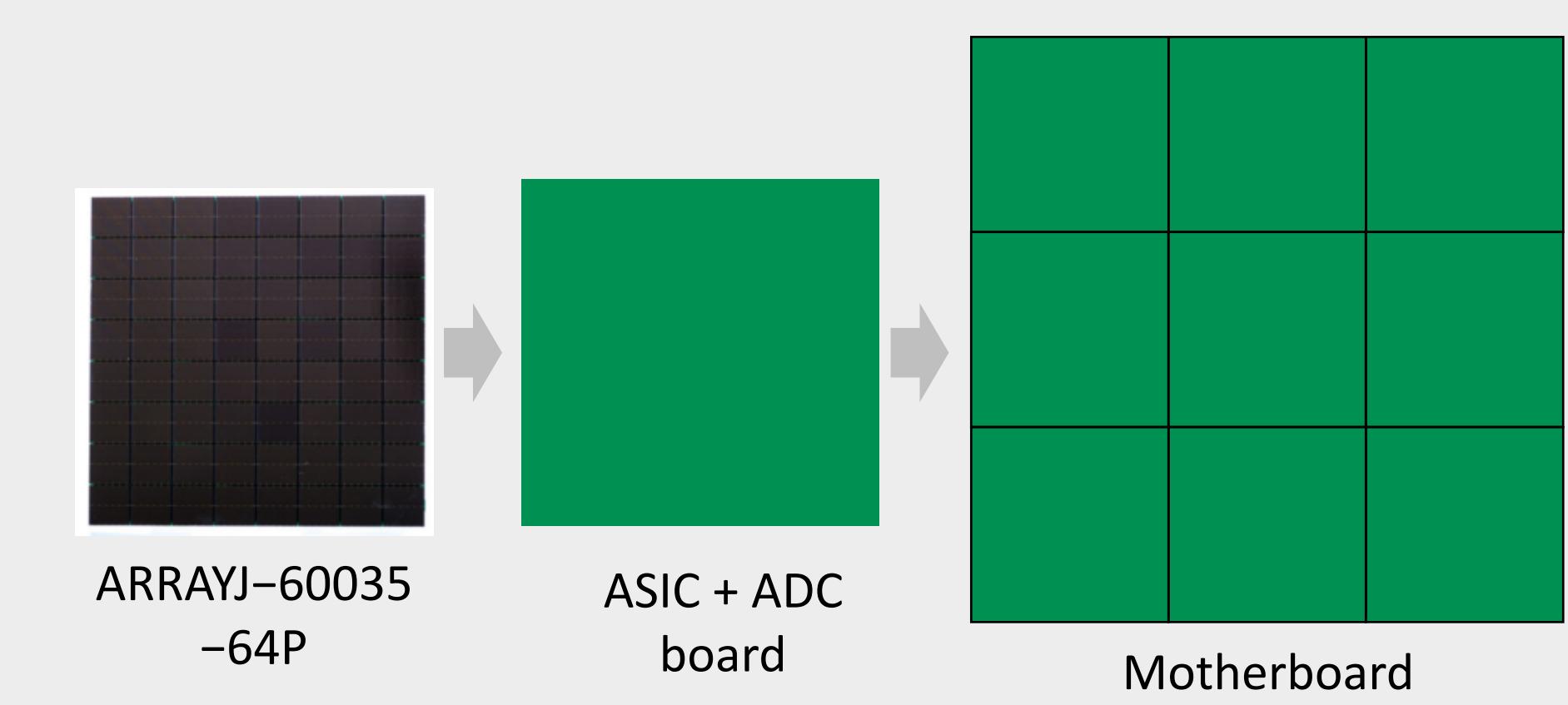

**Electronics**

- 3x3 grid of 64-pixel J-series SiPM arrays

- Read out via FMS1 PSD ASICs developed by DTRA

- Motherboard houses FPGA for ASIC readout