# Final Technical Report (FTR)

## Cover Page

|                                       |                                                                                                                                                                                                         |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>a. Federal Agency</i>              | Department of Energy                                                                                                                                                                                    |

| <i>b. Award Number</i>                | DE-EE0010239                                                                                                                                                                                            |

| <i>c. Project Title</i>               | Planar Transformer Systems for Modular Power Electronics in Long-Haul, Low-Cost PV Systems                                                                                                              |

| <i>d. Recipient Organization</i>      | Arizona State University                                                                                                                                                                                |

| <i>e. Project Period</i>              | <i>Start:</i> Oct. 1, 2022 <i>End:</i> March 31, 2024                                                                                                                                                   |

| <i>f. Principal Investigator (PI)</i> | Name: Mike K. Ranjram<br>Title: Assistant Professor<br>Email address: <a href="mailto:mike.ranjram@asu.edu">mike.ranjram@asu.edu</a><br>Phone number: (857) 445-6676                                    |

| <i>g. Business Contact (BC)</i>       | Name: Heather Clark<br>Title: Assistant VP – Research Operations<br>Email address: <a href="mailto:heather.christina.clark@asu.edu">heather.christina.clark@asu.edu</a><br>Phone number: (408) 965-1427 |

Myra

Signature of Certifying Official

2024.07.23

---

*Date*

*By signing this report, I certify to the best of my knowledge and belief that the report is true, complete, and accurate. I am aware that any false, fictitious, or fraudulent information, misrepresentations, half-truths, or the omission of any material fact, may subject me to criminal, civil or administrative penalties for fraud, false statements, false claims or otherwise. (U.S. Code Title 18, Section 1001, Section 287 and Title 31, Sections 3729-3730). I further understand and agree that the information contained in this report are material to Federal agency's funding decisions and I have any ongoing responsibility to promptly update the report within the time frames stated in the terms and conditions of the above referenced Award, to ensure that my responses remain accurate and complete.*

**Acknowledgement:** "This material is based upon work supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) Solar Energy Technologies Office (SETO) under the DE-FOA-0002606 Award Number DE-EE0010239.

**Disclaimer:** "This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof."

## Executive Summary

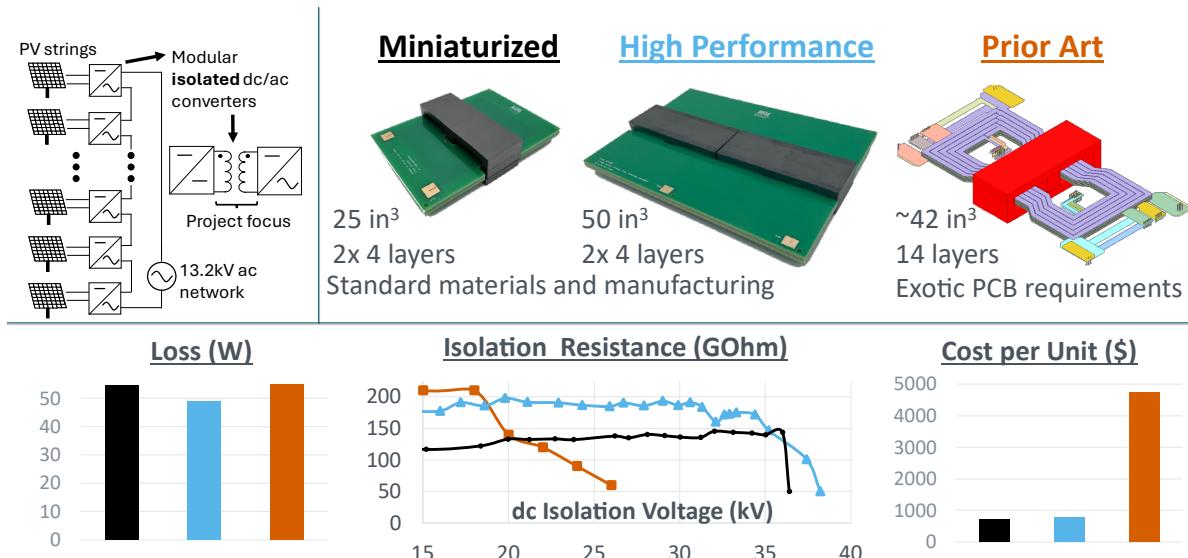

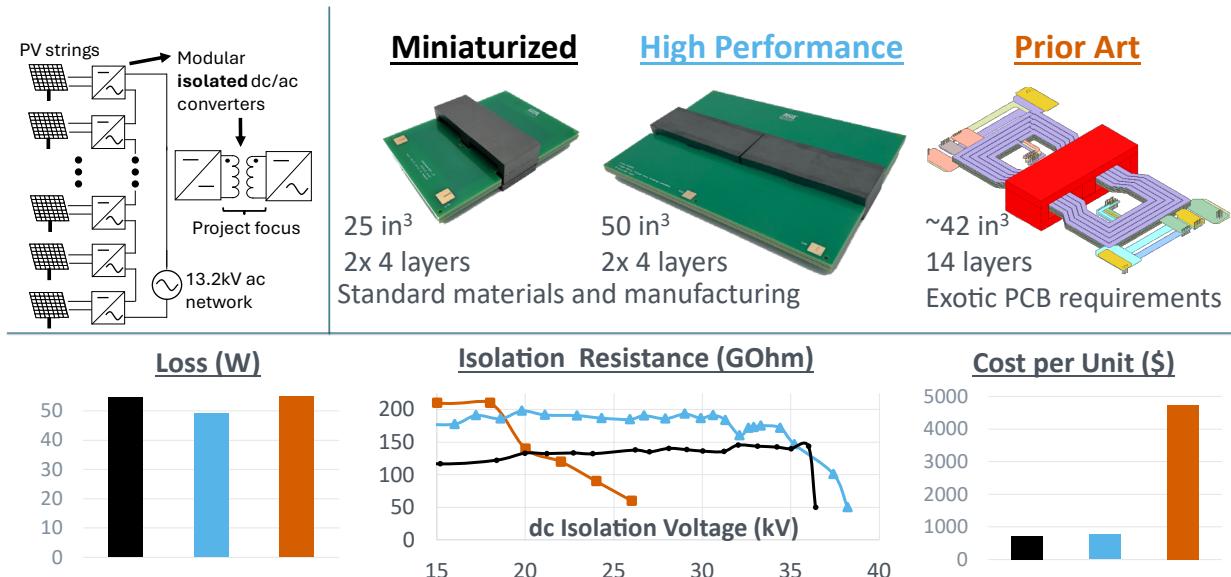

This project successfully developed and verified a new approach for medium voltage (MV) planar transformers for use in emerging, utility-scale, modular PV systems. This approach simplifies their manufacture, improves their isolation capability, lowers their cost, and reduces their volume and loss, while also creating flexibility in the materials that can be used. These key outcomes are summarized in the figure below.

In contrast to prior work, our approach targets the simplest possible winding arrangements in these transformers to minimize the number of MV isolation barriers. In other words, we prioritize meeting the critical isolation requirements of these systems. In so doing, we greatly expand the feasible PCB dielectrics and other insulation barrier concepts that can be considered for these systems, thereby mitigating sensitivity to supply chain changes in any particular material. This isolation barrier prioritization can be done without affecting a dramatic increase in copper loss compared to the prior art owing to an improved understanding developed in this project of the isolation design and spacing requirements of the windings and connecting vias in these transformers. We also show that multi-core design optimizations can employ series-connected transformers to trade-off core and copper losses to minimize overall losses.

In addition to a technology demonstration which verifies the proposed design approach, this project advances a PCB cost model for improved cost assessment of planar magnetic components which is especially relevant for LCOE-constrained solar PV systems. We also develop an automated core loss data collection testbed to accurately verify transformer losses. These cost and loss data comprise a design framework for planar transformers which elucidate trade-offs between efficiency, volume, and cost, and enable planar transformer designs for emerging utility-scale modular PV systems which produce best-in-class results in these three metrics. Such innovations are integral to developing the next generation of high-performance, low-cost utility-scale solar PV systems.

## Table of Contents

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| 1. Background .....                                                           | 5  |

| 1.1 Utility-scale PV Systems and Their Isolation Transformers .....           | 5  |

| 1.2 Medium-Voltage Planar Transformers and Limitations of the Prior Art ..... | 6  |

| 1.3 Planar Transformer Costs .....                                            | 8  |

| 1.4 Assessing Magnetic Core Loss .....                                        | 9  |

| 2. Project Objectives .....                                                   | 10 |

| 2.1 Project Goals and Outcomes .....                                          | 10 |

| 2.2 Significance, Innovation, and Fundamental Advancements .....              | 11 |

| 2.3 Summary of SOPO Tasks .....                                               | 11 |

| 3. Project Results and Discussion .....                                       | 14 |

| 3.1 Achievement of Milestones, Deliverables and Metrics .....                 | 14 |

| 4. Significant Accomplishments and Conclusions .....                          | 29 |

| 5. Path Forward .....                                                         | 30 |

| 6. Products .....                                                             | 31 |

| 7. Project Team and Roles .....                                               | 32 |

| 8. References .....                                                           | 32 |

## 1. Background

The aim of this project is to develop and verify a new approach to designing medium-voltage (MV) planar transformers for emerging, utility-scale, modular PV systems. This approach considers these MV planar transformers as *systems* rather than as *components*. This means they can comprise multiple individual magnetic cores and printed circuit boards (PCBs) which can be distinctly organized both electrically and physically to achieve maximum performance. Central to this approach is that low-complexity winding stack-ups are leveraged which simplify primary-to-secondary insulation requirements, mitigate the need for interleaved windings, and aid in streamlining manufacturing and greatly reducing cost. Additionally, these systems dramatically expand the available material choices for the PCB by significantly reducing their required dielectric strength. This is a key driver of low-cost PCBs and mitigates sensitivity to supply chain changes in any particular material.

The three key aspects of a medium voltage planar transformer in a solar PV application are its: (1) isolation capability, (2) cost, and (3) loss. This project comprehensively explores each of these three facets and we ultimately advance planar transformers having higher isolation capability, much lower cost, and lower loss than the state-of-the-art, at a comparable and lower volume. In this section, we provide background on each of these three key facets of the design.

### 1.1 Utility-scale PV Systems and Their Isolation Transformers

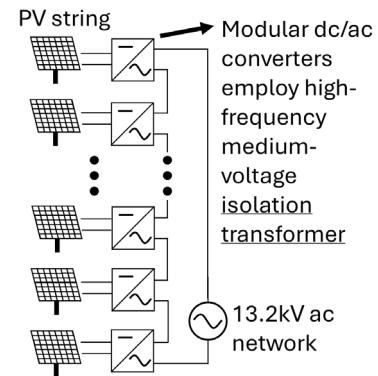

Modular isolated power converters are attractive solutions due to their flexibility, scalability, efficiency, and ease of maintenance making them well-suited for a wide range of applications- including utility-scale renewable energy systems, industrial power supplies, and electric vehicles. This project focuses on utility-scale PV systems and the modular string inverter architecture shown in Fig. 1 in which multiple isolated dc/ac inverters are connected in a series-output configuration. The inputs of these inverters each connect to a PV string. The outputs are connected in series such that they directly synthesize a 60Hz MV (e.g., 13.2kV line-to-line). These systems dramatically reduce balance of system costs (and correspondingly LCOE) via simpler maintenance, heightened reliability, increased efficiency, and economical wiring [1].

Today's utility-scale PV systems often employ string inverters which similarly interface to a set of PV strings at their input, but output an ac voltage around  $800\text{V}_{\text{ac}}$  [2]. This value is limited by the voltage blocking capability of today's high-performance semiconductors. Thus, a bulky and expensive 60Hz transformer is employed in these systems to provide isolation and to step up this voltage to MV for interfacing with the local distribution system. A highly attractive feature of modular architectures is that this bulky transformer is replaced by a miniaturized transformer within each isolated power converter module. This transformer experiences much higher frequencies within the power converter (e.g., in this project, 200kHz is the target) and this is a substantial driver of miniaturization as it enables much lower flux densities within the magnetic core of the transformer, and enables the use of high-

**Figure 1.** Multiple-input, series-output utility-scale PV conversion architecture. Two additional identical structures would implement the additional ac voltage phases in a three-phase system.

performance, low-loss MnZn ferrites. A further advantage in the architecture in Fig. 1 is that each transformer can be designed for a simple 1:1 conversion ratio since the MV is derived from series-stacking the converter modules. Each transformer in the converter modules only needs to provide isolation, with no voltage gain, which greatly simplifies their design. In the example traditional system, the transformer provides isolation and a voltage gain of  $\sim 60x$ .

Fundamental to these systems and gains is that the commonly employed grid-interfaced MV transformer is replaced with high-frequency miniaturized MV transformers in each module. However, transformers are inherently difficult to miniaturize owing to fundamental scaling constraints [3], and they bottleneck the power processing capability, size, and efficiency of proposed modular solutions. It is imperative that as cutting-edge modular architectures are proposed and developed, the low-cost, simple-to-manufacture, and high-performance magnetics required to enable them are advanced in kind.

## 1.2 Medium-Voltage Planar Transformers and Limitations of the Prior Art

Planar magnetics are inductors and transformers with windings that are implemented directly on printed circuit boards (PCBs). They represent an active area of research in high performance and miniaturized power conversion, owing to numerous advantages such as high repeatability, simplicity for manufacture, and improved thermals [4]. This technology has enabled strong improvements in power conversion applications with low isolation voltage requirements [1], [4], [5], but these benefits have not yet been realized in applications requiring medium voltage isolation.

To date, virtually all MV high-frequency transformers employ wire-wound constructions. These are much more expensive and complicated to manufacture than planar constructions, typically employing Litz wire and requiring bobbins and coil formers in their construction [6] and manufacture. However, they also greatly simplify meeting insulation requirements since the entire construction is controlled. In being much simpler to manufacture, planar transformers are also much more restrictive. The planar transformer design approach proposed in this project is foundational to maximally leveraging this technology in this and other MV applications (such as electric vehicle charging stations), and creates a basis to fundamentally consider the transformer bottleneck in ideating future low-cost, miniaturized modular MV architectures.

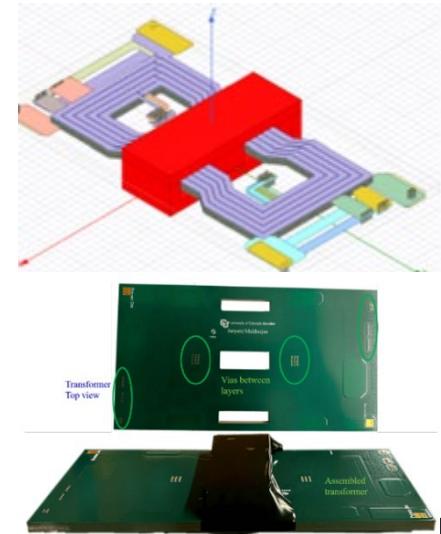

One previous study has explored fully-PCB-based MV planar transformers [7]. In that work, the authors developed a transformer for the converter architecture in Fig. 1 with transformer ratings of 1kV:1kV, 7.5kW, 200kHz switching frequency under dual active bridge-type (DAB) excitations. This work achieved a dc isolation capability of 26kV for a 13.2kVac grid interface application, lower than the designed expectation of 35kV. Their design is shown in Fig. 2 and employs interleaved, 12-layer windings (although the PCB comprises 14 layers, as discussed in Section 2). Interleaving refers to a transformer construction in which the turns of the primary and secondary windings

Figure 2. Illustration of planar transformer and corresponding hardware prototype from prior work [6].

are arranged in an alternating pattern in the PCB stack-up (e.g., in a four-layer board, fully interleaved windings would be arranged as layer 1: primary, layer 2: secondary, layer 3: primary, layer 4: secondary). Doing this can reduce the ac resistance associated with high layer counts [8]. However, a 12-layer interleaved winding arrangement imposes 11 isolation barriers between the windings and forces the use of an uncommon very-high-breakdown-voltage (276kV/mm) polyimide film dielectric (RF775) in the PCB, which dramatically increases its cost and compromises manufacturability.

Through our project, we identified three discrepancies with the approach in prior art, which we include here as background as it is the best place to contextualize prior work. However, we emphasize that these represent key findings of this project and they are addressed again in Sections 3 and 4.

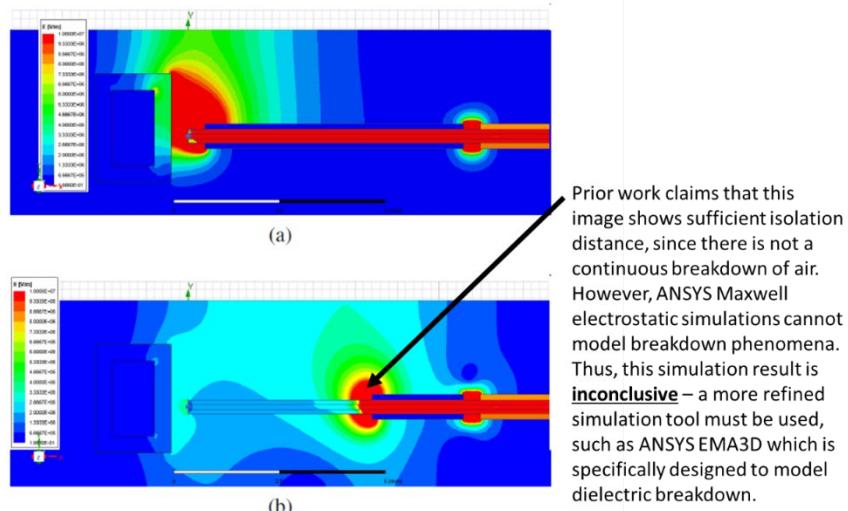

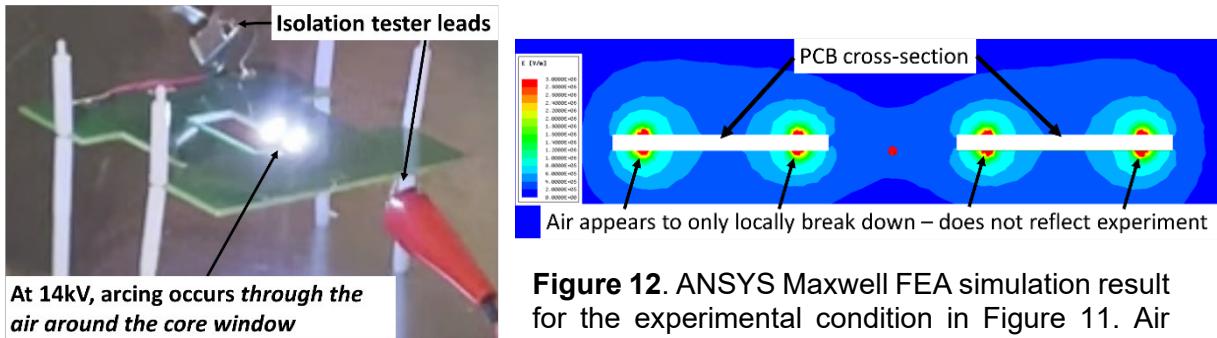

First, the prior approach uses ANSYS Electrostatic simulations to design the transformer's insulation. The difficulty is that this software cannot simulate dielectric breakdown, and so its results are ambiguous if the simulated electric field strength exceeds the dielectric's rating. In [7], and reproduced in Fig. 3, an ANSYS electrostatic simulation result is interpreted as verifying a safe isolation distance because full breakdown of the air is not observed. However, the 3kV/mm dielectric rating of dry air at standard temperature and pressure is exceeded around the windings, and so this results in simulation ambiguity. An example simulation tool that can model dielectric breakdown is ANSYS EMA3D Charge Plus.

Figure 3: 2D field simulations showing fringing electric fields for (a) windings 1.2 mm away from the core and (b) windings 5.2 mm away from the core for a potential difference of 20 kV between two layers.

**Figure 3.** Figure from prior work [7] suggesting how ANSYS electrostatic simulations can be used to design the isolation spacing between windings and the transformer core. In this project, we show that this is an inappropriate use of this software owing to its inability to propagate the effects of dielectric breakdown. The true results of this simulation are ambiguous, and our in-lab tests confirm breakdown through the air in this arrangement closer to 14kV rather than better than 20kV.

Second, the prior design employs through-hole vias to connect its interleaved winding layers, as seen in Fig. 2. This is a key trade-off of interleaved windings: since the windings are interlaced, interconnecting the turns on the different layers becomes more difficult (these vertical connections must not connect to the turns of the other winding). In

the prior design, significant volume is devoted to isolation spacing between the through-hole vias and the windings and this also dramatically increases the winding length of each turn. This large spacing is designed assuming dry air separates the windings from the vias, but the inner layers of the PCB are surrounded by the high-dielectric-strength PCB dielectric and so this large spacing is unnecessary. Furthermore, our simulations of this design indicate that the top and bottom winding layers *cannot* be exposed to air owing to breakdown conditions occurring between the turns on these layers. This means that the top and bottom layers must also be enveloped by an insulator. Notably, this additional insulation requirement is implied but not explicitly discussed by the prior work -- the fabricated design, shown in Fig. 2 includes additional top and bottom PCB dielectric layers encapsulating the identified 12 winding layers. This effectively results in a 14-layer board with 12 “inner” winding layers. Given that all the winding layers are actually enveloped by PCB dielectric, the detrimental spacing requirement imposed by the prior design is unnecessary.

Finally, the prior design encapsulates the transformer core in a high insulation epoxy material to prevent dielectric breakdown between the windings and the core. However, because the windings *must* be fully encapsulated by PCB dielectric, the only remaining breakdown path through air is between the through-hole vias and the core. This suggests that a small amount of epoxy can be used to insulate the vias, rather than a large amount of epoxy being used to insulate the core, greatly simplifying manufacture.

In this project, the focus is on employing non-interleaved windings to greatly simplify the isolation design, which represents the biggest burden on the design of these transformers. We reduce the number of winding layers from 12 to 4 to minimize the number of isolation barriers and minimize the ac resistance penalty of non-interleaved windings, and we maintain a similar copper loss owing to the elimination of the winding excursion in the prior design. Furthermore, the planar transformer system concept allows a fine-tuned trade-off between core loss and copper loss and can further help to minimize the copper loss penalty in a non-interleaved design.

Our original vision was to employ a single four-layer PCB for both the primary and secondary windings, with blind vias interfacing L1-L2 and L3-L4. However, the discovery of the need for winding encapsulation changed this to a focus on each winding being implemented by its own PCB with encapsulation. We determined the best solution to be a 4-layer board where only the two inner layers are used, rather than seeking encapsulation with an alternative material (such as insulating epoxy). Our approach to targeting the most insulation-favorable designs resulted in demonstrating planar transformers having a fraction of the cost, tremendous flexibility in dielectric material selection, lower loss, and lower volume than the prior art, while achieving 1.5x higher isolation capability.

### 1.3 Planar Transformer Costs<sup>1</sup>

A widely touted feature of planar magnetics is their cost savings compared to wire-wound alternatives. This benefit is typically assessed qualitatively, for example, by noting the simpler manufacturing of printing the windings and slotting in a planar core compared to using a coil former to wind turns on a bobbin, mounting that bobbin on a core, and then installing the magnetic unit onto a PCB. Similarly, the cost impact of certain planar design

---

<sup>1</sup> This section includes direct excerpts from the introduction of the paper we published on this topic [9].

choices, such as the number of layers, is also typically assessed qualitatively (e.g., by the reasonable assumption that a board with fewer layers will be less costly [5], [10], [11] or that some designs are complex to fabricate than others [12]). Cost is an important metric in the trade-offs of considering a planar magnetic design. While the quotation from PCB manufacturers determines specific final costs, the ability to understand cost trends and estimate cost impacts in a planar magnetic design is useful.

In utility-scale solar PV applications, planar transformer cost estimates are necessary to compute the levelized cost of electricity (LCOE) and is thus fundamental to assessing the benefit of a new approach. However, because the literature does not contain a clear assessment of planar magnetic costs, existing LCOE optimizations have relied on conventional volume-scaled cost models which are poorly suited for planar magnetics [7]. Furthermore, the work in [7] has identified the transformer cost as critically impacting LCOE, emphasizing the importance of being able to identify it accurately.

Typical wire-wound magnetic components have costs that scale reasonably with volume since the primary materials that comprise the component, such as silicon steel and copper in a power transformer, are priced by weight (and by proxy, volume)<sup>2</sup>. In contrast, two planar magnetic components having similar volumes may have dramatically different costs, depending on the details and complexity of their manufacturing requirements.

The literature on cost considerations in planar magnetics is sparse. The most relevant study is in [13] which formulates a cost-benefit analysis comparison between a planar and conventional transformer for a specific 100kHz power supply. However, this study does not provide a basis to compare two different planar magnetic components, and it does not consider constructions wound directly on a PCB (instead, it considers the historically more common implementation of planar magnetics in which the windings are implemented by multiple separate PCBs)<sup>3</sup>. Similarly, [14] offers a clear description of the process by which a manufacturer develops a PCB cost quote but does not offer quantitative insight into modern cost trends for planar magnetic windings.

In this project, we clarify and quantify the key factors affecting the cost of planar magnetic windings to enable their cost-informed design. In doing so, we acknowledge that assessments of cost can be tenuous, as it is inherently affected by a multitude of economic factors which are difficult to control, including the local cost of labor, the impact of economies of scale, purchasing power of an entity (e.g., of an academic laboratory versus a multinational corporation), and the current state of the relevant supply chains. However, a clear, well-justified assessment of the relative cost impacts is a useful tool for researchers and designers who are exploring new planar magnetic architectures and configurations or who wish to leverage these components in cost-constrained systems. Our intent is not to provide exact price models for planar magnetics but to create a model allowing cost to *inform* their design and compare between designs.

#### 1.4 Assessing Magnetic Core Loss

Transformers have two loss mechanisms: conduction loss in the windings (called “copper loss”) and losses in the magnetic core (called “core loss”). The former is

---

<sup>2</sup> Modifications to cost owing to specialized windings (e.g., Litz wire) or insulation materials can also be readily estimated from manufacturer catalogues.

<sup>3</sup> Importantly, this study also indicates that the planar magnetic winding cost can be dominant, further emphasizing the importance of modeling it well.

straightforward to assess from small-signal measurements and can be extracted from standard in-lab equipment, such as an impedance analyzer. The latter cannot be extracted from a small-signal measurement. To support the optimized design of planar transformers, especially for the planar transformer systems explored in this work which involve a careful trade-off between core loss and copper loss, we developed an in-house core loss tester. This tester generates square wave voltages which drive flux densities that are representative of their true deployment in a dual-active-bridge-style converter.

During our testing, we automated this tester. This was both convenient but also critical for ensuring repeatable measurements. We used this automated tester to report the core loss of our developed transformer and confirm the accuracy of our loss modeling. We also validated it against the MagNet dataset, which is the first open-source large-scale core loss dataset [15]. In performing this validation, we recognized a challenge: this representative dataset was originated by one research group on one experimental test bed, and there are inherent errors associated with this testbed which are likely to be different from the data produced by our testbed. Thus, we proposed simple error characterization methods for new contributions to these kinds of datasets, and to better contextualize errors between our data and the MagNet dataset.

## 2. Project Objectives

Numerous recent SETO-supported projects target modular conversion for utility-scale PV as a pathway towards industry and SETO goals of higher reliability, repairability, and efficiency to enable long-haul systems that meet SETO's LCOE target of \$0.02/kWh by 2030 [1], [16]. This project greatly improves the ability for this suite of emerging converter concepts to meet these goals as it targets cost-optimized, high-isolation-strength, low-loss design of the high-frequency transformer they ubiquitously require. Thus, it greatly strengthens LCOE gains of these architectures while also simplifying their manufacture. The proposed framework can also be directly employed within existing foundational efforts to optimize the LCOE of modular PV systems [17].

### 2.1 Project Goals and Outcomes

The overall objective of this project is to develop and experimentally demonstrate a framework for designing these planar transformer systems to elucidate trade-offs between efficiency, volume, and cost, and to enable planar transformer designs for emerging utility-scale modular PV systems which produce best-in-class results in these three metrics while supporting MV isolation requirements.

The project goal was that a planar transformer would be demonstrated with a loss less than 55W (i.e., lower than the state-of-the-art [7]) and/or a volume better than 30in<sup>3</sup> (i.e., much lower than the state-of-the-art at ~42in<sup>3</sup> box volume) while having lower cost than a 12-layer board using Panasonic Felios RF775 dielectric and using industry-standard PCB construction materials and layer counts to yield significant cost reductions. This last metric, developed at the start of the project, did not account for the prior art's true deployment as a 14-layer board as discussed in Section 1.2. A demonstrated isolation voltage better than 26kV was targeted to meet or exceed the isolation capability of the prior art.

It is important to note that no standard yet exists which defines the isolation requirement of transformers embedded in power electronics. Recognizing this, PI Ranjram joined the P3105 IEEE working group which is developing recommendations for

such standards. In the absence of a standard, the focus in this project is an isolation metric relative to the prior work (>26kV).

## 2.2 Significance, Innovation, and Fundamental Advancements

This project pursued six technology innovations to achieve the project goal:

1. Develop non-interleaved low-layer-count PCB planar transformers to reduce the number of MV isolation barriers to one, dramatically reducing the dielectric strength requirement of this barrier compared to prior art, and greatly expanding the possible PCB materials that can be used for MV isolation applications.

2. Advance the implementation of these transformers as systems which comprise multiple series connections of transformers to optimize the trade-off between core loss and copper loss.

3. Develop a design framework to design these planar transformer systems to minimize their loss within a desired box volume.

4. Develop a planar magnetic winding cost model which captures the impacts of PCB complexity to replace previously proposed volume-scaled approaches.

5. Develop a square-wave core loss tester to accurately characterize the core loss of the developed transformers, and to verify the core loss estimation.

6. Establish high voltage isolation test capability to experimentally validate the isolation voltages of the developed transformers.

7. Correct the design discrepancies in designing the MV isolation barrier proposed in prior art.

## 2.3 Summary of SOPO Tasks

The technical tasks of this project were partitioned into five categories:

1. **PCB manufacturer cost surveying** (explicitly via direct correspondence and implicitly via quotation of exemplar transformers) and the **development of an empirical cost model** (in contrast to the state-of-the-art, which assumes linear scaling of cost with overall volume and does not account for pricing effects of non-standard dielectrics or board complexity).

2. **Design framework scope reduction** via evaluation of material availability, grounding requirements, creepage/clearance distances, transformer excitation type, and viable transformer system configurations.

3. **Design framework development and verification**, which employs simple loss models (Dowell's equation for copper loss [18] and the improved General Steinmetz Equation for core loss [19]). An output produced by this framework is compared to Finite Element Analysis simulations to ensure sufficient matching in predicted and simulated loss and insulation capability.

4. **Experimental development and measurement** of at least three planar transformer systems produced by the design framework. This includes the in-house development of a core loss tester capable of square-wave excitations reflecting the transformer excitation type, resistance measurements to characterize the conduction loss characteristics, and hi-pot dc isolation testing of the fabricated systems.

5. **Knowledge transfer** of the innovations gained in the project.

The specific SOPO subtasks are specified in the table below, including their end of project status. Highlighted tasks in this table correspond to milestones. There were no Go/No-Go decision points. All tasks were successfully completed, with augmentations occurring during the project to 2.7, 3.1, and 5.4 as discussed below.

| Task Number |                                                                                                               | Comment                                                                                                                                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 1.1: Obtain PCB cost data                                                                                     | Complete.                                                                                                                                                                                                                                                                            |

|             | 1.2: Develop empirical cost model                                                                             |                                                                                                                                                                                                                                                                                      |

| 2           | 2.1: Select representative ferrite core material and coreset options                                          | Complete.                                                                                                                                                                                                                                                                            |

|             | 2.2: Evaluate transformer core grounding requirements and corresponding insulating potting options            | Complete.                                                                                                                                                                                                                                                                            |

|             | 2.3: Perform electrostatic FEA to determine transformer creepage and clearance to meet isolation requirements | Complete. This task was planned according to the design procedure in the prior art. It was determined during the project that this approach was not viable, and this was confirmed in subtask 2.7.                                                                                   |

|             | 2.4: Down-select transformer excitation type                                                                  | Complete.                                                                                                                                                                                                                                                                            |

|             | 2.5: Down-select viable planar transformer configurations                                                     | Complete.                                                                                                                                                                                                                                                                            |

|             | 2.6: Create a report on the down-selection process                                                            | Complete. EOP Deliverable.                                                                                                                                                                                                                                                           |

| 3           | 2.7: Isolation measurement of exemplar transformers                                                           | Complete. This was an additional task added after Q1 of the project. Once we discovered the design inconsistencies in the prior art, we pivoted to an “experiment-in-the-loop” design approach.                                                                                      |

|             | 3.1: Merge developed cost model with existing simplified transformer loss models                              | Augmented. The loss and cost model frameworks were both successfully developed. It was decided to keep them as separate tools rather than merge them as the planar winding cost model can be used in many other applications. The developed instructions are sufficient to use both. |

| 4           | 3.2: Verify a design output by the model in FEA simulation                                                    | Complete.                                                                                                                                                                                                                                                                            |

|             | 4.1: Design the core-loss tester circuit and verify in simulation                                             | Complete.                                                                                                                                                                                                                                                                            |

|             | 4.2: Fabricate and verify operation of the developed core loss circuit                                        | Complete.                                                                                                                                                                                                                                                                            |

|   |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <b>4.3: Experimental confirmation of core loss tester accuracy</b>                                   | Complete.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | <b>4.4: Fabricate planar transformer systems</b>                                                     | Complete.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | <b>4.5: Obtain core loss, resistance measurements, and insulation results of transformer systems</b> | Complete.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | <b>5.1: Research dissemination</b>                                                                   | Complete and in progress. One published peer reviewed conference paper, and two more peer reviewed conference papers accepted. Plans to submit journal manuscripts post EOP.                                                                                                                                                                                                                                                         |

|   | <b>5.2: Lecture development</b>                                                                      | Complete. EOP deliverable.                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | <b>5.3: Framework dissemination</b>                                                                  | Augmented. We have drafted detailed instructional documents in lieu of companion videos. EOP deliverable.                                                                                                                                                                                                                                                                                                                            |

|   | <b>5.4: Industry feedback</b>                                                                        | Augmented. PI Ranjram joined the IEEE P3105 working group, which kicked-off during this project. This group is drafting recommendations for a future standard on the isolation requirements of grid-connected power electronic converters with embedded high frequency isolation transformers. This participation established two final gaps towards the commercial deployment of our planar transformers as discussed in Section 5. |

### 3. Project Results and Discussion

All project milestones were achieved. We demonstrated medium voltage planar transformers with 1.5x greater isolation capability, >4x lower cost, and both lower volume and lower loss compared to the state of the art. Fig.4 summarizes the high-level achievement of the project.

**Figure 4.** High-level summary of the project's achievement. The planar transformers developed in this project are smaller, lower loss, have higher isolation capability, and have much lower cost than the prior art.

#### 3.1 Achievement of Milestones, Deliverables and Metrics

The project tasks, subtasks and milestones are summarized in Section 2.3. First, we describe the specific achievement of the milestones and their metrics. Then, we address the deliverables.

##### Milestone 1.1.1

This milestone relates to the successful completion of Task 1.1 in which representative PCB cost data is collected to develop the cost model. The performance metric, success value, assessment, and verification process are summarized in the table below.

| Performance Metric                                           | Success Value                                                                                        | Assessment Tool / Method of Measuring Success Value                                        | Verification Process              |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------|

| PCB manufacturer responses AND planar transformer quotations | Similar cost estimates in responses from two PCB manufacturers AND >13 planar transformer quotations | Cost estimates within 20% from two manufacturers.<br>AND<br>Number of quotations obtained. | Verification of responses by DOE. |

A cost survey was prepared and sent out to 18 US PCB manufacturing houses to obtain explicit responses on cost impacts of key PCB design choices. Five detailed responses

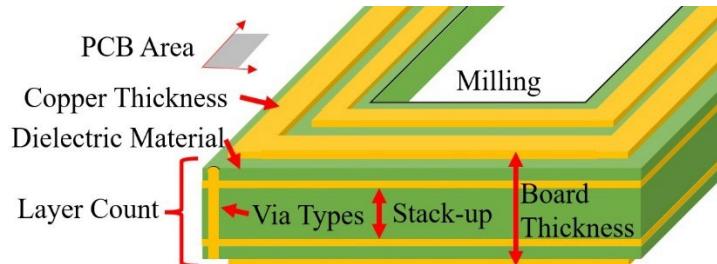

were received, as well as three more general ones. The cost-impact estimates provided in these responses were within 20% across more than two manufacturers, meeting the first requirement of milestone 1.1.1. These qualitative cost impacts are summarized in the table below, with Fig. 5 showing how these parameters relate to planar PCB windings.

| Feature                      | % increase in cost                                           | Connection to planar winding design                                                                    |

|------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Layer count                  | 35-40% for every additional layer pair (e.g., 4 to 6 layers) | Key driver of copper loss – affects the number of turns per layer, ability to interleave               |

| Via configuration            | 20-30% increase for every additional via set                 | Strongly related to layer count and interleaving structure                                             |

| PCB area                     | Scales with number of panels used (100% cost increase)       | Board area is defined by the planar magnetic footprint                                                 |

| Copper thickness             | 10-20% for increasing from 1oz to 2oz                        | Related to winding loss                                                                                |

| Board thickness and stack-up | Non-standard stack-ups cost more, too variable to generalize | Typically specified to achieve a certain isolation requirement or to control interwinding capacitances |

| Dielectric material          | 10-60% depending on the material                             | Related to isolation requirements, loss, and board thickness                                           |

| Board milling                | 0%                                                           | Related to core shape and isolation requirements. Stated to weakly affect cost.                        |

**Figure 5.** Key planar magnetic winding features are considered in the cost assessment.

The second performance metric was also met, with 81 PCB quotations obtained for 10 exemplar designs. These data are summarized in Fig. 6.

| Design | PCB dim.   | Spacing                        | Man. 1 [Q: \$ cost]       | Man. 2 [Q: \$ cost]        | Man. 3 [Q: \$ cost]       | Man. 4 [Q: \$ cost]                 |

|--------|------------|--------------------------------|---------------------------|----------------------------|---------------------------|-------------------------------------|

| 1      | 4.57x5.01" | L2-L3:<br>52 mils              | 5: 4,112.9<br>20: 4,714.6 | 10: 4,127.3<br>50: 6,387.5 | 5: 1,135.0<br>20: 2,207.6 | 10: 1,582.0<br>50: 3,573.5          |

| 2      |            | L2-L3:<br>70 mils              | 5: 4,112.9<br>20: 4,714.6 | 10: 4,127.3<br>50: 6,387.5 | 5: 1,145.0<br>20: 2,237.6 | 10: 1,595.0<br>50: 3,648.5          |

| 3      | 8.62x5.01" | L2-L3:<br>96 mils              | 5: 3,434.8<br>20: 4,160.6 | 10: 3,434.8<br>50: 6,116.0 | 5: 1,165.2<br>20: 2,172.6 | 10: 1,502.3<br>50: 3,673.5          |

| 4      |            | L2-L3:<br>52 mils              | 5: 4,127.3<br>20: 5,844.8 | 10: 4,714.5<br>50: 9,667.5 | 5: 1,457.3<br>20: 2,823.2 | 10: 2,082.6<br>50: 5,094.5          |

| 5      | 4.57x8.71" | L2-L3:<br>70 mils              | 5: 3,573.3<br>20: 5,290.6 | 10: 4,160.5<br>50: 8,559.5 | 5: 1,472.3<br>20: 2,883.2 | 10: 2,112.6<br>50: 5,229.5          |

| 6      |            | L2-L3:<br>96 mils              | 5: 4542.8<br>20: 6609.2   | 10: 5,268.5<br>50: 10,792  | 5: 1,502.3<br>20: 3,003.2 | 10: 2,172.6<br>50: 5,499.5          |

| 7      | 4.57x8.21" | 10 layers;<br>5 mil b/w layers | -                         | -                          | -                         | 5: 3,579                            |

| 8      |            | 12 layers;<br>5 mil b/w layers | -                         | -                          | -                         | 5: 19,800                           |

| 9      |            | 12 layers;<br>5 mil b/w layers | -                         | -                          | -                         | 5: 4,500                            |

| 10     |            |                                | -                         | -                          | -                         | 4: 3,473<br>2: 26,675<br>10: 69,245 |

|        |            |                                |                           |                            | -                         | 10: 4,982<br>4: 39,107              |

**Figure 6.** Obtained PCB cost data. All quotes use 2oz copper on all layers. Designs 1-6 employ stock FR-4, four layers, two sets of blind vias while designs 8 and 10 use RF775 and only through-hole vias. Designs 7 and 9 are identical to designs 8 and 10, respectively, except they were quoted with FR-4 dielectric (to isolate dielectric cost).

Critically, the obtained quotations confirmed one of the driving aspects of this project which is that the multi-layer construction of prior work which leverages a special, non-stock dielectric is substantially more costly than the simpler 4-layer constructions being pursued in this project. In particular, these PCBs were too costly for prototyping in this project, and so designs of this nature were not developed. However, this confirms the immense cost savings associated with targeting commonly stocked manufacturer PCB dielectrics.

#### Milestone 1.1.2<sup>4</sup>

This milestone relates to the successful completion of Task 1.2 in which an empirical PCB winding cost model was developed. The performance metric, success value, assessment, and verification process are summarized in the table below.

| Performance Metric                                           | Success Value                                                                                                                                                                                                                  | Assessment Tool / Method of Measuring Success Value                                                                                                                                                                   | Verification Process                                                                                                                                                 |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Planar PCB winding cost prediction matching to obtained data | <25% variation in predicted vs manufacturer reported costs across variations AND<br>Correct trend prediction (i.e., that features predicted by the model to yield higher cost are consistent with the data obtained in 1.1.1.) | Aggregate manufacturer trends and create cost versus variation correlations for reported quotations. All manufacturer data is combined into the dataset to smoothen effect of possible manufacturer cost differences. | Cost model reported to DOE including plot of reported trends or empirical data points versus prediction of the model. Plot shows required matching tolerance of 25%. |

We proposed a “cost index” approach for modeling the total cost (TC) of a quantity Q of PCB windings:

$$TC = GFC \times DFI_d \times MFCI_m + Q \times (DIVC + BA \times DI_d \times LI_l \times GVC \times MVCI_m)$$

<sup>4</sup> This section includes excerpts from our work in [9].

In this model, there are fixed cost indices related to:

1. General fixed costs (GFC), such as the labor and overhead required to manufacture a PCB separate from the quantity that is produced or the specific design parameters. The model fits a single value of GFC on all the data it is trained on to extract a single "general" fixed cost associated with manufacturing a PCB.

2. Choice of dielectric material ( $DFI_d$ ). For example, if a material is not typically stocked, then there may be an upfront cost in stocking that material which the customer incurs separate from the number of units that are ordered. Every material that is part of the training data is assigned its own value of DFI (and labeled with a unique numerical subscript  $d$ ), with  $DFI_1$  assigned to 1. This indicates the relative fixed cost of using a different dielectric.

3. Choice of manufacturer ( $MFCI_m$ ), which modulates the above costs (e.g. different manufacturers may have different labor or overhead costs, or different ability to source dielectrics). Every manufacturer that is part of the training data is assigned its own value of MFCI (and labeled with a unique numerical subscript  $m$ ),  $MFCI_1$  assigned to 1. This indicates the relative fixed cost of using a different manufacturer.

There are also costs related to the quantity of PCBs which are being manufactured, which we term "variable costs". Specifically, we consider:

1. Choice of dielectric material ( $DI_d$ ). Every material that is part of the training data (labeled with numerical subscript  $d$ ) is assigned its own value of DI, with  $DI_1$  assigned to 1.

2. Number of layers ( $LI_l$ ). One LI value is produced for each layer configuration in the data that is being fitted (labeled with numerical subscript  $l$  which is equal to the number of layers), with one layer count assigned to 1. For example, if the data has 4-, 10-, and 12-layer information, then three LI indices are produced which indicates the relative cost of moving between these layer configurations.

3. General variable costs (GVC). The model fits a single value of GVC on all the data it is trained on to extract a single indicator of variable costs that can be impacted by board area. For example, it can capture scrap and copper weight effects.

4. Design-independent variable costs (DIVC), such as the labor and overhead required to manufacture a given PCB design which scale with the number of units that must be produced but are independent of the design details, including board area. In principle this can always be set to zero and its impacts absorbed by GVC, but its inclusion is a reasonable generalization (separating quantity-dependent effects from quantity- and area-dependent effects).

5. The choice of manufacturer ( $MVCI_m$ ) which modulates the above costs. Each manufacturer is assigned a value of MVCI (labeled with numerical subscript  $m$ ), with  $MFCI_1$  assigned to 1.

The indices of the model can be interpreted as relative cost factors for the feature captured by each index. For example, the quantitative data contains designs having 4, 10, and 12 layers. We choose four layers to have  $LI = 1$ , and the fitted model will produce index values for 10 layers and 12 layers (for example,  $LI_4 = 1, LI_{10} = 2.6, LI_{12} = 3.0$  ). This indicates the relative cost penalty of a design changing between these layer counts which is separated from the other index factors. Thus, the cost indices approach has the advantage that cost trends or comparisons of two designs can be made by eliminating the manufacturer's parameter and quantity parameters to compare the cost of designs.

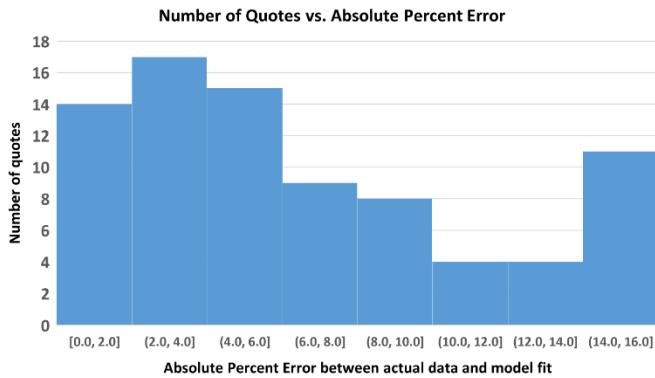

Note that there are no indices for via configuration or copper weight. In the former case, this is because the quotations have a direct coupling between via configuration and layer count - the four-layer boards use two sets of blind vias while the higher layer boards use only through hole vias. So, these two features are combined into the layer count. In the latter case, there is only one copper weight to be fit from the data and so the model does not require an index for this parameter. The model can be modularly extended to add additional features and this is discussed in detail in [9]. The indices derived for the collected data are shown in Fig. 7.

The SOPO plot is shown in Fig. 8. The model achieves a 6.53% mean absolute percentage error with a standard deviation of 4.65% between the predicted and quoted values of the cost data, better than the 25% milestone requirement. The trend prediction is also correct (e.g., exotic dielectrics are much more costly, as are increasing layer counts). The model was also tested on a new set of cost data and shown to have good predictive power for cost features included in the training data. For example, the cost of a new 4 layer, 2oz board having a smaller area of  $2.61 \times 5.21$ " was predicted with 13% error. The index-basis of the model also ensures that trends are well predicted, as the penalty for adding increased cost components is clearly captured by the index method, as described above. For example, the relative cost of a 12, 10, and 4 layer board is extracted by the model.

### Milestone 1.2.5

This milestone relates to the successful completion of Task 2.5, in which viable planar transformer configurations are selected which can achieve the EOP goals. The

| Feature/Index                       | Value                                      |

|-------------------------------------|--------------------------------------------|

| <b>Design-independent / General</b> |                                            |

| GFC / GVC / DIVC                    | 3304 / 2.72 / 0.0                          |

| <b>Dielectric and Layers</b>        |                                            |

| FR-4 <sup>8</sup>                   | $DFI_1 = DI_1 = 1.0$                       |

| Felios RF775                        | $DFI_2 = 19.3; DI_2 = 4.1$                 |

| Layers                              | $LI_4 = 1.0; LI_{10} = 2.6; LI_{12} = 3.0$ |

| <b>Manufacturers</b>                |                                            |

| Manufacturer 1                      | $MFCI_1 = 1.00; MVCI_1 = 1.00$             |

| Manufacturer 2                      | $MFCI_2 = 0.32; MVCI_2 = 0.75$             |

| Manufacturer 3                      | $MFCI_3 = 1.04; MVCI_3 = 0.34$             |

| Manufacturer 4                      | $MFCI_4 = 0.75; MVCI_4 = 0.99$             |

Figure 7. Cost model indices derived from the obtained PCB quotations.

Figure 8. Summary of the cost index model error.

Figure 8. Summary of the cost index model error.

performance metric, success value, assessment, and verification process are summarized in the table below.

| Performance Metric | Success Value                                                                                                                        | Assessment Tool / Method of Measuring Success Value         | Verification Process                                       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|

| Viability          | At least 3 different systems have a volume less than 45in <sup>3</sup> , with at least one less than or equal to 30in <sup>3</sup> . | Volume estimate based on coresets sizes and configurations. | Verification of volume assessments and methodology by DOE. |

Completing this milestone relied on completing a new task (Task 2.7) which was introduced after Q1 of the project. For completeness, we first begin by describing the work completed on this task.

After learning that prior work was not a 12-layer design as reported, but rather a 14-layer one (employing two additional PCB dielectric layers on the top and bottom of the board) [7], it was decided to pursue and experiment-in-the-loop approach to self-verify the isolation characteristics of possible transformer structures. A custom safety enclosure was designed and fabricated to ensure user safety during the high voltage testing in this project, as shown in Fig. 9. High voltage personal protective equipment (PPE) was also purchased (insulation blanket, insulation gloves, and glove protectors), as was a thermo-hygrometer for recording temperature and relative humidity. A safety procedure was devised for using the high voltage tester (PTS-75) with this enclosure and PPE.

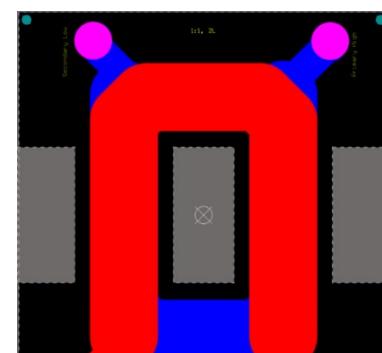

A two-layer board with one turn for each winding and 2.4mm of FR-4 between the two copper layers was fabricated having 4.8mm clearance between the edge of the windings and the cutouts for the core, as shown in Fig. 10. The primary winding and secondary winding were each short-circuited, and the high voltage from the PTS-75 was applied between these two short-circuits. A smartphone on a tripod was used to record all isolation tests. This winding arrangement was only able to support 14kV before failing. The video recording confirmed that it was not the FR-4 dielectric of the PCB which failed, but rather that arcing occurred through the air. A screenshot from this video is shown in Fig. 11. Critically, an ANSYS Maxwell Finite Element Analysis (FEA) simulation of this setup in Fig. 12 shows that only

**Figure 9.** High voltage test enclosure for multi-kV isolation testing of planar transformers in this project. The 0.09" aluminum enclosure is 5' x 3' x 2' and is solidly connected to earth. The viewing window is 0.25" Lexan.

**Figure 10.** Two-layer, single-turn design for PCB isolation testing. This matches the spacings selected through the tasks completed in Q1 of the project. The red trace is the primary, the blue trace is the secondary.

**Figure 111.** Screenshot from isolation testing recording of 2L board in air.

“partial” breakdown of the air occurs, which is not sufficient for breakdown according to prior work [7]. This confirms that ANSYS simulations do not correlate to experimental results of isolation testing. ANSYS Maxwell cannot model dielectric breakdown propagation. While breakdown is likely occurring where Maxwell suggests it is in Fig. 12, the software is incapable of propagating that breakdown.

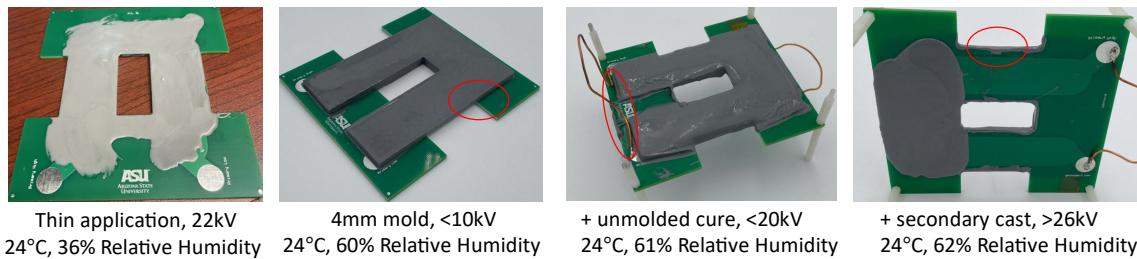

This experimental result confirms the importance of the additional top- and bottom-layer isolation layers used but not discussed in prior work [7]. Critically, the FR-4 dielectric is not the bottleneck on isolation in this experiment – it is the breakdown of air around the PCB which causes isolation failure. To confirm this, Sylgard 164 insulation material was applied to different copies of the same PCB design in Fig. 10. This material has a dielectric rating of 19kV/mm, and a number of different applications were explored (ref. Fig. 13) including: (1) a thin layer applied by hand to the primary, (2) a 4mm mold applied using a 2-part applicator gun to the primary, (3) the previous design, but with the mold removed during curing, (4) the previous design, but with Sylgard 164 also applied to part of the secondary winding.

**Figure 12.** Example applications of 19kV/mm Sylgard 164 insulation material. The red circles indicate points of failure observed in experiment.

The 4mm mold failed at a relatively low voltage (arcing at 19kV). It was cured in a 3D mold, and when that mold was removed the insulation was also slightly “peeled” off the board. An air-channel was formed at the location highlighted in Fig. 13 which likely concentrated the electric field and yielded the much lower resistance. To avoid peeling, this method was revised by pouring the Sylgard 164 into the developed mold, but removing the mold during curing, so that it would adhere to the PCB. This increased the measured resistance but failed at 20kV due to arcing from the primary winding connection, emphasizing the importance of considering how the primary winding is

connected to the rest of the system. Isolation was further added to the secondary winding and improved the breakdown to  $>26\text{kV}$ , with the failure occurring outside of the isolated section of the secondary.

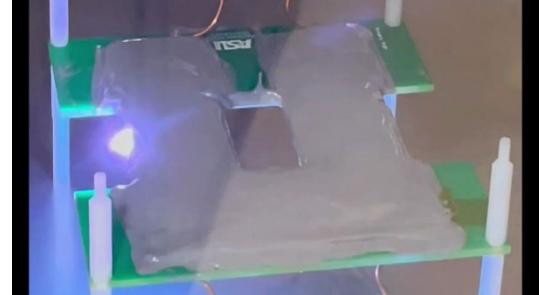

It is emphasized that dielectric failure of the PCB was not observed during any testing. Failure always occurred through the Sylgard 164 material through the air. For example, one failure observed at 30kV for the unmolded cure with secondary insulation is shown in Fig. 14. This suggests a thickness of approximately 1.5mm in the region of failure, which is consistent with a visual observation of the application there. This emphasizes that the PCB dielectric is only part of the design requirement, and very careful consideration must be made for how the windings exposed to air, and to the core, achieve the required isolation. The design procedure proposed in prior work to use ANSYS Maxwell electrostatic simulations is insufficient.

Based on these results, new constraints are imposed on the developed transformer systems. Namely, there must be a solution for fully isolating the primary winding of the core. The following options were considered:

1. Top and bottom isolation is achieved entirely through the PCB's construction. In this case, through-hole vias cannot be used because it interrupts the primary-to-secondary isolation and increases the winding length of each winding (since they must be routed to avoid these through-hole vias). Thus, the only feasible method is to implement each winding on its own PCB. These can both be 4-layer boards with the windings applied on the two internal layers and connected with through-hole vias or buried vias. Thus, the PCB's dielectric serves as the top- and bottom-layer isolation for the winding, as in the prior work. If through-hole vias are used, a small amount of Sylgard 164 isolation material is applied to isolate them.

2. Top and bottom isolation is achieved via Sylgard 164 isolation material (or similar material). This was not pursued owing to the manufacturing inconvenience, cost, and poor repeatability of employing the molded winding concept illustrated in Fig. 13.

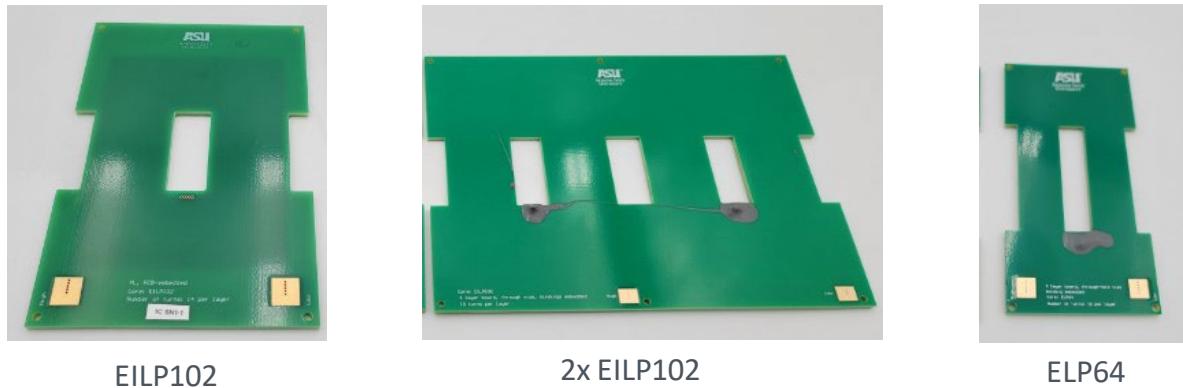

Based on the isolation results of Task 2.7, four core-to-winding spacings were considered in Task 2.5: 3, 5, 7.5 and 10mm. The larger this is, the simpler it becomes to achieve the required isolation (giving more separation through the dielectric that will be applied to shield the windings) but the worse the losses are (as less of the winding window is available for the transformer windings). A separation of at least the same amount in the vertical direction of the core window is also required for isolation between the primary windings and the core, which is nominally at the same potential as the secondary winding. This limits the cores under consideration to: EILP102, ELP102, and ELP64, having core window heights of 20.3, 26.6, and 10.2mm, respectively. Three copper thickness arrangements are considered: 3/3/3/3oz, 3/2/2/3 oz, and 2/2/2/2 oz copper for layers 1/2/3/4, respectively. Owing to the severity of the isolation requirement, only series

**Figure 13.** Isolation breakdown during experimental testing always occurred through the air.

connected transformer systems are considered. This greatly simplifies connection of the primary windings to the circuit it interfaces to, which we have seen is a critical element for isolation design. Milestone 1.2.5 requires the selection of three planar transformer configurations having less than  $45\text{in}^3$ , with at least one having less than or equal to  $30\text{in}^3$ . These are:

1. EILP102 core, 3/3/3/3oz copper, 3mm core-trace spacing, standalone, 28 turns on both primary and secondary. Estimated volume:  $17.6\text{in}^3$ , estimated loss: 38W.

2. ELP64 core, 3/3/3/3oz copper, 3 mm core-trace spacing, 2 in series, 32 total turns on both primary and secondary. Estimated volume:  $14\text{in}^3$ , estimated loss: 39W.

3. ELP102 core, 3/3/3/3oz copper, 10mm core-trace spacing, 2 in series, 34 total turns on both primary and secondary. Estimated volume:  $45\text{in}^3$ , estimated loss: 55W.

These are the lowest loss design, the lowest volume design, and a design which supports a large 10mm core-trace spacing with a large core window, respectively. Note that the first two model results exceed the minimum requirement of better-than 55W and/or better than  $30\text{in}^3$  volume. The details of the loss estimates are explained in the Milestone 1.3.2 description.

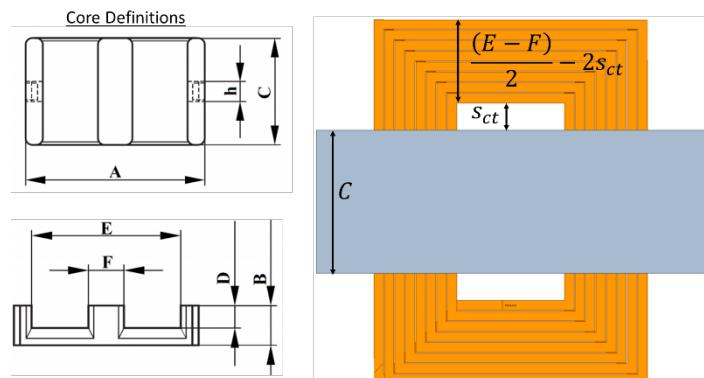

The volume is assessed as the box volume of the transformer including its windings. For example, Fig. 15 shows an example back-to-back ELP core, the box volume is

$$V_{box} = A \times (2B) \times (C + E - F - 2s_{ct})$$

For transformer system arrangements, it is assumed that the cores are side-by-side and touching, so that no volume is lost to spacing between the cores. In this case, the volume of a two-transformer system is simply twice the volume of one of the transformers.

Figure 14. Planar transformer volume estimate parameters.

### Milestone 1.3.2

This milestone relates to the successful completion of Task 3.2, in which the developed loss estimation models are verified against an FEA simulation. The performance metric, success value, assessment, and verification process are summarized in the table below.

| Performance Metric | Success Value                                                                                                                                      | Assessment Tool / Method of Measuring Success Value                                  | Verification Process             |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|

| Loss matching      | Better than 15% matching in copper loss and 15% matching core loss between a design output by the framework and FEA, with justification for error. | FEA eddy current simulation for copper loss; FEA transient simulation for core loss. | Loss comparison verified by DOE. |

The design framework requires estimation of the core and copper loss of a given transformer system construction, and Milestone 1.3.2 requires better than 15% matching

between the estimated loss and a FEA simulation of loss. To estimate copper loss, Dowell's equation is used [18]. Namely

$$R_{ac} = F_R R_{dc}$$

where  $R_{dc}$  is the dc resistance of the winding and  $F_R$  is the "ac resistance factor" which quantifies the resistance-increasing, frequency-dependent skin and proximity effects. Dowell's equation is accurate for planar transformer systems with no gap in the core path. The total loss is computed as

$$P_{copper} = \frac{1}{2} \sum_{n=1}^{11} I_{n,pk}^2 R_{ac}(nf)$$

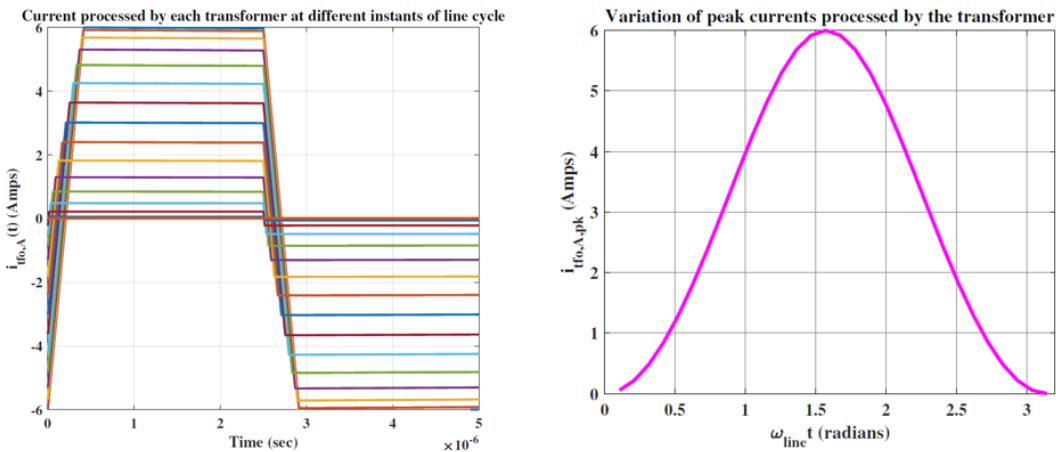

Where  $I_{n,pk}$  is the  $n_{th}$  harmonic of the current through the transformer and  $f$  is the fundamental frequency (200kHz). This Fourier decomposition is required since the currents in the transformer are trapezoidal, as shown in .

**Figure 15.** The transformers carry trapezoidal currents, with the peak of these currents changing during one 60Hz line cycle as shown in [7].

The first 11 harmonics are chosen because these well capture the frequency content of a symmetric trapezoid. The copper loss associated with 31 different peak currents are computed and then averaged to compute the net effective copper loss. Note, for example, that while the transformer must be rated to carry  $7.55A_{pk}$  at 200kHz (associated with the first harmonic of the trapezoid with peak 6A), it only operates here for a fraction of the overall line cycle. The average of the loss across the line cycle is the actual indicator of average loss and is consistent with the reporting in [7].

The core loss is computed using the improved General Steinmetz Equation [19], with the Steinmetz parameters extracted from [20]. The corresponding equation is

$$P_{core} = k_{iGSE} \cdot \left( \frac{V}{NA_c} \right)^\beta \cdot (2f)^{\alpha-\beta} \cdot V_e$$

Where  $k_{iGSE}$ ,  $\alpha$  and  $\beta$  are the Steinmetz coefficients in the iGSE framework,  $V$  is the peak square voltage applied to the core (1000V),  $N$  is the total number of turns which support this voltage on each winding,  $A_c$  is the cross sectional area of the centerpost of the core ( $F \times C$  in Fig. 15),  $f$  is the switching frequency (200kHz), and  $V_e$  is the volume of the core which carries flux (initially assumed to be the full core volume).

An example design featuring 16 primary and secondary turns and an EILP102 core is input into ANSYS Maxwell, with 500V applied to the secondary winding, mimicking the voltage across it if it was in a two-transformer system. This simulation predicts 25.8W of copper loss for a  $6A_{pk}$  trapezoidal current, and 10.3W core loss in this 16-turn transformer. The model predicts 24.7W of copper loss and 12.8W of core loss. The error in the copper loss prediction is within bounds (5%, less than the 15% requirement). The core loss prediction is too high (24%). This is attributed to the fact that the simulation properly accounts for the flow of core flux, and the “outer edges” of the core carry almost no flux, as shown in Fig. 17. On a total cross-sectional area of  $1827\text{mm}^2$ , the estimated zero loss regions are approximately  $208.3\text{mm}^2$ . This suggests that the core loss estimate should be reduced by 11.4%. Doing so yields 11.3W, which is within 10% of the prediction of the model, as required.

**Figure 16.** Simulation showing the core loss locations in a cross-section of the simulated core. The preference for flux to avoid corners of the core is clear (blue indicates zero loss). Thus, the effective volume for estimating core loss is lower than the actual core’s volume by approximately 11.4%.

#### Milestone 1.4.3

This milestone relates to the successful completion of Task 4.3, in which the developed core loss tester’s measurement accuracy is validated to publicly available core loss data. The performance metric, success value, assessment, and verification process are summarized in the table below.

| Performance Metric                                            | Success Value                                                                                                                                                                                                                                                                                                                      | Assessment Tool / Method of Measuring Success Value              | Verification Process                                                      |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|

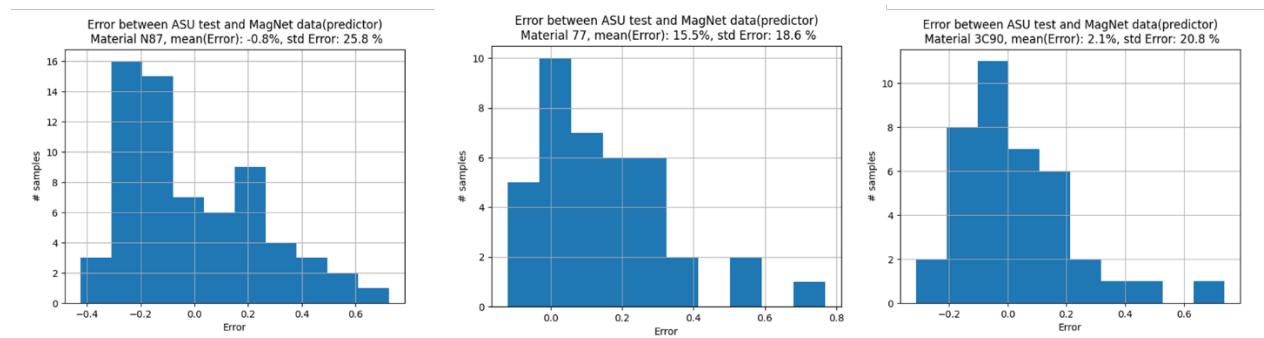

| Measured core loss match to publicly available core loss data | Better than 30% matching in measured and publicly available core loss measurements on at least three different core materials. At least 20 points of varying flux densities and frequencies will be tested for each core material. The average of these 20 points must have better than 30% matching for each core that is tested. | Performed on in-house core loss tester developed during project. | Core loss test waveforms and measurement data comparison reviewed by DOE. |

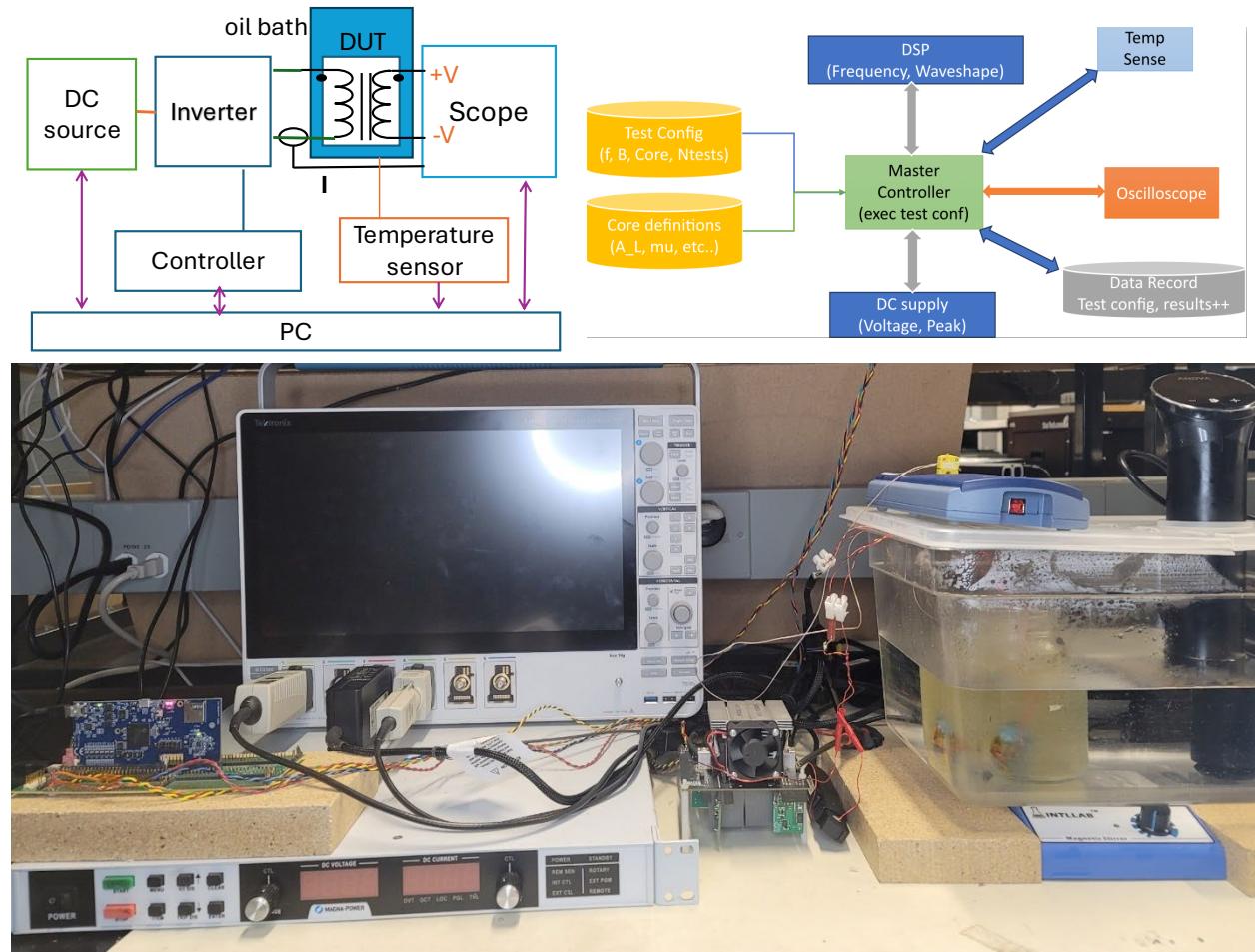

To ensure consistent data measurements, an automated test setup was developed using the core loss tester. A schematic block diagram of the tester is shown in Fig. 18. The setup comprises an oscilloscope, which records voltage and current measurements on the device under test, a dc power supply with powers the tester, a gate driver power supply, a DSP controller which transmits gating commands to the switches of the square wave inverter, and a temperature sensor for recording the temperature of the core under test. The core is wound with two sets of windings, the first connected to the exciting square wave generator and the second used to measure the voltage on the core. By

measuring the current through the first winding and the voltage on the second winding, taking their product, and then computing the average of this product (all done on the system oscilloscope), the power loss in the core can be measured. The frequency and flux density of the core is settable by controlling the switching frequency of the inverter and the voltage of the dc power supply, respectively. This control is all commanded through a central computer to ensure consistency in system measurements. The tester can produce waveforms up to 400kHz.

**Figure 17.** Automated core loss tester. Top left: overall measurement schematic. Top right: automation structure. Bottom: Hardware image showing oscilloscope, dc power supply, custom full-bridge inverter, inverter control card, Anova precision temperature controller, and Pico Technology thermocouple logger.