## III-NITRIDE ION IMPLANTATION AND DEVICE PROCESSING

J. C. Zolper,<sup>a</sup> R. J. Shul,<sup>a</sup> A. G. Baca,<sup>a</sup> S. J. Pearton,<sup>b</sup> C. R. Abernathy,<sup>b</sup>

R. G. Wilson,<sup>c</sup> R. A. Stall,<sup>d</sup> and M. Shur<sup>e</sup>

<sup>a</sup>Sandia National Laboratories, Albuquerque, NM 87185-0603

<sup>b</sup>Dept of Mat Sci. and Eng., Un. of Florida, Gainesville, FL 32611

<sup>c</sup>Hughes Research Labs, Malibu CA 90265

<sup>d</sup>Emcore Corp., Somerset, NJ

<sup>e</sup>Dept. of Elec. Eng., Un. of Virginia, Charlottesville, VA 22903-2442

Ion implantation doping and isolation has played a critical role in the realization of high performance photonic and electronic devices in all mature semiconductor material systems. This is also expected to be the case for the binary III-Nitride materials (InN, GaN, and AlN) and their alloys as the epitaxial material quality improves and more advanced device structures are fabricated. We report here on the recent progress in ion implantation doping of III-Nitride materials that has led to the first demonstration of a GaN JFET. The JFET was fabricated with all ion implantation doping. In particular, the demonstration of p-type doping of GaN with Ca has been achieved with an estimated acceptor ionization energy of 169 meV. O-implantation has also been studied and shown to yield n-type conduction with an ionization energy of ~29 meV. Neither Ca or O display measurable redistribution during a 1125 °C, 15 s activation anneal which sets an upper limit on their diffusivity at this temperature of  $2.7 \times 10^{-13} \text{ cm}^2/\text{s}$ .

## INTRODUCTION

Ion implantation has been the foundation of most advanced electronic and, to a lesser extent, photonic devices in mature semiconductor materials systems such as silicon and gallium arsenide. The selective doping and isolation capabilities of ion implantation enables many high performance device structures. The III-V nitrides are far from a mature materials system, however, ion implantation has already been used successfully to achieve selective area n- and p-type doping, isolation, and an all implanted transistor. In this paper we review recent developments in ion implantation processing in the III-V nitrides and present results for the first GaN Junction Field Effect Transistor (JFET). The JFET was made with implanted p- (Ca) and n-type (Si) dopants.

Previously we have reported on the realization of n- and p-type ion implantation doping of GaN with Si and Mg+P implants, respectively [1-3]. That work demonstrated the necessity of an activation annealing temperature of 1100 °C for GaN. In addition, the ionization energies of Si and Mg were shown to be ~25-60 meV and ~170 meV, respectively [3]. These relatively large ionization energies limit the number of free carriers at room temperature due to the exponential nature of the ionization process as related by the Boltzman factor,  $\exp(-E_A/kT)$ , where  $E_A$  is the ionization energy,  $k$  is Boltzmann's constant, and  $T$  is the absolute temperature. Therefore, it is worthwhile to study other dopant species to search for elements with shallower ionization energies, particularly for the acceptor species.

MASTER

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

DLC

#### **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

In this paper, we present results for implant doping of GaN with Ca and O. Ca had been theoretically suggested to be a shallow acceptor in GaN [4] while O is thought to play a role in the background n-type conductivity of GaN [5,6]. The redistribution properties of these elements during the implant activation anneal is also studied. Finally, processing details and device results are given for an ion implanted GaN JFET.

## EXPERIMENTAL APPROACH

The GaN layers used in the experiments were 1.5 to 2.0  $\mu\text{m}$  thick grown on c-plane sapphire substrates by metalorganic chemical vapor deposition (MOCVD) in a multiwafer rotating disk reactor at 1040 °C with a ~20 nm GaN buffer layer grown at 530 °C [7]. The GaN layers were unintentionally doped, with background n-type carrier concentrations  $\leq 5 \times 10^{16} \text{ cm}^{-3}$ . The as-grown layers had featureless surfaces and were transparent in the visible with a strong bandedge luminescence at 3.484 eV at 14 K.

$^{40}\text{Ca}$  or  $^{16}\text{O}$  ions were implanted at a dose of  $5 \times 10^{14} \text{ cm}^{-2}$  at energies of 180 or 70 keV, respectively, to place the ion peak roughly 100 nm from the surface. One Ca-sample was also implanted with  $^{31}\text{P}$  (130 keV,  $5 \times 10^{14} \text{ cm}^{-2}$ ) to study the effect of co-implantation, which has been shown to be required to achieve p-type conduction for Mg-implantation in GaN [1]. SIMS samples were prepared with the same implant conditions except  $^{18}\text{O}$  isotopes were used to reduced interference problems with background  $^{16}\text{O}$  and improve the sensitivity of the SIMS analysis for O. Samples were annealed for 10 to 15 s in flowing N<sub>2</sub> in a SiC coated graphite susceptor between 900 and 1150 °C to study the electrical activation and redistribution of the dopant species.

## Ca IMPLANTATION

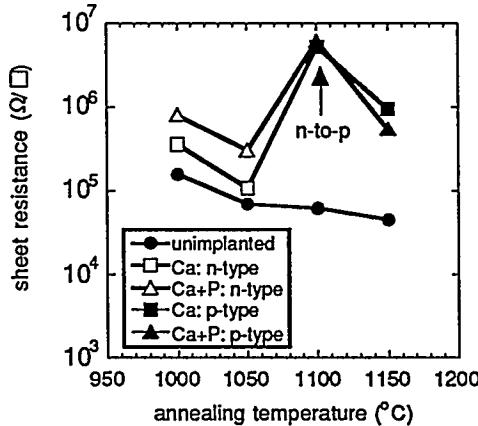

FIG 1. Sheet resistance versus annealing temperature for Ca-implanted GaN with and without a P co-implant. Both the Ca-only and Ca+P samples convert from n-to-p type after a 1100 °C anneal.

Although there had been a theoretical suggestion that Ca may be a shallow acceptor in GaN no experimental results had been reported on Ca-doping in GaN until recently [4, 8]. Figure 1 is the electrical activation data for Ca-implanted GaN with and without the P co-implantation. An unimplanted and annealed sample is included for comparison. Both the

Ca-only and the Ca+P samples convert from n-type to p-type after a 1100 °C anneal while the unimplanted samples remain n-type. This is slightly higher than the temperature required to achieve p-type conduction in Mg+P implanted GaN [1] and may be the result of more implantation induced damage associated with the heavier Ca-ion. The acceptor activity is seen to continue to increase after annealing at 1150 °C with the P co-implanted sample having a 43% lower sheet resistance and a correspondingly higher sheet hole concentration (1.57 versus  $1.14 \times 10^{12} \text{ cm}^{-2}$ ). Under the same annealing conditions, the unimplanted sample remains n-type with a slight decrease in sheet resistance that may result from the creation of additional N-vacancies or the depassivation of other n-type impurities. The Hall hole mobility of the Ca-only and Ca+P samples was  $\sim 7 \text{ cm}^2/\text{Vs}$  after a 1150 °C anneal which is in the range reported for epitaxial Mg-doped GaN [9, 10].

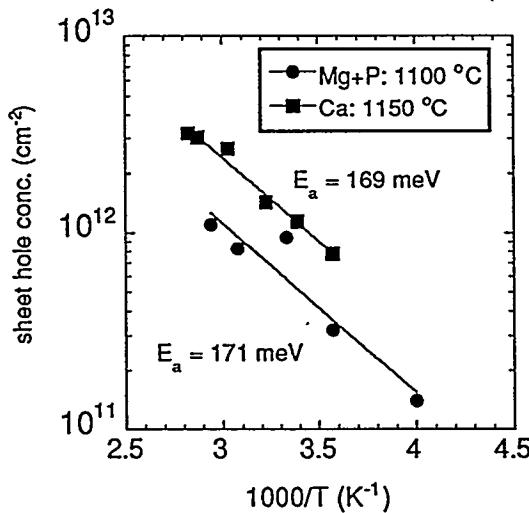

Figure 2 is an Arrhenius plot of the sheet hole concentration of the 1150 °C annealed Ca-implanted sample along with data for a Mg+P implanted sample annealed at 1100 °C. A least squares fit to the data gives an ionization level for Ca of  $169 \pm 12 \text{ meV}$  that is very close to the 171 meV for the Mg+P implanted sample [3].

FIG 2. Arrhenius plot of the sheet hole concentration for Mg+P and Ca implanted GaN annealed at the temperatures shown. The fitted ionization energies are listed on the graph.

Using the measured sheet hole concentration and ionization energy, the free hole concentration can then be determined from Eqns 1 through 3 [11]:

$$N_A^- = \frac{N_A}{1 + g \exp\left(\frac{E_A - E_F}{kT}\right)} \quad (1)$$

where  $N_A^-$  is the concentration of ionized acceptors,  $N_A$  is the total acceptor concentration which can be related to the implant dose [12], and  $g$  is the ground-state degeneracy (assumed to be 4). The free hole concentration is then given by:

$$p = N_V \exp\left(-\frac{E_F - E_V}{kT}\right) \quad (2)$$

where  $N_V$  is the valence band density-of-state defined as:

$$N_V \equiv 2\left(\frac{2\pi m_h kT}{h^2}\right)^{3/2} \quad (3)$$

Taking the hole effective mass ( $m_h$ ) as  $0.8m_e$  [13, 14], the valence band density-of-states is calculated to be  $1.18 \times 10^{19} \text{ cm}^{-3}$ . For the Ca+P sample annealed at  $1150^\circ\text{C}$  with a measured sheet hole concentration of  $1.57 \times 10^{12} \text{ cm}^{-2}$  the free hole concentration is calculated to be  $1.12 \times 10^{17} \text{ cm}^{-3}$ . This will be an average value for the implanted region. Converting this back to a sheet density by dividing by two implant straggles ( $\sim 90\%$  of the implant profile) or  $0.15 \mu\text{m}$ , gives  $p_s = 1.68 \times 10^{12} \text{ cm}^{-2}$ . By now dividing by the implant dose ( $5 \times 10^{14} \text{ cm}^{-3}$ ), we estimate only 0.3% of the implanted Ca-ions are ionized at room temperature.

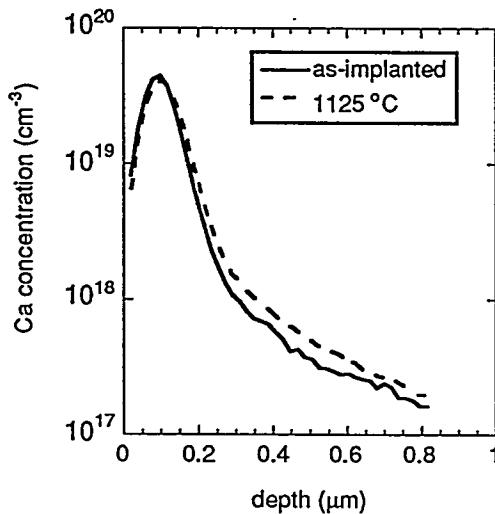

We now turn to the redistribution properties of Ca in GaN during the high temperature activation anneal. Figure 3 shows secondary ion mass spectrometry (SIMS) profiles for Ca-implanted GaN as-implanted and annealed ( $1125^\circ\text{C}$ , 15 s). No measurable redistribution has occurred during the anneal. This sets an upper limit on the diffusivity of Ca in GaN at  $1125^\circ\text{C}$  of  $2.7 \times 10^{-13} \text{ cm}^2/\text{s}$ .

FIG 3. SIMS profiles of Ca-implanted GaN either as-implanted or after a  $1125^\circ\text{C}$ , 15 s anneal.

## O IMPLANTATION

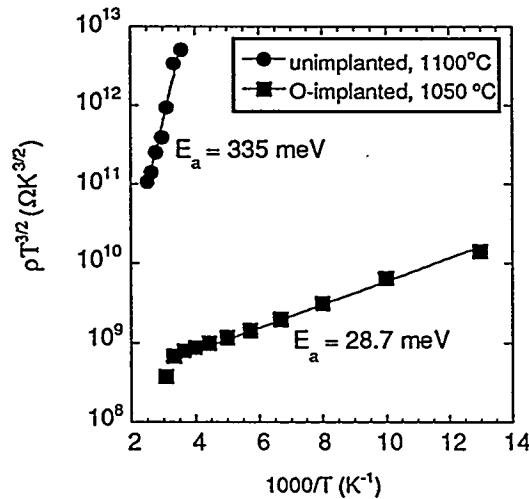

Figure 4 is an Arrhenius plot of the resistance/temperature product of O-implanted GaN annealed at 1050 °C along with data for an unimplanted and annealed (1100 °C) GaN sample. For n-type conduction, an Arrhenius plot of the resistance/temperature product is thought to be more appropriate to account for the potential presence of two band conduction in GaN [15]. O is seen to have an ionization level of 28.7 meV. A similar analysis of Si-implanted GaN yielded an ionization energy of 29 meV [2]. Following a similar treatment as for Ca above, the conduction band density-of-states is calculated to be  $2.28 \times 10^{18} \text{ cm}^{-3}$  assuming  $m_e = 0.2m_o$  [14]. The free electron sheet density is then calculated to be  $5.73 \times 10^{12} \text{ cm}^{-2}$  which corresponds to 1.1% of the implanted O being ionized at room temperature. The low activation of O may be the result of the lighter O-ion not creating sufficient lattice damage, and therefore N-vacancies, for the O to occupy a substitutional N-site. This situation may be improved in the future by using a co-implantation scheme. The low apparent O activation may also be explained by the existence of a second deep level for O in GaN that is associated with an oxygen complex. If this were the case, the electrons in the deep level would remain unionized at room temperature and not contribute to the measured electron density. Note that the unimplanted and annealed material has an activation energy for conduction of 335 eV.

FIG 4. Arrhenius plot of the resistance/temperature product for O-implant and unimplanted GaN annealed at the temperatures shown for 15 s. The estimated ionization energy for each sample is shown on the graph.

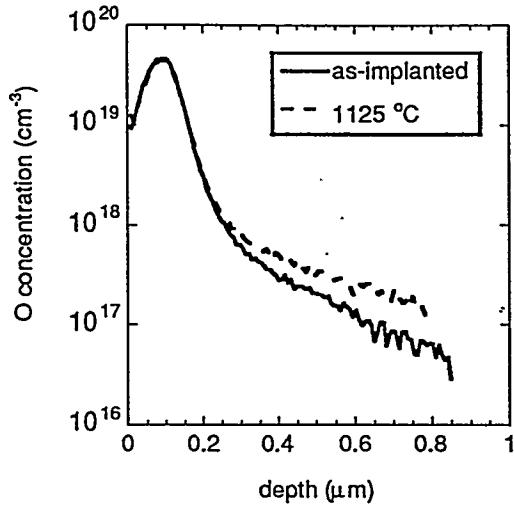

Figure 5 shows SIMS profiles for O-implanted GaN as-implanted and annealed (1125 °C, 15 s). Here again, no measurable redistribution has occurred during the anneal. This sets an upper limit on the diffusivity of O in GaN at 1125 °C of  $2.7 \times 10^{-13} \text{ cm}^2/\text{s}$ .

FIG 5. SIMS profiles for O-implanted GaN either as-implanted or after a 1125 °C, 15 s anneal.

### ION IMPLANTED GaN JFETs

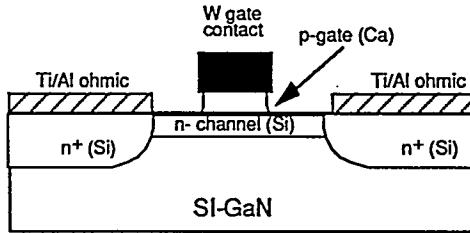

FIG 6. Schematic of ion implanted GaN JFET (Drawing not to scale).

Figure 6 shows a schematic of the ion implanted GaN JFET structure [16]. The key processing steps are as follows: 1) selective area ion implantation of the n-channel ( $^{28}\text{Si}$ : 100 keV,  $2 \times 10^{14} \text{ cm}^{-2}$ ) and p-gate  $^{40}\text{Ca}$  (40 keV,  $5 \times 10^{14} \text{ cm}^{-2}$ ), 2) sputter deposition of 300 nm of W gate contact metal, 3) RIE gate contact patterning using an  $\text{SF}_6/\text{Ar}$  plasma, 4) selective area, non-self-aligned  $^{28}\text{Si}$  ion implantation of the source and drain regions, 5) a 1150 °C, 15 s rapid thermal anneal to activate the implanted dopants, 6) ECR-plasma etching of ~50 nm of p-GaN from the source and drain regions using a  $\text{BCl}_3/\text{H}_2/\text{Ar}$  chemistry [17] 7) deposition of Ti/Al (20 nm/ 200 nm) ohmic metal, and 8) 500 °C, 15 s ohmic alloy. This structure minimizes the gate capacitance often associated with JFETs by self-aligning the p-type gate to the gate contact metal [18]. In addition, since the doping was done in selective areas, device isolation was realized via the semi-insulating properties of the GaN substrate. That is, no implant isolation or mesa etch isolation was required to isolate these devices.

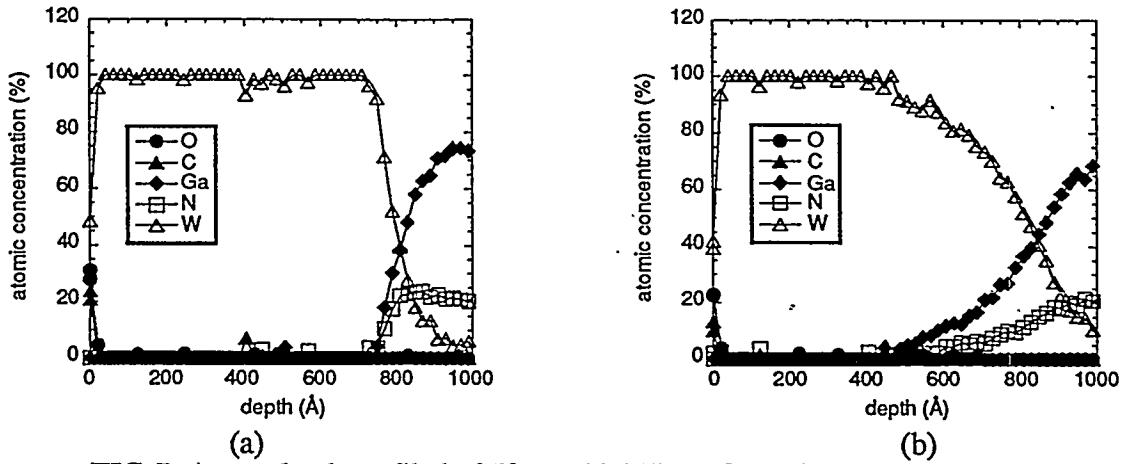

FIG 7. Auger depth profile of 50 nm thick W on GaN either a) as deposited or b) after a 15 s, 1100 °C anneal. W indiffusion is estimated to be 100 Å after annealing.

An important feature of this device structure is that the W-gate contact is in-place during the high temperature implant activation anneal. This will allow for self-aligned source-and-drain implants as has been demonstrated in GaAs JFETs (18,19). However, this approach also requires that the W not spike down through the p/n junction during the anneal. Figure 7 shows Auger depth profiles for 50 nm thick W on GaN either as deposited or after a 1100 °C, 15 s anneal. By comparing the two profiles, we estimate that after annealing the W has diffused into the GaN by only ~100 Å while Ga and N are diffusing out into the W over a distance of ~300 Å. Therefore, the Auger data demonstrates that the W/GaN interface is sufficiently stable during the implant activation anneal since the junction depth is expected to be near 450 Å and it is the indiffusion of W that could short the junction. This annealing data also demonstrates the extreme thermal stability of this gate structure for high temperature device operation.

## DEVICE RESULTS

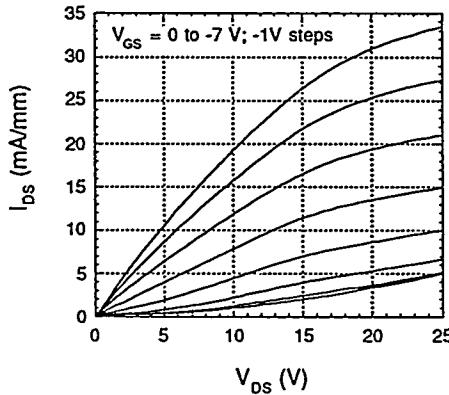

FIG 8. Room temperature  $I_{DS}$  versus  $V_{DS}$  curves for the first GaN JFET ( $V_{GS}$  starts at 0 V with -1 V steps). The JFET is 1.7  $\mu$ m x 50  $\mu$ m.

Figure 8 shows the room temperature  $I_{DS}$  versus  $V_{DS}$  curves for varied gate biases and  $I_{DS}/g_m$  versus  $V_{GS}$  for a  $\sim 1.7 \mu\text{m} \times 50 \mu\text{m}$  GaN JFET with a  $4 \mu\text{m}$  source-to-drain spacing. The JFET demonstrates good modulation characteristics with nearly complete pinch-off at a threshold voltage of approximately  $-6 \text{ V}$  for  $V_{DS} = \sim 7 \text{ V}$ . The reverse breakdown voltage of the gate junction is estimated to be  $\sim 35 \text{ V}$ .

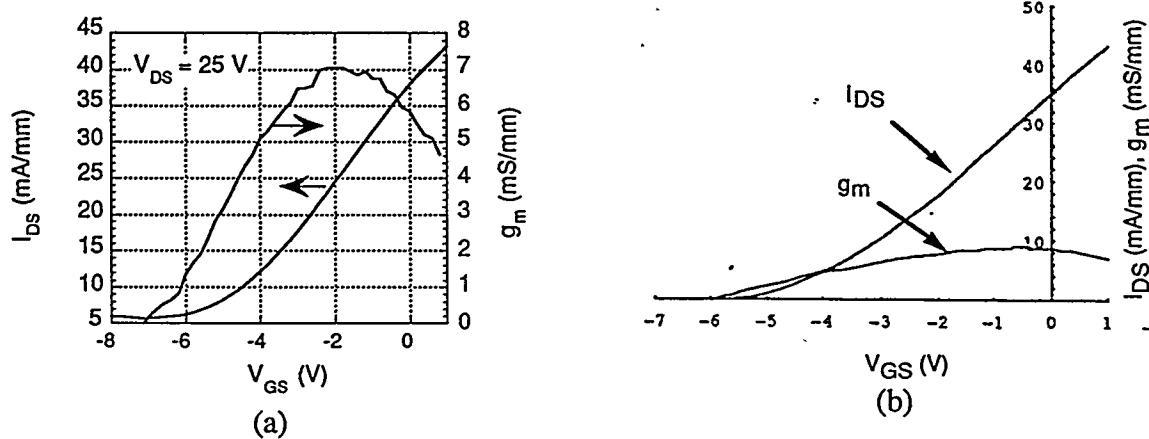

FIG 9. a) measured and b) simulated  $I_{DS}$  and  $g_m$  versus  $V_{GS}$  for a  $1.7 \mu\text{m} \times 50 \mu\text{m}$  GaN JFET. The simulation assumed  $\mu_e = 150 \text{ cm}^2/\text{Vs}$  and  $v_{sat} = 2 \times 10^7 \text{ cm/s}$ .

Figure 9 shows measured and calculated curves for  $I_{DS}$  and  $g_m$  versus  $V_{GS}$ . For  $V_{DS} = 25 \text{ V}$ , a maximum transconductance of  $7 \text{ mS/mm}$  was measured at  $V_{GS} = -2.0 \text{ V}$  with a saturation current of  $38 \text{ mA/mm}$  at  $V_{GS} = 0 \text{ V}$ . This is in good agreement with the simulated data where a value of  $150 \text{ cm}^2/\text{Vs}$  was assumed for the electron channel mobility. Four-probe measurements of the source resistance gave  $R_s \approx 500 \Omega$ . Although this value of  $R_s$  is extremely large, it only accounts for a 20% reduction in the external transconductance with respect to a corrected internal transconductance of  $8.5 \text{ mS/mm}$ . This high resistance is attributed to the region between the ohmic contact and the channel since transmission line method (TLM) test structures using the same source and drain implants on GaN witness pieces gave a value of the specific contact resistance of  $\sim 1 \times 10^{-5} \Omega\text{-cm}^2$  [3]. This access resistance can be substantially reduced by optimizing the source and drain implant conditions and by self-aligning these implants to the gate contact metal. A second possible cause of the low transconductance is low electron mobility in the implanted channel region. This is supported by the simulation fit for  $\mu_e = 150 \text{ cm}^2/\text{Vs}$  since an epitaxial GaN MESFET would have an electron mobility in the range of  $300$  to  $400 \text{ cm}^2/\text{Vs}$ . If this is the case, optimization of the implant activation process should lead to improved mobilities. In addition, optimization of the epitaxial GaN layers for maximum electron mobility, as has been done for epitaxial FETs, should result in improved JFET performance. At room temperature this device demonstrated a unity gain cut-off frequency of  $2.7 \text{ GHz}$  and a maximum oscillation frequency of  $9.4 \text{ GHz}$ . These frequency metrics are comparable to similar dimension epitaxial GaN MESFETs [20].

## CONCLUSION

Ion implantation can be expected to play an enabling role in advanced devices based on III-Nitride materials. In this paper, we have reported results for implantation doping of GaN with Ca for p-type and O for n-type conduction. Ca is seen to have an estimated ionization energy of 169 meV which is similar to that of Mg, the only other acceptor with  $E_i < 200$  meV. Both Ca and O were shown to display no measurable redistribution for an RTA at 1125 °C. The first GaN JFET was also reported which also represents the first III-Nitride based device fabricated with ion implantation doping. The GaN JFET demonstrated DC and rf performance equivalent to a similar gate length epitaxial GaN MESFET.

## ACKNOWLEDGMENTS:

The authors gratefully acknowledge the technical assistance of J. Escobedo for ion implantation and G. Lopez for JFET processing. This work was supported by the Department of Energy under DOE contract #DE-AC04-94AL85000

## REFERENCES

- [1] S. J. Pearton, C. R. Abernathy, C. B. Vartuli, J. C. Zolper, C. Yuan, R. A. Stall, *Appl. Phys. Lett.* **67**, 1435 (1995).

- [2] J. C. Zolper, M. Hagerott Crawford, A. J. Howard, S. J. Pearton, C. R. Abernathy, C. B. Vartuli, C. Yuan, R. A. Stall, J. Ramer, S. D. Hersee, R. G. Wilson, *Conf Proc. MRS, Fall 1995, symposium AAA* (Materials Research Society, Pittsburgh, PA, in press).

- [3] J. C. Zolper, M. Hagerott Crawford, S. J. Pearton, C. R. Abernathy, C. B. Vartuli, C. Yuan, and R. A. Stall, *J. Elec. Mater.* **25**, 839 (1996).

- [4] S. Strite, *Jpn. J. Appl. Phys.* **33**, L699 (1994).

- [5] B-C. Chung and M. Gershenson, *J. Appl. Phys.* **72**, 651 (1992).

- [6] H. Sato, T. Minami, E. Yamada, M. Ishii, and S. Takata, *J. Appl. Phys.* **75**, 1405 (1994).

- [7] C. Yuan, T. Salagaj, A. Gurary, P. Zawadzki, C. S. Chern, W. Kroll, R. A. Stall, Y. Li, M. Schurman, C.-Y. Hwang, W. E. Mayo, Y. Lu, S. J. Pearton, S. Krishnankutty, and R. M. Kolbas, *J. Electrochem. Soc.* **142**, L163 (1995).

- [8] J. C. Zolper, R. G. Wilson, S. J. Pearton, and R. A. Stall, *Appl. Phys. Lett.* **68**, 1945 (1996).

- [9] H. Amano, M. Kito, K. Hiramatsu, and I. Akasaki, *Jap. J. Appl. Phys.* **28** L2112 (1989).

- [10] S. Nakamura, T. Mukai, M. Senoh, and N. Iwasa, *Jap. J. Appl. Phys.* **31** L139 (1992).

- [11] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed (Wiley-Interscience, New York, 1981) pp. 18-24.

- [12] J. C. Zolper, J. F. Klem, A. G. Baca, M. E. Sherwin, M. J. Hafich, and T. J. Drummond, *J. Appl. Phys.* (in press).

- [13] J. I. Pankove, S. Broom, and G. Harbecke, *RCA Rev.* **36**, 163 (1975).

- [14] M. Suzuki and T. Uenoyama, *Jpn. J. Appl. Phys.* **34**, 3442 (1995).

- [15] R. J. Molnar, T. Lei, and T. D. Moustakas, *Appl. Phys. Lett.* **62**, 72 (1993).

- [16] J. C. Zolper, R. J. Shul, A. G. Baca, R. G. Wilson, S. J. Pearton, and R. A. Stall, *Appl. Phys. Lett.* **68**, 2273 (1996).

- [17] R. J. Shul, A. J. Howard, S. J. Pearton, C. R. Abernathy, C. B. Vartuli, P. A. Barnes, and P. Davies, *Conf. Proc. MRS, Fall 1995, symposium AAA (Material Research Society, Pittsburgh PA, in press)*.

- [18] J. C. Zolper, A. G. Baca, R. J. Shul, A. J. Howard, D. J. Rieger, M. E. Sherwin, M. L. Lovejoy, H. P. Hjalmarson, B. L. Draper, J. F. Klem, and V. M. Hietala, *IEEE Trans. Elec. Dev.* **41**, 1078 (1994).

- [19] J. C. Zolper, M. E. Sherwin, A. G. Baca, R. J. Shul, J. F. Klem, and V. M. Hietala, *IEEE Elec. Dev. Lett.* **15**, 493 (1994).

- [20] S. C. Binari, L. B. Rowland, G. Kelner, W. Kruppa, H. B. Dietrick, K. Doverspike, and D. K. Gaskill, in *Proceedings of 1994 International Symposium on Comp. Semiconductors*, San Diego, CA Sept. 1994 (Institute of Physics, Bristol, UK, 1995) pp. 492-496.

---

## DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

---