DOI: 10.1002/ ((adma.202108025))

**Article type: Perspective**

**Progress and Challenges for Memtransistors in Neuromorphic Circuits and Systems**

Xiaodong Yan, Justin H. Qian, Vinod K. Sangwan\*, and Mark C. Hersam\*

Dr. X. Yan, J. H. Qian, Dr. V. K. Sangwan, Prof. M. C. Hersam

Department of Materials Science and Engineering

Northwestern University, Evanston, Illinois 60208, USA

E-mail: [vinod.sangwan@northwestern.edu](mailto:vinod.sangwan@northwestern.edu), [m-hersam@northwestern.edu](mailto:m-hersam@northwestern.edu)

Prof. M. C. Hersam

Department of Electrical and Computer Engineering

Northwestern University, Evanston, Illinois 60208, USA

Prof. M. C. Hersam

Department of Chemistry

Northwestern University, Evanston, Illinois 60208, USA

**Keywords:** memristors; gate-tunable; non-volatile memory; van der Waals materials; artificial intelligence

**Abstract**

Due to the increasing importance of artificial intelligence (AI), significant recent effort has been devoted to the development of neuromorphic circuits that seek to emulate the energy-efficient information processing of the brain. While non-volatile memory (NVM) based on resistive switching, phase-change memory, and magnetic tunnel junctions have shown potential for implementing neural networks, additional multi-terminal device concepts are required for more sophisticated bio-realistic functions. Of particular interest are memtransistors based on low-dimensional nanomaterials, which are capable of electrostatically tuning memory and learning behavior at the device level. In this Perspective, a conceptual overview of the memtransistor is provided in the context of neuromorphic circuits. Recent progress is surveyed for memtransistors and related multi-terminal NVM devices including dual-gated floating-gate memories, dual-gated ferroelectric transistors, and dual-gated van der Waals heterojunctions. The different materials systems and device architectures are classified based on the degree of control and relative tunability of synaptic behavior, with an emphasis on device concepts that harness the reduced dimensionality, weak

This is the author manuscript accepted for publication and has undergone full peer review but has not been through the copyediting, typesetting, pagination and proofreading process, which may lead to differences between this version and the [Version of Record](#). Please cite this article as [doi: 10.1002/adma.202108025](https://doi.org/10.1002/adma.202108025).

This article is protected by copyright. All rights reserved.

electrostatic screening, and phase changes properties of nanomaterials. Finally, strategies for achieving wafer-scale integration of memtransistors and multi-terminal NVM devices are delineated, with specific attention given to the materials challenges for practical neuromorphic circuits.

## 1. Introduction

The field of artificial intelligence has experienced massive growth due to innovations in algorithms and the increased computational power of complementary metal-oxide-semiconductor (CMOS) technology. The proliferation of digital data acquisition and communication has further accentuated the need for rapid local data processing to enable timely decision-making. Although the miniaturization of individual devices has slowed, commercially available graphics processing units (GPUs) have sustained the growth in computation power that is necessary for training deep neural networks (DNNs) with increasing complexity.<sup>[1-4]</sup> However, current machine learning and artificial neural network (ANN) algorithms continue to rely on CMOS chips that use the von Neumann architecture,<sup>[5]</sup> where data must be constantly shuttled between the processing and memory units. With large amounts of data, this architecture leads to poor scaling of computational time and energy consumption due to limited bandwidth that is often referred to as the von Neumann bottleneck.<sup>[6]</sup> To circumvent this intrinsic limitation of CMOS technology, increasing effort has been devoted to neuromorphic computing approaches that attempt to emulate the energy-efficient information processing in biological neural networks.<sup>[7]</sup> Neuromorphic circuits aim to take advantage of the parallel, low-power, and fault-tolerant processing of the brain by mimicking the functions of neurons and synapses in highly interconnected networks.<sup>[8]</sup>

Synapses greatly outnumber neurons in both the brain ( $\sim 10^{15}$  synapses versus  $\sim 10^{11}$  neurons) and fully connected ANN architectures, making them critical elements for neuromorphic hardware implementations. Biological synapses can either enhance or inhibit the transmitted signal between neurons. The level of transmission is determined by the strength of the synaptic connection, which is updated during learning. Consequently, artificial synapses should not only store

This article is protected by copyright. All rights reserved.

an analog weight but also possess a physical mechanism to update the weights based on simple protocols. In solid-state electronic devices, the synaptic weights are often represented using different conductance states, where the conductance range and weight update rules are constrained by materials properties. For most ANN applications, non-volatile memory (NVM) and time-independent linear and symmetric weight update rules are sufficient. However, bio-realistic synaptic functions are complex and temporally influenced, requiring more complicated learning rules such as short-term and long-term plasticity,<sup>[9, 10]</sup> paired-pulse facilitation,<sup>[11]</sup> spike-time dependent plasticity (STDP),<sup>[12, 13]</sup> spiking-rate dependent plasticity (SRDP), heterosynaptic plasticity,<sup>[14]</sup> and metaplasticity.<sup>[15]</sup> Like synapses, bio-realistic neuron behavior is also highly diverse, which has motivated the development of mathematical neuron models with varying levels of complexity.<sup>[16-20]</sup> Often highly simplified cases such as the perceptron<sup>[21]</sup> are sufficient for ANNs, resulting in many neuron models being designed to imitate only the ability of the neuron to integrate incoming signals and fire output spikes after reaching a predefined threshold.

While biological neurons and dendrites can achieve an extremely large number of synaptic connections in three dimensions, the physical realization of neuromorphic circuit architectures has thus far been constrained by the planar and rigid nature of integrated circuits. For ANN architectures, fully connected one-dimensional layers of perceptrons called multi-layer perceptrons (MLPs)<sup>[22]</sup> can be implemented in a planar geometry using crossbar arrays. Although MLPs and other DNNs using back-propagation and gradient descent-based supervised learning algorithms have shown success for select AI applications, they fail to incorporate many features of biological neural networks and require large amounts of computationally intensive matrix multiplication.<sup>[23]</sup> In contrast, bio-realistic spiking neural networks (SNNs) are an emerging architecture that rely on temporally coded spikes to transmit information and are typically trained using STDP-based unsupervised learning rules.<sup>[24, 25]</sup> Despite their inferior performance for pattern recognition, SNNs are more energy-efficient than ANNs due to their temporally dependent and sparse spiking.

This article is protected by copyright. All rights reserved.

behavior, and are well-suited for event-driven applications.<sup>[25, 26]</sup> Importantly, SNNs also provide opportunities for additional bio-realistic functionality such as reinforcement learning and other reward-based learning rules. Other network models that are optimal for particular problems, such as recurrent neural networks (RNNs) for natural language processing, convolutional neural networks (CNN) for image recognition, and reinforcement neural networks for robotic applications are also relevant, and often come with unique requirements at the device and circuit level.<sup>[3, 4, 27-29]</sup>

Due to its technological maturity, silicon was the first platform used for exploring neuromorphic computing<sup>[30]</sup>, and the semiconductor industry remains interested in developing in-memory<sup>[31]</sup> using CMOS-based field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs).<sup>[32, 33]</sup> SpiNNaker,<sup>[34]</sup> TrueNorth,<sup>[35]</sup> and Loihi,<sup>[36]</sup> are large-scale examples of spike-based neuromorphic hardware that seeks to take advantage of the unique characteristics of SNNs at the hardware level.<sup>[34, 36]</sup> However, these CMOS-based examples suffer from high power consumption due to the von Neumann bottleneck, with an extreme example being the GPU-based training of a neural architecture search (NAS) model consuming over 650,000 kWh of power.<sup>[37]</sup> Consequently, emerging NVM technologies are considered to be a promising alternative due to lower power consumption and smaller footprints.<sup>[38]</sup> In crossbar array implementations, each NVM node between rows and columns acts like a synapse. The output current from each node is summed along the rows and columns before feeding into the neurons that are further connected with the same or another set of crossbar synapses. In this manner, crossbar arrays of NVM elements can be used to directly map ANN weights to device conductance states, enabling parallel operations for analog vector-matrix multiplication (VMM).<sup>[39]</sup> The fundamental switching mechanisms, materials science, and applications of NVM devices have been extensively reviewed elsewhere,<sup>[40]</sup> including implementations based on nanomaterials,<sup>[41]</sup> organic electronics,<sup>[42]</sup> van der Waals layered materials,<sup>[43]</sup> phase-change materials,<sup>[44]</sup> ferroelectric and multiferroic materials,<sup>[45]</sup> Mott insulators,<sup>[46]</sup> spintronics,<sup>[47]</sup> memristors,<sup>[6, 38]</sup> and other inorganic synaptic transistors.<sup>[48]</sup>

This article is protected by copyright. All rights reserved.

Among these NVM options, memristors have attracted significant recent attention due to their small footprint, fast switching time, low power consumption, and capability for multi-state storage. Furthermore, memristors can implement bio-inspired functionality such as STDP due to the underlying similarities between ionic motion in biological synaptic channels and the correlated drift and diffusion of electrons, defects, vacancies, and ions in memristive systems. However, memristors are simple two-terminal devices, and typically require an additional element like a transistor to select individual nodes. An NVM device with gate-tunable memory not only integrates selection functionality at the device level but can also use the gate electrode to influence the switching behavior and achieve on-demand learning rules. In a single two-terminal device, this level of tunability is not possible because switching mechanisms involving resistance state changes are intimately tied to underlying physical processes such as electron transport, ion migration, phase change, thermal transport, and spin flipping processes. Despite these limitations, some progress has been made in tailoring the switching behavior of two-terminal memristors by controlling material stoichiometry or using multi-layered structures. For example, Ag islands in an oxide matrix can disperse under an applied electric field and regroup due to surface tension, resulting in a bio-realistic delay and relaxation response.<sup>[49]</sup> Nevertheless, even if a memristive system can display a bio-realistic response and desired learning rules for a specific data-centric problem, a memristor-based circuit offers limited additional reconfigurability at individual nodes due to the two-terminal architecture. In this context, nanomaterials are capable of alternative device architectures where the underlying resistive switching can be coupled to additional control parameters such as electrostatic gating and photoexcitation.<sup>[41, 50]</sup> In particular, two-dimensional (2D) materials not only allow anisotropic in-plane conductivities and multi-terminal geometries but also present opportunities for van der Waals heterojunctions with other low-dimensional nanomaterials.<sup>[51]</sup>

Three-terminal gate-tunable memristors, also known as memtransistors, are promising device prototypes that exploit the weak electrostatic screening of low-dimensional nanomaterials.

This article is protected by copyright. All rights reserved.

Typically, memtransistors are based on Schottky barrier tuning at metal-semiconductor interfaces using vacancy/ion transport, charge trapping, or ferroelectric domain switching. Other switching mechanisms, such as those found in phase-change materials, have also been explored. In addition to their intrinsic resistive switching, the channels are atomically thin and therefore can be strongly tuned using electrostatic gating. Electrostatic gating not only allows for control of the channel conductance through the field effect, but it can also be used to directly influence the switching mechanism of the NVM state. Therefore, by combining NVM with gate tunability in a single device, memtransistors simplify addressability in crossbar arrays and efficiently enable tunable learning rules and bio-realistic functions such as heterosynaptic plasticity, continuous learning, neuromodulation, and multi-temporal plasticity.

**Figure 1** summarizes the areas of interest for memtransistors including materials synthesis, devices, architectures, and applications. In the following sections, we will first review concepts and mechanisms underlying memristors, memtransistors, and related devices such as dual-gated synaptic transistors, and how these mechanisms are influenced by material defects. We will also explore how defects can be engineered during the materials synthesis process. We will then discuss recent experimental demonstrations of gated memory devices and memtransistors based on 2D materials, van der Waals heterojunctions, and related material systems. Initial attempts to integrate memtransistors and related devices in scaled circuit architectures will be delineated, with a specific focus on the opportunities enabled by the ultrathin nature of 2D materials. Finally, we will outline the remaining challenges and opportunities for moving from individual memtransistor devices to full neuromorphic circuits and systems, such as requirements for wafer-scale integration, opportunities for realizing novel bio-inspired functions, and the need to develop new software and neuromorphic architectures to fully take advantage of the unique properties of memtransistors.

**Figure 1. Summary of memtransistor synthesis, device structures, architectures, and neuromorphic applications.** Synthesis methods include physical vapor deposition (PVD), chemical vapor deposition (CVD), metal-organic chemical vapor deposition (MOCVD), and solution-based processing to realize materials suitable for memtransistors. Memtransistor device structures can be designed with different gating schemes to enable new device functions. Connecting multiple memtransistors in crossbar arrays and/or three-dimensional (3D) integration can further facilitate applications in neuromorphic computing, bio-mimetic robotics, and brain-machine interfaces. The memtransistor schematic at the center is adapted with permission.<sup>[52]</sup> Copyright 2018, Springer Nature. The 3D integration schematic is adapted with permission.<sup>[53]</sup> Copyright 2017, Springer Nature.

## 2. Memtransistor Fundamentals

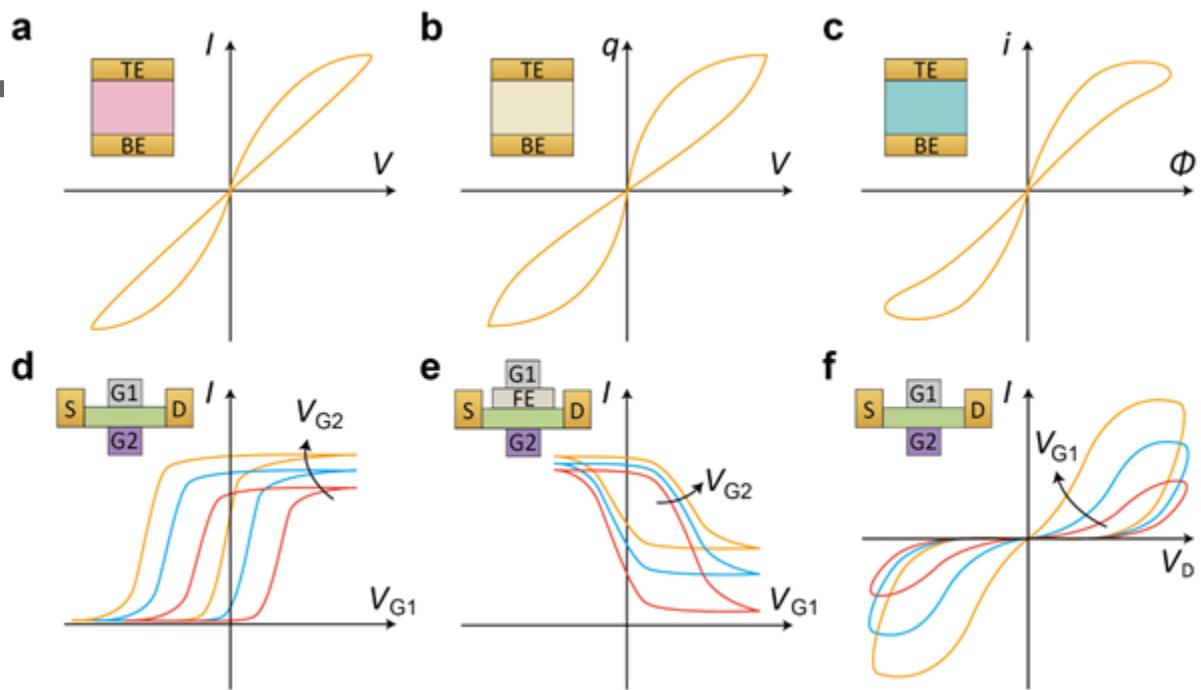

**Figure 2. Current-voltage (I-V) characteristics of two-terminal memristive systems, multi-terminal memtransistors, and related device concepts.** (a) Memristor. (b) Memcapacitor. (c) Meminductor. (d) Dual-gated synaptic transistor. (e) Dual-gated ferroelectric field-effect transistor (FeFET). (f) Dual-gated memtransistor. (d-f) The arrow shows how the device behavior changes under increasing gate voltage bias ( $V_{G2}$ ). TE and BE stand for top electrode and bottom electrode, respectively. S, D, G1, and G2 stand for source electrode, drain electrode, gate electrode 1, and gate electrode 2, respectively. FE stands for ferroelectric dielectric.

The prototypical memristor<sup>[54, 55]</sup> consists of a metal/insulator/metal stack, whose current-voltage (I-V) characteristic displays a pinched hysteresis loop<sup>[56, 57]</sup> (Figure 2a). The resistance of the device is controlled by the migration of defects, dopants, or ions, which modulate the conductance through the formation and rupture of a filament or by modifying the Schottky barriers at the

contacts. Depending on the switching mechanism, different types of volatile and non-volatile memristive behavior have been observed such as bipolar, unipolar, threshold, complementary, and diffusive resistive switching.<sup>[41, 58-60]</sup> The concept of memristive systems has also been extended to meminductors and memcapacitors,<sup>[61]</sup> which show similar pinched hysteresis loops for charge-voltage and current-flux curves, respectively, and are mainly used to pursue hardware implementation of spiking neurons and neuristors (Figure 2b-c).<sup>[62]</sup> Furthermore, higher-order memristive systems include more than two coupled internal state variables with intrinsic dynamical behavior, with second-order and third-order memristors having been demonstrated experimentally.<sup>[63-66]</sup>

The memistor<sup>[67]</sup> is distinct from but related to the memristor in that it is a combination of “memory” and “resistor” but consists of three terminals. The third terminal is used as a gate to modulate the formation and rupture of the conductive filament, which was first demonstrated with copper electroplating of a graphite rod.<sup>[67]</sup> Due to the recent interest in using NVM for neuromorphic circuits, three-terminal devices like memristors have gained traction as a means of decoupling the write and read terminals in the network. One simple way to create the circuit equivalent of a memistor is by connecting two memristors in parallel using independent source terminals and a common drain terminal.<sup>[68]</sup> However, a more compact approach to achieve the same response is to engineer memristor materials and device geometries so that only a single third terminal is needed for modulation of the resistive switching. For example, in a three-terminal  $\text{TiO}_2$  memristor realized using angled evaporation of metals, an applied voltage at a third terminal was shown to modulate the resistance between the first two terminals by a factor of 20. Similar multi-terminal memristor schemes have also been explored in oxide nanowires to understand resistive switching mechanisms,<sup>[69]</sup> and in planar films of Ag nanoclusters to demonstrate heterosynaptic plasticity.<sup>[70]</sup> Three-terminal memristors have also been studied in  $\text{Ta}_2\text{O}_5$ ,<sup>[71-73]</sup>  $\text{TiO}_2$ ,<sup>[68]</sup>  $\text{SrTiO}_3$ ,<sup>[74]</sup> and Ag/Cu atomic switches,<sup>[75]</sup> often with the addition of a gate dielectric to reduce the leakage currents from the third

This article is protected by copyright. All rights reserved.

terminal (Figure 3a). However, while memistors can show continuous conductance states with a wide dynamic range,<sup>[76]</sup> the additional terminal increases the device footprint and fabrication complexity, limiting their suitability as synaptic elements. As suggested by Zidan,<sup>[77]</sup> one possibility is to use memistors as a selector element in memristor crossbar arrays. Because of their exceptionally high off-state resistance and non-volatile switching, memistors would enable fine control over individual nodes while consuming less power compared to conventional selectors.

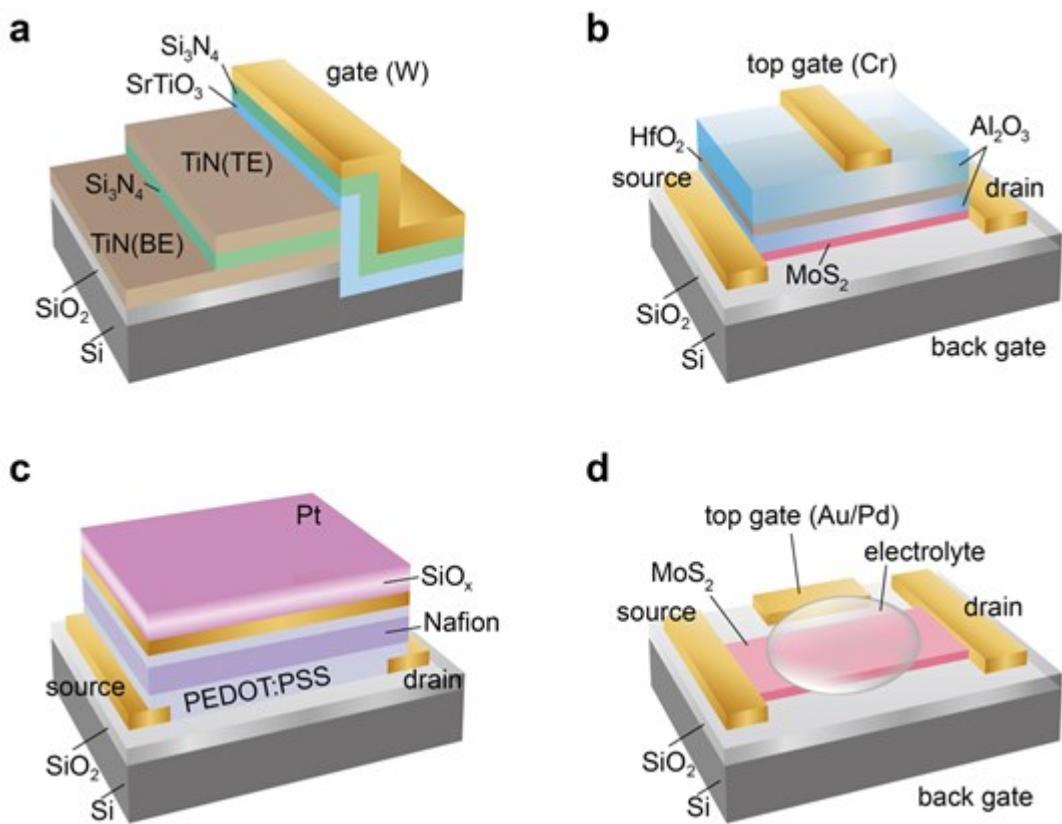

In addition to memistors, three-terminal transistors with integrated memory have also been developed for neuromorphic applications.<sup>[48]</sup> The earliest transistors for synaptic emulation (i.e., synaptic transistors) were fabricated using conventional CMOS technology, namely floating-gate flash memory.<sup>[78]</sup> More recently, floating-gate transistors based on 2D semiconductors such as monolayer MoS<sub>2</sub> and graphene have been explored (Figure 3b) due to their improving scaling potential and the ultrafast speed of charge tunneling through the van der Waals barrier.<sup>[79-82]</sup> Similarly, synaptic transistors based on interface charge trapping have been explored in a variety of contexts due to their potentially lower power consumption per synaptic weight update operation.<sup>[83-86]</sup>

<sup>86]</sup> In particular, charge trapping carbon nanotube<sup>[87]</sup> and MoS<sub>2</sub><sup>[88]</sup> synaptic transistors have been demonstrated and used to implement STDP protocols for SNNs. Nanomaterial-based devices are highly advantageous in this regard due to the high surface area and large curvature that results in increased access to interfacial and other midgap trap states. Additionally, the reduced charge screening of nanomaterials allows for greater electrostatic control via dual-gated and self-aligned device architectures.<sup>[89, 90]</sup> While dual-gated synaptic transistors have been demonstrated using CMOS platforms, they typically require complicated structures such as fin field-effect transistor (FinFET) or gate-all-around (GAA) structures to achieve full electrostatic control.<sup>[91]</sup> In contrast, a simple lateral structure is sufficient for full electrostatic control over 2D materials. For example, dual-gated MoS<sub>2</sub> synaptic transistors have been demonstrated with oxide bilayer charge trap memory using Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stacks.<sup>[92]</sup> Dual-gated MoS<sub>2</sub> synaptic transistors have also been

This article is protected by copyright. All rights reserved.

realized with floating-gate memory using hBN as a tunnel barrier and either metal<sup>[93]</sup> or graphene<sup>[94]</sup> as the floating gate. Sweeping the top gate in these synaptic transistors typically leads to a transfer curve with a large hysteresis window, which is dependent on the magnitude of the voltage sweep. Applying a back-gate voltage then shifts the threshold voltage and also changes the size of the hysteresis window via doping/de-doping of the channel (Figure 2d), enabling multi-level weight storage and tunable learning curves<sup>[94]</sup> for neuromorphic applications. Charge trapping memory can also be programmed using the source and drain contacts, to obtain a two-terminal charge-trapping memristor (i.e., memflash). This concept has been demonstrated in both silicon CMOS<sup>[95, 96]</sup> and van der Waals heterojunction<sup>[97, 98]</sup> floating-gate devices. However, gate-tunable memristive behavior is difficult to achieve in these cases since the tunneling primarily occurs underneath the metallic contacts, which screen the electric field from the gate electrode.

Another strategy to achieve gate-controlled NVM is by using ferroelectric gate dielectrics in ferroelectric FETs (FeFETs).<sup>[45, 99]</sup> For example, ZnO transistors with a Pb(Zr, Ti)O<sub>3</sub> ferroelectric dielectric have been used as synaptic devices in a Hopfield neural network,<sup>[100]</sup> and IGZO transistors with a HfZrO<sub>x</sub> ferroelectric dielectric have been used in multi-layer perceptrons.<sup>[101]</sup> FeFETs with ultrathin channels can also be implemented in dual-gated structures for tunable memory.<sup>[102]</sup> However, unlike dual-gated charge-trapping or flash memory, the effect of the additional gate in FeFETs is more complicated due to electrostatic coupling, and thus additional constraints often need to be addressed to obtain large on/off ratios (Figure 2e.). In a demonstration of a dual-gated SnO transistor with a ferroelectric P(VDF-TrFE) polymer,<sup>[103]</sup> the threshold voltage remained relatively unaffected by the back-gate voltage since the ferroelectric polymer layer was largely screened by the 30-nm-thick channel. In contrast, in a dual-gated FeFET with a few-layer MoS<sub>2</sub> or black phosphorous channel and the same P(VDF-TrFE) ferroelectric layer, the channel showed a strong electrostatic interaction with the bottom and top gates, resulting in an on/off ratio exceeding 10<sup>3</sup>.<sup>[104]</sup>

This article is protected by copyright. All rights reserved.

Gate-tunable synaptic responses have also been achieved with electrolyte-gated transistors (EGTs) that are modulated by ionic electric double layers (EDLs) and organic electrochemical transistors (OECTs) that are modulated by redox reactions.<sup>[42, 105]</sup> However, electrolyte-based NVM suffers from poor retention times due to ionic relaxation, although the integration of OECTs with diffusive Ag-oxide memristors (Figure 3c) can enhance the state stability and enable parallel operation of crossbars.<sup>[106]</sup> Li-ion-based synaptic transistors based on solid-state electrolytes have also shown promise due to linear and symmetric learning behavior for low-power analog computation.<sup>[107]</sup> For example, dual-gated Li-ion-intercalated MoS<sub>2</sub> synaptic transistors (Figure 3d) have demonstrated neuristor behavior with independently controlled responses from the electrolyte and dielectric gates.<sup>[108]</sup> Electrolyte gating also enables the integration of multiple gate terminals with spatially and temporally coupled signals, which is particularly well-suited for niche neuromorphic applications such as sound localization. The non-rectilinear channel geometries in electrolyte and ion-gel-based materials have further been used to demonstrate heterosynaptic plasticity in MoS<sub>2</sub> synaptic transistors<sup>[109-111]</sup> and OECT synaptic transistors<sup>[112]</sup> in addition to homeostatic plasticity in EGT synaptic transistors.<sup>[113, 114]</sup>

The memtransistor is also a three-terminal device based on the memristor. Unlike a memistor or a synaptic transistor, the gate electrode in the memtransistor is used to modulate the resistive switching behavior rather than drive it. While synaptic transistors and memristors possess hysteresis and pinched loops in their transfer curves, a memtransistor (Figure 2f) has a gate-tunable pinched hysteresis loop in the output characteristics ( $I_D$ - $V_D$ ) that can be achieved without gate-bias hysteresis in the transfer characteristics ( $I_D$ - $V_G$ ). Therefore, single-gated memtransistors incorporate the intrinsic resistive switching behavior of memristors while also achieving a similar node selection function as previously described in dual-gated synaptic transistors. Furthermore, in a dual-gated four-terminal memtransistor, the node selection and tuning functions can be concurrently achieved with no additional circuitry,<sup>[115]</sup> and differently configured gates can be used to realize bio-mimetic

This article is protected by copyright. All rights reserved.

functions.<sup>[116]</sup> In the following section, we will review recent experimental progress for memtransistors, which have been primarily implemented using 2D materials and van der Waals heterojunctions.

**Figure 3. Device architectures for gate-tunable memory devices.** (a) Three-terminal memristor based on  $\text{Si}_3\text{N}_4$  and  $\text{SrTiO}_3$ . Adapted with permission.<sup>[74]</sup> Copyright 2018, IEEE. (b) Dual-gated  $\text{MoS}_2$  charge trapping memory device possessing tunable hysteresis. Adapted with permission.<sup>[92]</sup> Copyright 2015, American Chemical Society. (c) Ionic floating-gate memory device consisting of an organic electrochemical transistor and diffusive memristor for parallel operation of the crossbar array. Adapted with permission.<sup>[106]</sup> Copyright 2019, The American Association for the Advancement of Science. (d) Dual-gated  $\text{MoS}_2$  synaptic transistor with an electrolyte top gate and a Si/ $\text{SiO}_2$  back gate and dielectric stack. Adapted with permission.<sup>[108]</sup> Copyright 2019, American Chemical Society.

### 3. Memtransistor Materials, Mechanisms, and Architectures

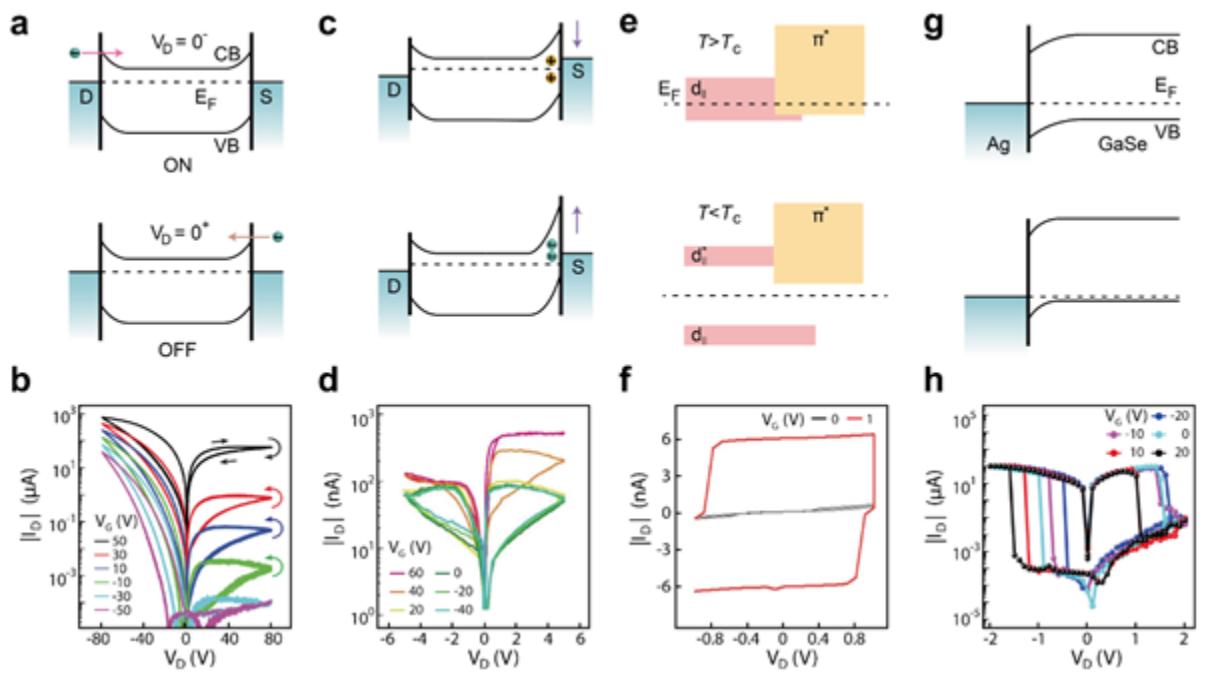

**Figure 4. Band diagrams and I-V characteristics of memtransistors and related memory devices.** (a-b) Band diagram of a monolayer polycrystalline MoS<sub>2</sub> memtransistor<sup>[117]</sup> showing switching of the dominant Schottky contact in the OFF and ON states (top) and corresponding I<sub>D</sub>-V<sub>D</sub> characteristics (bottom) at different gate voltage biases (V<sub>G</sub>). Arrows show the direction of the curves. Reproduced with permission.<sup>[52]</sup> Copyright 2018, Springer Nature. (c-d) Band diagram of an α-In<sub>2</sub>Se<sub>3</sub> ferroelectric memtransistor (top) showing Schottky barrier modulation via in-plane ferroelectric polarization and corresponding I<sub>D</sub>-V<sub>D</sub> characteristics (bottom) showing gate tunability. Reproduced with permission.<sup>[118]</sup> Copyright 2019, Wiley. (d-e) Change in VO<sub>2</sub> band structure during the Mott metal-to-insulator transition (top) and corresponding I<sub>D</sub>-V<sub>D</sub> characteristics of the VO<sub>2</sub> memtransistor (bottom) showing gate tunability of the Mott transition. Reproduced with permission.<sup>[119]</sup> Copyright 2021, Wiley. (f-g) Schottky barrier modulation associated with the filament formation mechanism in a GaSe memtransistor (top) leading to I<sub>D</sub>-V<sub>D</sub> characteristics (bottom) with gate-tunable resistive switching. Reproduced with permission.<sup>[120]</sup> Copyright 2019, Elsevier.

### 3.1. *MoS<sub>2</sub> Memtransistors*

Resistive switching in bulk materials relies on vacancy or ion migration to modulate the Schottky barrier height or to form and rupture conductive filaments in memristors. Using 2D materials, this mode of resistive switching has also been achieved in thin vertical memristors and atomristors.<sup>[41, 43, 121, 122]</sup> Although some control over device characteristics can be realized with thickness and stoichiometry control, these two-terminal memristors achieve essentially the same NVM synaptic functions as conventional metal-oxide memristors, and have limited gate tunability due to the vertical structure that results in strong screening by the electrodes.<sup>[43, 123, 124]</sup> In contrast, planar memristive behavior in 2D semiconductors was first demonstrated using polycrystalline, sulfur-deficient MoS<sub>2</sub> grown by chemical vapor deposition (CVD), where the planar geometry enabled strong gate tunability.<sup>[125]</sup> Different types of switching behaviors were observed for different grain boundary topologies, and the sulfur-deficient stoichiometry was found to be essential for resistive switching. The MoS<sub>2</sub> memtransistor response was then made considerably more reproducible by employing multiple grain boundaries in the channel to avoid the discrete dependence on single grain boundary topologies.<sup>[117, 126]</sup> A diverse range of *in-situ* measurements, such as cryogenic charge transport,<sup>[117]</sup> electrostatic force microscopy (EFM),<sup>[117, 125, 126]</sup> Auger electron spectroscopy,<sup>[127]</sup> and Kelvin probe force microscopy (KPFM),<sup>[127]</sup> have provided further insight into the underlying switching mechanism, consistently implicating lateral field-driven defect motion. At a device level, resistive switching in polycrystalline MoS<sub>2</sub> with Ti/Au contacts originates from modification of the Schottky injection<sup>[127]</sup> in a manner analogous to certain interface switching mechanisms in bulk memristors (**Figure 4a**). It should be noted that the Schottky injection can be modulated by defect migration and/or charge trapping at MoS<sub>2</sub> grain boundaries or neighboring dielectrics, and charge trapping has also been used to demonstrate gate-tunable memristive behavior.<sup>[128]</sup>

Measuring the  $I_D$ - $V_D$  characteristics at different gate biases reveals the gate-tunable nature of the memristive switching, where each resistance state is non-volatile (Figure 4b). At gate biases lower than the threshold voltage, a positive bias at the drain switches the device from a high-resistance state (HRS) to a low-resistance state (LRS), whereas a negative bias switches from LRS to HRS, signifying bipolar resistive switching. Varying the gate voltage not only modulates the current level and switching ratio ( $I_{LRS}/I_{HRS}$ ) but can also qualitatively change the switching behavior such as inverting the switching direction of the resistance state at high positive gate bias<sup>[115]</sup> (Figure 4a). These initial  $\text{MoS}_2$  memtransistors showed tunable synaptic behavior in long-term potentiation and depression, multi-state memory, and indirect spike-timing-dependent plasticity, albeit at relatively high voltages due to the large device dimensions.<sup>[52, 115, 129]</sup> More recently demonstrated  $\text{MoS}_2$  memtransistors with smaller grain sizes (1-3  $\mu\text{m}$ ) and thinner (20 nm) high-k gate dielectrics operate at substantially lower voltages (< 1V) and powers ( $\sim$ 20 fJ), and recent work suggests that the operating voltage and switching speed of  $\text{MoS}_2$  memtransistors can be further scaled with smaller channel lengths.<sup>[52, 130]</sup> The planar nature of memtransistors also opens the possibility for surface functionalization. For example, a  $\text{Nb}_2\text{O}_5$  interfacial layer between the  $\text{MoS}_2$  channel and the  $\text{Al}_2\text{O}_3$  gate dielectric was used to create a larger Schottky barrier, resulting in improved linearity and an increased number (>200) of distinct conductance states.<sup>[131]</sup>

In 2D memtransistors, the open planar geometry in conjunction with spatially localized switching has been used to demonstrate novel forms of heterosynaptic plasticity through the integration of additional terminals on the 2D channel.<sup>[117, 132]</sup> Similarly, shared terminals to multiple  $\text{MoS}_2$  memtransistors<sup>[127]</sup> can achieve symmetric heterosynaptic plasticity. The semiconducting nature of the  $\text{MoS}_2$  channel also lends itself to additional gating schemes that have not been explored in previous oxide-based memory devices. For example, photo-induced modulation of the Schottky injection increases the switching ratio by two orders of magnitude beyond what has been achieved using only electrostatic gating.<sup>[133]</sup> Optical illumination can further provide concomitant and

This article is protected by copyright. All rights reserved.

independent short-term and long-term plasticity in  $\text{MoS}_2$  memtransistors, where photons act as additional synaptic inputs with only short-term memory.<sup>[134]</sup> Triple-gated  $\text{MoS}_2$  memtransistors based on electrical, optical, and ionic liquid gates have further revealed diverse synaptic behaviors such as reverse and anti-Hebbian STDP, metaplasticity, and homeostatic regulation.<sup>[135]</sup> In general, the 2D nature of memtransistors allows diversification of the input signals and memory mechanism, which is useful for implementing more complex bio-realistic functions.

### 3.2. Ferroelectrics

Schottky-barrier-based resistive switching has also been realized in 2D materials without vacancy or ion migration by using the van der Waals  $\alpha\text{-In}_2\text{Se}_3$  semiconductor as a ferroelectric channel.<sup>[118, 136, 137]</sup> In lateral  $\alpha\text{-In}_2\text{Se}_3$  devices, the in-plane polarization switching of the ferroelectric domains is controlled via the drain voltage, resulting in modulation of the Schottky injection (Figure 4c). In these optoelectronically-active devices, the ferroelectric switching is largely decoupled from photogenerated electron-hole pairs, enabling the read current to be either the dark current or the photocurrent (Figure 4d). Furthermore, in the case of thin flakes, drain-induced ferroelectric switching can be additionally modulated using the field effect of the gate electrode. In other words, electrostatic gating can be used to directly switch the in-plane polarization (IP) via coupling with the gate-switchable out-of-plane polarization (OOP). This coupling between IP and OOP polarization enables multi-terminal heterosynaptic plasticity that can be generalized to other ferroelectric van der Waals materials. Although many ferroelectric switching channel devices suffer from incomplete polarization, this issue can be mitigated for 2D ferroelectric semiconductors since they allow dual gating schemes that provide stronger electrostatic control.<sup>[138]</sup> For example, applying pulses at additional modulatory terminals has been shown to increase the switching ratio of  $\alpha\text{-In}_2\text{Se}_3$  memtransistors by over an order of magnitude.<sup>[137]</sup> Although these devices suffer from poor

This article is protected by copyright. All rights reserved.

switching speed ( $\sim$ seconds) due to the need for in-plane polarization switching and relatively large ( $\sim 1\mu\text{m}$ ) device channel lengths, ferroelectric resistive switching materials are intrinsically capable of much faster switching speeds ( $\sim 10$  ns) due to low levels of atomic displacement.<sup>[139]</sup>

### 3.3. Ion and Vacancy Migration

The general concept of gate-tunable memristive switching has also been explored beyond the van der Waals material family. For example, Schottky barrier tuning based on hydrogen ion migration has been exploited for gate-tunable memristive behavior in zinc oxide thin films.<sup>[140]</sup> In addition to interface-mediated mechanisms that typically exhibit soft switching, filament-based hard-switching has also been explored in memtransistor designs. In particular, methylammonium lead iodide ( $\text{MAPbI}_3$ ) perovskite memtransistors have shown gate-tunable resistive switching behavior.<sup>[141, 142]</sup> Memristive behavior in  $\text{MAPbI}_3$  is driven by the migration of  $\text{I}^-$  vacancies that form conductive channels, thus exploiting what is usually a degrading ion migration effect in photovoltaic applications.<sup>[143]</sup> Similar to 2D material-based memtransistors, light can be used as an additional input with these devices typically displaying photoinduced carrier and ion migration.<sup>[142]</sup> Gate-tunable filamentary switching has also been demonstrated in memtransistors based on GaSe nanosheets.<sup>[120]</sup> In GaSe memtransistors, a positive drain voltage bias leads to migration of  $\text{Se}^{2-}$  ions to the drain contact, inducing the formation of a conductive filament consisting of p-type Ga vacancies, which can then be broken by reversing the voltage direction (Figure 4e). Unlike  $\text{MoS}_2$  memtransistors, the I-V characteristics of GaSe memtransistors exhibit prototypical hard-switching behavior that involves an abrupt increase in current (to LRS) after passing a SET voltage, and a similarly abrupt decrease in current (to HRS) after passing a RESET voltage in the reverse direction (Figure 4f). In this case, the effect of the gate voltage is to tune the SET/RESET voltages while also modulating the readout (drain) current by a factor of 100 through field-effect gating of the channel.

This article is protected by copyright. All rights reserved.

Gate tunability of the switching voltage threshold has also been achieved in  $\text{TiO}_x$  memristors<sup>[144]</sup> and  $\text{Cu}_{2-\alpha}\text{S}$  memristors, but with weaker field-effect modulation.<sup>[145, 146]</sup> These examples illustrate that thinner materials provide the most effective gate modulation by allowing for independent control over the volatile channel conductance states and non-volatile memristive states. As the size of the neuromorphic memtransistor circuits increases, the requirement for low off-current becomes more stringent,<sup>[77]</sup> suggesting that larger bandgap 2D semiconductors with larger resistive switching ratios will be required.

### 3.4. Phase-Change Materials and Other Mechanisms

Another class of memristive devices involves a phase change such as a metal-to-insulator (MIT) transition or a current-induced crystal phase change. For example, vanadium oxide undergoes a Mott MIT transition at 341 K that can be stimulated electrically or thermally (Figure 4g).<sup>[119]</sup> Polycrystalline  $\text{VO}_2$  thin films have been used for low-power memtransistors, where the MIT-based resistive switching is sharply tuned with only a small gate voltage bias of 1 V (Figure 4h). This system also exhibits significantly faster switching speeds (35 ns) compared to other memtransistors of comparable channel length, since switching does not rely on atom or charge migration. However, while the transition from insulator to metal in  $\text{VO}_2$  can theoretically be achieved with even faster switching speeds (< 1 ps), the relaxation back to the insulating state has so far been limited to tens of nanoseconds.<sup>[147]</sup> Additionally, the switching behavior in  $\text{VO}_2$  memtransistors is especially complicated due to the intermixing of the dielectric and the channel materials that leads to the formation of a  $\text{VSiO}_x$  interlayer. Recently, dual-gated phase-change memory (PCM) memtransistors have also been demonstrated,<sup>[116]</sup> where the gate voltage was not used to tune the switching ratio, but instead to introduce short-term plasticity for sequential learning and homeostatic regulation.

Finally, organic and polymer-based memtransistors have been realized based on UV-gated charge trapping<sup>[148]</sup> and ion exchange.<sup>[149]</sup>

### 3.5. Van der Waals Heterojunctions

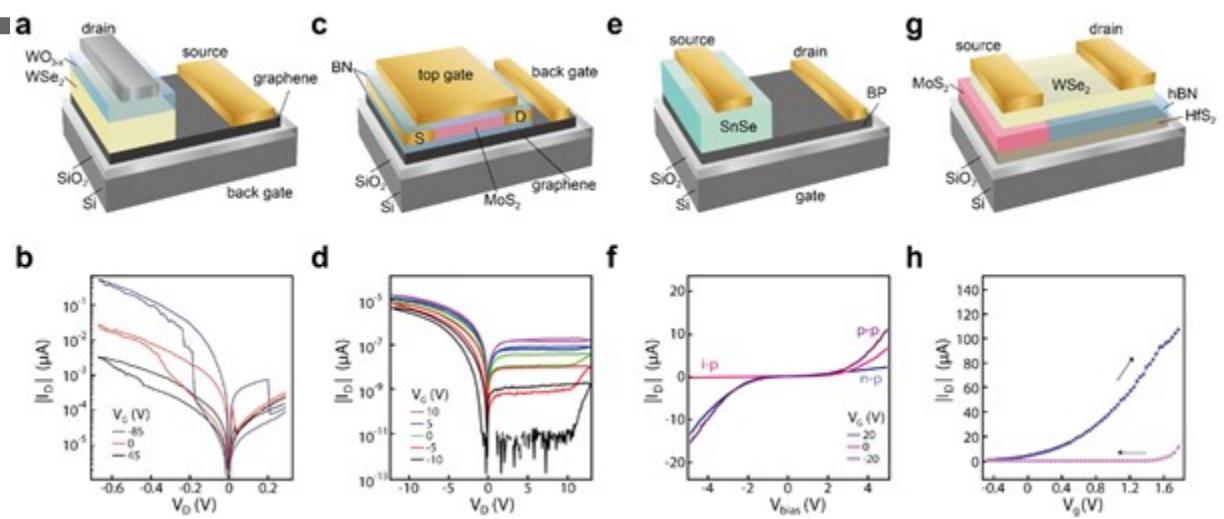

The ability of 2D materials to form diverse heterostructures through van der Waals bonding enables heterojunction memtransistors, especially those based on barrier-type mechanisms. **Figure 5a** shows a vertical device based on graphene/WSe<sub>2</sub>/WO<sub>3-x</sub> exhibiting gate-tunable resistive switching (Figure 5b) via electrostatic control of the graphene/WSe<sub>2</sub> Schottky barrier height.<sup>[150]</sup> Due to its similarity to a graphene-silicon barristor<sup>[151]</sup>, this device can be viewed as an integrated barristor and oxide memristor. Although the gate does not directly interact with the channel, gate-modulated synaptic learning is achieved by controlling the relative distribution of fields at the interface, which is determined by the gate-controlled Fermi level in the graphene layer. Similar concepts have also been shown in graphene/ReSe<sub>2</sub> heterojunctions,<sup>[152]</sup> graphene/InN nanowires,<sup>[153]</sup> and hBN/graphene/MoS<sub>2</sub> heterojunctions.<sup>[154]</sup> Volatile reconfigurable synaptic devices have further been explored in BP/SnSe heterojunctions (Figure 5c) that are capable of excitatory or inhibitory synaptic behavior depending on the electrostatically controlled configuration of the junction (Figure 5d).<sup>[155]</sup> Beyond Schottky barrier control, van der Waals heterojunctions also can be used to engineer well-defined charge-trapping interfaces, such as those found in floating-gate synaptic transistors.<sup>[80-82]</sup> Recent work has further shown that floating-gate van der Waals heterojunctions can achieve ultrafast (10 ns) writing with moderate (10 s) refresh times (Figure 5e-f).<sup>[79]</sup> Since carefully designed flash memory devices with lateral offsets are capable of programming, erasing, and reading with only two terminals, a third gate terminal can then be used for modulatory purposes. For example, Figure 5g-h shows a MoS<sub>2</sub>/hBN flash memory device with gate-tunable memristive hysteresis.<sup>[156]</sup> These devices possess fast writing (~50 ns) and non-volatile memory in addition to improved training

for pattern recognition via gate-tunable learning. A summary of device metrics for demonstrated memtransistor devices is provided in **Table 1**.

**Figure 5. Device architectures and I-V characteristics of van der Waals heterojunction memtransistors and related devices.** (a-b)  $\text{WO}_{3-x}/\text{WSe}_2/\text{graphene}$  synaptic barristor (top) showing gate tunable memristive characteristics (bottom) based on Schottky barrier modulation. Adapted with permission.<sup>[150]</sup> Copyright 2018, Wiley. (c-d) Schematic of a  $\text{MoS}_2/\text{hBN}$  van der Waals heterojunction (top) that shows bottom gate-tunable  $I_D-V_D$  characteristics (bottom) of a memtransistor. An additional top floating gate was used to strongly modulate the switching behavior to achieve heterosynaptic functionality. Adapted with permission.<sup>[156]</sup> Copyright 2020, American Chemical Society. (e-f) Schematic (top) and I-V characteristics (bottom) of a bottom-gated BP-SnSe heterojunction artificial synapse. The heterojunction can be reconfigured between p-p, i-p, and n-p junctions based on the gate voltage bias, allowing for a highly tunable synaptic response. Adapted with permission.<sup>[155]</sup> Copyright 2017, American Chemical Society. (g-h)  $\text{MoS}_2$  semi-floating-gate van der Waals memory device with ultrafast writing time (100 ns) and long refresh time (10 s), and transfer curves in the on (blue) and off (purple) states. Adapted with permission.<sup>[79]</sup> Copyright 2018, Springer Nature.

**Table 1: Summary of Device Metrics for Demonstrated Memtransistor Devices**

| Channel Material                              | Dielectric Material                                            | Proposed Mechanism | Operating Voltage (V) | Switching Ratio | Conductance States | Endurance | Retention (min)* | Switching Energy (J)  | Speed (s)            | Ref   |

|-----------------------------------------------|----------------------------------------------------------------|--------------------|-----------------------|-----------------|--------------------|-----------|------------------|-----------------------|----------------------|-------|

| MoS <sub>2</sub>                              | SiO <sub>2</sub>                                               | Schottky           | 40                    | ~100            | >11                | >500      | >1500            | ~3×10 <sup>-9</sup>   | 10 <sup>-3</sup>     | [117] |

| MoS <sub>2</sub>                              | Nb <sub>2</sub> O <sub>5</sub> /Al <sub>2</sub> O <sub>3</sub> | Schottky           | 10                    | ~40             | >200               | >200      | >16              | ~6×10 <sup>-12</sup>  | 10 <sup>-2</sup>     | [131] |

| MoS <sub>2</sub>                              | Al <sub>2</sub> O <sub>3</sub>                                 | Schottky           | 0.5                   | ~5000           | >100               | >150      | >800             | ~2×10 <sup>-14</sup>  | 10 <sup>-2</sup>     | [130] |

| α-In <sub>2</sub> Se <sub>3</sub>             | SiO <sub>2</sub>                                               | Ferroelectric      | 4                     | ~100            | 2                  | >40       | >15              | ~8×10 <sup>-7</sup>   | 4                    | [118] |

| α-In <sub>2</sub> Se <sub>3</sub>             | SiO <sub>2</sub>                                               | Ferroelectric      | 4                     | ~5000           | 6                  | >1000     | >3000            | ~8×10 <sup>-10</sup>  | 2                    | [137] |

| GaSe                                          | SiO <sub>2</sub>                                               | Filamentary        | 1.5                   | ~1000           | 2                  | >5000     | >160             | ~1.5×10 <sup>-5</sup> | 10 <sup>-1</sup>     | [120] |

| MAPbI <sub>3</sub>                            | Al <sub>2</sub> O <sub>3</sub>                                 | Filamentary        | 5                     | ~100            | 2                  | >1000     | >160             | ~5×10 <sup>-9</sup>   | 10 <sup>-2</sup>     | [141] |

| VO <sub>2</sub>                               | VSiO <sub>x</sub> /SiO <sub>2</sub>                            | Mott MIT           | 0.5                   | ~3              | >20                | >6000     | >500             | ~2×10 <sup>-13</sup>  | 3.5×10 <sup>-8</sup> | [119] |

| Pentacene                                     | PVN/ SiO <sub>2</sub>                                          | Charge trapping    | 10                    | ~5000           | >50                | N/A       | >16              | ~4×10 <sup>-5</sup>   | 2×10 <sup>-6</sup>   | [148] |

| Graphene/ WSe <sub>2</sub> /WO <sub>3-x</sub> | SiO <sub>2</sub>                                               | Schottky           | 1                     | ~100            | >30                | >1000     | >16              | ~10 <sup>-10</sup>    | 10 <sup>-2</sup>     | [150] |

| hBN/ graphene /MoS <sub>2</sub>               | SiO <sub>2</sub>                                               | Filamentary        | 8                     | ~5000           | 10                 | >50       | N/A              | N/A                   | N/A                  | [154] |

| Graphene/ ReSe <sub>2</sub>                   | SiO <sub>2</sub>                                               | Filamentary        | 4                     | ~10000          | >5                 | >250      | >160             | N/A                   | N/A                  | [152] |

| MoS <sub>2</sub>                              | SiO <sub>2</sub>                                               | Charge trapping    | 12                    | ~100            | >30                | >500      | >16              | 7.3×10 <sup>-15</sup> | 5×10 <sup>-8</sup>   | [156] |

\*The listed retention times and endurance are experimentally demonstrated. Device retention times can be extrapolated from the experimental data, and are often significantly longer (~few years).

## 4. Integration into Neuromorphic Circuits and Systems

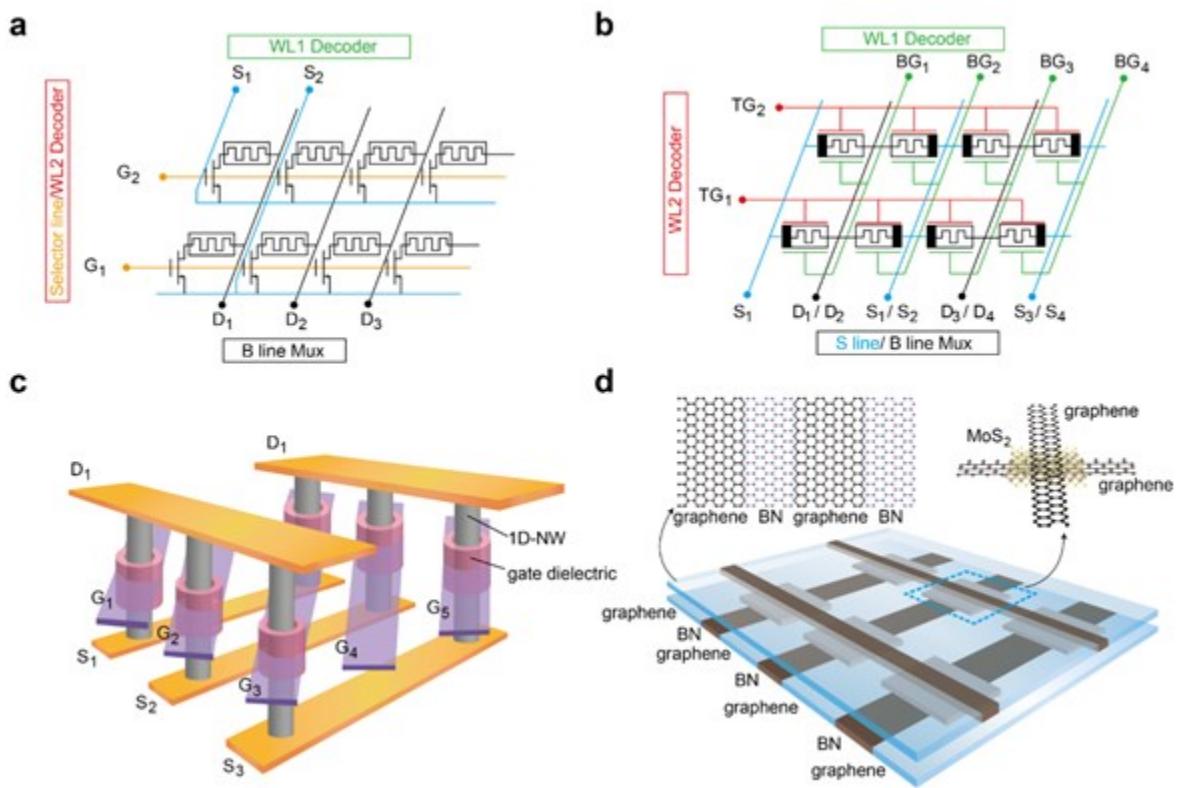

**Figure 6. Crossbar integration strategies for memtransistors and related memristive systems. (a)**

Schematic of a traditional one-transistor-one-memristor (1T1M) crossbar array where a transistor at each node minimizes the sneak current between neighboring memristors. Reproduced with permission.<sup>[115]</sup> Copyright 2020, Wiley. (b) Schematic of the dual-gated memtransistor crossbar array where an additional transistor is not needed. Reproduced with permission.<sup>[115]</sup> Copyright 2020, Wiley. (c) Schematic of a proposed gate-all-around vertical nanowire memtransistor crossbar array. High device density with strong electrostatic control can be realized in this geometry. (d) Schematic of an all-2D graphene/MoS<sub>2</sub>/graphene crossbar array using lateral stitching based on a bottom-up growth technique.

Two-terminal memristor-based crossbar arrays are widely employed for in-memory computing due to their small footprint, low power, and design simplicity.<sup>[58]</sup> The memristor crossbar paradigm has been explored extensively for neuromorphic computing algorithms that require high parallelism including vector-matrix multiplication for ANNs, SNNs, and CNNs.<sup>[40, 58]</sup> **Figure 6a** shows a typical crossbar array architecture using a 1T1M configuration, where the transistor serves as a switch to minimize the sneak current and crosstalk between neighboring memristors.<sup>[115]</sup> However, while the simplicity of two-terminal memristors is desirable for scaling reasons, it also results in certain intrinsic limitations. In particular, when using passive NVM in crossbar arrays, each node needs to be individually addressed to minimize the crosstalk and sneak-path current between the neighboring nodes during the read and write operations.<sup>[157]</sup> Typically, this addressability constraint requires an additional electrical component at each node. For example, in the one-selector-one-memristor (1S1M) design, the selector is a diode, a threshold switch, or an intrinsic Schottky barrier built within the memristor.<sup>[59, 158]</sup> However, the sneak current in the 1S1M scheme still scales with crossbar array size, and special biasing protocols are needed to access individual nodes. Alternatively, each node can be integrated with a transistor<sup>[77]</sup> in a one-transistor-one-memristor (1T1M) design, resulting in a reduced sneak current that is determined by the off-current of the transistor.<sup>[159]</sup> Overall, 1T1M designs lead to increased footprint and complexity due to the integration of two disparate technologies.

Compared to memristors, memtransistors possess an intrinsic selector, but the additional terminals also present integration challenges. Some early efforts have already begun to integrate memtransistors into crossbar arrays at the hardware level. For example, Lee *et al.* demonstrated a 10 x 9 crossbar array (Figure 6b) using dual-gated four-terminal MoS<sub>2</sub> memtransistors as a synaptic element, where a symmetric and linear weight update rule was achieved by gate-tunable learning.<sup>[115]</sup> Dual gating also allows two desired functions simultaneously: (1) sneak current suppression using one of the gates in a manner similar to the 1T1M architecture; (2) gradual tuning

This article is protected by copyright. All rights reserved.

of the long-term potentiation behavior by the second gate. This control of synaptic learning enables *in-situ* modification of weight update rules during training in dynamical neural networks. In addition, while a large Schottky barrier in memtransistors in the sub-threshold regime enables a wide dynamic range of synaptic learning,<sup>[115]</sup> a small Schottky barrier makes the resistive switching direction more sensitive to the gate voltage bias. This latter principle was utilized by Yuan *et al.* for memtransistors using MoS<sub>2</sub> grown by chemical vapor deposition on sapphire substrates. In this case, tuning the gate voltage allowed for switching between LTP and LTD responses without changing the polarity of drain bias pulses in a manner that is analogous to biological systems. The shapes of the LTP and LTD learning curves were further varied from sub-linear to super-linear curves by using time-varying pulsing schemes, thus enabling the SNNs to demonstrate continuous learning.<sup>[160]</sup> Feng *et al.* have also demonstrated a single-gated 10 x 10 memtransistor crossbar array for ANN applications while achieving a record switching energy (20 fJ/bit) and operating voltage (0.42 V) through careful grain boundary engineering and device scaling.<sup>[130]</sup> Their architecture uses a shared-drain (bit line) layout to achieve a cell size of 4.5 F<sup>2</sup> (F = 4λ = minimum half-pitch), which compares favorably to 1M (4 F<sup>2</sup>) and 1T1M (7 F<sup>2</sup>) structures. These authors further hypothesized that the use of an overlapping source line could further reduce the cell footprint to 3 F<sup>2</sup>. While memtransistor crossbars have thus far been limited to small-scale demonstrations, these proof-of-concept studies suggest that there are no fundamental barriers to wafer-scale implementation.

Novel crossbar array architectures also hold promise for realizing the scalable integration of memtransistors. Figure 6c shows a crossbar array composed of one-dimensional (1D) memtransistors that consists of etched mesas of bulk memristive materials, or organic/inorganic nanowires. GAA structures in 1D and vertical memtransistors are advantageous over other gating schemes because the strong electrostatic control of the 1D channel results in high current densities. The vertical orientation also allows for overlapping word/bit and selector lines, further improving lateral scalability. Figure 6d shows another potential crossbar array, this time realized using 2D

This article is protected by copyright. All rights reserved.

materials that are grown and integrated via a bottom-up approach. Recently, different combinations of 2D materials including semiconductors, insulators, and semimetals have been grown and stitched together either with covalent bonds or by using overlapping van der Waals gaps in the lateral plane.<sup>[161-164]</sup> With the small lattice mismatch between hBN and graphene (1.7%), purely 2D lateral growth of hBN-graphene heterostructures has also been reported,<sup>[165-168]</sup> which could potentially enable all-2D integrated memtransistors. In this scheme, a “stripe-by-stripe” hBN-graphene superlattice would serve as the contact layer for a crossbar array based on 2D materials. The switching layer consists of an array of the 2D mesa, which can be precisely patterned from a single monolayer 2D sheet. An all-2D crossbar array of memtransistors built with bottom-up growth and transfer techniques has the potential to incorporate both vertical and lateral heterostructures while providing ultimate scalability.

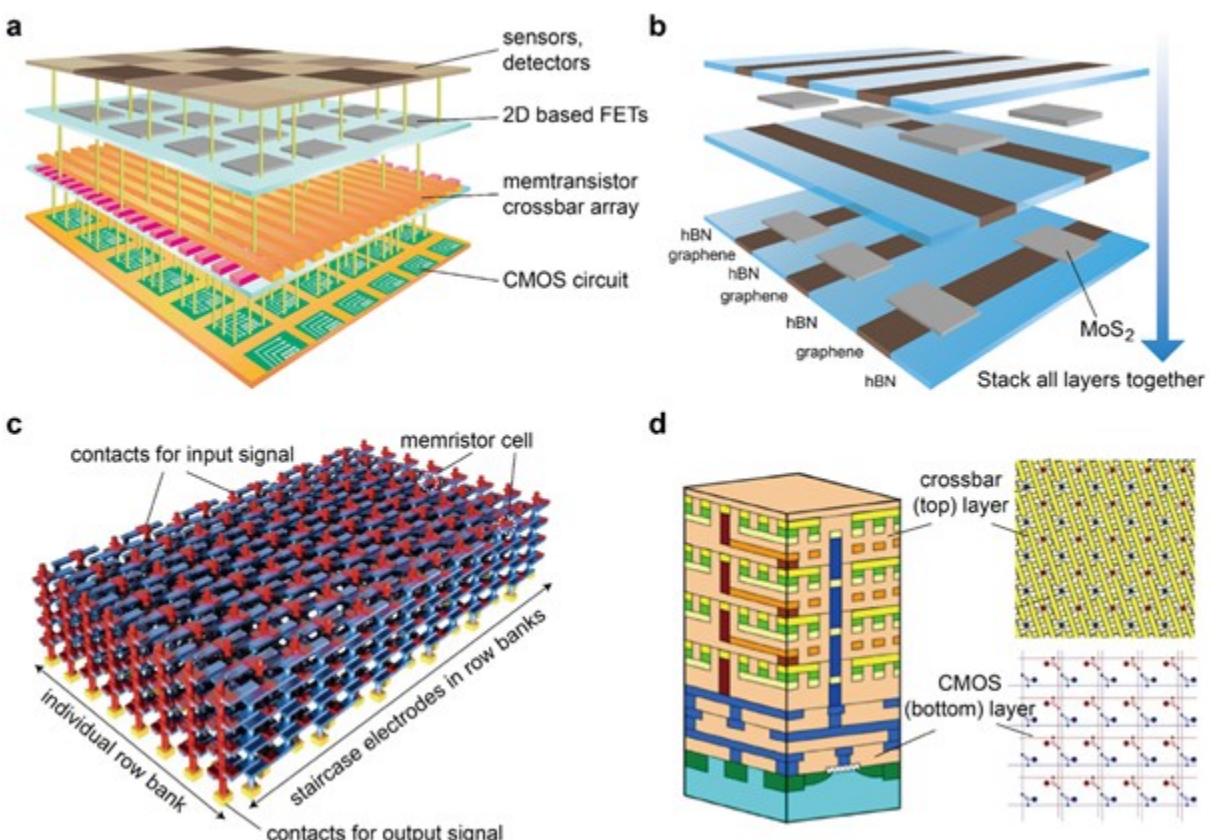

These all-2D arrays are of high interest due to their many desirable properties, including atomic thickness, pristine interfaces, high in-plane thermal conductivity, and a wide range of controllable bandgaps. These properties make them ideal candidates for building three-dimensional (3D) circuits.<sup>[169]</sup> For 3D integration, mobility degradation restricts the vertical scaling limit of bulk channel materials such as Si and GaN, whereas 2D materials retain high mobilities at ultra-thin thicknesses.<sup>[169]</sup> 3D integration using stacked memory and computing has been explored for neuromorphic computing,<sup>[26]</sup> and memtransistors as crossbar elements in this context are particularly promising since 1T1M designs are difficult to scalably integrate in a 3D manner.<sup>[60]</sup> **Figure 7a** illustrates a schematic of this concept in which multiple computing and memory elements, including CMOS circuitry, FETs, memtransistor crossbar arrays, sensors, and photodetectors, can be stacked. Such 3D integrated circuits have been experimentally demonstrated by Shulaker *et al.* using CMOS devices, conventional memristors, and CNT thin-film transistor (TFT) sensors.<sup>[53]</sup> These circuit architectures take advantage of the high bandwidth and dense interconnections enabled by 3D integration to create a computing ecosystem that is capable of massive data collection, local data

This article is protected by copyright. All rights reserved.

storage, in-memory computing, analog-to-digital data conversion, and fast weight update speed. Figure 7b illustrates a stacking scheme using an all-2D memtransistor crossbar (Figure 6d) to form a 3D integrated circuit. Due to the high vertical integration density, stacking 2D material memtransistor crossbars has the potential to achieve exceptionally high overall integration density, which partly compensates for the inherently larger footprint of lateral memtransistors compared to vertical memristors. Besides achieving high device density, carefully tailored 3D designs can be used for other purposes such as networks with high interconnectivity. For example, Figure 7c shows a staircase-like stacking of conventional oxide memristors that is purposely designed for parallel kernel operations in a CNN that are too complex to be realized in simple crossbar arrays.<sup>[170]</sup> Since selection devices are challenging to integrate into 3D designs, this architecture relies on stacking mismatch to reduce the sneak current by minimizing the overlap of the shared electrodes among devices.

One issue with 3D integration is that high-density vertical interconnects not only increase perturbations in accessing individual nodes but also degrade the bandwidth and speed of data communication. To prevent these deleterious effects while maintaining a high density of memristive devices, Strukov *et al.*<sup>[171]</sup> demonstrated a CMOS and crossbar integrated 3D system (Figure 7d, left plot), where each device in a rotated crossbar array is uniquely connected to two vias (blue and red dots in the right plots of Figure 7d represent two vias from the lower and upper wire levels). The rotation of crossbars provides a multiplicative factor that allows the high-density crossbars to be addressed by CMOS circuitry built at a larger lithographic scale. A similar scheme can be used to stack layers of 2D memtransistors, enabling high bandwidth and low communication latency between memtransistor and CMOS platforms without sacrificing high device density.

Integrating memtransistors in three-dimensional (3D) circuits can also enable additional data communication channels in the vertical direction for feedback loops and control lines between

different layers of neural networks<sup>[53, 171]</sup>. For example, Shulaker *et al.* deposited thin inter-layer dielectrics followed by etching and filling to fabricate high-density metal interlayer vias (2  $\mu\text{m}$  pitch) that connected CNT sensing and logic with an RRAM crossbar array. Similar high-density interconnects could be used in a memtransistor crossbar array for *in-situ* rewiring of the gate terminal. One possibility is to use the gate terminal to implement evolving synaptic connectivity patterns into the hardware so that both synaptic learning and neural connectivity can be tailored to realize desired neuromorphic functions. This strategy is analogous to the continuous topographic mapping architectures and recurrent loop architectures that are common in biological neural models such as the mammalian visual system.<sup>[172]</sup> In general, the addition of the gate terminal increases the number of state variables available without sacrificing the capability of 3D integration. Consequently, memtransistors are ideally suited for exploring hardware implementations of highly interconnected neural networks that underlie complex bio-realistic synaptic behavior.

**Figure 7. Three-dimensional integration strategies for memtransistors and related memristive systems.** (a) Schematic of a proposed 3D integration of memtransistor crossbar arrays with other semiconductor technologies including sensors and CMOS digital circuits. Adapted with permission.<sup>[53]</sup> Copyright 2017, Springer Nature. (b) Schematic showing 3D stacking of an all-2D memtransistor crossbar array. (c) Schematic of 3D circuits composed of high-density staircase output electrodes (blue) and pillar input electrodes (red). Reproduced with permission.<sup>[170]</sup> Copyright 2020, Springer Nature. (d) Schematic of a 4D address topology for circuits with stacked multi-layer crossbar arrays. Reproduced with permission.<sup>[171]</sup> Copyright 2009, National Academy of Sciences.

## 5. Remaining Challenges and Future Outlook

This article is protected by copyright. All rights reserved.

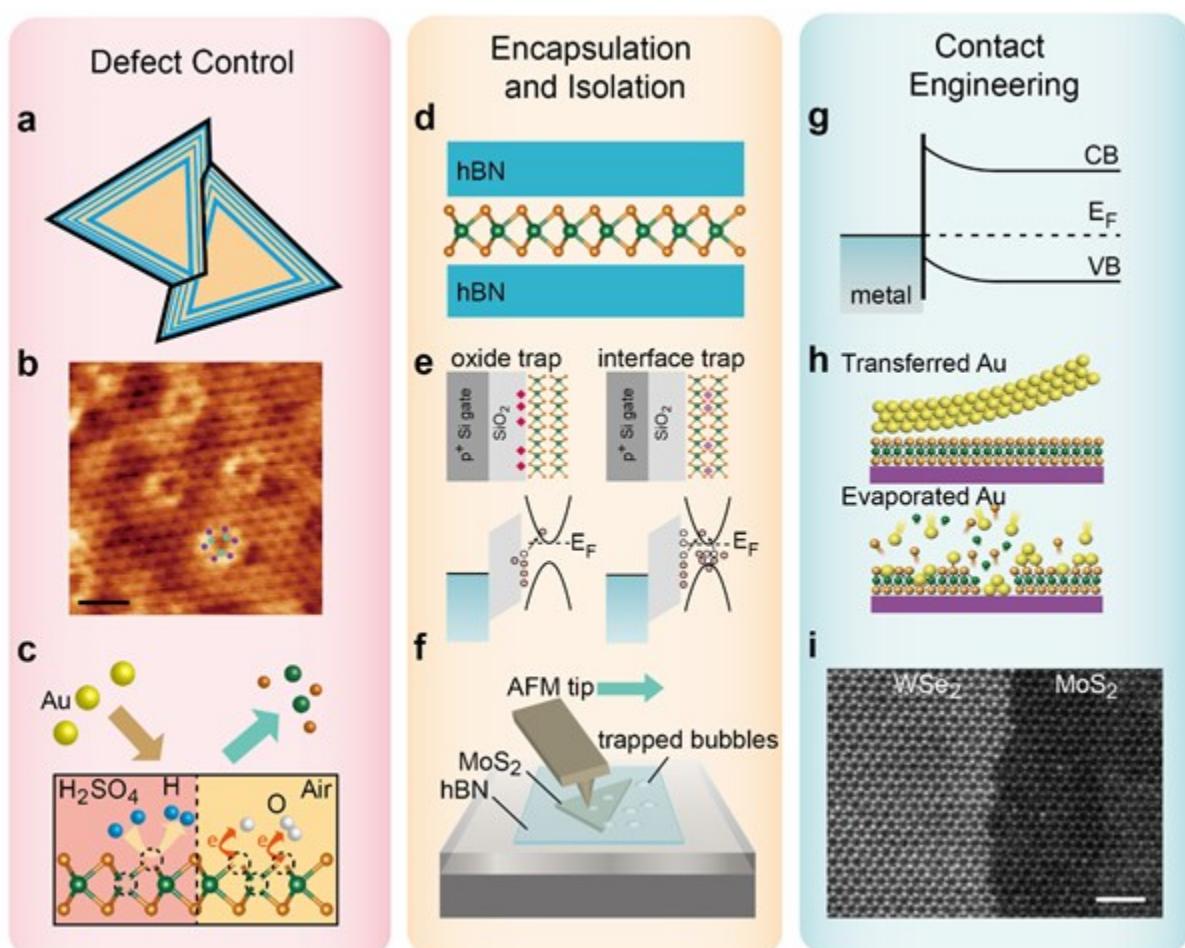

**Figure 8. Remaining challenges and future outlook for memtransistors in neuromorphic circuits and systems.** (a) Schematic showing grain boundary formation in monolayer MoS<sub>2</sub> during CVD. Reproduced with permission.<sup>[173]</sup> Copyright 2015, Wiley. (b) Scanning tunneling microscopy (STM) image of a single sulfur vacancy in monolayer MoS<sub>2</sub>. The scale bar is 1 nm. Light blue dots represent Mo atoms and purple dots represent S atoms. Reproduced with permission.<sup>[174]</sup> Copyright 2020, Springer Nature. (c) Methods for defect engineering MoS<sub>2</sub> include ion irradiation, chemical modification, and annealing. Reproduced with permission.<sup>[175]</sup> Copyright 2018, American Chemical Society. (d) Schematic showing hBN encapsulation of monolayer MoS<sub>2</sub>. Reproduced with permission.<sup>[176]</sup> Copyright 2019, American Chemical Society. (e) Charge trapping and other mechanisms of hysteretic memory in gated MoS<sub>2</sub> devices.<sup>[177]</sup> (f) Nano-Squeegee for forming clean van der Waals interfaces using contact-mode atomic force microscopy. Adapted with permission.<sup>[178]</sup> Copyright 2018, American Chemical Society. (g) Schematic showing the Schottky barrier formation between metal electrodes and semiconductors with memristive properties.<sup>[179]</sup> (h) Schematic of transferred versus evaporated contacts for 2D materials showing pristine atomic surface and degraded surface, respectively. Reproduced with permission.<sup>[180]</sup> Copyright 2018, Springer Nature. (i) Schematic showing the lateral stitching growth for a lateral WSe<sub>2</sub>-MoS<sub>2</sub> heterojunction. A single 2D layer with metallic and semiconducting materials stitched together may allow greater electrostatic control of the tunable Schottky barrier in dual-gated architectures. Reproduced with permission.<sup>[161]</sup> Copyright 2015, American Association for the Advancement of Science.

In this Perspective, recent progress has been surveyed for memtransistors as building blocks for neuromorphic hardware applications. In addition, related devices with tunable NVM states were delineated including floating-gate memristive systems and phase-change devices. For synaptic applications, high endurance and retention are required due to repeated readout during inference.

This article is protected by copyright. All rights reserved.

Large dynamic ranges with low noise and fast switching speeds are necessary due to the large number of weight updates performed during training. A large dynamic range is also beneficial for achieving a large number of continuous, multi-level states, and for reducing the effect of device-to-device variability and noise. Power consumed during each weight update step is another critical parameter. In particular, lower operating voltages and write times during the weight update and low readout currents during inference are desirable to minimize energy consumption. Furthermore, especially for non-filamentary devices, tradeoffs exist between the programming voltage and other performance metrics (e.g., higher voltage enables a larger dynamic range and faster switching speed) that can be tailored specifically to desired applications. While neural networks are fairly robust against variation due to the large number of connections present, excessive stochasticity will lead to degraded network performance, thus motivating efforts to improve device-to-device uniformity. Although the existing literature on memtransistors is still largely in the exploratory phase, initial reports on disparate materials systems including polycrystalline monolayers, ferroelectric  $\alpha$ -InSe, Mott materials, van der Waals heterojunctions, and Schottky-barrier-based 2D memtransistors have already shown significant improvements in key performance metrics. In particular, for Schottky-barrier-dependent  $\text{MoS}_2$  memtransistors, scaling down channel lengths and using high- $k$  dielectrics resulted in significantly improved device operating voltage and switching ratio.<sup>[130]</sup> Detailed characterization and optimization of these memtransistor systems will help further understand and improve device metrics and uniformity.

Advances in 2D material growth and defect control will facilitate the implementation of memtransistors into wafer-scale architectures. Early  $\text{MoS}_2$  memtransistors have relied on randomly oriented grain boundaries, which presents challenges for device scaling. While the majority of existing growth efforts have focused on wafer-scale growth of 2D materials with large grain sizes for traditional electronics and optoelectronics, memtransistors that exploit grain boundaries<sup>[173, 181, 182]</sup> and sub-stoichiometric defects<sup>[174, 175]</sup> necessitate growth efforts specifically designed to achieve

This article is protected by copyright. All rights reserved.

smaller and uniform grain sizes with controlled stoichiometry (Figure 8a-c). Computational modeling and *in-situ* atomically resolved microscopy of defect dynamics under applied electric fields will also facilitate a better understanding of memtransistor switching mechanisms.<sup>[183]</sup> Studies on helium-beam-modified MoS<sub>2</sub> memtransistors,<sup>[184]</sup> plasma-treated MoS<sub>2</sub> memtransistors,<sup>[185]</sup> and air-treated GaSe memtransistors<sup>[120]</sup> suggest that post-growth defect engineering is also a promising avenue for exploration. Data-driven approaches such as machine learning<sup>[186, 187]</sup> are also likely to aid in the identification of optimal stoichiometries, defect densities, and electrical contacts for high-performance memtransistors. Additionally, ongoing research on the direct growth of lateral van der Waals heterostructures will be highly beneficial for realizing 2D heterojunction-based memtransistors.<sup>[161, 165, 188, 189]</sup> Finally, exploring alternative low-cost synthesis methods based on solution processing, such as MoS<sub>2</sub> percolating networks<sup>[190]</sup> and printed lead halide perovskite memtransistors,<sup>[142]</sup> may be useful for biosensing and wearable electronics. Liquid phase exfoliation of layered materials is also showing promise for spiking neuron applications due to the intrinsic volatile switching behavior originating from thermally activated electrical discharge due to the large curvature at the edges of 2D nanosheets.<sup>[191]</sup> This low voltage (~2 V) switching has been observed in a diverse range of 2D materials (e.g., MoS<sub>2</sub>, WS<sub>2</sub>, ReSe<sub>2</sub>, and InSe) prepared in multiple solvent systems, thus paving a way for additive manufacturing of memristive systems.

In resistive switching devices, multiple competing and interacting memory mechanisms are often at play, and this issue is further compounded in memtransistors due to the complexity introduced by additional gate terminals and dielectric interfaces.<sup>[177]</sup> Therefore, an improved understanding of switching behavior is needed through *in-situ* analyses, simulations, and device modeling.<sup>[192, 193]</sup> At the device level, encapsulation layers,<sup>[176]</sup> interface control,<sup>[178, 194]</sup> and heterostructure assembly<sup>[195]</sup> are particularly useful methods to control the properties of all-surface 2D materials and to engineer heterojunctions (Figure 8d-f). In memtransistors involving Schottky barrier modulation, contact engineering and van der Waals heterojunction formation are also

This article is protected by copyright. All rights reserved.

promising for achieving desired behavior, but have yet to be fully explored (Figure 8g-i).<sup>[179, 196-200]</sup> For 2D materials specifically, emerging schemes of transferred contacts,<sup>[180, 201]</sup> edge contacts,<sup>[202, 203]</sup> and ion-permeable contacts<sup>[204]</sup> can further be explored to enable improved control. Additionally, the use of tunnel barriers and interfacial layers with well-defined charge trapping states can yield gate-controlled Schottky barriers that underlie memtransistor characteristics. Lastly, electric-field-induced or ion-induced phase transitions in 2D materials, such as MoS<sub>2</sub><sup>[132, 205]</sup> and MoTe<sub>2</sub>,<sup>[206-208]</sup> in addition to moiré ferroelectricity in 2D material heterostructures<sup>[209]</sup> are of potential interest as alternative memtransistor switching mechanisms.

Memtransistors also present key challenges and opportunities at the circuit and software levels. High-yield integration of 2D materials with existing fabrication technology remains an ongoing challenge. Additionally, while extensive research has been conducted on the design and protocols for large-scale memristor-based crossbar arrays,<sup>[58, 159]</sup> memtransistors have been limited to a few small-scale demonstrations. However, compared to conventional memristor circuit architectures like 1T1M crossbar arrays or four-terminal synaptic transistors, three-terminal memtransistors can be scalably incorporated into 3D architectures for ultra-high-density integration. Memtransistors can also be dual-gated, solving the long-standing issues of sneak current in memristor crossbar arrays, while simultaneously enabling tunable learning for dynamical neural networks. Another promising use of memtransistors is to emulate bio-realistic synapses through additional gate tuning,<sup>[116, 160]</sup> such as reconfigurable STDP behavior<sup>[52, 115, 130, 160]</sup> for improved SNN learning.<sup>[210, 211]</sup> Incorporation of long-term memory at the memtransistor gate terminal through ferroelectric dielectrics or charge trapping is also a possibility and would provide a second layer of nonvolatile memory that is independent of the memristive behavior. In general, realizing the full potential of memtransistors for network-level applications will require the exploration of concepts that take full advantage of the high tunability at the device level, such as using multiple state variables for reinforcement learning<sup>[36]</sup> or using gate-terminal tuning to mitigate device variability effects. Ultimately, the diverse

This article is protected by copyright. All rights reserved.

set of potential functionalities in multi-terminal memtransistors, including independently expressed long-term and short-term plasticity,<sup>[212, 213]</sup> heterosynaptic functionality,<sup>[117, 137]</sup> and neuromodulation,<sup>[116]</sup> has the potential to drive neuromorphic computing hardware toward increasing levels of bio-realism that represent the next frontier of artificial intelligence.

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

### **Acknowledgments**

This research was supported by the National Science Foundation Materials Research Science and Engineering Center at Northwestern University (NSF DMR-1720139) in addition to the Laboratory Directed Research and Development Program at Sandia National Laboratories (SNL). SNL is a multi-mission laboratory managed and operated by National Technology and Engineering Solutions of Sandia LLC, a wholly owned subsidiary of Honeywell International Inc. for the U.S. DOE National Nuclear Security Administration under contract DE-NA0003525. This paper describes objective technical results and analysis. Any subjective views or opinions that might be expressed in the paper do not necessarily represent the views of the U.S. DOE or the United States Government.

### **Author Contributions**

X.Y. and J.H.Q. contributed equally to this work. All authors wrote the manuscript and discussed the results at all stages.

### **Conflict of Interest**

The authors declare no conflict of interest.

This article is protected by copyright. All rights reserved.

## ORCID

Xiaodong Yan: 0000-0002-7737-6984

Vinod K. Sangwan: 0000-0002-5623-5285

Mark C. Hersam: 0000-0003-4120-1426

Received: ((will be filled in by the editorial staff))

Revised: ((will be filled in by the editorial staff))

Published online: ((will be filled in by the editorial staff))

## References

- [1] C. A. Mack, *IEEE Transactions on Semiconductor Manufacturing* **2011**, *24*, 202.

- [2] R. S. Williams, *Computing in Science & Engineering* **2017**, *19*, 7.

- [3] Y. Lecun, Y. Bengio, G. Hinton, *Nature* **2015**, *521*, 436.

- [4] I. Goodfellow, Y. Bengio, A. Courville, *Deep Learning*, MIT press, Cambridge, MA **2016**.

- [5] J. Von Neumann, *The Computer and the Brain*, Yale University Press, New Haven, Connecticut **2012**.

- [6] M. A. Zidan, J. P. Strachan, W. D. Lu, *Nature Electronics* **2018**, *1*, 22.

- [7] C. Mead, *Proceedings of the IEEE* **1990**, *78*, 1629.

- [8] M. Bear, B. Connors, M. A. Paradiso, *Neuroscience: Exploring the Brain, Enhanced Edition: Exploring the Brain*, Jones & Bartlett Learning, Burlington, Massachusetts **2020**.

- [9] G.-Q. Bi, M.-M. Poo, *The Journal of Neuroscience* **1998**, *18*, 10464.

- [10] D. O. Hebb, *The Organization of Behavior: A Neuropsychological Theory*, Psychology Press, Hove, East Sussex **2005**.

- [11] A. Rozov, N. Burnashev, B. Sakmann, E. Neher, *The Journal of Physiology* **2001**, *531*, 807.

- [12] H. Markram, *Science* **1997**, *275*, 213.

- [13] A. Morrison, M. Diesmann, W. Gerstner, *Biological Cybernetics* **2008**, *98*, 459.

- [14] C. H. Bailey, M. Giustetto, Y.-Y. Huang, R. D. Hawkins, E. R. Kandel, *Nature Reviews Neuroscience* **2000**, *1*, 11.

- [15] W. C. Abraham, *Nature Reviews Neuroscience* **2008**, *9*, 387.

This article is protected by copyright. All rights reserved.

[16] E. M. Izhikevich, *IEEE Transactions on Neural Networks* **2003**, *14*, 1569.

[17] J. L. Hindmarsh, R. Rose, *Proceedings of the Royal Society of London. Series B. Biological sciences* **1984**, *221*, 87.

[18] J. Nagumo, S. Arimoto, S. Yoshizawa, *Proceedings of the IRE* **1962**, *50*, 2061.

[19] C. Morris, H. Lecar, *Biophysical Journal* **1981**, *35*, 193.

[20] A. L. Hodgkin, A. F. Huxley, *The Journal of Physiology* **1952**, *117*, 500.

[21] F. Rosenblatt, *Psychological Review* **1958**, *65*, 386.

[22] K. Hornik, M. Stinchcombe, H. White, *Neural Networks* **1989**, *2*, 359.

[23] D. E. Rumelhart, G. E. Hinton, R. J. Williams, *Nature* **1986**, *323*, 533.

[24] A. Grüning, S. M. Bohte, "Spiking neural networks: Principles and challenges", presented at *ESANN*, Bruges, April **2014**.

[25] A. Tavanaei, M. Ghodrati, S. R. Kheradpisheh, T. Masquelier, A. Maida, *Neural Networks* **2019**, *111*, 47.

[26] M. Bouvier, A. Valentian, T. Mesquida, F. Rummens, M. Reyboz, E. Vianello, E. Beigne, *ACM Journal on Emerging Technologies in Computing Systems* **2019**, *15*, 1.

[27] S. Pouyanfar, S. Sadiq, Y. Yan, H. Tian, Y. Tao, M. P. Reyes, M.-L. Shyu, S.-C. Chen, S. S. Iyengar, *ACM Computing Surveys* **2019**, *51*, 1.

[28] A. Shrestha, A. Mahmood, *IEEE Access* **2019**, *7*, 53040.

[29] V. François-Lavet, P. Henderson, R. Islam, M. G. Bellemare, J. Pineau, *Foundations and Trends® in Machine Learning* **2018**, *11*, 219.

[30] G. Indiveri, B. Linares-Barranco, T. J. Hamilton, A. Van Schaik, R. Etienne-Cummings, T. Delbrück, S.-C. Liu, P. Dudek, P. Häfliger, S. Renaud, *Frontiers in Neuroscience* **2011**, *5*, 73.

[31] A. Sebastian, M. Le Gallo, R. Khaddam-Aljameh, E. Eleftheriou, *Nature Nanotechnology* **2020**, *15*, 529.

[32] C. D. Schuman, T. E. Potok, R. M. Patton, J. D. Birdwell, M. E. Dean, G. S. Rose, J. S. Plank, (Preprint) arXiv:1705.06963, v1, submitted: May **2017**.

[33] W. Haensch, T. Gokmen, R. Puri, *Proceedings of the IEEE* **2019**, *107*, 108.

[34] S. B. Furber, D. R. Lester, L. A. Plana, J. D. Garside, E. Painkras, S. Temple, A. D. Brown, *IEEE Transactions on Computers* **2013**, *62*, 2454.