Modbus RTU for Embedded Cyber Secure Inverter Controller

A thesis submitted in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

by

Brady McBride

University of Arkansas

Bachelor of Science in Engineering, 2021

May 2023

University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D.

Thesis Director

---

Chris Farnell, Ph.D.

Committee Member

---

Jia Di, Ph.D.

Committee Member

## Abstract

The Modbus communication protocol is a widely adopted communication standard in industrial control systems. This communication protocol is known for being reliable and straightforward to implement while being versatile in terms of its operating parameters while supporting multiple formats over various hardware infrastructures and architectures. Many intelligent devices such as Programmable Logic Controllers (PLCs), Human-Machine Interfaces (HMIs), Internet-of-Things (IoT), and various Operational Technologies (OT) utilize Modbus for their communication systems. These types of systems must communicate with each other through a standardized and central communication process. To support the integration of these modular systems, a Field-Programmable Gate Array (FPGA) can act as an embedded central routing fabric for this communication to take place.

Embedded systems are versatile enough to interface with various devices and systems to accomplish various goals. Additionally, embedded systems require relatively small physical designs to minimize the required resources to facilitate the intended application by providing low-level system access. This minimization of system resources goes hand in hand with reducing the financial cost of a proposed solution or system. As remotely collaborating researchers often use FPGAs to prototype designs that are required to have a method for data transmission among systems, it is imperative to provide a baseline standard for communications among devices and systems.

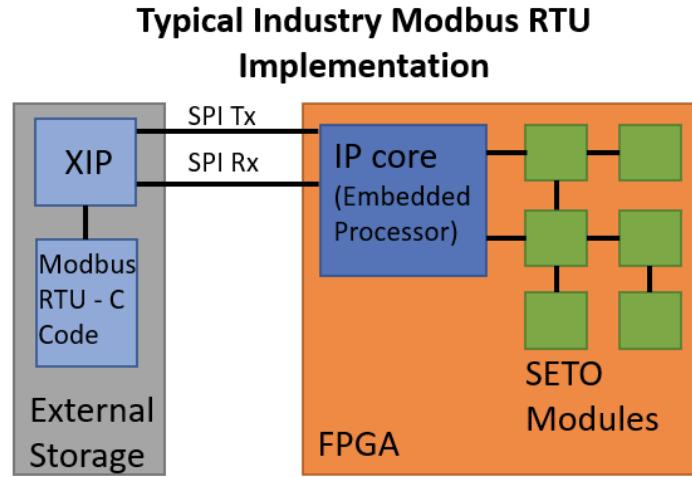

A typical method of implementing the Modbus RTU communication protocol in an embedded environment is using integrated logic architectures within the FPGA called “Intellectual Property (IP) cores.” IP cores can be designed using integrated logic or circuit designs to function as an embedded processor. These IP cores can then perform the required computational actions to support the Modbus RTU communication protocol by utilizing high-level programming languages such as the C programming language.

The hardware description language of Very High-Speed Integrated Circuit Hardware Description Language (VHDL) allows for the control of real hardware at the logic gate and signal level. These logic gates and signals can be designed and controlled to perform desired actions based on the system

design. Programming an FPGA using VHDL allows an individual to access the lowest abstraction level of the system during FPGA development. This level of abstraction is referred to as the register-transfer level (RTL), which gives access to manipulating values and variables at the register level. This register-level manipulation provides precision over creating the logical circuit within the FPGA, thus minimizing the required code to perform desired operations.

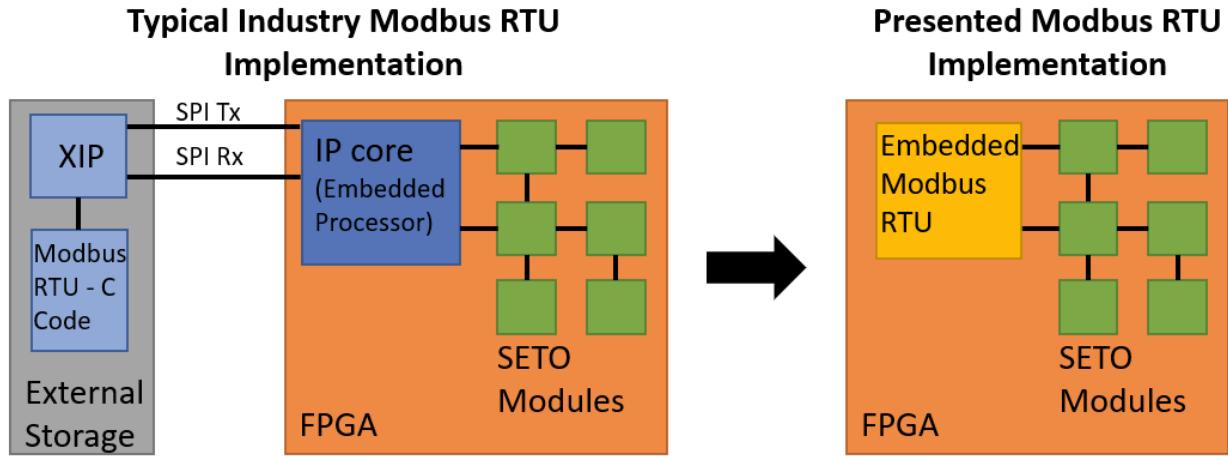

The Modbus RTU communication protocol can be implemented within an FPGA using VHDL programming to establish a standardized and embedded serial communication pathway. This implementation provides a standardized communication protocol to streamline research efforts among researchers, thus increasing the efficiency of research efforts. Additionally, this Modbus RTU implementation requires fewer resources when compared to typical communication protocol implementations that utilize an IP core, reducing the hardware requirement for effective research efforts.

©2023 by Brady McBride

All Rights Reserved

## Acknowledgement

I am filled with immense gratitude and appreciation towards Dr. H. Alan Mantooth, my advisor and committee chair, for giving me the incredible opportunity to work alongside him and his research group at the MSCAD Lab. I cannot thank him enough for the doors that he has opened for me and the invaluable guidance he has provided throughout my journey. Through his mentorship, I have gained a depth of hands-on experience that has exceeded my expectations and allowed me to stand on the shoulders of giants. I will forever be grateful for his generosity and support.

I am overwhelmed with gratitude towards Dr. Chris Farnell for his unwavering support and guidance during my time as a member of the Cyber-Physical Security section of the MSCAD Lab research group. Under his mentorship, I was given the freedom to develop my skills and capabilities independently, while also benefiting from his vast experience and valuable perspective. Dr. Farnell's influence has been pivotal in shaping my problem-solving abilities and has helped me grow both personally and professionally. I cannot thank him enough for the significant role he has played in my development and success.

I am deeply grateful for the immense support and opportunities that Dr. Jia Di has provided me. His unwavering encouragement and belief in my abilities have been a constant source of motivation and comfort, inspiring me to pursue a career path that I am truly passionate about. I cannot thank him enough for the invaluable opportunity he has given me by admitting me into the CyberCorps: SFS program. His generosity and support have been instrumental in shaping my future, and I will always cherish his mentorship and guidance.

I am immensely grateful for the financial and professional support provided by the National Science Foundation's CyberCorps: Scholarship for Service award, which made this endeavor possible. I feel deeply honored to be a part of this distinguished program, which has given me the opportunity to work on some of the most challenging issues related to our nation's critical infrastructure. I will always cherish this experience and remain grateful for the support that enabled me to participate in this program.

I would like to express my heartfelt gratitude to Paulo Custodio for his invaluable support and guidance during this project. Paulo has been an exceptional team member, consistently providing constructive

feedback and insights that have greatly contributed to the success of my research efforts. Working alongside him has been a valuable learning experience, and I am thankful for the knowledge and expertise he has shared with me.

Finally, I cannot express enough gratefulness to my supportive family, especially my loving spouse, who stood by me unwaveringly throughout the years of completing this work. Their unconditional love and understanding gave me the strength and motivation to keep going, even during the toughest moments. I am deeply thankful for their unwavering support, which played a significant role in my success. I look forward to embarking on new adventures with my wife, as we close this chapter and move forward together.

## Table of Contents

|                                                                   |    |

|-------------------------------------------------------------------|----|

| Chapter 1.....                                                    | 1  |

| Introduction.....                                                 | 1  |

| 1.1 – Motivation.....                                             | 1  |

| 1.2 – Solar Energy Technologies Office Project Contribution ..... | 4  |

| 1.3 – Thesis Organization.....                                    | 4  |

| Chapter 2.....                                                    | 6  |

| Background.....                                                   | 6  |

| 2.1 – Introduction .....                                          | 6  |

| 2.2 – Power Electronics and SMA Inverter .....                    | 6  |

| 2.3 – Serial Communication.....                                   | 7  |

| 2.3.1 – RS-232 Serial Communication Standard .....                | 8  |

| 2.3.2 – Universal Asynchronous Receiver-Transmitter (UART) .....  | 9  |

| 2.4 – Modbus RTU .....                                            | 11 |

| 2.4.1 – Data Representations and Configurational Parameters ..... | 12 |

| 2.4.2 – Read and Write Commands .....                             | 12 |

| 2.4.3 – Packet Structure .....                                    | 13 |

| 2.4.4 – Cyclical Redundancy Check (CRC) .....                     | 18 |

| 2.4.5 – Message RTU Framing .....                                 | 19 |

| 2.4.6 – Modbus TCP .....                                          | 21 |

| 2.5 – Power Electronics Unified Controller Board (UCB) .....      | 21 |

| 2.5.1 – UCB Architecture.....                                     | 23 |

| 2.5.2 – Communication Peripherals and Capabilities .....          | 24 |

| 2.5.3 – UCB's FPGA.....                                           | 26 |

|                                                     |    |

|-----------------------------------------------------|----|

| 2.6 – FPGA Environment and VHDL .....               | 27 |

| 2.6.1 – FPGA Overview.....                          | 28 |

| 2.6.2 – VHDL Overview .....                         | 31 |

| 2.6.3 – Intellectual Property Cores .....           | 32 |

| Chapter 3.....                                      | 34 |

| Modbus RTU FPGA Implementation via VHDL .....       | 34 |

| 3.1 – Introduction .....                            | 34 |

| 3.2 – System Components .....                       | 34 |

| 3.2.1 – SETO Modules Requiring Communication .....  | 35 |

| 3.2.2 – Communication and Bus Infrastructure .....  | 41 |

| 3.3 – Modbus RTU Design .....                       | 44 |

| 3.3.1 – Design Parameters.....                      | 45 |

| 3.3.2 – Next State Logic Algorithm - Overview ..... | 47 |

| 3.3.3 – Command Request Processing Algorithm .....  | 50 |

| 3.3.4 – Command Response Processing Algorithm ..... | 52 |

| 3.3.5 – Cyclic Redundancy Check .....               | 55 |

| 3.3.6 – Transmission Error Handling.....            | 56 |

| 3.4 – Modbus RTU, Multiple Instantiations .....     | 57 |

| Chapter 4.....                                      | 59 |

| Test Setup and Experimental Results.....            | 59 |

| 4.1 – Introduction .....                            | 59 |

| 4.2 – Test Setup .....                              | 60 |

| 4.3 – Simulation Testing and Results .....          | 61 |

| 4.4 – Development Board Testing and Results .....   | 68 |

|                                                                               |     |

|-------------------------------------------------------------------------------|-----|

| 4.5 – UCB Testing and Results .....                                           | 70  |

| 4.6 – Python Resiliency Testing and Results .....                             | 76  |

| 4.7 – Bootloader and Hotpatching Testing and Results .....                    | 78  |

| 4.8 – Resource Utilization.....                                               | 85  |

| Chapter 5.....                                                                | 88  |

| Conclusions and Future Work.....                                              | 88  |

| 5.1 – Summary of Conclusions.....                                             | 88  |

| 5.2 – Summary of Future Work.....                                             | 89  |

| 5.3 – Discussion on the Limitations of Low-Cost FPGAs .....                   | 92  |

| References.....                                                               | 94  |

| Appendices .....                                                              | 97  |

| Appendix A: Code .....                                                        | 97  |

| A-1 Modbus RTU Algorithm: FPGA VHDL Code.....                                 | 97  |

| A-2 Digital Twin Top File With Modbus RTU Instantiation: FPGA VHDL Code ..... | 134 |

| A-3 Python Resiliency Testing Code .....                                      | 153 |

| A-4 CRC Verification with C Code .....                                        | 156 |

## List of Figures

|                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. Sequential data transmission of serial communication [13] .....                                           | 7  |

| Figure 2.2. Voltage-Binary logic of RS-232 communication protocol [14] .....                                          | 8  |

| Figure 2.3. Three-wire serial communication connection diagram [15] .....                                             | 9  |

| Figure 2.4. UART interface connection with Data Bus [16] .....                                                        | 10 |

| Figure 2.5. Packet structure of UART message [16] .....                                                               | 10 |

| Figure 2.6 – Modbus RTU read holding register command.....                                                            | 14 |

| Figure 2.7 – Read holding register breakdown 1 of 3.....                                                              | 15 |

| Figure 2.8 – Read holding register breakdown 2 of 3.....                                                              | 15 |

| Figure 2.9 – Read holding register breakdown 3 of 3 .....                                                             | 16 |

| Figure 2.10 – Modbus RTU, read holding register command and response packet structure .....                           | 17 |

| Figure 2.11 - Modbus RTU, write holding register command and response packet structure .....                          | 18 |

| Figure 2.12 - Cyclical Redundancy Check (CRC) flowchart [19] .....                                                    | 19 |

| Figure 2.13 – RTU message frame [20].....                                                                             | 20 |

| Figure 2.14 – RTU message framing. Acceptable message framing (left). Unacceptable message framing (right) [20]...... | 20 |

| Figure 2.15 – Modbus TCP packet components [21] .....                                                                 | 21 |

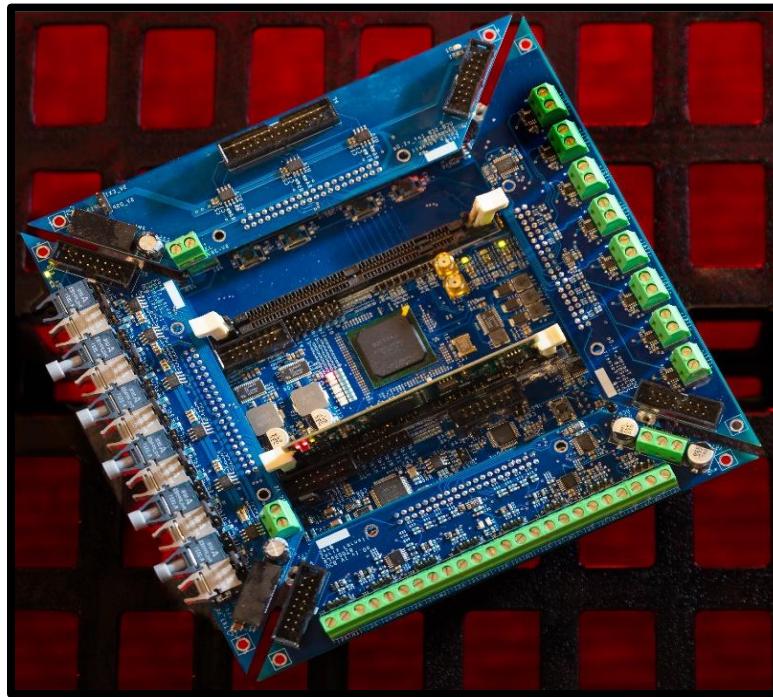

| Figure 2.16 – Image of Unified Controller Board (UCB) .....                                                           | 22 |

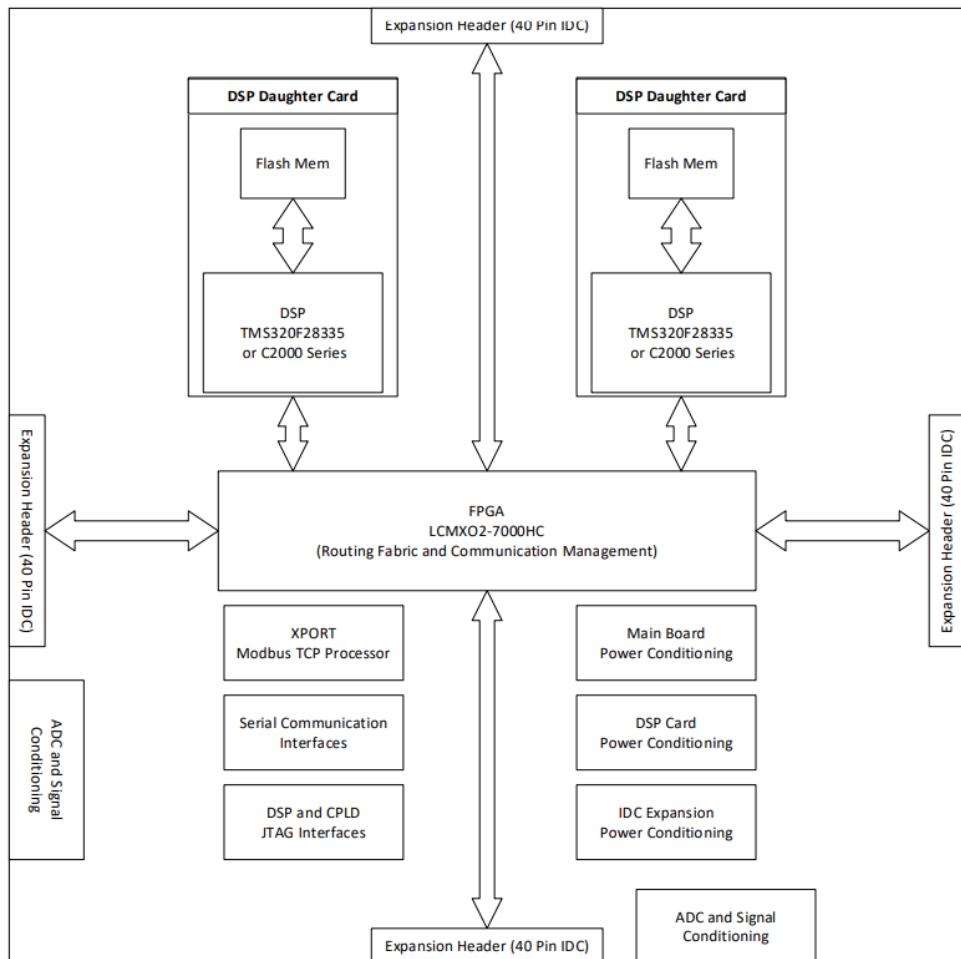

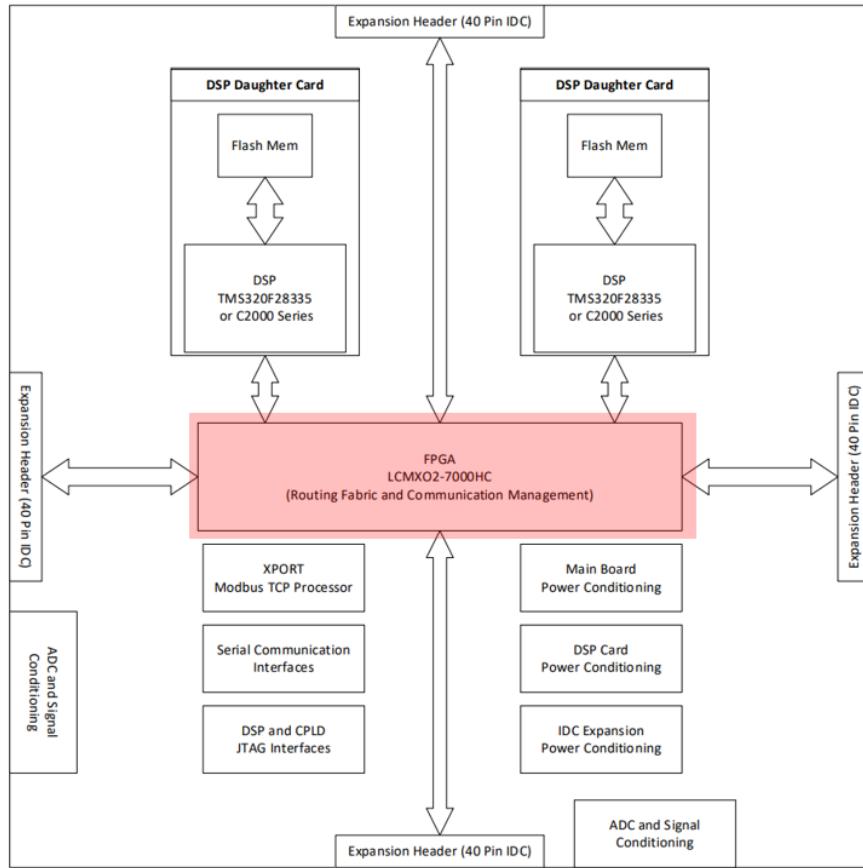

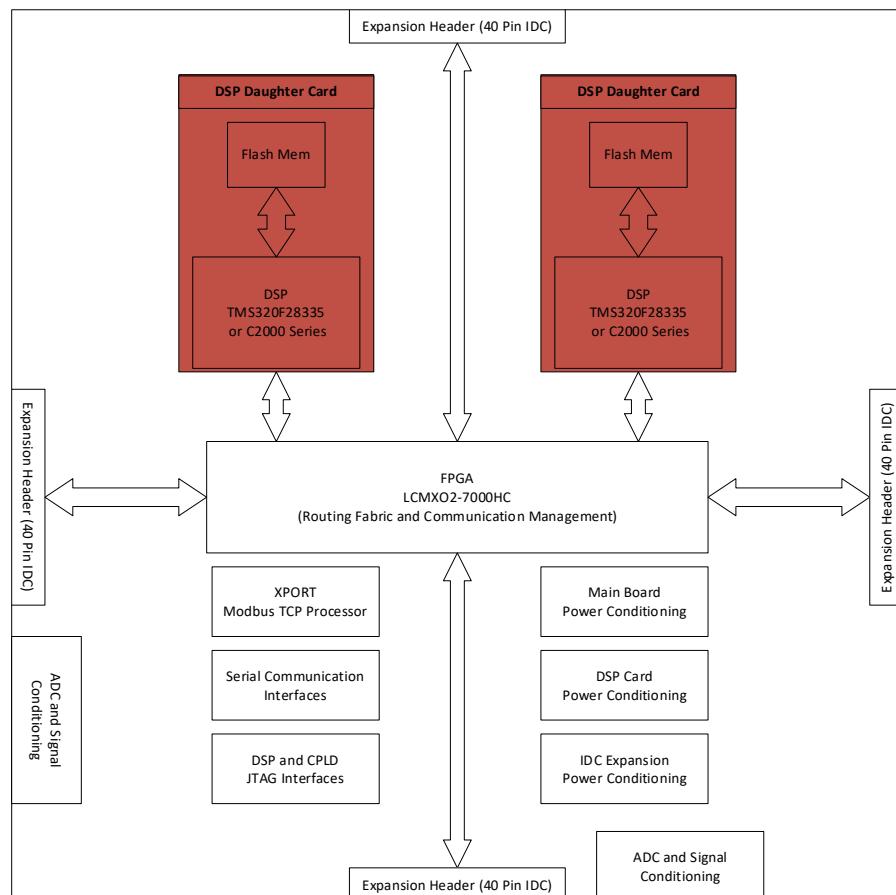

| Figure 2.17 – UCB architecture diagram .....                                                                          | 23 |

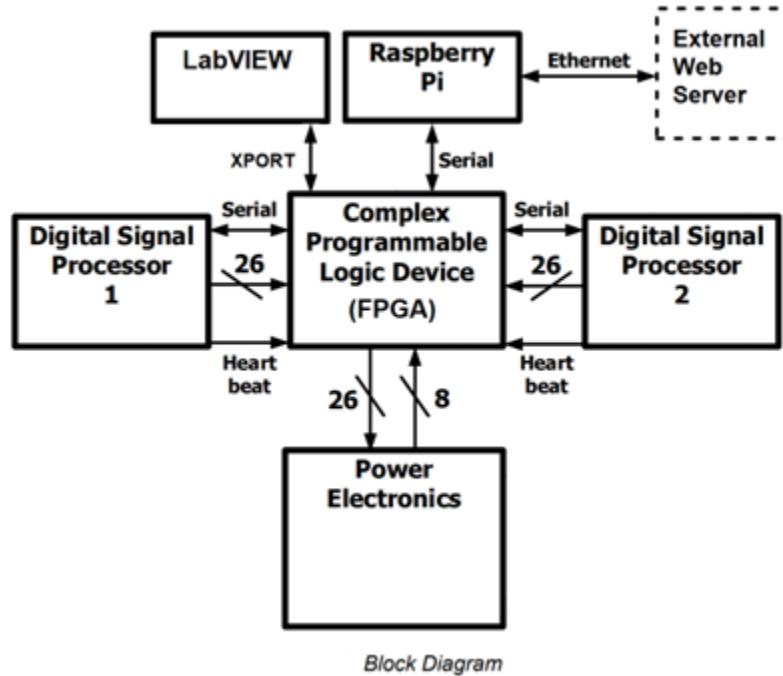

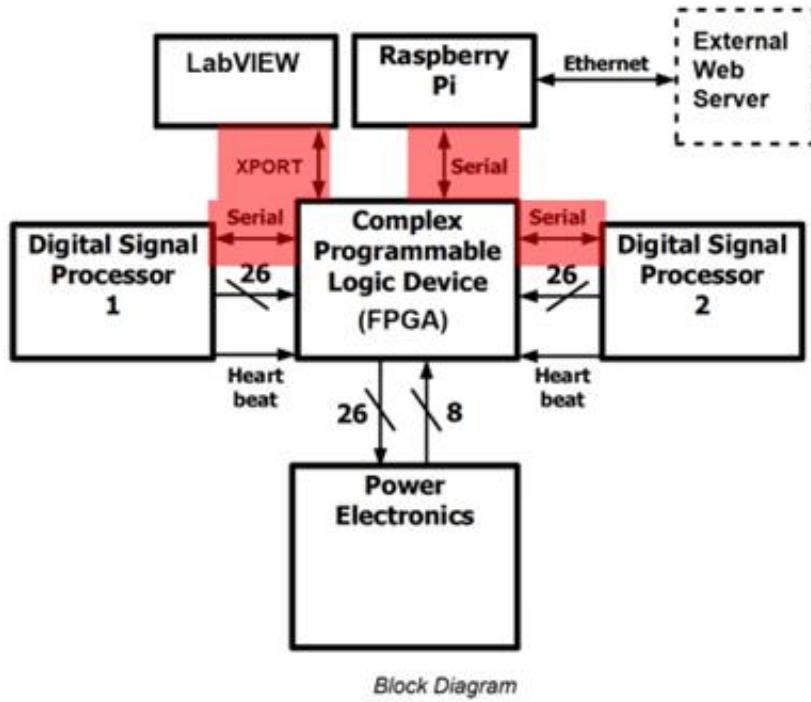

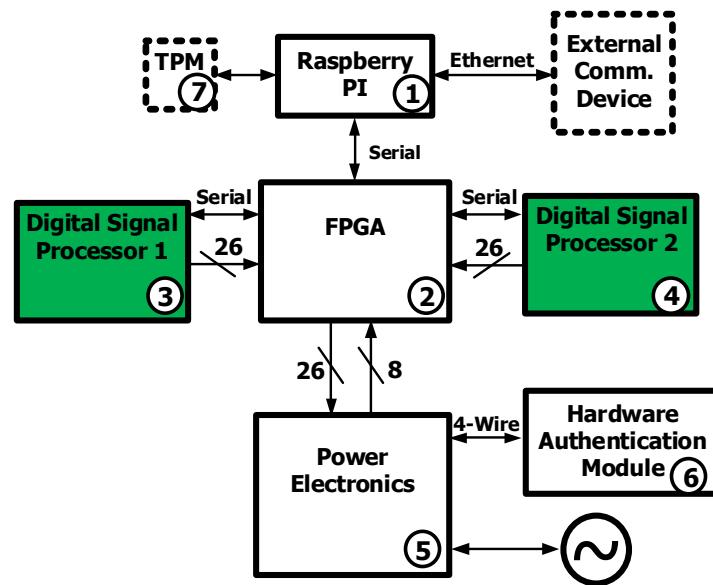

| Figure 2.18 – SETO hardware architecture system component block diagram .....                                         | 24 |

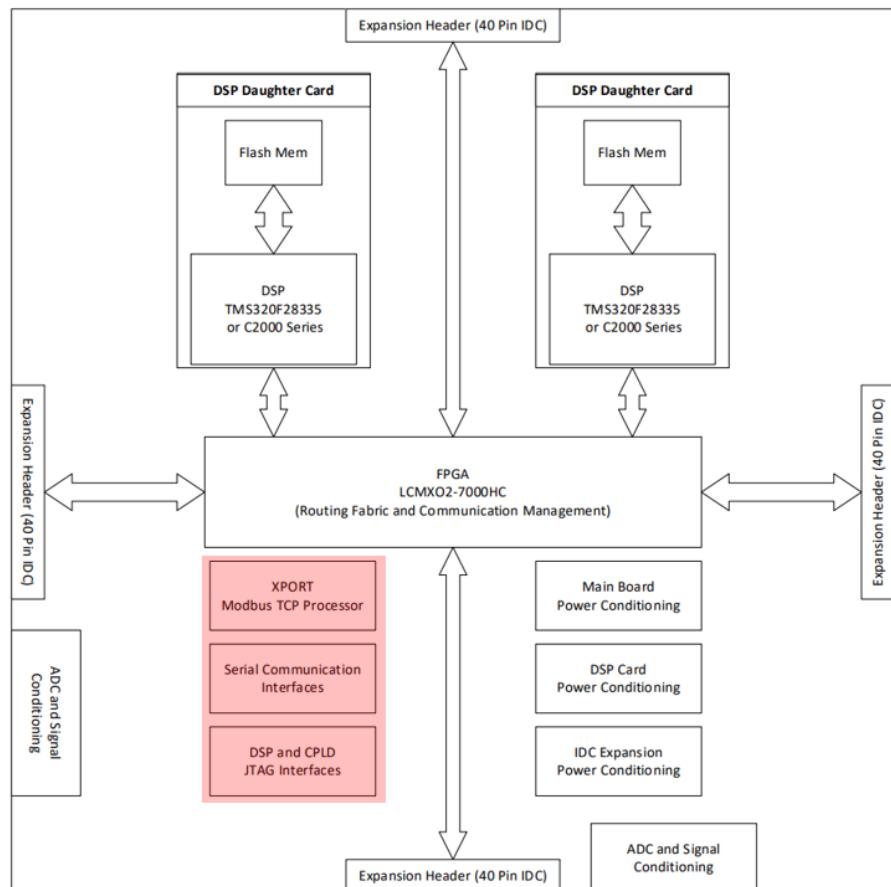

| Figure 2.19 – UCB architecture diagram – communication component highlighted.....                                     | 25 |

| Figure 2.20 – SETO hardware architecture system components block diagram – communication pathways highlighted.....    | 26 |

| Figure 2.21 – UCB architecture diagram – FPGA highlighted .....                                                       | 27 |

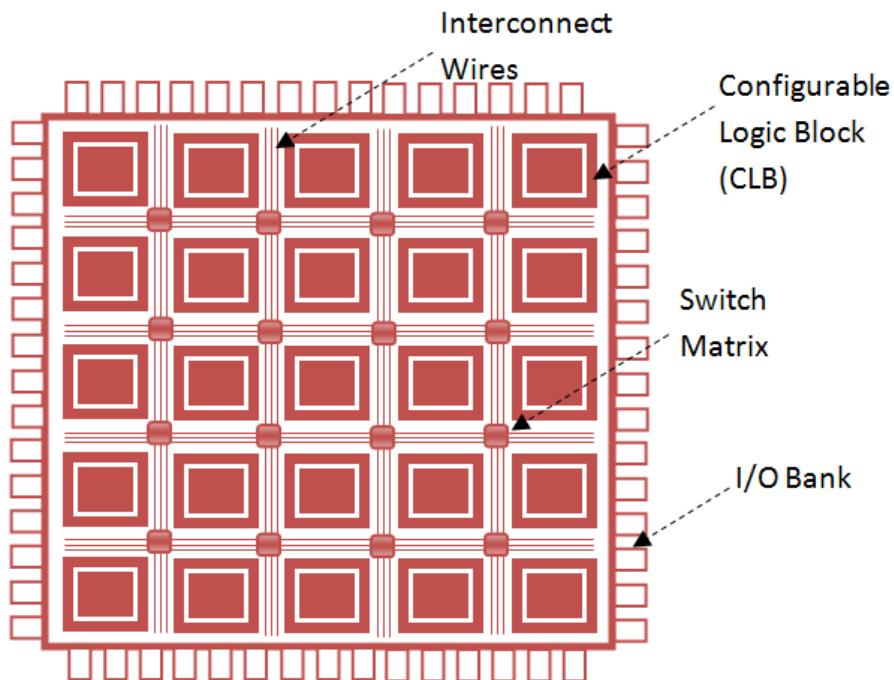

| Figure 2.22 – FPGA Architecture with Configurable Logic Blocks [24] .....                                             | 28 |

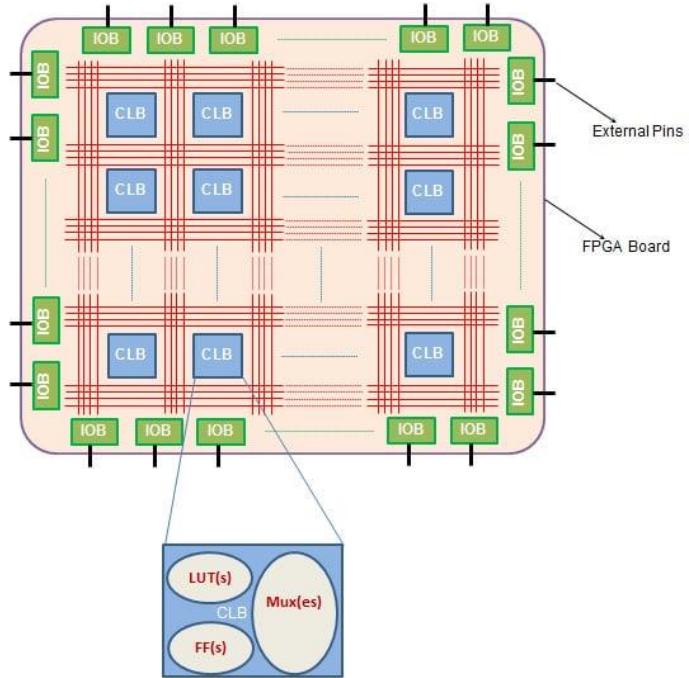

| Figure 2.23 – The internal architecture of a typical FPGA [26].....                                                   | 30 |

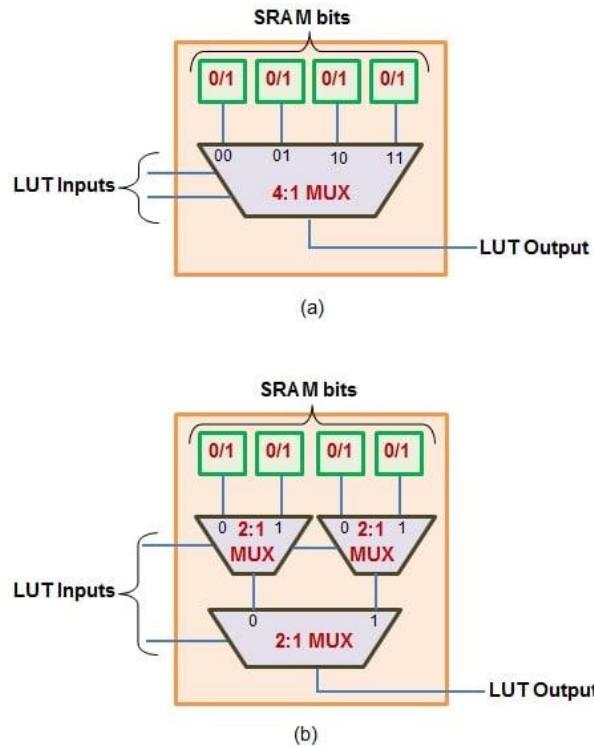

| Figure 2.24 – Internal structure of a 4-bit LUT, (a) 4:1 MUX, (b) 2:1 MUX [26].....                                   | 30 |

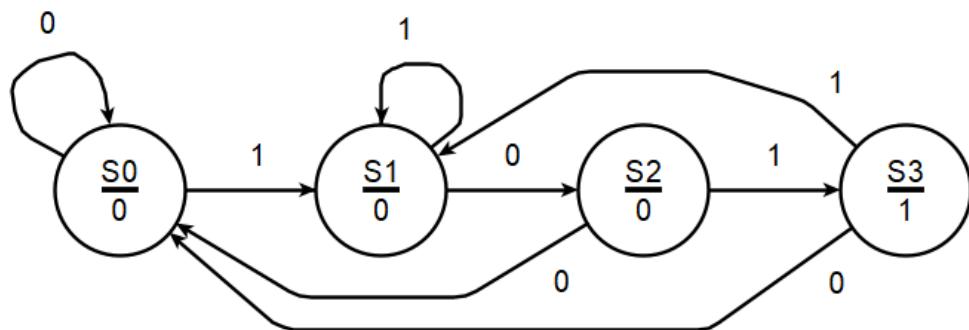

| Figure 2.25 – Resetting ASM – Detects bit sequence of “1010”.....                                                     | 32 |

|                                                                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

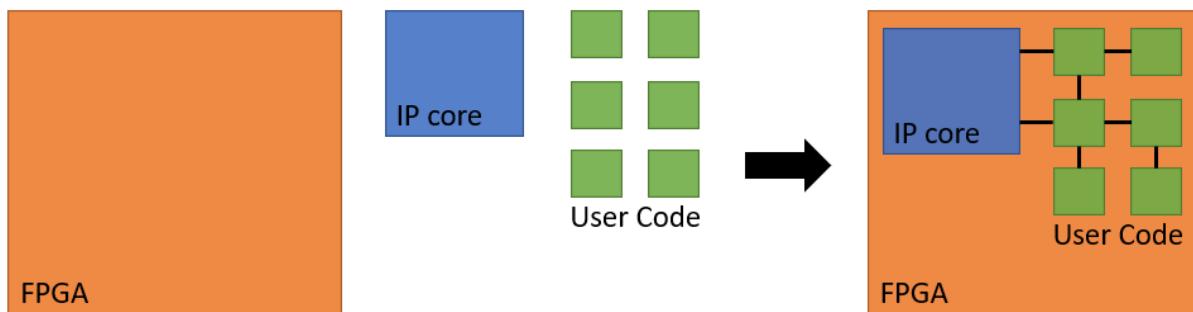

| Figure 2.26 – Diagram of IP core and user code components using the available resources of an FPGA; Illustrates an IP core resides with user modules.....                                           | 33 |

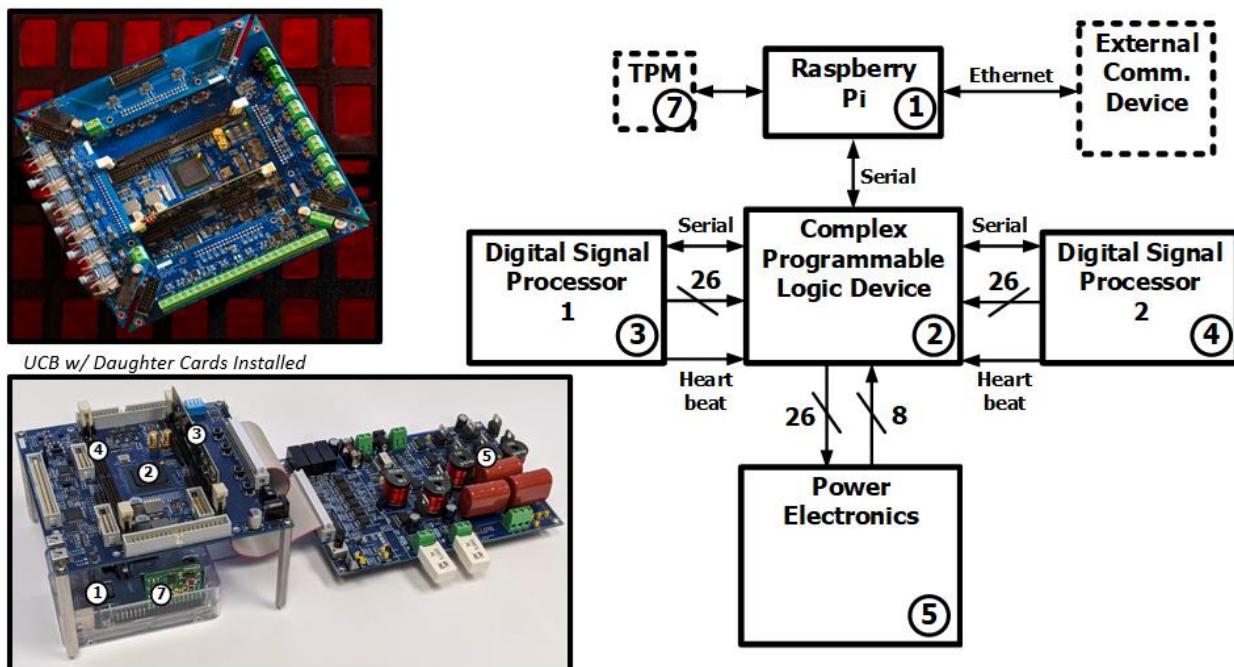

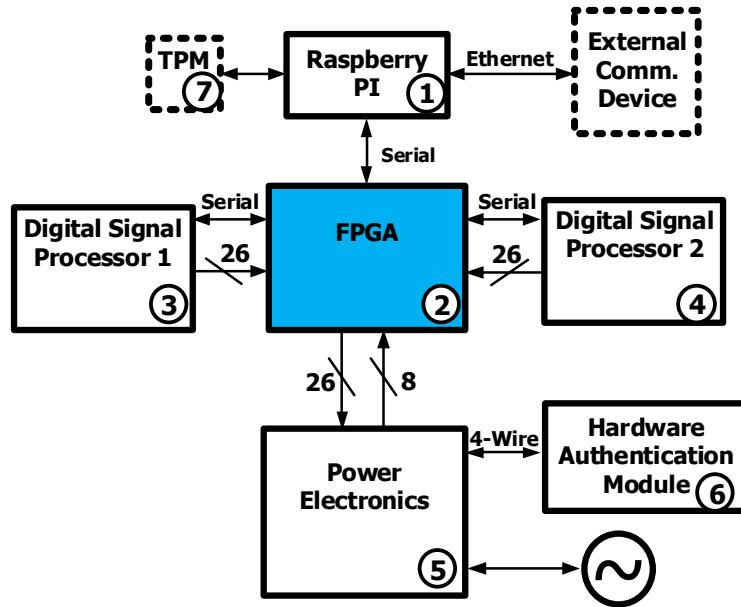

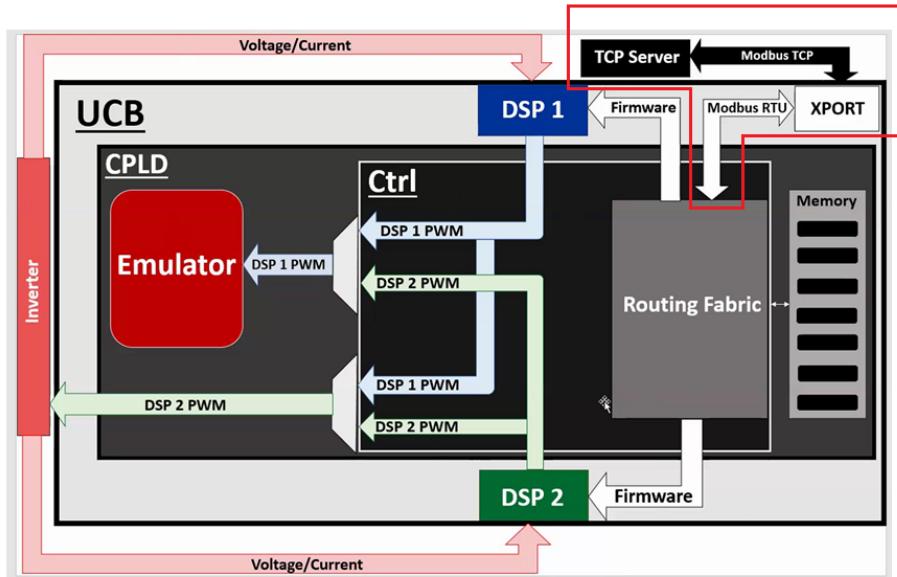

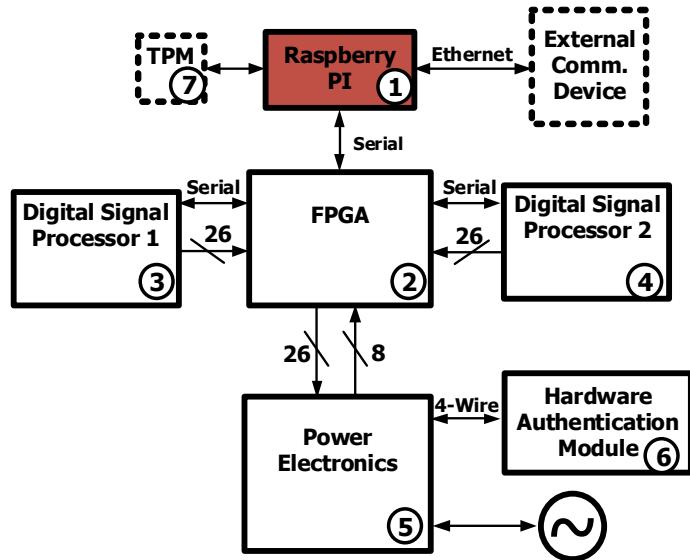

| Figure 3.27 – Diagram of SETO project architecture interconnects (right), UCB (top left), and UCB connected to Raspberry Pi and power electronics board (bottom left).....                          | 35 |

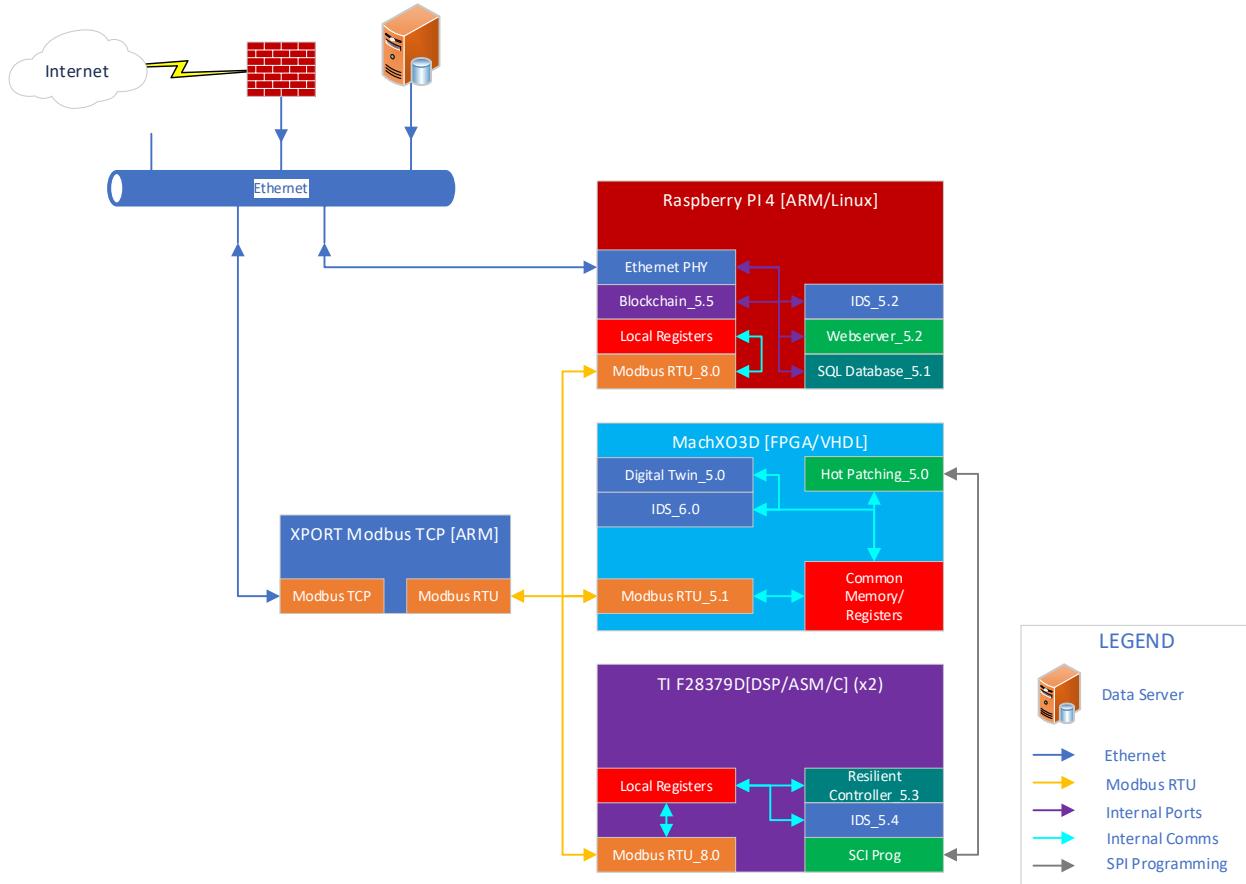

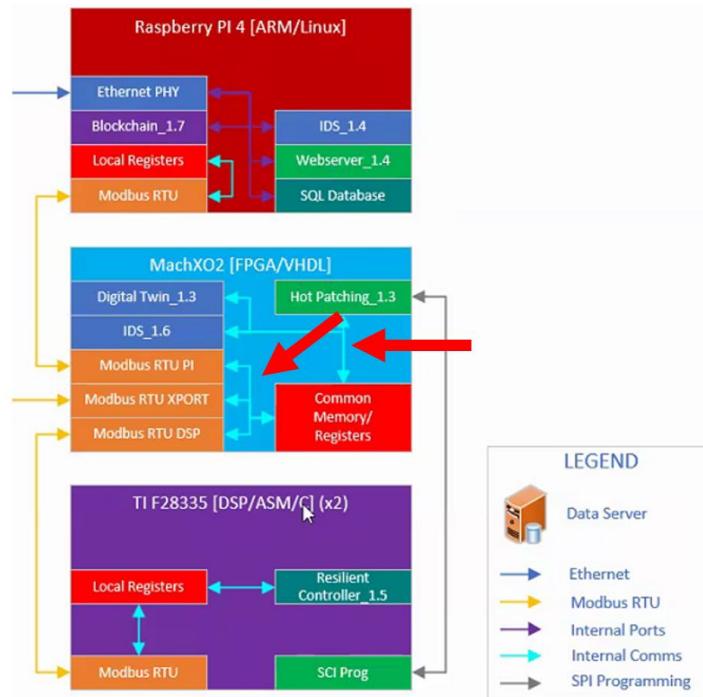

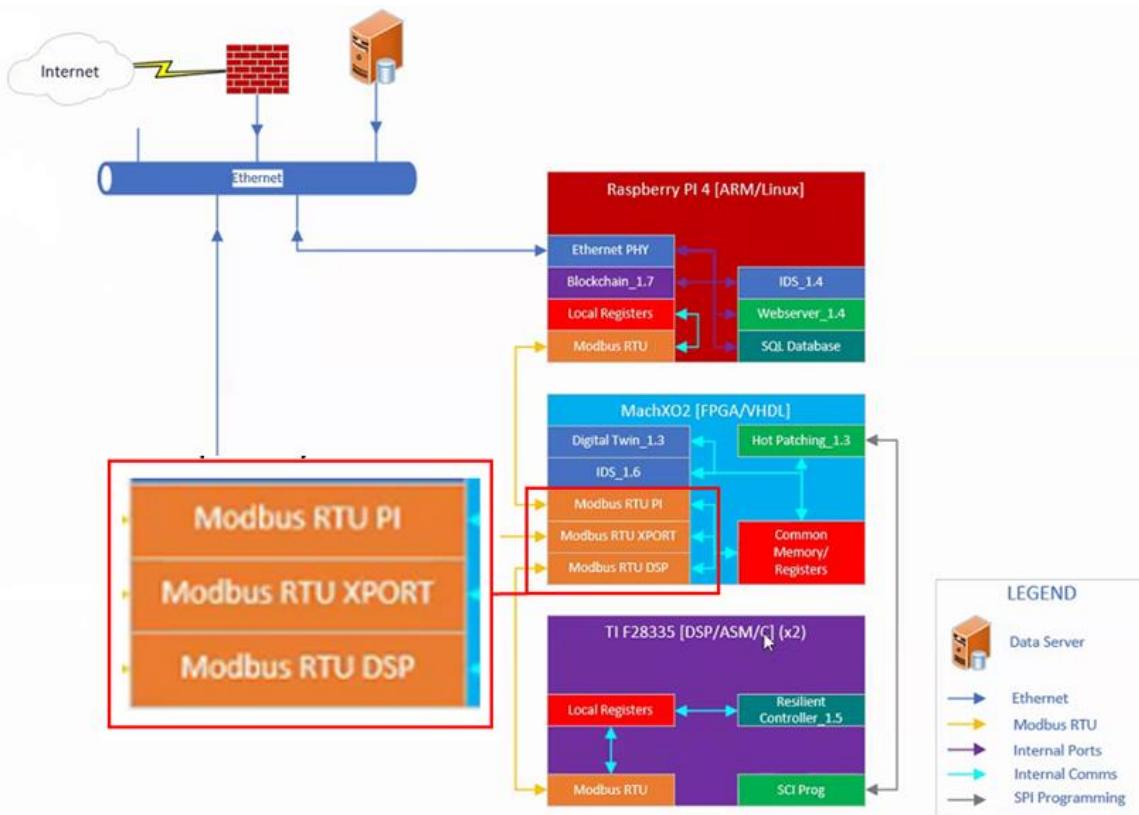

| Figure 3.28 – SETO module network interconnection diagram of FPGA, DSPs, Raspberry Pi, and ethernet/internet (numbers after module name denote SETO task identifiers) .....                         | 36 |

| Figure 3.29 - SETO hardware architecture system component block diagram, FPGA highlighted.....                                                                                                      | 37 |

| Figure 3.30 – Diagram of Digital Twin within UCB of SETO project, Modbus RTU communication components outlined in red (top right) .....                                                             | 38 |

| Figure 3.31 - SETO hardware architecture system component block diagram, Raspberry Pi highlighted.                                                                                                  | 39 |

| Figure 3.32 - SETO hardware architecture system component block diagram, DSPs highlighted .....                                                                                                     | 40 |

| Figure 3.33 - UCB architecture diagram – DSPs highlighted .....                                                                                                                                     | 40 |

| Figure 3.34 - SETO module network interconnection diagram of FPGA, DSPs, Raspberry Pi, and ethernet/internet. Red arrows indicate the internal serial bus infrastructure of the Bus Interface. .... | 42 |

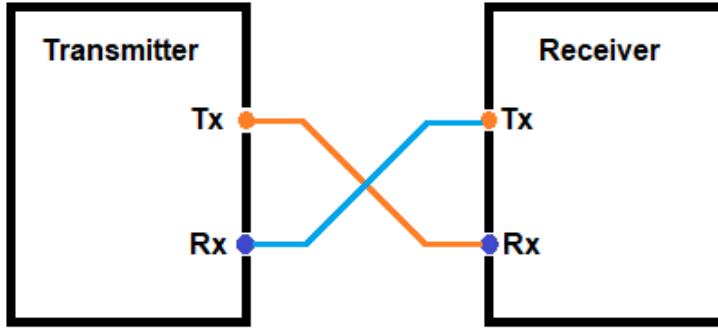

| Figure 3.35 – Full duplex signal transmission connections .....                                                                                                                                     | 46 |

| Figure 3.36 – Case statements of next state logic algorithm with VHDL behavioral architectural modeling style .....                                                                                 | 48 |

| Figure 3.37 – Overview of the state diagram of the Next-State-Logic algorithm for the Modbus RTU VHDL implementation .....                                                                          | 49 |

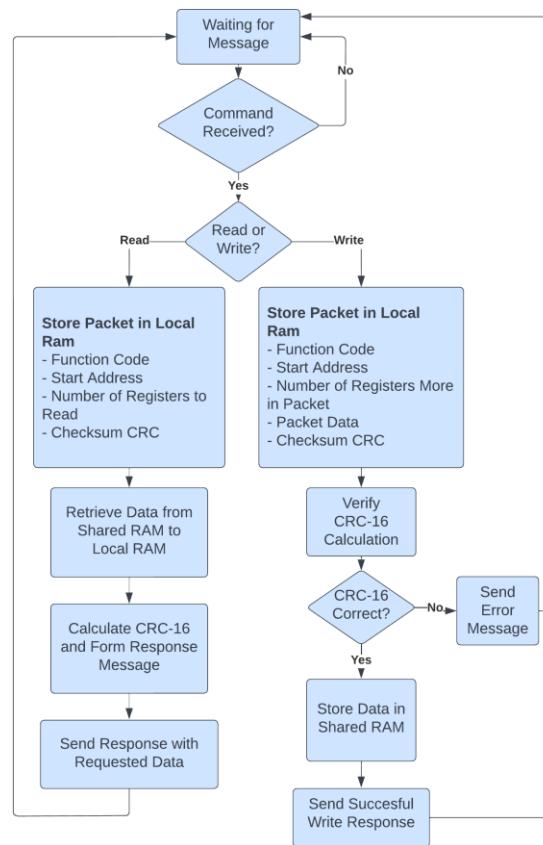

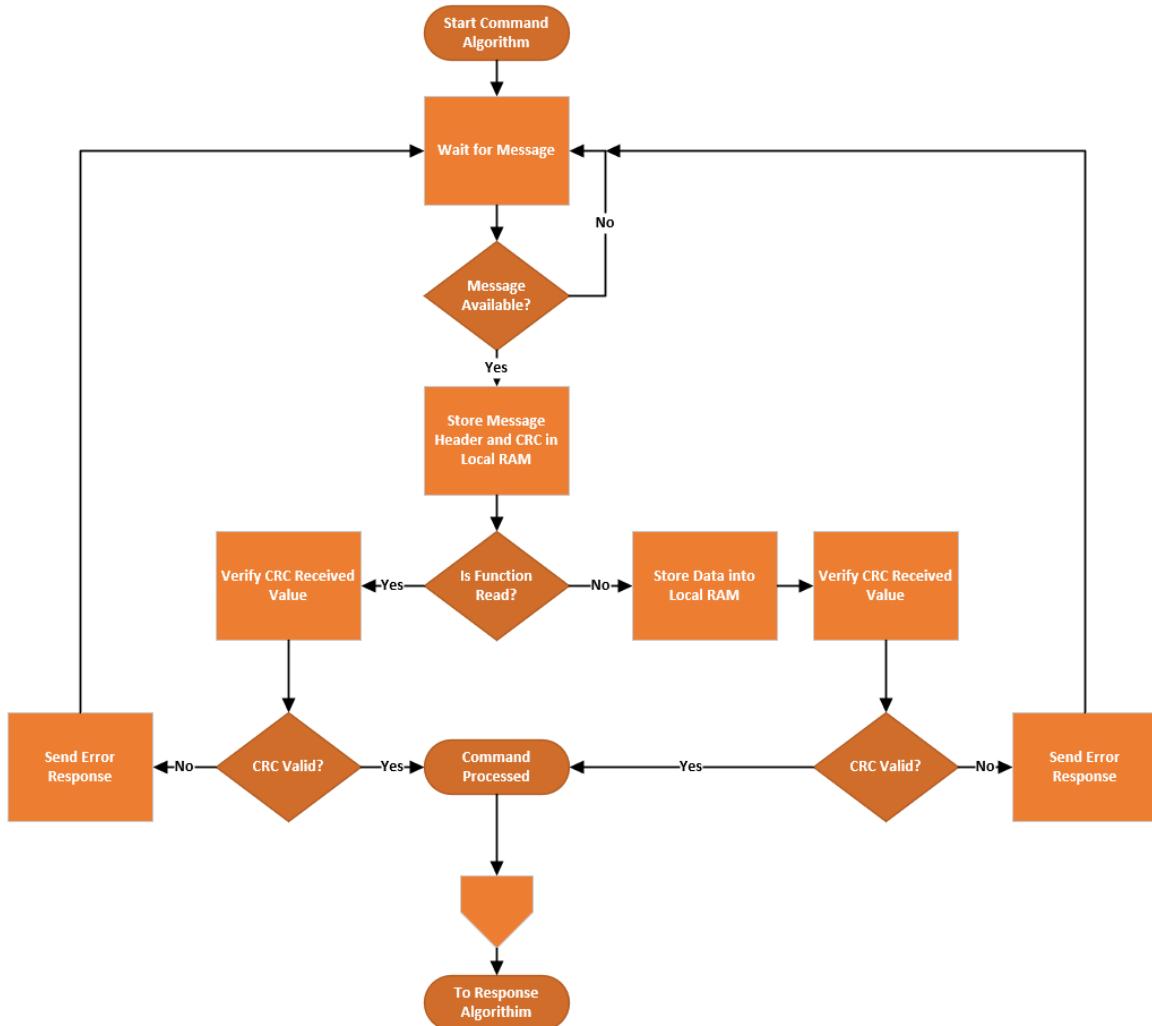

| Figure 3.38 - State diagram of the next-state-logic algorithm used for the processing of a Modbus RTU command request received by the slave device .....                                            | 50 |

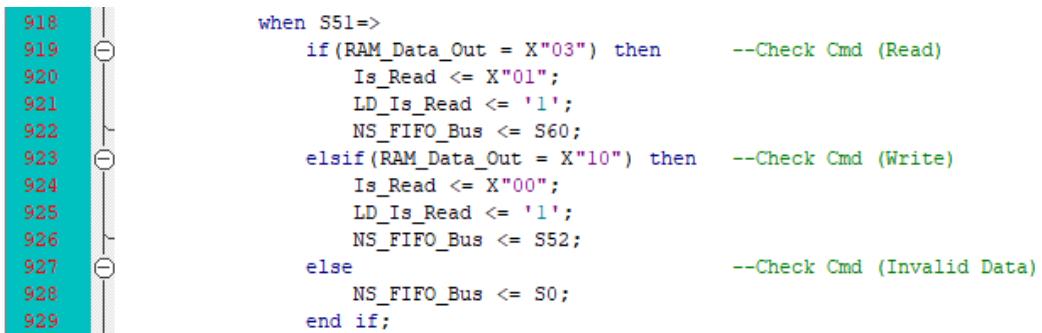

| Figure 3.39 – VHDL code in NSL algorithm that routes state pathway based on read or write request ....                                                                                              | 51 |

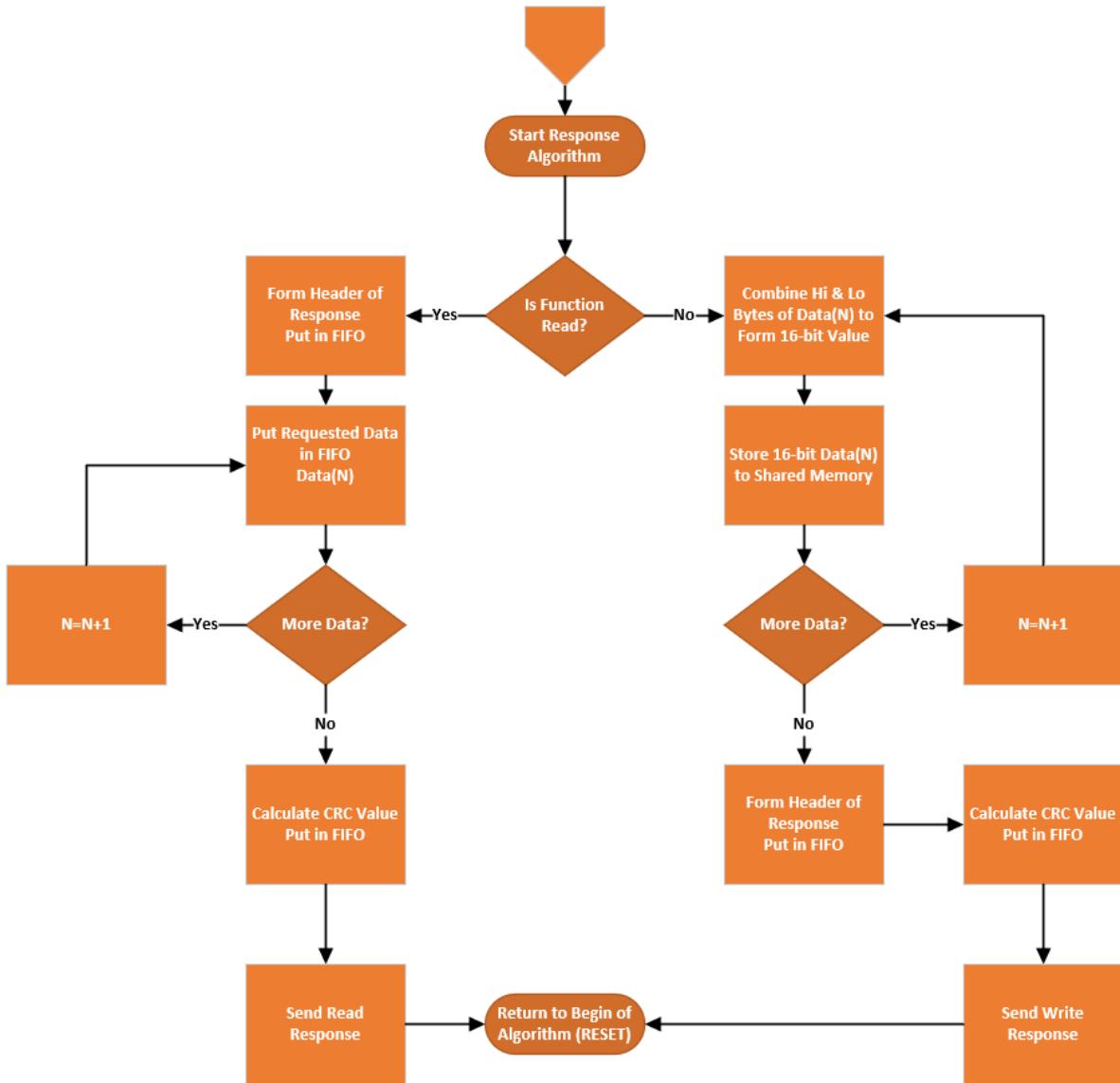

| Figure 3.40 - State diagram of the next-state-logic algorithm used for the processing and fulfillment of the Modbus RTU command response received by the slave device.....                          | 53 |

| Figure 3.41 - SETO module network interconnection diagram highlighting the three embedded Modbus RTU instantiations servicing the Raspberry Pi, Ethernet connection, and DSPs .....                 | 57 |

| Figure 3.42 – Mini-USB connection for Modbus RTU communication with Raspberry Pi through TI port on UCB.....                                                                                        | 58 |

|                                                                                                                                                                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

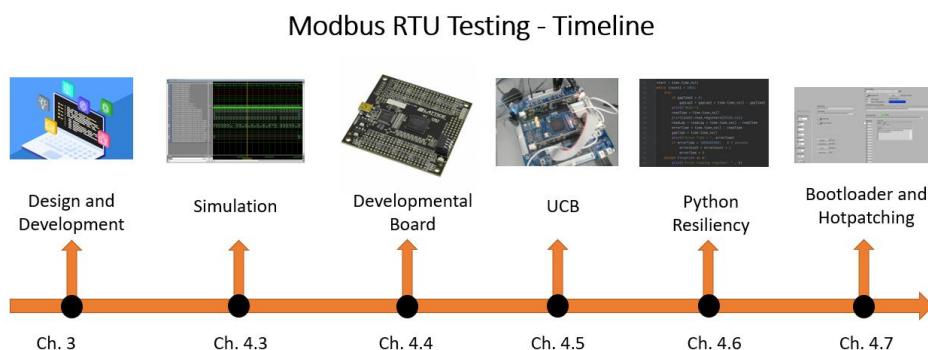

| Figure 4.43 - Timeline of the testing process for the embedded Modbus RTU implementation .....                                                                                                                                                                                                         | 59 |

| Figure 4.44 – VHDL code of nearly identical case statements to account for propagation delay when storing values in RAM .....                                                                                                                                                                          | 62 |

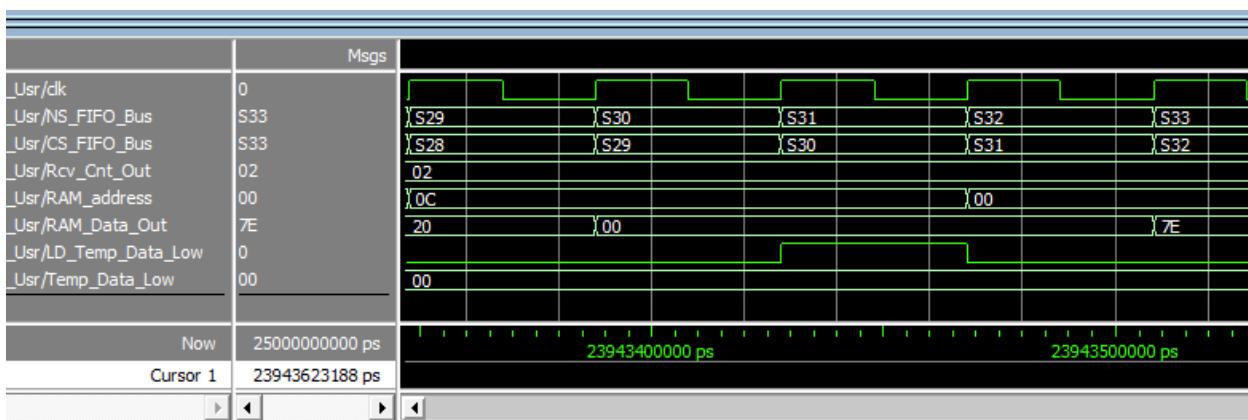

| Figure 4.45 – VHDL simulation of code from Figure 4.44, depicting the gate-level simulation of redundant case statements to allow RAM data to be available on physical hardware before storing .....                                                                                                   | 62 |

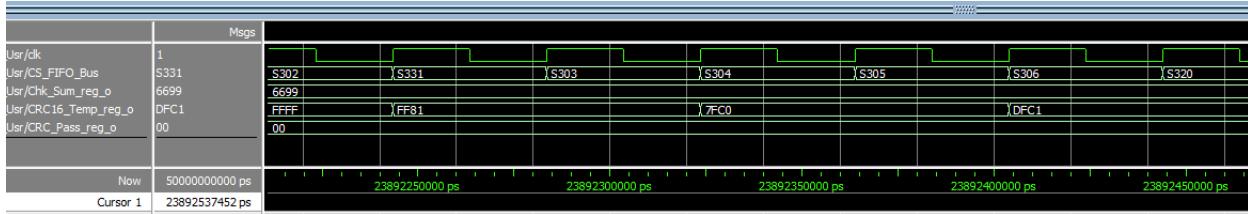

| Figure 4.46 – High fidelity simulation results of CRC calculations, showcasing case statement, and CRC register value transitions .....                                                                                                                                                                | 63 |

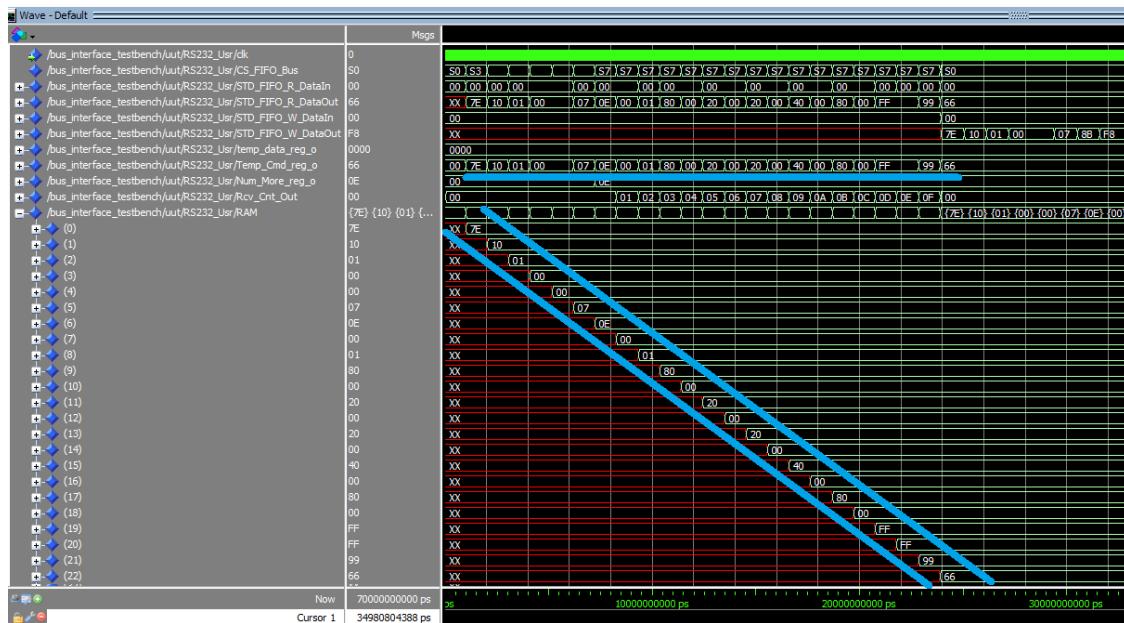

| Figure 4.47 – Simulation results showcasing the NSL algorithm storing the incoming message components (top horizontal blue line) into the local RAM (diagonal blue lines) to be used for various references and calculations .....                                                                     | 64 |

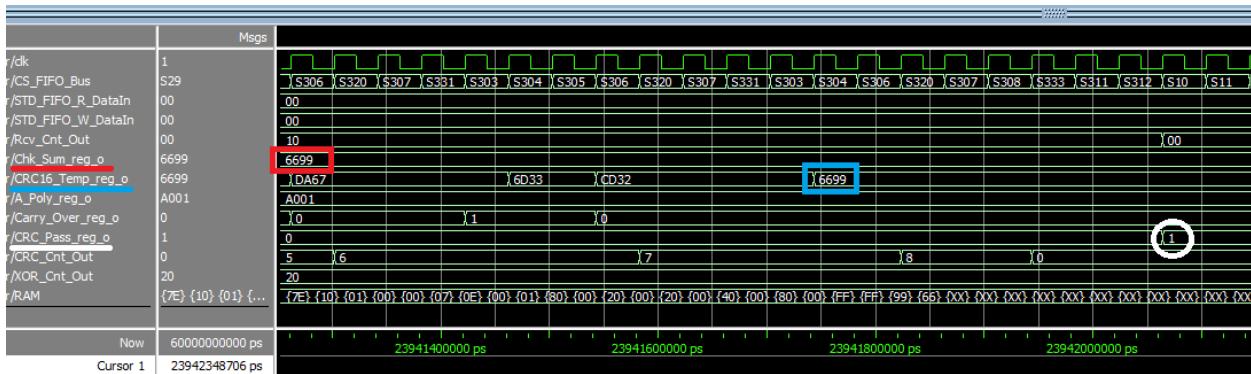

| Figure 4.48 – Simulation waveform of register-level CRC verification process when validating a received CRC from an incoming message, the received value (red) is recalculated (blue) based on the received message contents, and a flag (white) is asserted if the values match .....                 | 66 |

| Figure 4.49 – Simulation of a read command depicting the results of the verification of the received CRC value (blue) and the calculation of the response CRC value (white), the yellow bars represent the data that is used within the CRC calculation for the subsequent highlighted CRC value.....  | 66 |

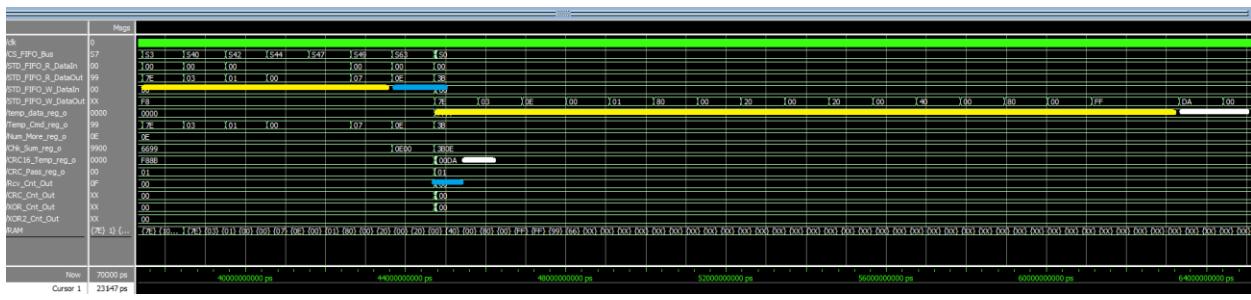

| Figure 4.50 - Simulation of a write command depicting the results of the verification of the received CRC value (blue) and the calculation of the response CRC value (white), the yellow bars represent the data that is used within the CRC calculation for the subsequent highlighted CRC value..... | 67 |

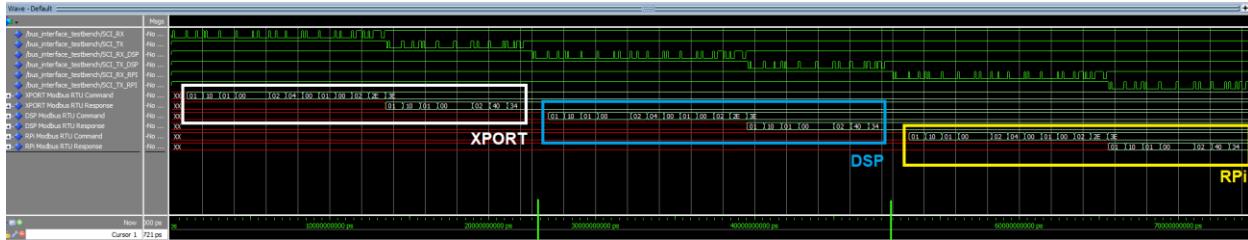

| Figure 4.51 – Simulation waveform of master device write commands and slave device responses for three Modbus RTU module instantiations: XPORT module (white), DSP module (blue), and Raspberry Pi module (yellow) .....                                                                               | 68 |

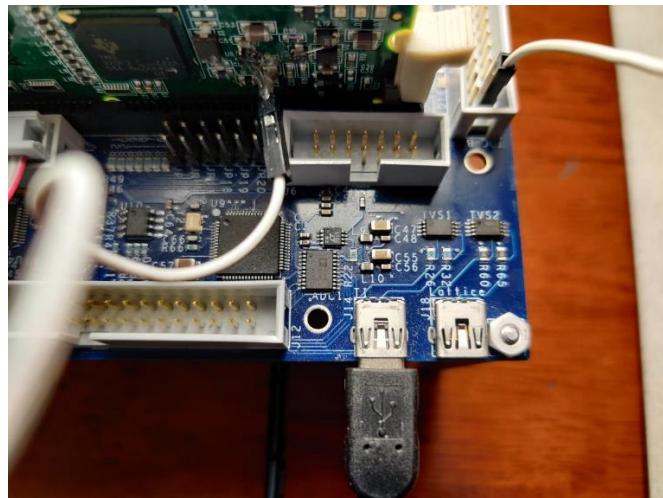

| Figure 4.52 – Lattice breakout board equipped with a MachX03D FPGA (model LCMX03D-9400HC) ....                                                                                                                                                                                                         | 68 |

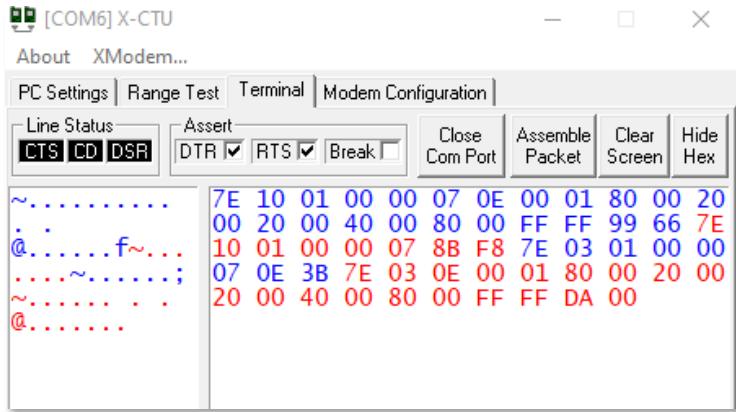

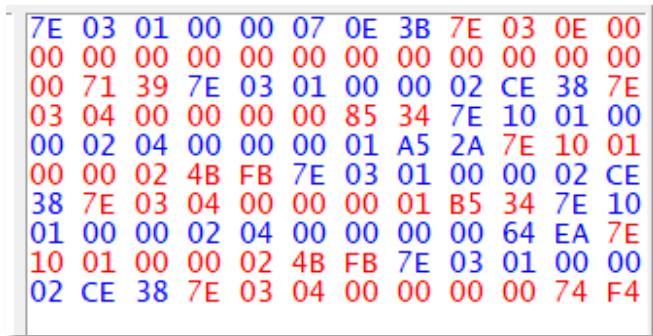

| Figure 4.53 – Communication between the XCTU software and the embedded Modbus RTU module via a USB connection, the blue bytes in hexadecimal represent the manually input command request while the red bytes are the response from the FPGA .....                                                     | 70 |

|                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.54 – Additional image of communication between the XCTU software and the embedded Modbus RTU; each manual command (blue) is requesting to read a different number of registers while the responses (red) deliver accordingly .....                                                                                                                                                       | 70 |

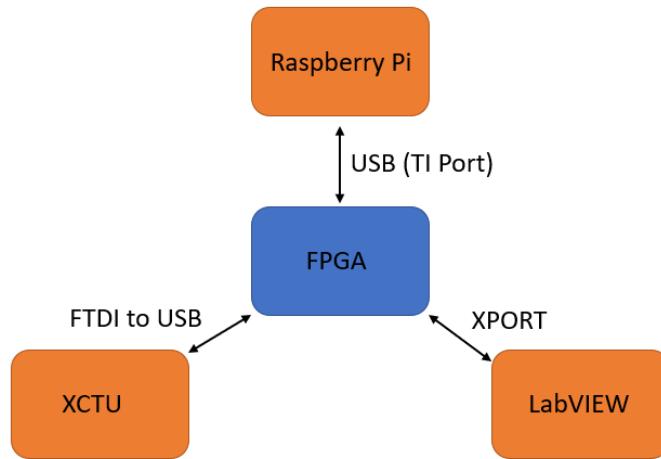

| Figure 4.55 – Connection diagram of three embedded Modbus RTU instantiations for the UCB testing in the hardware phase .....                                                                                                                                                                                                                                                                      | 71 |

| Figure 4.56 – Basic Python code using the “MinimalModbus” package to use Modbus RTU to read and write with registers within the FPGA through embedded Modbus RTU .....                                                                                                                                                                                                                            | 72 |

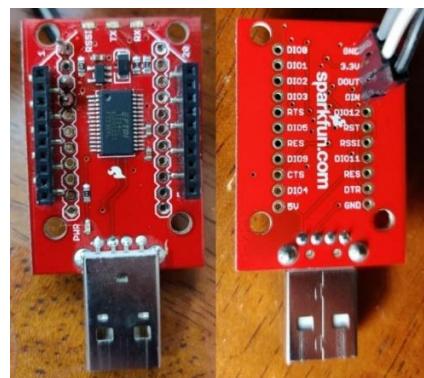

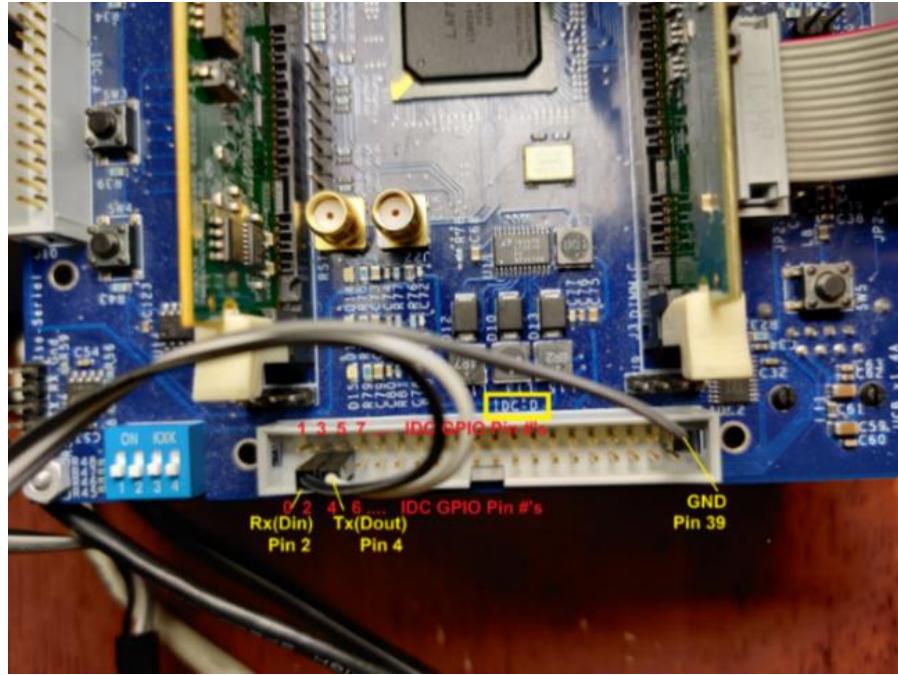

| Figure 4.57 – External FTDI chip for converting between serial communication and the USB standard...<br>Figure 4.58 – Connection of pins from IDC-D on UCB to jumper wires of FTDI chip (seen in the top right of Figure 4.57) utilizes the signals of Tx, Rx, and a ground reference .....                                                                                                       | 72 |

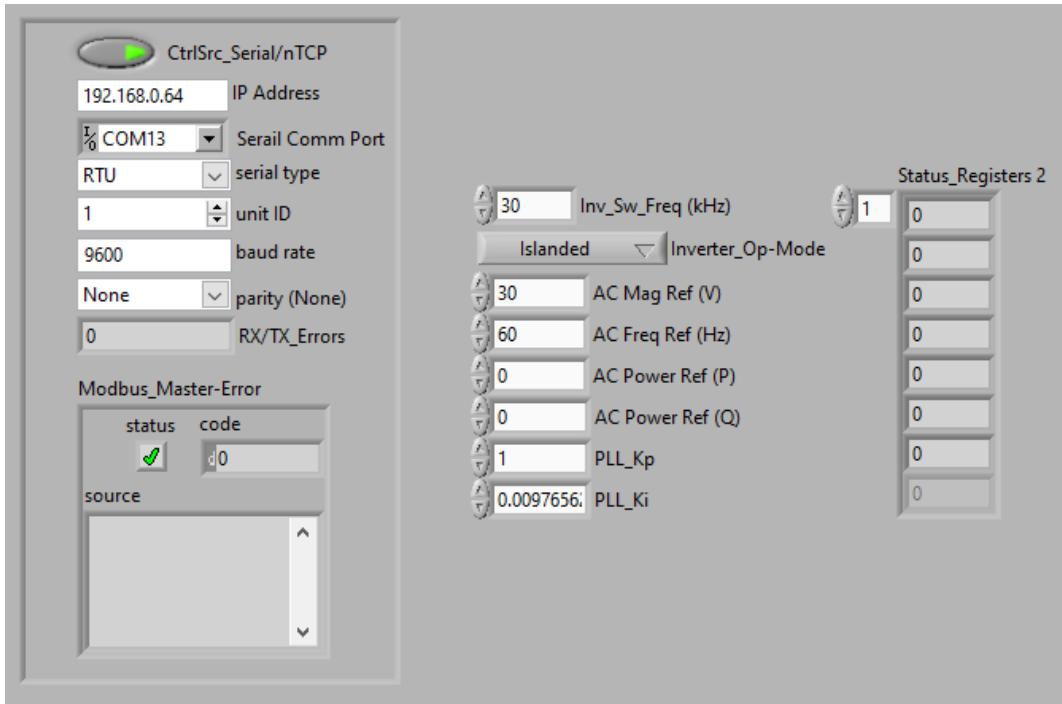

| Figure 4.59 – LabVIEW interface created to facilitate the testing of the embedded Modbus RTU algorithm, three columns (from left to right) represent the configuration setup and error reporting, the register values to write, and the register values being read, respectively .....                                                                                                            | 74 |

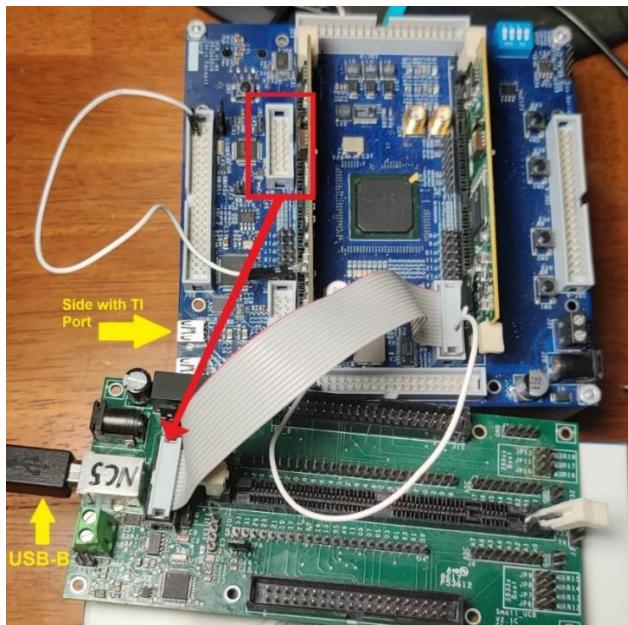

| Figure 4.60 – UCB connected with a “Small UCB” (seen in green) through a ribbon cable to provide access to the external debugger for troubleshooting with Code Composer Studio.....                                                                                                                                                                                                               | 75 |

| Figure 4.61 – Results from testing the average time to fulfill a Modbus RTU read and write command on a Windows device .....                                                                                                                                                                                                                                                                      | 77 |

| Figure 4.62 - Results from testing the average time to fulfill a Modbus RTU read and write command on a Linux device .....                                                                                                                                                                                                                                                                        | 77 |

| Figure 4.63 - Results from testing the accuracy of data for 10,000 iterations of Modbus RTU read and write commands; the results were nominal, all data passing the accuracy check.....                                                                                                                                                                                                           | 78 |

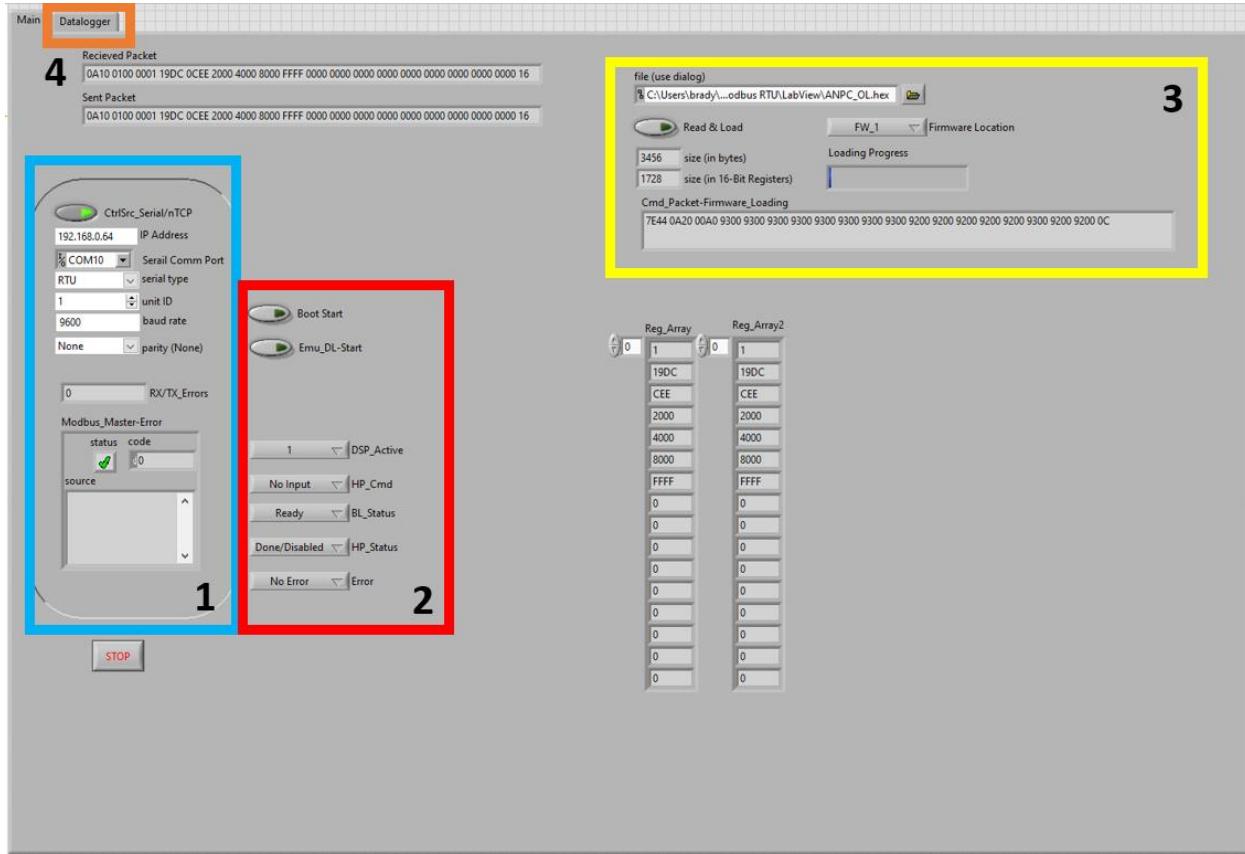

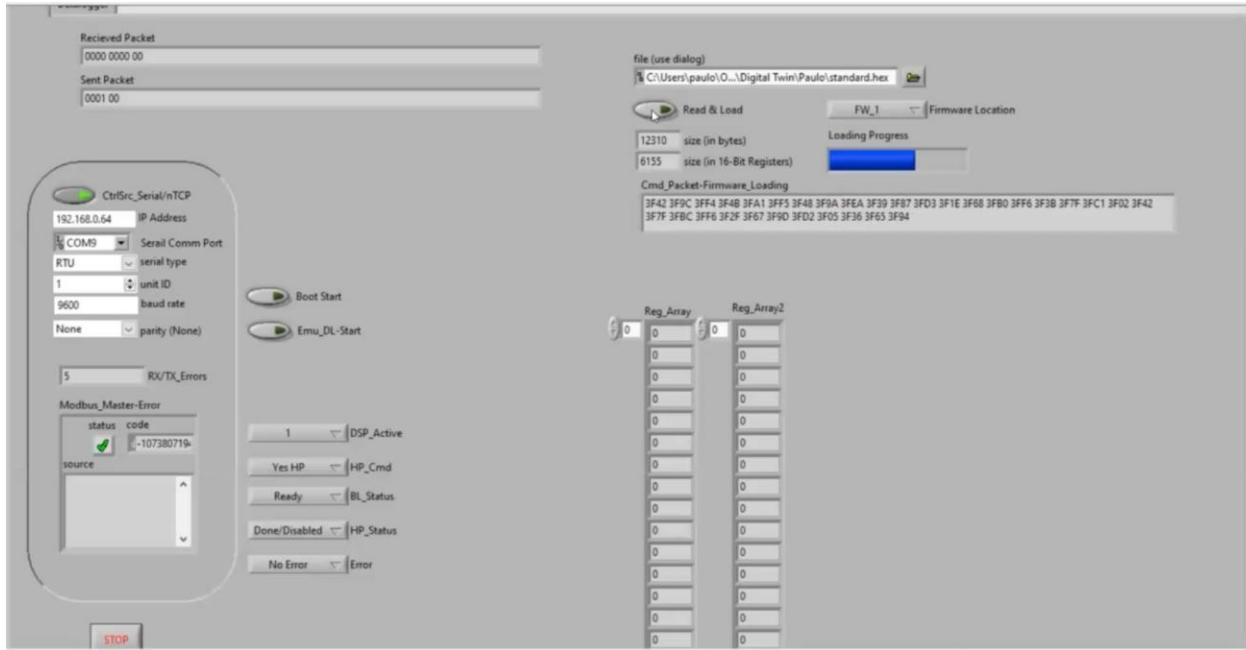

| Figure 4.64 – LabVIEW HMI for bootloader and hotpatching features of the SETO project, 1) (blue) configuration settings for Modbus RTU, 2) (red) interface for bootloading, digital twin emulation, hotpatching, and DFTTr, 3) (yellow) interface for bootloading of ANPC inverter firmware and status indicator, 4) (orange) datalogger for digital twin ANPC inverter emulation waveforms ..... | 79 |

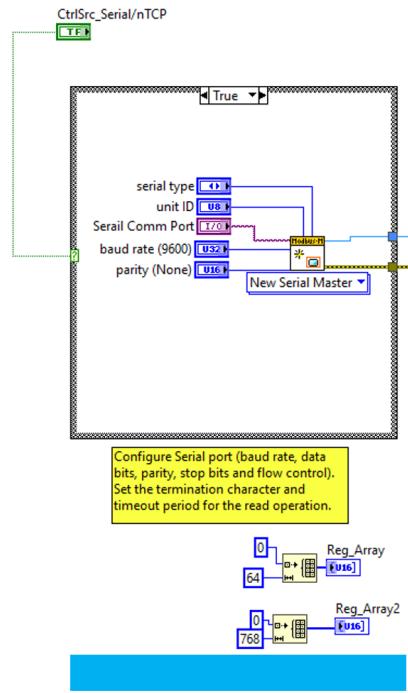

| Figure 4.65 – LabVIEW HMI backend of Modbus RTU configuration settings shown in Figure 4.64 .....                                                                                                                                                                                                                                                                                                 | 80 |

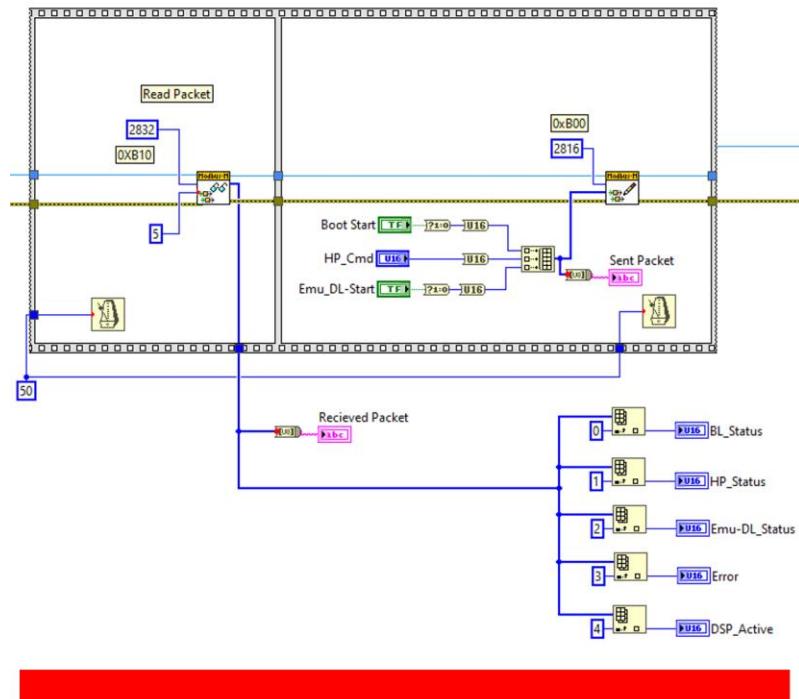

| Figure 4.66 - LabVIEW HMI backend of interface and indicators for bootloading, digital twin emulation, hotpatching, and DFTTr showed in Figure 4.64 .....                                                                                                                                                                                                                                         | 80 |

|                                                                                                                                                                                                                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

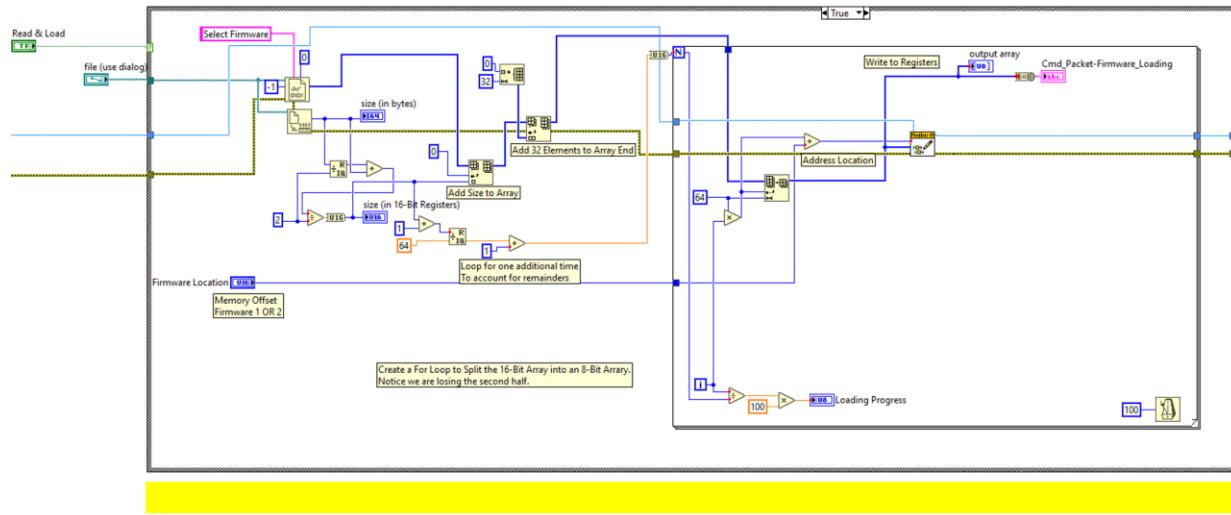

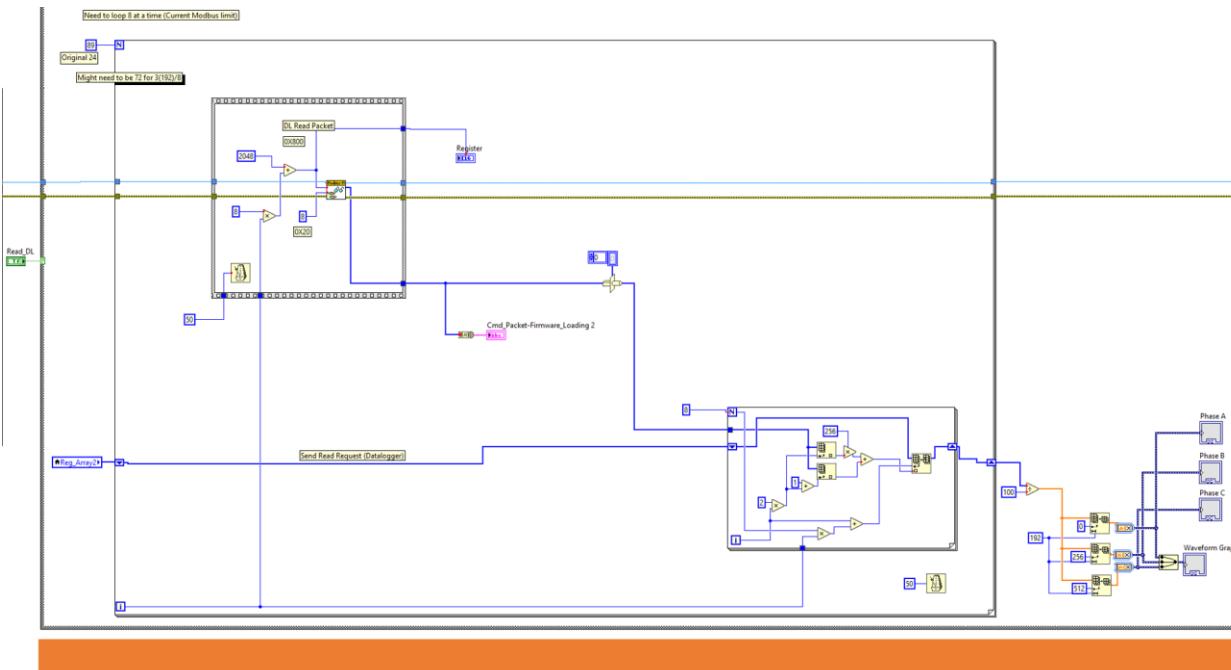

| Figure 4.67 - LabVIEW HMI backend of bootloading process of ANPC inverter firmware and status indicator shown in Figure 4.64 .....                                                                                                                                                                          | 81 |

| Figure 4.68 - LabVIEW HMI backend of datalogger of the Digital Twin emulation of ANPC inverter shown in Figure 4.64 .....                                                                                                                                                                                   | 81 |

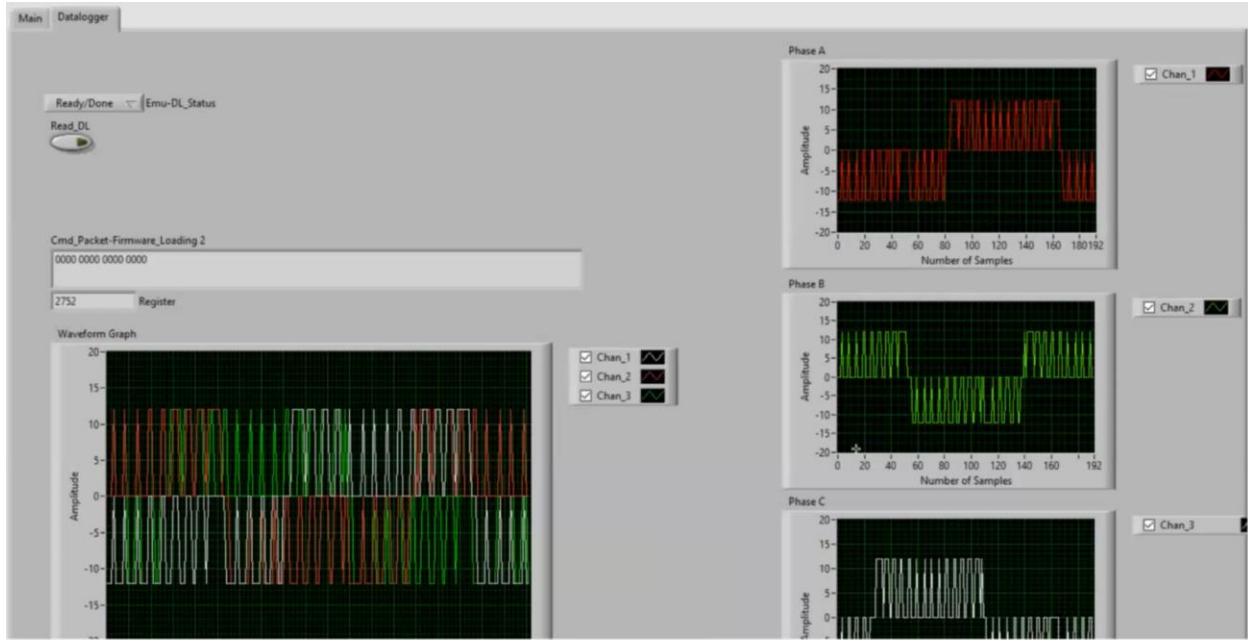

| Figure 4.69 – LabVIEW HMI running the bootloader sequence to load inverter controller firmware into the ANPC inverter Digital Twin of the SETO project for the firmware validation of the DFT <sub>r</sub> module .....                                                                                     | 83 |

| Figure 4.70 – LabVIEW HMI datalogger view of ANPC inverter controller output waveforms of a three-phase system .....                                                                                                                                                                                        | 84 |

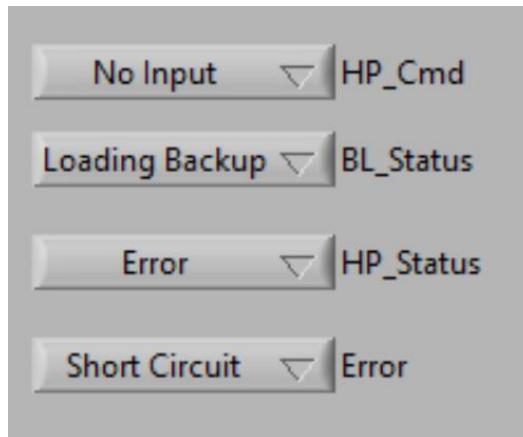

| Figure 4.71 – LabVIEW HMI interface output of results of DFT <sub>r</sub> SETO module indicating a short circuit error exists in the inverter controller firmware .....                                                                                                                                     | 85 |

| Figure 4.72 – Diagram of a typical industry method for implementing Modbus RTU within an embedded system using external storage to house the related Modbus RTU C code and a method of retrieving the code to be executed from the external storage.....                                                    | 86 |

| Figure 4.73 – Comparison of typical industry embedded processor-based Modbus RTU implementation and the embedded Modbus RTU presented in this work.....                                                                                                                                                     | 87 |

| Figure 4.74 - Resource allocation comparison within the FPGA of the project without (left) and with (right) the three embedded Modbus RTU instantiations .....                                                                                                                                              | 87 |

| Figure 5.75 - State diagram of the next-state-logic algorithm used for the processing and fulfillment of the Modbus RTU command response received by the slave device modified with the AES-128 encryption and SHA-256 message authentication IP cores (seen in black) incorporated into the algorithm..... | 91 |

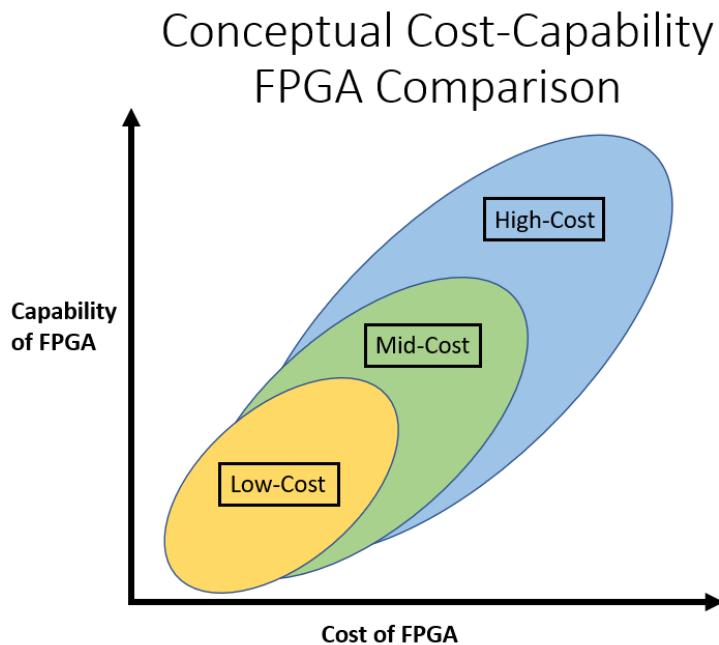

| Figure 5.76 – Conceptual comparison between the capabilities of an FPGA with respect to cost .....                                                                                                                                                                                                          | 92 |

## **List of Tables**

|                                                                                              |    |

|----------------------------------------------------------------------------------------------|----|

| Table 1 – Modbus RTU Function Commands.....                                                  | 13 |

| Table 2 – Modbus RTU Framing Time Measurements.....                                          | 47 |

| Table 3 – Register mapping for local RAM of Modbus RTU packet structure components .....     | 65 |

| Table 4 – Comparison of resources between Lattice's MachXO2-7000HC and MachXO3D-9400HC ..... | 93 |

### List of Abbreviations

|        |                                                          |

|--------|----------------------------------------------------------|

| ADC    | Analog to Digital Converter                              |

| ASM    | Algorithmic State Machine                                |

| CBA    | Common Bus Architecture                                  |

| CCS    | Code Composer Studio                                     |

| CLB    | Configurable Logic Block                                 |

| CRC    | Cyclical Redundancy Check                                |

| CPLD   | Complex Programmable Logic Device                        |

| DER    | Distributed Energy Resource                              |

| DOE    | Department of Energy                                     |

| DT     | Digital Twin                                             |

| EBR    | Embedded Block RAM                                       |

| EEPROM | Electrically Erasable Programmable Read-Only Memory      |

| FIFO   | First-In-First-Out                                       |

| FPGA   | Field Programmable Gate Array                            |

| HDL    | Hardware Description Language                            |

| HMI    | Human Machine Interface                                  |

| ICS    | Industrial Control System                                |

| IDC    | Insulation-Displacement Contact                          |

| IP     | Intellectual Property                                    |

| I/O    | Input/Output                                             |

| LUT    | Lookup Table                                             |

| MBAP   | Modbus Application Protocol                              |

| MUX    | Multiplexer                                              |

| NCREPT | National Center for Reliable Electric Power Transmission |

| NSL    | Next State Logic                                         |

| PCB    | Printed Circuit Board                                    |

| P&R    | Place-and-Route                                          |

| RAM    | Random Access Memory                                     |

| RPi    | Raspberry Pi                                             |

| RTU    | Remote Terminal Unit                                     |

| SCADA  | Supervisory Control and Data Acquisition                 |

| SETO   | Solar Energy Technologies Office                         |

|      |                                                                  |

|------|------------------------------------------------------------------|

| SoC  | System-on-Chip                                                   |

| SPI  | Serial Peripheral Interface                                      |

| TCP  | Transport Control Protocol                                       |

| TI   | Texas Instruments                                                |

| UCB  | Unified Controller Board                                         |

| VHDL | Very High-Speed Integrated Circuit Hardware Description Language |

## Chapter 1

### Introduction

#### 1.1 – Motivation

The modern power grid is an essential component of our critical infrastructure that plays a significant role in contemporary society. Our reliance on the availability and reliability of the electric utility grid makes it an essential component to facilitate the needs of individuals, such as performing a role in providing access to food, clean water, and sanitary conditions. Beyond servicing critical needs, the power grid is in virtually every amenity and aspect of our daily lives. As society continues to grow and develop, the demands on the electric power grid continue to increase. Additionally, with more substantial considerations of where this power is sourced, the transition to alternative sources, such as renewable energy, is continually in demand [1]. This newfound transition to renewable energy is often achieved with distributed energy resources (DERs), which naturally require network communication and coordination with the larger power grid. This, combined with a push for a “smart grid” to service society’s electrical needs with a more efficient and resilient electric grid, has increased the complexity of this critical infrastructure. To address the dynamically changing demands of the modern power grid, there has been a rise in the addition of network-connected grid devices [2].

While the addition of communication and networking infrastructure into the electric grid supports a more effective and efficient system, this change also introduces additional vulnerabilities to which these systems were not previously prone. Cyber attackers can utilize these networks to traverse once-isolated systems and gain access to previously “untouchable” critical infrastructure. As more critical components of the electric grid are connected to various networks, a resulting increase in the occurrences and the potential threat for cyber-physical attacks is undesirable [3]. In response to the looming threat of cyber-attacks on society’s critical infrastructures, governments such as the federal government of the United States have increased funding towards critical infrastructure improvements to enhance the electric grid’s resiliency and cyber defense capabilities [4]. To effectively address both the cyber and physical demands at a dynamic level, researchers need focused and effective efforts to respond to these problems.

As the growing availability of improving technologies is coupled with the widespread efforts of retrofitting the electric power grid to meet the ever-increasing energy demands, improvements in how these evolving technologies and techniques are utilized must be introduced. As the market transition to alternative energy sources arises, so does the necessity for cost-effective and impactful power and cyber-physical research solutions and methods to this problem. Money and time are two of the most imperative and finite resources required to address these issues. To continue creating more reliable and resilient critical infrastructure, adequate financing to support these efforts is essential. The time required to foster these innovations is arguably equal to the funding of these research efforts is the time required to foster these innovations. As the threat of cyber-attacks is consistent and growing, it is imperative to respond proactively and with swiftness.

To address the challenges of substantial research investments regarding money and time, improving efforts to lower solution costs while increasing collaborative research productivity is paramount. As technological advancements in the electric power grid require improved or additional electronic hardware, one method of reducing financial expenses is to utilize equipment with a lower fiscal cost. The drawback often seen with the reduction in the price of more affordable equipment and hardware is a comparable reduction in these devices' capability and computational resources. Thus, a lower-cost implementation requires research solutions that function on hardware with lower computational capabilities. Presenting research solutions that minimize the required computational and hardware resources effectively addresses the constant challenge of limited fiscal resources. The second finite resource is time. Bad actors are always persistent in their efforts to improve their cyber-attack capabilities. To be proactive in meeting these often-restless adversaries, vital considerations to the development time for research solutions must be made. By standardizing components of the research efforts, an increase in progress efficiency among collaborators is possible. In research, multiple entities often collaborate on the same project while being geographically distanced. By providing standardized solutions and components, researchers have a common platform during the design and development phase that promotes rapid prototyping between collaborators.

The Modbus RTU communication protocol is widely adopted within Industrial Control Systems (ICS). This communication protocol is commonly used as a standardized method of communication as it is open-source and known for being reliable. Embedded systems, such as FPGAs, are often used in ICS applications [5]. These embedded systems can integrate serial communication capabilities, such as Modbus RTU. An embedded processor architecture is a typical method of providing embedded systems with Modbus RTU functionality. These embedded processor architectures are often called “Intellectual Property cores” or “IP cores.” Embedded processors utilize logical algorithms to describe the embedded processor architecture and essentially function as a processor inside an embedded system, such as an FPGA. These embedded processors are then used to execute code from higher-level programming languages such as C. Such an implementation of the Modbus communication protocol using the ARM Cortex-M0 embedded processor can be seen in [6]. A similar method of Modbus RTU implementation within an embedded Linux system can be seen in [7]. These researchers continued their work to develop a data acquisition and monitoring system can be seen in [8] that is based on the embedded processor-operated Modbus RTU of [7]. The work presented in [9] is an example of using an embedded processor to utilize the Modbus RTU communication protocol to control an industrial plant (crop) factory system. The work in [10] utilizes an ARM Cortex A-9 embedded processor to utilize Modbus RTU to manage the communication in their production control system.

This thesis presents the design and development of a Modbus RTU communication protocol implementation using VHDL within an FPGA that does not require an embedded processor. Thus, the required resources to utilize the Modbus RTU communication protocol are less when compared with the typical industry method of using an embedded processor. This reduction in required resources addresses the concern of cost-effective and resource-efficient solutions for communication within embedded systems. This custom Modbus RTU communication protocol resides within a low-cost FPGA mounted within a Unified Controller Board (UCB) to provide standardized communication to support multiple modules within the controller architecture for a multi-level cyber-hardened solar inverter. This approach provides a standardized serial communication protocol that operates as the routing fabric and communication between cyber-defense-related modules within the controller of a solar inverter. Implementing the Modbus RTU communication protocol was successfully developed while keeping the

required space smaller than typical embedded processor-based implementations. This work will discuss the design and development of an embedded Modbus RTU implementation designed to work within a low-cost FPGA while providing researchers with a reliable and resilient communication protocol to support data transmission.

## **1.2 – Solar Energy Technologies Office Project Contribution**

The work presented in this thesis contributes to a greater project sponsored by the Department of Energy (DEO) Solar Energy Technologies Office (SETO). This SETO project is named “Multilevel Cybersecurity for Photovoltaic Systems” and addresses cybersecurity at both the inverter and system levels for photovoltaic energy systems. The embedded Modbus RTU implementation in this thesis contributed to this SETO project by providing a common and standardized data transmission point throughout the inverter controller architecture. The Modbus RTU implementation controls the FPGA’s routing fabric, giving access to shared memory for multiple modular cybersecurity-focused components within the inverter controller architecture. Further details regarding the SETO project and its relevance to this thesis’ contents will be discussed in Chapter 3.

## **1.3 – Thesis Organization**

The list below sequentially outlines the contents and structure of this thesis:

- Chapter 1 discusses the motivation for designing and developing a Modbus RTU implementation using VHDL within an FPGA to provide a standardized serial communication protocol that utilizes fewer hardware resources.

- Chapter 2 defines the background concepts and fundamental knowledge considered in the design process. Additionally, this chapter discusses additional information that may be pertinent to the reader, such as topics related to hardware, communication protocols, and coding.

- Chapter 3 explains the system components and the design and development for creating the custom Modbus RTU implementation. Additionally, this chapter will discuss in further detail the involvement and application of this Modbus RTU implementation concerning the greater efforts of the SETO project.

- Chapter 4 demonstrates the experimental test setup and results of the various testing phases for this work. This chapter will discuss testing involving simulations, hardware, application, and the resiliency of this implementation.

- Chapter 5 concludes this design and development of the Modbus RTU communication protocol within an FPGA. This chapter also discusses additional steps taken to increase the throughput of this communication implementation. It outlines recommendations and actions to use encryption and message authentication techniques to secure packet contents when transmitting data.

## Chapter 2

### Background

#### 2.1 – Introduction

As mentioned in the previous chapter, the primary motivation for this work is to provide a method of standardized communication to assist with improving the effectiveness of research efforts while simultaneously reducing the associated costs. As the risk of cyber-physical attacks and events is a constant and ever-moving target, it is imperative to be proactive and adequate to address these threats. The solutions presented by researchers and industry professionals must be current and conscious of these changing challenges and the limited resources available to manage them. These contemporary concerns are addressed regarding communication systems by implementing the Modbus RTU communication protocol within a standardized embedded device that requires fewer resources than typical embedded methods. The remainder of this chapter will discuss the concepts of the Modbus RTU communication protocol and the pertinent information regarding serial communication, associated hardware, and power electronics.

Additionally, the work presented in this thesis is in conjunction with a greater project focused on improving the cyber-physical security of power grid congrid-connected photovoltaic energy generation farms. This project is funded by the U.S. Department of Energy (DOE) Solar Energy Technologies Office (SETO) and is titled “Multilevel Cybersecurity for Photovoltaic Systems” (Award #DE-EE0009026).

#### 2.2 – Power Electronics and SMA Inverter

As mentioned in the introduction of this section, the work presented in this thesis covers the contributions of developing the communication protocol implementation for developing a cyber-hardened photovoltaic inverter. The solar inverter used in this research project is an SMA Sunny Highpower PEAK 3 utility grid-connected photovoltaic (PV) inverter (henceforth referred to as an “SMA inverter”). This SMA inverter is a 60 Hz commercial off-the-shelf grid-connected PV inverter rated for 1500 volts of direct current (VDC) for 125 kW of power [11].

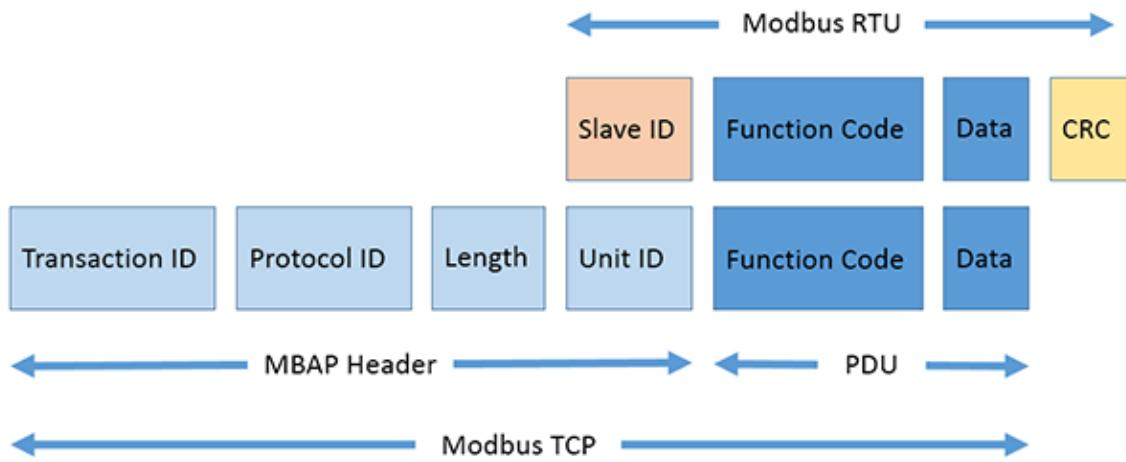

The SMA inverter is integrated with a Modbus interface that allows the device to communicate with various modules utilizing the Modbus communication protocol. This SMA inverter supports the Modbus TCP and Modbus UDP configurations of the Modbus communication protocol. Modbus TCP allows for both the reading and writing of registers, while Modbus UDP only supports the writing of registers. While the work presented in this thesis discusses developing a Modbus implementation using the Modbus RTU configuration, the existing hardware in the controller architecture allows for the conversion of Modbus RTU to that of Modbus TCP. This topic will be discussed in more detail in Chapter 2.5 and Chapter 3.2.1.

The SMA interface supporting the Modbus communication protocol was a significant determining factor in developing a Modbus RTU communication protocol implementation for this project. Modbus is a standardized communication protocol widely used and supported in applications such as distributed industrial control systems and inverter-based technologies [12].

### 2.3 – Serial Communication

Serial communication is a method that sequentially transmits data over a communication bus, bit-by-bit, as seen in Figure 2.1. This data transmission configuration only requires a few wires to send signals between devices. Thus, the infrastructure needed for serial communication is relatively low [13]. Within the family of serial communication, several communication standards exist. Two of the most common communication standards are RS-232 and RS-485. This project implements Modbus RTU under the RS-232 communication standard and will be the primary standard of discussion.

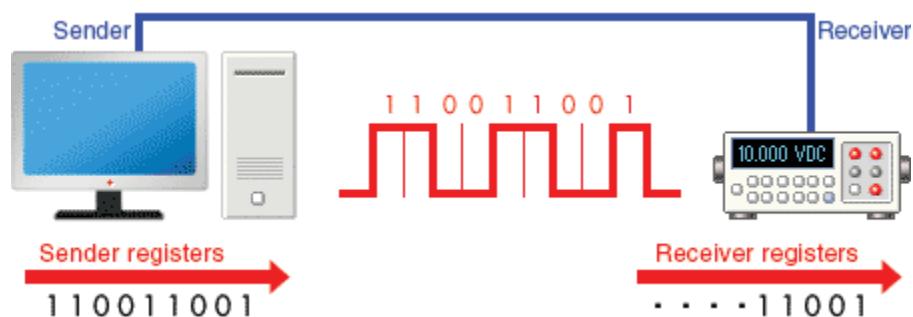

Figure 2.1. Sequential data transmission of serial communication [13]

Serial communication supports asynchronous and synchronous data transfer. In synchronous data transfer, the transmission of each bit of data is controlled by an external clock signal shared between the sending and receiving devices. This synchronization with a clock signal ensures that the data transfer across the communication pathway is coordinated and the interpretation of the data is read. This configuration requires additional infrastructure as the communication method's integrity relies on the synchronization between the sending and receiving devices [14]. As opposed to synchronous data transfer, asynchronous data transfer requires less infrastructure to implement as it is not reliant on a clock signal to orchestrate the transfer of data. Asynchronous data transfer sends a serial bit stream at a predetermined transmission rate. The message is then interpreted by the receiving device while reading the data bit-by-bit at the predetermined transmission rate. This data transmission rate is called the "baud rate" and represents the number of bits transmitted per second [14].

### 2.3.1 – RS-232 Serial Communication Standard

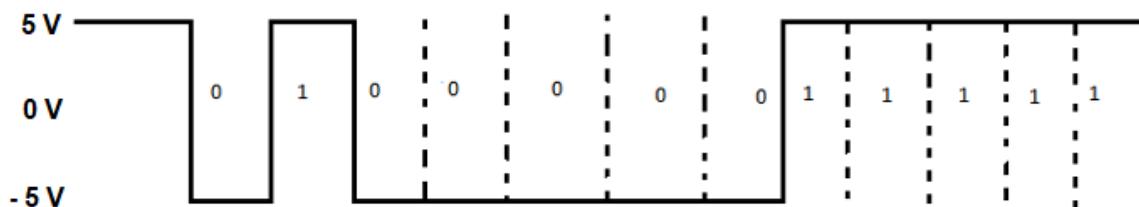

The RS-232 communication standard outlines the signals connected from the transmitting and receiving devices and characterizes the signals' electrical characteristics. The serial data exchange in the RS-232 standard protocol is carried out by controlling the voltage level on the communication bus and the rate the data is transmitted. To indicate a binary '0' or binary '1' signal on the communication line, the voltage level is modified with respect to a ground reference. The binary value of '0' is asserted when the voltage level of +3 V to +13 Vdc is read on the line, and a binary value of '1' is declared when the voltage level is -3 V to -13 Vdc [14]. A diagram of the voltage-binary logic can be seen in Figure 2.2

Figure 2.2. Voltage-Binary logic of RS-232 communication protocol [14]

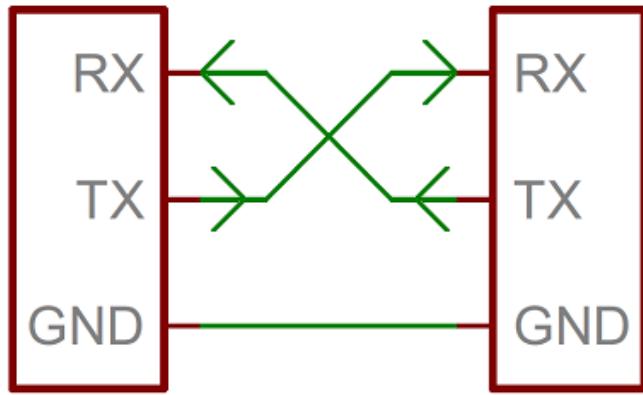

The most basic wiring configuration to carry out serial communication requires three signal connections: Transmit (TX), Receive (RX), and Ground (GND). This wiring configuration can be seen in Figure 2.3. The wire connection from the transmitting device's TX port is fed into the port of the receiving device's RX port and vice versa. The voltage level across these signal lines is then changed to indicate the previously mentioned binary '0' or '1' value depending on the voltage with reference to the shared ground wire. This communication bus infrastructure allows for a dedicated signal pathway for both directions from each device's perspective. This configuration is called "full duplex" and allows for the simultaneous sending and receiving of data on each bus communication line [13].

Figure 2.3. Three-wire serial communication connection diagram [15]

### 2.3.2 – Universal Asynchronous Receiver-Transmitter (UART)

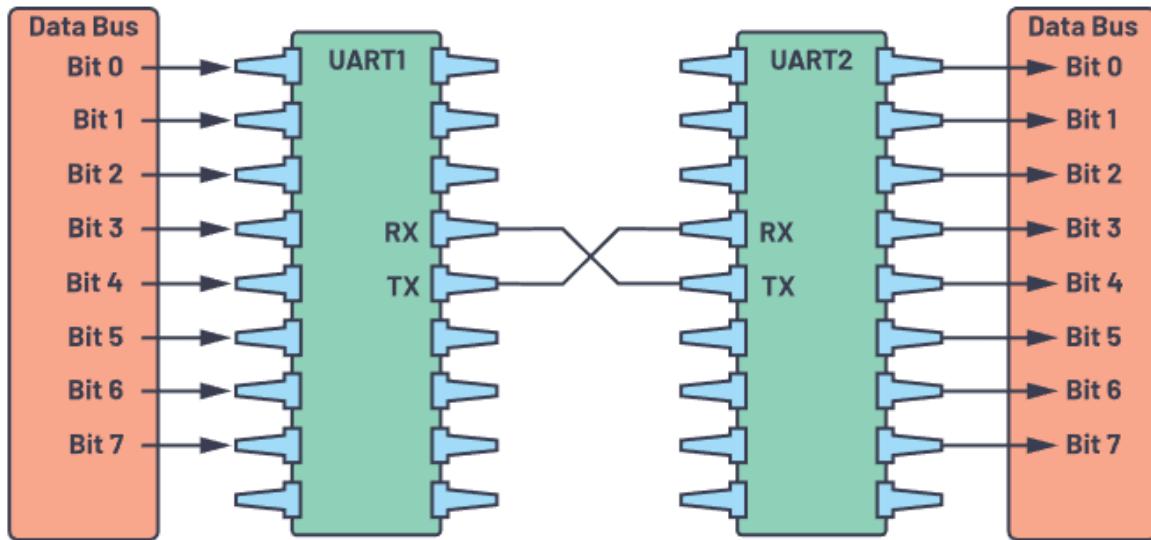

Universal Asynchronous Receiver-Transmitter (UART) is used by embedded systems as a method for device-to-device hardware communication [16]. This system utilizes a three-wire setup to carry out the communication between devices. As this is an asynchronous system, a clock signal is not used to synchronize the output of transmission bits.

UART is configured to send data across a serial bus from one UART interface to another. A UART interface processes data in parallel, as seen in Figure 2.4, and sends that data across a serial bus line at a predetermined baud rate. As the data is sent sequentially, the UART system must frame the data in a manner that allows the system to determine when the start and stop of transmission are received. This process is referred to as "data framing" and consists of four components: start bit, data frame, parity,

and stop bit(s) [16]. These components together create the packet structure of the data transmission, as shown in Figure 2.5. A UART transmission line maintains a high voltage when waiting to receive data transmission. Then, it reads the incoming data when the line is pulled low by the incoming binary '0' of the start bit. The size of the data frame is predetermined in the transmission configuration. Once the start bit is active, the UART device will process the incoming data at the predetermined baud rate. The parity bit allows the UART system to determine if the received message was error-free. To determine if the parity bit is to be a binary '0' or '1', the number of bits with a binary '1' value is counted. If the number of binary '1's' in the data frame is even, then the data frame is considered to have "even parity," and the even parity bit is asserted by the transmitting device. This same parity calculation is done by the receiving device to confirm that the calculated parity value during the transmission was correct. Finally, the stop bit returns the voltage level of the UART device to a high signal for one or two clock cycles (a predetermined number of clock cycles is used).

Figure 2.4. UART interface connection with Data Bus [16]

|                        |                                    |                               |                              |

|------------------------|------------------------------------|-------------------------------|------------------------------|

| Start Bit<br>( 1 bit ) | Data Frame<br>( 5 to 9 Data Bits ) | Parity Bits<br>( 0 to 1 bit ) | Stop Bits<br>( 1 to 2 bits ) |

|------------------------|------------------------------------|-------------------------------|------------------------------|

Figure 2.5. Packet structure of UART message [16]

## 2.4 – Modbus RTU

The Modbus RTU serial communication protocol is an open-source communication protocol widely adopted within the Industrial Control Systems (ICS) and automation industries. The packet structure of this communication protocol is relatively simple and is known for its reliability in carrying out serial communication. Because of the known reliability of this communication protocol, it is virtually supported in all communication infrastructure in the marketplace in the field of control systems and automation. The Modbus RTU communication protocol is typically implemented within an RS-232 or RS-485 interface [17].

The Modbus RTU communication protocol connects a supervisory or controlling device to a Remote Terminal Unit (RTU) within ICS and automation systems. This configuration is typical in supervisory control and data acquisition (SCADA) systems, where a master (client) device is responsible for communicating with one or more slave (server) devices to carry out data-based algorithms or controls. The high-level operation of the master and slave relationship consists of the master device sending a command to the slave device. This command is then deciphered, verified for integrity, and carried out by the slave device. These actions consist of two fundamental operations: reading and writing data. This data transmission may then be used to carry out control algorithms or functions of the system as intended.

The essential function of the Modbus RTU communication protocol is to connect various control instrumentation to logic controllers or to provide a data transmission pathway between two systems that are reliant on sharing data. The bulk of this thesis will focus on the latter, where the implementation design and goal are to be capable of transmitting data between various systems. Additionally, the scope of this work only requires the ability to read and write data to and from holding registers. Thus, the remainder of this background section will focus on the information pertinent to data movement between holding registers using Modbus RTU and any associated methods or communication protocol transformations.

#### **2.4.1 – Data Representations and Configurational Parameters**

Data transmission within the Modbus RTU communication protocol occurs at a predetermined baud rate and must be maintained at both the transmitting and receiving devices. Baud rates are typically standardized and occur at 9600, 19200, or 115200. This work was initially created to operate at a baud rate of 9600 bits-per-second. The potential to drive at higher baud rates, customize, and scale will be discussed in Chapter 5.

The Modbus communication protocol supports the transmission of two types of data: coils and holding registers. Coils represent a single bit of data, typically as a Boolean value of binary '1' or '0', respectively 'ON' or 'OFF' in an active high scenario. These coils represent the discrete status value of a system where an application may be a variable being asserted, indicating the status of a system. Holding registers represent 16-bit unsigned values capable of representing the hexadecimal values from 0x000 to 0xFFFF (0 to 65535) [17].

The first two bytes of a Modbus RTU packet contain the value of the device ID or the identifying value for which device the transmission is intended. If a device receives a message with a device ID matching its own, it carries out the command request from the master device. The value of the device ID can vary from 0x01 to 0XFF (1 to 255), where 0x00 (0) is reserved for a specific broadcast function. The broadcast function is intended for the master to send a command to all slave devices to be fulfilled by all devices.

#### **2.4.2 – Read and Write Commands**

The Modbus communication protocol uses a master and slave relationship architecture to perform the function commands based on the received function code. In this architecture, a master device is responsible for issuing orders to the slave device. The slave device responds to those commands and fulfills the requested operation. Modbus RTU supports eight different function operations that can be used to read or write from discrete coils or holding registers, denoted by their unique respective function codes. The eight supported function codes for these data types can be seen in Table 1.

Table 1 – Modbus RTU Function Commands

| Function Code    | Function Operation              | Data Value Type |

|------------------|---------------------------------|-----------------|

| <b>0x01 (01)</b> | Read Coil                       | Discrete        |

| <b>0x02 (02)</b> | Read Input Status               | Discrete        |

| <b>0x03 (03)</b> | Read Multiple Holding Registers | 16-bit          |

| <b>0x04 (04)</b> | Read Input Registers            | 16-bit          |

| <b>0x05 (05)</b> | Write Single Coil               | Discrete        |

| <b>0x06 (06)</b> | Write Single Holding Register   | 16-bit          |

| <b>0x0F (15)</b> | Write Multiple Coils            | Discrete        |

| <b>0x10 (16)</b> | Write Multiple Registers        | 16-bit          |

The remainder of this thesis will discuss the reading and writing of holding registers using the Modbus RTU communication protocol. This is due to the scope of work for the greater project only requiring access to data stored in holding registers. Additionally, as this thesis covers a custom implementation of the Modbus RTU communication in an embedded system, the required resources were able to be minimized by only containing a partial implementation of the Modbus RTU protocol. The utilized read and write function codes for this project are 0x03 and 0x10 which represent the actions to read and write multiple holding registers, respectively.

#### 2.4.3 – Packet Structure

The Modbus RTU packet structure consists of two main configurations, read packets and write packets, while each packet structure can further be broken down into multiple components. A Modbus RTU packet's components are device address (ID), function code, address of a register in memory, number of registers requested, number of bytes more in the packet transmission, the data values, and the checksum.

The device address (ID) denotes the unique identifier for the slave device. Each slave device is programmed to only respond to requests explicitly made to itself. The function code is the operation carried out, such as reading or writing to holding registers. The address of the register in memory is the

value that indicates where the data being read or written is coming from or being written in memory. This data is separated into high (“Hi”) and low (“Lo”) bytes to form 16-bit data. The number of registers requested specifies how many registers are to be read or written to. The value for the number of bytes more indicates how many additional bytes of data will be following this value in the serial data stream. This is used to point to the device how much more data it is to expect to be coming through the serial transmission. The data values represent the data being read from memory or written to memory. This data is separated into high (“Hi”) and low (“Lo”) bytes to form 16-bit data. Finally, the checksum cyclical redundancy check (CRC) is a calculation performed by the master and slave device to verify message integrity.

In addition to the components of the reading and writing of holding registers, there are packet components for error handling. An error message is sent in response to a command request from the slave device back to the master device when a command cannot be carried out for any reason. The additional components of the error message are the modified function code indicating to the master that the slave device experienced an error and the error code indicating what the error experienced was.

### Breakdown of Packet Structure

An example of the packet structure of a Modbus RTU transmission issuing a read command can be seen below in Figure 2.6. To break down each component of this packet structure, the remainder of this subsection will go over each component in sequentially highlighted figures.

| Packet Component | Device Address | Functional Code | Address of First Register - Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Checksum CRC - Lo Byte | Checksum CRC - Hi Byte |

|------------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|------------------------|------------------------|

| Byte (Hex)       | 11             | 03              | 00                                  | 6B                                  | 00                            | 03                            | 76                     | 87                     |

Figure 2.6 – Modbus RTU read holding register command

The first component of the Modbus RTU packet structure is the device address, which can be seen below in Figure 2.7, highlighted in brown. The device address component is an 8-bit unique identifier that is used to dictate which slave device a command is intended for. Each slave device has its

own unique device address and is programmed to only respond to messages addressed to its unique device identifier. The next component is the function code, or operational code, which can be seen below in Figure 2.7, highlighted in blue. This function code indicates to the slave device what the requested operation is. In this example, the requested operation is hexadecimal 0x03, which indicates the operation requested is a read command.

| Packet Component | Device Address | Functional Code | Address of First Register - Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Checksum CRC - Lo Byte | Checksum CRC - Hi Byte |

|------------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|------------------------|------------------------|

| Byte (Hex)       | 11             | 03              | 00                                  | 6B                                  | 00                            | 03                            | 76                     | 87                     |

Figure 2.7 – Read holding register breakdown 1 of 3

The next component of the packet structure is the address of the first register in the request, which can be seen below in Figure 2.8, highlighted in brown. This is a 16-bit value that indicates what the first address in memory is to index the read request. This packet component is sent in two 8-bit values representing the Hi and Lo bytes of the 16-bit value. The next component in the packet structure is the number of registers to read, which is shown below in Figure 2.8, highlighted in blue. This is a 16-bit value that indicates how many registers are to be read back to the master device. This packet component is sent in two 8-bit values representing the Hi and Lo bytes of the 16-bit value.

| Packet Component | Device Address | Functional Code | Address of First Register - Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Checksum CRC - Lo Byte | Checksum CRC - Hi Byte |

|------------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|------------------------|------------------------|

| Byte (Hex)       | 11             | 03              | 00                                  | 6B                                  | 00                            | 03                            | 76                     | 87                     |

Figure 2.8 – Read holding register breakdown 2 of 3

The final component of the Modbus RTU packet structure is that of the cyclical redundancy check (CRC). The CRC is a 16-bit value that is calculated and sent with the message contents. The calculation method of the CRC will be discussed in section 2.4.4. The role of the CRC is to confirm message integrity

and validity through a cyclical and robust algorithm of calculations and data modification. This packet component is sent in two 8-bit values representing the Hi and Lo bytes of the 16-bit calculated value. This packet component has its Hi and Lo bytes switched, where the Lo byte is sent before the Hi byte.

| Packet Component | Device Address | Functional Code | Address of First Register - Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Checksum CRC - Lo Byte | Checksum CRC - Hi Byte |

|------------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|------------------------|------------------------|

| Byte (Hex)       | 11             | 03              | 00                                  | 6B                                  | 00                            | 03                            | 76                     | 87                     |

*Figure 2.9 – Read holding register breakdown 3 of 3*

### Read and Write Command and Response Structure

As the packet structure of a Modbus RTU request command is arranged in a certain manner, the response packet sent back from the slave device to the master device is similarly structured. While the read and write packets have similar packet components, there are some significant differences in the resulting message packet. The remainder of this subsection will discuss the request message and the responding message of both read and write commands, respectively.

First, the read command from the master device and the read response from the slave device for the Modbus RTU communication protocol are discussed. The packet structure of both the command and response can be seen below in Figure 2.10. From the figure, the read command sent from the master device is intended for the device with the unique device address of 0x11, and the function code of 0x03 indicates a request to read multiple holding registers. The address to index of the first register to be read is 0x006B, and the master device is requesting 0x0003 (3) 16-bit registers. Finally, the CRC is calculated and attached to the end of the Modbus RTU packet.

After this read holding register command request is sent from the master device, the slave device fulfills the request by providing data from the requested holding registers. The first two 8-bit components of the response packet contain the device address and function code repeated back from the original read request. The next component is an 8-bit value that represents how many more bytes of data will exist in the remainder of the packet transmission, excluding the CRC component. This portion is so the

master device knows how much data it is expecting to receive in the transmission. The CRC value is the final component attached to the packet structure of the read response.

| Packet Component | Device Address | Functional Code | Address of First Register - Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Checksum CRC - Lo Byte | Checksum CRC - Hi Byte |

|------------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|------------------------|------------------------|

| Byte (Hex)       | 11             | 03              | 00                                  | 6B                                  | 00                            | 03                            | 76                     | 87                     |

### ↑ Read Command

### ↓ Read Response

| Packet Comp. | Device Address | Functional Code | Number of Bytes More | ---- Data ----                        |                                       |                                       |                                       |                                       |                                       |  |  | CRC - Lo Byte | CRC - Hi Byte |

|--------------|----------------|-----------------|----------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|--|--|---------------|---------------|

|              |                |                 |                      | Register Value – 1 <sup>st</sup> Byte | Register Value – 2 <sup>nd</sup> Byte | Register Value – 3 <sup>rd</sup> Byte | Register Value – 4 <sup>th</sup> Byte | Register Value – 5 <sup>th</sup> Byte | Register Value – 6 <sup>th</sup> Byte |  |  |               |               |

| Byte (Hex)   | 11             | 03              | 06                   | AE                                    | 41                                    | 56                                    | 52                                    | 43                                    | 40                                    |  |  | 49            | AD            |

Figure 2.10 – Modbus RTU, read holding register command and response packet structure

Next, the write request and response will be discussed. The write command for holding registers has a similar structure to the read command. The first six bytes of the packet structure are the same for the write command as the read command. This contains the information of the device address, function code, address of the first register to index, and the number of registers to be written to the holding registers. The next byte of information in the request is the number of bytes of data that will be contained in the transmission. The next portion is the actual data that is to be written to the 16-bit registers. This data is separated into bytes by the Hi and Lo byte. Finally, the CRC is the last component of the Modbus RTU packet structure for the write command.

After the write command request is sent from the master device, the slave device fulfills the request by storing the data in memory and providing a confirmation that the requested data has been written to the associated holding registers. The write response packet structure is very similar to the packet header information contained in the write command. The first six bytes of the response packet are the same as the first six bytes of the command packet. This information is repeated back to the master

device from the slave device to confirm that the data was written to the holding registers at the requested location. The final component of the write response is the CRC packet component.

| Packet Comp. | Device Address | Functional Code | Address of First Register – Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Number of Bytes More | Register Value – 1 <sup>st</sup> Byte | Register Value – 2 <sup>nd</sup> Byte | Register Value – 3 <sup>rd</sup> Byte | Register Value – 4 <sup>th</sup> Byte | CRC - Lo Byte | CRC - Hi Byte |

|--------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|----------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------|---------------|

| Byte (Hex)   | 11             | 10              | 00                                  | 01                                  | 00                            | 02                            | 04                   | 00                                    | 0A                                    | 01                                    | 02                                    | C6            | F0            |

↑ Write Command

---- Data ----

↓ Write Response

| Packet Component | Device Address | Functional Code | Address of First Register - Hi Byte | Address of First Register - Lo Byte | Number of Registers - Hi Byte | Number of Registers - Lo Byte | Checksum CRC - Lo Byte | Checksum CRC - Hi Byte |

|------------------|----------------|-----------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------|------------------------|------------------------|

| Byte (Hex)       | 11             | 10              | 00                                  | 01                                  | 00                            | 02                            | 12                     | 98                     |

Figure 2.11 - Modbus RTU, write holding register command and response packet structure

#### 2.4.4 – Cyclical Redundancy Check (CRC)

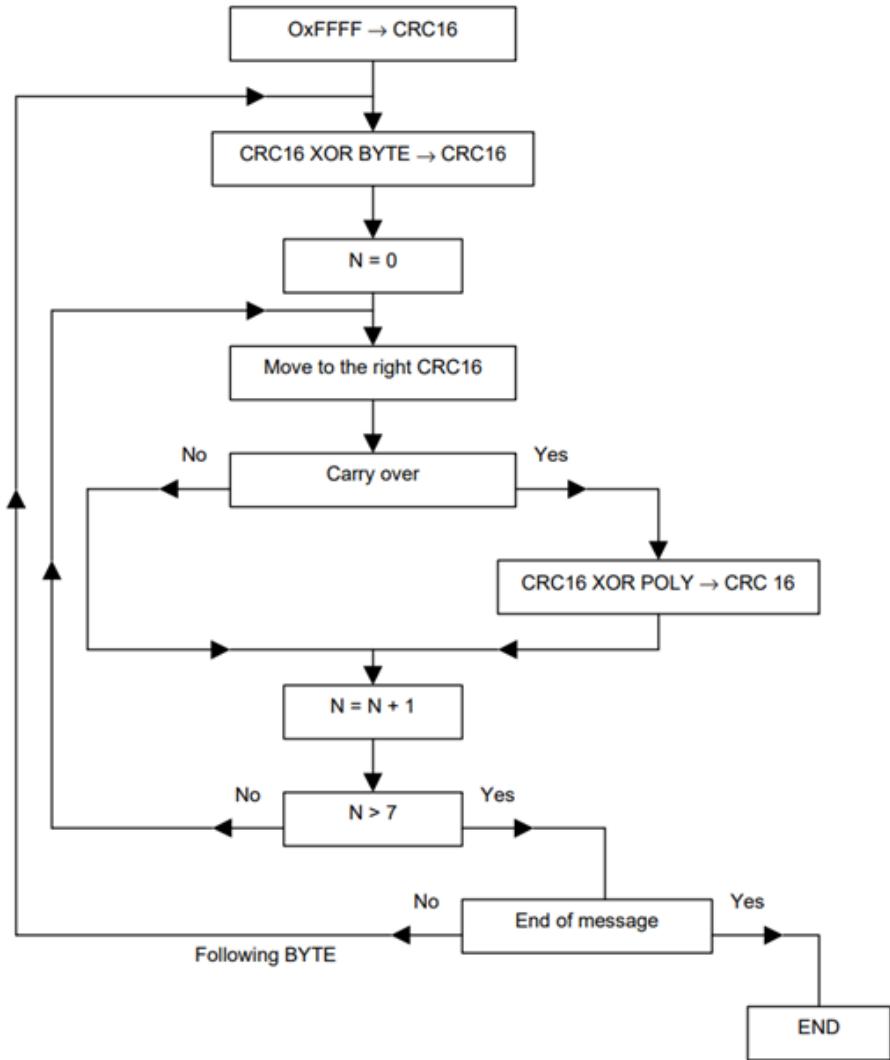

The Modbus RTU communication protocol uses a 16-bit cyclical redundancy check (CRC-16) to confirm the integrity and accuracy of the message contents that are transmitted in both request and response messages. The CRC-16 calculation is known for being robust and reliable, with an ability to detect 99.9985% of errors [18]. The CRC calculation follows an algorithm that consists of various logical XOR operations with multiple values and register value bit-shifts. The flowchart for the CRC-16 algorithm can be seen below in Figure 2.12. Each byte of data is sent through this CRC algorithm, and the final value of the “CRC16” variable is the value that is used for the CRC component of the Modbus RTU packet.

Figure 2.12 - Cyclical Redundancy Check (CRC) flowchart [19]

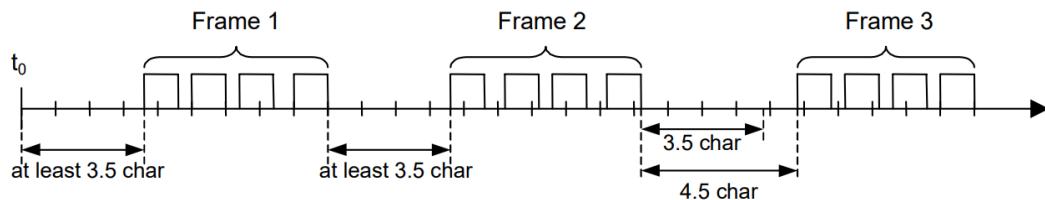

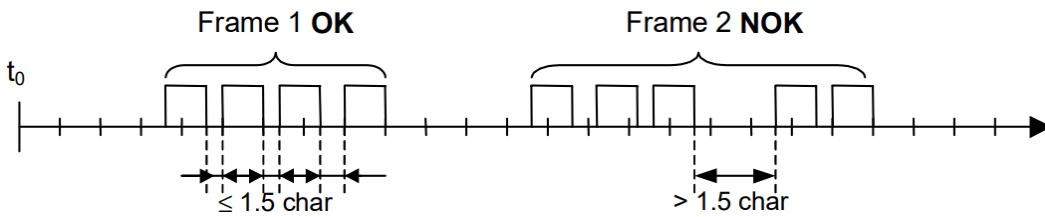

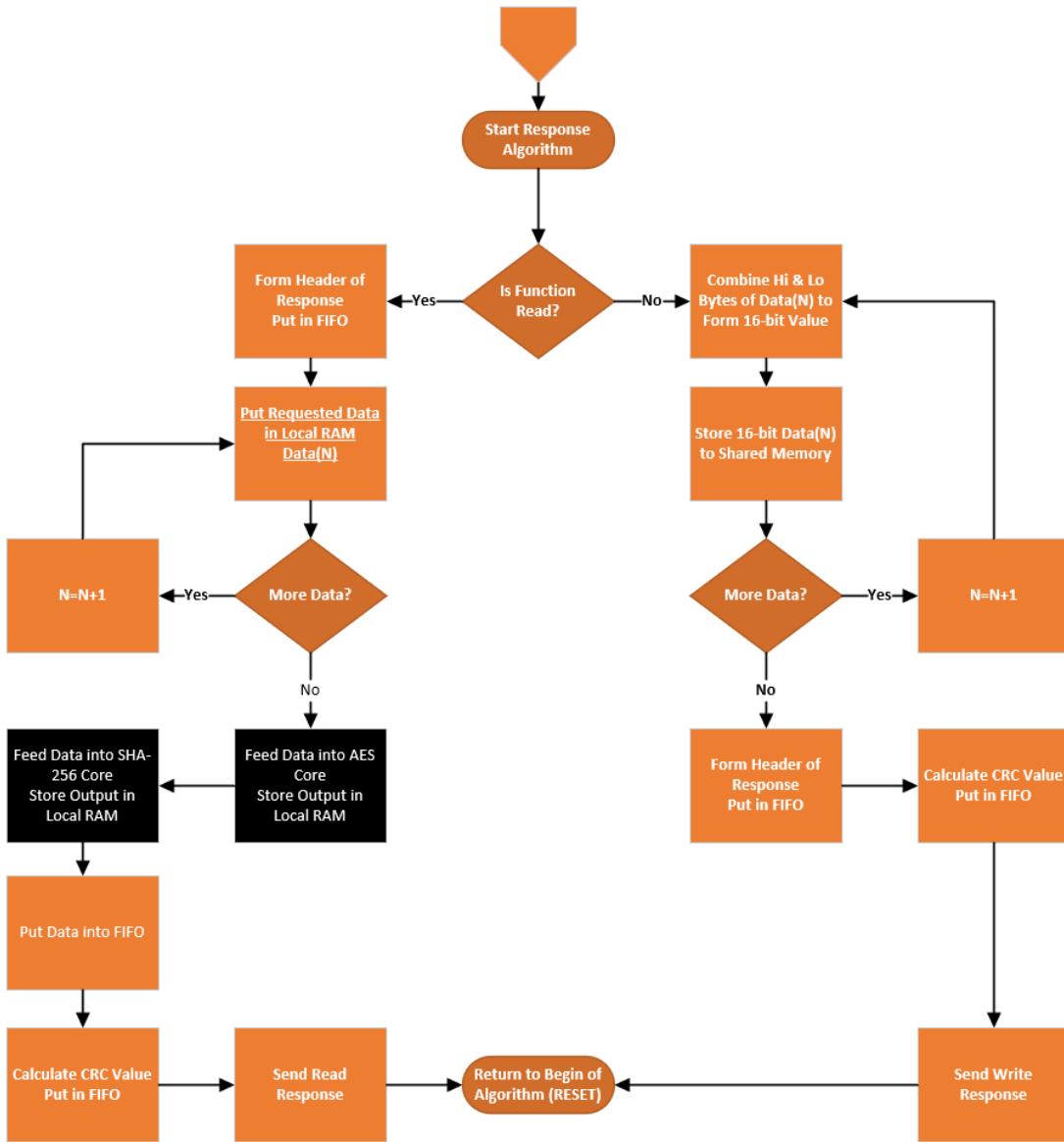

#### 2.4.5 – Message RTU Framing