## Final Technical Report (FTR)

|                                                                |                                                                                                                  |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| <b>a. Federal Agency</b>                                       | Department of Energy                                                                                             |

| <b>b. Award Number</b>                                         | DE-EE0008346                                                                                                     |

| <b>c. Project Title</b>                                        | Modular Wide-bandgap String Inverters for Low-cost Medium-voltage Transformerless PV Systems                     |

| <b>d. Recipient Organization</b>                               | University of Washington                                                                                         |

| <b>e. Project Period</b>                                       | 9/1/2018 – 11/30/2022                                                                                            |

| <b>f. Principal Investigator</b>                               | Name: Brian Johnson<br>Title: Assistant Professor<br>Email address: brianbj@uw.edu<br>Phone number: 217-778-3667 |

| <b>g. Business Contact</b>                                     | Name: Carol Rhodes<br>Email address: osp@uw.edu<br>Phone number: 206-543-4043                                    |

| <b>h. Certifying Official (if different from the PI or BC)</b> | Name:<br>Title:<br>Email address:<br>Phone number:                                                               |

Signature of Certifying Official

1/18/2024

Date

*By signing this report, I certify to the best of my knowledge and belief that the report is true, complete, and accurate. I am aware that any false, fictitious, or fraudulent information, misrepresentations, half-truths, or the omission of any material fact, may subject me to criminal, civil or administrative penalties for fraud, false statements, false claims or otherwise. (U.S. Code Title 18, Section 1001, Section 287 and Title 31, Sections 3729-3730). I further understand and agree that the information contained in this report are material to Federal agency's funding decisions and I have any ongoing responsibility to promptly update the report within the time frames stated in the terms and conditions of the above referenced Award, to ensure that my responses remain accurate and complete.*

**1. Acknowledgement:** This material is based upon work supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) under Solar Energy Technology Office (SETO), and DE-FOA-0001740 and Award Number DE-EE0008346.

**2. Disclaimer:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

**3. Executive Summary:** The proposed technology combines advances in wide-bandgap power electronics with breakthroughs in distributed and decentralized control to produce ultra-low-cost medium-voltage transformerless PV inverters that are composed of stackable lightweight blocks. Taken together, the proposed circuit designs and accompanying control strategies will yield integrated control+circuit (C2) blocks, each comprising a converter and local controller, that can be assembled in a modular fashion to obtain distributed conversion interfaces for next-generation commercial and utility-scale PV systems. We will utilize SiC devices to obtain C2 blocks that can individually operate at a voltage and power in excess of 1 kV and 100 kW, respectively, such that ensembles of series-connected blocks perform direct dc to three-phase ac conversion at medium voltages (e.g., 12 kV–35 kV) and at multi-MW power levels.

#### 4. Table of Contents:

## Contents

|          |                                                                                                          |           |

|----------|----------------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Summary of Project Milestones</b>                                                                     | <b>5</b>  |

| <b>2</b> | <b>Design of a three-phase DC-AC converter module: Architecture</b>                                      | <b>11</b> |

| 2.0.1    | Design requirements for the three-phase DC-AC converter module . . . . .                                 | 12        |

| 2.0.2    | Design of the three-phase DC-AC converter module . . . . .                                               | 13        |

| <b>3</b> | <b>High voltage planar magnetics and medium voltage transformer</b>                                      | <b>13</b> |

| 3.0.1    | Design requirements for the MV planar transformer . . . . .                                              | 14        |

| 3.0.2    | Isolation requirements for MV transformer design . . . . .                                               | 14        |

| 3.0.3    | Design of a planar transformer . . . . .                                                                 | 14        |

| 3.0.4    | MV Isolation testing . . . . .                                                                           | 15        |

| 3.0.5    | Prototype Module with the High-Frequency MV Planar Transformer . . . . .                                 | 16        |

| <b>4</b> | <b>Soft switching in a QAB converter</b>                                                                 | <b>17</b> |

| <b>5</b> | <b>AC-side controllers for decentralized power sharing and interleaving</b>                              | <b>20</b> |

| <b>6</b> | <b>Control Design of Cascaded Converters</b>                                                             | <b>22</b> |

| <b>7</b> | <b>Experimental Results for Cascaded PV-Powered Setup</b>                                                | <b>29</b> |

| <b>8</b> | <b>Medium-voltage prototype performance: NREL prototype</b>                                              | <b>35</b> |

| <b>9</b> | <b>Levelized Cost of Energy-Oriented System Optimization of the Novel Power Electronics Architecture</b> | <b>36</b> |

**5. Background:** Today, utility-scale PV inverters are predominantly built with conventional single-stage converter topologies that interface with an externally installed low-voltage to medium-voltage line-frequency transformer. Given the non-trivial costs and maintenance associated with centralized transformers, several leading manufacturers are exploring the development of transformerless inverters that produce medium voltage ac (MVAC) directly. Towards this end, multilevel inverters have emerged as a viable means of transferring energy at elevated voltages as the large number of series-connected devices allows for increased operational voltages. However, existing multilevel inverter topologies require bulky passive components that add costs and centralized controllers that impede scalability. Presently, multilevel inverters have a negligible role in the PV market.

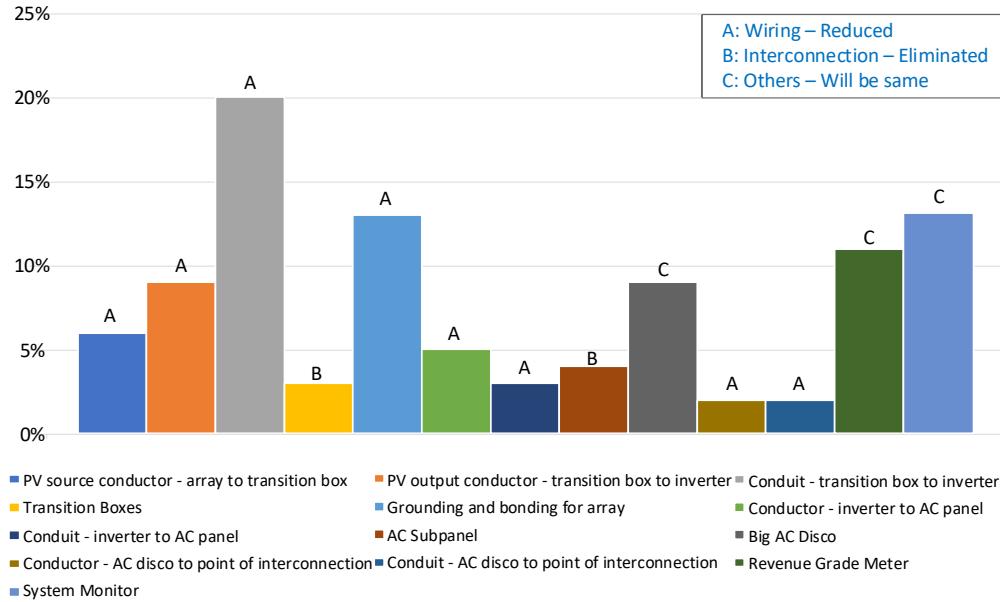

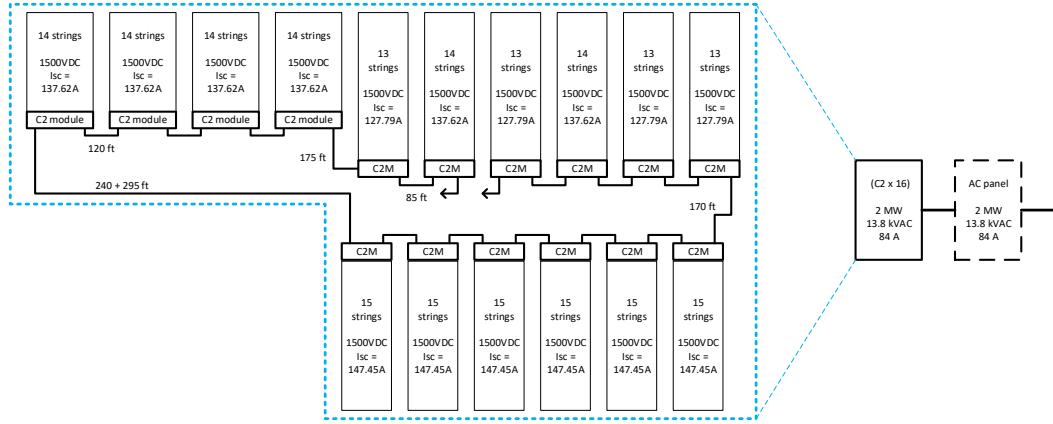

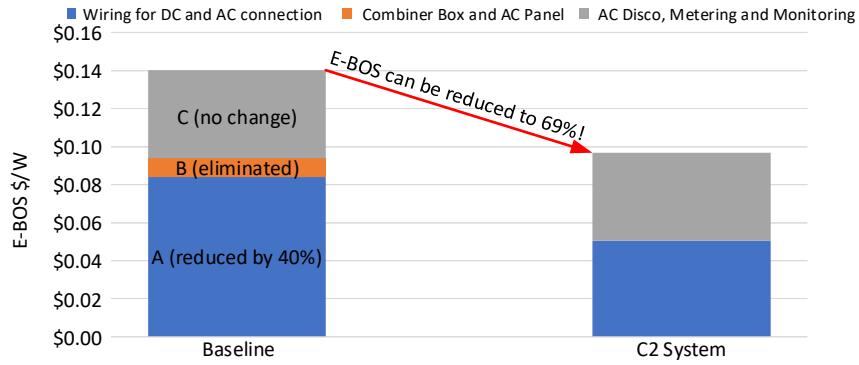

As inverter costs continue their downward trajectory, one of the main bottlenecks to further cost reductions is BOS costs. In fact, recent PV market analysis has demonstrated that BOS costs are playing an increasingly dominant role in overall system costs and now exceed inverter costs. For instance, centralized inverters have significant dc-side wiring costs and string-level three-phase inverters have substantial ac-side wiring requirements due to the high number of parallel units. Accordingly, a converter that has streamlined dc and ac wiring requirements would considerably reduce overall system cost.

One of the most well-established technologies for medium- and high-voltage power electronics ac systems is the MMC. Hence, we will consider it as an important frame of reference. There are

some distinct properties of the MMC that have hindered their use in transformerless PV inverters. For instance, one prerequisite of the MMC is that the dc input voltage must exceed the peak ac-side medium voltage for the system to be operational. If used in a PV application this implies that either medium voltage dc must be provided by the PV array directly or an additional boost converter stage is needed. Both approaches are undesirable since a medium voltage PV string would be infeasible for many reasons, such as costly dc-side protection and PV module voltage isolation, while an additional boost converter would add costs and reduce efficiency. In contrast, our proposed design straightforwardly accommodates standard PV string voltages used in industry today.

Another disadvantage of the MMC is its necessity for large and costly capacitor banks. This stems from its physical structure where each phase leg is composed of a distinct converter stack that must process single-phase power. Irrespective of whether each converter in the MMC stack is composed of half-bridges, full-bridges, diode clamped elements, or flying capacitors, the fundamental fact remains that each collection of converters in each phase-leg must process pulsating single-phase power. This necessitates significant capacitance within each modular converter in addition to centralized controllers that manage system capacitor voltages. Not only does the centralized MMC controller prevent system scalability, but it also acts as a single point of failure.

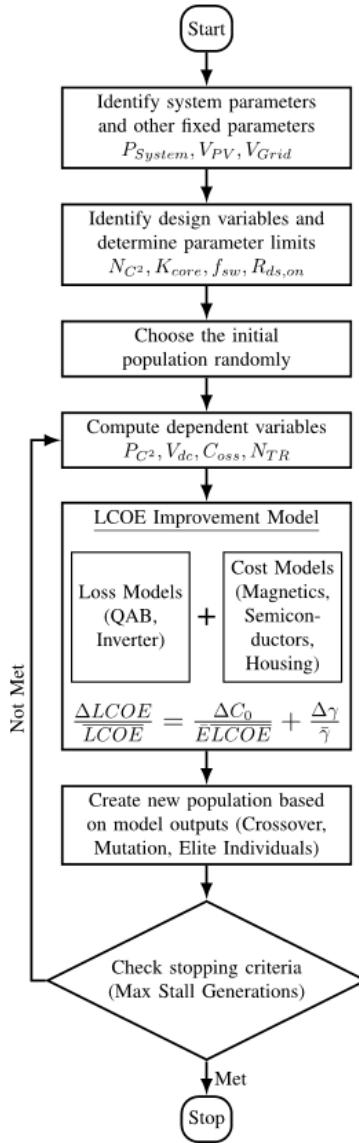

**6. Project Objectives:** At the core of the proposed system lies a novel dc to three-phase ac conversion block whose innovative controls and circuit design significantly reduces cost and weight while increasing efficiency. To obtain a modular architecture that maximizes resiliency and simplifies installation, we apply the latest advances in controls to obtain autonomously controlled C2 blocks that are stacked in series with minimal external wiring and can be bypassed during faults without interrupting system-wide power delivery. Using a cost-analysis-driven design that unambiguously links monetary costs with physical design variables, we will determine the optimal number of stacked C2 blocks, their parameters, and underlying components to achieve the lowest LCOE.

The proposed technology combines advances in wide-bandgap power electronics with breakthroughs in distributed and decentralized control to produce ultra-low-cost medium-voltage transformerless PV inverters that are composed of stackable lightweight blocks. Taken together, the proposed circuit designs and accompanying control strategies will yield integrated circuit+control (C2) blocks, each comprising a converter and local controller, that can be assembled in a modular fashion to obtain distributed conversion interfaces for next-generation commercial and utility-scale PV systems. We will utilize SiC devices to obtain C2 blocks that can individually operate at a voltage and power in excess of 1 kV and 100 kW, respectively, such that ensembles of series-connected blocks perform direct dc to three-phase ac conversion at medium voltages (e.g., 12 kV–35 kV) and at multi-MW power levels.

**7. Project Results and Discussion:** Provide a high-level, quantitative comparison of anticipated project outcomes against realized results with clearly stated quality metrics to assess the confidence of the results. A clear sense of progress against award milestones, both throughout and at award end, should be conveyed. State the project tasks and go/no-go milestones/deliverables and metrics and compare them to what was actually achieved. This section's structure should be based on the SOPO, making comparisons at the task level with the subtasks providing support for claimed progress. Milestone rows should be copied verbatim to appropriate points in the technical discussion. Enough detail and/or references to supporting documentation must be provided to make it clear that milestones were successfully accomplished. If milestones were not met, discuss any extenuating circumstances and difficulties encountered. The methodologies (e.g., modeling

approaches, experimental methods) utilized to obtain the results should also be included. Relevant figures and data tables should be included and discussed in enough detail to demonstrate the technical progress made on the award.

## 1 Summary of Project Milestones

All Task 1 Milestones were completed.

|      | Metric Definition                                                                     | Success Value                                                                                                                                                                                                           | Measured Value                                                                                                                                                                   | Assessment Tool                                                           | Goal Met (Y/N) | Supporting Data (pg. #)                                                                 |

|------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------|

| M1.1 | Updated cost data for cost optimization model.                                        | Set of data containing up to date costs for relevant system components.                                                                                                                                                 | The team has successfully obtained cost data for the key system components.                                                                                                      | Existence of updated cost data                                            | Y              | Pages 35-37 of BP1 Q3 report.                                                           |

| M1.2 | Cost and efficiency models                                                            | The efficiency and cost of a system containing C2 blocks is expressed as a function of converter-level parameters and ratings such as voltage rating, current rating, magnetics characteristics, and device properties. | The efficiency and cost models have been completed. Existing results include all semiconductor and magnetics losses.                                                             | Project team review and written summary of review discussion              | Y              | Pages 38-40 of BP1 Q3 report, Pages 15-20 of BP1 Q2 Report & pages 3-6 of BP1 Q1 Report |

| M1.3 | A comprehensive LCOE-improvement model and corresponding design optimization problem. | A LCOE improvement model which incorporates inverter capital costs, BOS costs, and efficiency is formulated and translated into a design optimization problem.                                                          | The optimization problem has been formulated. This design optimization problem has been solved with a few types of solvers and the performance of the solvers has been compared. | Design problem presented to DOE and demonstrated with numerical examples. | Y              | Pages 4-7 of BP1 Q4 Report, Pages 41-44 of BP1 Q3 Report, Pages 15-20 of BP1 Q2 Report. |

## All Task 2 Milestones were completed.

|      | Metric Definition                                                                                                | Success Value                                                                                                                                                                                                                 | Measured Value                                                                                                                                          | Assessment Tool                                                                              | Goal Met (Y/N) | Supporting Data (pg. #)                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|

| M2.1 | A simulation of five or more cascaded C2 blocks with fully functional MPPT, dc-link, and power sharing controls. | A simulation showing that all dc-link voltages stay within 10% of the setpoint, the PV maximum power point is tracked within 10%, and power is shared on the ac side in proportion to the PV maximum power for each C2 block. | A detailed switch-cycle averaged simulation was assembled and the overall system performance was validated. All performance targets were satisfied.     | Quantitative simulation results from a performance evaluation script within MATLAB/Simulink. | Y              | Page 7 of BP1 Q3 report.                                                                                            |

| M2.2 | A simulation showing five or more interleaved C2 blocks with communication-free interleaving controllers.        | A simulation showing that the generation of a low-distortion $2N + 1$ level ac waveform without communication.                                                                                                                | An improved version of the controller was developed and tested in HIL. Simulations and experiments demonstrated feasibility of the proposed controller. | Quantitative simulation results from a performance evaluation script within MATLAB/Simulink. | Y              | Page 9 of BP1 Q3 report, Pages 9-12 of BP1 Q2 report & Pages 9-11 of BP1 Q1 report.                                 |

| M2.3 | A hardware validation of decentralized dc-link controllers.                                                      | Measurements on five or more low-voltage C2 block which shows that the dc-link voltages stay within 10% of the setpoint.                                                                                                      | The low-voltage hardware was built and debugged. Each of the 5 C2 blocks was tested and dc-link voltages were maintained within 10% of the setpoint.    | Electrical measurements.                                                                     | Y              | Pages, 9-13 of BP1 Q4 Report, Page 12 of BP1 Q3 report, Pages 11-14 of BP1 Q2 report, Pages 12-16 of BP1 Q1 report. |

## All Task 3 Milestones were completed.

|      | Metric Definition                                                             | Success Value                                                                                                                                                                                                                              | Measured Value                                                                                                                                                                                                                                                                                                       | Assessment Tool                                                                             | Goal Met (Y/N) | Supporting Data (pg. #)                                   |

|------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------|

| M3.1 | A candidate magnetics design which accommodates rated power transfer.         | Detailed simulations and analysis demonstrate that the QAB magnetics can deliver 15kW from the dc input to the three-phase ac outputs.                                                                                                     | A magnetics design was finalized and detailed models show it can transfer rated power at high efficiency.                                                                                                                                                                                                            | Quantitative simulation results and accompanying analysis/models.                           | Y              | Pages 14-19 of BP1 Q3 report, Pages 3-6 of BP1 Q2 report. |

| M3.2 | A high-level HV-PCB layout which ensures voltage isolation of at least 30 kV. | A diagram which prescribes the physical placement of the primary circuit and three secondary circuits associated with the QAB and an accompanying finite-element model which shows electric fields below the arcing threshold for HV-PCBs. | A first version of the high-level prototype design was created. This initial design specifies the hardware architecture, sensors, control boards, magnetics placement, communications, and interconnects. A finite element model of the HV-PCB planar magnetics board also demonstrates isolation of at least 30 kV. | A diagram and simulation results from an electromagnetic finite-element simulation package. | Y              | Pages 21-22 of BP1 Q3 report, pages 6-7 or BP1 Q2 report. |

| M3.3 | A candidate converter circuit design with at least 98.5% CEC efficiency.      | Analysis and simulation of candidate 15kW power stage design demonstrates at least 98.5% CEC efficiency.                                                                                                                                   | Simulations of candidate designs demonstrate that an efficiency of at least 98.5% efficiency is feasible. Detailed loss analysis supports this conclusion.                                                                                                                                                           | Quantitative simulation results from a performance evaluation script.                       | Y              | Pages 16-18 of BP1 Q4 Report, Page 33 of BP1 Q3 report.   |

## All Task 4 Milestones were completed.

|      | Metric Definition                                                                                                                                                                              | Success Value                                                                                                                                                           | Measured Value                                                                                                                                    | Assessment Tool                                                                   | Goal Met (Y/N) | Supporting Data (pg. #)                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------|---------------------------------------------------|

| M4.1 | Cost data that is updated in BP2 and used for design optimization                                                                                                                              | Set of data containing up to date BP2 costs for relevant system components                                                                                              | Updated cost data has been imported into the optimization code.                                                                                   | Existence of updated cost data                                                    | Y              | BP2 Q3 report pages 3-4                           |

| M4.2 | A comprehensive optimization-driven design framework which incorporates market cost data                                                                                                       | Existence of a design framework and accompanying output data produced by the design routine                                                                             | A fully-functional optimization routine has been created.                                                                                         | Design optimization models are presented to DOE                                   | Y              | BP2 Q3 report pages 4-6                           |

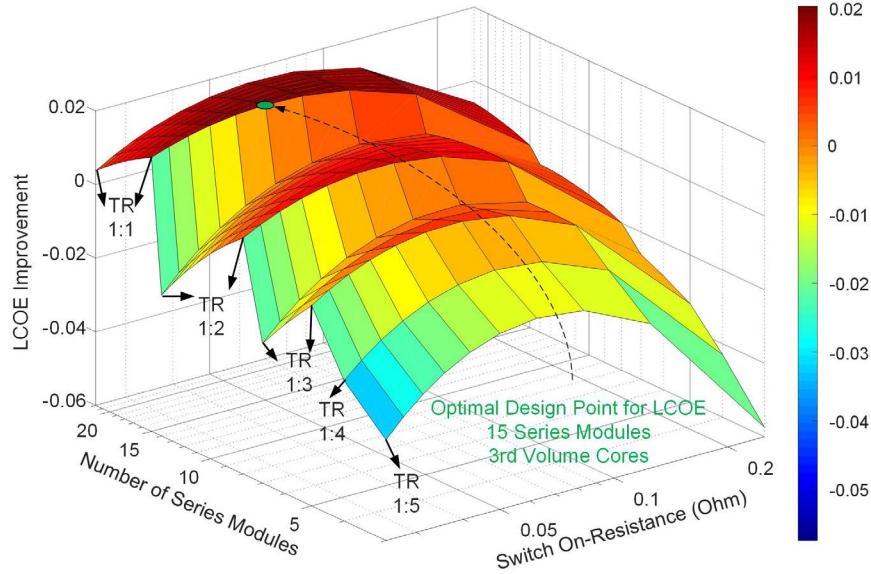

| M4.3 | Design optimization results for a utility-scale system and LCOE reduction estimates in comparison to centralized inverters (and three-phase string inverters) with line frequency transformers | A utility-scale candidate design which shows LCOE reductions in comparison to centralized inverters (and three-phase string inverters) with line frequency transformers | Preliminary results including potential improvements in electric BOS and system rating as free variable indicate a roughly 5.5% LCOE improvement. | Numerical data produced by design/cost optimization and cost sensitivity analysis | Y              | BP2 Q3 report pages 6-10. BP2 Q4 report pages 6-7 |

All Task 5 Milestones were completed.

|      | Metric Definition                                                                                                                 | Success Value                                                                                                                                                                                           | Measured Value                                                                    | Assessment Tool         | Goal Met (Y/N) | Supporting Data (pg. #)                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|----------------|---------------------------------------------------|

| M5.1 | Experimental results from five or more cascaded low-voltage C2 blocks with the proposed dc-link, MPPT, and power sharing controls | Measurements on all low-voltage C2 blocks show that the PV maximum power point is tracked within 5%, the dc-link voltages stay within $\pm 10\%$ of the setpoint, and ac-side power sharing is achieved | Convergence to MPPT was within 5% and dc link voltages were regulated within 10%. | Electrical measurements | Y              | BP2 Q1 report pages 5-6, BP2 Q4 pages 8-12.       |

| M5.2 | A system of five or more C2 blocks with decentralized interleaving controls                                                       | Measurements showing that the system of five or more cascaded low-voltage C2 blocks reaches the interleaved state without communication                                                                 | A system of 5 cascaded C2 blocks achieved decentralized interleaving in hardware. | Electrical measurements | Y              | BP2 Q3 report pages 12-13, BP2 Q4 report page 15. |

All Task 6 Milestones were completed. Note that it was agreed that M6.2 could be completed via simulation due to limitations on existing off-the-shelf magnetics components which impeded hardware efficiency.

|      | Metric Definition                                                                                      | Success Value                                                                                                                                                      | Measured Value                                                                                                         | Assessment Tool         | Goal Met (Y/N) | Supporting Data (pg. #)                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| M6.1 | Fabricated planar magnetics components which meet leakage inductance specs for required power transfer | Measurements show that the target leakage inductances are obtained and the required power transfer is feasible                                                     | Measurements have been carried out on planar transformer and inductor prototypes for 7.5kW of power transfer.          | Electrical measurements | Y              | BP2 Q3 report pages 15-17.                                                                                                                 |

| M6.2 | A 7.5 kW C2 block with at least 98.5% CEC efficiency                                                   | Electrical measurements show that 98.5% CEC efficiency can be met or exceeded. (Agreed to meet this in simulation.)                                                | Models and simulations (which have been validated against measurements) show that a >98.5% CEC efficiency is feasible. | Electrical measurements | Y              | BP2 Q3 report pages 18-24, BP3 Q1 report pages 3-6, BP3 Q2 report pages 5-7, BP3 Q5 report pages 3-5.                                      |

| M6.3 | A 7.5 kW C2 block which can withstand 13kV of voltage isolation                                        | The absence of arcing or faults when 13kV is subjected across the magnetic isolation barrier within a C2 block                                                     | >18 kV of isolation was measured.                                                                                      | Electrical measurements | Y              | BP2 Q1 report page 15.                                                                                                                     |

| M6.4 | A simulation with 10 or more cascaded 7.5 kW C2 blocks                                                 | Simulations which match planned 13.2 kV experiments and show that all dc-link voltages stay within 10% of the setpoint and ac-side power sharing is achieved.      | Simulations show ac-side power sharing and dc link voltages regulated within 1% of reference value.                    | Electrical measurements | Y              | BP2 Q2 report page 16                                                                                                                      |

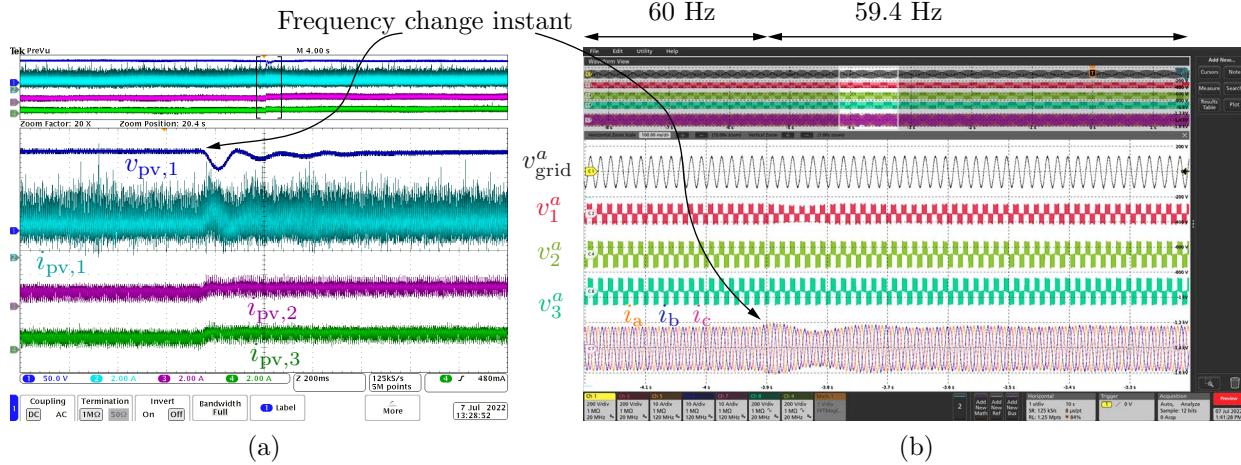

| M6.5 | An experiment with 3 or more cascaded 7.5 kW C2 blocks                                                 | Measurements showing that the cascaded system can maintain dc-link voltages within 10% of the setpoint and ac-side power sharing is achieved while grid-connected. | Experiment successfully completed on three module setup.                                                               | Electrical measurements | Y              | BP2 Q3 report pages 25, BP2 Q4 report pages 17-18, BP3 Q1 report pages 3-6, BP3 Q2 report pages 4, BP3 Q3 pages 4-7, Final Report page 32. |

All Task 7 Milestones were completed.

|      | Metric Definition                                   | Success Value                                | Measured Value                                     | Assessment Tool | Goal Met (Y/N) | Supporting Data (pg. #)    |

|------|-----------------------------------------------------|----------------------------------------------|----------------------------------------------------|-----------------|----------------|----------------------------|

| M7.1 | A written summary of IAB feedback obtained over BP2 | Existence of documentation with IAB feedback | Feedback was consolidated into a written document. | Report          | Y              | Report will be sent to DOE |

All Task 8 Milestones were completed.

|      | Metric Definition                                                                            | Success Value                                                                                                                                                                     | Measured Value                                                                                                                                                   | Assessment Tool         | Goal Met (Y/N) | Supporting Data (pg. #)                                                      |

|------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|------------------------------------------------------------------------------|

| M8.1 | Measurements from low-voltage testbed showing operation during realistic system disturbances | Uninterrupted power delivery during the following scenarios: 1) a unbalanced voltage sag of 5% on one ac grid phase, and 2) dc-side MPPT mismatches within 10% of a nominal value | Controllers were experimentally shown to accommodate low-voltage faults above 5% and large dc-side power mismatches above 10% with uninterrupted operation.      | Electrical measurements | Y              | BP3 Q2 report pages 9-10, BP3 Q4 report pages 4-9, BP3 Q5 report pages 6-11. |

| M8.2 | LCOE framework which includes conductor costs, uninterrupted operation, and maintenance.     | A mathematical model and numerical study will be used to demonstrate a greater than 3% LCOE reduction.                                                                            | With the final LCOE-oriented design optimization method, the team presented the potential LCOE improvement of 5.5 % with the new power electronics architecture. | Numerical modeling      | Y              | BP3 Q3 report pages 8-12                                                     |

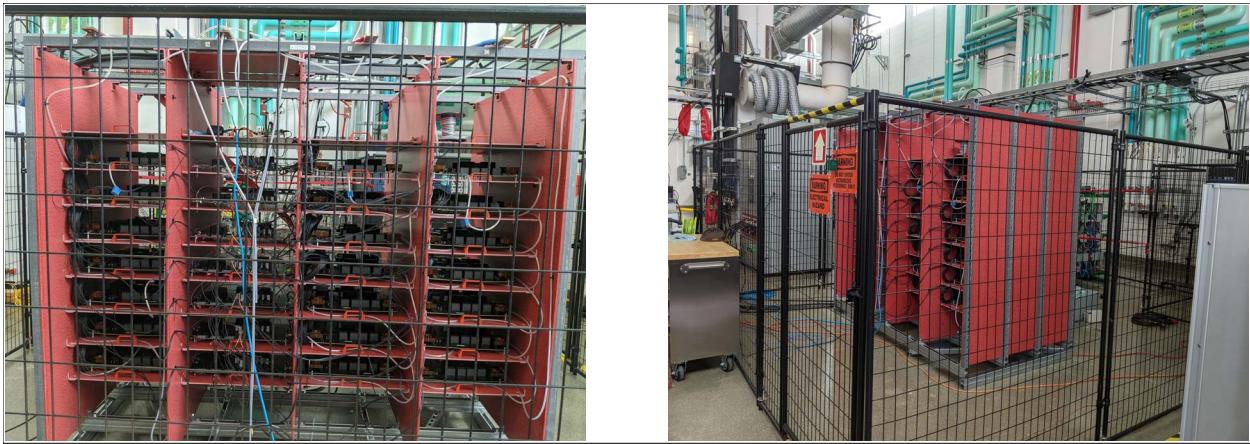

Nearly all Task 9 Milestones were completed. We were unable to run the experiment at full voltage due to noise corrupting the centralized controller synchronization signal. This indicates that the decentralized methods we developed are indeed important and used in future projects/experiments. The existing results were limited to three series-connected converter blocks across a resistive load.

|      | Metric Definition                                                                                                     | Success Value                                                                                                    | Measured Value                                                                                               | Assessment Tool                            | Goal Met (Y/N) | Supporting Data (pg. #)                                                                        |

|------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|------------------------------------------------------------------------------------------------|

| M9.1 | A controllable grid interface configured to produce 13.2 kV and with appropriate instrumentation for data collection. | Electrical diagrams, design documentation, and photos showing completed experimental setup.                      | Testing plans at NREL were completed with necessary devices identified including meters and switches.        | Diagrams, design documentation, and photos | Y              | BP3 Q1 report page 15, BP3 Q2 report pages 12-13, BP3 Q3 report pages 14-15.                   |

| M9.2 | A system of seven or more C2 blocks across a 7.2 kV grid.                                                             | Electrical measurements showing full-rated power delivery (within 5% of 7.5 kW) when connected to a 7.2 kV CGI.  | The multi-converter racks were built and operated with three-units across a resistive load at reduced power. | Experimental measurements                  | N, Partial     | BP3 Q1 report page 16, BP3 Q4 report pages 10-13, BP3 Q5 report page 13, Final Report page 33. |

| M9.3 | A system of fourteen or more C2 blocks across a 13.2 kV grid.                                                         | Electrical measurements showing full-rated power delivery (within 5% of 7.5 kW) when connected to a 13.2 kV CGI. | The overall experiment was built but ran out of time to conduct experiment at full voltage.                  | Experimental measurements                  | N              | BP3 Q4 report pages 10-13.                                                                     |

All Task 10 Milestones were completed.

|       | Metric Definition                                                      | Success Value                                                                                                              | Measured Value                                                                                                                                       | Assessment Tool                                   | Goal Met (Y/N) | Supporting Data (pg. #) |

|-------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|-------------------------|

| M10.1 | Final project results and industry feedback regarding market adoption. | Conclusion of meetings with industry contacts.                                                                             | The team gathered industry feedback at the midpoint of the project and that report was submitted. Industry feedback is contained within that report. | Results evaluated in quarterly report and review. | Y              | See M7.1 report         |

| M10.2 | Final project report.                                                  | A final project report that includes technical results, lessons learned, and feedback obtained from industry stakeholders. | The final report has been completed and submitted.                                                                                                   | Final project report.                             | Y              | This report.            |

## 2 Design of a three-phase DC-AC converter module: Architecture

Recently, modular converter typologies have gained attention as effective interfaces between low voltage (LV) dc/ac systems and the medium voltage (MV) ac grid. These architectures have been applied in a diverse set of use cases from electric vehicle (EV) charging to photovoltaic (PV) power

systems.

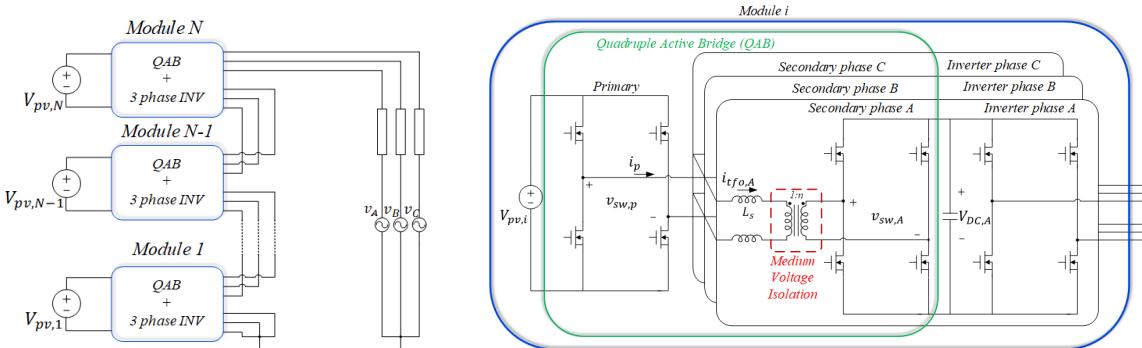

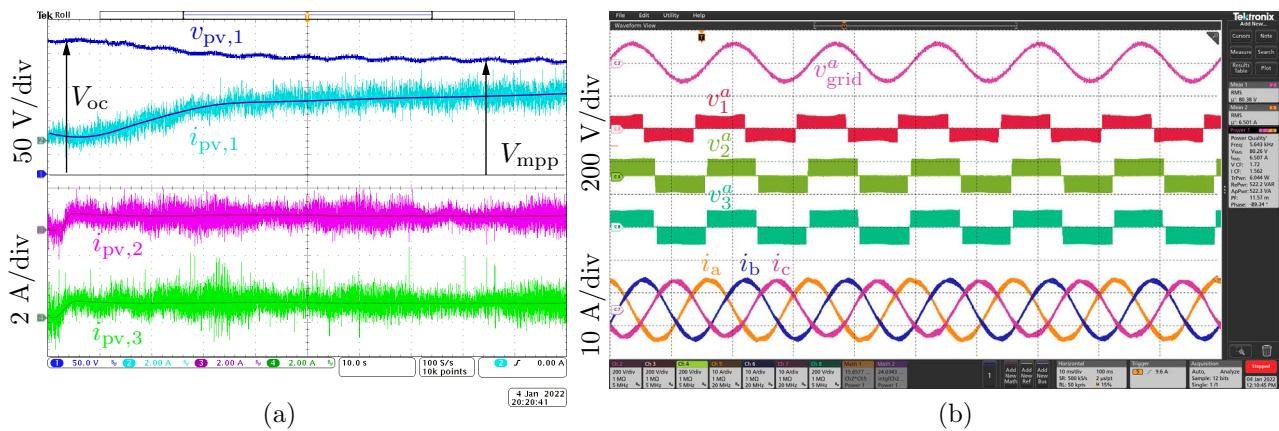

The proposed stackable, modular architecture is shown in Figure. 1 (a), where each module is comprised of a single dc port and three isolated single-phase ac ports. Each port can be used independently or configured to stack in series or parallel depending on the application requirements. Figure. 1 (a) provides an example configuration where each dc port is tied to independent LV sources like PV strings, while the ac ports are combined in series to facilitate connection with the MV three-phase grid. The architecture takes advantage of balanced three phase power to eliminate pulsating power at twice the line frequency at the dc port, effectively reducing energy storage requirements. The topology of each module is shown in Figure. 1 (b) and is comprised of a single quadruple active bridge (QAB) creating three isolated dc link voltages, each followed by a single-phase dc-ac inverter bridge. The QAB is operated as a fixed ratio converter known as a dc transformer (DCX) and provides galvanic isolation between the primary and each of the individual ac phases through solid state transformers (SST) that will be discussed in Section 3. This provided isolation allows for flexible stacking of each module's ac ports.

Each QAB phase  $A$ ,  $B$ , and  $C$  provide time-varying power  $p_A(t)$ ,  $p_B(t)$ , and  $p_C(t)$  respectively, containing both a dc and a twice-line-frequency ac component. The three phase currents sum together on the primary side, resulting in dc power transfer from the input. This balanced three-phase power transfer allows for significant reduction in the sizes of passive components, specifically the dc-link capacitance.

This provides a significant advantage as compared to single-phase systems that require bulky dc-link capacitors capable of filtering the twice-line-frequency ac component. The three-phase power transfer eliminates this requirement, meaning the capacitors only need to be sized to filter switching ripple of the secondary-bridge and inverter bridge currents.

### 2.0.1 Design requirements for the three-phase DC-AC converter module

The overall system requirements are highlighted below:

1. System is capable of interfacing with a 13.2 kV ac grid and PV arrays rated for 1 kV dc.

2. System is comprised of 14 modules with ac output ports connected in series.

These system requirements educated the design choices made for each module. The design specifications for the module are highlighted below:

1. One module can supply 7.5 kW total output power, where 2.5 kW is delivered to each phase

2. Capable of 1 kV dc voltage operation

3. 1.7 kV silicon carbide devices from Wolfspeed Cree are used

4. Distributed control strategy, the primary and each secondary have their own dedicated microcontroller

5. Medium voltage isolation between the primary and each secondary is provided with planar magnetics, see Section 3.

## 2.0.2 Design of the three-phase DC-AC converter module

Taking the design constraints into consideration, a switching frequency of 200 kHz and an optimal phase shift of  $30^\circ$  is selected for the QAB and a switching frequency of 10 kHz is selected for each inverter. Steady state analysis can then be performed for each converter to determine component selection for filter inductance of the QAB and inverter as well as dc-link capacitance. The QAB component value selections are:

1.  $66 \mu\text{H}$  series inductance

2.  $385 \mu\text{H}$  magnetizing inductance

3.  $64 \mu\text{F}$  dc-link capacitance at output of each QAB

The inverter component value selections are:

1.  $320 \mu\text{H}$  filter inductance

## 3 High voltage planar magnetics and medium voltage transformer

Medium voltage transformers are gaining extreme popularity in power electronics applications, such as solid-state transformers (SST). Such SSTs eliminate intermediate conversion stages and improve efficiency. Planar transformers with printed circuit boards (PCBs) are commonly used in various applications. However, no literature or current state-of-the-art has ever explored a planar transformer to achieve high-frequency MV isolation in 10's of KV. A challenge is that standard PCB dielectrics like FR4 cannot offer adequate isolation between layers, and in fact require impractical distances between the layers, which may not be feasible to design. This challenge comes from the fact that interleaving the primary and secondary layers is very much necessary to reduce AC winding losses in high-frequency transformers. To overcome such challenges, a novel PCB technology and a design approach for high-frequency MV planar transformers is illustrated below:

As described in Section 2, multiple of these dc-ac modules are connected in series to interface the PV string modules to an MV ac grid without the need for bulk line frequency transformers, as shown in the Figure. 1 (a). Figure. 1 (b) is the same as the module shown in Section 2. From Figure. 1 (b), it can be seen that the ac line voltage appears across the primary and secondary of the high-frequency transformers, which must therefore meet MV isolation requirements. The planar transformer is designed for the QAB stages in the stacked architecture of Figure. 1.

Figure 1: (a) Stackable architecture for PV string to medium voltage ac conversion, (b) Module schematic. In a target system, the nominal operating conditions are 1 kV dc string voltage, and 13.2 kV MVAC grid voltage.

### 3.0.1 Design requirements for the MV planar transformer

The design specifications for the planar transformer are highlighted as below:

1. 1 kV DC input and three-phase AC output voltages per module

2. Each MV transformer per module is rated for an output power of 2.5 kW

3. The switching frequency is around 200 kHz

### 3.0.2 Isolation requirements for MV transformer design

While interleaving the primary and secondary windings, the dielectric between the adjacent layers must have a sufficiently high breakdown voltage. Second, the vias interconnecting primary or secondary layers must be spaced sufficiently far from the windings since the vias and the windings act as two adjacent conductors with high potential difference between them. Third, the fringing electric fields at the edge of the PCB winding may result in voltage breakdown and arcing to the ferrite core or to an adjacent layer. With a breakdown voltage rating of 7 kV/mil (276 kV/mm), polyimide (Panasonic Felios RF775) is an attractive and low-cost dielectric option. Having a dielectric with 5 mil (0.13 mm) of RF775 enables potential difference of  $\approx 35$  kV between two adjacent PCB layers. In contrast, using standard FR4 material as dielectric (breakdown voltage 500V/mil) would require a 70 mil (1.8 mm) thick dielectric in order to withstand the same voltage of 35 kV, leading to an impractical PCB design.

The location of the vias interconnecting the primary and secondary windings must be placed far away from the windings. Further, it is a better and safer option to move the windings away from the core in order to avoid breakdown and arcing to the ferrite core due to high fringing fields.

### 3.0.3 Design of a planar transformer

While preserving the constraints due to MV isolation requirements discussed in the previous section, the core geometry and the PCB windings can be selected to minimize the loss of the transformer under application-specific operating conditions. As indicated above, the specifications on the DC bus voltages are around 1 kV, while the average power processed by each module is about 7.5 kW.

Assuming quasi-steady-state operation at each point along the line cycle, the core loss is estimated following the iGSE method, and the ac winding losses are computed using Dowell's equations for up to the 11<sup>th</sup> harmonic of the transformer currents. Finally, the overall loss is obtained by averaging the losses over a line cycle. The process is repeated for various core sizes and winding arrangements to arrive at a design where the total average loss is minimized subject to meeting the isolation constraints.

The final design summary of the transformer is as follows:

- No. of turns in primary and secondary: 30

- No. of turns per layer: 5

- Total no. of layers: 12

- Core size and material: EILP 102 with N87 material

- Copper thickness: 4oz

The design parameters are obtained following an optimization procedure that minimizes the overall loss at 75% of maximum power. Hipot testing was done at NREL to validate the MV isolation.

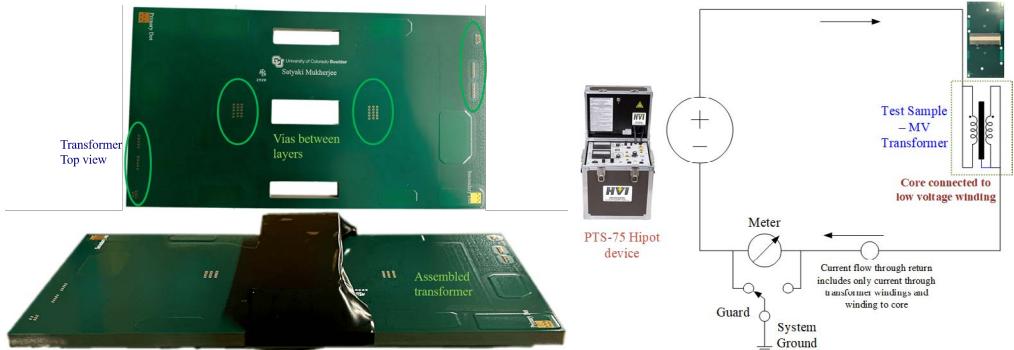

A MV transformer is built with 5 mils of Panasonic Felios RF 775 as the dielectric, according to the specifications described earlier in the section. The isolation capability is tested using the setup described in Section 3.0.4. A complete fabricated planar MV transformer is shown in Fig. 2 (a) with the PCB winding top view and assembly. Further, a circuit diagram of the guarded hipot test setup used to verify the isolation capability of the MV transformer is also shown in Fig. 2 (b)

Figure 2: MV transformer and hipot test setup: (a) Fabricated planar MV transformer: PCB winding top view and assembly, and (b) circuit diagram of the guarded hipot test setup used to verify the isolation capability of the MV transformer.

### 3.0.4 MV Isolation testing

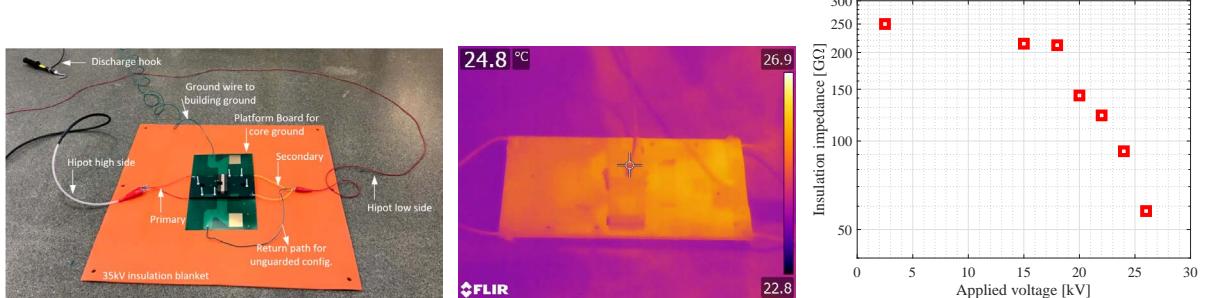

Figure 3: Hipot test setup and result data: (a) Photograph of the hipot testing setup with the device under test and connections from the PTS-75 hipot tester marked, (b) thermal image of the MV transformer with 26 kV applied between its primary and secondary terminals with grounded core segments, and (c) measurements of insulation impedances reported using the hipot tester across a wide range of applied voltages. Operating conditions : Ambient temperature : 21.9°C, Relative humidity : 10.10%, elevation from sea level : 5,675 ft.

Fig. 2(a) shows a fully assembled transformer with the dielectric between two copper layers capable of withstanding  $\approx 35$  kV using a sheet of 5 mil polyimide (Felios RF775). A high-voltage test setup using PTS-75 hipot tester is utilized to test the isolation capability of the MV transformer at the Energy Systems Integration Facility of the National Renewable Energy Laboratory at an elevation of 5,675 ft. from the sea level. Using the hipot tester, medium voltage is applied between the primary and the secondary windings of the prototype transformer. The core of the transformer is connected to the low-voltage side, which is referred to as the system ground. In accordance

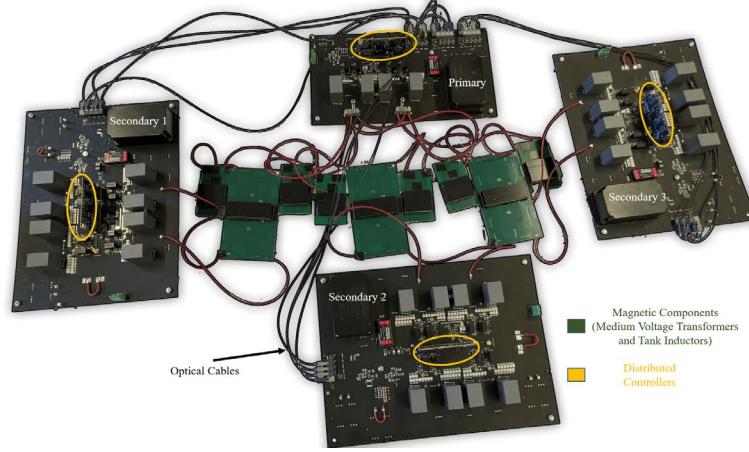

Figure 4: Photograph of the dc-to-ac module comprising one primary and three secondary full bridges, three MV transformers, and six power-transfer series inductors. Distributed controllers are marked on each of the primary and secondary boards.

with the hipot tester recommended procedure, a guarded return connection was used to accurately measure the leakage current between the transformer windings as well as between the high voltage windings and the grounded ferrite core. The connection diagram of the hipot test setup is shown in Fig. 2(b).

The insulation impedance is measured using the applied voltage and the hipot built-in high precision current meter. Fig. 3(a) shows a photograph of the MV transformer undergoing the hipot test procedure with all the connections labeled appropriately.

Fig. 3(b) shows a thermal image of the transformer under hipot testing, with 26 kV applied between the primary and the secondary terminals demonstrating operation unaffected by the applied voltage. In Fig. 3(c), the insulation impedance measured using the PTS-75 hipot tester is plotted against a wide range of applied voltages. The device under test, i.e. the prototype transformer, is capable of maintaining  $> 50 G\Omega$  impedance up to 26 kV across the transformer terminals, indicating no breakdown. Testing up to 26 kV allows for almost 140% margin on the isolation requirement given by the peak line-to-neutral voltage of 10.8 kV at the nominal system operating point in the 13.2 kV line-to-line MV ac (MVAC) grid, thus meeting the ANSI NETA ATS 2017 standard for isolation requirements. The insulation on the MV transformer was found to be most prone to the breakdown between the high-voltage winding and the grounded core. A separate experiment with only the planar PCB excluding grounded ferrite core segments demonstrated  $152 G\Omega$  insulation impedance at 26 kV applied across the windings.

### 3.0.5 Prototype Module with the High-Frequency MV Planar Transformer

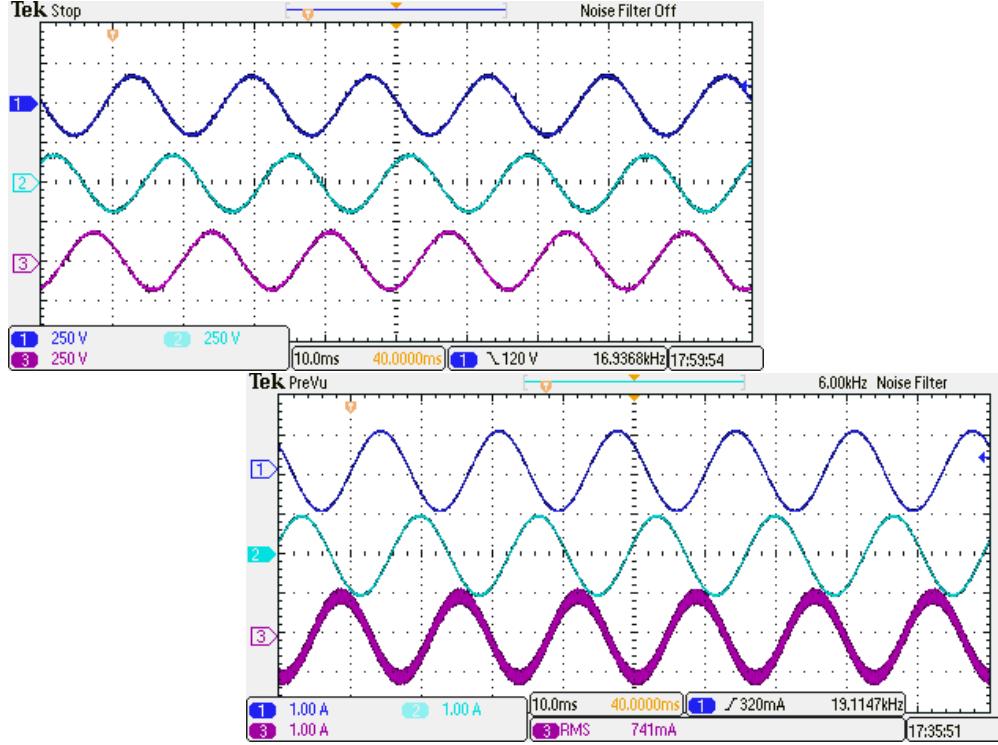

Fig. 4 shows a completely assembled module utilizing three MV transformers of Fig. 2(a). A primary board with a full bridge inverter of the QAB stage and three secondary boards each consisting of a full bridge rectifier for the QAB stage and a low-frequency full bridge inverter, all utilizing 1700 V SiC devices with distributed controllers are shown in Fig. 4.

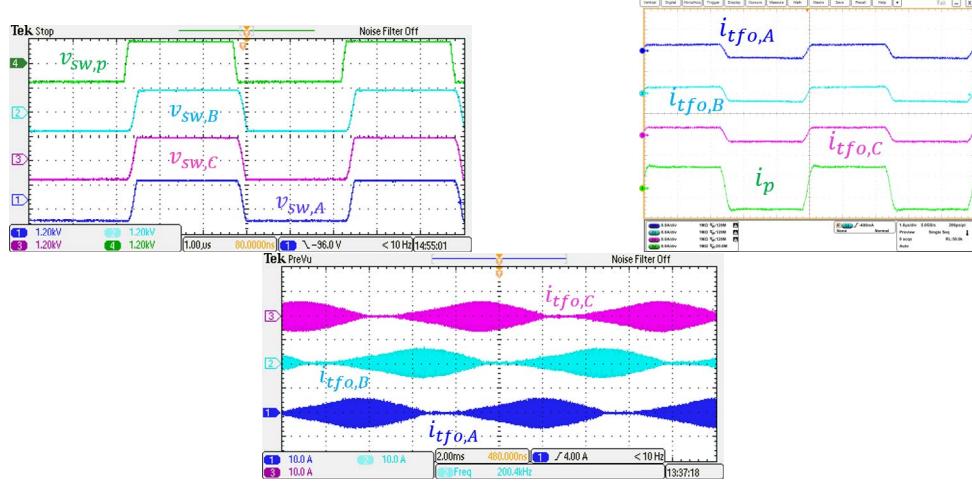

Fig. 5(a) demonstrates switch-node voltages with zero voltage switching of the high-frequency SiC MOSFETs. High-frequency primary and secondary current waveforms of all three DAB mod-

Figure 5: (a) Switch-node voltage waveforms in the dc-to-ac module illustrating generation of three isolated dc bus voltages from the primary input dc voltage of 1000 V, (b) zoomed-in high-frequency flat-top current waveforms processed by the MV transformers, and (c) secondary currents of the three module transformers with twice line-frequency components illustrating three-phase operation of the module delivering a total of 7.5 kW.

ules in the QAB stage are shown in Fig. 5(b), utilizing the MV transformer at  $V_{pv,i} = V_{DC,link} = 1000$  V,  $L_s = 60\mu$  H and processing 7.5 kW power with 97% overall efficiency. Additionally, Fig. 5(c) shows pulsating currents processed by the three MV transformers over the line cycle for dc-to-3 phase ac operation of the module. Predicted transformer loss of approximately 55 W per transformer, with 7.5 kW three phase power processed by the converter module, is consistent with the experimental results. Out of a total loss of 55 W, 15 W is the core loss and 40 W is the conduction loss. The conduction losses are largely attributed to two factors: 1) presence of an airgap, in order to ensure zero voltage switching of the secondary SiC MOSFETs, which degrades interleaving of the high-frequency windings and results in a higher current density in the top winding layer, and 2) to maintain proper isolation, the length of the transformer windings are increased resulting in a larger dc resistance. The transformer losses are related to the choice of the planar core (EILP 102), which is the largest standard planar core available. If a larger core was available, a design with fewer turns would result in a more efficient planar MV transformer.

## 4 Soft switching in a QAB converter

The most important feature of this topology of a QAB converter is that it is of utmost importance to achieve zero voltage switching over the entire line cycle. In order to guarantee ZVS operation over the entire line cycle, it is enough to show that ZVS can be achieved at zero power instant. The tank inductance does not have enough energy stored in it in order to ensure ZVS at zero power intervals. Thus, we rely on the circulating currents induced due to the magnetizing inductance of the transformer. However, these circulating currents greatly reduce the switching loss at the expense of increased conduction losses. As an alternative, a larger series inductance could be used, but this approach would result in reduced efficiency at full load.

Over a line cycle, the power processed by each secondary is determined by the corresponding

phase shift between the secondary and the primary full bridge:

$$\begin{aligned}\varphi_A(t) &= \varphi_m \sin^2(\omega_0 t) \\ \varphi_B(t) &= \varphi_m \sin^2\left(\omega_0 t + \frac{2\pi}{3}\right) \\ \varphi_C(t) &= \varphi_m \sin^2\left(\omega_0 t - \frac{2\pi}{3}\right),\end{aligned}\quad (1)$$

where  $\varphi_m$  is the maximum phase shift, and  $\omega_0$  is the angular line frequency.

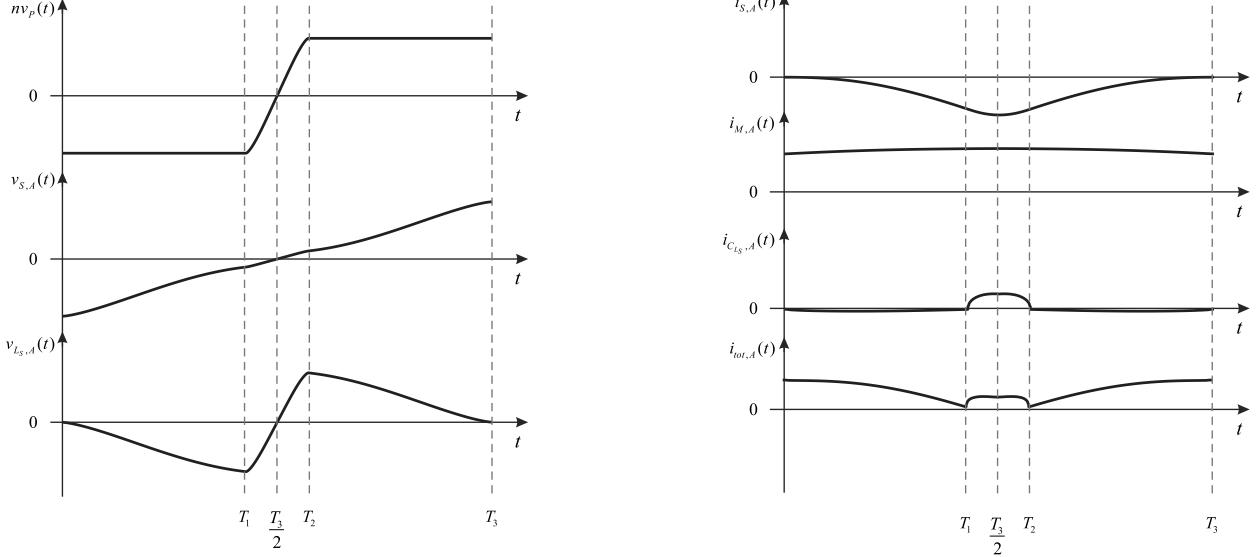

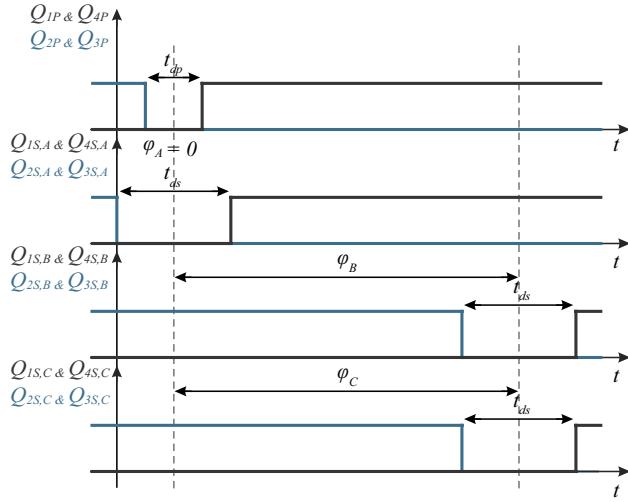

Figure 6: Model-based waveforms of the ZVS transition at the zero power transfer instant for Phase A. Referring to Fig. 7,  $T_3 = t_{ds}$  and  $T_2 - T_1 = t_{dp}$ .

Figure 7: QAB switch control signals at the time when the secondary Phase A processes zero power.

Consider the time instant when the power processed by phase A is zero, while phases B and C contribute non-zero instantaneous power levels to maintain constant overall power in the three-phase module. The corresponding switch control signals are shown in Fig. 7. The phase shift  $\varphi_A$

Table 1: Time instants of the switching sequence during ZVS transition

|       |                        |

|-------|------------------------|

| $T_1$ | $0.5(t_{ds} - t_{dp})$ |

| $T_2$ | $0.5(t_{ds} + t_{dp})$ |

| $T_3$ | $t_{ds}$               |

Table 2: Time intervals of the switching sequence during ZVS transition

|              |                    |

|--------------|--------------------|

| Interval I   | $0 \leq t < T_1$   |

| Interval II  | $T_1 \leq t < T_2$ |

| Interval III | $T_2 \leq t < T_3$ |

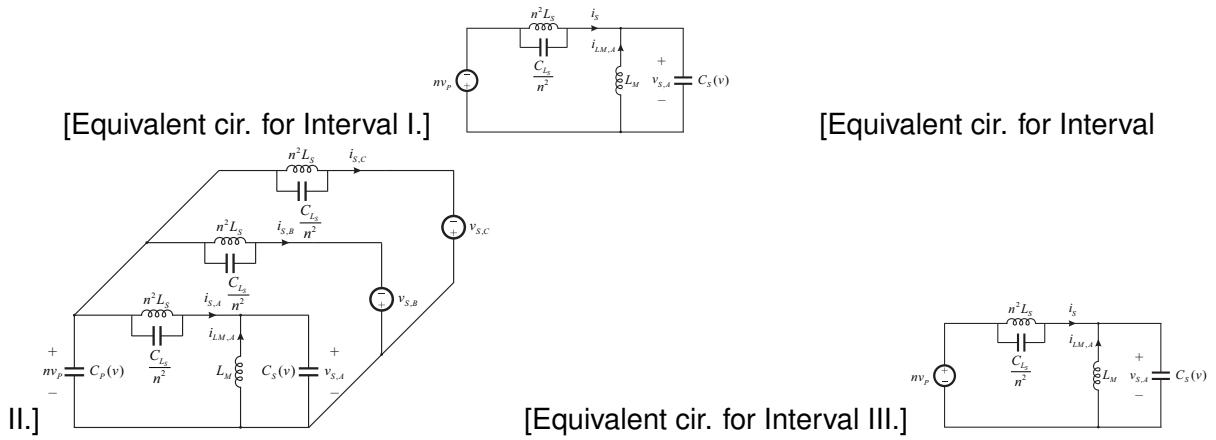

between the primary bridge and the phase A secondary bridge is zero, so that the corresponding control pulses are centered around the same instant. Theoretical, model-based waveforms during the rise-time transition of the secondary switching node are shown in Fig. 6. Definitions of the time instants and the time intervals during the transition are given in Tables 1 and 2, while the corresponding equivalent circuit models for the switching sequence consisting of Intervals I, II and III are shown in Fig. 8.

Figure 8: Equivalent circuits during ZVS transition at the zero power transfer instant for one of the phases.

At the beginning of time Interval I (Fig. 8(a)), the secondary side switches  $Q_{2S,A}$  and  $Q_{3S,A}$  are turned off. The magnetizing inductance current  $i_{M,A}$  starts charging voltage dependent switching-node capacitance  $C_S(v)$  of the phase A secondary bridge, and the switching node voltage  $v_{S,A}$  starts increasing. As  $v_{S,A}$  increases, a negative voltage is applied across the series inductance, and the current  $i_{S,A}$  starts decreasing.

The primary-side switches  $Q_{2P}$  and  $Q_{3P}$  turn off at the beginning of Interval II. The equivalent circuit in Interval II is shown in Fig. 8(b). During this interval, phases B and C are charging the switching-node capacitance  $C_P(v)$  on the primary side. It is assumed that the QAB is closed-loop controlled to operate as a DCX, so that  $v_{S,B}$  and  $v_{S,C}$  can be considered constant voltage sources. The rise time of the primary side switching node  $v_P$  is faster than  $v_{S,A}$ , because the sum of the currents  $i_{S,B}$  and  $i_{S,C}$  is much higher than the peak of the magnetizing current. This implies that  $\frac{dv}{dt}$  across the series inductance parasitic capacitance  $C_{L_s}$  is approximately constant, therefore the constant current through  $C_{L_s}$  charges  $v_{S,A}$  linearly.

At the mid-point of Interval II,  $nv_P$  becomes higher than  $v_{S,A}$ , and the slope of  $i_{S,A}$  changes polarity. Interval II ends, completing the ZVS transition of  $v_P$ , at the end of the primary-side dead time  $t_{dp}$ .

Interval III starts with turning on switches  $Q_{1P}$  and  $Q_{4P}$  of the primary full bridge. The corre-

sponding equivalent circuit is shown in Fig. 8(c). During this interval, current  $i_{S,A}$  is increasing until  $v_{S,A}$  reaches the end of the ZVS transition. At that instant,  $Q_{1S,A}$  and  $Q_{4S,A}$  are turned on, which ends Interval III and the secondary phase A dead time  $t_{ds}$ .

It should be noted that the total current that charges the switching node capacitance,

$$i_{tot,A} = i_{S,A} + i_{M,A} + i_{C_{L_S,A}} \quad (2)$$

reaches a minimum at the beginning of the Interval II. If this current became negative, it would start discharging the secondary side switching-node capacitance  $C_S(v)$ , which means that it would not be possible to complete the ZVS switching sequence as described above. Fig. 6 shows theoretical waveforms for the case when the minimum of  $i_{tot,A}$  is zero. This represents the optimal design, in the sense of achieving ZVS operation while minimizing the peak of the magnetizing inductance current, and therefore minimizing the conduction losses introduced by the circulating current. Proper sizing of the magnetizing inductance and appropriate selection of primary and secondary dead-times is critical for an optimal design

Thus, an optimal design procedure gives the following values:

- Primary side dead-time: 110 ns

- Secondary side dead-time: 740 ns

- Magnetizing inductance: 385  $\mu$ H

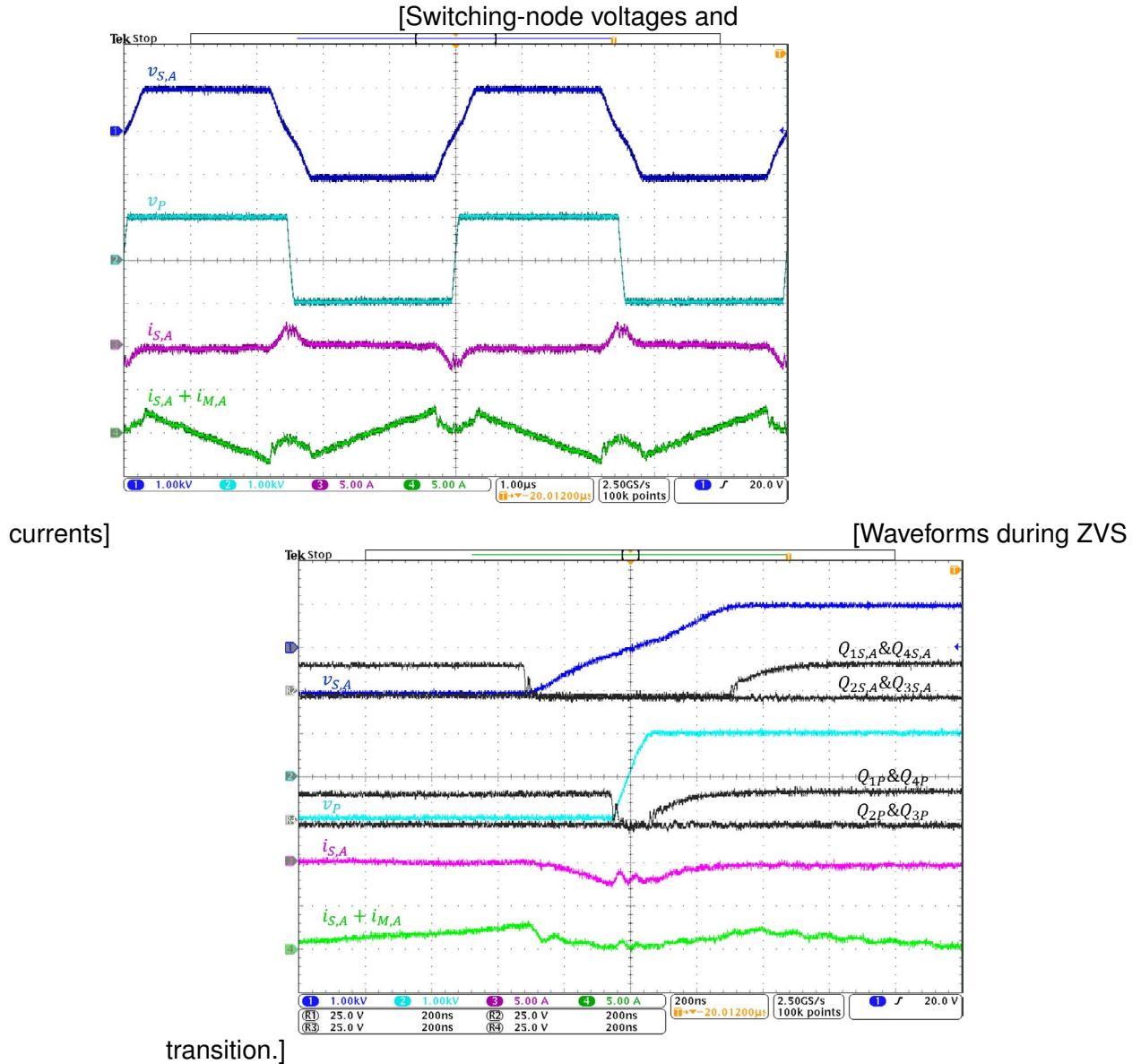

The above parameters ensure ZVS over the entire line cycle. Fig. 9(a) shows ZVS operation at the zero power crossing of phase A, while Fig. 9(b) confirms that the measured waveforms closely match the theoretical waveforms shown in Fig. 6. It should be noted that the planar implementation of the magnetic components have pronounced parasitics, which result in increased high-frequency parasitic oscillations.

## 5 AC-side controllers for decentralized power sharing and interleaving

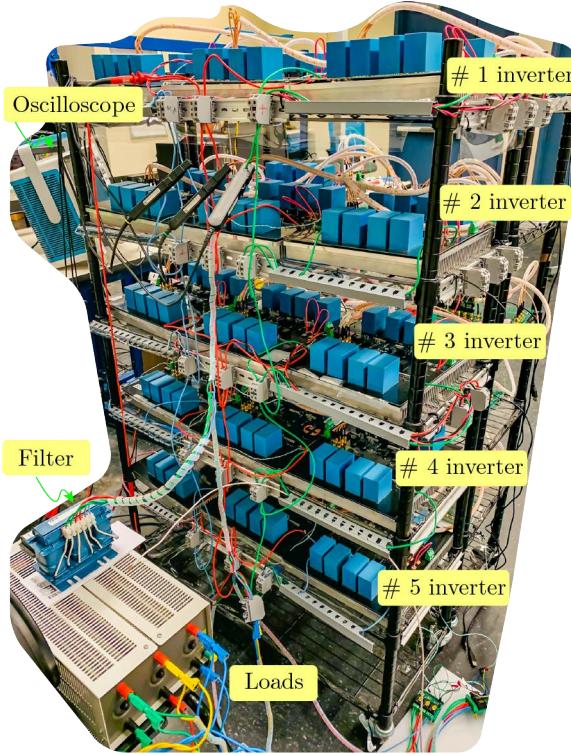

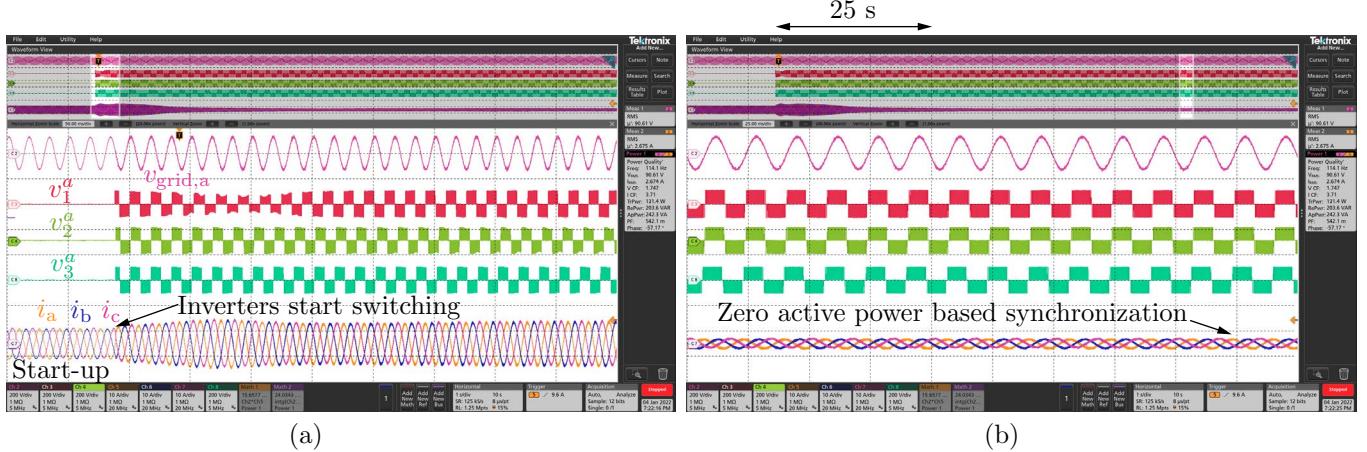

In this work, we formulated a model of the stacked converter system equipped with the Andronov-Hopf Oscillators (AHO) to control active and reactive power delivery on the ac side of the system. The aim was to obtain a decentralized structure that bypassed the need for a centralized controller which may act as a single point of failure and hinder scalability. In prior reports, we determined the parameters of the AHO controller that will result in stable operation of the system. Here, the experimental results that validate the performance of the proposed AHO-based controller for cascaded dc-ac inverters is presented. The laboratory-scale experimental hardware platform consisting of 5 cascaded three-phase inverters as shown in Fig. 10. On the ac-side the inverter stack is interfaced to an R-L load through an inductive line filter. The most noteworthy feature of this control method is that there is no communication links among the stacked inverters.

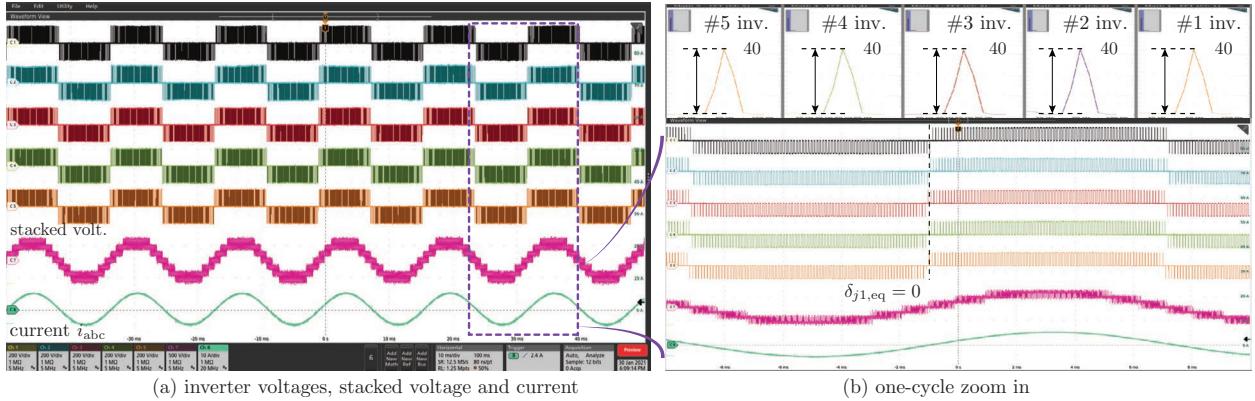

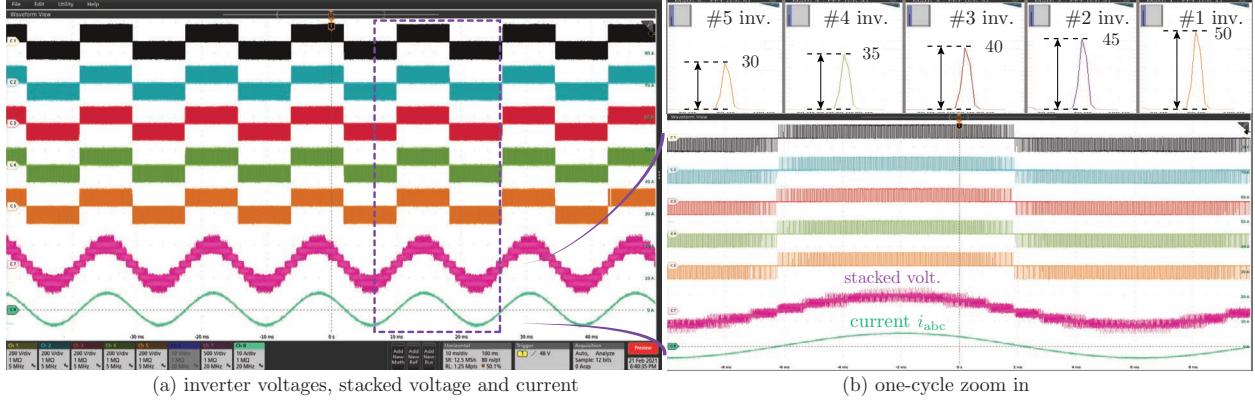

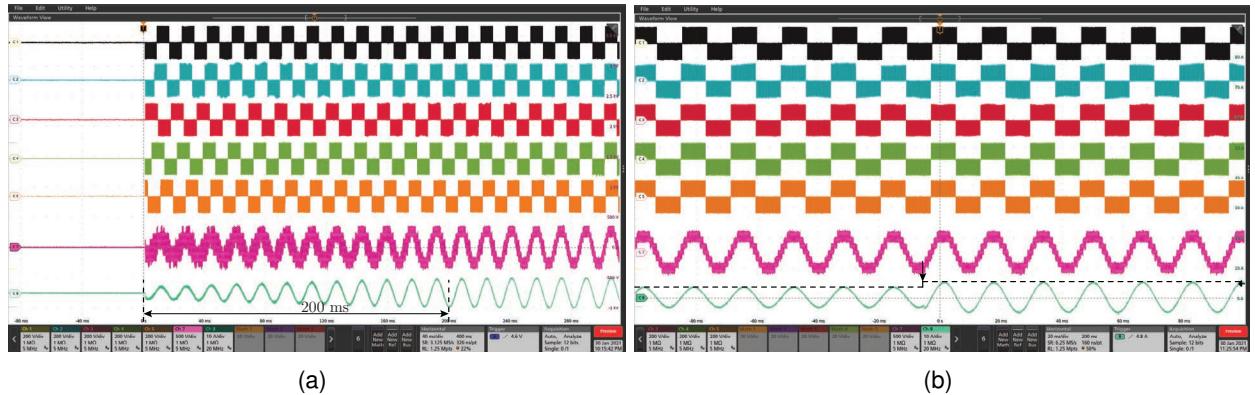

Experimental validation of the proposed AHO-based cascaded inverter control method is demonstrated in Figs. 11–14(b). Figure 11(a) shows steady-state operation of the system with equal nominal RMS voltage set-points at  $V_{nom} = 40$  V, for all the 5 units. In this case, the overall stack voltage is 200  $V_{rms}$  and every unit delivers 420 W of active power to the load. A zoomed-in view of the inverter phase voltages is shown in Fig. 11(b) (bottom), which verifies the fact that the inverter output voltages have zero relative angle difference at steady state ( $\delta_{j1,eq} = 0$ ,  $j = 1, \dots, 5$ ), owing to uniform voltage and power set-points along the stack. Figure 11(b) (top) shows the fundamental 60 Hz component in individual inverter output voltages that verify uniform voltage sharing.

Figure 9: Waveforms illustrating zero voltage switching at the zero power instant for phase A.

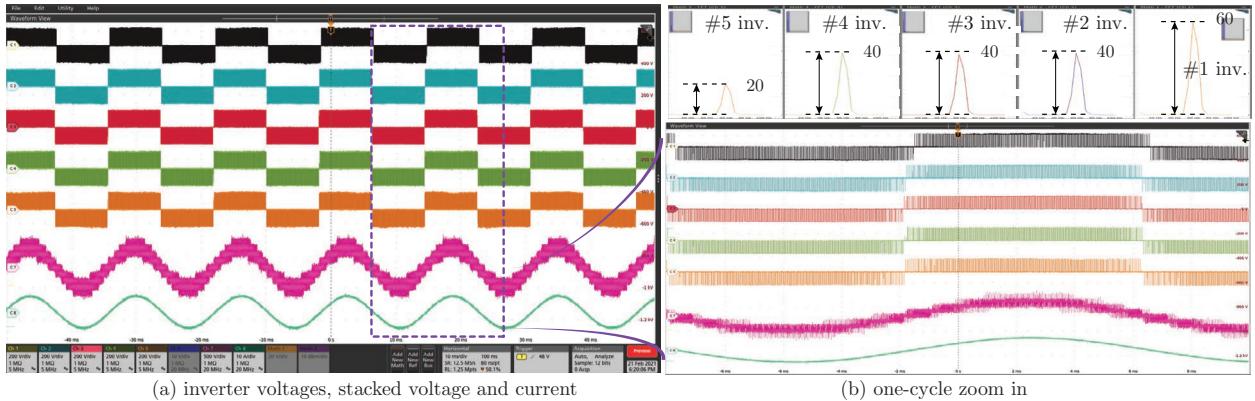

Figs. 12 and 13 demonstrate non-uniform power sharing in the cascaded system. Figure 12(a) shows the system steady state operation with unequal nominal voltage set-points as,  $V_{\text{nom}1} = 50$  V,  $V_{\text{nom}2} = 45$  V,  $V_{\text{nom}3} = 40$  V,  $V_{\text{nom}4} = 35$  V,  $V_{\text{nom}5} = 30$  V. In this case, the inverters share the total load power according to their power ratings. Even if the inverters generate unequal voltages, their relative angle differences are still same as can be seen in Fig. 12(b) (bottom). Figure 12(b) (top) shows the fundamental 60 Hz component in the inverter voltages which are unequal and vary according to the nominal voltage set-point of the inverter. Fig. 13 shows another case of non-uniform power sharing where 3 inverters are of equal power rating while the other two have different ratings. These results illustrate how series-connected converters can share adjustable power and voltages without explicit communication channels.

Next, Fig. 14(a) demonstrates the communication-free synchronization of the inverters from randomized initial voltages to the desired nominal voltage  $V_{\text{nom}} = 40$  V. The time required for the

Figure 10: Developed experimental platform: 5 cascaded inverters supplying common loads.

Figure 11: Uniform load sharing:  $V_{\text{nom}1} = 40 \text{ V}$ ,  $V_{\text{nom}2} = 40 \text{ V}$ ,  $V_{\text{nom}3} = 40 \text{ V}$ ,  $V_{\text{nom}4} = 40 \text{ V}$ ,  $V_{\text{nom}5} = 40 \text{ V}$ .

inverter voltages to synchronize with one another is around 200ms.

In Fig. 14(b) the dynamic response of the stack of inverters to a load-step change is shown. In this case, the load is stepped up by 33% and the inverters step up their power output while regulating their output voltages within the specified 2% offset range. Also, as can be seen, the response time of the inverters to this load step change is less than 1 ac cycle.

## 6 Control Design of Cascaded Converters

Practical implementation of the quadruple-active bridge converter module in PV systems requires a variety of controllers that collectively achieve maximum power point tracking, dc-link regulation, and ac-side power control. Design of such multi-loop systems is generally quite challenging due

Figure 12: Non-uniform load sharing. Case-1:  $V_{\text{nom}1} = 50$  V,  $V_{\text{nom}2} = 45$  V,  $V_{\text{nom}3} = 40$  V,  $V_{\text{nom}4} = 35$  V,  $V_{\text{nom}5} = 30$  V.

Figure 13: Non-uniform load sharing. Case-2:  $V_{\text{nom}1} = 60$  V,  $V_{\text{nom}2} = 40$  V,  $V_{\text{nom}3} = 40$  V,  $V_{\text{nom}4} = 40$  V,  $V_{\text{nom}5} = 20$  V.

Figure 14: Transient performance : (a) Start up transient and (b) Load step change 30%.

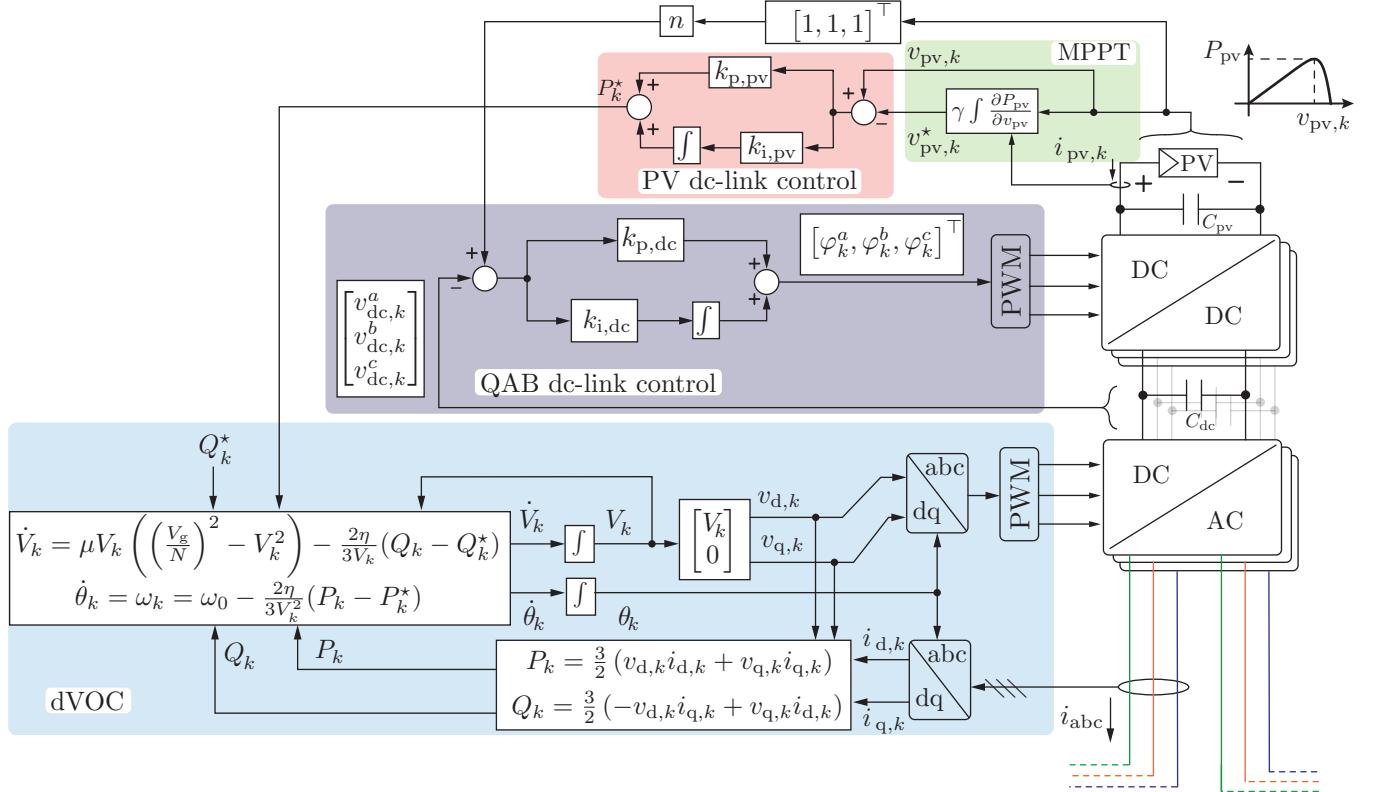

to the potential for destabilizing interactions among loops. We propose a design approach where singular perturbation theory is used to decompose the timescales at which each control loop operates and provides a systematic framework for parametric selection. Our approach also ensures system stability of multiple modules with identical controls connected in series across a grid. Next, we discuss the various control subsystems.

Figure 15: The control architecture of the  $k$ -th converter module contains the following interconnected control loops: MPPT, PV dc-link control, floating dc-link controls, and dVOC-based ac-side control. The quadruple active bridge converter is compactly depicted with three dc-dc blocks, and the dc-ac H-bridge inverters interface to adjacent units in the system.

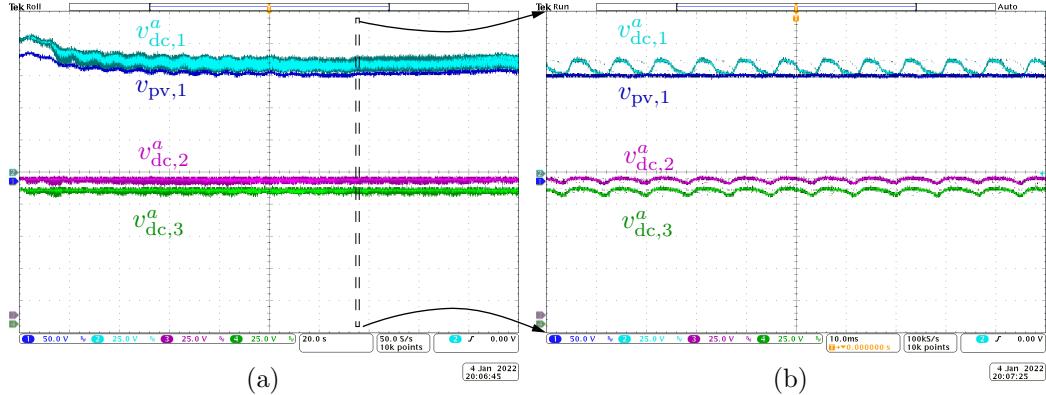

**QAB with Floating Dc Links:** The primary side bridge is common to each of the three floating secondary bridges. All four bridges are modulated to produce an ac voltage waveform with 50% duty ratio, and the primary-side bridge acts as an angular reference to the remaining three others. Accordingly, the phase shifts of the secondary bridge waveforms relative to the primary side will act as our control signal for dc link voltage regulation. We denote the phase shift of the secondary DAB bridge associated with the  $j$ -th ac phase within the  $k$ -th module as  $\varphi_k^j$ , where  $j \in \{a, b, c\}$ . The voltage across each of the floating dc links evolves as

$$C_{dc} \frac{dv_{dc,k}^j}{dt} = \frac{v_{pv,k}}{nL\omega_{sw}} \varphi_k^j \left( 1 - \frac{\varphi_k^j}{\pi} \right) - \frac{P_k^j}{v_{dc,k}^j}, \quad (3)$$

where  $\omega_{sw}$  is the DAB switching frequency in rad/s,  $\varphi_k^j$  is the phase shift of each secondary bridge with respect to the primary, and  $v_{pv,k}$  is the dc voltage across the PV input.  $P_k^j$  denotes the power transferred from the primary to the  $j$ -th secondary.

A proportional-integral (PI) controller ensures DCX operation such that the dc voltage across  $C_{dc}$  tracks  $nv_{pv}$ . This gives the following control law:

$$\varphi_k^j = k_{p,dc}(nv_{pv,k} - v_{dc,k}^j) + C_{dc}k_{i,dc} \int (nv_{pv,k} - v_{dc,k}^j) dt \quad (4)$$

This controller is replicated across the three dc links where  $j \in \{a, b, c\}$ . The proportional and integral gains are denoted as  $k_{p,dc}$  and  $k_{i,dc}$ , respectively.

Within a given module, we assume the floating dc-link voltage for each phase,  $v_{dc,k}^j$ , is approximately equal to its steady state value,  $v_{dc,k}^0$ . Furthermore, each DAB is assumed to operate with small phase shifts such that  $(\varphi_k^j)^2$  is negligibly small. Taken together, these modeling constructs allow us to convert the dynamics in (3) into the simplified model given by

$$C_{dc} \frac{dv_{dc,k}^j}{dt} = \frac{v_{pv,k}}{nL\omega_{sw}} \varphi_k^j - \frac{P_k^j}{v_{dc,k}^0}. \Rightarrow C_{dc} \frac{dv_{dc,k}}{dt} = \frac{v_{pv,k}}{nL\omega_{sw}} \varphi_k - \frac{P_k}{3v_{dc,k}^0},$$

where lumped variables  $v_{dc,k}$  and  $\varphi_k$  are defined as  $v_{dc,k} = (1/3) \sum_j v_{dc,k}^j$ ,  $\varphi_k = (1/3) \sum_j \varphi_k^j$ .

**Ac-Side Dynamics:** Each set of module-level three-phase H-bridges is modulated with the dVOC dynamics given by

$$\dot{V}_k = \mu V_k \left( \left( \frac{V_g}{N} \right)^2 - V_k^2 \right) - \frac{2\eta}{3V_k} (Q_k - Q_k^*), \quad (5a) \quad \dot{\theta}_k = \omega_k = \omega_0 - \frac{2\eta}{3V_k^2} (P_k - P_k^*), \quad (5b)$$

where  $\mu$  and  $\eta$  are control gains, and  $\omega_0$  is the nominal grid frequency. The peak voltage generated by each single phase inverter is denoted as  $V_k$ , and the three-phase waveforms are in the vector  $v_k = [v_k^a, v_k^b, v_k^c]^\top$ . Active and reactive power delivered by the  $k$ -th module are represented as  $P_k$  and  $Q_k$ , respectively. Similarly,  $P_k^*$  and  $Q_k^*$  denote the corresponding references for active and reactive power, respectively. In subsequent analysis, we will show that  $P_k^*$  is generated by an upstream control loop whereas  $Q_k^*$  will be assumed constant.  $N$  series-connected sets of ac terminals with the aforementioned control give the following line filter dynamics:

$$\sum_{k=1}^N V_k \cos \delta_k = L_f \frac{di_d}{dt} - L_f \omega i_q + R_f i_d + V_g, \quad \sum_{k=1}^N V_k \sin \delta_k = L_f \frac{di_q}{dt} + L_f \omega i_d + R_f i_q \quad (6)$$

where  $P_{in,k}$  is the PV-generated power and  $P_{out,k}$  is power delivered to the QAB. Assuming the QAB circuitry is lossless, it follows that  $P_{out,k}$  equals the ac side power,  $P_k$ , for the  $k$ -th module. The input power is expressed as  $P_{in,k} = v_{pv,k} i_{pv,k}$  where the PV current  $i_{pv,k}$  takes the form

**PV Terminal Dynamics:** Energy buffering between the PV panel and QAB stage is provided by the PV-side capacitance  $C_{pv}$ . The PV voltage dynamics can be expressed as

$$\frac{d}{dt} \left( \frac{1}{2} C_{pv} v_{pv,k}^2 \right) = P_{in,k} - P_{out,k}, \quad (7)$$

A small signal dynamic model is obtained by the addition of perturbations to  $v_{pv,k}$ ,  $P_{in,k}$ , and  $P_{out,k}$  in (7). This gives

$$V_{pv,k} C_{pv} \frac{dv_{pv,k}}{dt} = f_{pv}(v_{pv,k}, i_{pv,k}, r_{pv,k}) - p_k^*. \quad (8)$$

We will simplify (8) by approximating the value of  $f_{pv}(v_{pv,k}, i_{pv,k}, r_{pv,k})$  at distinct regions across the PV curve.

$$f_{pv,k}(\cdot) = \begin{cases} I_{pv,k} v_{pv,k}, & \text{when } v_{pv,k} < V_{mpp,k} - \frac{\epsilon}{2} \\ -\frac{v_{pv,k}^2}{R_{mpp,k}}, & \text{when } V_{mpp,k} - \frac{\epsilon}{2} < v_{pv,k} < V_{mpp,k} + \frac{\epsilon}{2} \\ -\frac{V_{pv,k}}{r_{pv,k}} v_{pv,k}, & \text{when } v_{pv,k} > V_{mpp,k} + \frac{\epsilon}{2} \end{cases}$$

The PV dc-link controller ensures the  $k$ -th PV voltage,  $v_{\text{pv},k}$ , is regulated to follow the command  $v_{\text{pv},k}^*$ , which is produced by the MPPT. To this end, a PI controller processes the voltage error and generates the ac side power reference,  $P_k^*$ . The PV dc-link controller is given by

$$P_k^* = k_{\text{p,pv}}(v_{\text{pv},k} - v_{\text{pv},k}^*) + C_{\text{pv}}k_{\text{i,pv}} \int (v_{\text{pv},k} - v_{\text{pv},k}^*) dt. \quad (9)$$

**MPPT Control:** To evaluate MPPT performance we seek a simplified version of (8) and linearize the algebraic expression of the pv current around the MPP to obtain

$$i_{\text{pv},k} = I_{\text{mpp},k} - \frac{1}{R_{\text{mpp},k}}(v_{\text{pv},k} - V_{\text{mpp},k}), \quad (10)$$

To track the MPP, we employ the integral control law that acts on the slope of the PV power-voltage curve as follows:

$$v_{\text{pv},k}^* = \gamma \int \frac{\partial(v_{\text{pv},k} i_{\text{pv},k})}{\partial v_{\text{pv},k}} dt \quad (11)$$

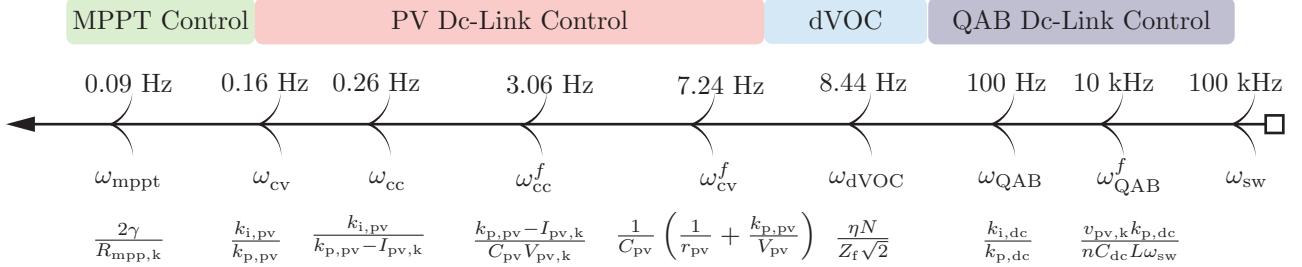

For each of the aforementioned subsystems, we now shift our focus to designing the controllers after application of singular perturbation theory. Our overall strategy is predicated on an intuition of how the various subsystems within each module interact and seeking a logical ordering of timescales over which they operate. Towards this objective, we first apply singular perturbation to each subsystem such that it is partitioned into fast and slow modes. This yields a form that is amenable to design such that we can obtain the preordained ordering and separation of timescales while also guaranteeing stability within and among subsystems. In the ensuing analysis we apply the aforementioned strategy and describe each subsystem sequentially from fastest to slowest.

#### **QAB Dc-link Voltage Regulation:**

*State Equations:* Dc link voltage control is achieved through the PI regulator in (4). To cast the subsystem in (3)–(4) into the singular perturbation framework, we define two new states as

$$e_{1,k} := nv_{\text{pv},k} - v_{\text{dc},k}, \quad e_{2,k} := C_{\text{dc}} \int_0^\tau e_{1,k} d\sigma + e_{2,k}(0),$$

where  $\tau = t/C_{\text{dc}}$  is the new time variable associated with the fast mode. Now (3) and (4) can be rewritten as

$$C_{\text{dc}} \frac{de_{1,k}}{d\tau} = \frac{-v_{\text{pv},k}}{nL\omega_{\text{sw}}} (k_{\text{p,dc}}e_{1,k} + k_{\text{i,dc}}e_{2,k}) + \frac{P_k}{3v_{\text{dc},k}^0}, \quad (12a) \quad \frac{de_{2,k}}{d\tau} = C_{\text{dc}}e_{1,k}. \quad (12b)$$

From (12a), we set  $C_{\text{dc}}$  to zero, obtain the algebraic solution of  $\bar{e}_{1,k}$ , and substitute that into (12b) to obtain the reduced order model as follows:

$$\frac{d\bar{e}_{2,k}}{dt} = -\frac{k_{\text{i,dc}}}{k_{\text{p,dc}}} \bar{e}_{2,k} + \left( \frac{v_{\text{pv},k}}{nL\omega_{\text{sw}}} \right)^{-1} \frac{P}{3k_{\text{p,dc}}v_{\text{dc},k}^0} \quad (13)$$

The fast mode model is

$$\frac{d\tilde{e}_{1,k}}{d\tau} = -\frac{v_{\text{pv},k}k_{\text{p,dc}}}{nC_{\text{dc}}L\omega_{\text{sw}}} \tilde{e}_{1,k} =: -\omega_{\text{QAB}}^f \tilde{e}_{1,k}, \quad (14)$$

where  $\tilde{e}_{1,k}$  captures the error in excess of  $\mathcal{O}(\varepsilon)$  in  $e_{1,k} - \bar{e}_{1,k}$ .

*Stability and Control Parameter Selection:* For stability, it is necessary to ensure  $k_{\text{p,dc}} \geq 0$  and  $k_{\text{i,dc}} \geq 0$ . From (13), the effective bandwidth of the QAB loop is  $\omega_{\text{QAB}} = \frac{k_{\text{i,dc}}}{k_{\text{p,dc}}}$ . This leads us to the first stability criteria as

$$\omega_{\text{QAB}} \ll \omega_{\text{QAB}}^f \ll \omega_{\text{sw}}, \quad (15)$$

where  $\omega_{QAB}$  corresponds to the slower acting integral control and  $\omega_{QAB}^f$  captures the bandwidth of the fast mode model in (14). Appropriate substitutions into (15) give the following guideline for control gain selection:

$$\frac{k_{i,dc}}{k_{p,dc}} \ll \frac{v_{pv,k} k_{p,dc}}{n C_{dc} L \omega_{sw}} \ll \omega_{sw}. \quad (16)$$

### DVOC-based Inverter Control:

*State Equations:* The nonlinear DVOC control law exhibits slower dynamics than the plant in (6). This follows from the observation that the small perturbation parameter  $L_f/R_f$  gives fast line dynamics. Hence, we set  $L_f/R_f = 0$  and obtain the following algebraic solution from (6):

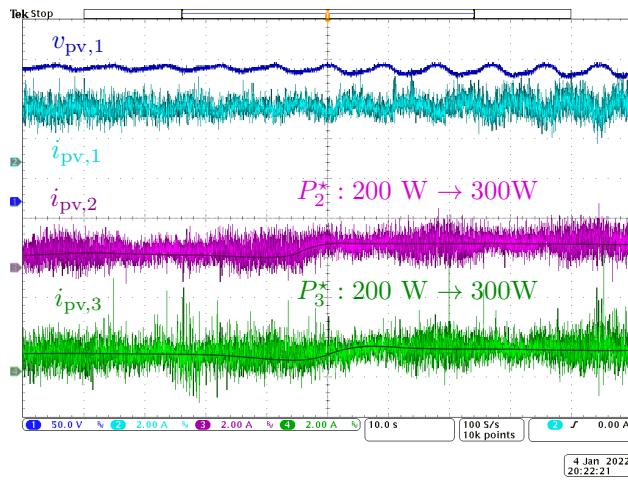

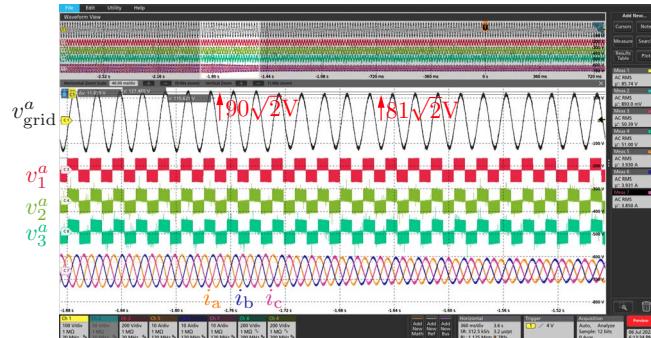

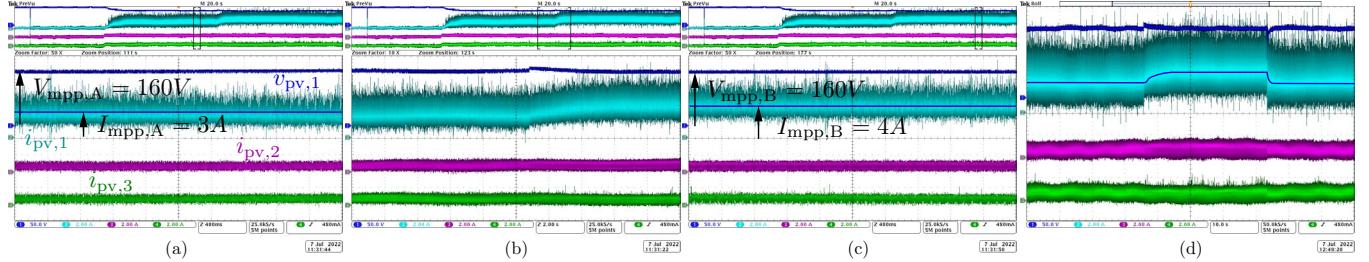

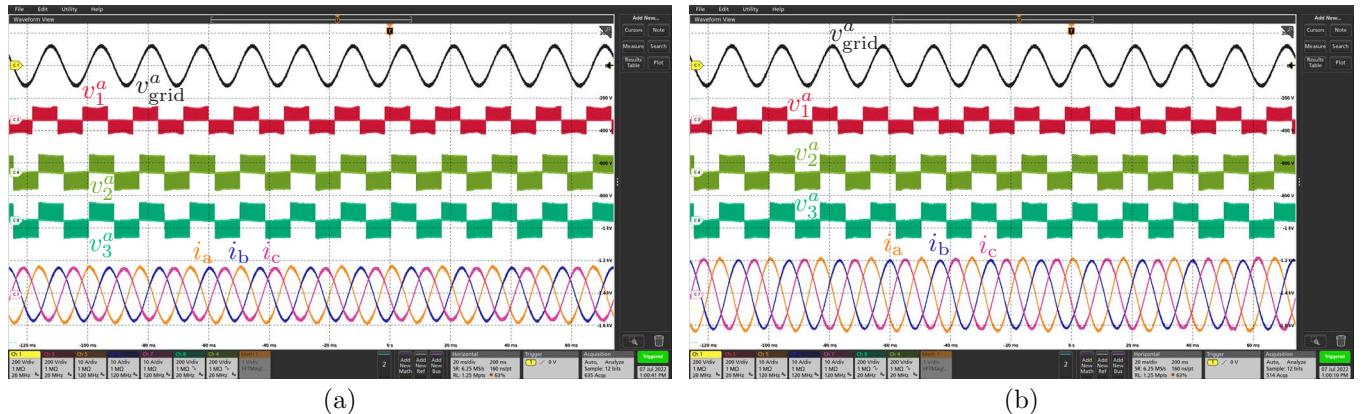

$$i_d = \frac{\sum_{k=1}^N V_k \cos(\delta_k - \phi_f) - V_g \cos(\phi_f)}{Z_f}, \quad (17a) \quad i_q = \frac{\sum_{k=1}^N V_k \sin(\delta_k - \phi_f) + V_g \sin(\phi_f)}{Z_f}, \quad (17b)$$