# High Voltage Regrown GaN P-N Diodes Enabled by Defect and Doping Control

Andrew Armstrong,<sup>1</sup> Daniel Feezell,<sup>2</sup> Andrew Allerman,<sup>1</sup> Greg Pickrell,<sup>1</sup> Andrew Aragon,<sup>2</sup> Mary Crawford,<sup>1</sup> Kimberlee Celio,<sup>1</sup> F. Leonard,<sup>1</sup> and A. Alec Talin<sup>1</sup>

<sup>1</sup>Sandia National Laboratories, <sup>2</sup>University of New Mexico

## GaN electronics for domestic energy security

**Goal:** Demonstrate 1.2 kV GaN diodes using selective area regrowth

**Challenge:** Regrown GaN diodes exhibit current leakage and premature breakdown

## Quantitative correlation of ICP etching, deep level defects and reverse leakage

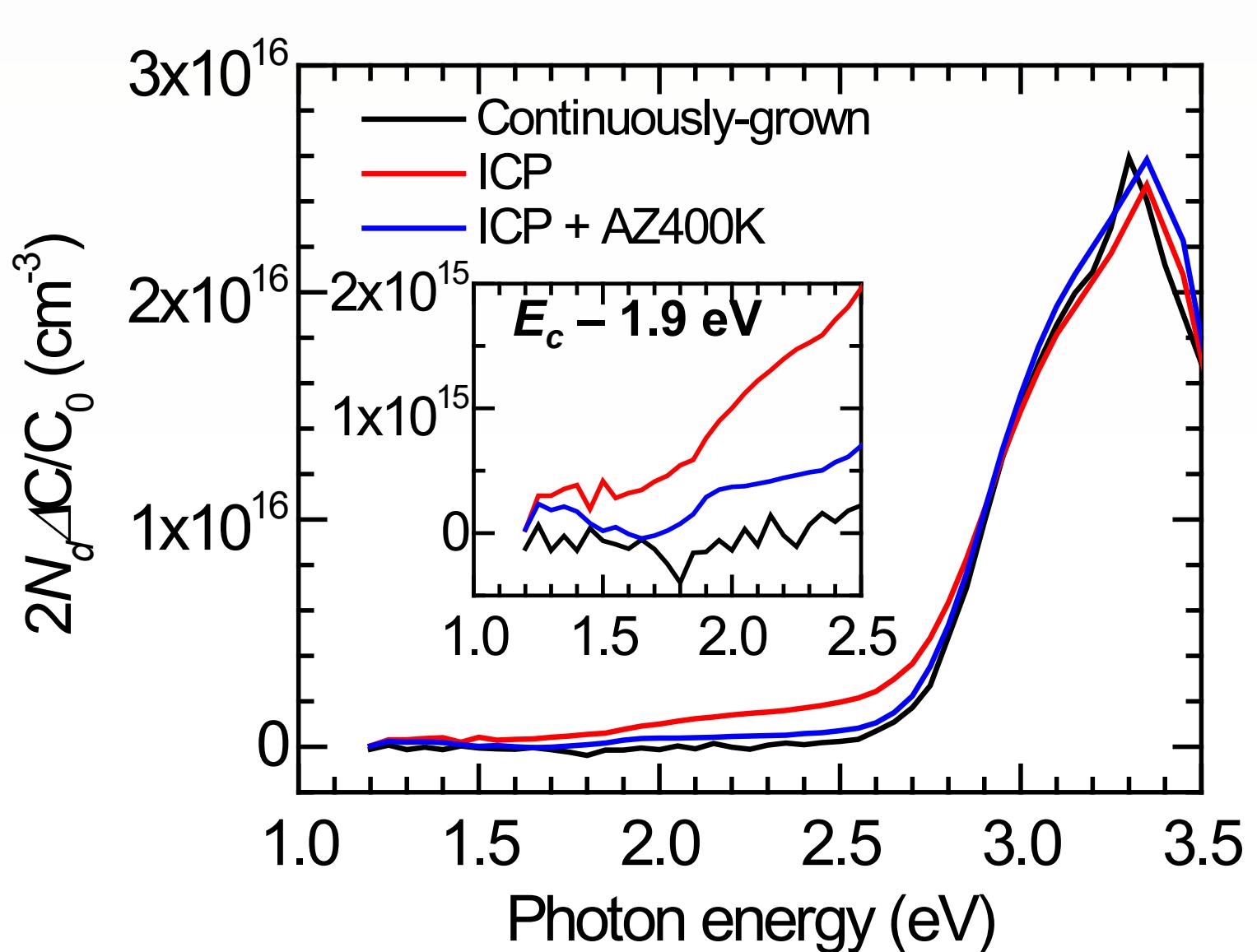

### Steady-State Photocapacitance

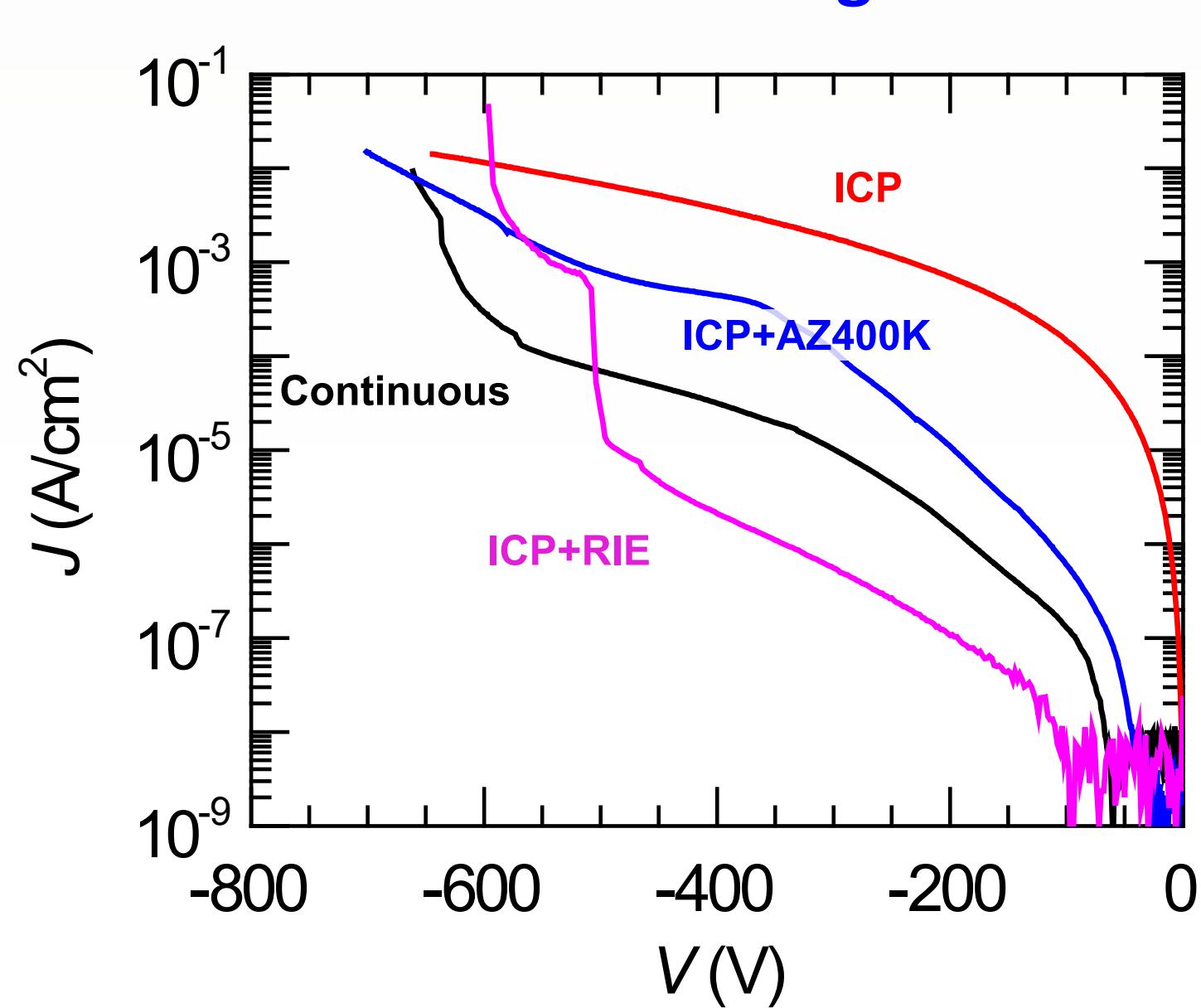

### Reverse leakage

### ICP etch and regrowth

- Etch-enhanced  $E_c - 1.9$  eV deep level correlated with increased reverse leakage

- ICP+AZ400K reduces  $E_c - 1.9$  eV deep level relative to ICP only

- Correlated with large reduction in reverse leakage

## Remove ICP etch damage using slow RIE etch

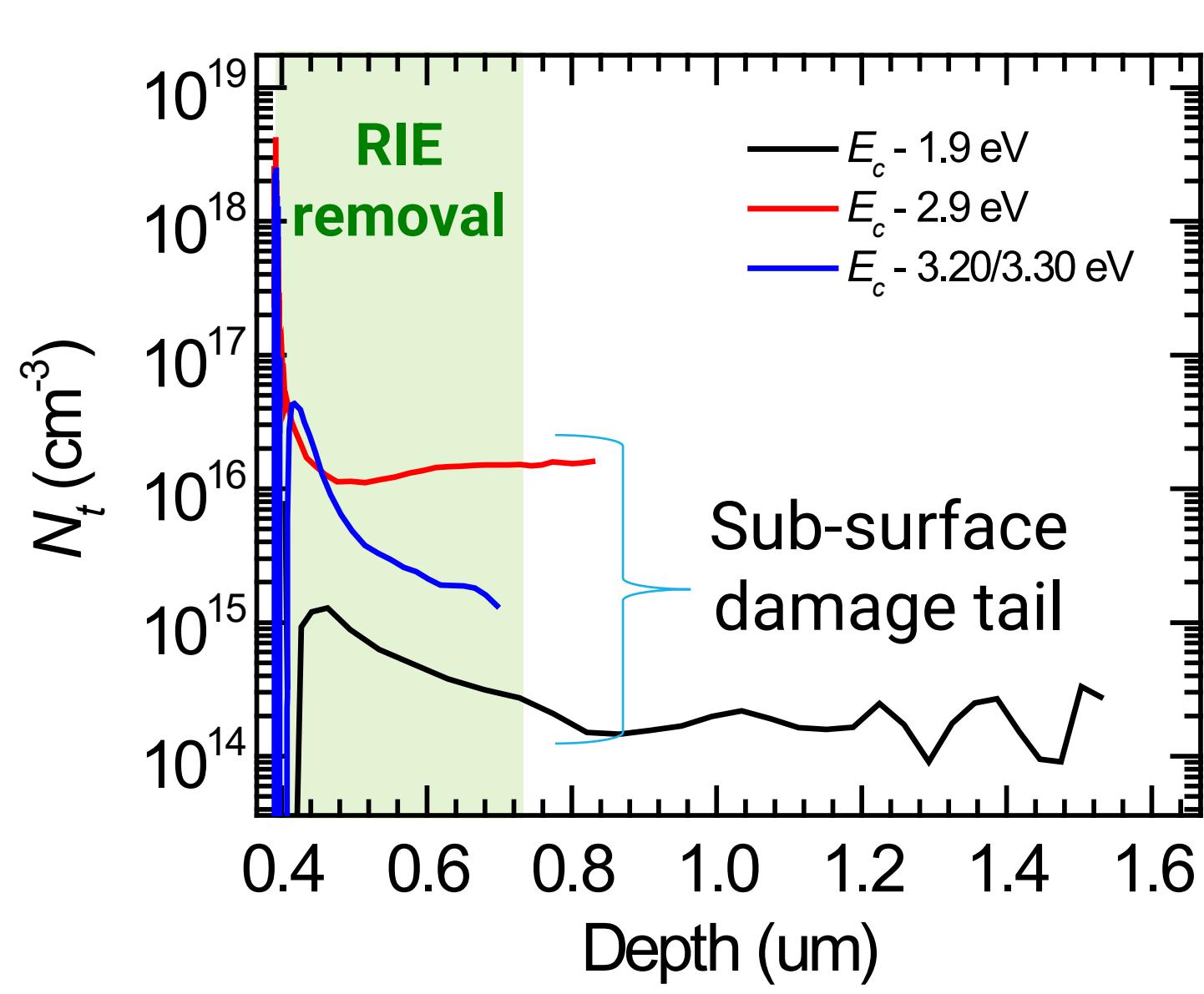

### Deep level depth profile for AZ400K treatment

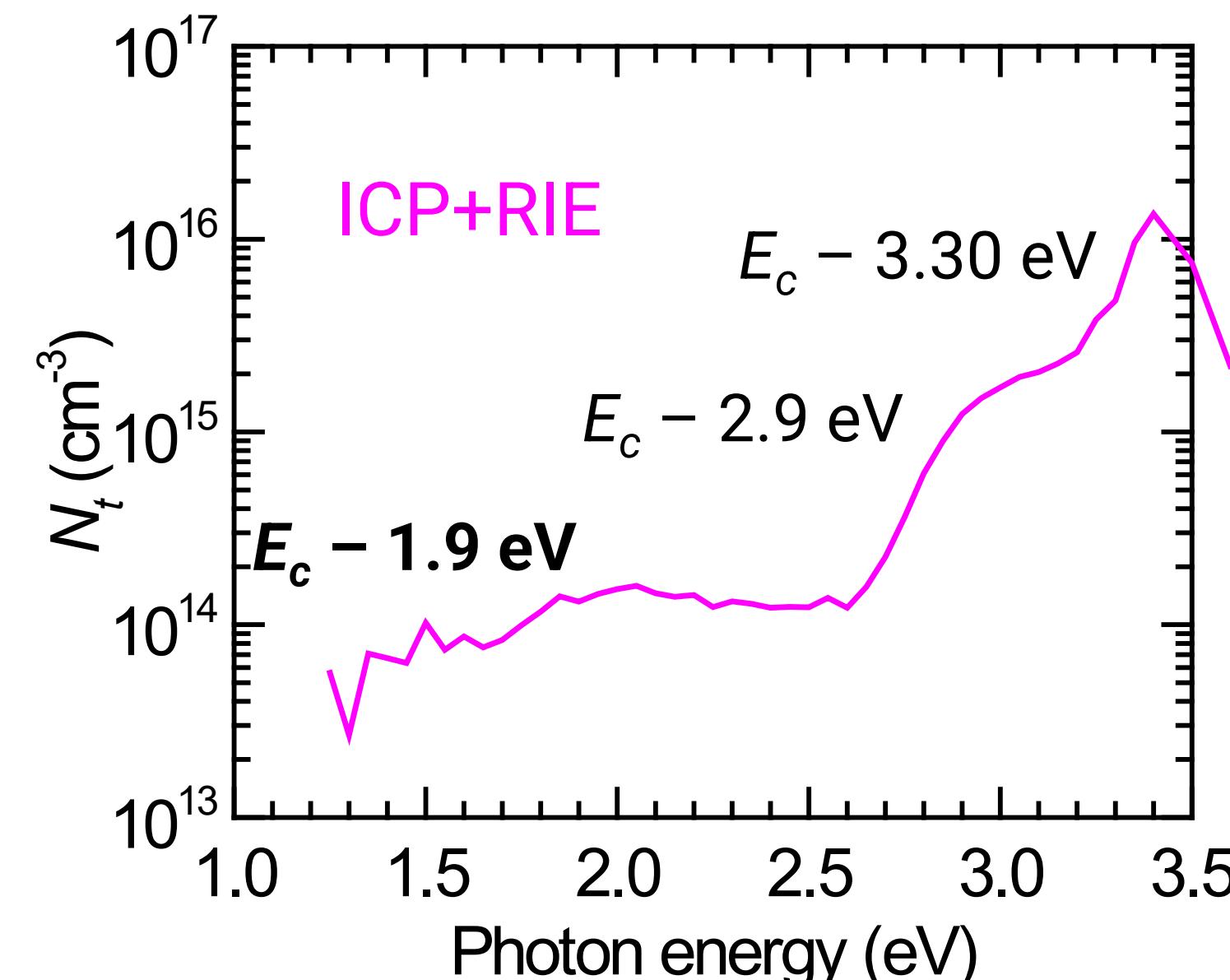

### SSPC of ICP+RIE pn-diode

### RIE after ICP removes sub-surface damage

- Depth profiling of deep levels reveals sub-surface damage not removed by AZ400K

- Removed 270 nm of material below ICP-etched surface using slow RIE etch

- RIE etch reduces  $E_c - 1.9$  eV defect state and reverse leakage to as-grown levels

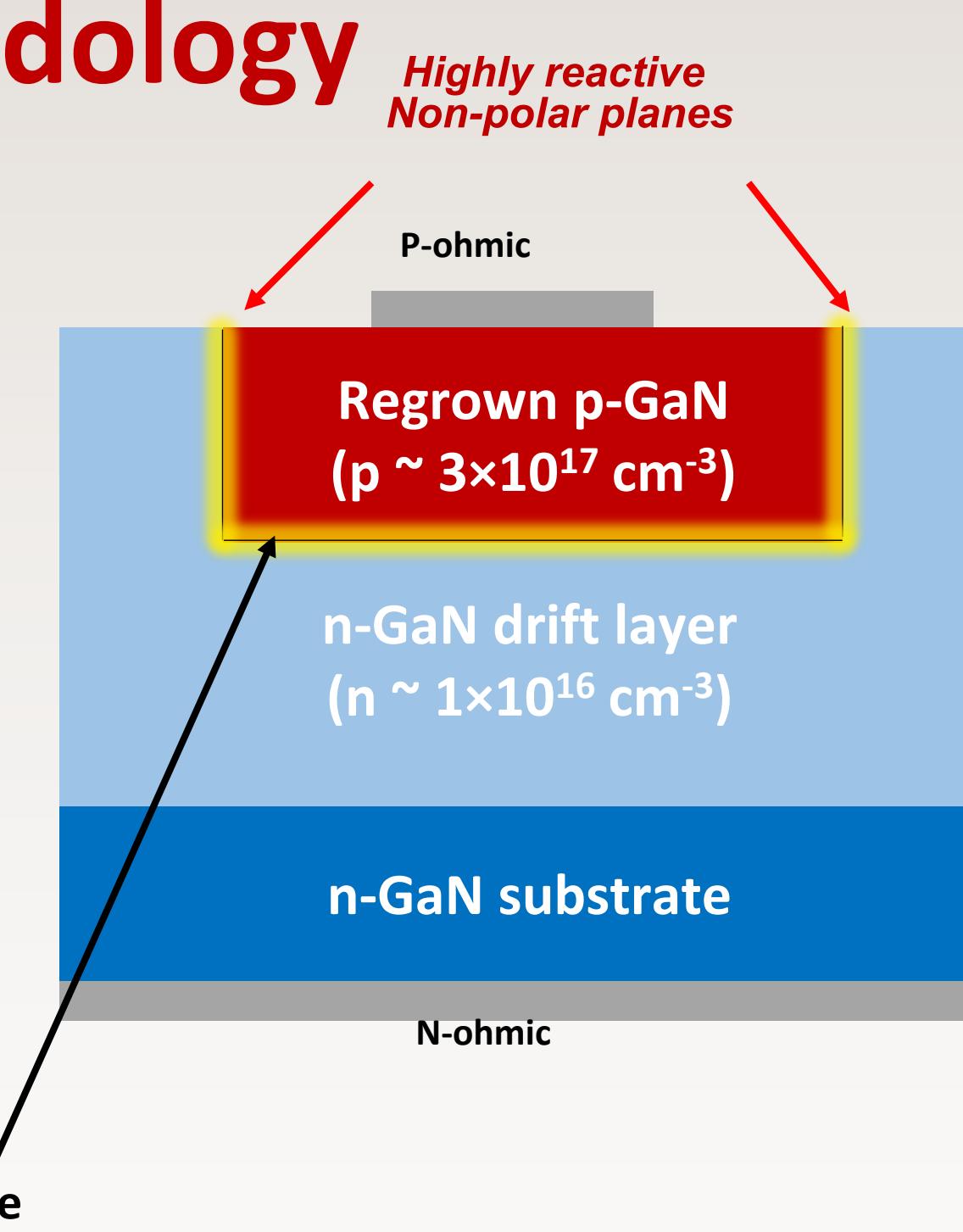

## Problem and Methodology

- Regrowth interfaces have elevated impurity concentrations that can lead to excess leakage

- Si is main concern for c-plane

- Si and O impurities are important for m-plane sidewalls

- Control impurities at regrowth interface of c-plane and m-plane regrown diodes

- Optimized regrowth so that Si contamination is not detrimental to diode operation

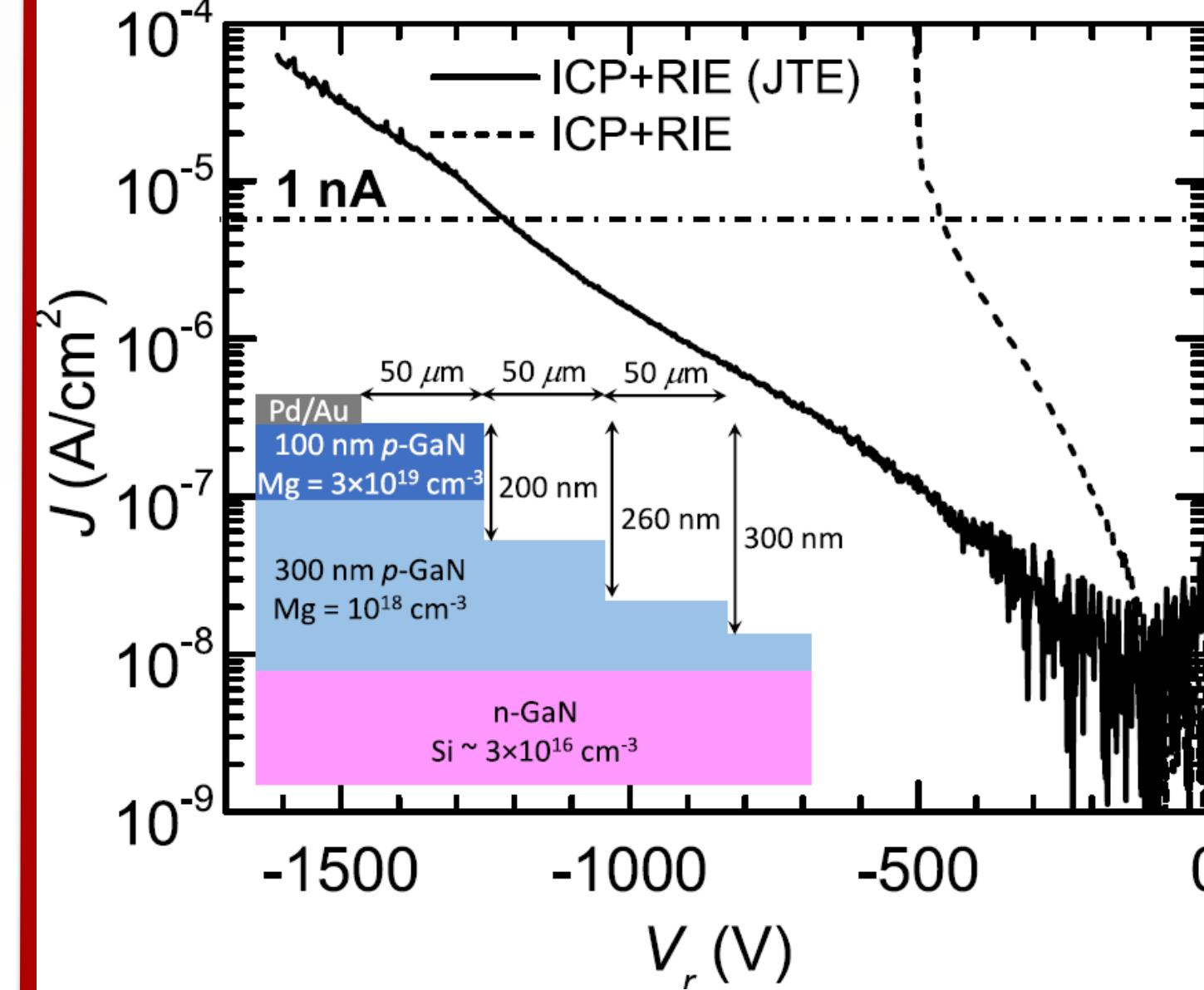

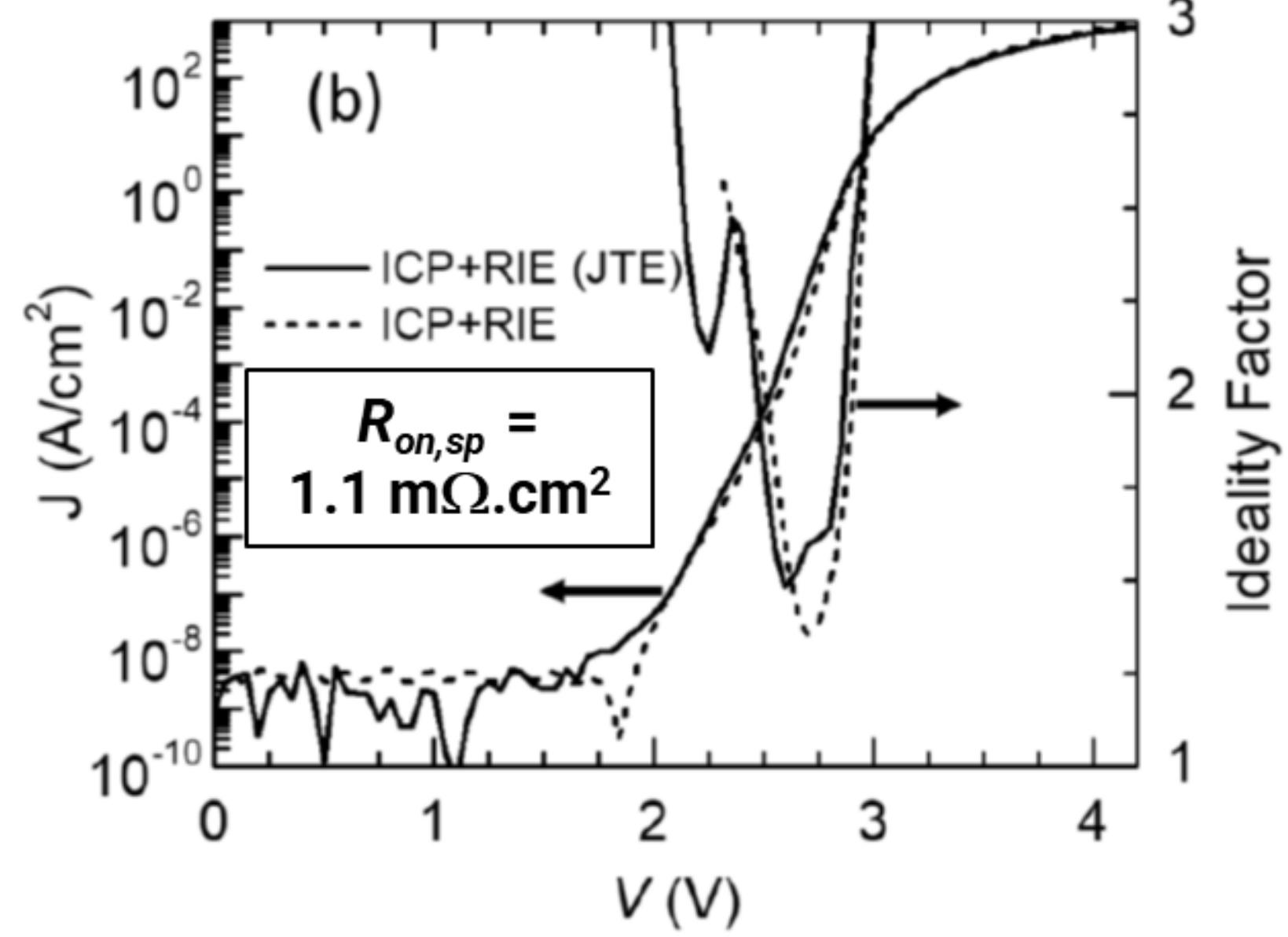

## 1500 V etched-and-regrown diode using ICP+RIE and Junction Termination Extension (JTE)

### Reverse I-V for ICP+RIE with JTE

### Forward I-V for ICP+RIE with JTE

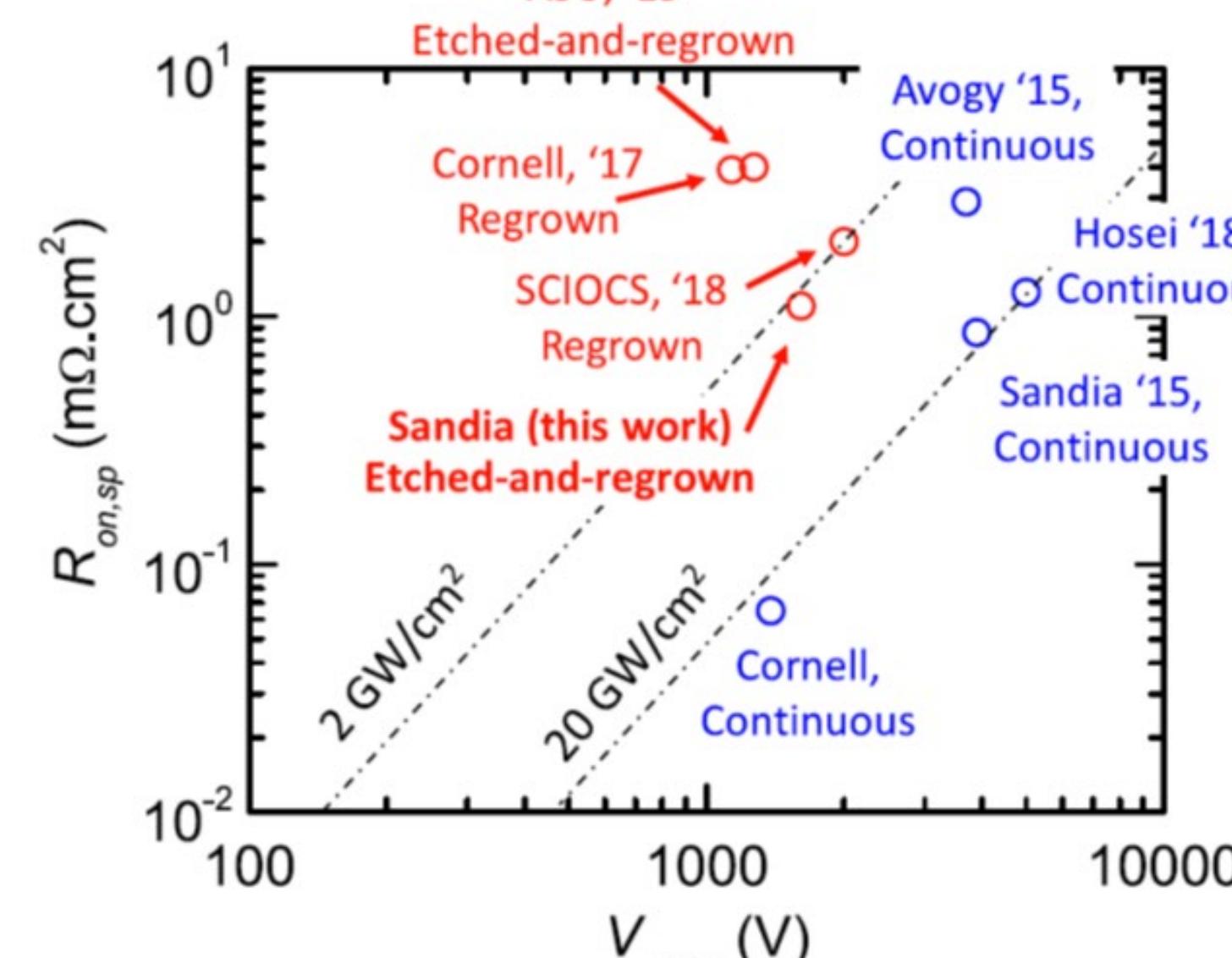

## kV-class etched-and-regrown diodes with JTE

- 1.5 kV diode with lower leakage (< 1.2 kV) than best reported regrown diode (no etch)\*

- Figure-of-merit still lags continuously-grown diodes

- Suggests other leakage paths exist beyond defectivity in drift region

\* H. Fujikura, et al., APEx 11, 045502 (2018).

## Summary and Conclusions

- ICP etch strongly increases  $E_c - 1.9$  eV deep level concentration and reverse leakage

- Slow RIE etch after ICP reduces  $E_c - 1.9$  eV concentration and reverse leakage to as-grown levels

- Achieved 1.5 kV etched-and-regrown diode by combining ICP+RIE with JTE

- Additional leakage path must exist beyond deep levels because ICP+RIE w/ JTE diode FOM lags that of continuously-grown diode