> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

# PCB-on-DBC GaN Power Module Design with High-Density Integration and Double-Sided Cooling

Xingyue Tian, *Student Member, IEEE*, Niu Jia, *Student Member, IEEE*, Douglas DeVoto, *Senior Member, IEEE*, Paul Paret, *Senior Member, IEEE*, Hua Bai, *Senior Member, IEEE*, Leon M. Tolbert, *Fellow, IEEE*, Han Cui, *Senior Member, IEEE*

**Abstract**— Lateral gallium nitride (GaN) high-electron-mobility transistors (HEMTs) present better electrical characteristics compared to silicon or silicon carbide devices such as high switching speed and low gate charge, but also present additional challenges on the module design. This paper discusses a high-density GaN power module with double-sided cooling, low inductance, on-package decoupling capacitors, and integrated gate drivers. The GaN dies as well as the gate drive are sandwiched between the printed circuit board (PCB) and direct bonded copper (DBC) substrate to achieve compact loop and double-sided cooling effect. Design considerations and thermal performance are analyzed. A module assembly procedure is presented utilizing the layer-by-layer attachment process. Finally, a 2.7 cm × 1.8 cm half-bridge GaN power module is fabricated and tested, achieving a low power-loop inductance of 1.03 nH, and the overshoot voltage of the switching waveform is less than 5% under a 400-V/25-A double-pulse test. The thermal resistance is 0.32 K/W, verified by simulation and experimental results. The design and assembly process can be generalized and applied to high power applications to achieve high power density and high performance.

**Index Terms**—Double-sided cooling, Hybrid PCB and DBC technology, GaN, integrated gate driver, parasitic inductance, power module.

## I. INTRODUCTION

Gallium nitride (GaN) semiconductors are being applied in many power electronics applications, especially in high-frequency, volume-constrained applications such as wall adapters, data centers, electric vehicles, and aircraft [1]–[3]. Compared to silicon (Si) and silicon carbide (SiC) devices, GaN devices can switch at a higher speed with lower on-state resistance thanks to the high electron mobility and high breakdown field, which allow GaN devices to switch a given current with a smaller size and lower switching loss [4].

Due to the high cost and low growth rate of vertical GaN devices [5], most GaN devices available today are lateral HEMTs. The GaN layer can deposit on the Si substrate, and several buffer layers should be inserted between the GaN layer and other material layers when GaN is grown on Si. There are several concerns regarding the design of GaN power modules. First, the lateral enhancement-mode (E-mode) GaN HEMTs

have a minimal value of gate capacitance ( $C_{gs}$ ), which enables faster switching speed. However, the fast switching speed requires more attention to the circuit design, especially the parasitic elements [6], [7]. Its lower gate threshold voltage makes the device more likely to be mis-triggered [8]. Second, ringing and overshoot at the gate signal during switching transients is another challenge for GaN devices because the margin of lateral GaN gate voltage is highly stringent. Thus, the gate loop inductance should be minimized when driving the GaN HEMTs. Third, large parasitic inductance in the power loop will cause more severe voltage overshoot and switching losses across the lateral GaN HEMTs, which decreases the reliability and shortens the lifetime of GaN HEMTs [9]. Last but not least, the heat dissipation of lateral GaN dies should be well designed because of the narrow conductive path of the lateral structure and high current density, which leads to a smaller size under a given current compared to Si and SiC. Overall, designing a reliable GaN power module requires balancing electrical performance and thermal performance.

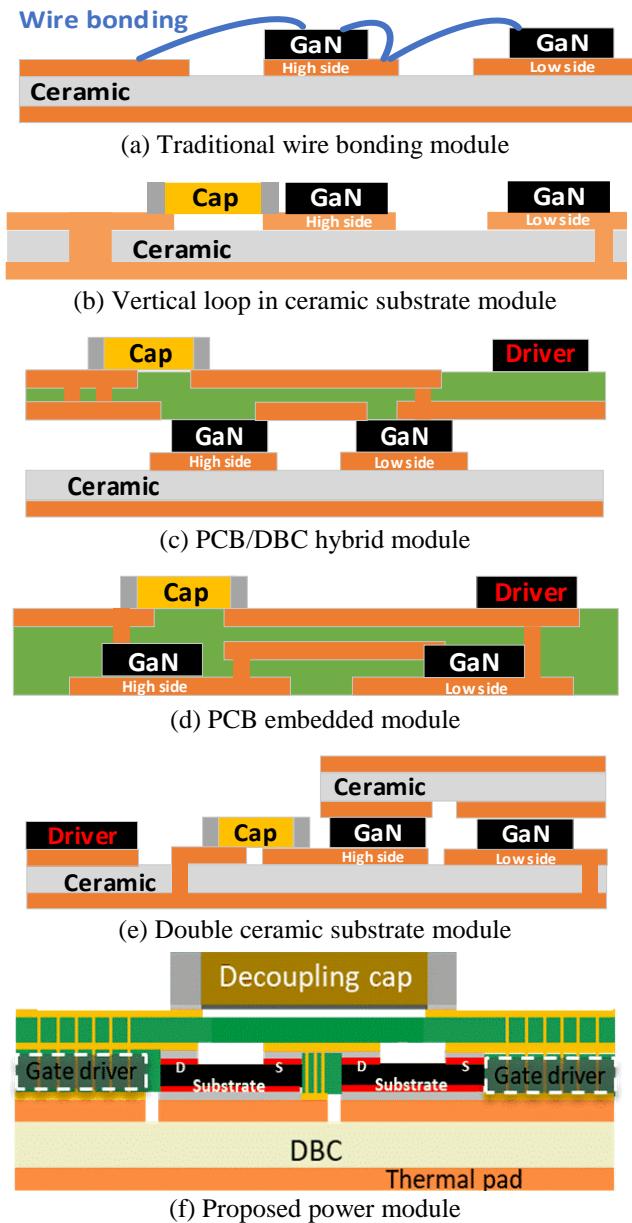

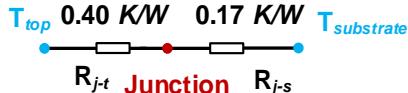

Several literatures have discussed improved structures of power modules to maximize GaN device performance. As shown in Fig. 1(a), traditional wire bonding solutions for GaN HEMTs integration [10]–[13] are reliable and cost-effective. However, the power loop inductance is large due to the lateral power loop through the introduction of bonding wires. Implementation of through-holes in the ceramic substrate can achieve a vertical power loop to minimize power loop inductance (Fig. 1(b) [6]) but at the expense of increased cost and limited layers for design flexibility. A hybrid concept has been followed in [7], [14]–[17], as shown in Fig. 1(c). These modules use insulated metal substrate or direct bonded copper (DBC) as substrate and a regular printed circuit board (PCB) placed on the top of the substrate to integrate the decoupling capacitors and gate drive circuits. The gate loop inductance and power loop inductance are at levels of several nanohenries. With the advancement of PCB manufacturing technology, GaN HEMTs can be embedded inside the PCB, and peripheral components are integrated on the PCB surface layer, as shown in Fig. 1(d) [18]–[20]. However, the thermal performance is not attractive compared to the hybrid solution [21]. A recent effort

This work was supported in part by the PowerAmerica Member Initiated Projects 3 and U.S. DOE (#2014-0654-85).

Xingyue Tian, Niu Jia, Hua Bai, Leon M. Tolbert, and Han Cui are with the Department of Electrical and Computer Engineering, University of Tennessee, Knoxville, TN 37996 USA (e-mail: xtian7@vols.utk.edu, njia@vols.utk.edu, hbai2@utk.edu, tolbert@utk.edu, and helencui@utk.edu).

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

Authorized licensed use limited to: NREL Library. Downloaded on September 26, 2023 at 05:44:48 UTC from IEEE Xplore. Restrictions apply.

© 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See <https://www.ieee.org/publications/rights/index.html> for more information.

Douglas DeVoto and Paul Paret are with the National Renewable Energy Laboratory, Golden, CO 80401 USA (e-mail: douglas.devoto@nrel.gov and paul.paret@nrel.gov).

Color versions of one or more of the figures in this article are available online at <http://ieeexplore.ieee.org>

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

**Fig. 1.** Advancement of GaN power module packaging.

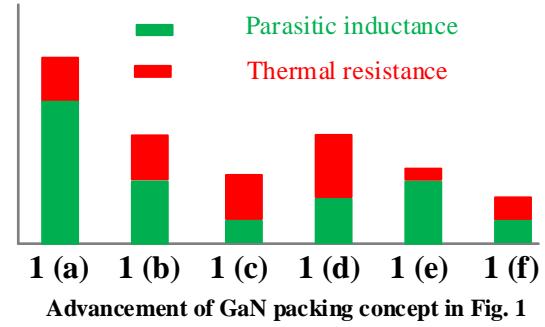

to improve the thermal performance of GaN hybrid power modules with integrated components is by implementing double-sided cooling (DSC). The GaN HEMTs and integrated components are sandwiched between two direct-plated copper, as shown in Fig. 1(e) [22]. However, the area of the top direct-plated copper is limited by the height mismatch between the GaN die and other components and there are limitations on the design flexibility using DBC for the power and gate loop layouts. The power module structure proposed herein employs the hybrid PCB-on-DBC structure, but with additional heat dissipation path that yields double-side cooling effect and lower thermal impedance compared to Fig. 1(c). To illustrate the design trade-off between electrical and thermal performance, Fig. 2 compares the proposed concept with the state-of-the-art packaging structures depicted in Fig. 1. Thanks to the multilayer design flexibilities in the PCB techniques, the design

**Fig. 2.** Comparison of parasitic inductance and thermal resistance for 600-V and 650-V GaN power modules shown in Fig. 1.

**Fig. 3.** Parasitic inductance and integration level of different 600-V and 650-V GaN power modules.

can be more compact and lower parasitic inductance is obtained compared to Fig. 1(e). Although the thermal resistance of the proposed module is not the lowest considering only one ceramic substrate is used, the overall performance is optimal, balancing modules the electrical and thermal performance. The comparison of these power modules' integration level regarding their power loop inductance and gate loop inductance is shown in Fig. 3. The closer to the lower left corner of Fig. 3, the lower the parasitic inductances (of both power and gate loop) and the higher the integration level of the power module.

The paper's primary contribution is the analysis, fabrication, and characterization of the hybrid PCB-on-DBC configuration that facilitates DSC and high-density integration with only one substrate for the GaN power module. The organization of the manuscript is as follows. The design considerations of the proposed module, optimization of parasitic parameters and thermal analysis are discussed in Section II in detail. The fabrication procedure to realize the PCB-on-DBC structure is described in Section III, and Section IV shows the electrical and thermal evaluations of the fabricated module. Conclusions are given in Section V. Such modules will find immediate applications in on-board chargers of electric vehicles and data centers with significantly increased power density and operating frequency.

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

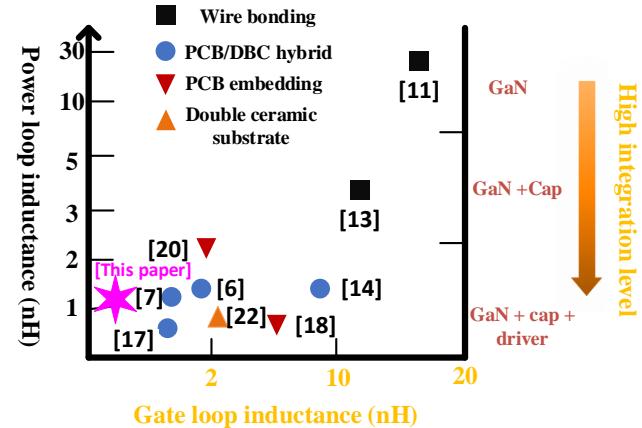

**Fig. 4.** Thermal model of lateral GaN HEMT (GS-065-060).  $R_{j-s}$  is the thermal resistance from junction to substrate.  $R_{j-t}$  is the thermal resistance from junction to top.

TABLE I

STATIC CHARACTERIZATION OF GAN DIE

| PARAMETERS   | 25°C    | 90°C    | CONDITION                         |

|--------------|---------|---------|-----------------------------------|

| $R_{DS(ON)}$ | 20.2 mΩ | 33.5 mΩ | $V_{GS} = 6$ V<br>$I_{DS} = 20$ A |

| $V_{GS(th)}$ | 1.2 V   | 1.5 V   | $V_{DS} = 10$ V                   |

| $C_{ISS}$    | 500 pF  | 502 pF  | $V_{DS} = 400$ V                  |

| $C_{OSS}$    | 123 pF  | 125 pF  | $V_{GS} = 0$ V                    |

| $C_{RSS}$    | 1.5 pF  | 1.9 pF  | $f = 100$ kHz                     |

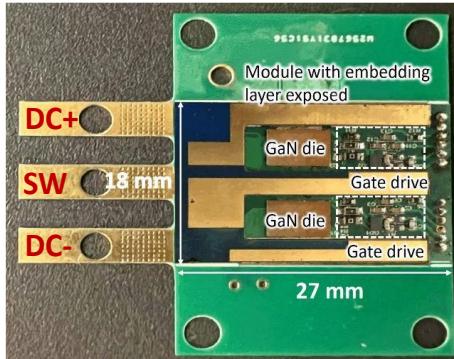

**Fig. 5.** Bottom view of the PCB showing gate drivers and GaN dies in the middle layer without DBC attached.

## II. DESIGN OF PROPOSED PCB-ON-DBC POWER MODULE

### A. Static Characterization of GaN HEMTs

Heat dissipation is a major challenge for GaN-based power modules because GaN HEMTs have smaller die areas than SiC at the same voltage and current level. Its two-dimensional (2D) electron gas layer is the conductive path where most of the heat is generated. While the substrate is the main path to dissipate the heat, a notable amount of the heat can still be dissipated through the top surface since the 2D electron gas is closer to the electrical pad. The thermal circuit of the selected GaN die (GS-065-060) is shown in Fig. 4. Considering the thermal model of the selected GaN die, adopting a DSC strategy can further improve the power module's thermal capability [23].

To gain an in-depth understanding of the performance of the selected GaN die, the curve tracer B1505A from Keysight was used to conduct a static characterization at different temperatures. Table I shows the impact of temperature on the on-state resistances ( $R_{DS(ON)}$ ), gate-source threshold voltages ( $V_{GS(th)}$ ), input capacitance ( $C_{ISS}$ ), output capacitance ( $C_{OSS}$ ), and reverse transfer capacitance ( $C_{RSS}$ ). The  $R_{DS(ON)}$  of the tested

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

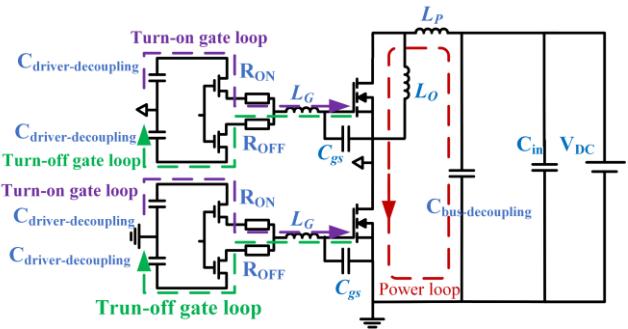

**Fig. 6.** Key parasitic inductances and components in half-bridge power module circuit

devices increases by more than 60% when the temperature is elevated from 25 °C to 90 °C. The  $V_{GS(th)}$  increases slightly while capacitances ( $C_{ISS}$ ,  $C_{OSS}$ ,  $C_{RSS}$ ) remain the same. Overall, the GaN die presents a temperature-sensitive resistance, low threshold gate voltage, and small capacitances compared to Si and SiC power devices. These characteristics enable fast-switching capability, but also add extra challenges on the gate loop design. Section II. D discusses the gate drive circuit design in detail to address these challenges.

### B. Proposed PCB-on-DBC Structure

Fig. 1(f) shows the cross-section view of the power module, which has a multilayer PCB on the top and DBC at the bottom. The hybrid structure adopts the benefit of both low-cost PCB and highly thermally conductive DBC substrate. Two GaN dies are placed in the middle layer sandwiched between the PCB on the top and the DBC on the bottom, as shown in Fig. 5. The substrate and source of GaN dies are connected by thermal vias filled with copper to assist the heat dissipation. Therefore, two paths are formed to dissipate the heat: one through the substrate, where the die is attached to the DBC directly; and the other from the top side of the die through the PCB thermal vias to the DBC. The DBC substrate is leveraged for both sides' heat dissipation so that DSC is achieved. The decoupling capacitors and gate drivers are integrated into the multilayer PCB to reduce the parasitic inductance in both the power loop and the gate loop. An electromagnetic interference filter is also integrated with the module on the top of the PCB to improve the noise attenuation, which is elaborated in [24] and thus omitted herein. In the end, the highly integrated power module has a size of 2.7 cm × 1.8 cm targeting applications of <10 kW.

### C. Power Loop Design and Optimization

The parasitic power loop inductance in a half-bridge power module induces the voltage overshoot and affects the switching loss [26], [27]. The influence of the power loop inductance becomes more severe for extremely fast-switching GaN devices. Fig. 6 shows the key parasitic parameters in the proposed half-bridge power module, including power loop inductance  $L_P$  and gate loop inductance  $L_G$ . The circuit components also include two GaN dies, bus decoupling capacitors, gate driver and drive decoupling capacitors. A 650-V/30-A double-pulse test (DPT) simulation is established shown in Fig. 6, in which an inductor is used as the output inductor to short the upper die and the lower die is the device

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

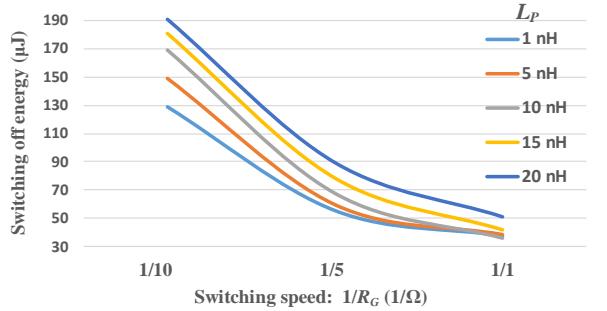

(a)

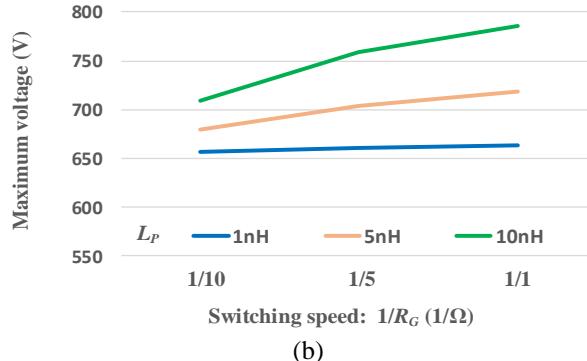

(b)

**Fig. 7.** Power loop inductance's impact on the (a) switching-off energy and (b) voltage overshoot.

under test. To illustrate this issue, GS66508T from GaN Systems is selected [28] and results are presented in Fig. 7. The switching speed represented by  $1/R_G$  is changed by the gate resistor  $R_G$  within the range of 1–10 Ω. Higher switching speed (i.e., smaller  $R_G$ ) reduces the switching transient period and results in significantly lower switching loss (see Fig. 7(a)), but increases the drain current slope  $di/dt$  and results in higher voltage overshoot (see Fig. 7(b)). The voltage overshoot occurring on top of the steady-state voltage  $V_{dc}$  in the switching transient is related to the  $di/dt$  and power loop inductance  $L_p$  by

$$V = L_p \frac{di}{dt} + V_{dc} \quad (1)$$

Large voltage overshoot poses high voltage stress (e.g., 800 V) across the device that goes beyond the maximum transient voltage (i.e., 750 V) of the GaN device, which will cause device failure and reduced lifetime. Therefore, the power loop inductance needs to be minimized to get both low voltage overshoot and low switching loss. In the example shown in Fig. 7(b), the power loop inductance needs to be less than 5 nH with 5-Ω gate resistance to keep the voltage below the 750-V limit.

To minimize the power loop parasitic inductance, a vertical power loop layout is desired, as lateral loop design still results in relatively large inductance [10]–[13]. The conceptual design of the proposed PCB-on-DBC power module is based on the concept of a vertical power loop. The parasitic inductance is reduced significantly due to the self-cancellation of magnetic flux. The GaN dies are placed into the cavity layer inside the multilayer PCB to minimize the vertical distance without sacrificing the design flexibility. The integration of decoupling

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

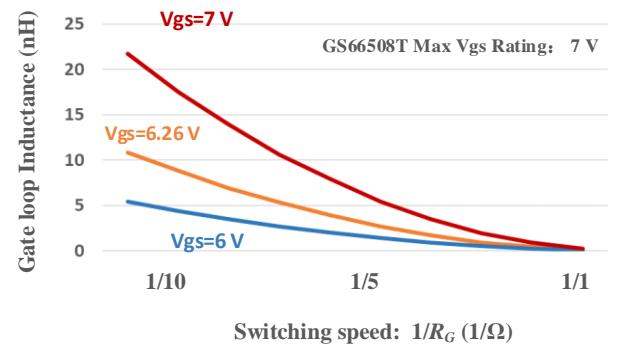

**Fig. 8.** Parasitic gate loop inductance's impact on the gate voltage overshoot.

capacitors on the top also helps to decouple the busbar inductance and leads to extremely low power loop inductance. The perpendicular distance, or the board thickness, is selected as 0.4 mm due to the PCB manufacturing limits. The PCB layout of the geometry shown in Fig. 5 is imported to ANSYS Q3D for parasitic inductance extraction, where the power loop inductance yields 1.27 nH.

#### D. Gate Loop Design and Optimization

The gate loop parasitic inductance is also important for GaN module designs. Lateral E-mode GaN HEMTs have a small gate capacitance ( $C_{gs}$ ) and low threshold voltage, which make the device more likely to be mis-triggered. Moreover, its gate-voltage range is highly stringent (e.g., -10 V to 7 V), so the maximum tolerable voltage at gate for the selected GaN chip is only 1 V if using 6 V to turn on.

The gate loop parameters include the gate resistance  $R_G$ , the gate loop inductance  $L_G$ , and the gate-source capacitance of the device  $C_{gs}$  as shown in Fig. 6. Most practical gate designs adopt the Kelvin connection to avoid the common-source inductance-associated issues in the gate loop [29], [30]. Therefore, the common-source inductance  $L_{CS}$  is not considered in the circuit model. The dynamic response of the turn-on path is a form of a second-order system. The expressions for relative overshoot voltage ( $\sigma\%$ ) and damping ratio ( $\xi$ ) are as follows:

$$\sigma\% = e^{\frac{-\pi\xi}{\sqrt{1-\xi^2}}} \quad (2)$$

$$\xi = \frac{R_G}{2} \sqrt{\frac{C_{iss}}{L_G}} \quad (3)$$

From the equations above, either increasing the gate resistance or reducing the loop inductance  $L_G$  will decrease the gate voltage overshoot. However, large gate resistance will decrease the switching speed and increase the switching loss (Fig. 7(a)). Thus, small gate loop inductance is preferred to minimize the voltage overshoot without reducing the switching speed. Under a given maximum voltage limit at the gate, the maximum gate loop inductance allowed can be calculated by (2) and (3). Fig. 8 shows the relationship between gate loop inductance and gate resistance under different overshoot voltages when using 6 V to turn on. The  $C_{iss}$  value for the device

represents the authors' peer-reviewed, accepted manuscript.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

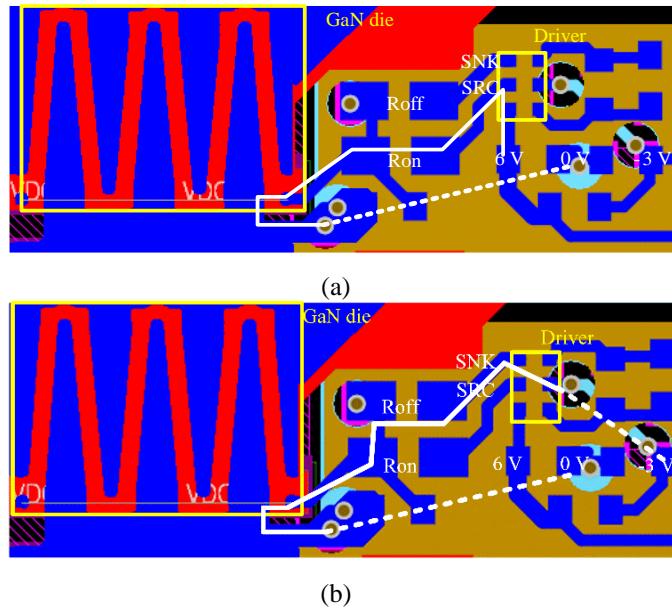

**Fig. 9.** PCB layout showing (a) turn-on gate loop and (b) turn-off gate loop.

selected is 242 pF [28]. Smaller gate loop inductance allows the use of smaller gate resistance (with high speed and low loss) without exceeding the maximum gate voltage of the selected GaN device.

Therefore, a compact GaN power module integrated with gate drivers is necessary. In the proposed power module, the gate drivers are integrated close to the GaN dies to reduce the gate loop area as shown in Fig. 9. In addition, a gate driver with small footprints (1EDN7550U) is selected to further reduce the gate loop area. The simulated turn-on and turn-off gate loop inductance of the upper die are 0.32 nH and 0.29 nH, respectively; and those of the lower die are 0.30 nH and 0.34 nH, respectively. According to (3) with a damping ratio of 0.5, the minimum gate resistance allowed at the pull-up path of the gate driver is found to be 1.6 Ω. In the end, a 5.1-Ω gate resistance is adopted in the turn-on loop for the margin of safety, while the internal gate resistance of the 1EDN7550U is 0.85 Ω.

During the turn-off transient, the turn-off gate resistance selection is based on the Miller effect. The high  $dv/dt$  is generated by the turn-on of the complementary switch, which creates a current through the Miller capacitance and then tries to sink in the gate driver. The current flowing through the turn-off gate resistor generates a gate-source voltage. If this voltage is higher than the threshold voltage, it may lead to a false turn-on. The calculation of the maximum turn-off gate resistance is calculated as [31] in (4).

$$R_{OFF} \leq \frac{V_{thG}}{C_{gd} \times \frac{dv}{dt}} = \frac{1.7 \text{ V}}{1.8 \text{ pF} \times 200 \frac{\text{V}}{\text{ns}}} = 4.7 \text{ ohm} \quad (4)$$

To increase the switching speed, the external turn-off resistance is chosen as zero, while the internal gate resistance is 0.35 Ω. This choice considers both the impact of the parasitics issue and the Miller effect.

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

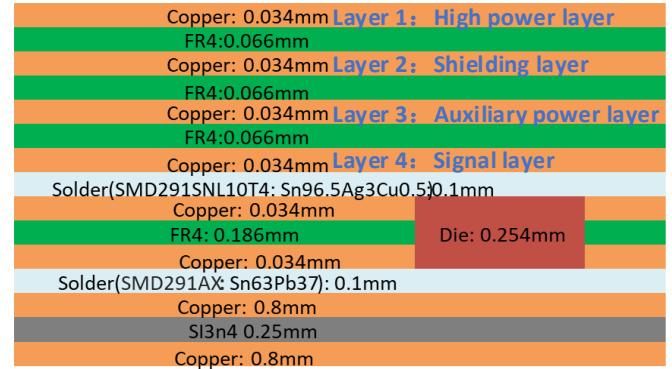

**Fig. 10.** Layer stack of proposed power module.

TABLE II

COUPLING CAPACITANCES BETWEEN POWER NODE ( $V_{DC}$ ) AND HIGH-SIDE SIGNALS

|                         | V <sub>DC+</sub> TO PULSE-WIDTH MODULATION | V <sub>DC+</sub> TO AUXILIARY POWER (-3 V) | V <sub>DC+</sub> TO AUXILIARY POWER (6 V) |

|-------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------|

| With shielding layer    | 0.00 pF                                    | 0.01 pF                                    | 0.00 pF                                   |

| Without shielding layer | 4.68 pF                                    | 7.5 pF                                     | 1.7 pF                                    |

#### E. Cross-Coupling Capacitance Minimization

Overlapping conductor layers induce coupling capacitances that provide noise traveling paths harmful to the switching condition. Take the half-bridge circuit as an example; an extremely high  $dv/dt$  is generated at the switch node since the voltage swings between the bus voltage ( $V_{DC+}$ ) and the ground ( $V_{DC-}$ ). The coupling capacitance between the power nodes (e.g.,  $V_{DC+}$  and switch node) and the signal nodes (e.g., gate drive) could cause coupling noises that lead to falsely triggered switches. Therefore, it is critical to decouple the power layers and the signal layers by using shielding layers (see Fig. 10) for high-frequency GaN module designs. Take the high-side GaN HEMT as an example; all signals are referenced to the high-side ground by the shielding layer with the same potential as the high-side ground, so that the coupling capacitances between the  $V_{DC+}$  and the signal traces are minimized. The coupling capacitance on the high side with the shielding layer is simulated in Ansys Q3D and compared to those without the shielding layer, as listed in Table II. It shows a significant reduction in coupling capacitance with the shielding.

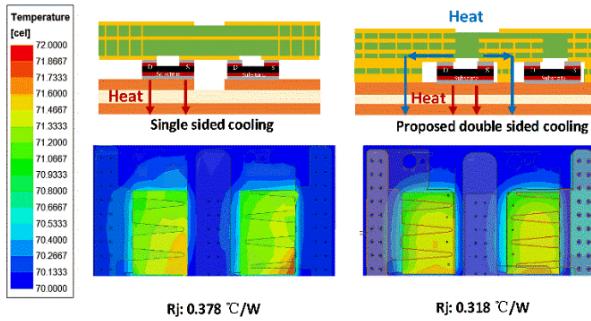

#### F. Thermal Performance Evaluation

Fig. 11 shows the traditional single-sided cooling hybrid GaN power module. The heat is dissipated through the DBC only. As discussed in the previous section, 70% of the heat of the GaN die is dissipated through the bottom, and 30% of heat is dissipated through the top. The equivalent DSC is applied to the proposed power module, and the steady-state thermal performance is compared to a counterpart with single-sided cooling using the same GaN die, outline dimensions, and thermal boundary. The power loss of each GaN die is set as 5 W, and the temperature at the module exterior is kept constant

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

**Fig. 11.** Thermal simulation setup and results of single-sided cooling and double-sided cooling.

TABLE III

COMPONENTS IN POWER MODULE PROTOTYPE

| COMPONENT          | VALUE       | PART                 |

|--------------------|-------------|----------------------|

| GAN DIE            | 650 V/ 60 A | GS-065-060           |

| DRIVER             |             | 1EDN7550U            |

| TURN-ON RESISTOR   | 5 $\Omega$  | RCS06035R10FKEA      |

| TURN-OFF RESISTOR  | 0 $\Omega$  | HCJ0603ZT0R00        |

| DRIVER             | 1 $\mu$ F   | CGB2A1X5R1E105K033BC |

| DECOUPLING CAP     |             |                      |

| BUS DECOUPLING CAP | 0.3 $\mu$ F | C4532X7T2J304M250KA  |

at 70 °C. All the layer stack information used in the Ansys Icemark simulation are shown in Fig. 10. The thermal vias diameter is 0.2 mm based on the capabilities offered by the PCB manufacturer. According to the simulation results shown in Fig. 11, the proposed equivalent DSC further reduces the junction-to-case thermal resistance to 0.318 K/W due to the additional path dissipating heat from the top side of the die. Given that the geometry of these two configurations is identical, except for the absence of the cavity board, we can obtain from parallel relationship that the estimated value of the top thermal resistance is approximately 2.008 K/W. Employing larger thermal vias will further reduce the thermal resistance.

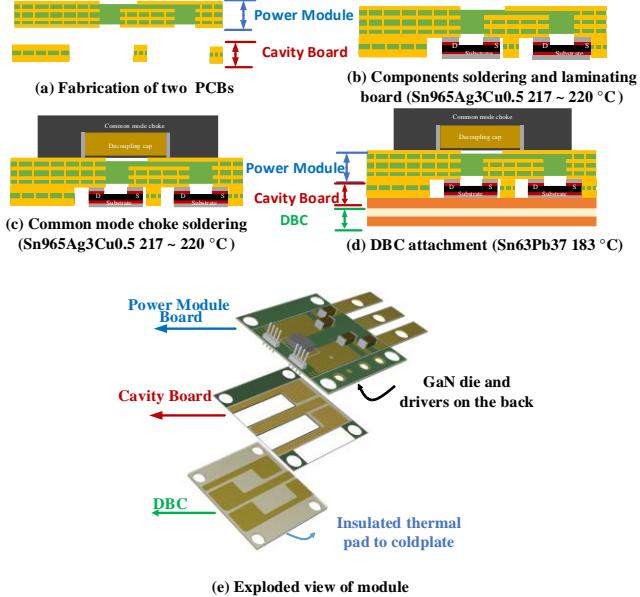

### III. POWER MODULE FABRICATION

The components used to fabricate the power module are listed in Table III. The GaN die used in the module has a size of 6.0 mm × 4.0 mm × 0.27 mm. For the PCB-on-DBC power module, the gate driver selection is critical since the size and thickness should be comparable to those of the GaN dies. In this design, 1EDN7550U [32] is chosen due to the small PG-TSNT-6 package with a size of 1.5 mm × 1.1 mm × 0.375 mm. The 0.1-mm difference in the thickness between the gate driver and GaN die can be evened by screen printing the soldering layer. The decoupling capacitance should be higher than 100 times of the  $C_{oss}$  of the selected die [33] and is chosen as 1  $\mu$ F to reduce the influence of inductance on the power loop. To realize the hybrid PCB and DBC structure, a layer-by-layer lamination process is adopted as shown in Fig. 12. The detailed process is described as follows:

1) The power module board and cavity board are fabricated. The power module PCB have 1-oz copper, and the

**Fig. 12.** Fabrication process of the proposed GaN power module.

thickness is 0.4 mm to ensure a low power loop inductance. The cavity PCB is selected to have a thickness of 0.254 mm to be aligned with the GaN die thickness. It has through-hole plated vias filled with copper to achieve better thermal performance.

2) A 100- $\mu$ m-thick stencil board is used to screen print the solder paste Sn96.5Ag3.0Cu0.5 with a melting temperature of 217°C on the bottom layer of the power module PCB. The Sn96.5Ag3.0Cu0.5 is recommended by the GaN die manufacturer because of its good fluidity, which ensures an even solder layer to avoid voids. After the GaN dies, gate drivers and the cavity PCB are placed on the power module PCB, and the power module PCB is reflowed in the T-962A reflow oven under a suitable temperature profile [34] with the top layer facing down.

3) The bus decoupling capacitors and the common mode choke are hand-soldered onto the top layer of the power module with the Sn96.5Ag3.0Cu0.5 solder wire.

4) A second reflow profile is used to attach the DBC substrate to the power module board with the cavity board. This step requires careful handling to prevent the solder in the previous step from melting. The ceramic material of DBC in the proposed power module is AlN with high thermal conductivity compared to other ceramic materials, and the thickness of copper metallization on both sides is 0.2 mm. The Sn63Pb37 solder paste is selected in this step with a melting temperature of 183 °C, which is lower than that of the solder used in Step 2. First, the solder paste is applied to all the pads on the DBC, and the DBC is attached to the power module with the cavity PCB. Second, the whole power module with the DBC layer facing down is heated by a hot plate, and a thermocouple is used to closely monitor the temperature until it reaches 185°–195°C. The ramp rate is kept below 0.3°C/second to avoid damaging.

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

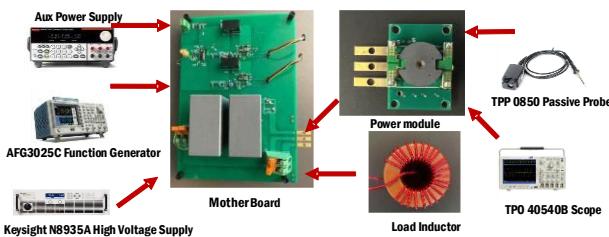

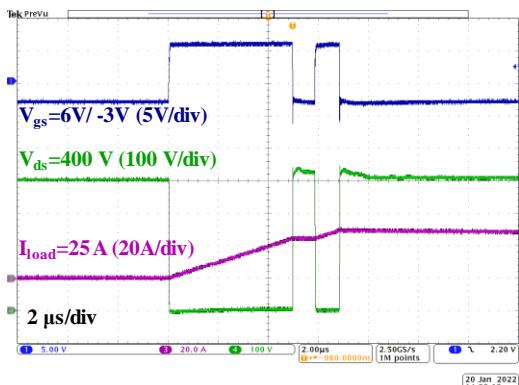

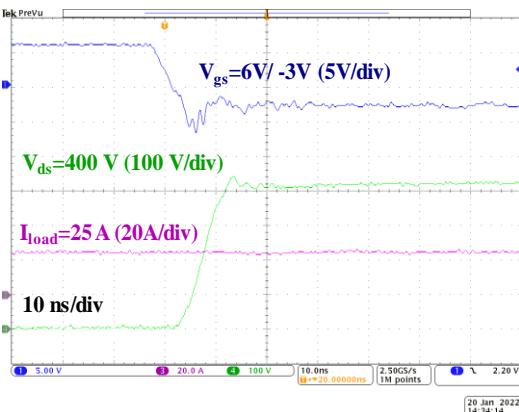

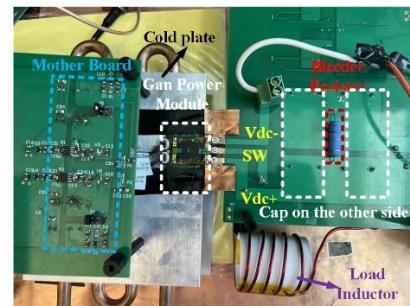

Fig. 13. Double-pulse test prototype setup.

Fig. 14. Switching waveforms obtained from the double-pulse test under 400 V and 25 A.

Fig. 15. Zoom-in view of switching waveforms at the turn-off transient showing low overshoot and fast  $dv/dt$ .

#### IV. POWER MODULE CHARACTERIZATION

This section focuses on the electrical and thermal characterizations of the power module. The electromagnetic interference performance of the power module with integrated common mode choke is discussed in [24]-[25] and omitted herein.

##### A. Electrical Characterization of the Proposed Power Module

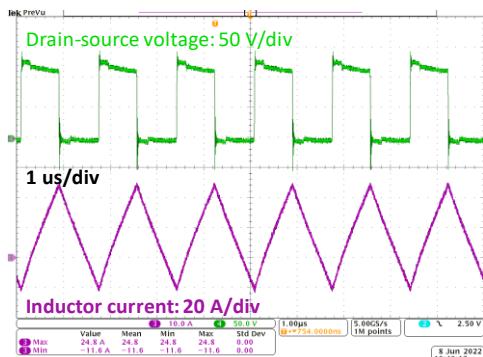

A double-pulse test circuit was built as shown in Fig. 13 to characterize the power module's electrical performance. A static -3 V was applied at the gate of the top GaN die, and the bottom die was the device under test. The power module was tested at 400-V DC-bus voltage and 25-A load current at room temperature (25 °C), and the characterization results of the hard-switching transition for the proposed power module are

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

Fig. 16. Experiment setup of 500-W/600-kHz buck converter using the proposed power module.

shown in Fig. 14. A 1,000-V passive probe (TPP0850) was used to capture the drain-to-source voltage. The bandwidth is up to 800 MHz, and the input capacitance is 1.8 pF to minimize the probe's loading effect on the circuit. The bandwidth of the probe should be high enough to capture the rise/fall time, as well as the high-frequency oscillation of the fast-switching transient of the GaN device.

The turn-off transient is shown in Fig. 15. The overshoot voltage across the die is less than 5% of the static voltage at 25 A, and no appreciable undershoot is observed in the gate loop, even with 0-ohm external gate resistor. Moreover, the loop inductance extracted from the ringing frequency yields 1.03 nH using the following equation:

$$L_{loop} = \frac{T^2}{4\pi^2(C_{oss} + C_{para} + C_{probe})} = \frac{2.3\text{ ns}^2}{4\pi^2(127 + 1.5 + 1.8)\text{ pF}} = 1.03\text{ nH} \quad (5)$$

where  $C_{oss}$  is the output capacitance of GaN die,  $C_{para}$  is the parasitic capacitance induced by the PCB layout, and  $C_{probe}$  is the capacitance induced by the passive probe. As shown in Fig. 3, both the power loop inductance and gate loop inductance are among the lowest of comparable designs. Moreover, the module has low thermal impedance thanks to DSC, and the fabrication does not involve any exotic process.

##### B. Continuous Switching Test of the Power Module

Based on the proposed hybrid power module with the DSC design, a buck converter is built for the power module with the integrated gate drivers to demonstrate the continuous switching performance. Fig. 16 shows the experimental setup, and the heat dissipation method is liquid cooling. The proposed power module is placed on the cold plate with a thin layer of thermal interface material in between. The input voltage is set to 120 V with a duty cycle of 0.5. The output power of the converter is kept at 500 W when the switching frequency is 600 kHz with zero-voltage switching to minimize switching loss and avoid any shoot-through. As shown in Fig. 17, the drain-source voltage is very clean, which indicates the proposed GaN power module works very well at 600 kHz. The module is actually designed to be capable of handling higher power and frequency. However, a higher power level was not tested due to the selected gate driver's operation limits [32]. Our future work involves modifying the module such that gate drivers for

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

**Fig. 17.** Buck converter experiment waveforms of the proposed power module with 500-W output power and 600-kHz switching frequency.

higher-power operation can be accommodated into the sandwiched structure, which will be reported in subsequent publications.

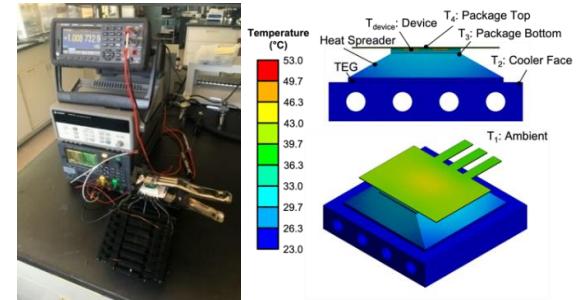

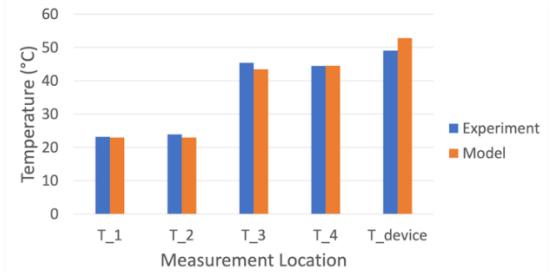

### C. Thermal Characterization of the Proposed Power Module

For thermal characterization of the GaN power module, the devices were first shorted and connected to a power supply. The heat generated within the devices by reverse conduction was controlled by the power supply's output voltage and current settings and was ramped from 1 W to 12 W. A thermoelectric generator was placed in the thermal path to confirm dominate pathway of GaN heat loss flow. Four thermocouples were also placed at key locations of interest to measure ambient, heat sink, bottom of the package, and top of the package temperatures. These thermocouple measurements were compared to a revised thermal model that replaced the liquid cold plate with a heat sink. Fig. 18 shows the experimental thermal setup and corresponding thermal model. The thermal model results and experimental measurements exhibited similar temperatures through the package, as shown in Fig. 19. More accurate measurements of all interface layers (solders and grease) would further improve the model correlation.

## V. CONCLUSION

A compact PCB-on-DBC GaN half-bridge power module with DSC, low inductance, low thermal resistance, and integrated gate drivers has been proposed. Hybrid PCB and DBC technology is explored with multiple layer attachment as a cost-effective solution to achieve DSC and enhanced design flexibility. The experimental results validate the module performance under 400-V/25-A double-pulse test with 1.03-nH power loop inductance and less than 5% overshoot voltage. In the continuous switching test, a 500-W buck converter is built based on the presented GaN module with an operating frequency of 600 kHz. Furthermore, the proposed module is verified with thermal characterization results that show low junction-to-case thermal resistance of 0.32 K/W. In the future, the module will be tested under higher frequency and power level with updated gate driver integration and substrate selection for improved module reliability.

**Fig. 18.** Experiment thermal setup of the GaN power module, power supply, thermoelectric generator, and heat sink with corresponding thermal model.

**Fig. 19.** Experimental thermocouple measurements compared to the thermal model with 10 W of module heat loss.

## ACKNOWLEDGMENTS

The authors would like to thank PowerAmerica Member Initiated Projects 3 and U.S. DOE (#2014-0654-85) for funding and supporting this work, as well as GaN Systems for providing the GaN die. This work was authored in part by the National Renewable Energy Laboratory (NREL), operated by Alliance for Sustainable Energy, LLC, for the U.S. Department of Energy (DOE) under Contract No. DE-AC36-08GO28308. Support for the work at NREL was provided by the University of Tennessee, Knoxville under TSA-20-17265. The views expressed in the article do not necessarily represent the views of the DOE or the U.S. Government. The U.S. Government retains and the publisher, by accepting the article for publication, acknowledges that the U.S. Government retains a nonexclusive, paid-up, irrevocable, worldwide license to publish or reproduce the published form of this work, or allow others to do so, for U.S. Government purposes. A portion of the research was performed using computational resources sponsored by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy and located at the National Renewable Energy Laboratory.

## REFERENCES

- [1] A. Letellier, M. R. Dubois, J. P. Trovao, and H. Maher, "Gallium nitride semiconductors in power electronics for electric vehicles: Advantages and challenges," in *Proc. IEEE Veh. Power Propulsion Conf.*, 2015, pp. 1–6.

- [2] T. P. Chow, "Wide bandgap semiconductor power devices for energy efficient systems," in *Proc. IEEE Workshop Wide Bandgap Power Devices Appl.*, Nov. 2015, pp. 402–405.

- [3] A. Q. Huang, "Power semiconductor devices for smart grid and renewable energy systems," *Proc. IEEE*, vol. 105, no. 11, pp. 2019–2047, Nov. 2017.

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

[4] E. A. Jones, F. F. Wang, and D. Costinett, "Review of commercial GaN power devices and GaN-based converter design challenges," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 707–719, Sep. 2016.

[5] S. Pimputkar, "Ammonothermal growth of gallium nitride," Ph.D. dissertation, Univ. California, Santa Barbara, Santa Barbara, CA, USA, 2012.

[6] F. Luo, Z. Chen, L. Xue, P. Mattavelli, D. Boroyevich, and B. Hughes, "Design considerations for GaN HEMT multichip halfbridge module for high-frequency power converters," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2014, pp. 537–544.

[7] A. I. Emon et al., "Design and optimization of gate driver integrated multichip 3D GaN power module," *IEEE Trans. Transport. Electricif.*, pp. 4391–4407, Dec. 2022.

[8] O. C. Spro, S. Basu, I. Abuishmais, O.-M. Midtgard, and T. Undeland, "Driving of a GaN enhancement mode HEMT transistor with zener diode protection for high efficiency and low EMI," in *Proc. 19th Eur. Conf. Power Electron. Appl.*, Sep. 2017, pp. 1–10.

[9] Z. Yuan et al., "Design and evaluation of laminated busbar for three-level T-type NPC power electronics building block with enhanced dynamic current sharing," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 395–406, Mar. 2020.

[10] W. Zhang et al., "A new package of high-voltage cascode gallium nitride device for megahertz operation," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1344–1353, Feb. 2016.

[11] J. A. Brothers and T. Beechner, "GaN module design recommendations based on the analysis of a commercial 3-phase GaN module," in *Proc. IEEE Energy Convers. Congr. Expo.*, Sep. 2019, pp. 4109–4116.

[12] B. Passmore et al., "A 650 V/150 A enhancement mode GaN-based halfbridge power module for high frequency power conversion systems," in *Proc. IEEE Energy Convers. Congr. Expo.*, Montreal, QC, Canada, 2015, pp. 4520–4524.

[13] L. Kou and J. Lu, "Applying GaN HEMTs in conventional housing-type power modules," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2020, pp. 4006–4011.

[14] L. Lu, D. Chen, and L. Yushyna, "A high power-density and high efficiency insulated metal substrate based GaN HEMT power module," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2017, pp. 3654–3658.

[15] A. B. Jørgensen, S. Bęczkowski, C. Uhrenfeldt, N. H. Petersen, S. Jørgensen, and S. Munk-Nielsen, "A fast-switching integrated full-bridge power module based on GaN eHEMT devices," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2494–2504, 2019.

[16] Y. Yan, L. Zhu, J. Walden, Z. Liang, H. Bai, and M. H. Kao, "Packaging a top-cooled 650 V/150 A GaN power modules with insulated thermal pads and gate-drive circuit," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Jun. 2021, pp. 2345–2350.

[17] A. I. Emon et al., "A 650V/60A gate driver integrated wire-bondless multichip GaN module," in *Proc. IEEE 12th Int. Symp. Power Electron. Distrib. Gener. Syst.*, 2021, pp. 5366–5371.

[18] Z. Qi, Y. Pei, L. Wang, Q. Yang, and K. Wang, "A highly integrated PCB embedded GaN full-bridge module with ultralow parasitic inductance," *IEEE Trans. Power Electron.*, vol. 37, no. 4, pp. 4161–4173, Apr. 2022.

[19] S. Savulak, B. Guo, and S. Krishnamurthy, "Three-phase inverter employing PCB embedded GaN FETs," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2018, pp. 1256–1260.

[20] S. Moench et al., "PCB-Embedded GaN-on-Si half-bridge and driver ICs with on-package gate and DC-link capacitors," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 83–86, Jan. 2021.

[21] S. Lu, T. Zhao, Z. Zhang, K. D. T. Ngo, R. Burgos and G. -Q. Lu, "Low parasitic-inductance packaging of a 650 V/150 A half-bridge module using Enhancement-Mode Gallium-Nitride high electron mobility transistors," *IEEE Trans. Ind. Electron.*, vol. 70, no. 1, pp. 344–351, Jan. 2023.

[22] B. Li, X. Yang, K. Wang, H. Zhu, L. Wang, and W. Chen, "A compact double-sided cooling 650V/30A GaN power module with low parasitic parameters," *IEEE Trans. Power Electron.*, vol. 37, no. 1, pp. 426–439, Jan. 2022.

[23] M. Liu, A. Coppola, M. Alvi, and M. Anwar, "Comprehensive review and state of development of double-sided cooled package technology for automotive power modules," *IEEE Open J. Power Electron.*, vol. 3, no. 2644–1314, pp. 271–289, May 5, 2022.

[24] N. Jia, X. Tian, L. Xue, H. Bai, L. M. Tolbert and H. Cui, "In-package common-mode filter for GaN power module with improved radiated EMI performance," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2022, pp. 974–979.

[25] N. Jia, X. Tian, L. Xue, H. Bai, L. M. Tolbert and H. Cui, "Integrated Common-Mode Filter for GaN Power Module With Improved High-Frequency EMI Performance," *IEEE Trans. Power Electron.*, vol. 38, no. 6, pp. 6897–6901, June 2023, doi: 10.1109/TPEL.2023.3248092.

[26] Z. Chen, D. Boroyevich, and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," in *Proc. Int. Power Electron. Conf.*, 2010, pp. 164–169.

[27] Z. Zhang, J. Fu, Y.-F. Liu, and P. C. Sen, "Switching loss analysis considering parasitic loop inductance with current source drivers for buck converters," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1815–1819, Jul. 2011.

[28] "GS66508T datasheet." GaN System. [Online]. Available: <https://gansystems.com/wp-content/uploads/2018/04/GS66508T-DS-Rev-180424.pdf>

[29] Z. Chen, "Electrical Integration of SiC Power Devices for High-Power Density Applications", PhD dissertation, Virginia Tech, Blacksburg, VA, USA, 2013.

[30] J. Lu, H. Bai, A. Brown, M. McAmmond, D. Chen, and J. Styles, 917 "Design consideration of gate driver circuits and PCB parasitic para918 meters of paralleled e-mode GaN HEMTs in zero-voltage-switching 919 applications," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 920 Mar. 2016, pp. 529–535.

[31] "Design and application guide for high speed MOSFET Gate Drive Circuits." [Online]. Available: <http://www.radiosensors.se/download/gate-driver2.pdf>

[32] "Eicedriver 1ednx550 datasheet." Infineon, Inc. [Online] Available: [https://www.infineon.com/dgdl/Infineon-1EDN7550U-DataSheetv02\\_02-EN.pdf?fileId=5546d462700c0ae60170522057e14b61](https://www.infineon.com/dgdl/Infineon-1EDN7550U-DataSheetv02_02-EN.pdf?fileId=5546d462700c0ae60170522057e14b61).

[33] Z. Chen, D. Boroyevich, P. Mattavelli, and K. Ngo, "A frequency-domain study on the effect of DC-link decoupling capacitors," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2013, pp. 1886–1893.

[34] "SMD291SNL10T4 datasheet." ChipQuick, Inc. [Online]. Available: <http://www.chipquik.com/datasheets/SMD291SNL10T4.pdf>.

[35] A. Yeo, C. Lee, and J. H. L. Pang, "Flip chip solder joint reliability analysis using viscoplastic and elastic-plastic-creep constitutive models," *IEEE Trans. Compon. Packag. Technol.*, vol. 29, no. 2, pp. 355–363, Jun. 2006.

[36] P. P. Paret, D. J. DeVoto, and S. Narumanchi, "Reliability of emerging bonded interface materials for large-area attachments," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 6, no. 1, pp. 40–49, Jan. 2016.

**Xingyue Tian** (Graduate Student Member, IEEE) received the B.E. degree in electrical engineering from Sichuan University, Chengdu, China in 2018, and the M.S. degree in electrical engineering from The Ohio State University, Columbus, United States in 2020. He is currently pursuing her Ph.D. degree in the Center for Ultra-Wide-Area Resilient Electric Energy Transmission Networks (CURENT) at The University of Tennessee, Knoxville, United States. His research interests include GaN device integration and power module packaging, and current sensor.

**Niu Jia** (Graduate Student Member, IEEE) received the B.E. degree in electrical engineering from Hefei University of Technology, Hefei, China in 2018, and the M.S. degree in electrical engineering from The Ohio State University, Columbus, United States in 2020. She is currently pursuing her Ph.D. degree in the Center for

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript. The published version of the article is available from the relevant publisher.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Ultra-Wide-Area Resilient Electric Energy Transmission Networks (CURENT) at The University of Tennessee, Knoxville, United States. Her research interests include WBG power module packaging, EMI, and magnetics.

**Douglas DeVoto** joined the National Renewable Energy Laboratory in 2010. He leads reliability evaluation and prognostics research for automotive power electronics with a focus on bonded interfaces, electrical interconnects, and high-temperature packaging, within the Advanced Power Electronics and Electric Machines (APEEM) Group. He is experienced with accelerated testing, thermal and thermomechanical FEA modeling, and developing strategies to improve the reliability of innovative power electronics for electric-drive vehicles and other applications. Douglas has a B.S. in mechanical engineering from the University of Delaware and a M.S. in mechanical engineering from the University of Maryland. He is an ASME member and an IEEE Senior Member.

**Paul Paret** is a researcher in the Center for Integrated Mobility Sciences at the National Renewable Energy Laboratory. In this role, Paul leads the computational modeling efforts to simulate the thermal and thermomechanical behavior and develop lifetime prediction models of various bonded materials in power electronics packages used in electric-drive vehicles and aviation systems. He conducts design optimization studies to identify the optimal component layers and geometry within power electronics package topologies to improve their power density, efficiency, and reliability. Additionally, he performs reliability evaluation experiments to identify the fundamental failure mechanisms of materials under harsh operating conditions. Paul has published several articles including journals, conference papers, technical reports, and a book chapter on the thermomechanical performance and lifetime prediction models of power electronics materials. Paul has a master's degree in Aerospace Engineering Sciences from the University of Colorado, Boulder and a bachelor's degree in Mechanical Engineering from College of Engineering, Trivandrum, India. He is an ASME member and an IEEE Senior Member.

**Hua "Kevin" Bai** received BS and PHD degree from Department of Electrical Engineering of Tsinghua University in 2002 and 2007, respectively. In 2010 he joined Kettering University (former General Motor Institute) as an assistant professor and is presently an associate professor in EECS, The University of Tennessee, Knoxville since 2018. His research interests include power electronics with motor drives, EV battery chargers, DC/DC converters and battery management systems. He is the author of 2 books, >140 IEEE papers and hold 11 industrial patents. He is meanwhile associate editor of SAE International

Pursuant to the DOE Public Access Plan, this document represents the authors' peer-reviewed, accepted manuscript.

The published version of the article is available from the relevant publisher.

Journal of Electrified Vehicles, and associate editor of IEEE Transactions on Transportation Electrification.

**Leon M. Tolbert** (Fellow, IEEE) received the Bachelor's, M.S., and Ph.D. degrees in electrical engineering from the Georgia Institute of Technology, Atlanta, in 1989, 1991, and 1999, respectively.

He is currently a Chancellor's Professor and the Min H. Kao Professor in the

Department of Electrical Engineering and Computer Science, The University of Tennessee. He is a founding member and testbed thrust leader for the NSF/DOE Engineering Research Center, CURENT. He is also an adjunct participant with Oak Ridge National Laboratory, where he previously worked from 1991 to 2020. His research interests include the utility applications of power electronics, microgrids, electric vehicles, and wide bandgap semiconductors.

Dr. Tolbert was the recipient of the 2001 IEEE Industry Applications Society Outstanding Young Member Award, and ten prize paper awards from the IEEE Industry Applications Society and IEEE Power Electronics Society. He was an Associate Editor of the IEEE Power Electronics Letters and IEEE Transactions on Power Electronics from 2003 to 2013 and the Paper Review Chair for the Industry Power Converter Committee of the IEEE Industry Applications Society from 2014 to 2017. He is currently the Academic Deputy Editor-in-Chief of the IEEE Power Electronics Magazine (2021-2023) and the Publications Chair for the IEEE Industry Applications Society.

**Han (Helen) Cui** (S'12-M'17-SM'22) received the B.S. degree in electrical engineering from Tianjin University, Tianjin, China, in 2011, and the M.S. and Ph.D. degrees from Virginia Tech, Blacksburg, in 2013 and 2017, respectively, both in electrical engineering. Upon graduation, she

joined the Electrical and Computer Engineering Department at University of California, Los Angeles as a post-doctoral researcher to expand the knowledge of magnetics modeling for high-frequency applications. She is currently an Assistant Professor at the University of Tennessee, Knoxville. Her research interests include design and optimization of magnetics with high energy density and low loss for both power electronics and microwave applications, simulations and circuit modeling of inductors and transformers, magnetic devices, and microscopic material properties.