# Integrating Si/SiGe quantum devices with on-chip classical circuitry

Michael Wolfe<sup>1</sup>, Tom McJunkin<sup>1\*</sup> Dan Ward<sup>2†</sup>, DeAnna Campbell<sup>2</sup>, Lisa Tracy<sup>2</sup>, and M. A. Eriksson<sup>1</sup>

<sup>1</sup>Department of Physics, University of Wisconsin-Madison, WI 53706

<sup>2</sup>Sandia National Laboratories, Albuquerque, NM 87185, USA

\*Present address: John Hopkins University Applied Physics Laboratory, Laurel, Maryland 20723

†Present address: HRL Laboratories, LLC, 3011 Malibu Canyon Road, Malibu CA 90265, USA

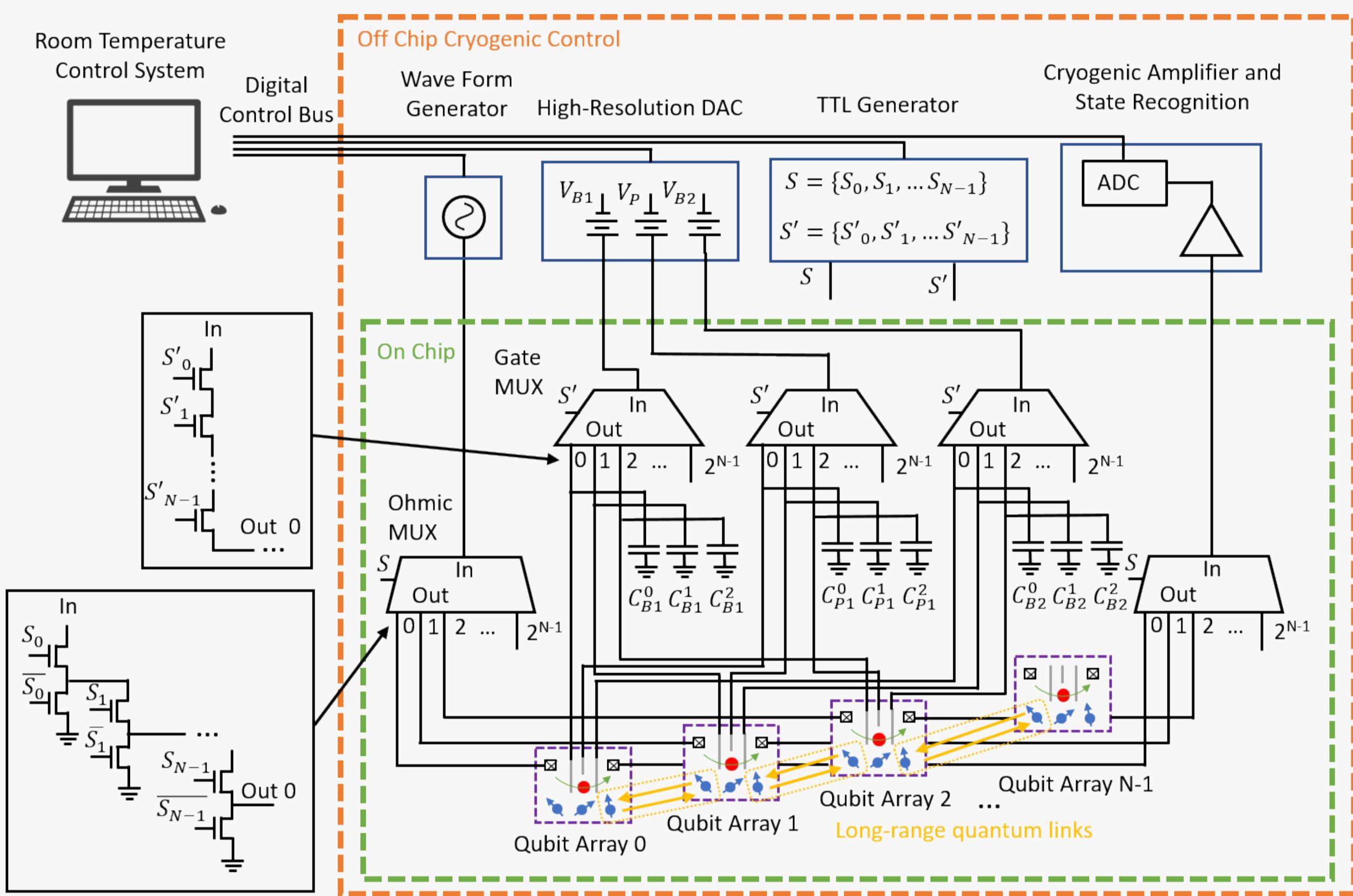

## Scalable readout for silicon qubits

The rapid acceleration of quantum computing technologies is poised to reach an interconnect bottleneck, where the qubit count in a quantum processor is limited by the number of input/output (I/O) connections. Quantum processors in silicon provide natural integration of on-chip control logic in the host semiconductor. This work demonstrates multiplexing on-chip which takes advantage of the fabrication compatibility between silicon quantum devices and classical transistor technology.

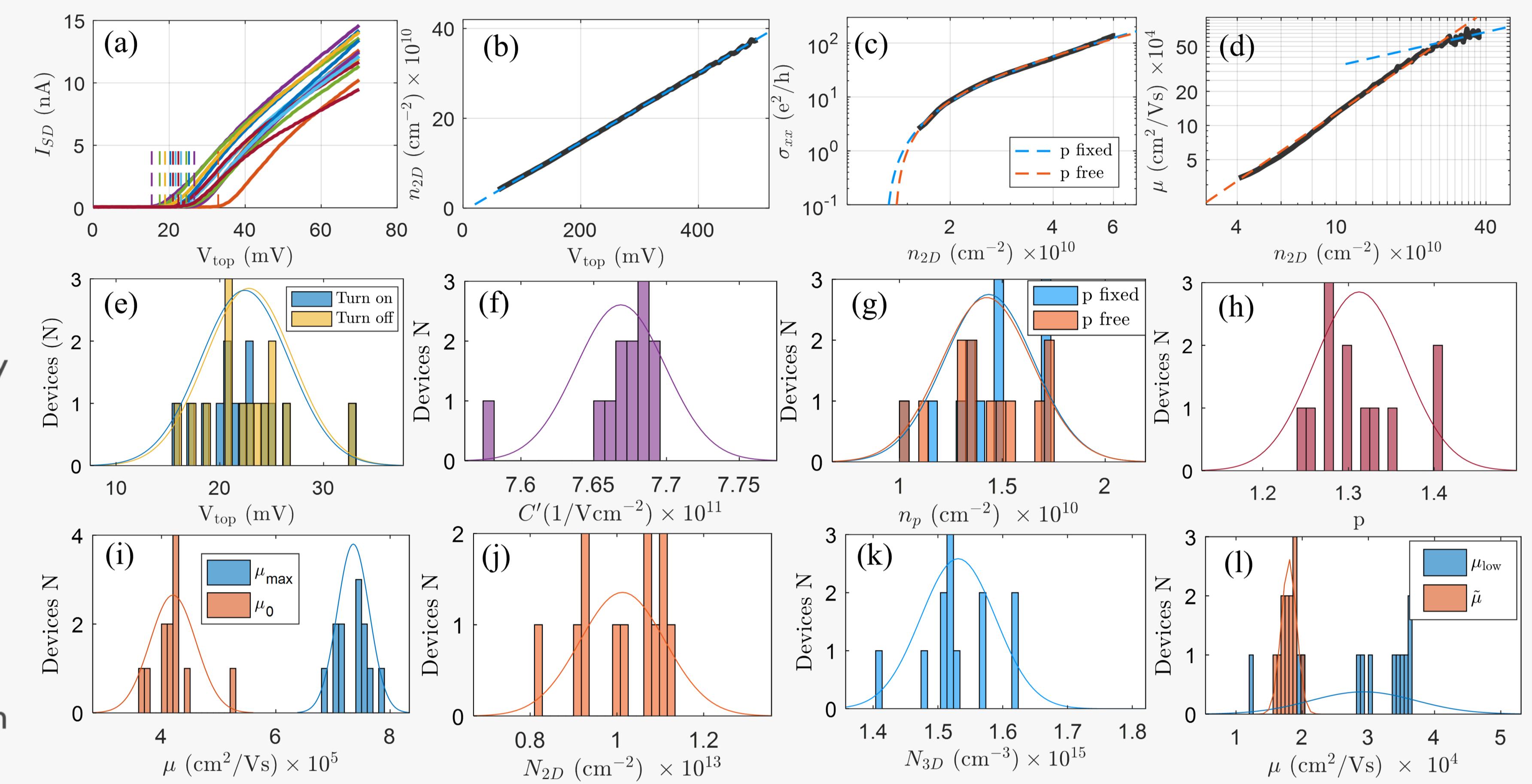

## Operation of multiplexers to assess Hall bar device uniformity

(a) Turn-on curves overlaid for each Hall bar. (b) Hall bar capacitance, (c) percolation density, (d) mobility for the  $S_0 = 0000$  device. Statistical histograms for (e) threshold voltage, (f) Hall bar capacitance, (g) percolation density, (h) percolation density exponent, (i), mobility fixed at  $n_{2D} = 2 \times 10^{11} \text{ cm}^{-2}$  and max mobility, (j) defect density for remote impurities, (k) defect density in the background quantum well, (l) lowest measurement mobility and mobility extracted from turn-on curve.

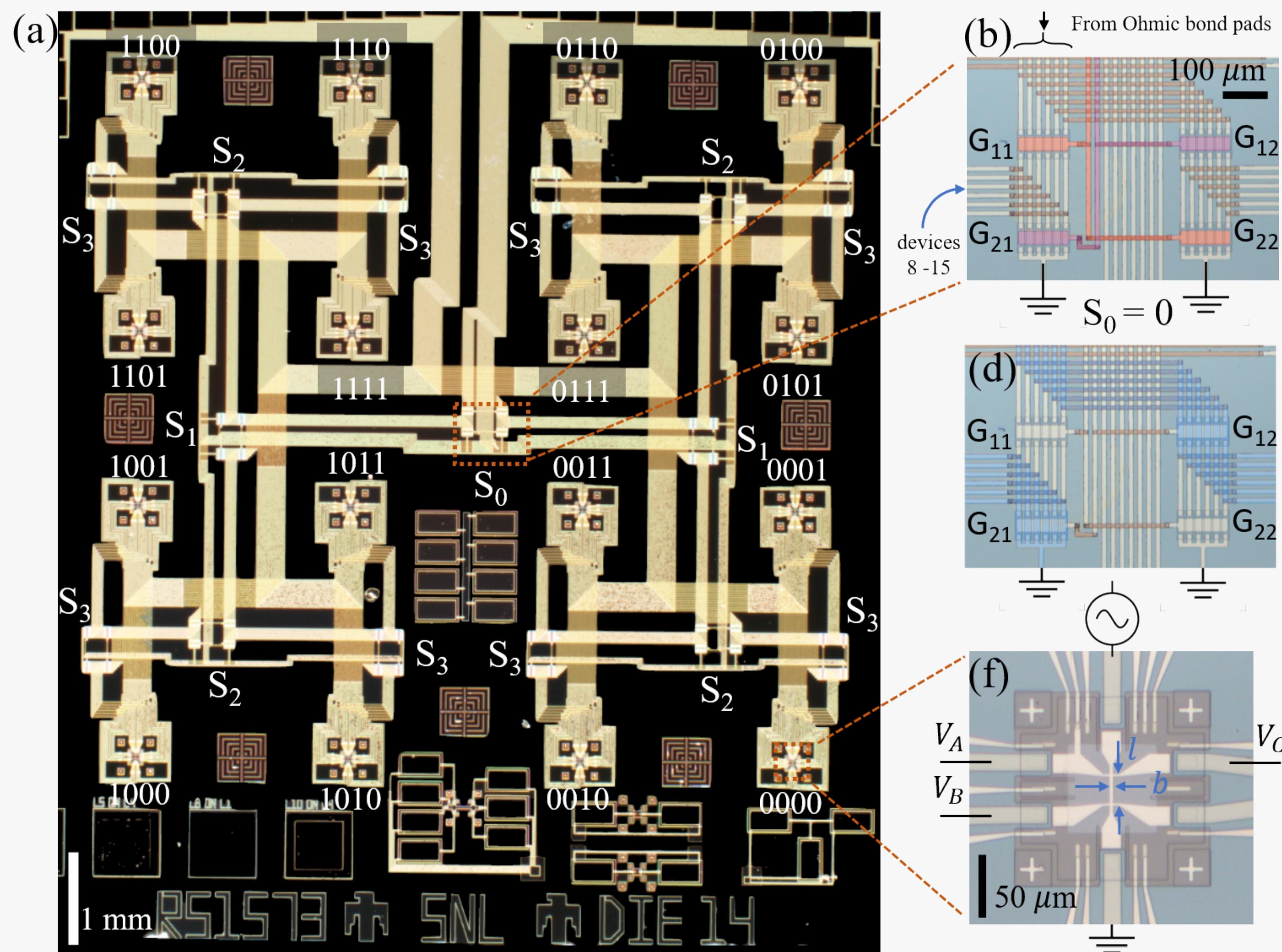

## Fabrication and Integration of Si/SiGe on-chip multiplexers

(a) Sixteen quantum device construction zones are multiplexed across a single 11.5 cm  $\times$  11.5 cm chip. (b)-(c) Each switch is composed of four FETs for signal routing of ohmic contacts. (d) Operation of switch in  $S_0 = 0$  state and (e)  $S_0 = 1$  state. (f) Example of quantum Hall device fabricated with electron-beam lithography. Sixteen non-multiplexed Hall bars require 112 electrical connections. This chip requires a total of 16 wire bonds. (g) Si/SiGe heterostructure stack of the mesa for each device in the construction zone.

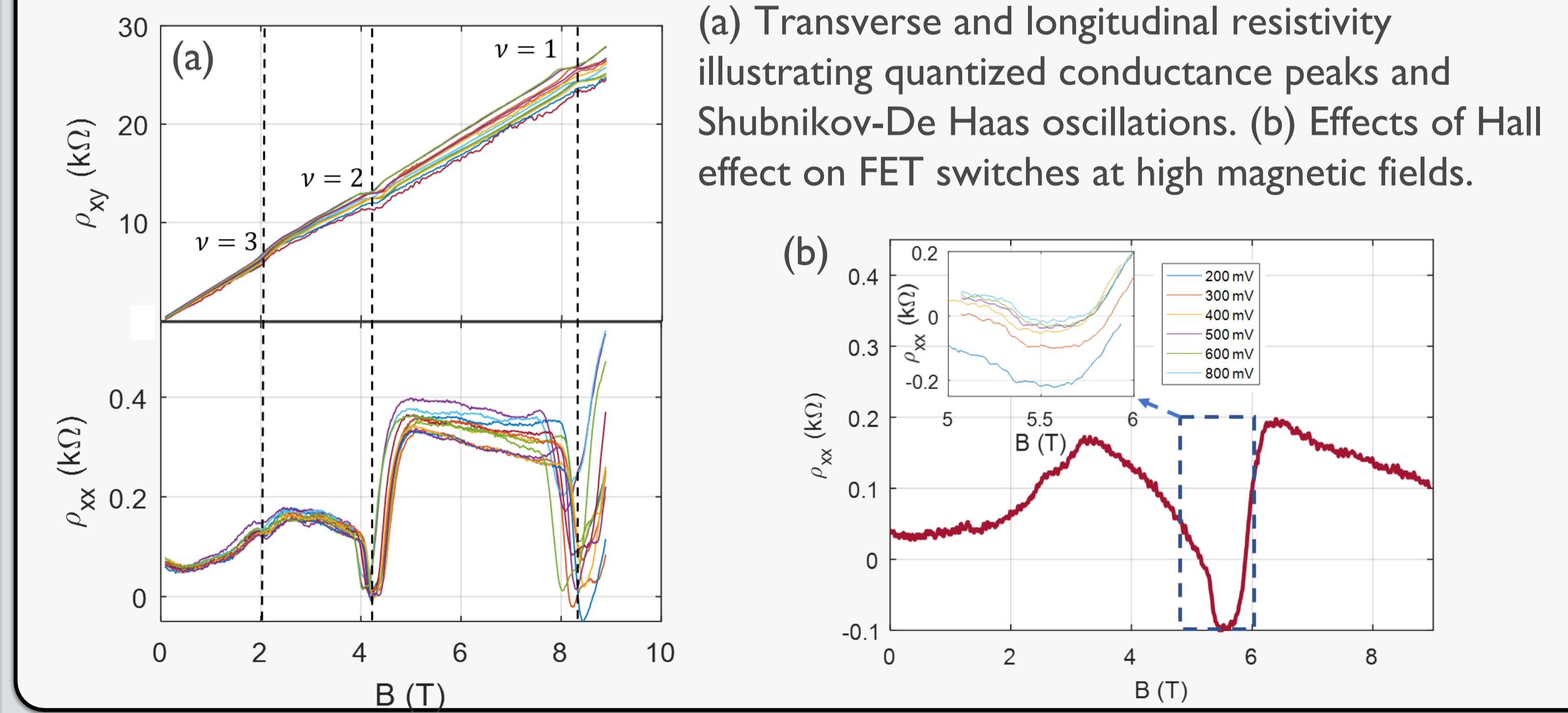

## Operation in large magnetic fields

## Acknowledgements

We acknowledge Lisa Edge of HRL Laboratories, LLC, for providing the heterostructure material used in this work. Research was sponsored in part by the Army Research Office (ARO) under Grant Number W911NF-17-1-0274. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Army Research Office (ARO), or the U.S. Government. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation herein. Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.