*Exceptional service in the national interest*

**Veeco D-125 MOCVD system**

## Selective Area Regrowth of p-type GaN and AlGaN for Power Diodes

**Andrew Allerman, M.H. Crawford, A.T. Binder, A.M. Armstrong, G.W. Pickrell, V.M. Abate, J. Steinfeldt and R.J. Kaplar**

*Sandia National Laboratories, Albuquerque, NM*

This research was supported by the US Department of Energy (DOE) Vehicle Technologies Office (VTO) under the Electric Drive Train Consortium. Supported by the Laboratory Directed Research and Development program at Sandia National Laboratories, a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC., a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA-0003525.

# Outline

- **Selective area p-type doping for diodes and transistors**

- **PN junction formation by P-GaN regrowth on etched n-GaN**

- Ex-situ processing to remove residual etch damage

- In-situ XeF<sub>2</sub> to remove residual etch damage

- **PN junction formation by regrowth in Al<sub>0.3</sub>Ga<sub>0.7</sub>N diodes**

- Planar, non-selective area PN junctions

- PN junctions with selective area p-type Al<sub>0.3</sub>Ga<sub>0.7</sub>N doping

- **Summary**

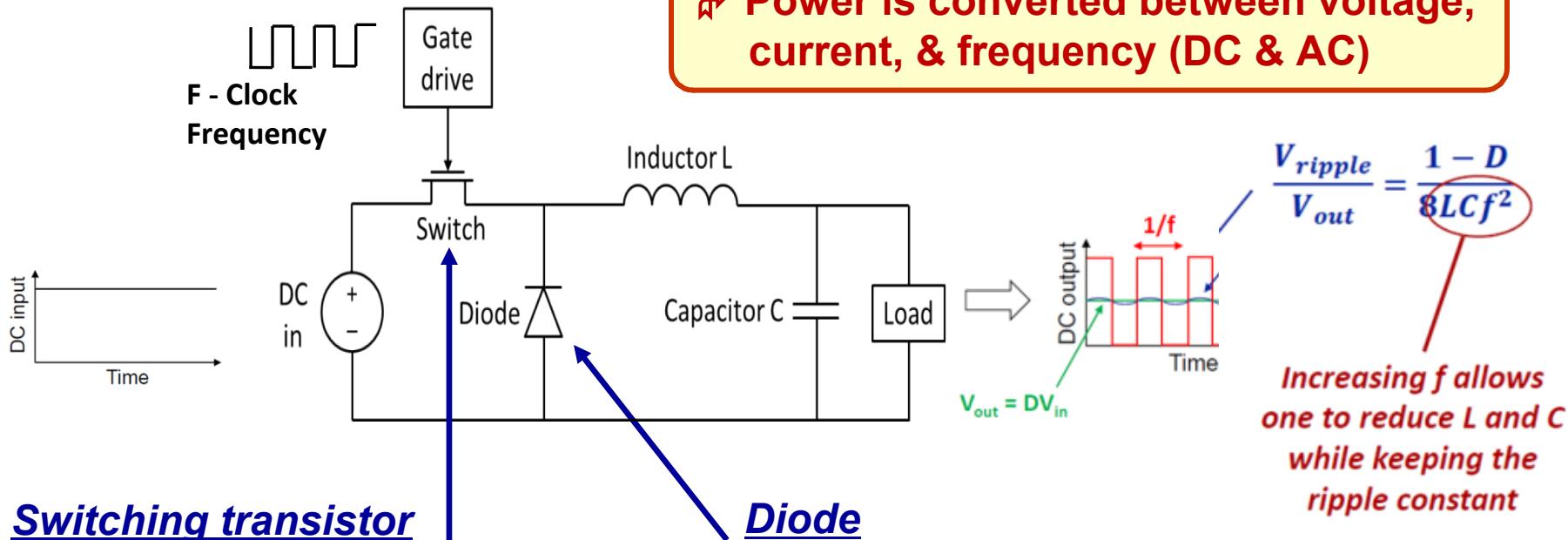

## Example: (Step down )DC to DC Buck converter

### Switching transistor

- Vertical current flow for high-current & voltage

- Voltage dropped across thick drift layer

- D-MISFET, JFET, MOSFET ..etc..

### Diode

- Vertical current flow

- SBD, PIN, and MPS diodes

Power management is based on diodes and transistors

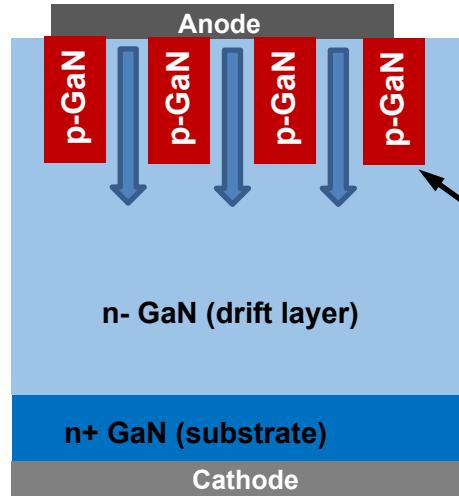

# Practical high-voltage diodes and transistor require selective area p-type doping

## Merged PIN Schottky (MPS) diode

## Double-well Metal-Insulator-Semiconductor Field-Effect-Transistor (D-MISFET)

- Reverse-bias PN junction key to multi-kilovolt blocking voltage ( $V_{br}$ )

- ☞ Must have low reverse leakage current

- P-layers formed by ion implantation and annealing for Si and SiC device

- ☞ p-implant into GaN is challenging but advancing

☞ Form the p-well by ICP etch epitaxial regrowth of p-GaN

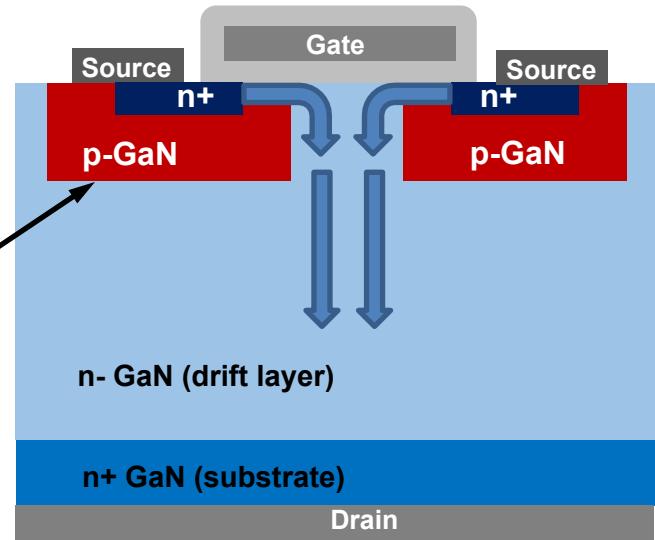

## Sources of current leakage at regrown PN interface

- Electrically active impurities (Si, O, etc.)

- Damage to crystal structure from ICP etch resulting in extended (?) and point defects (e.g. vacancies).

- Incorporation rates of impurities and growth rates depend on crystal plane

- Use maskless approach to regrowth — avoid growth and mask removal problems

↗ **Start simple, p-GaN regrowth on c-plane drift layers**

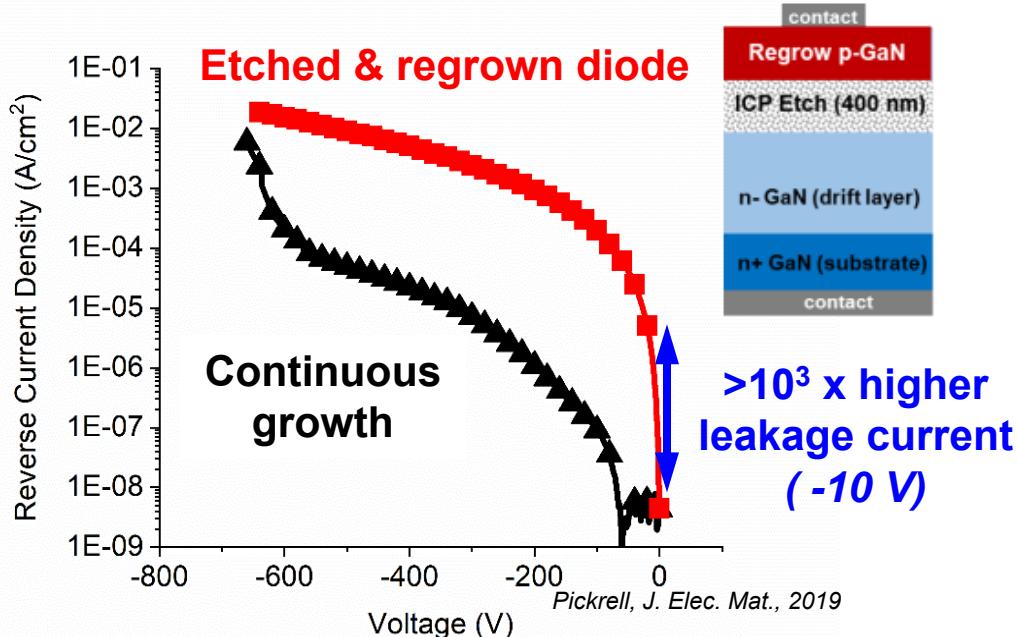

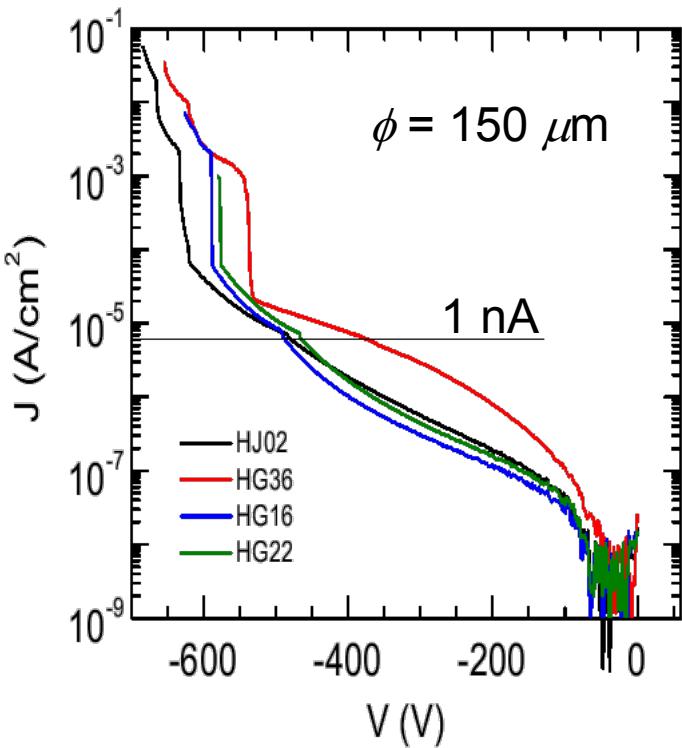

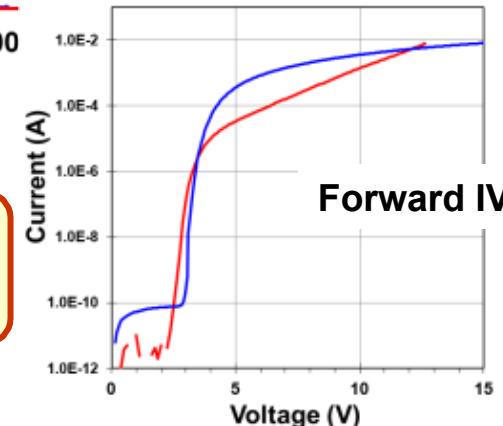

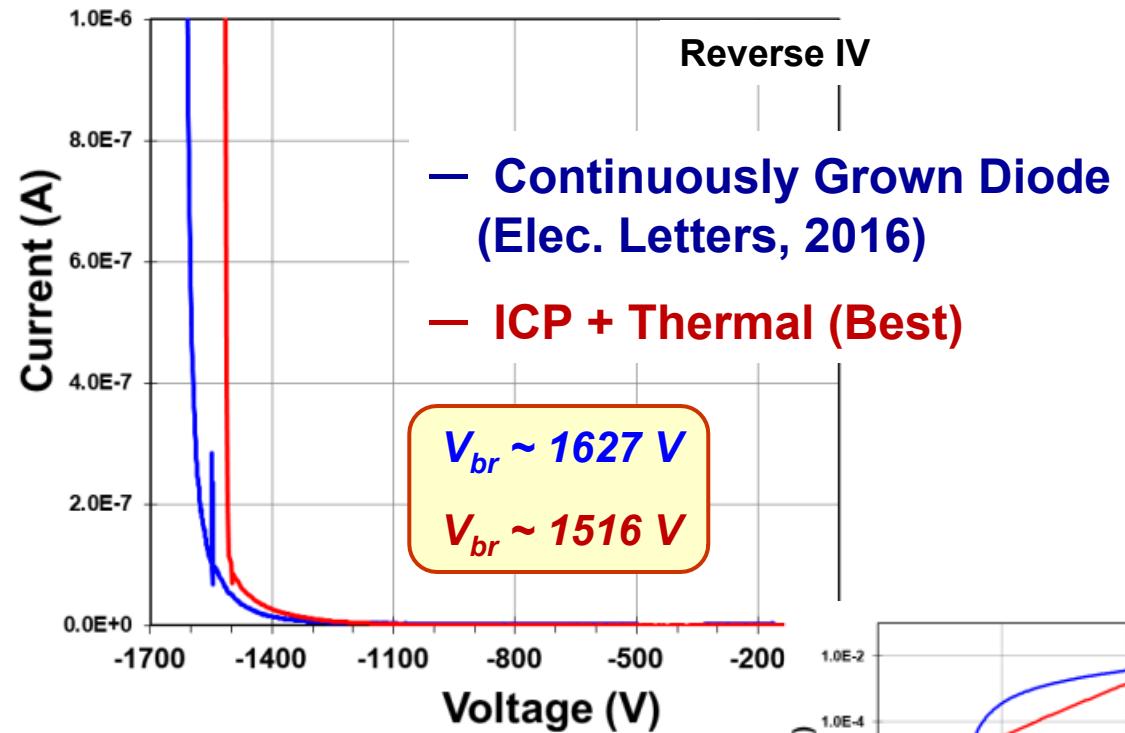

# Current-voltage characteristics of continuously grown and etched/regrown diode

## Reverse IV Characteristics of GaN PN diodes

- Quality of PN junction revealed within first 10-20V in reverse bias

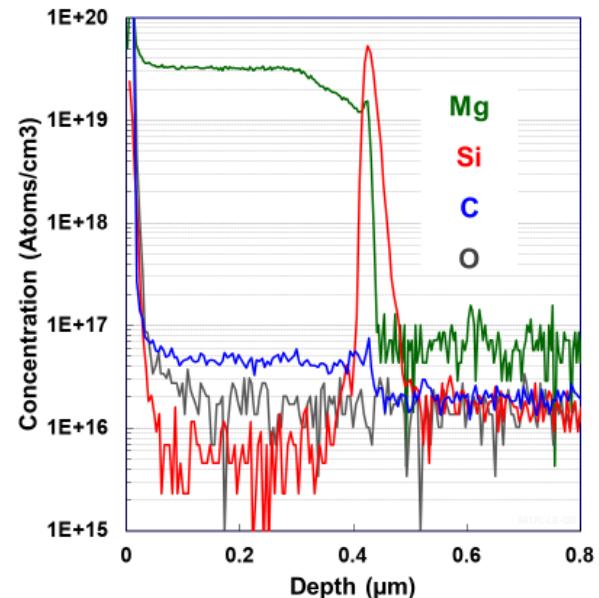

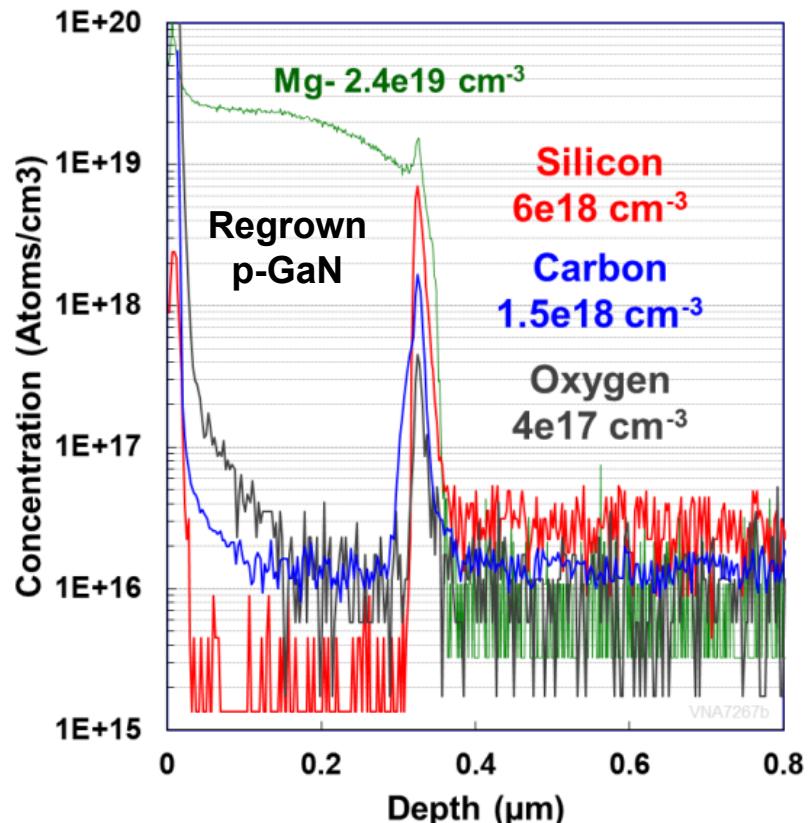

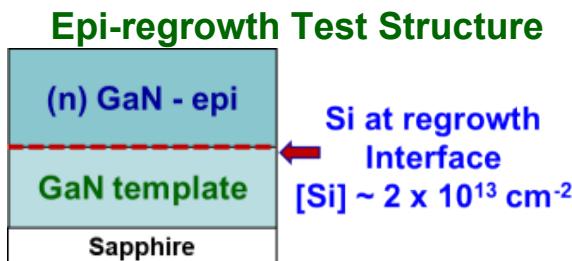

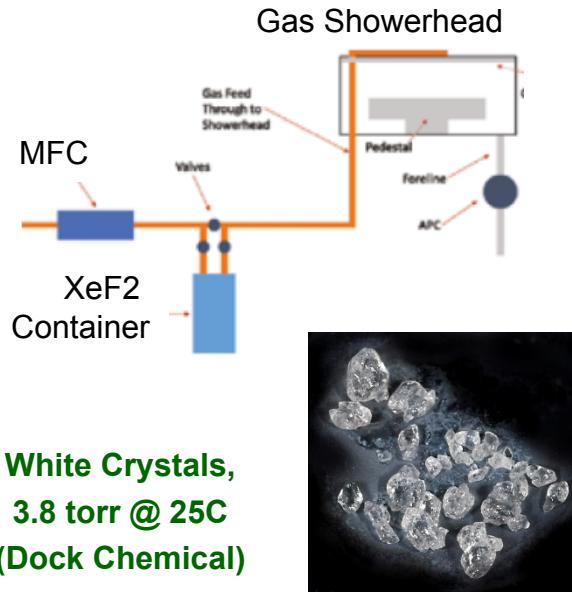

## SIMS: Regrowth of p-GaN on ICP etched n-drift layer

- Si spike found on surfaces exposed to air

### Differences between continuous diodes and etch and regrown diodes

- High reverse leakage near 0 V

- High Si concentration at regrowth interface

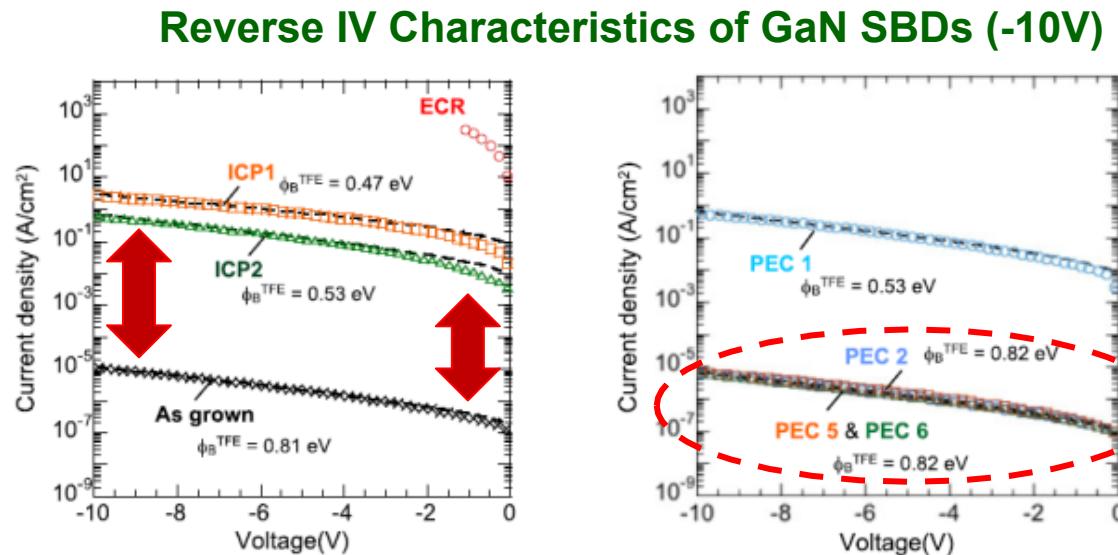

# Sub-surface etch damage from ICP etching

- Photo-assisted electrochemical (PEC) etching (Matsumoto, Jpn. J. Appl. Phys. 2018)

- ICP, ECR etched GaN drift layers

- PEC oxidation + TMAH oxide etch to remove sub-surface etch damage

- Fabricate SBDs

- Sub-surface etch damage:

- ECR etching  $\sim 230$  nm

- ICP etching  $\sim 70$ nm

- SBDs on ICP etched GaN have  $10^4 \times$  higher leakage

- Following PEC, IVs matched SBDs on as-grown GaN

↗ Sub-surface ICP etch damage  $\sim 50$ -300 nm

↗ Either prevent sub-surface etch damage or remove it

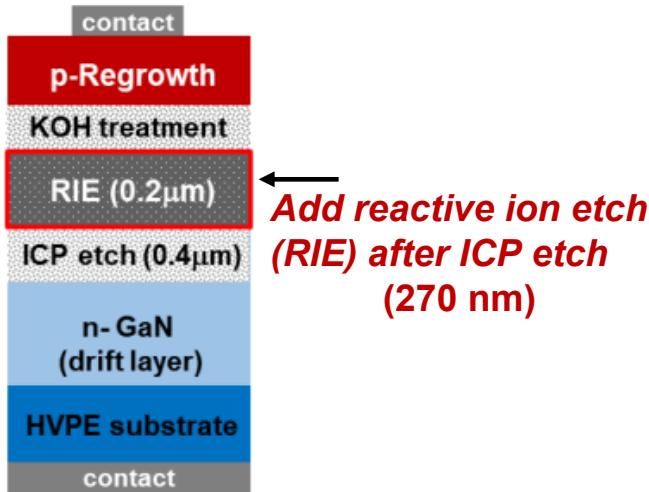

## Blanket etching of n-drift layer

- RIE etch - low damage etch used for gate recess for HEMTs

- RIE 270 nm — remove sub-surface ICP etch damage

- Finish with KOH, 10 min., 80 °C, DI rinse, N2 dry

☞ **Test low-damage RIE “clean-up” etch to remove sub-surface ICP etch damage**

## SIMS of Regrown PN Diode

- Very high levels of Si, C & O at regrowth interface

## Reverse IV Characteristics

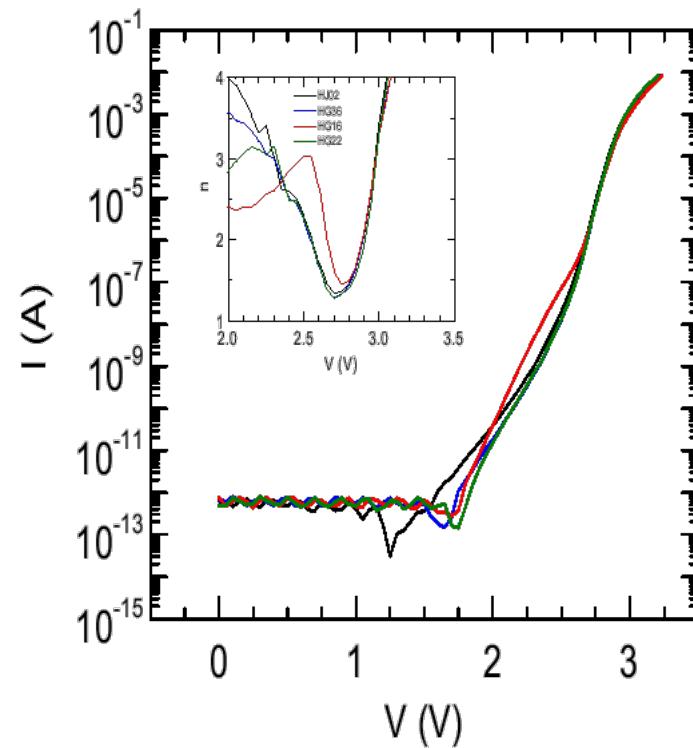

## Forward IV Characteristics

- 1 nA (6 mA/cm<sup>2</sup>) @ 500 V

- ASU: 20 mA/cm<sup>2</sup> @ 500 V (etched regrowth)

- Cornell: 2 mA/cm<sup>2</sup> @ 500 V (w/o etch regrowth)

- Low leakage < 2 V

- Ideality factor ~ 1.3

↗ Low leakage etched and regrown diodes demonstrated with RIE removal of sub-surface ICP etch damage

# Use in-situ etching to remove sub-surface ICP etch damage to GaN

$\text{CBr}_4$

$\text{CCl}_4$

$\text{TBCl}$

↗ Better surfaces follow J. Han's (APL 2019) conditions:

- pressure

- temperature

- low NH<sub>3</sub>

↗ No reduction of Si spike with listed halide sources

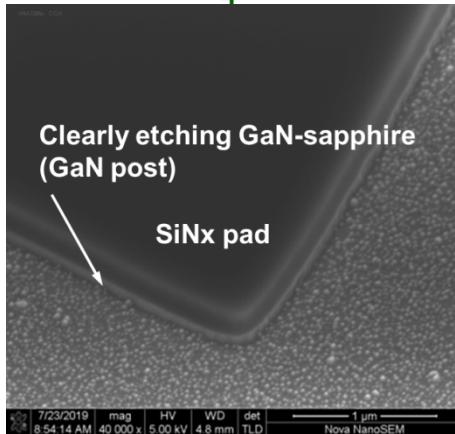

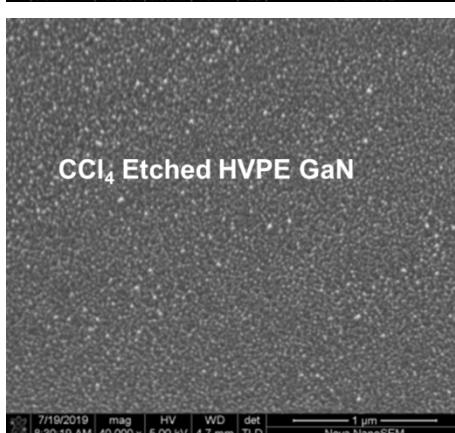

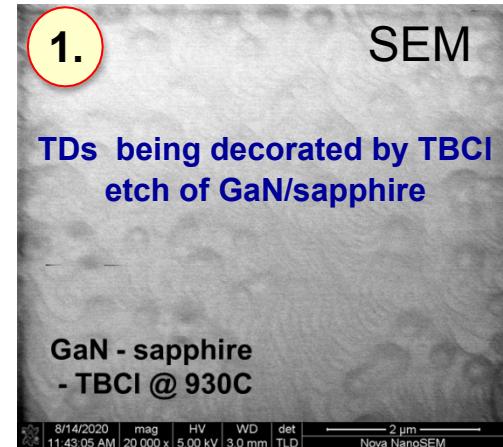

$\text{CCl}_4$  Etched HVPE GaN

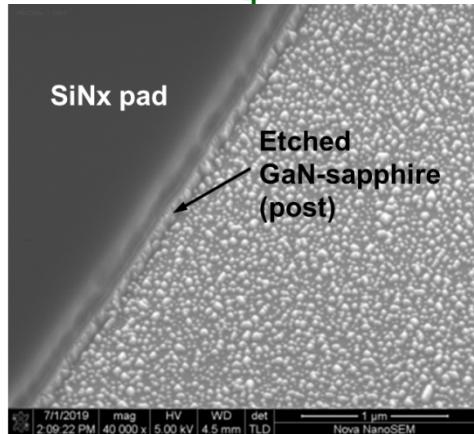

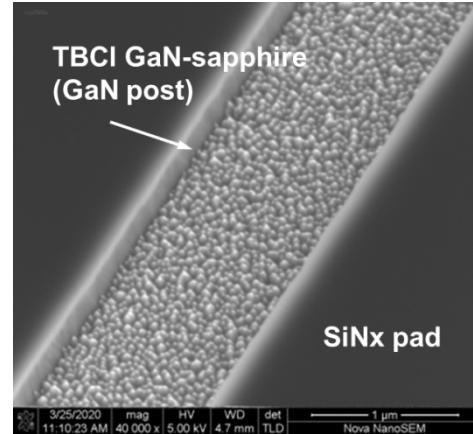

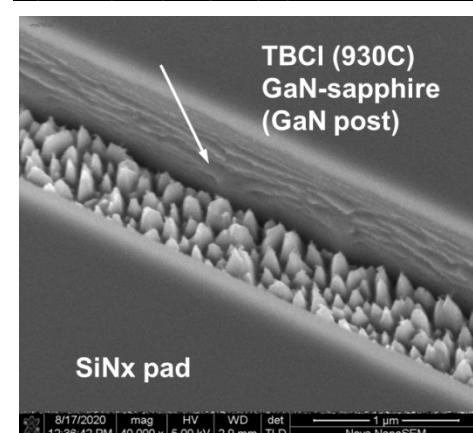

TBCl (930C) GaN-sapphire (GaN post)

- Surfaces exposed to air (months)

- Si always present by SIMS,  $> 1\text{e}19 \text{ cm}^{-3}$

• Typical poor surface observed for many etch conditions

• Rough surface if etching HVPE GaN, ICP etched GaN...

Æ Rough etched surfaces regardless of reactor conditions, chemistry or GaN crystal (HVPE, on sapphire) when surface is exposed to air.

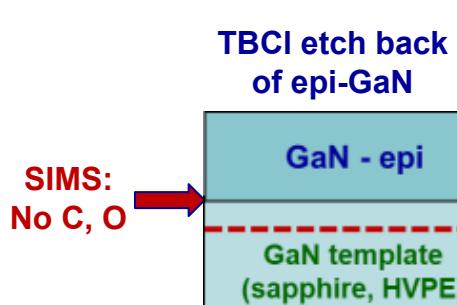

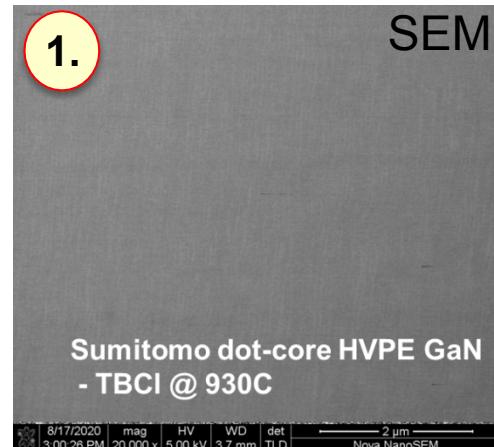

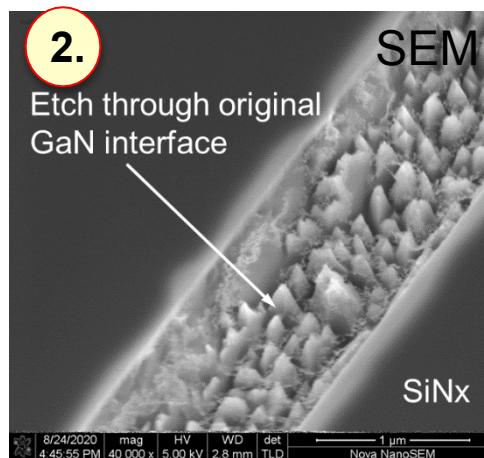

# In-situ TBCI etching of GaN grown without exposure to air

## TBCI etching of GaN epi surface following growth (No exposure to air)

- Smooth etch for epi on HVPE GaN not exposed to air

- Smooth etch for epi on HVPE GaN and GaN on sapphire

Æ Very different morphology for TBCI @ 930C depending on exposure to air

Æ Starting GaN surface (air exposure ↗ Si) is more important than etch conditions?

Æ Focus on Si removal as “surface prep”

- Rough etch once through re-growth interface for epi on HVPE GaN

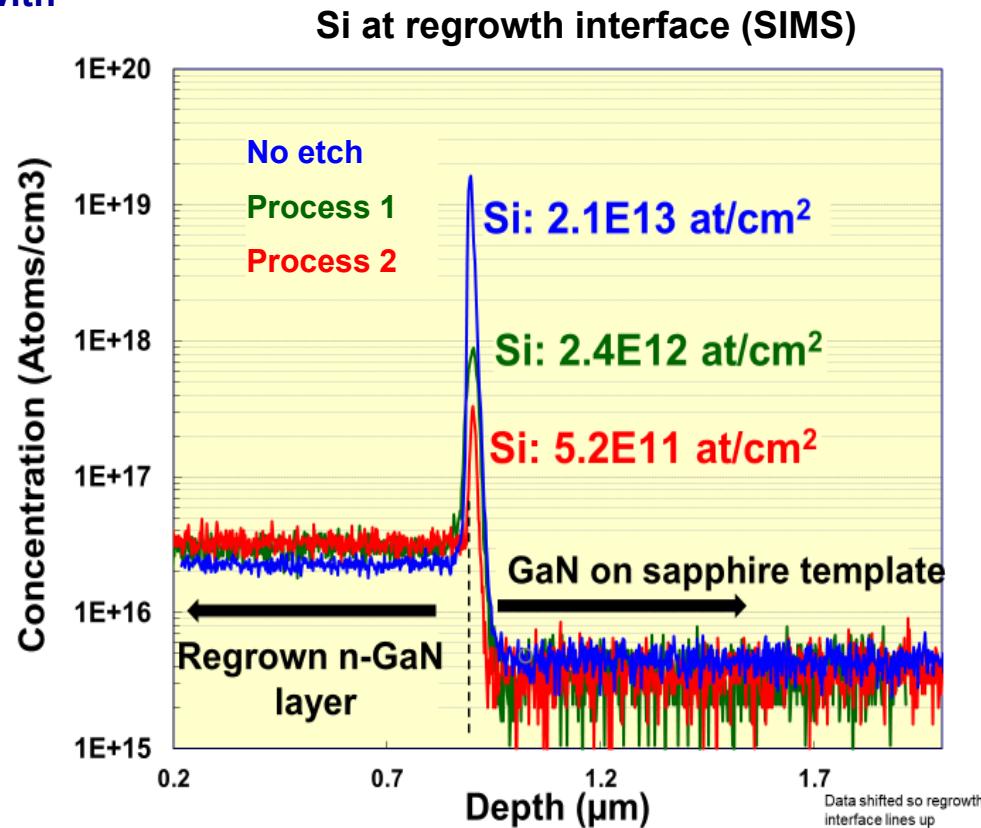

# Removal of Si at regrowth interface using $\text{XeF}_2$

## Use Si etch tool ( $\text{XeF}_2$ ) to remove interfacial Si prior to regrowth

Andrew Koehler

(NRL)

- Utilize commercial GaN/sapphire templates with consistently high surface Si concentration

- Expose GaN to different Si etch recipes (Si etch tool with pulsed  $\text{XeF}_2$ , RT process)

$$2\text{XeF}_2 + \text{Si} \rightarrow 2\text{Xe} + \text{SiF}_4$$

- Regrow GaN drift layer – (CV, SIMS)

Æ Good diodes made with intentional Si ~  $5 \times 10^{11} \text{ cm}^{-2}$

↗ > 10x reduction in interfacial Si with  $\text{XeF}_2$  process in Si etch tool

↗ Try  $\text{XeF}_2$  on MOCVD system

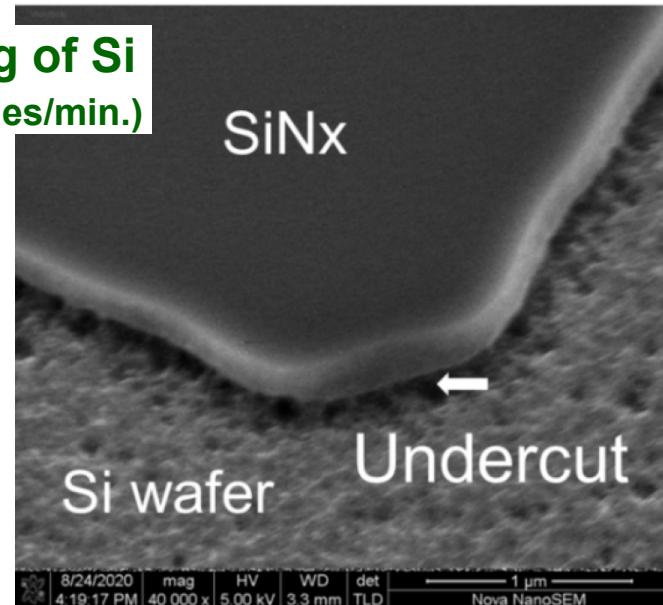

## Replicate Si etch tool ( $XeF_2$ ) process in MOCVD chamber

Drysdale (2015) –  $XeF_2$  etching of Si

- Continuous  $XeF_2$  flow (1-9 torr)

White Crystals,

3.8 torr @ 25C

(Dock Chemical)

$XeF_2$  etching of Si

(25C, 10  $\mu$ moles/min.)

- Si etch:  $\sim 1500 \text{ \AA/hr}$  @ RT

↗  $XeF_2$  is reaching surface

- Johnson (APL 2019) -  $XeF_2/BCl_3$  etching of GaN

↗ Try etching GaN with  $XeF_2$

Æ Essentially a MOCVD setup

operating at  $\sim 10$  torr

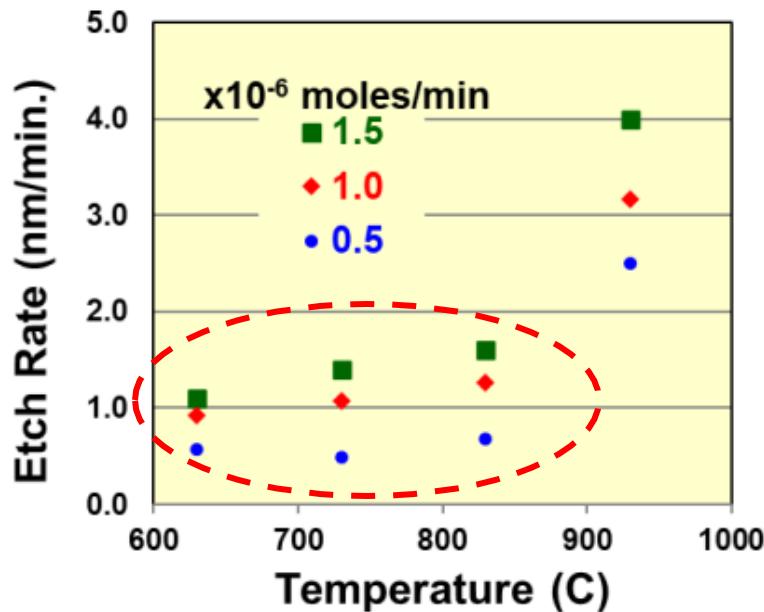

## Etch Rate vs. Temperature

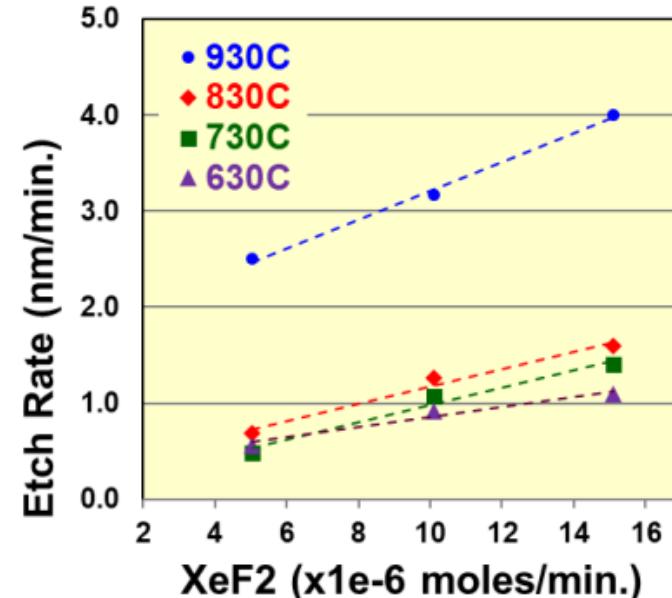

## Etch Rate of GaN vs. $\text{XeF}_2$ Flux

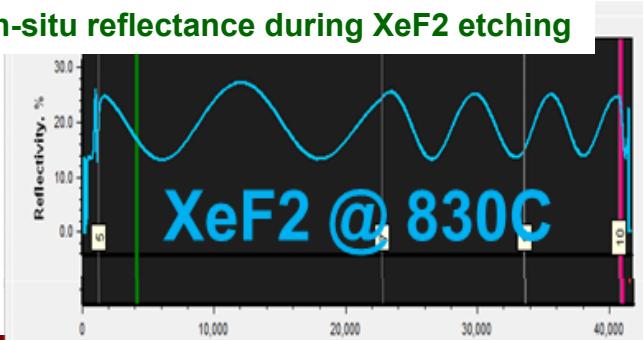

## In-situ reflectance during $\text{XeF}_2$ etching

- ↗ Etch rate is linear with  $\text{XeF}_2$  flow

- ↗ Stable reflectance @ 730C, 830C

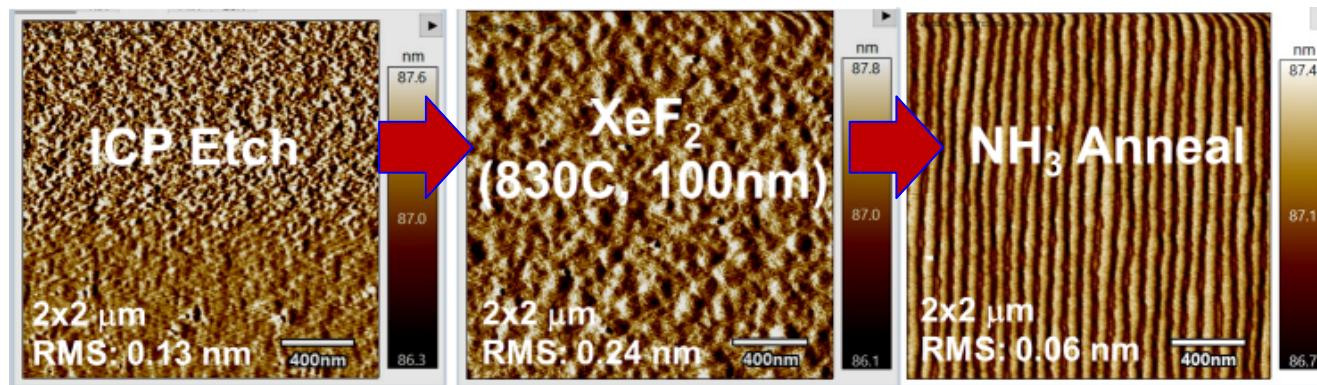

# In-situ $\text{XeF}_2$ etching of GaN (air exposed surface)

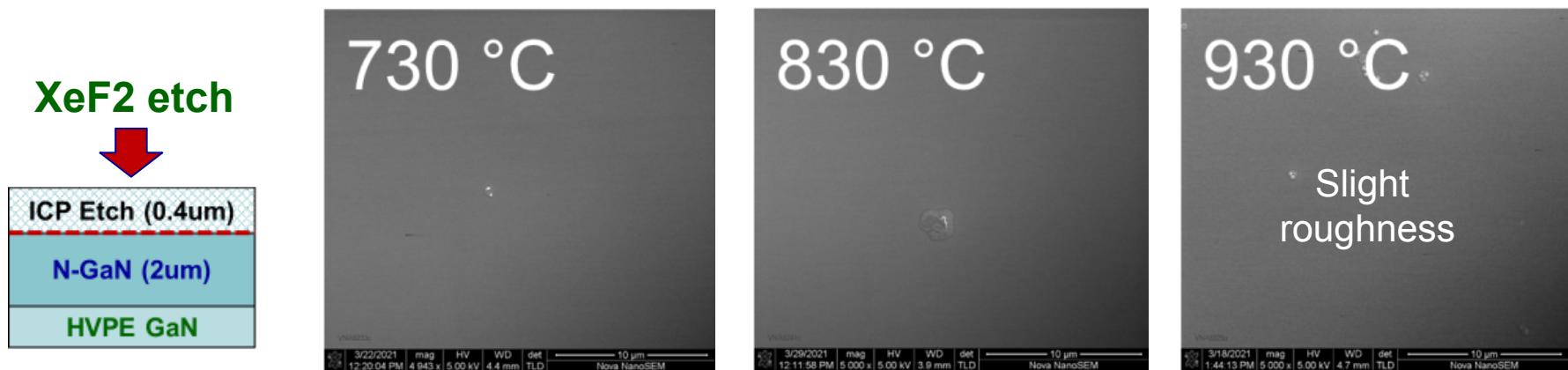

## SEM of $\text{XeF}_2$ etched - ICP etched GaN (air exposed)

## AFM of $\text{XeF}_2$ etched - ICP etched GaN (air exposed)

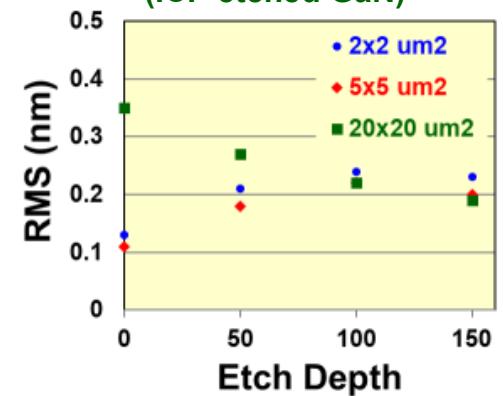

## RMS vs. $\text{XeF}_2$ etch depth (ICP etched GaN)

- *PN Diode IV Characteristics*

Regrow

p-anode

Regrown anode on ICP-etched drift region can produce AlGaN PN diodes equal to continuously grown diodes (c-plane)

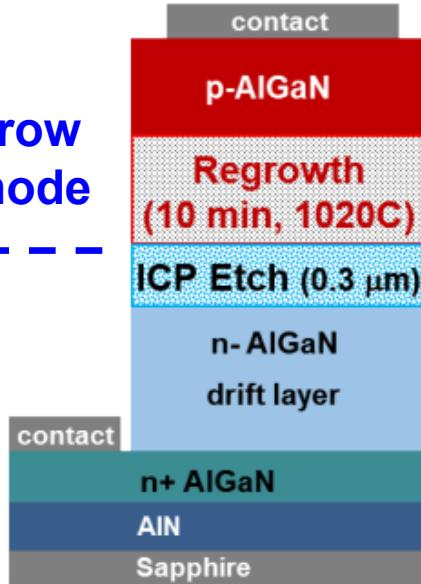

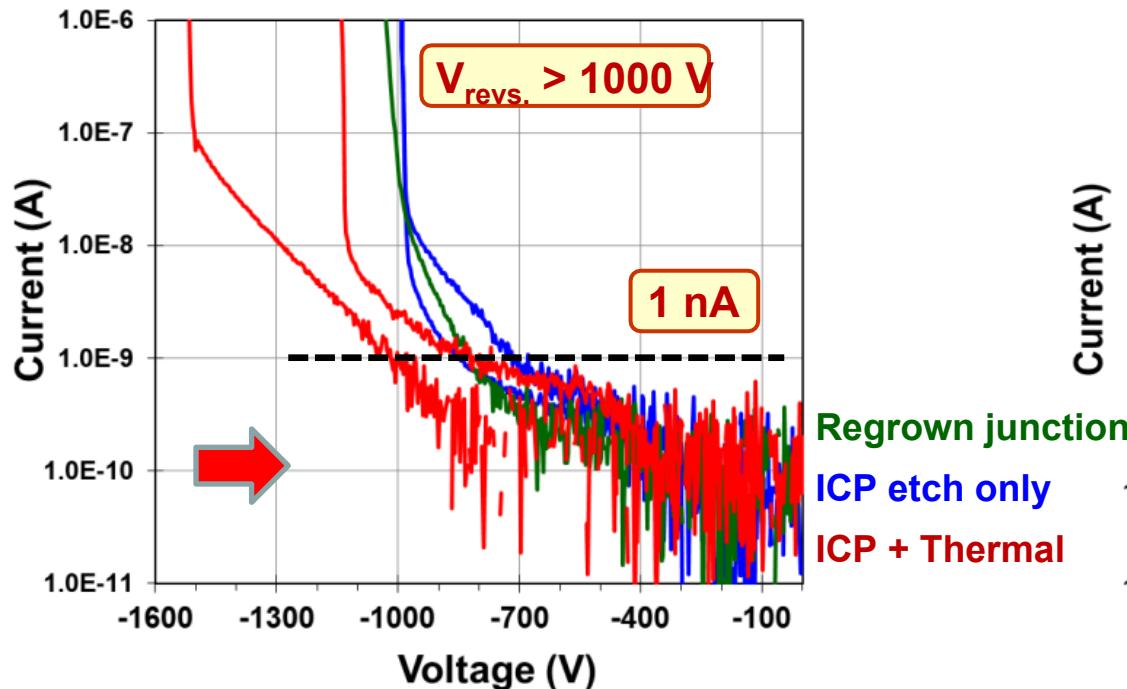

## ***PN Diode IV Characteristics on an ICP-etched drift layer***

***Reverse IV Characteristics***

***Forward IV Characteristics***

- Regrowth with thermal treatment reached  $V_{\text{revs.}} > 1500\text{V}$  (@  $1\mu\text{A}$ )

- Regrowth on “as-grown” diode repeated

- ICP-etched reached  $V_{\text{revs.}} \sim 1000\text{V}$  (@  $1\mu\text{A}$ )

- Very low forward current leakage indicates a good PN junction ( $TDD = \text{low } 10^9 \text{ cm}^{-2}$ )

↗ Regrowth of p-AlGaN on ICP-etched AlGaN yields kilo-volt class PN diodes with low leakage!

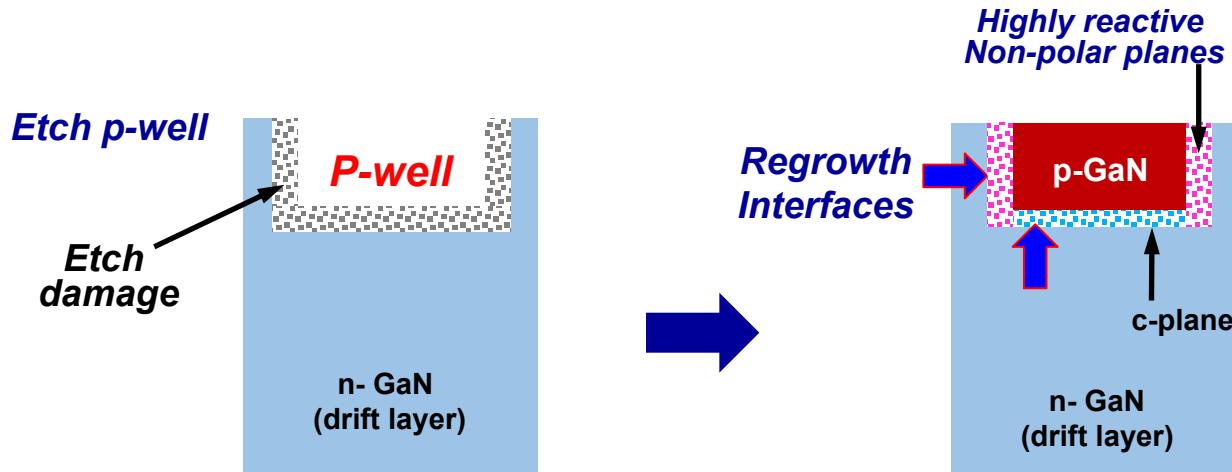

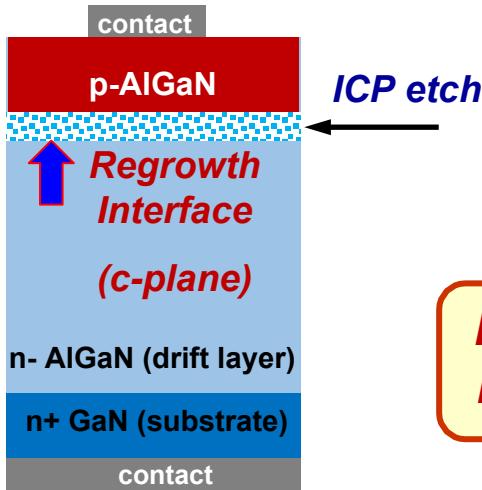

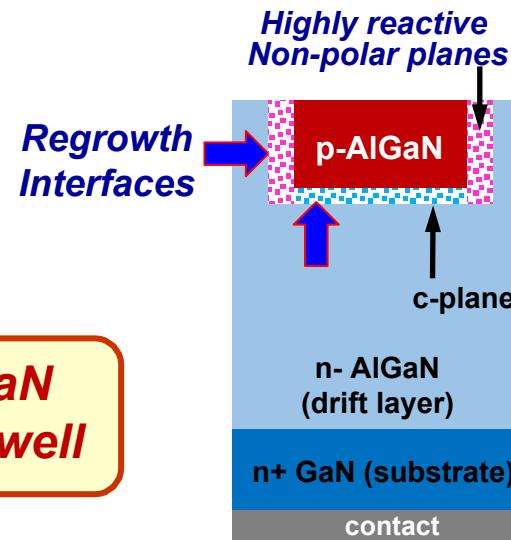

# Next develop p-AlGaN regrowth in etched well

## Regrowth on etched c-plane

## Regrowth in etched p-well

**Next develop p-AlGaN regrowth in etched well**

### NOT significant:

- Electrically active impurities at regrowth interface

- Damage to crystal structure and point defects from ICP etch

### Still in question:

- Incorporation rates of impurities and growth rates depend on crystal plane

- Non-selective mask or etch-back

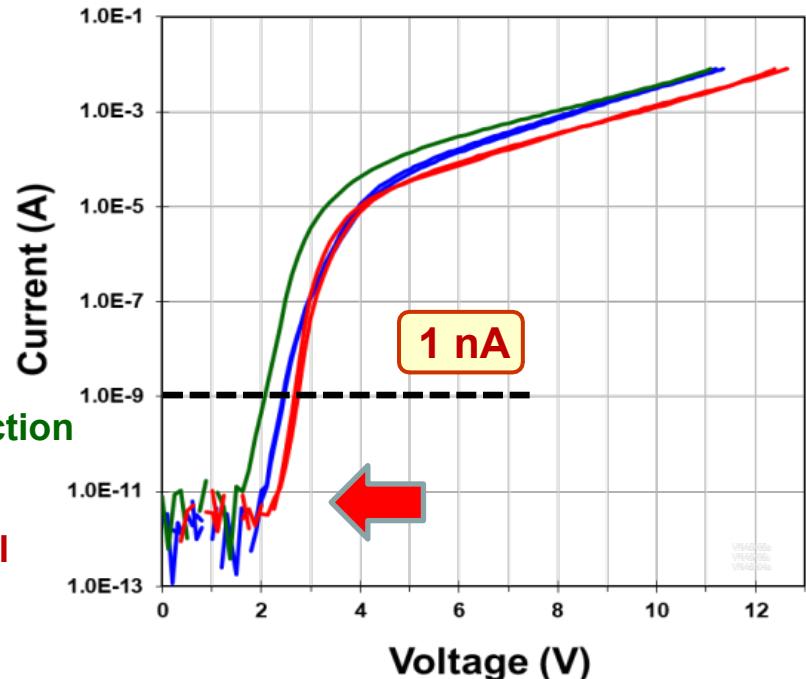

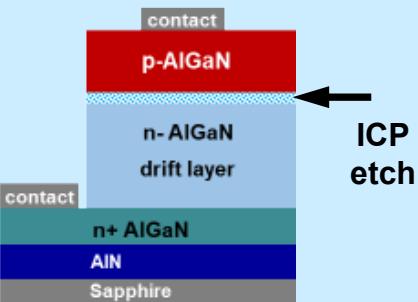

# PN diode by regrowth of p-30%AlGaN

## P- anode regrowth on planar etch drift layer

## P- anode regrowth in etched well in drift layer

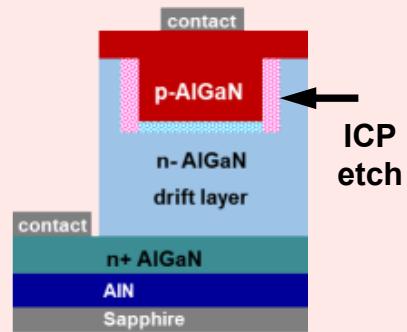

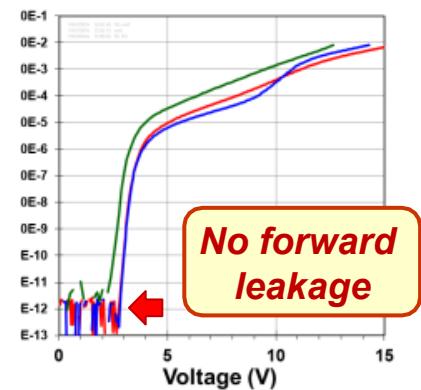

## Reverse IV

## Forward IV

Reverse leakage  $< 10^{-10} \text{ A}$

out to 1kV (noise floor)

$I_{revs} \sim 2e-6 \text{ A/cm}^2$

- ↗ NO difference between regrowth in etched well, planar etch and continuous growth! ( $\text{Al}_{0.3}\text{Ga}_{0.7}\text{N}$ )

- ↗ First SArG PN junction equal to continuously grown PN junction

- ↗ Foundational element for practical power devices:

MPS diode and J-FET, D-MISFET transistors

- **Plasma etched and regrown PN diodes in GaN face two problems**

- Due to crystalline defects induced by dry-etch process result in high reverse leakage currents

- High levels of Si contamination are present at the regrowth surface

- **Use of novel XeF<sub>2</sub> source in MOCVD is effective at in-situ etching of GaN to remove residual ICP etch damage**

- **XeF<sub>2</sub> is effective at removing Si contamination on the surface of GaN epilayers**

- **High performance regrown AlGaN PN diodes are tolerant to residual etch damage and surface Si contamination, unlike regrown GaN diodes**

*Funded by the Advanced Research Projects Agency – Energy (ARPA-E), U.S. Department of Energy under the PNDIODES program directed by Dr. Isik Kizilyalli.*