## I.1.1 High-Efficiency, Medium-Voltage-Input, Solid-State-Transformer-Based 400-kW/1000V/400A Extreme Fast Charger for Electric Vehicles ((Delta Electronics))

### Dr. Charles Zhu, Principal Investigator

Delta Electronics (Americas) Ltd.

39209 Six Mile Road, Suite #105

Livonia, MI 48152

E-mail: [Charles.zhu@deltaww.com](mailto:Charles.zhu@deltaww.com)

Start Date: July 20, 2018

Project Funding \$7,000,086

End Date: November 30, 2022

DOE share: \$3,499.961

Non-DOE share: \$3,500,124

### Project Introduction

Range anxiety and long battery charging time continue to be critical challenges to mass adaptation of EVs. A major identified gap to wider adoption of BEVs is the ability and availability to refuel quickly or to fast charge. Studies have shown that in areas where drivers have access to 50-kW or 120-kW fast charge stations, annual electric vehicle (EV) miles traveled (i.e., eVMT) increased by over 25%, even in cases where fast charging was used for 1% to 5% of total charging events [1]. Charge stations of higher power not only alleviate the “range anxiety” and reduce the driver’s waiting time, but also requires less investment. Michigan Energy Office completed a study in early 2019 titled “Electric Vehicle Charger Placement Optimization in Michigan: Phase I – Highways”. This study finds a system with 150kW chargers, though more expensive individually, actually has lower total system cost when compared to a 50kW charging system when serving the same battery size EV [2]. To be truly competitive to the ICEV refueling experience, even higher power stations are necessary. However, high power charge stations would create large power draws from the grid. If this occurs during peak demand periods, grid capacity could be overloaded. This problem needs to be addressed to reduce the impact on the electric utility infrastructure.

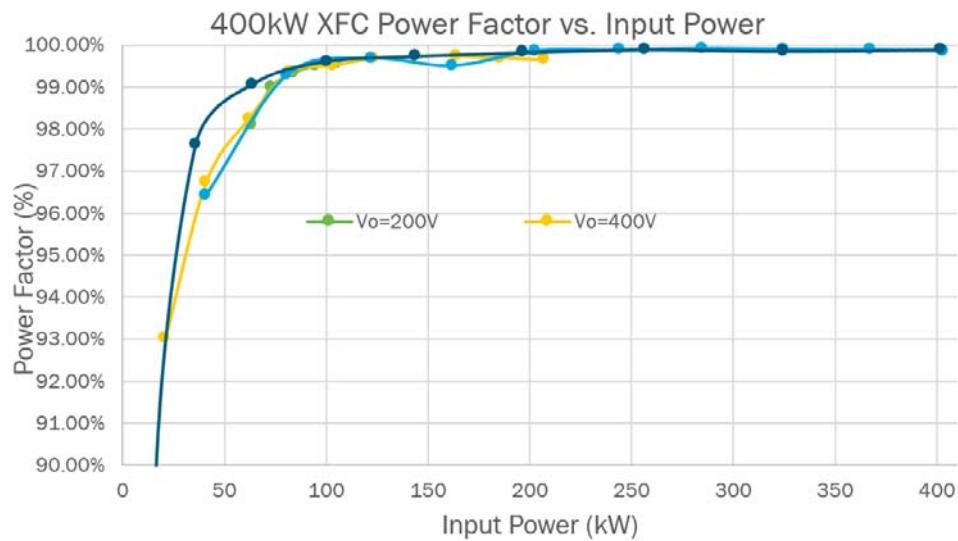

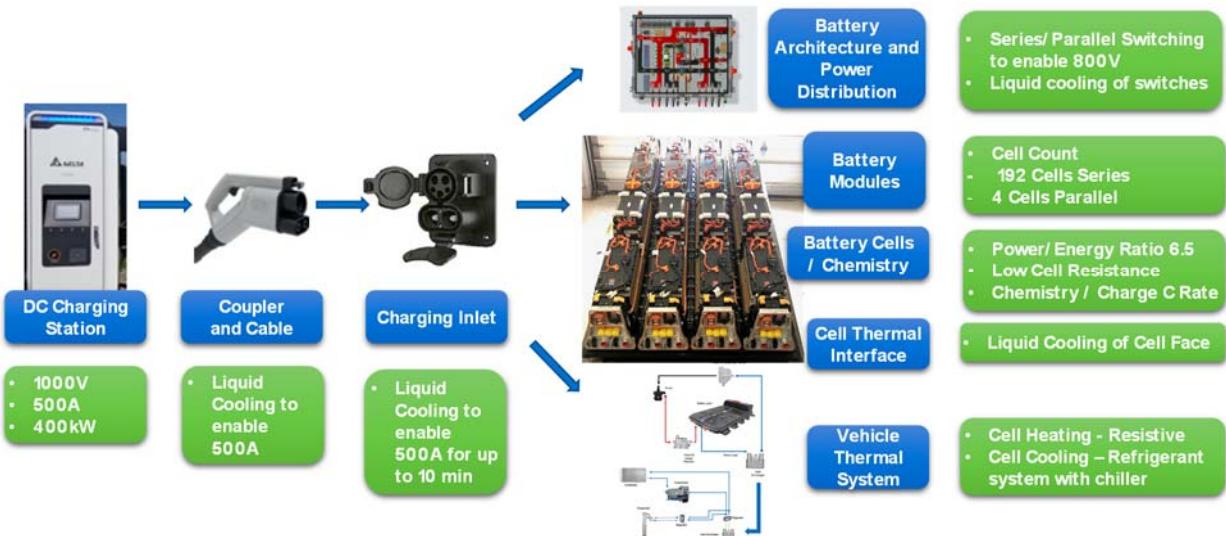

The main goal of this project is to develop a 400-kW/400-A XFC system targeting total efficiency of 96.5 percent from the MVAC grid to a vehicle. The novel SST power cell topology, combined with a new silicon carbide (SiC) MOSFET device, enables a 3.5 percent improvement in system efficiency, a 50-percent smaller equipment footprint, and four times less weight than today’s DCFC systems. The SST technology would directly utilize MVAC at 4.8-kV or 13.2-kV. This would eliminate the line frequency transformer (LFT), which steps down medium-voltage AC to 3-Phase 480-V line-to-line voltage in current DCFC systems.

### Objectives

The objectives of the program are:

To design and test a high-efficiency, medium-voltage-input, solid-state-transformer-based 400-kW Extreme Fast Charger (XFC) for electric vehicles, achieving better than 96.5 percent efficiency.

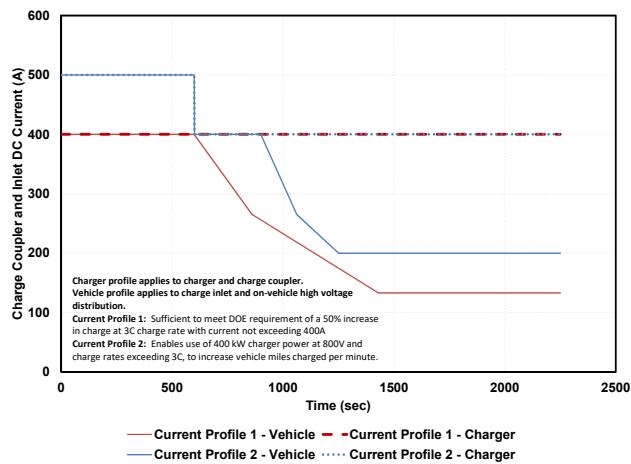

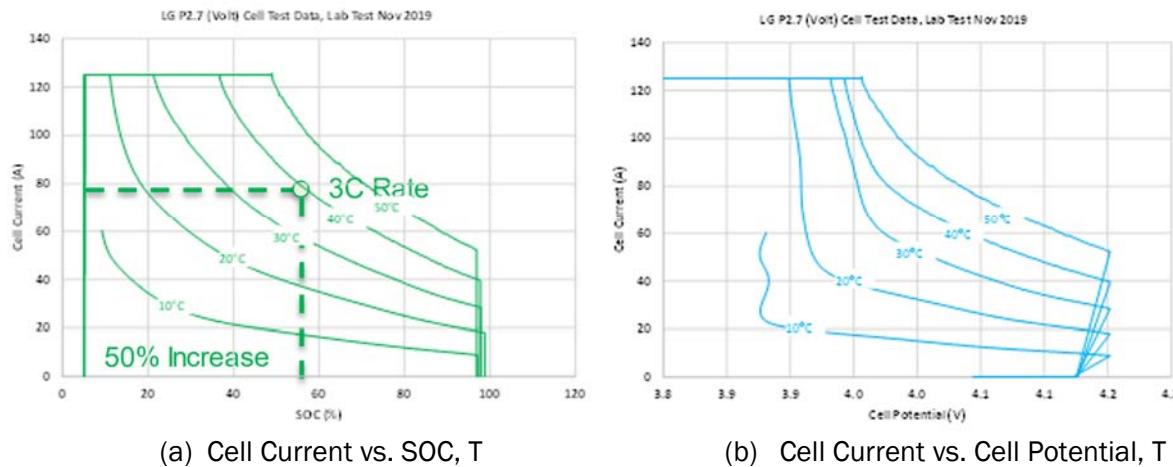

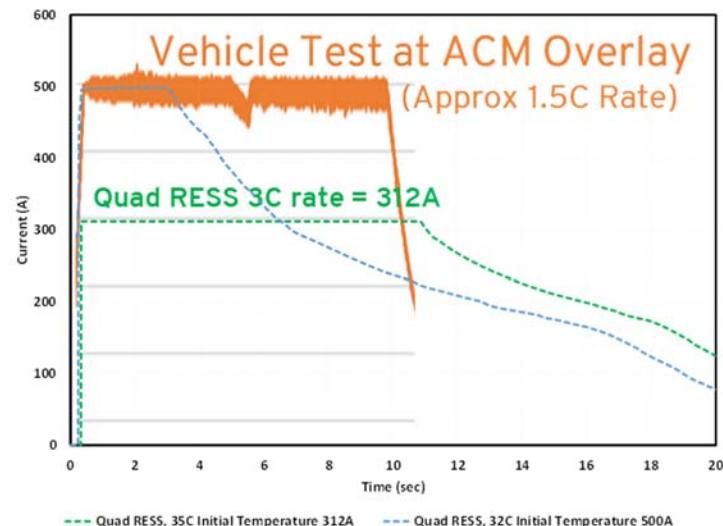

To demonstrate extreme fast charging with a retrofitted General Motors’ light-duty battery electric vehicle at 3C or higher charging rate for at least 50 percent increase of SOC.

To achieve a 180-mile charge within 10 minutes.

### Approach

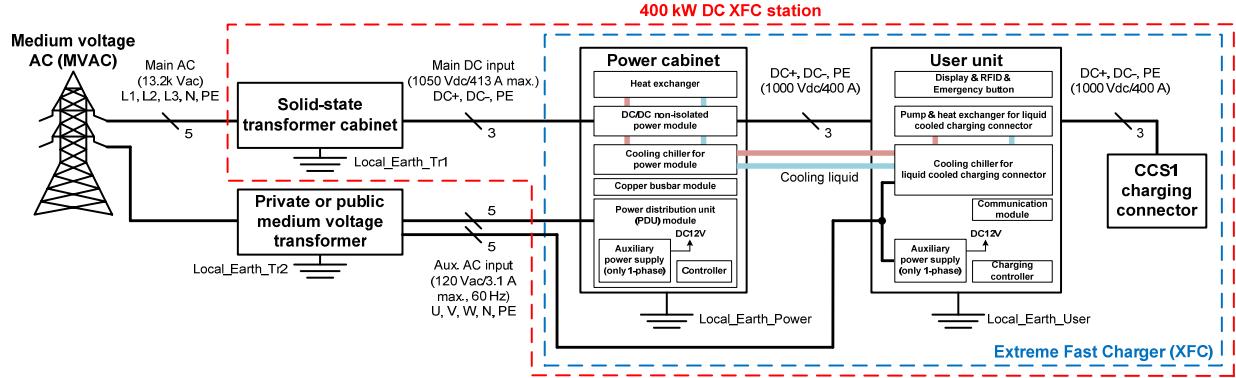

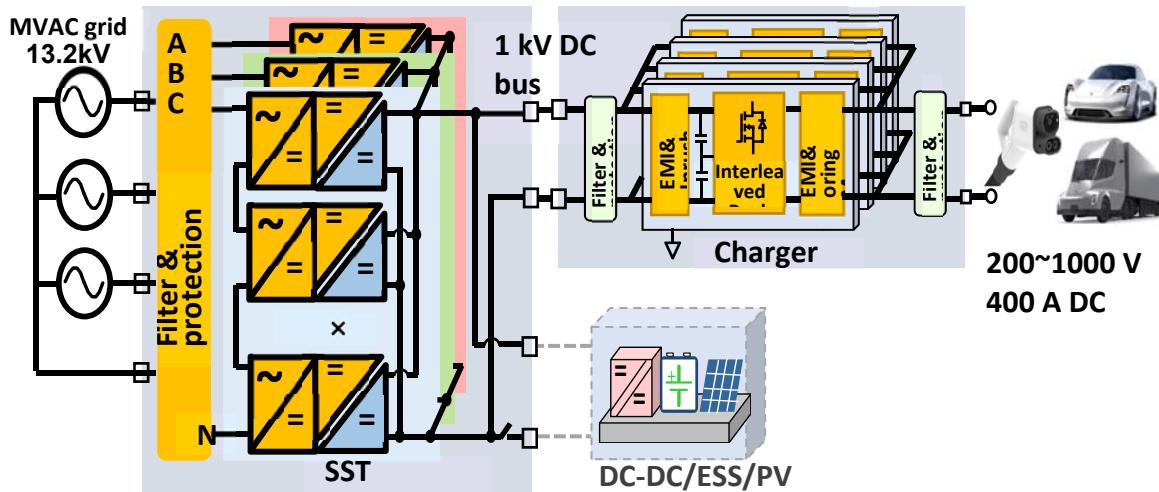

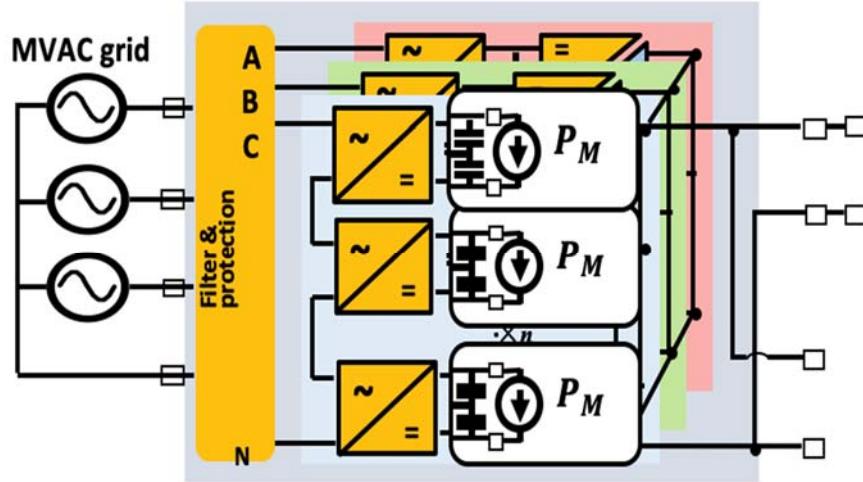

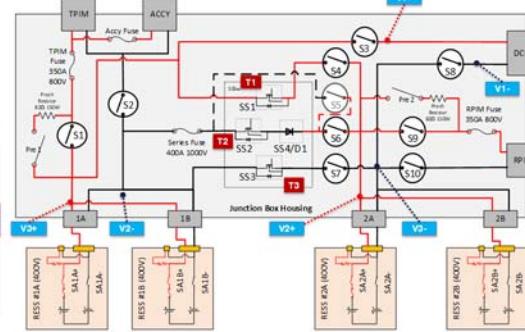

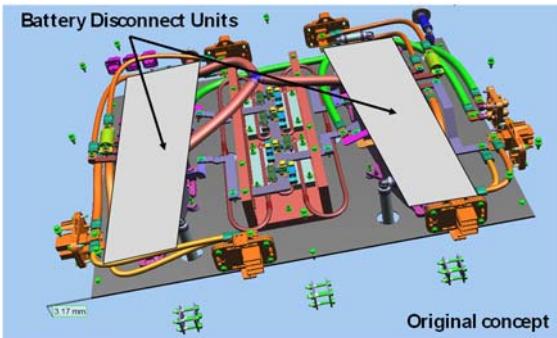

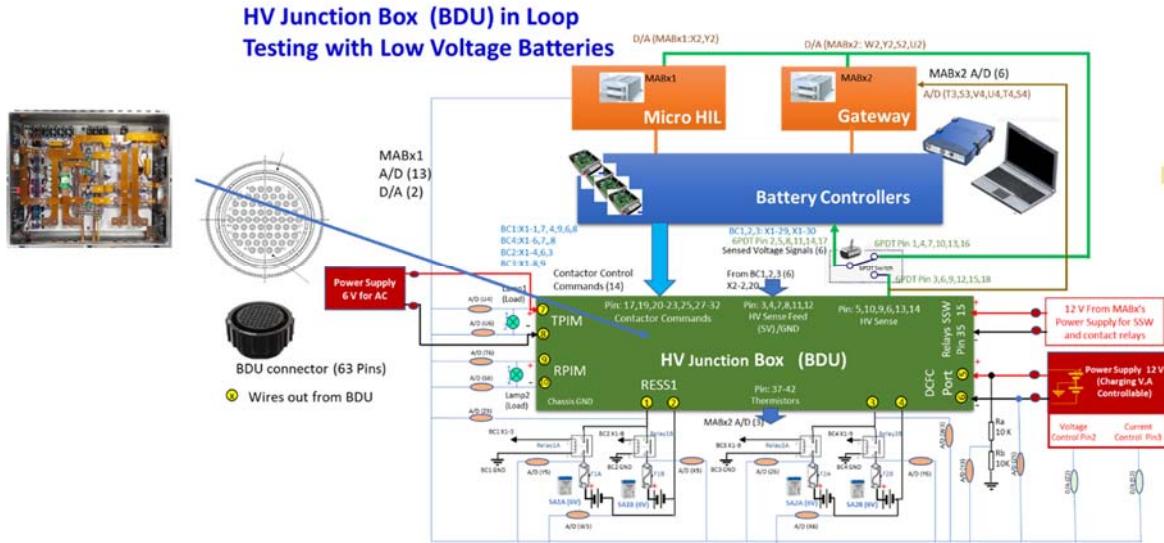

The team developed the XFC system specification and module specifications. It includes the System architecture, SST specification, DC charger specification, charge interface specification, communication architecture, fault protection specification, and installation specification. The system block diagram is illustrated in Figure I.1.1.1.

Figure I.1.1.1 XFC System Architecture

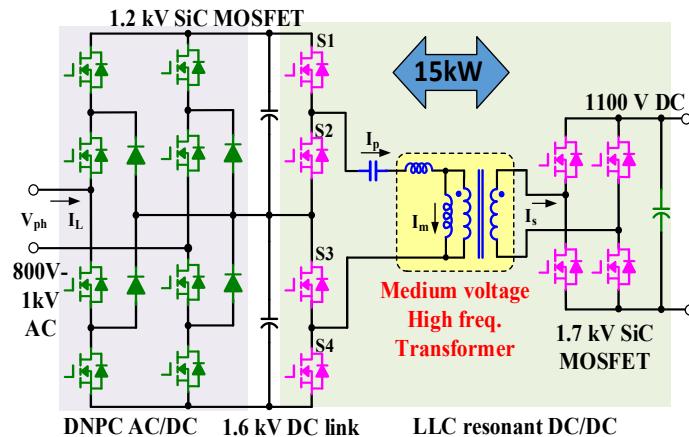

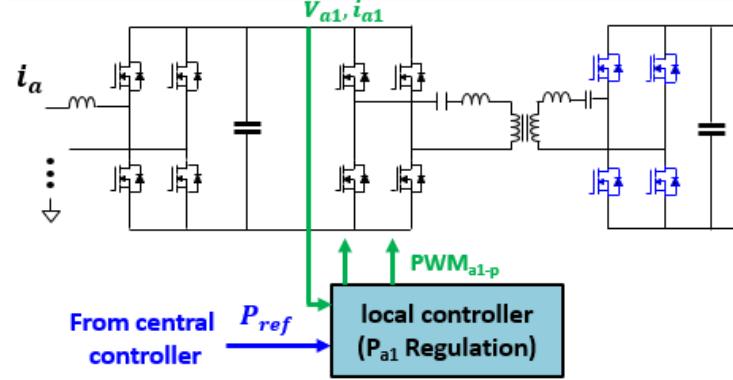

The XFC system consists of a Solid-State Transformer (SST), a Charge Controller (in power cabinet), and a Charge Dispenser (A.K.A. User Unit). The SST is the key component in the whole system because it has multiple functions such as voltage step-down, AC/DC conversion, MV insulation, and grid interface. Of all the possibilities of medium voltage levels, the standard voltages most often used in the United States are 4.16-KV, 4.8-KV, 12.47-KV, 13.2-KV, 13.8-KV, etc. The team selected modularized architecture to accommodate the various voltages. For the 4.8-kV AC medium-voltage applications, each phase has twelve modules connected in a four-series and three-parallel configurations. Alternatively, for a 13.2-kV medium-voltage application, nine power cells in each phase are connected in series for the higher voltage. For both voltage levels, the outputs of all the power cells are connected in parallel to provide total 400-kW power to the 1-kV intermediate DC bus. Each SST module is rated at 15-kW, which is optimized for the transformer thermal dissipation. Cascaded H-bridge (CHB) topology is used in system level, which lowers the voltage stress on semiconductor devices, reduces the filter size with more voltage level, and improves the power quality and electromagnetic interference (EMI) performance on grid side. The power module's circuit diagram is illustrated in Figure I.1.1.2.

Figure I.1.1.2 Circuit Diagram of Power Module

Silicon Carbide (SiC) power switches are more suitable for high voltage, high frequencies and high-temperature operation compared to the Si counterparts due to the superior properties [3]-[5]. For the SST and charge controller in the XFC system, high-efficiency and high-power density design is expected while the system operates at high voltage and high-switching frequency. As a result, SiC switches are the key technology to achieve the challenging design target.

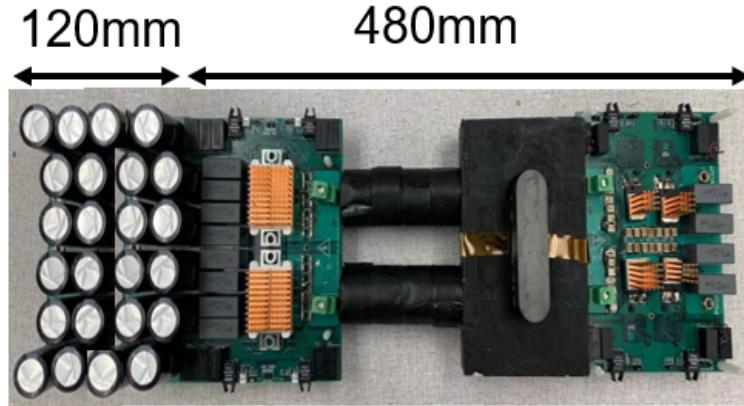

The transformer winding structure design with medium voltage insulation capability was analyzed in the context of SST converter topology to assess the best system performance. Different insulation material were compared. The transformer loss was simulated to achieve the best balance between winding loss and core loss. Electrical circuit, mechanical package and control software were developed around the power switch circuit and the isolation transformer. Two sets of version 1.5 SST cells have been built and tested. The picture of SST module is shown in the left half of Figure I.1.1.3.

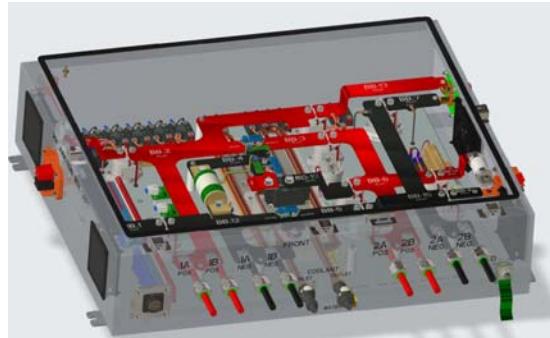

The 400-kW charging controller has a modularized design as well. The power modules, each capable of outputting 200-A, are connected in parallel. The maximum output power of each module is determined by the power dissipation and thermal design. Based on the original design target of 120-kW, four charge controller modules will be needed to provide 400-kW. Detailed analysis and simulation shows that the module has potential to output 135kW through design optimization. The charging controller module is based on Buck topology, thus also called Buck module. The buck converter runs at continuous conduction mode (CCM) with 50-kHz switching frequency. A full-bridge SiC MOSFET module with 1.2-kV, 50-A rating is used as the switching device. Two sets of version charging controller modules were built and tested. The picture of charging controller module is shown in the right half of Figure I.1.1.3.

**Figure I.1.1.3 Picture of an SST Module at left, and Charging Controller (Buck) Module at right**

The SST module, the charging controller module and the SST controller were integrated into a 15-kW charge system and tested.

Each SST module is capable of handling 1-kV AC input voltage. Four SST modules were connected in series for single phase of 4.8-kV system, which has 2.77-kV phase voltage. The output of the SST modules are connected in parallel. The output voltage of the SST modules is 1050V, to allow the charging controller to further step down to 1000V or less.

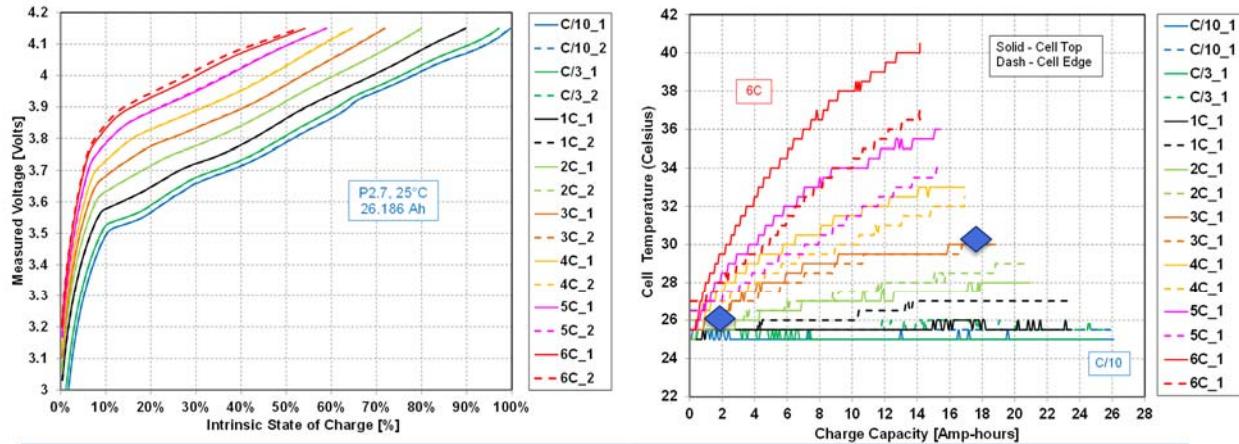

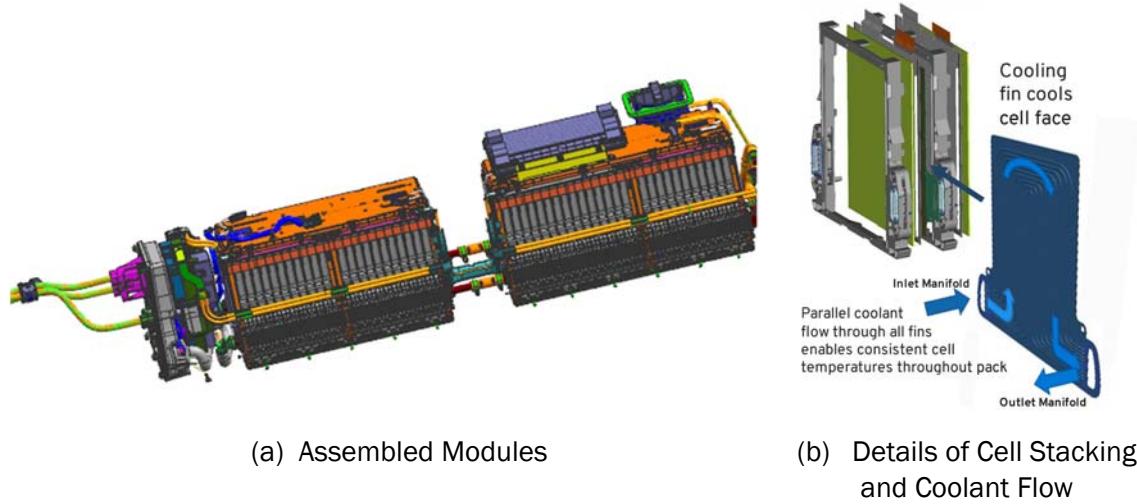

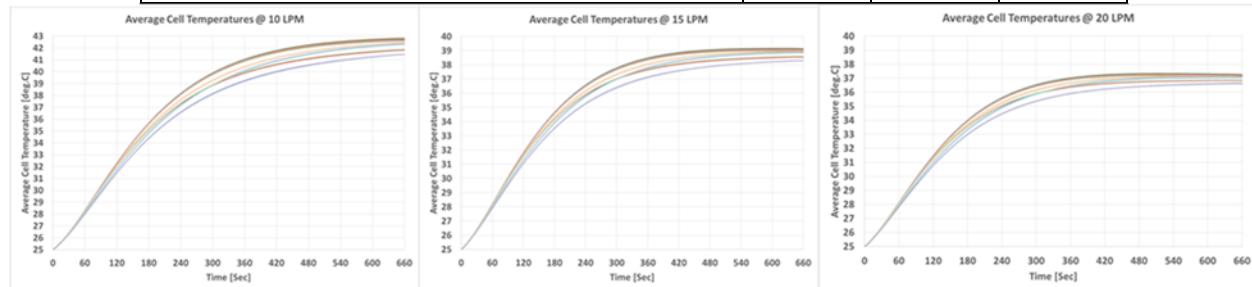

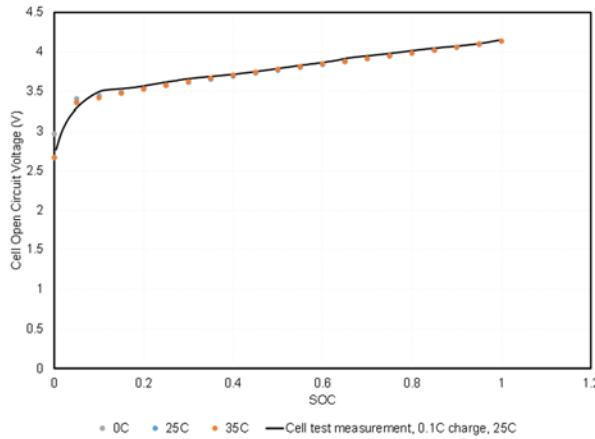

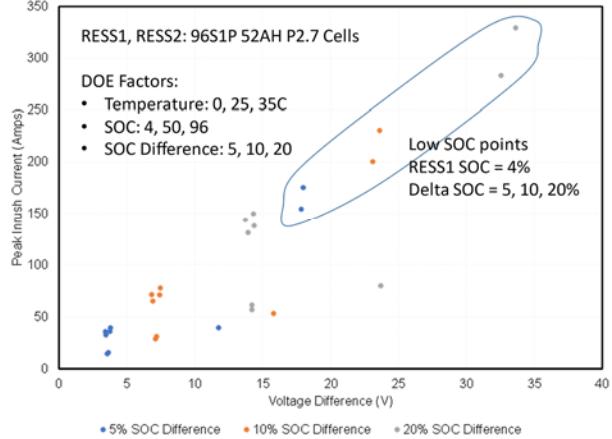

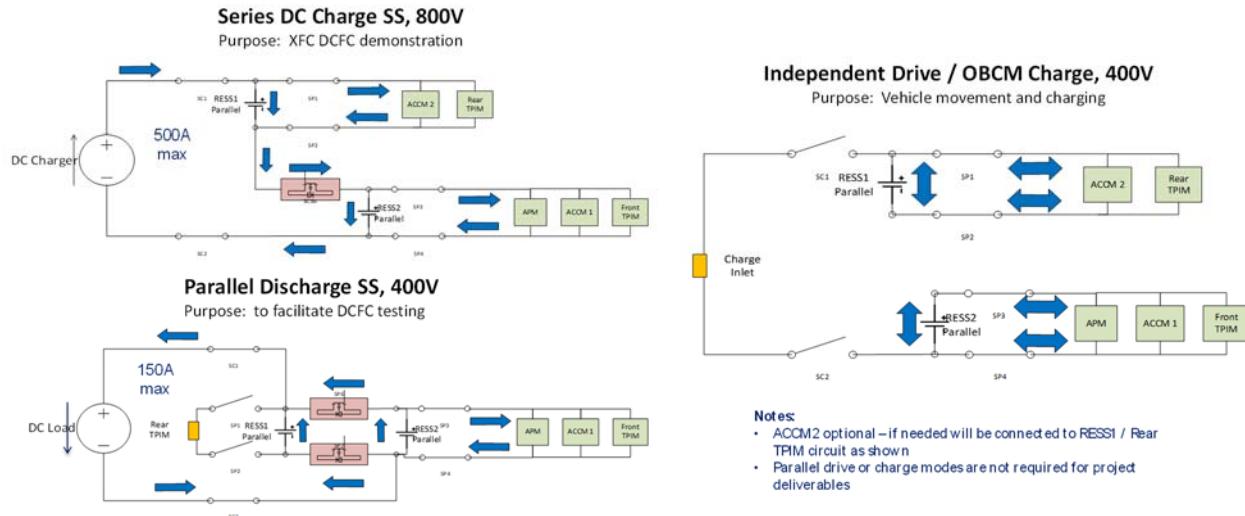

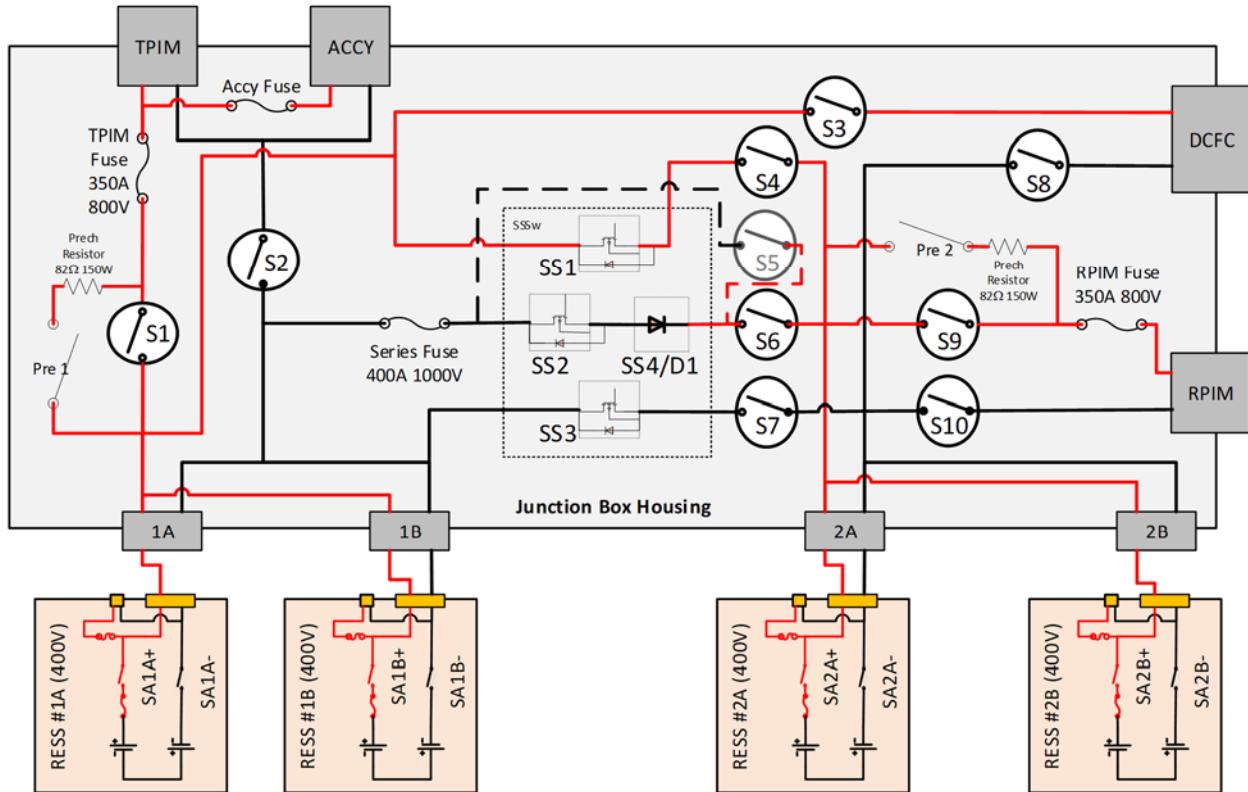

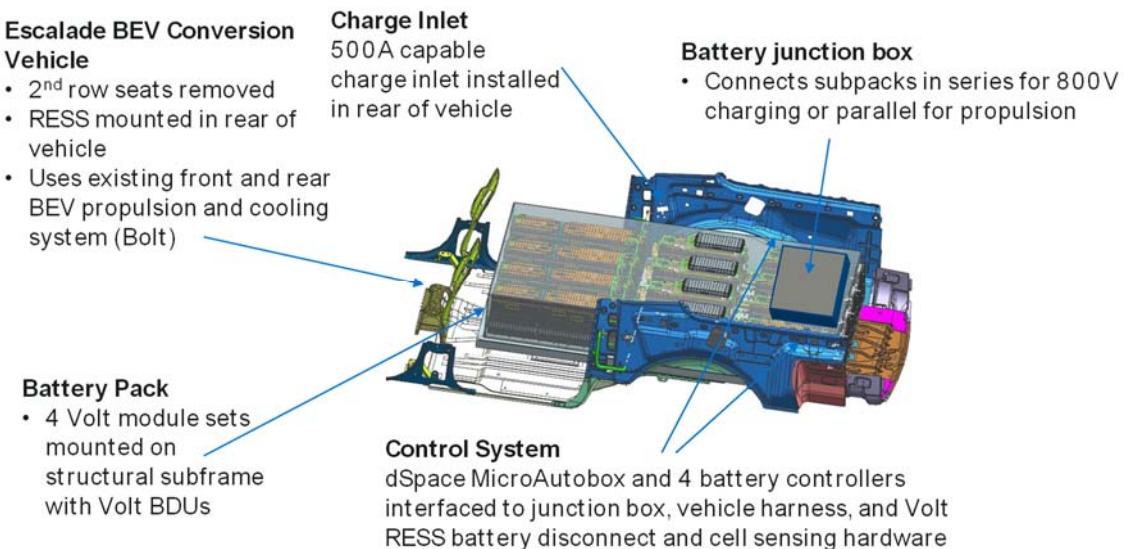

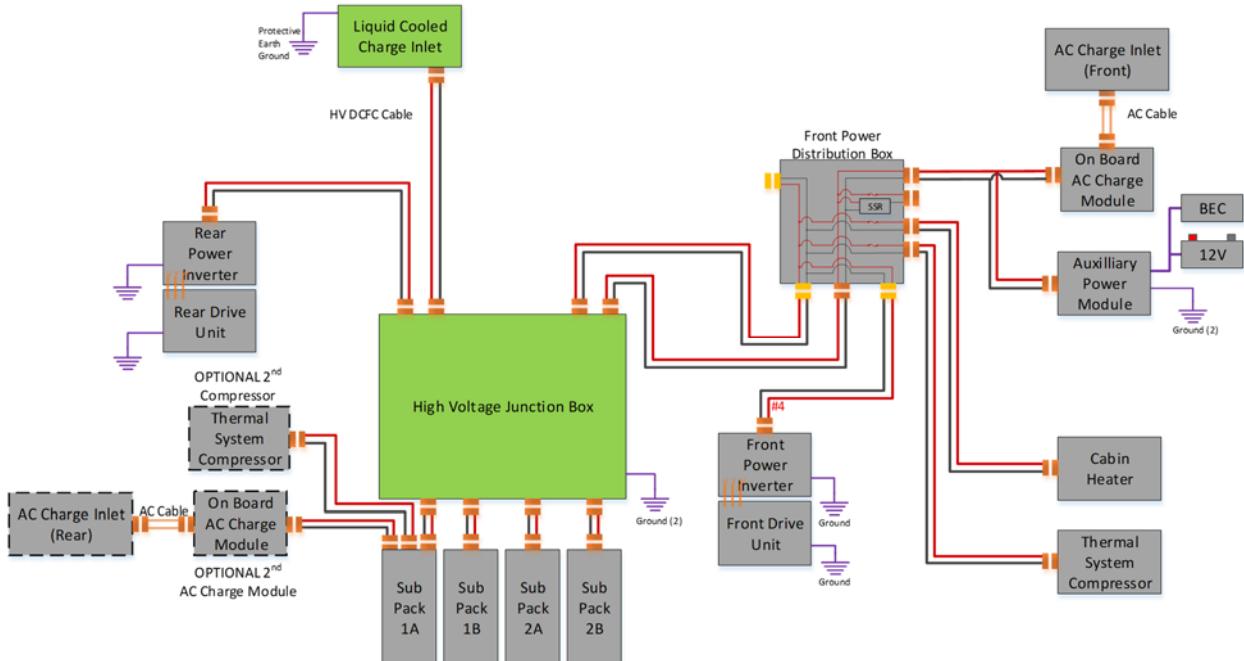

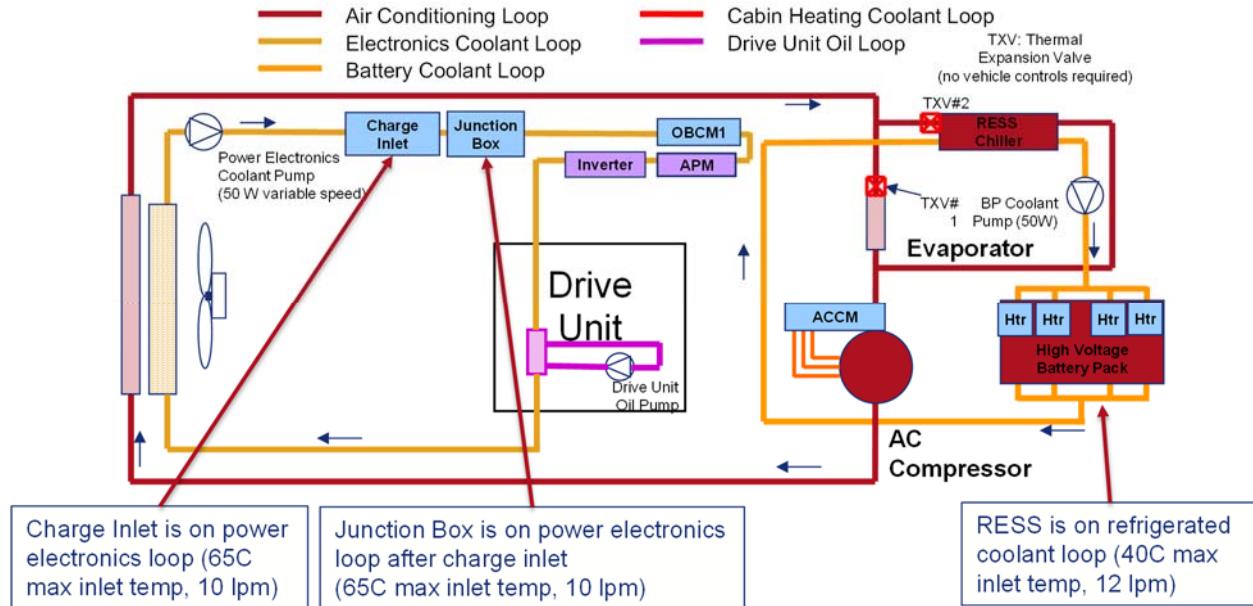

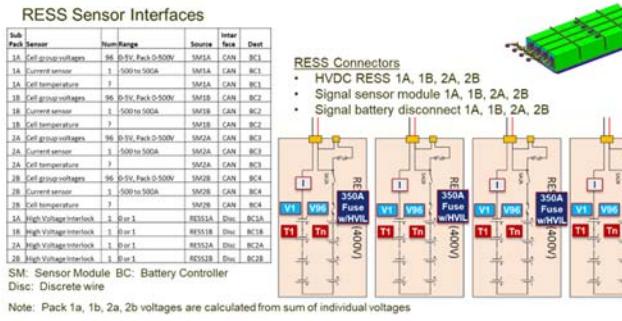

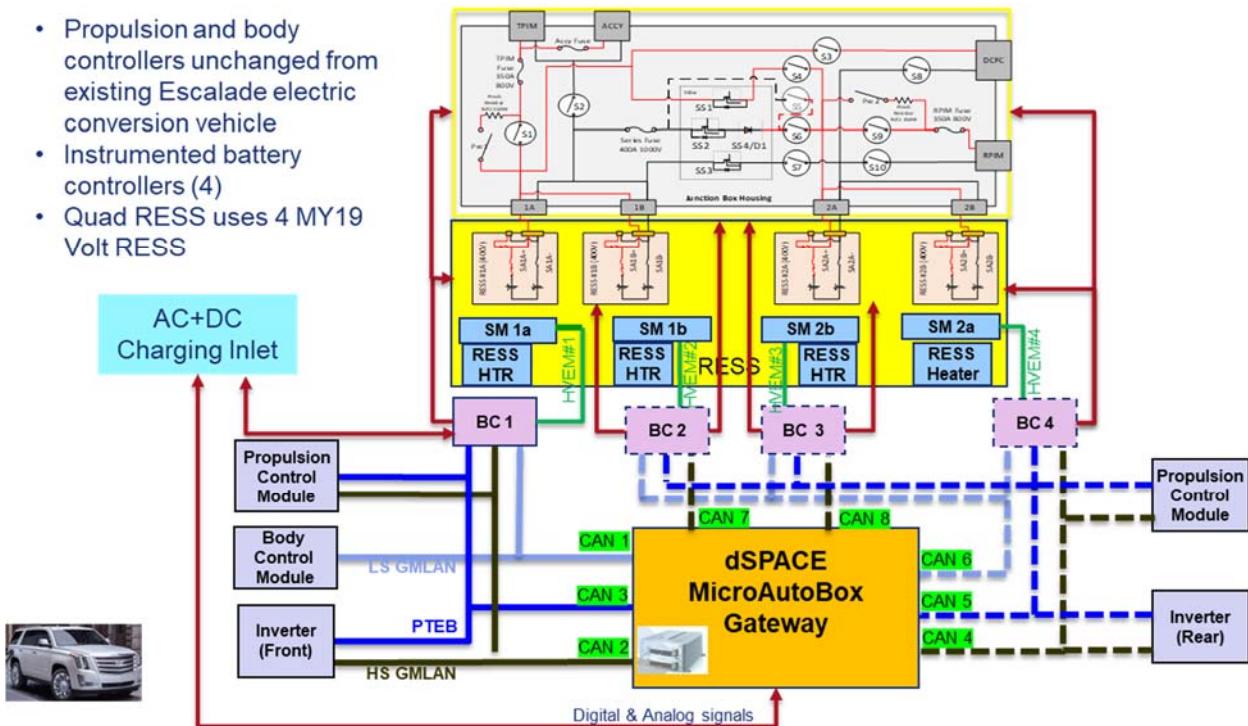

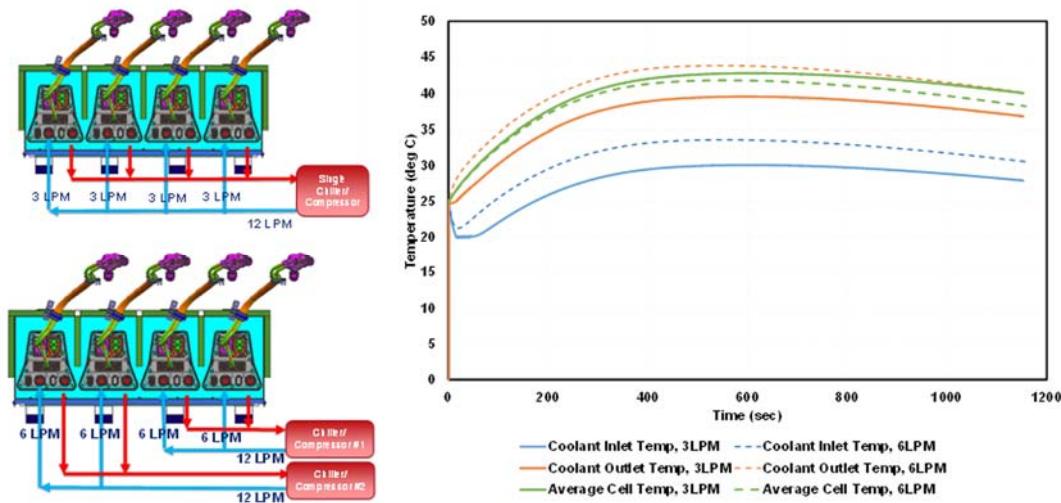

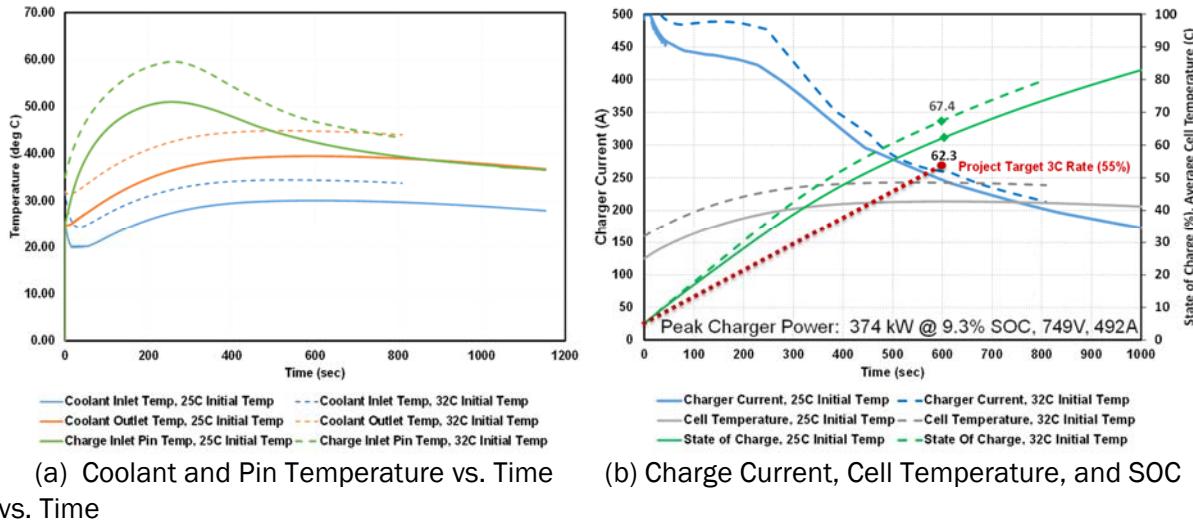

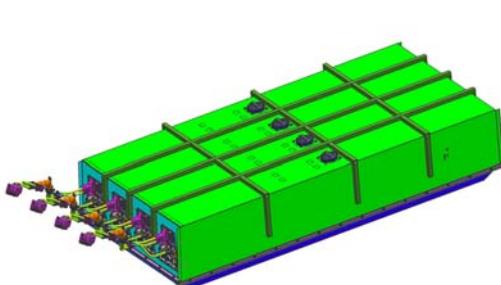

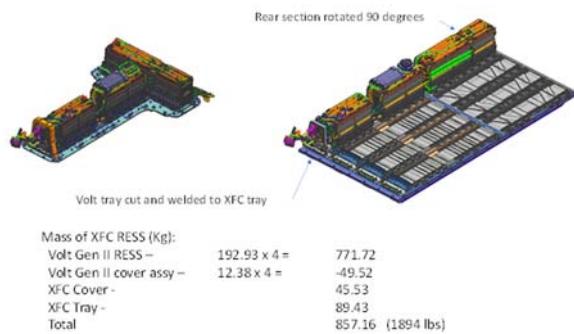

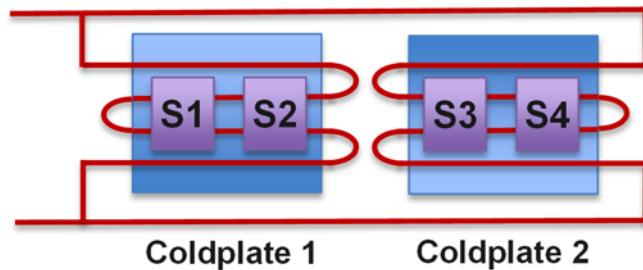

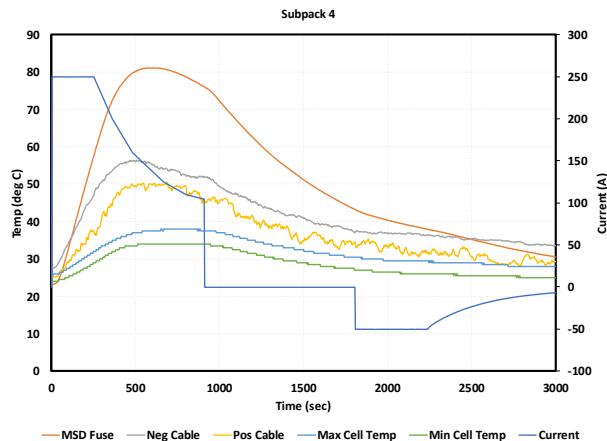

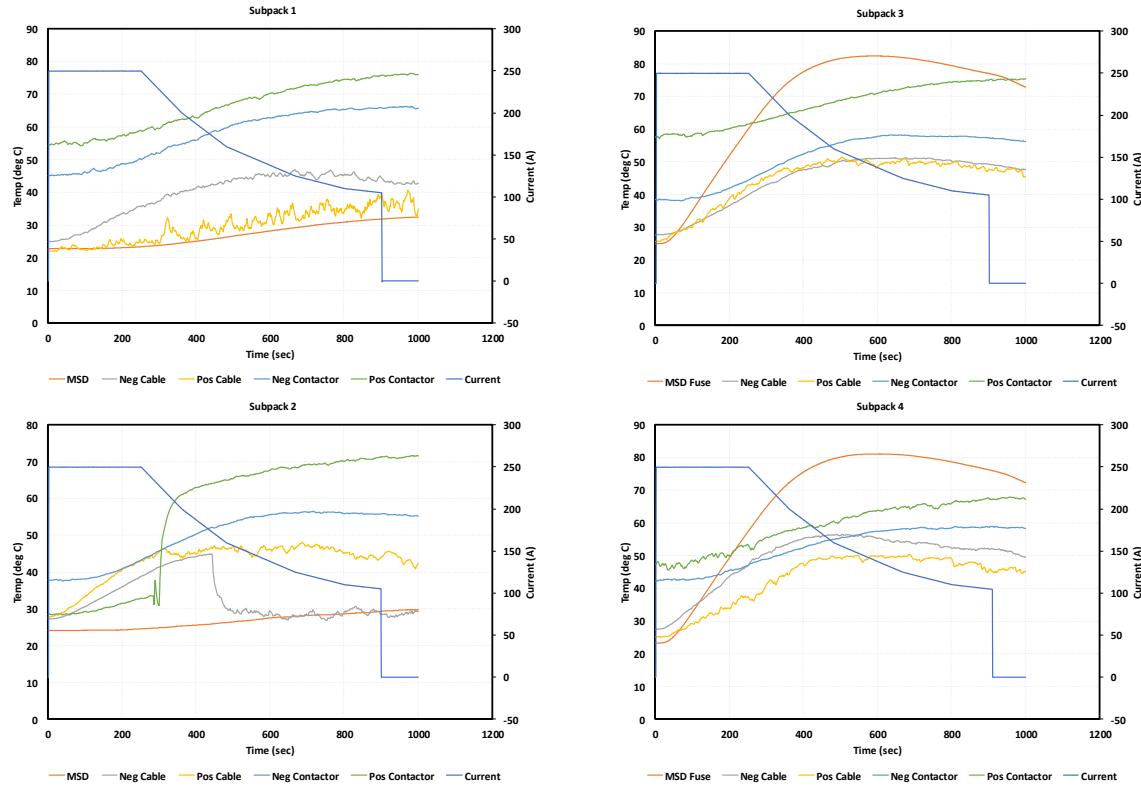

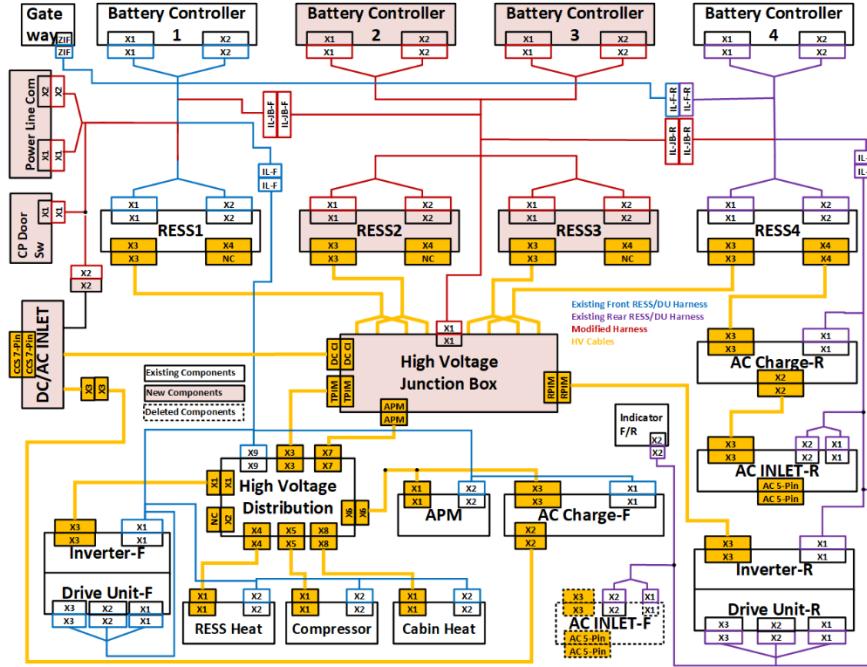

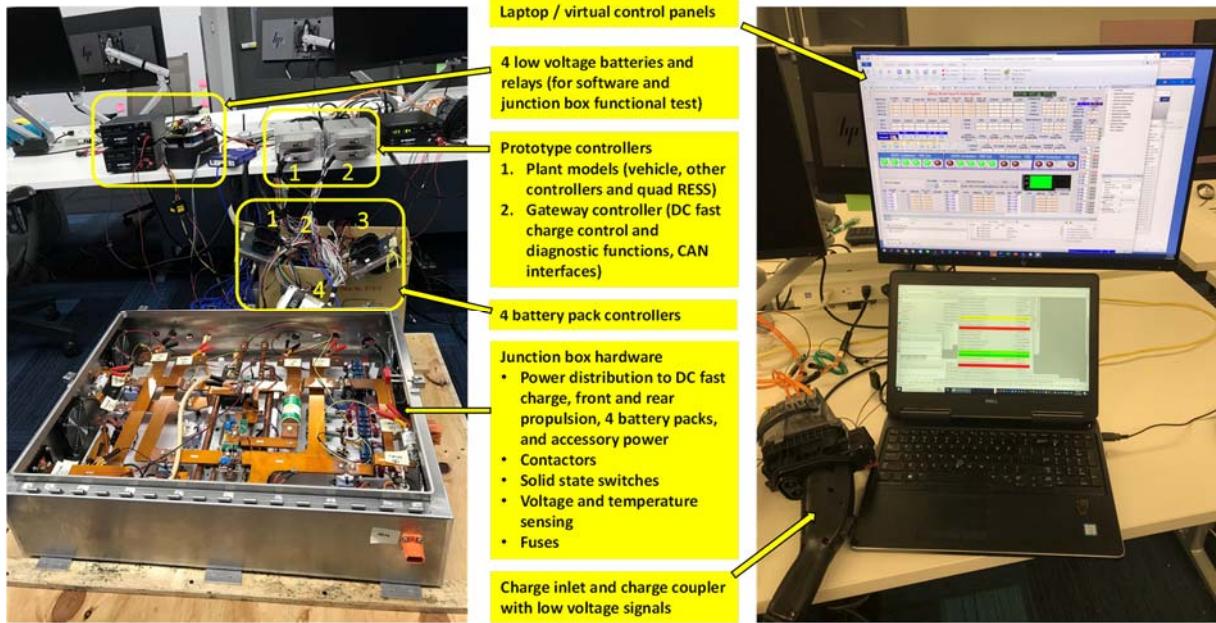

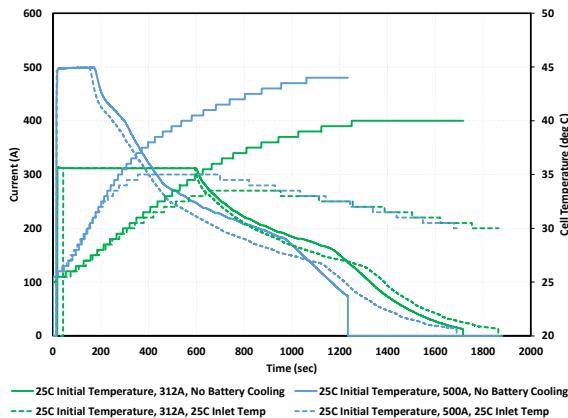

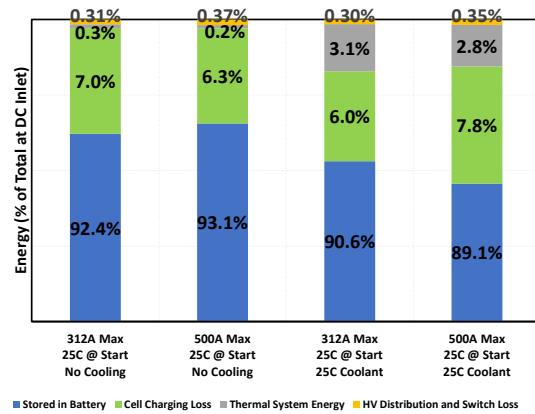

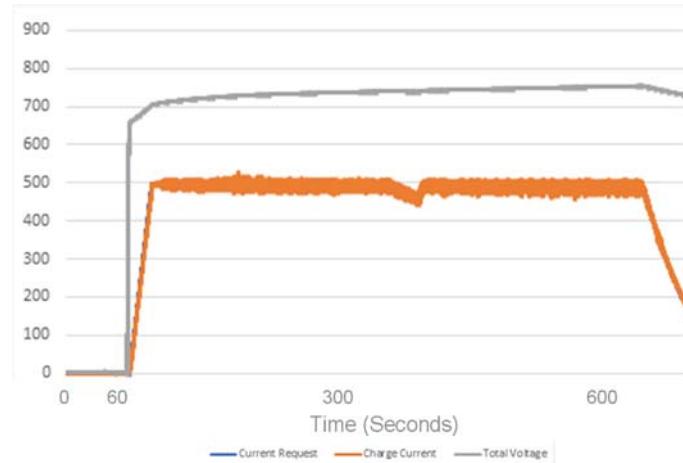

In parallel to the XFC development, General Motor has been developing the vehicle Rechargeable Energy Storage System (RESS), Charge Inlet, and Vehicle Integration Control Module (VICM). The team tested RESS candidate battery cell and verified the cells can take 3C charge and even higher rate for short time. The battery package is configured to receive 400-kW charge power, supporting the program objectives.

## Results

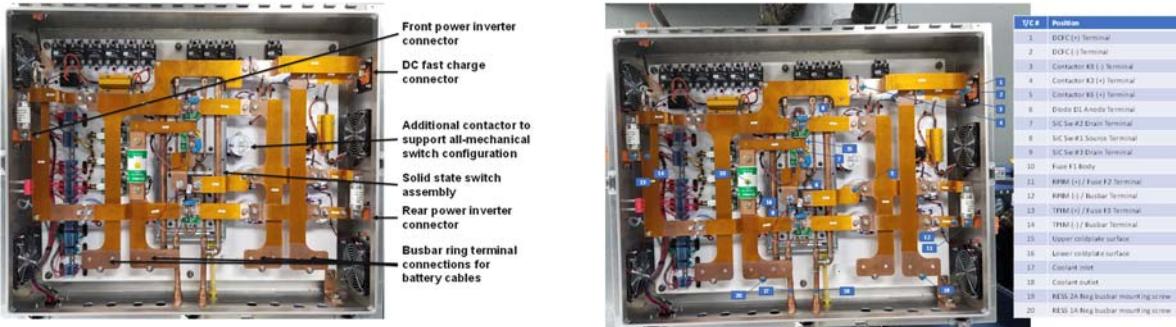

### Test Results from Delta's Livonia Lab

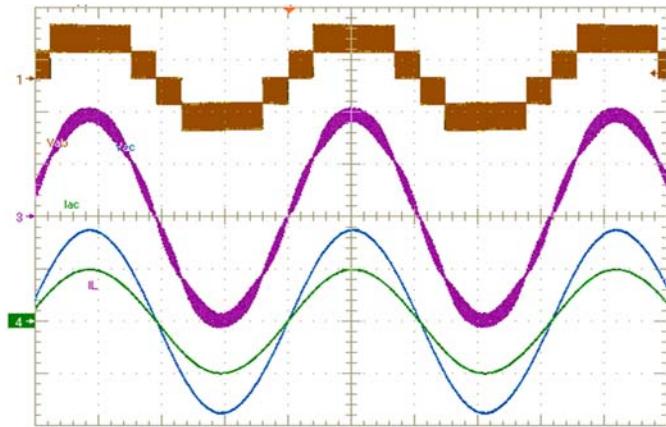

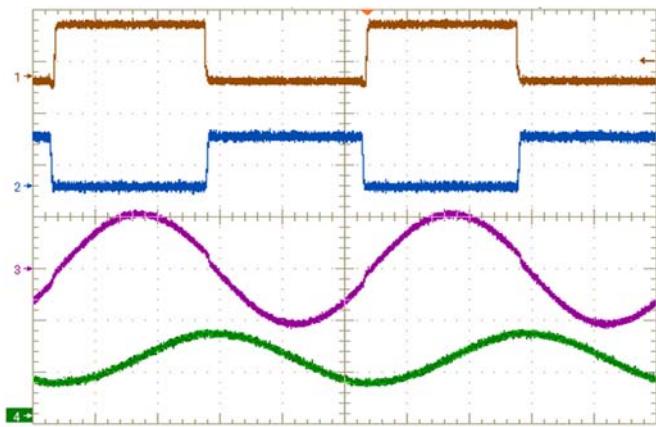

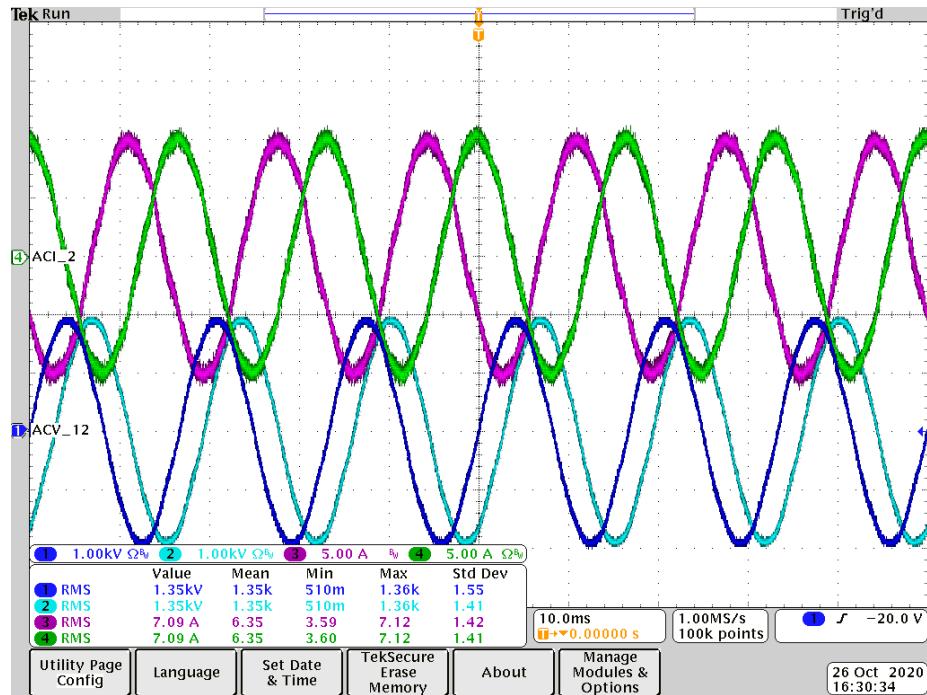

The SST module was tested on bench. The test result matches the design calculation very well and meets the specification. The peak efficiency is 97.8%. Figure I.1.1.4 shows one of the operation waveforms of the SST's AC/DC stage and Figure I.1.1.5 shows the operation waveforms of the SST's DC/DC stage.

Figure I.1.1.4 SST's AC/DC Stage Waveforms (CH1 brown:  $V_{ph}$ , CH2 blue:  $V_{AC}$ , CH3 purple:  $V_L$ , CH4 green:  $I_{AC}$ )

Figure I.1.1.5 SST's DC/DC Stage Waveforms (CH1 brown:  $V_{GS}$ , CH2 blue:  $V_{DS}$ , CH3 purple:  $I_{Lr}$ , CH4 green:  $V_{Cr}$ )

#### Buck Module

The Buck module was tested on bench. The result matches the design calculation and meets the specification. The peak efficiency is 99.2%.

#### 1-Phase Series SST and Buck Module Integrated Test

The four SST modules are integrated into the SST cabinet at center. The cabinet at left contains the line filter inductors, line voltage sensors and current sensors. The cabinet at right contains the SST controller and output filter. Figure I.1.1.6 shows the test system.

**Figure I.1.1.6 1-Phase Series SST and Buck Module Test Setup (up to 45-kW)**

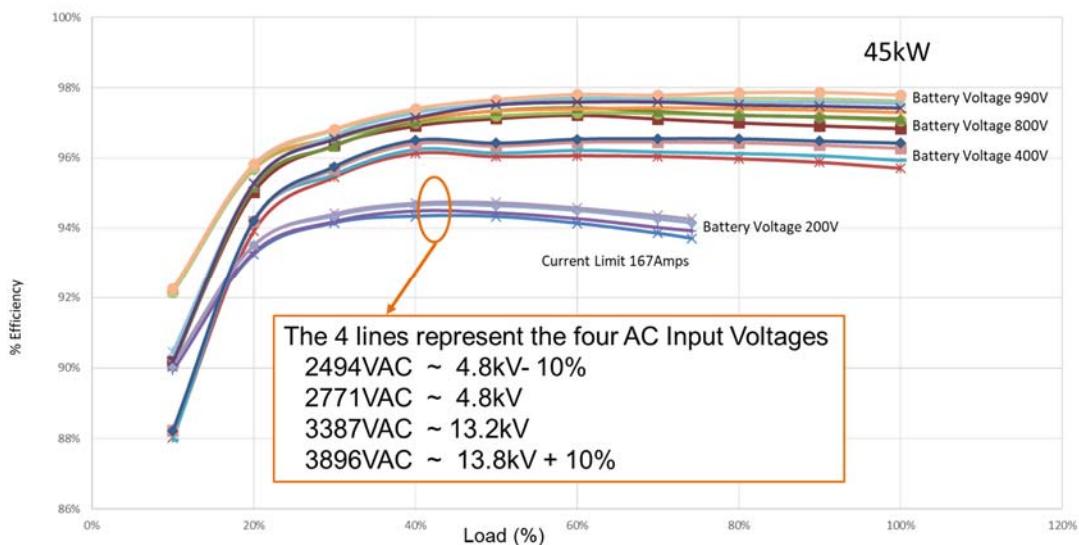

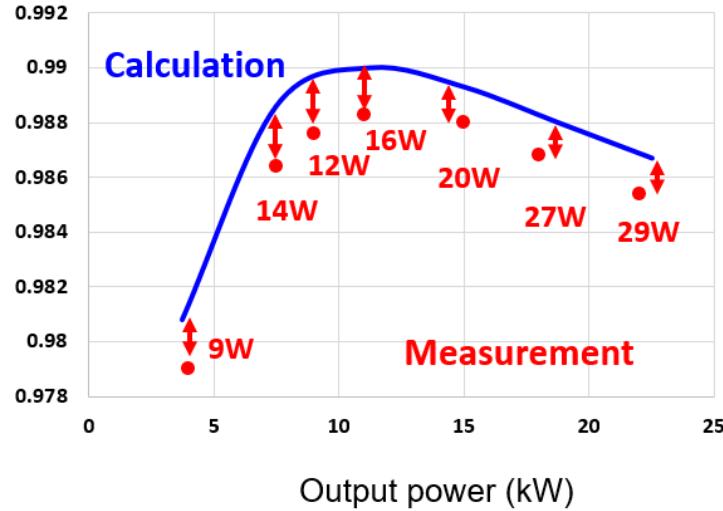

This system was tested from 4.5kW to 45-kW and in a wide range of input voltage and output voltage. Figure I.1.1.7 shows the efficiency test result.

**Figure I.1.1.7 1-Phase Series SST and Buck Module Efficiency Test Result (up to 45-kW)**

## Simulation and Study Results from Virginia Tech

## High frequency transformer with medium voltage insulation capability

### Transformer core material evaluation and selection.

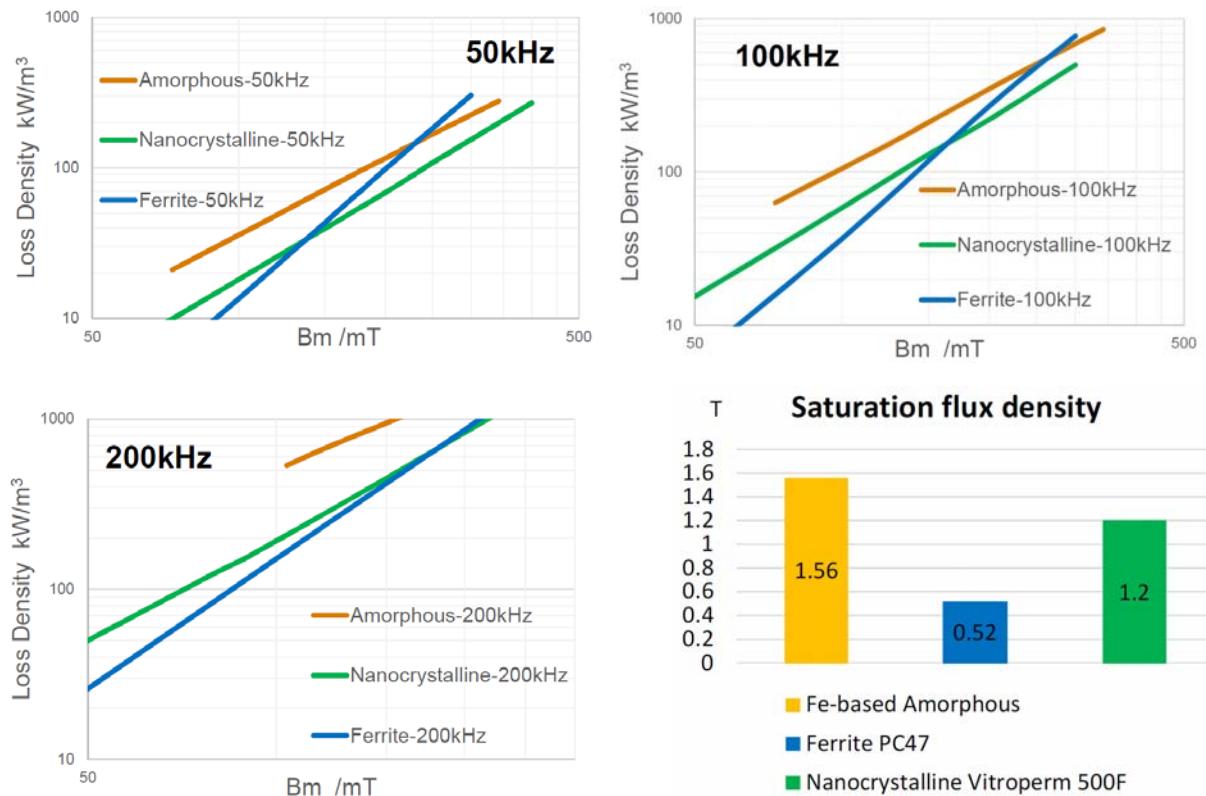

In high frequency applications, a good core material can provide high permeability as well as low core loss density. Three main material candidates for high frequency transformer are: amorphous, nanocrystalline, and ferrite. The core loss density of the three material candidates are compared at different frequency, as shown in Fig. 8. We can see that when the frequency is higher than 200 kHz, ferrite material is a very good candidate, especially considering that as the working frequency increases, the reasonable working flux density will decrease.

Fig. 8 Core material comparison

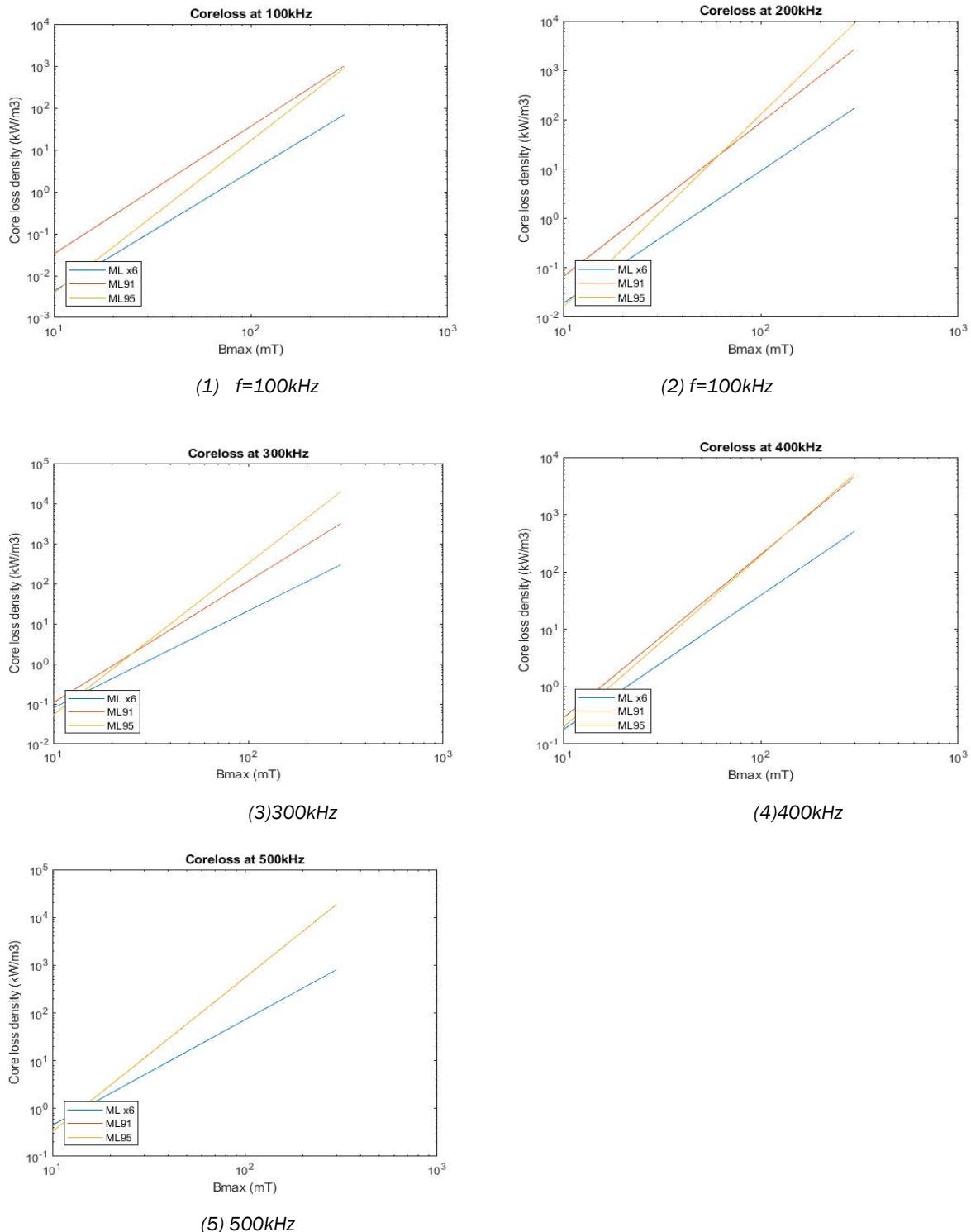

The newest materials we can have at this moment are: MLx6, ML91, and ML95. A comparison between these MnZn ferrite materials is also made. The test result is shown in Fig. 9 for different working frequencies.

Based on the test results, we will choose MLx6 as the core material for working flux density under 300mT and working frequency between 100 kHz and 500 kHz.

Fig. 9 Core loss density comparison between different MnZn ferrite material at 100~500kHz

## Transformer winding structure design with medium voltage insulation capability.

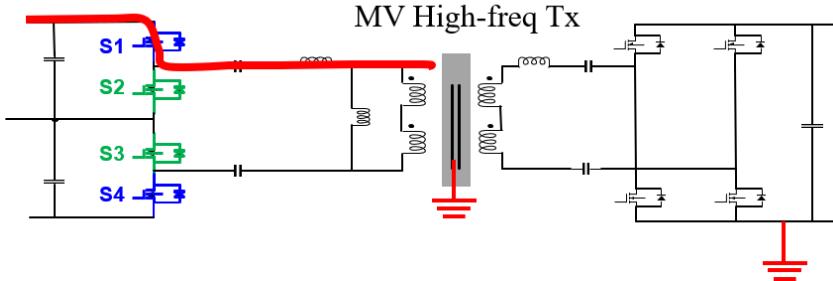

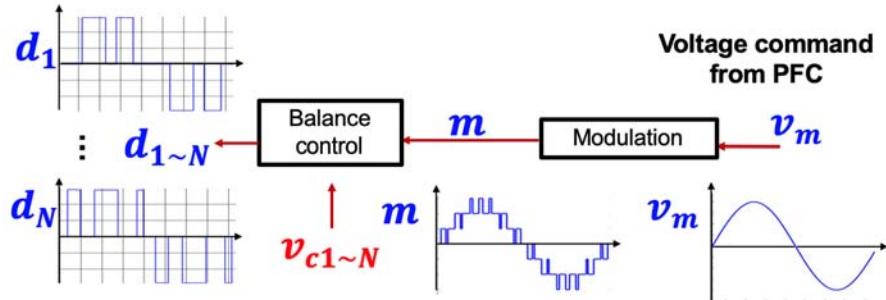

### System and module structure

The whole fast charger system is shown in Fig. 10 with a medium voltage (13.2kV) input and 1.1kV output voltage. The detail dc-dc circuit of one of the cascaded submodules is shown in Fig. 11. It is obvious that only the high frequency isolated transformer can provide insulation for overall system and it should be designed based on the input medium voltage. Insulation between primary high voltage winding and secondary low voltage winding and transformer core should be designed based on 13.2kV insulation requirement. However, insulation between secondary winding and core only need to be designed based on 1.1kV level.

Fig. 10 System Structure

High voltage

13.2kV

Fig. 11 DC/DC module

### Transformer structure

In this transformer design, UI core is selected and both primary and secondary windings on the two legs are connected in series.

Partial discharge (PD) is the most severe electrically driven degradation mode for ac insulation due to trapped air voids in the insulation system. If air is present inside or around the insulation, PD may happen in the air. The discharge will cause slow damage to the insulation that's next to the air volume. So, it is important to eliminate air voids around the high voltage insulation.

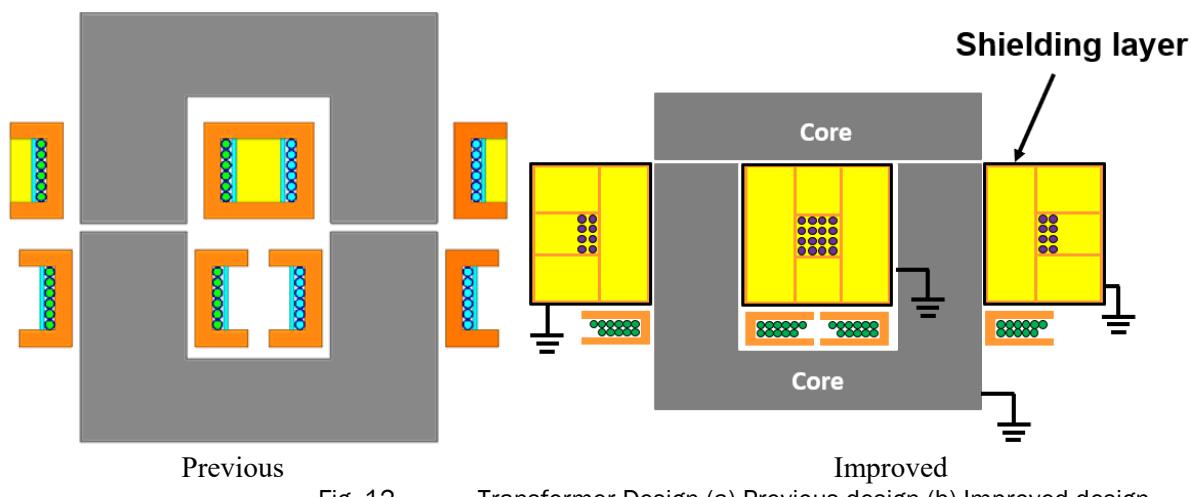

In previous transformer design, bobbin, tape, and epoxy are applied, as shown in Fig. 12. However, with this structure, there's many air voids around the primary side winding and it's almost impossible to eliminate these air voids. To eliminate the air voids between primary side winding and the insulation structure around it, we remove the bobbin and tape structure and then capsule the primary side winding with only epoxy.

Fig. 12 Transformer Design (a) Previous design (b) Improved design

To avoid partial discharge in the air between primary side winding/epoxy and core, we apply a shielding layer outside the epoxy. The shielding layer is also grounded and provides an electrical field shield. So, the electric field strength in the air is almost 0 and no partial discharge will happen.

Proper material is the key to the insulation encapsulation. For the dielectric strength, most insulation materials are at almost the same level (around 20kV/mm). Viscosity, thermal conductivity, curing time, and hardness are more crucial. From electric performance point of view, the insulation material should be with high thermal conductivity to avoid thermal issue. However, high thermal conductivity material always has high viscosity (e.g., 50-3182NC with 15000 cps and 1.66W/mK). It is hard for the air bubble to escape from the high viscosity insulation material. Partial discharge level will be higher than expectation with air bubble trapped in the insulation material. With low viscosity material, air voids can be easily eliminated from the insulation layer, which is beneficial to creating a partial discharge free insulation structure. Curing time is another important factor. The air bubble will not have enough time to escape from the insulation material with short cure time, which is harmful for the insulation manufacturing. From hardness point of view, gel is preferred rather than the hard epoxy after curing to avoid cracking which will damage the fragile insulation encapsulation.

The epoxy material candidates are listed in Table I. SilGel 612 is selected considering dielectric strength, thermal conductivity, and Viscosity. For a given material, the dielectric strength is a function of the thickness and can be estimated as:

$$\frac{E}{E_{ref}} = \left( \frac{D_{ref}}{d_{epoxy}} \right)^{0.4}$$

where  $E$  is the dielectric strength in Epoxy at given thickness  $d_{epoxy}$ , and  $E_{ref}$  is the dielectric strength at given testing thickness  $D_{ref}$ .

Insulation thickness is determined for 13.2kV application according to IEEE standard. Assume that the electric field in the epoxy is uniform. Then the thickness of epoxy can be calculated as:

$$\frac{48kV/d_{epoxy}}{23kV/mm} = 0.3 \times \left( \frac{3.175mm}{d_{epoxy}} \right)^{0.4}$$

Table I. Epoxy Material Candidates

| Insulation Material Candidate | 50-3182 NC                                | EPIC Resin R1055/H5083                | SilGel 612                            |

|-------------------------------|-------------------------------------------|---------------------------------------|---------------------------------------|

| Dielectric Strength           | 22 kV/mm                                  | 22.6 kV/mm                            | 23 kV/mm                              |

| Cure time                     | 85°C for 3-4 hours or 100°C for 2-3 hours | 25°C for 2 hours or 50°C for 100 mins | 25°C for 8 hours or 100°C for 15 mins |

| Thermal conductivity          | 1.66 W/mK                                 | 0.42 W/mK                             | 0.3 W/mK                              |

| Viscosity                     | 15,000                                    | 3,300                                 | 1,900                                 |

| Hardness after curing         | Hard                                      | Hard                                  | Soft                                  |

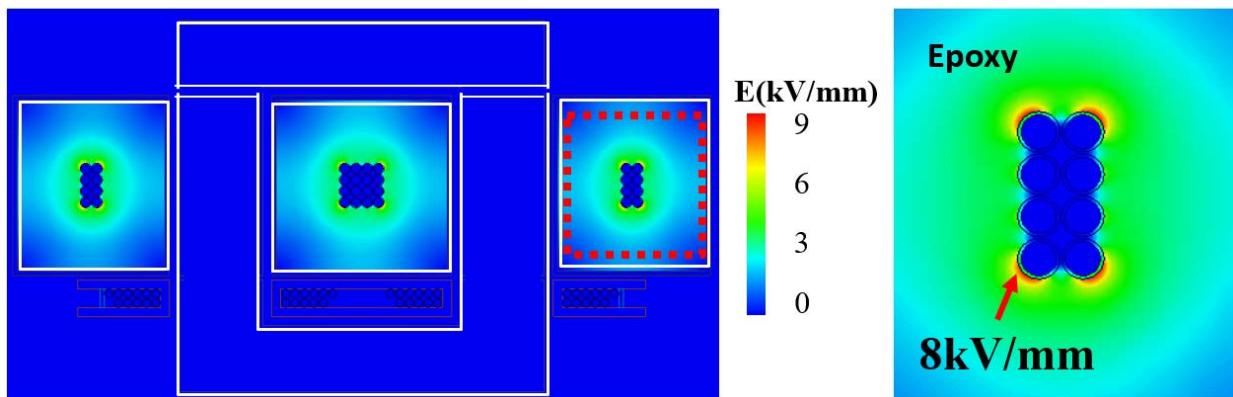

Insulation capability is preliminary verified in Finite Element Analysis (FEA) electric field simulation, as shown in Fig. 13.

Fig. 13 Electric field simulation result

From the simulation result, the highest electric field in the insulation material is no more than 8kV/mm, which satisfies the requirement of insulation.

### Termination Design

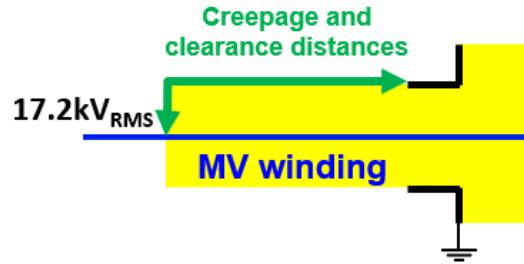

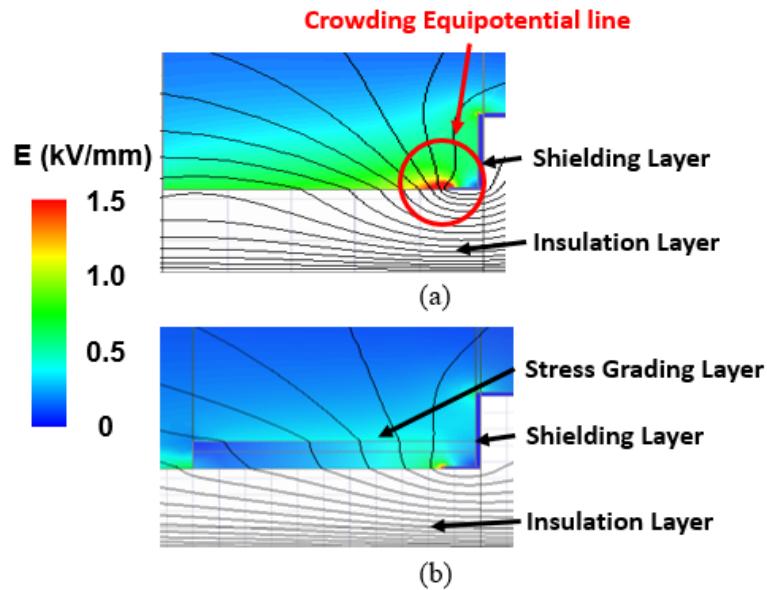

By applying the shielding layer, zero voltage potential is built on the surface of the winding encapsulation. Safe creepage and clearance distance is required between the high voltage primary side and the zero-voltage shielding, as shown in Fig. 14. However, the shielding layer's sharp fringes cause equipotential lines concentrating at the edge of the shielding layer on the termination sleeve, causing high electric field stress, as shown in Fig. 15(a). That also increases the possibility of generating partial discharge. A high permittivity layer is applied on the surface of the termination sleeves to solve this problem. This stress grading layer can be modeled as a series of RC network. Such method makes the equipotential line more uniform on the termination sleeve and lowers the electrical stress at the point of shield discontinuity by refracting the electrical stress. The stress grading layer allows the equipotential lines to spread out along the insulation interface of the termination sleeves, as shown in Fig. 15(b). By doing this, the surface stress of the termination is greatly reduced, which improves termination performance.

Fig. 14 HFT Termination Design

Fig. 15 Simulation result for termination design

(a) without stress grading layer, (b) with stress grading layer

### Litz wire's impact on partial discharge

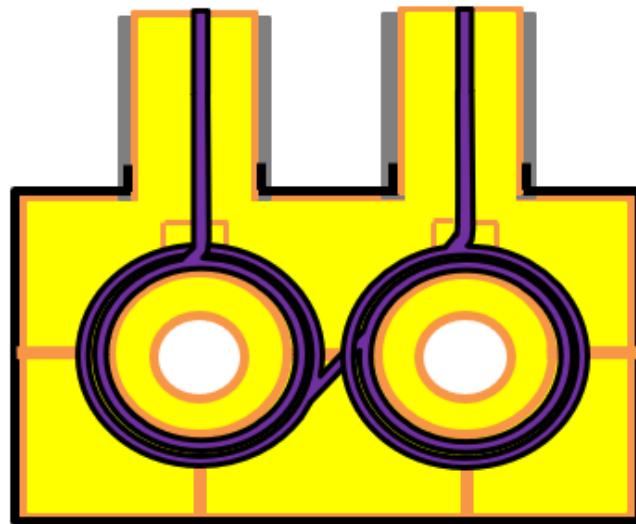

The air trap inside litz wire is another concern in this application and has a huge impact on the partial discharge test. Recently we noticed that the selection of litz wire insulation makes a big difference on the partial discharge inception voltage (PDIV). Fig. 16 shows the structure of the primary-side medium voltage winding with insulation capability.

Fig. 16 Structure of primary-side medium voltage winding with insulation

The tested PDIV is 8.2kV, which is far below 17.2kV as the standard indicates. Then several test results are compared to exclude two suspected reasons for partial discharge, either the sleeve of stress grading layer on termination or the air voids inside the insulation material (silicone). Finally, measurement results show that it is the insulation layer of the litz wire that makes a big difference. Previously we use the litz wire covered by a Teflon layer, as shown in Fig. 17(a). This kind of insulation layer has a high insulation level (1000V). However, also due to this Teflon layer, air voids are inevitable in the litz wire bundle. Then this air voids trapped in litz wire become the weak point when the whole medium voltage winding is under partial discharge test. By using another soft coating litz wire, as shown in Fig. 17(b), the air voids inside the litz wire bundle no longer exist because the liquid insulation material can now immerse through the soft coating and fill up the air voids inside a litz wire bundle. Experimental result shows that the medium voltage winding using the soft coating litz wire is partial discharge free at 17.2kV.

Fig. 17 (a)Litz wire with silk coating (b) Litz wire with FEP jacket

### Design and optimization of high frequency transformer

#### Transformer loss and size trade-off at given switching frequency

Previously, we have determined the core material, transformer structure, insulation material and litz wire gauge for a given switching frequency ( $f_s$ ), 200 kHz. Then the core loss ( $P_{core}$ ), winding loss ( $P_{winding}$ ), and transformer total volume ( $V_{Tr}$ ) can be calculated for each number of turns with given core loss density ( $P_v$ ).

#### Core Loss Model

To estimate the core loss, Steinmetz Equation is used as follows:

$$P'_v = k \cdot f_s^\alpha \cdot B_m^\beta$$

where  $P'_v$  is the core loss density under sinusoidal excitation.  $k, \alpha, \beta$  are constants from curve fitting data.  $f_s$  is the switching frequency of the sinusoidal waveform.  $B_m$  is the peak flux amplitude. For CLLC topology, the excitation on the transformer core is the square waveform, and the Rectangular Extension Steinmetz Equation is proposed to exactly predict core loss under the rectangular voltage excitation as follows:

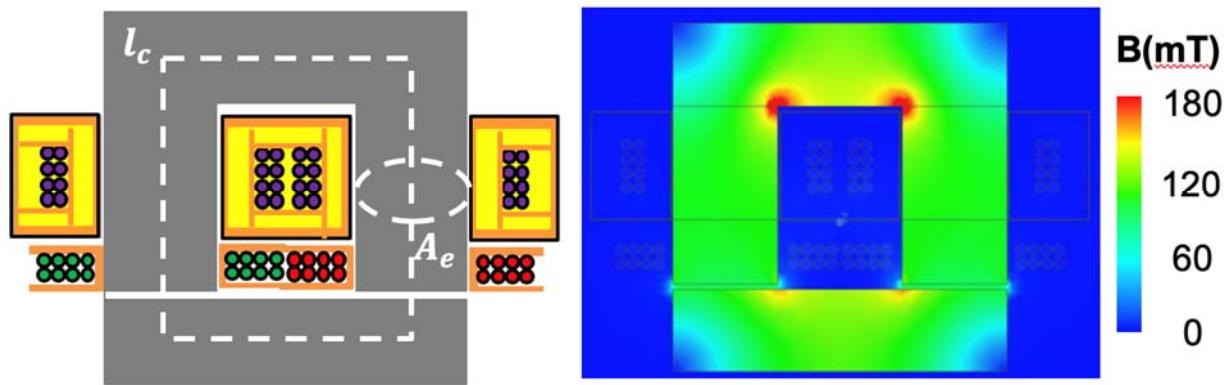

$$A_e = nV_0/(4N \cdot B_m \cdot f_s)$$

$$P_v = \frac{8}{\pi^2} k \cdot f_s^\alpha \cdot B_m^\beta$$

For cross section area of the core  $A_e$ , it is derived from the Faraday's Law. And the core loss is calculated by core loss density times core volume as shown below:

$$P_{core} = P_v \cdot A_e \cdot l_c$$

where  $V_o$  is the DC output voltage.  $n$  is the turns ratio.  $N$  represents the primary side turns number.  $l_c$  means magnetic loop length in the core.  $B_m$  is a function of  $P_v$  and  $f_s$ . Note that  $l_c$  is a function of  $A_e$  and  $N$ . Therefore, in order to calculate core loss, there are three design variables: turns number  $N$ , core loss density  $P_v$ , and switching frequency  $f_s$ .

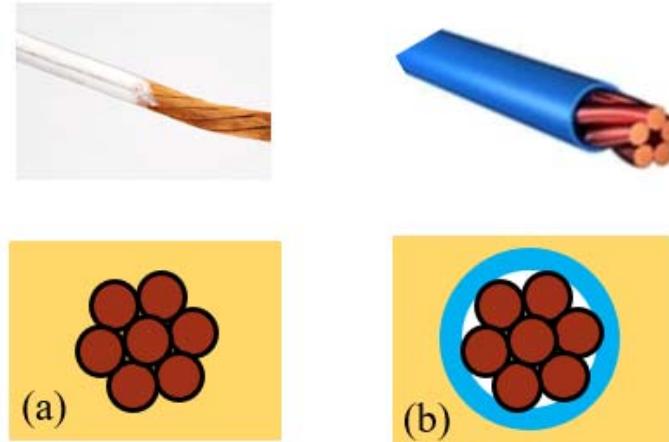

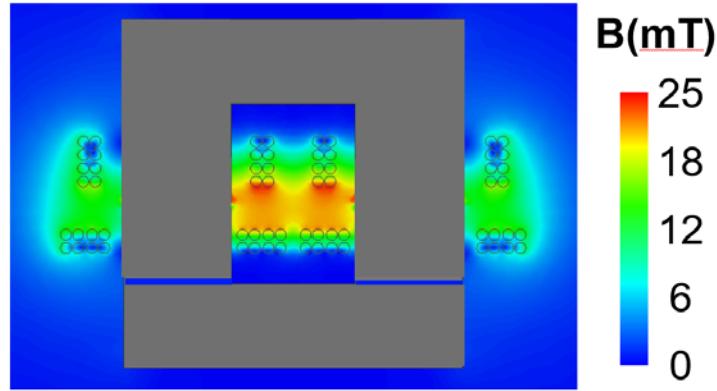

Such a method assumes magnetic flux distributes uniformly inside the core. To verify this assumption, an FEA simulation is built with  $N = 16$ ,  $P_v = 300 \text{ kW/m}^3$ , and  $f_s = 200 \text{ kHz}$ . The simulation and the result are shown in Fig. 18. Core loss is 24 W in the simulation and the calculated core loss is 25 W. The error between the calculation and simulation is negligible, which means the model is accurate and can be used for further analysis.

Fig. 18 Magnetic field distribution in the core.

### Winding Loss Model

Litz wire is widely used for the high frequency transformer. Litz wire strand AWG is selected based on operating frequency and manufacturer's recommendation. AWG 42 is

chosen for the 200-kHz application as an example. The equivalent AWG is selected as AWG 15 according to NPFA 70 National Electrical Code for a 15-kW 22-A RMS current application.

The winding insulation material is another critical component in medium voltage transformer design. The high dielectric strength is the first priority to achieve compact transformer winding design. For high frequency applications, the dissipation factor is also important for relatively low dielectric loss. High thermal conductivity is required to extract winding loss from insulation encapsulation. Material viscosity cannot be ignored during the fabrication process; it is easy for air cavity to be trapped inside high viscosity material. That increases the possibility for partial discharge. Three winding insulation material candidates are listed in TABLE II. SilGel 612 is finally selected for its low viscosity and high dielectric strength.

TABLE II WINDING INSULATION MATERIAL CANDIDATE COMPARISON

| Material candidate   | R1055/H5083 | 50-3182NC  | SilGel 612 |

|----------------------|-------------|------------|------------|

| Dielectric Strength  | 22.6kV/mm   | 22kV/mm    | 24kV/mm    |

| Dissipation Factor   | 0.022       | 0.018      | 0.008      |

| Thermal Conductivity | 0.42W/(mK)  | 1.66W/(mK) | 0.2W/(mK)  |

| Viscosity            | 3,000cps    | 15,000cps  | 1,900cps   |

To calculate Litz wire winding loss, the squared field derivative (SFD) method is used for eddy current power dissipation in turn  $j$ , with assumptions that the magnetic field remains constant inside each Litz wire strand and no eddy current flows between different strands.

$$P_{eddy,j} = \frac{\pi N_s l_j d_s^4}{64 \rho_c} \overline{\left( \frac{dB}{dt} \right)^2}_j$$

where  $N_s$  is the strands number,  $l_j$  is the winding length for turn  $j$ ,  $d_s$  is the strand diameter,  $\rho_c$  is the conductivity for copper,  $\langle \cdot \rangle_j$  is the space average for turn  $j$ , and  $\bar{x}$  is the time average.  $dB/dt$  can be obtained from the simulation, as shown in Fig. 19.

Fig. 19 Magnetic field distribution in the core.

The winding loss with non-eddy current effect can be calculated easily with  $I^2R$ , and the total winding loss is the sum of eddy current loss and non-eddy current loss as below.

$$P_{non-eddy,j} = \frac{4\rho_c l_j}{N_s \pi d_s^4} I_{rms}^2$$

$$P_{winding} = \sum_{j=1}^N \left( \frac{\pi N_s l_j d_s^4}{64\rho_c} \langle \overline{\left( \frac{dB}{dt} \right)^2} \rangle_j + \frac{4\rho_c l_j}{N_s \pi d_s^4} I_{rms}^2 \right)$$

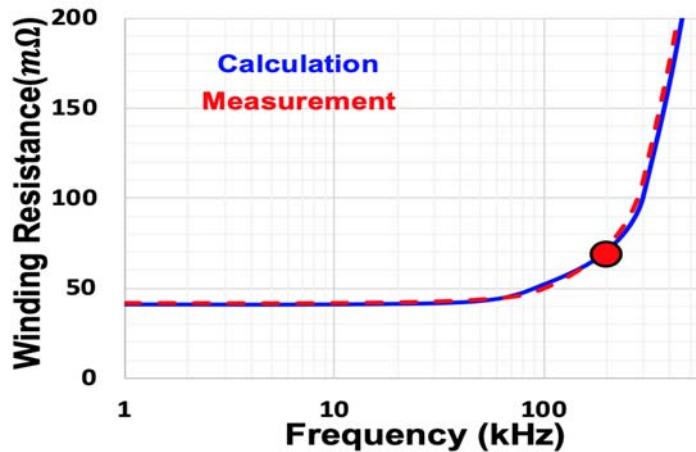

In winding loss,  $dB/dt$  is a function of switching frequency  $f_s$ .  $l_j$  is a function of cross section area  $A_e$ , which is related to turns number  $N$  and core loss density  $P_v$ .  $N$ ,  $P_v$ , and  $f_s$  are still the design parameters for winding loss. To verify this model, a transformer prototype is built, and the winding resistance is measured through an impedance analyzer. Fig. 13 indicates that the calculated winding resistance matches with the measurement.

Then the loss ( $P_{Tr}$ ) is the sum and winding loss.

Fig. 20 Winding Resistance verification.

transformer of core loss

$$P_{Tr} = P_{core} + P_{winding}$$

After selecting the core material, winding AWG, winding equivalent AWG, and insulation material, there are still three design variables, including turns number  $N$ , core loss density  $P_v$ , and switching frequency  $f_s$ . Based on the core loss and the winding loss model, a transformer optimization method is proposed for multiple design objectives, including core loss, winding loss, and transformer volume. In order to have a clear picture on the impact of each design variable, a 3-step optimization method is utilized.

### Transformer Optimization Steps

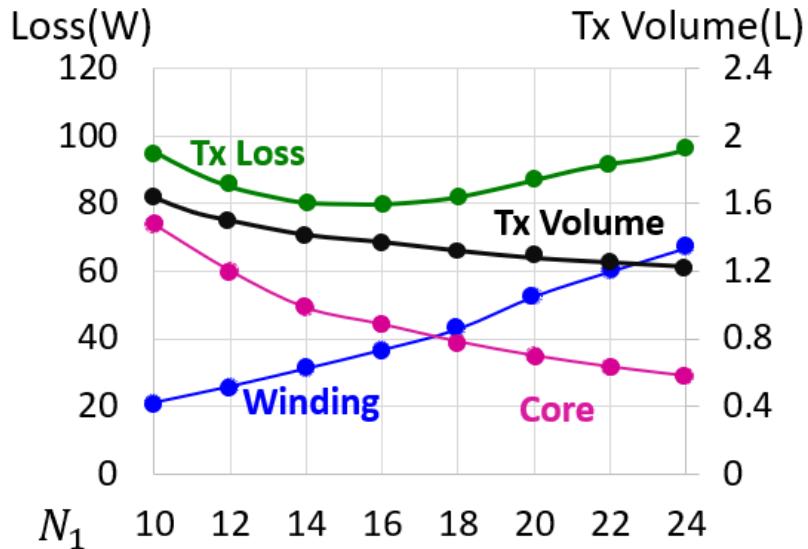

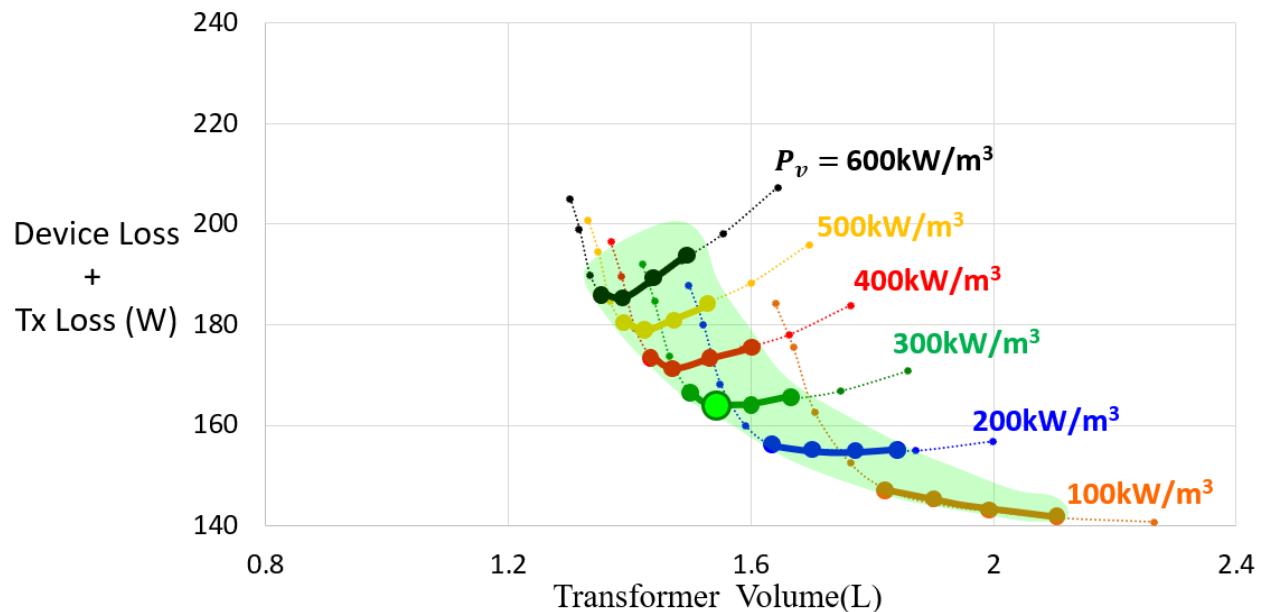

**Step #1:** Sweep turns number ( $N$ ) with given  $P_v = 300 \text{ kW/m}^3$  and  $f_s = 200 \text{ kHz}$

The transformer core loss, the winding loss, and the transformer volume with a swept  $N$  are plotted in Fig. 21. With given  $P_v$  and  $f_s$ , core loss will decrease when  $N$  increases. We learn that  $A_e$  will shrink with the increment of  $N$ , and thus core loss reduces. For winding loss, a larger turns number will increase the total length of the winding, leading to higher winding loss. From the volume point of view, the height of the transformer will be higher with the turns number increasing; however, the width and the length will decrease due to smaller  $A_e$ . The transformer volume will be smaller with larger turns numbers in the interested turns number range (8-24) obtained from the loss calculation.

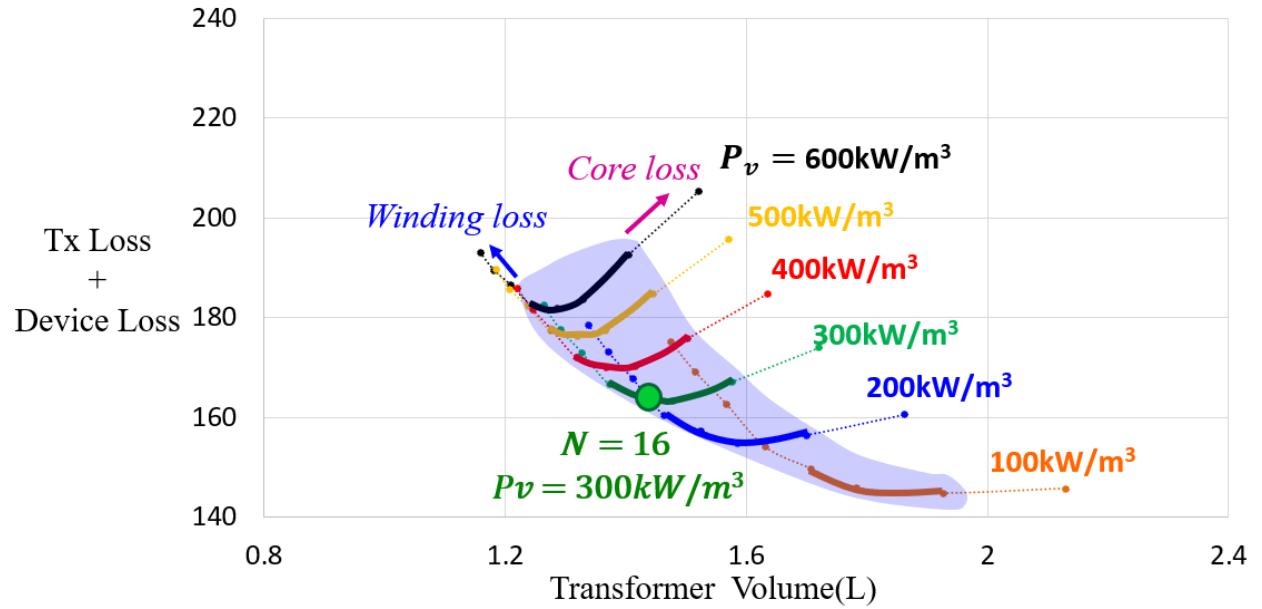

**Step #2:** Sweep  $N$  and  $P_v$  with given  $f_s = 200 \text{ kHz}$

*Fig. 16* Fig. 21 shows the design result when considering only the one parameter  $N$ . Adding core loss density and switching frequency information to the same plot will be complicated to read; therefore, a plot with total loss as the vertical axis and volume as the horizontal axis is proposed for better clarity. The transformer loss and device loss are both taken into consideration in this plot. That is because switching frequency will impact device loss. Bearing this in mind, total loss will be unbiased when switching frequency impact is taken into consideration. Two trade-offs are considered in the design process. The first trade-off is to find the best total loss and transformer volume. This is followed by the trade-off between core loss and winding loss. Insulation encapsulation always has lower thermal conductivity, which means lower winding loss is favored. Because of this, 24 turns cases will be ignored in the following analysis.

Core loss density from  $100 \text{ kW/m}^3$  to  $600 \text{ kW/m}^3$  are taken into consideration in order to evaluate the core loss density impact. A further simplification is made by hiding detailed design points. The result is shown in Fig. 22. Each line represents one core loss density. For a given core loss density, the turns number decreases from the left side to right. At the low core loss density region ( $P_v = 100 \text{ kW/m}^3$ ), the transformer volume increases while there is almost no benefit on loss. At the high core loss density region ( $P_v = 600 \text{ kW/m}^3$ ), the total loss is higher but the transformer volume is almost the same. According to such a phenomenon, the design region is restrained to  $P_v = 200 - 600 \text{ kW/m}^3$ . Among these four curves, the valley point for each curve is selected to have

smaller loss. Another curve can be drawn based on these four valley points, and the design region can be finally selected around such curve.

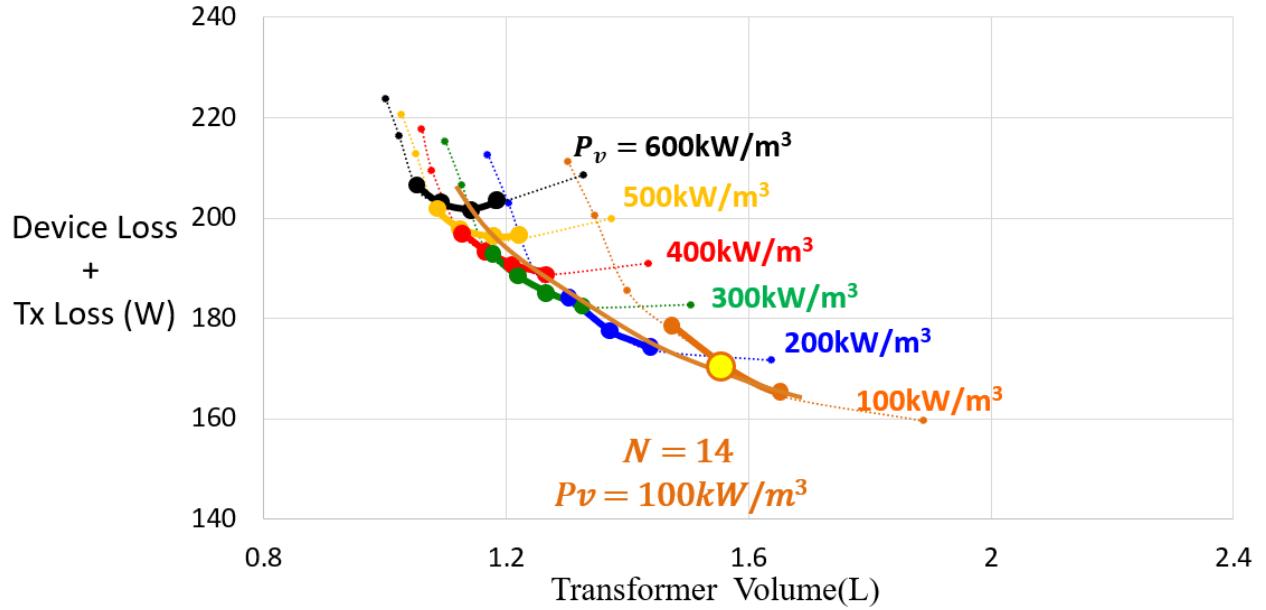

### Step #3: Sweep $N$ , $P_v$ and $f_s$

To explore the impact of switching frequency from 100 kHz to 300 kHz, the same methodology is utilized based on Step #2, as shown in Fig. 23 and Fig. 24. For each switching frequency, a design region could be selected. Five design regions can be plotted in the same plot to have a better understanding of how switching frequency impacts transformer design. This is shown in Fig. 25. One point can be selected for each frequency, and the final design region can be figured out. It is clear to see that when switching frequency is less than 200 kHz, the volume increases with almost the same loss. At high frequency region ( $f_s > 300$  kHz), total loss increases rapidly; however, there is no benefit from the transformer volume point of view. At 100 kHz, the core volume impacts the total volume a lot. Although low frequency will lead to lower eddy current loss and smaller core loss density with certain  $B_m$ , the core volume increases due to low frequency and winding length also increases. Thus, there is almost no benefit on loss reduction. For higher frequency range, both winding loss and core loss will increase at such a switching frequency. Although the core volume will decrease with the increasing switching frequency, the insulation volume cannot be compressed.

Fig. 21 Transformer loss and volume for given frequency and given core loss density

Fig. 22 Transformer loss and size trade-off at 200k Hz

Fig. 23 Transformer loss and size trade-off at 100k Hz

Fig. 24 Transformer loss and size trade-off at 300k Hz

Fig. 25 Transformer loss and size trade-off at different frequencies

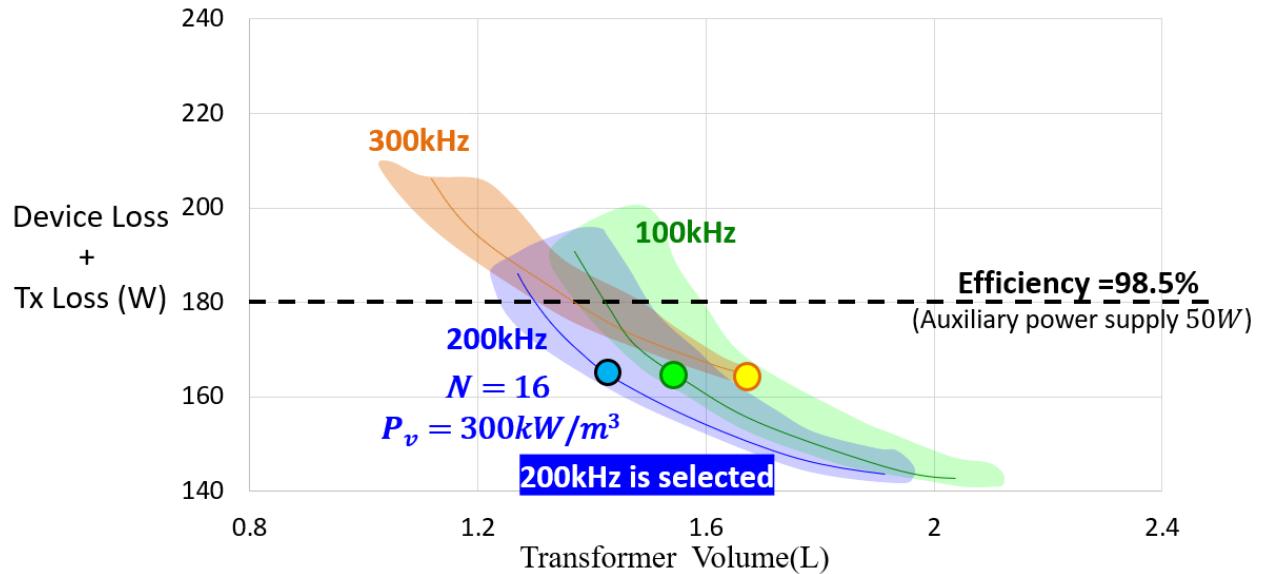

### Transformer design result

To determine the design point, the transformer loss and device loss are added together to get the total loss of the DC/DC converter, as shown in Fig. 25. The design point is picked according to total loss and transformer volume tradeoff.

To achieve a total efficiency of 98.5% and considering that the loss of auxiliary power supply is around 50W, the maximum total loss shall be less than 180W. If we further

increase the transformer volume, the total loss will drop. But the benefit on loss becomes very limited while the transformer volume increases significantly. Thus, the design point is selected to be  $P_{Tr} = 80W$  and  $V_{Tr} = 1.37L$ . Table III shows the result of this transformer design.

Table III. Transformer design result

| Design Parameter                   |                       | Values    |

|------------------------------------|-----------------------|-----------|

| <b>Switching frequency (fs)</b>    |                       | 200kHz    |

| <b>Device Loss</b>                 |                       | 100W      |

| <b>Core material</b>               |                       | MLx6      |

| <b>Core Loss Density</b>           |                       | 300 kW/m3 |

| <b>Magnetic Flux Density</b>       |                       | 153mT     |

| <b>Litz wire</b>                   | <b>AWG</b>            | 42        |

|                                    | <b>Strands Number</b> | 525       |

| <b>Number of Turn</b>              | <b>N1</b>             | 16        |

|                                    | <b>N2</b>             | 22        |

| <b>Tx</b>                          | <b>Winding Loss</b>   | 36W       |

|                                    | <b>Core Loss</b>      | 44W       |

|                                    | <b>Total Loss</b>     | 80W       |

|                                    | <b>Total Volume</b>   | 1.37L     |

| <b>Magnetizing Inductance (Lm)</b> |                       | 100uH     |

#### Manufacturing Process and Special Consideration For The Insulation Encapsulation

Besides the insulation structure design, the manufacturing for the insulation is also essential to creating an PD-free winding encapsulation. Different from the line frequency bulky transformer, the HFT has a much smaller volume. It is hard to use commercially available manufacturing process to make the insulation due to volume restrict. Many researchers

provide manufacturing process solution which are complicated. A relatively simple method is purposed in this chapter to create a PD-free insulation encapsulation.

A 3D-printed bobbin is used as the fixture to leave enough insulation thickness between the primary side winding and the zero potential grounded shielding. After wind the winding on the bobbin, the winding and bobbin are placed in another 3D-printed mold to create a sealed winding encapsulation. Insulation

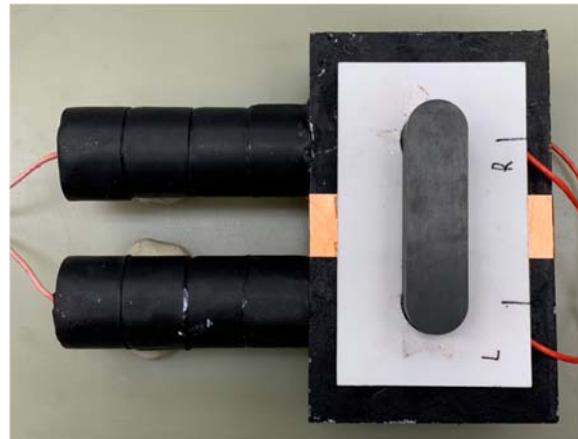

material Wacker SilGel 612 is filled up the winding unit from two terminals of the transformer. To create a partial discharge free transformer, vacuum pressure impregnation (VPI) process is applied. The winding unit with insulation material is placed in a vacuum chamber, as shown in Fig. 26. The air bubble in the insulation material will be squeezed out with the pressure gradually down to 50mbar in the vacuum chamber. If the pressure is too low in the vacuum chamber, the air bubble in the insulation material escapes fast and flows out from the winding unit. Also, a small vibrating table is placed in the chamber to vibrate the winding unit in order to eliminate air cavity inside the winding unit to achieve partial discharge free. The vacuum chamber is heated to 60 °C in half an hour. Which makes the air bubble easy to escape from the winding units with relatively high temperature. After the air cavity is removed, the winding unit is cured for 1 hours at 60 °C. Semi-conductive shielding layer is sprayed on the surface of the winding encapsulation with desired thickness except termination sleeves. Finally, the stress grading tape should be coated on the surface of the termination sleeves with minimized air cavities. The assembled transformer is shown in Fig. 27.

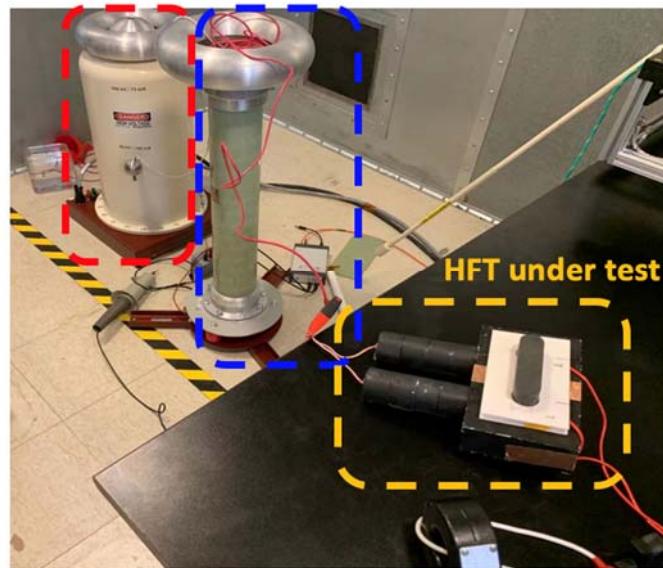

### **Hardware Prototype and Experimental Evaluation**

The transformer prototype is shown in Fig. 27. The secondary side winding is inside the white bobbin on the top. The primary side winding and the insulation silicone gel is covered by the black shielding. A copper tape is used to ground the shielding layer and the core. Thanks to the grounded shielding (in Black), there is no space between the primary side winding and the secondary side winding. The space between winding can core is also minimized. In this case, the space utilization is as much as possible and the volume can be shrunk from insulation point of view. The other black parts on the termination sleeve is the stress grading tape.

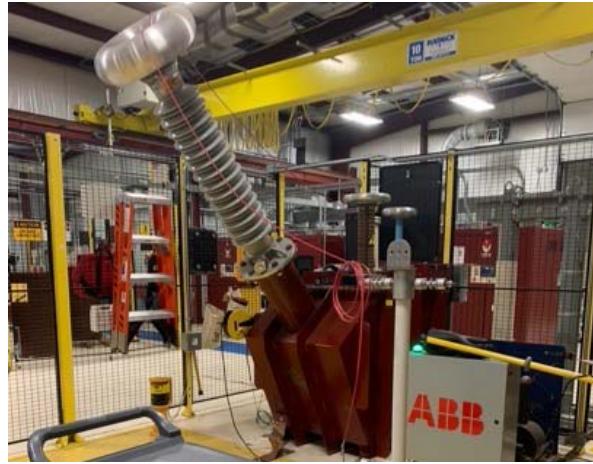

Fig. 26 Vacuum chamber for VPI

The applied voltage test as the overvoltage test is conducted based on IEEE C57.12.01. For the applied voltage test, the secondary side winding, shielding, and the core are all grounded. The primary high voltage winding is firstly shorted and then gradually applied 34 kV RMS line frequency medium voltage. The test setup is shown in Fig. 28. The voltage level is kept at 34kV RMS for 60 second in the test. During the test, there is no voltage breakdown in the HFT. The transformer prototype can pass such test.

Fig. 27 Transformer prototype for the 15kW CLLC with 13.2kV input level

Fig. 28 Line frequency transformer for 34kV applied voltage test

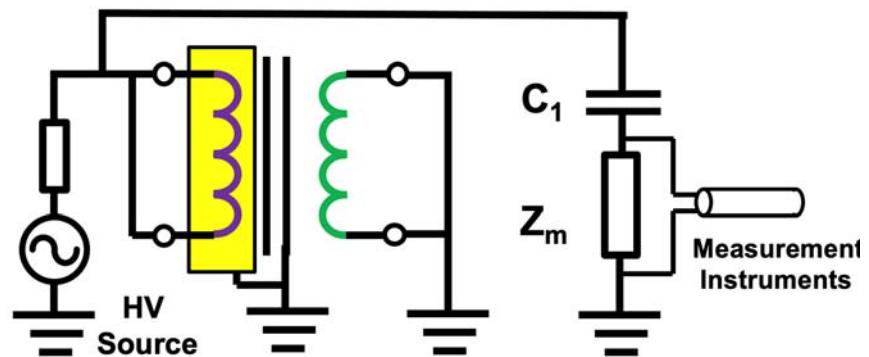

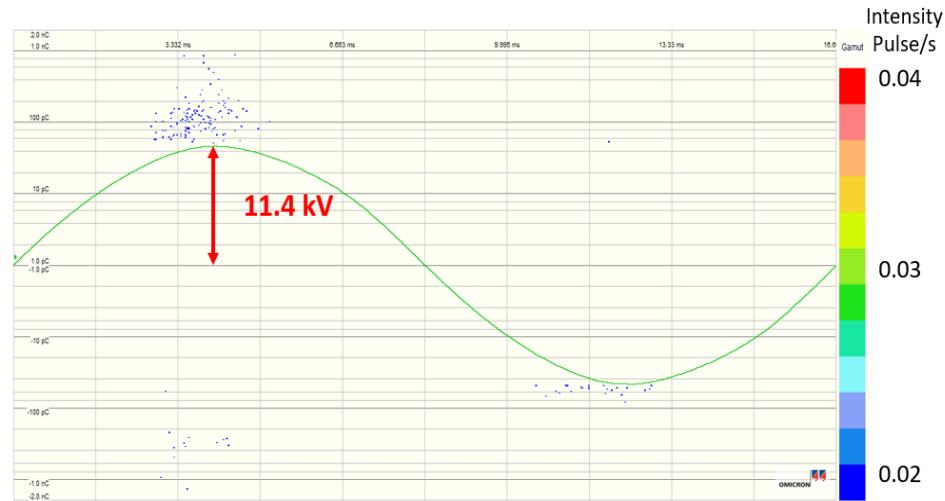

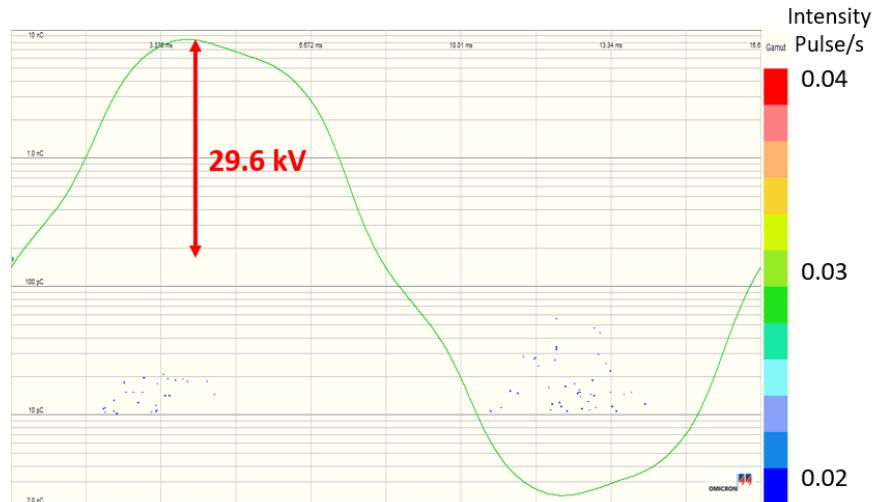

The partial discharge test is done to verify the partial discharge level for the HFT. The partial discharge test setup is shown in Fig. 29 and the equivalent circuit is shown in Fig. 30. In the partial discharge test, the difference between transformer with different Litz wire types is shown in Fig. 31 and Fig. 32. The test result for the transformer with FEP jacket is shown in Fig. 31. The partial discharge inception voltage occurs at 11.4kV peak (8.2kV RMS). However, using silk coating Litz wire instead of FEP jacket can lift the partial discharge inception voltage to 29.6kV peak (20.8kV RMS) under same manufacturing condition. The experimental result indicates that the silk coating Litz wire is more suitable for such medium voltage high frequency applications. Based on the standard, the partial discharge level at 17.2kV RMS ( $1.3V_o$ ) after 210 second is less than 10pC. The HFT can pass the partial discharge test.

60Hz Transformer      PD Measurement

Fig. 30 Equivalent circuit for partial discharge test

Fig. 31 Partial discharge test result for transformer with Litz wire with FEP jacket

Fig. 32 Partial discharge test result for transformer with Litz wire with silk coating

## High frequency high voltage three-level resonant converter with SiC MOSFET

### High frequency driving circuit with high dv/dt immunity

One of the most challenging aspect of the gate driving circuit design for SiC device is its ability to deal with the noise issue related to high dv/dt due to the ultra-fast switching capability of SiC devices. The noise path will be identified and special technique will be used to minimize noise amplitude. The gate drive solution for SiC device will achieve high dv/dt

immunity, high driving capability, and small propagation delay. The device we will use is FF23MR12W1M1\_B11 for the primary side and C3M0030090K for the secondary side. (See details in the last section about device selection.)

## 1EDI20H12AH Driver

The 1EDI20H12AH is a 1200-V galvanically isolated single-channel wide body gate driver with a small footprint for quick design-in cycles. It can deliver  $\pm 2.0$  A output current for high speed devices, like the FF23MR12W1M1\_B11.

The integrated galvanic isolation between control input logic and driving output stage grants additional safety. Its wide input voltage supply range supports the direct connection of various signal sources like DSPs and microcontrollers. The separated rail-to-rail driver outputs simplify gate resistor selection, save an external high current bypass diode and enhance dv/dt control. Based on Infineon's coreless transformer technology, the driver enables a benchmark-setting minimum common mode transient immunity (CMIT) of 100kV/us

## Switching performance evaluation for SiC MOSFETs

### Device loss evaluation and device selection

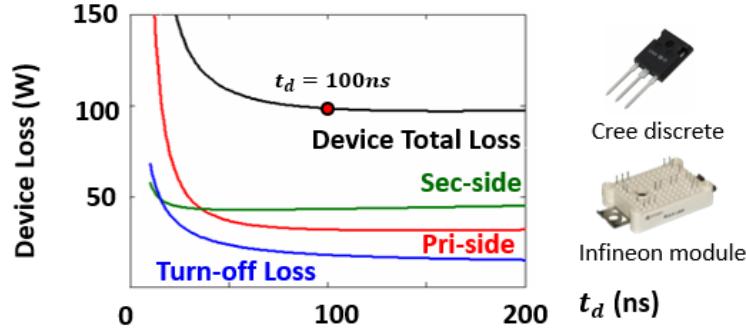

Since that in CLLC resonant converters, we can always achieve ZVS turn on for both primary and secondary sides, and ZCS turn off for secondary side, the total device loss will be the sum of conduction loss and driving loss on both sides, and turn-off loss on primary side, as shown below:

$$P_{total} = P_{conduction} + P_{driving} + P_{turnoff}$$

$$P_{conduction} = 4 \times (I_{dev\_pri}^2 \times R_{dson\_pri} + I_{dev\_sec}^2 \times R_{dson\_sec})$$

$$P_{driving} = 4 \times f_{sw} \times (Q_{g\_pri} \times V_{gs\_pri} + Q_{g\_sec} \times V_{gs\_sec})$$

$$P_{turnoff} = 4 \times f_{sw} \times E_{off(eq)}$$

where,

$I_{dev}$  is the RMS value of the current through a device;

$R_{dson}$  is the Drain-source on resistance;

$f_{sw}$  is the switching frequency;

$Q_g$  is the total gate charge of a device;

$V_{gs}$  is Gate-source voltage of a device;

$E_{off(eq)}$  is the compensated turn off energy of a device;

pri and sec stands for the primary side and secondary side respectively.

Assume that:

- 1)  $i_{Lr}$  is a sinusoidal waveform

- 2)  $i_{Lm}$  has a constant value during the dead-time  $t_d$  and has a constant slew rate in other time.

With the assumptions above, we can get the  $I_{dev\_pri}$  and  $I_{dev\_sec}$  as shown below:

$$I_{dev\_pri} = \frac{V_o}{8nR_L} \sqrt{\frac{n^4 R_L^2 T_s^2}{L_m^2} + 4\pi^2 + \frac{16\pi^2(T_0 t_d + t_d^2)}{T_0^2}}$$

$$I_{dev\_sec} = \frac{\sqrt{3}V_o}{12\sqrt{2}\pi R_L} \sqrt{\frac{(5\pi^2 - 48)n^4 R_L^2 T_o^3}{L_m^2(T_0 + 2t_d)} + \frac{12\pi^4 T_0}{T_0 + 2t_d} + \frac{48\pi^2(T_0 t_d + t_d^2)}{T_0(T_0 + 2t_d)}}$$

$$i_{Lm\_max} = \frac{nV_o T_s}{4L_m}$$

Then, the total loss is a function of  $t_d$ . For a given switching frequency, if  $t_d$  is too large, conduction time will decrease, leading to a higher conduction current and so is the conduction loss. If  $t_d$  is too small, then there will be large circulating energy, which also reduces the whole efficiency. So, we can minimize the total loss by choosing an appropriate  $t_d$ .

For the secondary side device, there is no switching loss. So, we will choose the device with the minimum  $R_{dson}$  value. Based on our most recent survey, we choose C2M0045170D from CREE. For the primary side, Table IV shows the three primary side device candidates and secondary side device selection according to our most recent survey:

Table IV: A Specification Three Level Resonant Converter

|           | Part No.         | Vds(V) | Rdson (@100°C) | Qg (nC) | Coss(pF) |

|-----------|------------------|--------|----------------|---------|----------|

| Primary   | C3M0075120K      | 1200   | 86 m ohm       | 51      | 58       |

|           | FF23MR12W1M1_B11 | 1200   | 30 m ohm       | 124     | 220      |

|           | IMZ120R045M1     | 1200   | 55 m ohm       | 62      | 115      |

| Secondary | C2M0045170D      | 1700   | 80 m ohm       | 188     | 171      |

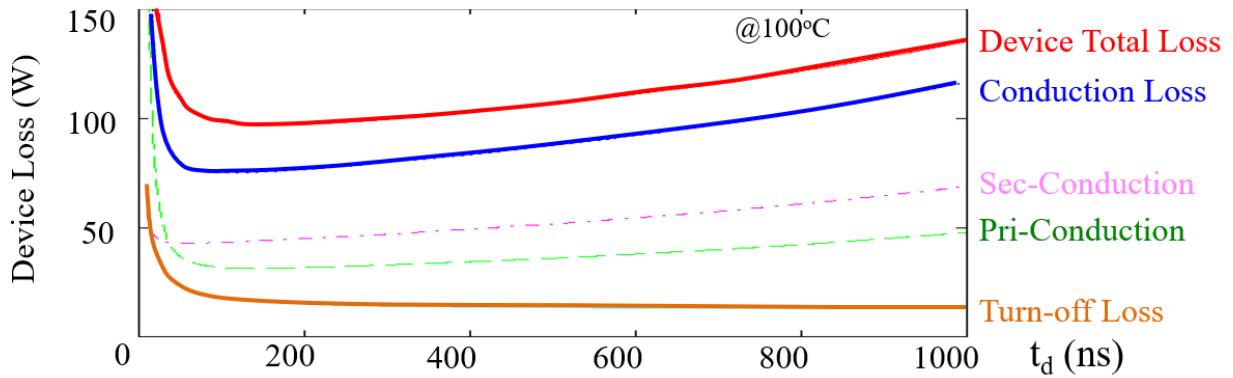

Fig. 33 Device losses versus deadtime

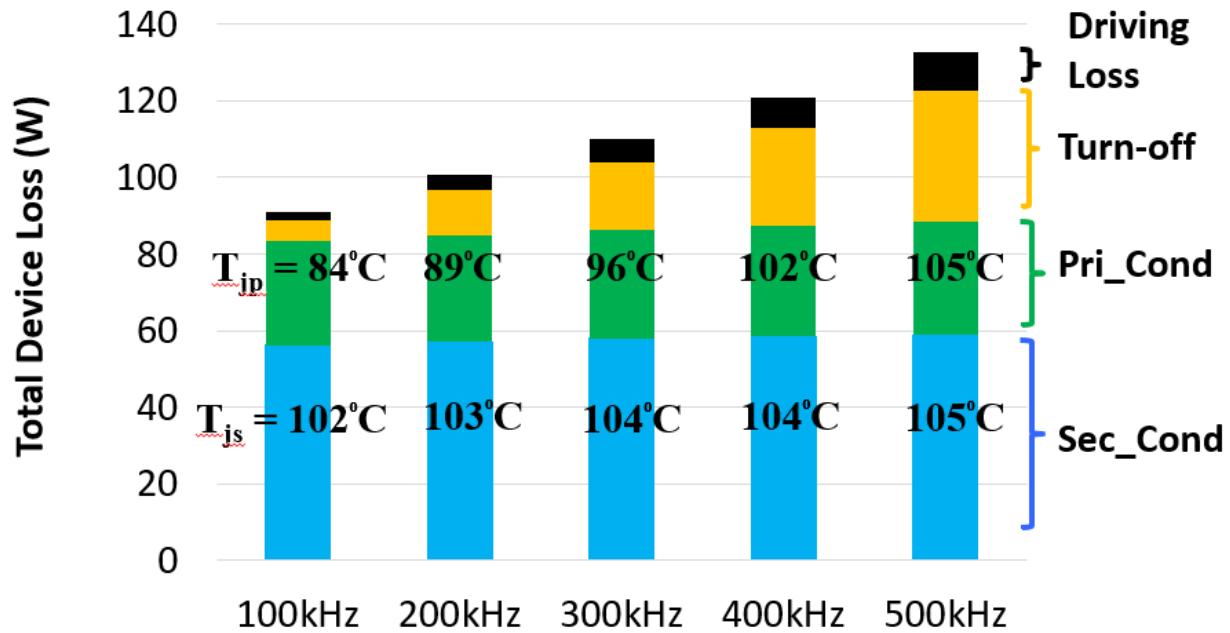

At  $f_s=200\text{kHz}$ , device loss is calculated versus deadtime  $t_d$ . The result is shown in Fig. 33 and Fig. 34. We can see that conduction losses dominate. Thus, we also pick the lowest  $R_{dson}$  device for the primary side. Loss breakdown is as shown below in Fig. 34.

Fig. 34 Device loss distribution at different switching frequency

Considering the auxiliary power supply loss of 45W and transformer loss of 80W, a total efficiency of 98.5% can be reached. Also, device temperature is estimated based on selected thermal sink.

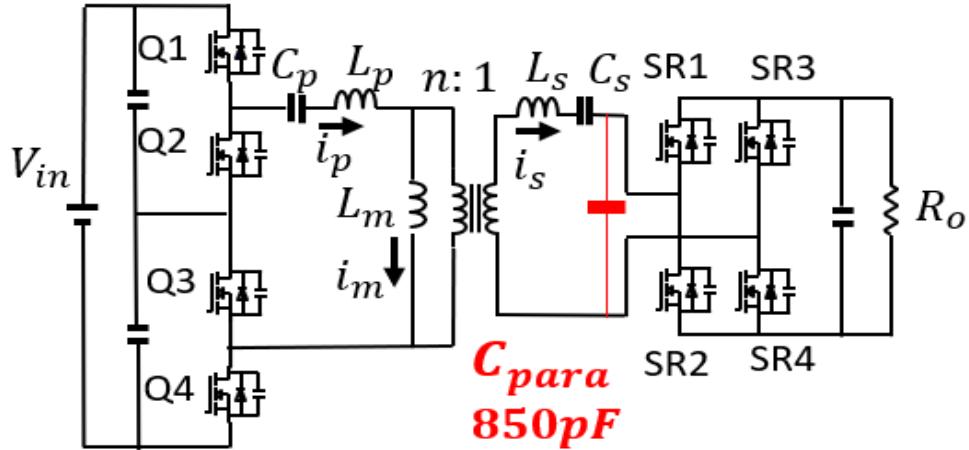

### G1 prototype development for high voltage three-level resonant converter

#### The Three Level Resonant Converter Design

At this moment, each part of this Three level resonant converter has been designed. Devices for both primary side and secondary side are selected based on device loss evaluation. Magnetizing inductance  $L_m$  and deadtime  $t_d$  are selected based on the requirement of zero voltage switching (ZVS). Transformer core material candidates are evaluated using the specialized core-loss measurement techniques developed at CPES and the core material is selected based on the switching frequency. Litz wire is also selected based on the switching frequency. Considering the insulation requirement, the insulation materials and winding structures are evaluated and selected to minimize the transformer volume. The

transformer loss is then calculated using the magnetic core loss model and litz wire winding loss model developed in CPES. Finally, all the transformer design parameters, such as number of turns, core loss density, and switching frequency are optimized based on the trade-off between the volume and converter total loss, as well as winding loss and core loss. The design result is summarized below as shown in Table V.

Table V: Three Level Resonant Converter Design Result

| Item                          | Spec.            |

|-------------------------------|------------------|

| Pri-side SiC MOSFET           | FF23MR12W1M1     |

| Sec-side SiC MOSFET           | C2M0045170D      |

| Insulation material           | SYGARD 3-6605    |

| Core material                 | ML27D            |

| Litz wire                     | TXXL525/42T2XX-2 |

| Number of turns ( $N_1:N_2$ ) | 16:22            |

| Switching frequency           | 200 kHz          |

## A. The Three Level Resonant Converter Prototype Development

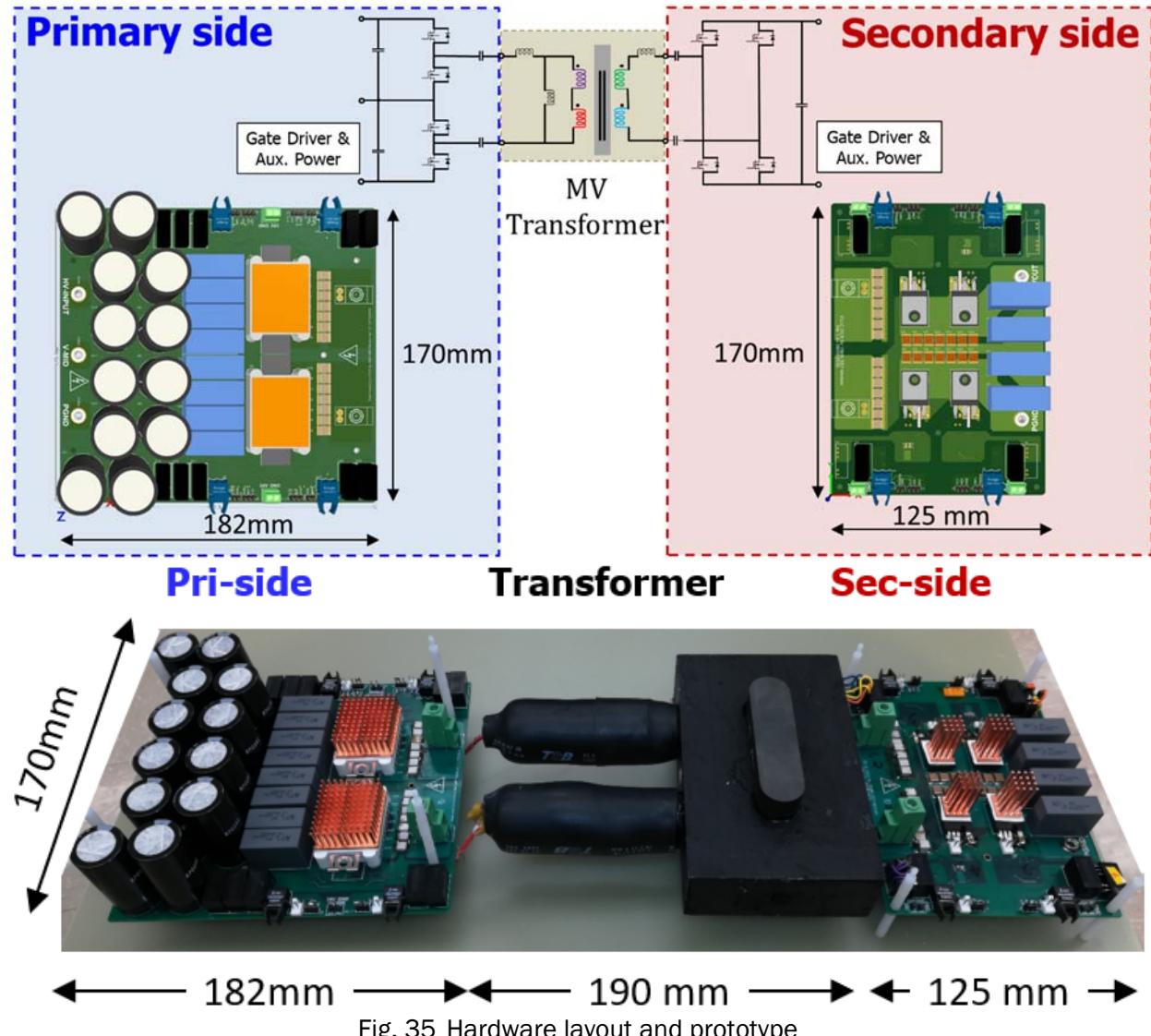

In circuit design stage, RECOM R24P series DC/DC brick type converter are selected as auxiliary power supplies for gate drivers and control circuits. The PCB layout and a photo of the prototype are shown in the Fig. 35 below. The width of primary and secondary PCB is the same, 170mm (6.69"), and the length of primary and secondary PCBs are 182mm (7.16") and 125mm (4.92"), respectively.

Fig. 35 Hardware layout and prototype

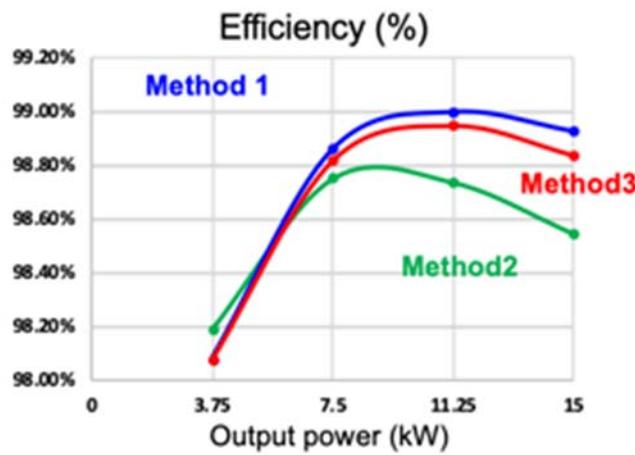

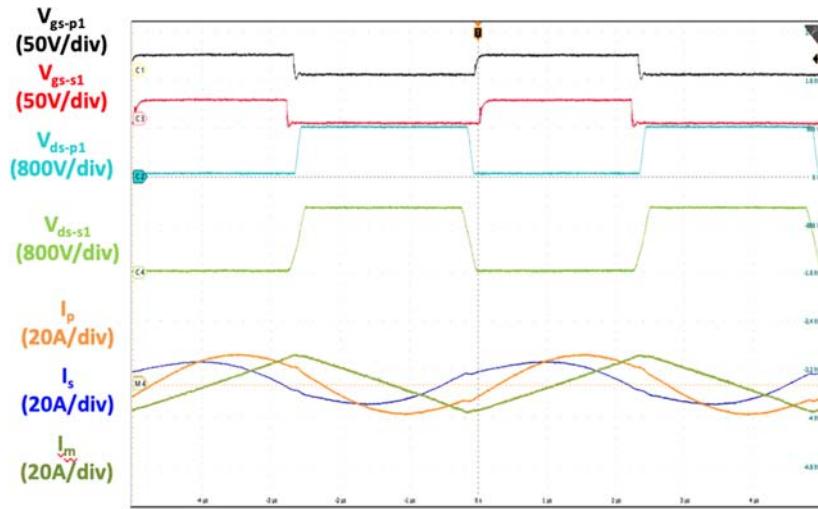

### Test Results

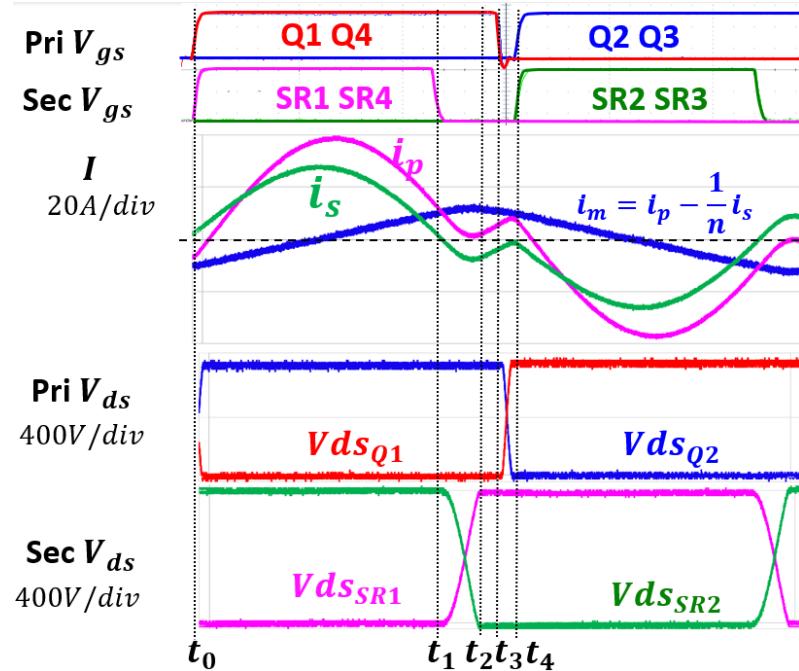

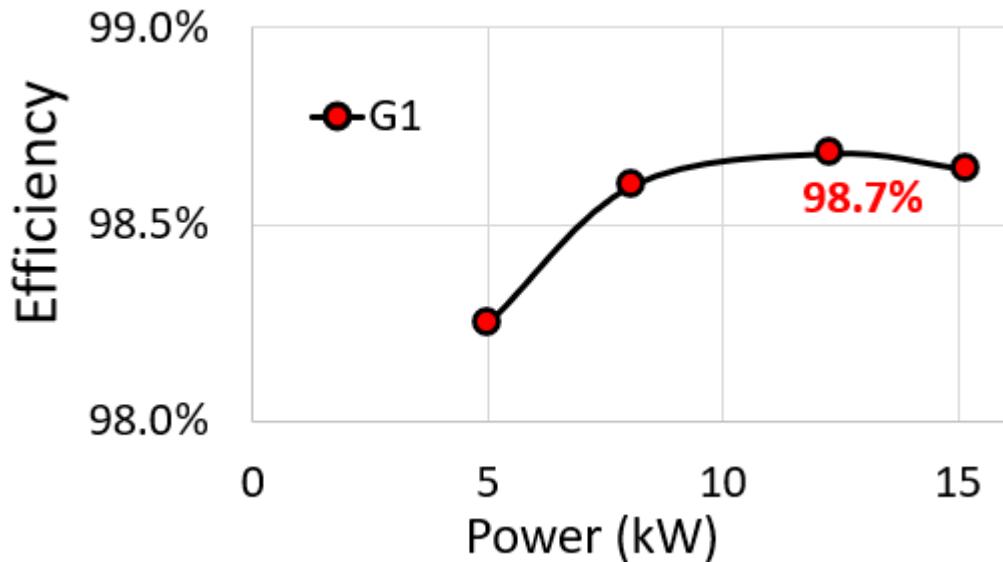

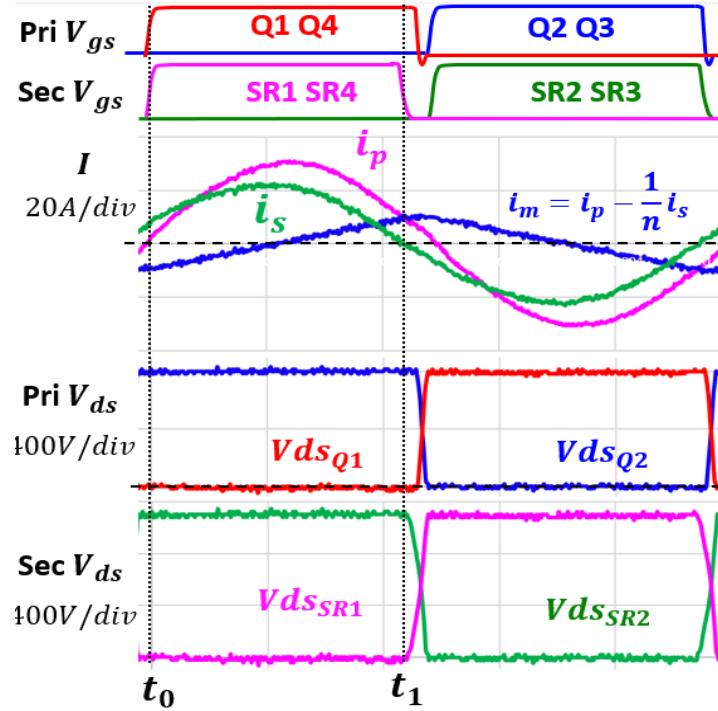

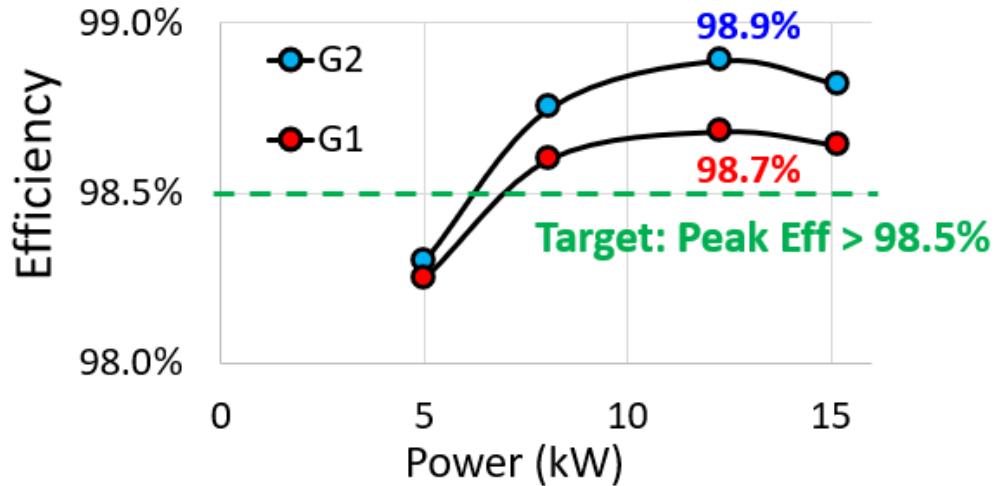

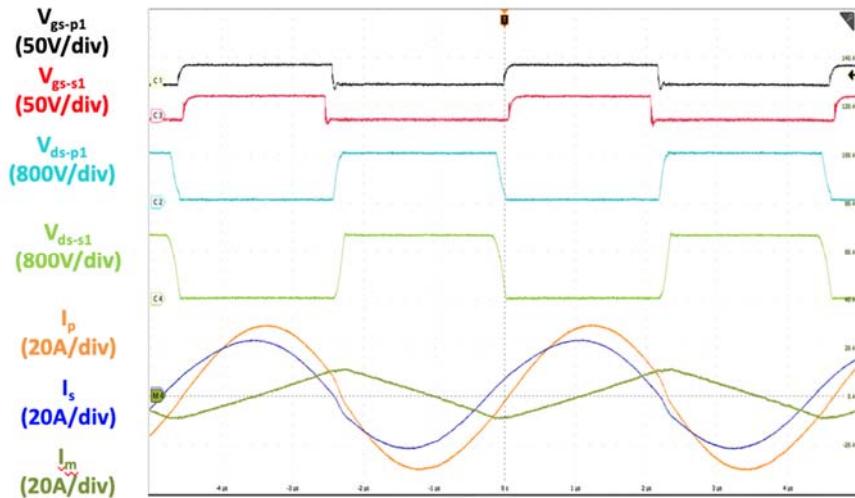

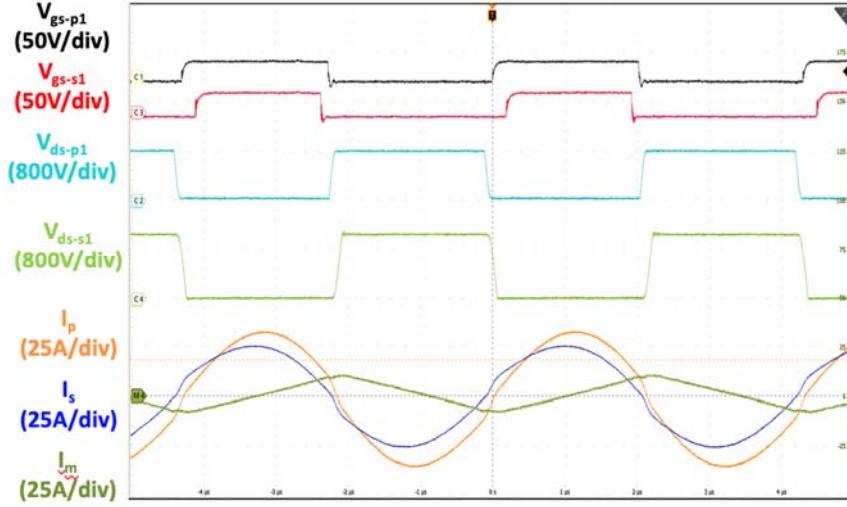

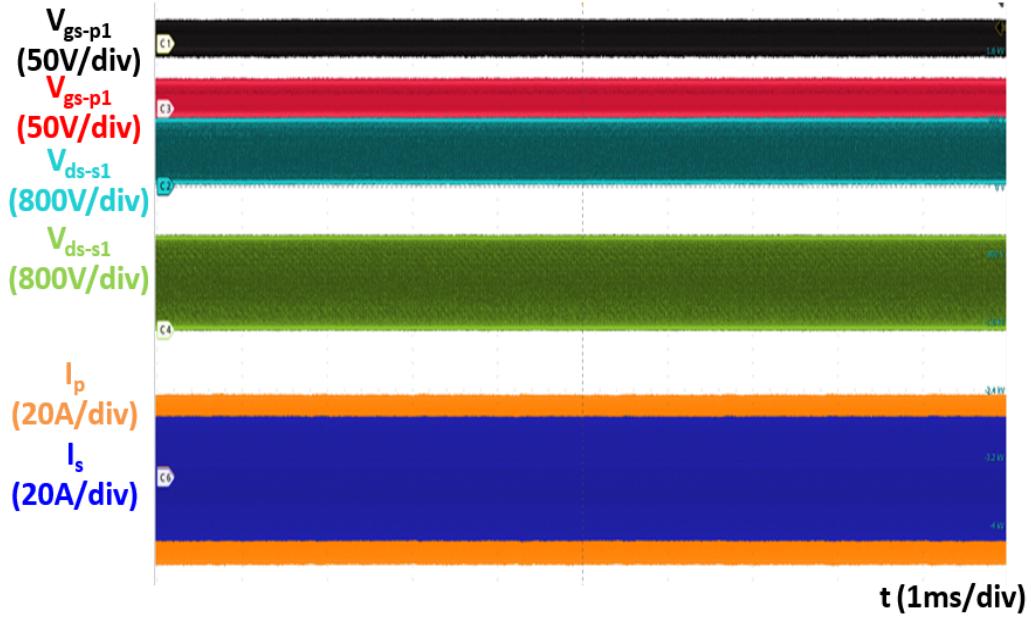

The prototype circuit is tested under the conditions as designed. During the test, the converter input DC voltage is increased gradually. To achieve ZVS, the converter is operating at a switching frequency slightly lower than the resonant frequency. The working waveforms are shown in Fig. 36. Primary side can achieve zero voltage turn on (ZVS) and low current turn off. While the secondary side can achieve both ZVS and zero current turnoff (ZCS). Under full load condition, the efficiency is 98.6%. And the efficiency curve under different load conditions is plotted in Fig. 37.

Fig. 36 Main working waveforms of G1 tests

Fig. 37 Tested Efficiency

### Further improvement of high frequency high voltage three-level resonant converter with SiC MOSFET

#### Design optimization for DC/DC stage

According to the G1 tested waveform, one minor issue is that the primary side has to wait until  $t_3$  to turnoff to achieve ZVS. And the interval of  $t_1 \sim t_3$  is determined by a high

frequency resonance, with leakage inductance, secondary side devices' junction caps, and parasitic caps on the PCB involved.

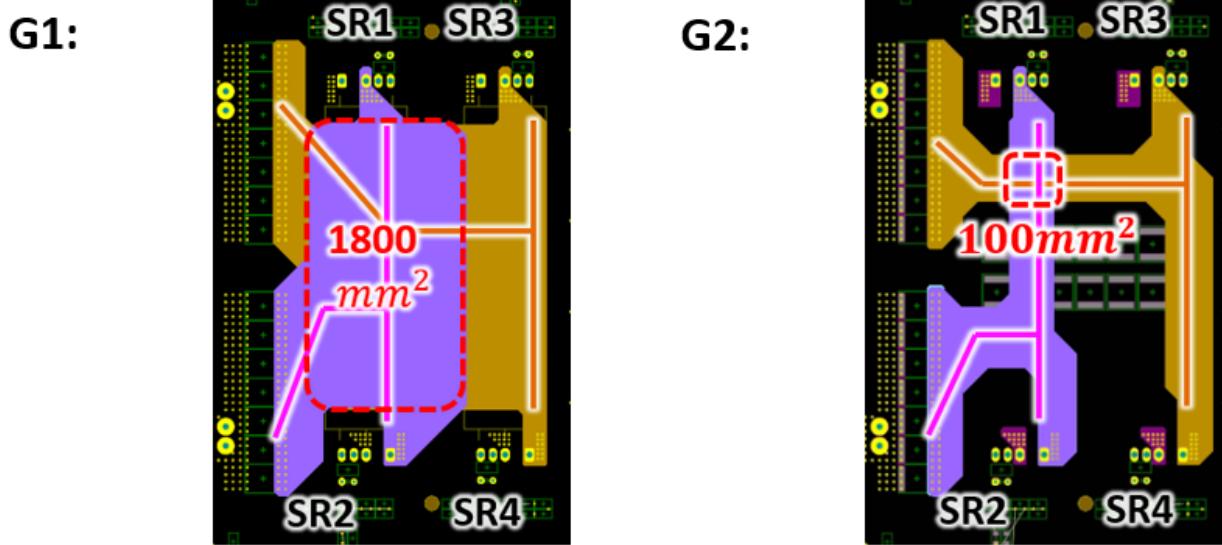

Fig. 38 Large parasitic capacitor in G1 secondary side PCB

On the secondary side PCB, there's too much overlap area between different copper layers of the main circuit. And this brings a huge parasitic capacitance (almost 850pF) between the two AC terminals on the secondary side, as shown in Fig. 38. This parasitic capacitance makes a huge impact on the waveform between  $t_1$  and  $t_2$  as shown in Fig. 36. During the commutation period, the parasitic cap is parallel to the junction caps on the secondary side and it will sink a lot of current from the primary side. Thus, if the primary side MOSFETs are turned off at the same time, the primary side current is not enough to discharge the junction cap on the primary side to realize ZVS. Then a time delay is applied to the primary side MOSFETs before the turn-off such that the primary side current is high enough to do ZVS. Since this parasitic capacitance is paralleled to the junction caps, it will also significantly increase the resonant period during the secondary side communication process. And due to no power is delivered during this  $t_1$  to  $t_2$  interval, the longer this interval is, the higher current RMS will be, and thus the higher conduction loss. In G2 design, to reduce the parasitic caps of PCB, the layout is improved to reduce the overlapped area of the power stages as shown in Fig. 39. And the parasitic cap is reduced from 850pF to 50pF.

Fig. 39 PCB layout improvement

|                       | G1                                  | G2                                 |

|-----------------------|-------------------------------------|------------------------------------|

| Overlap area          | <b><math>1800\text{mm}^2</math></b> | <b><math>100\text{mm}^2</math></b> |

| Parasitic cap         | <b><math>850\text{pF}</math></b>    | <b><math>50\text{pF}</math></b>    |

| $I_{pri}(\text{RMS})$ | <b><math>26.7\text{A}</math></b>    | <b><math>21.9\text{A}</math></b>   |

| $I_{sec}(\text{RMS})$ | <b><math>18.6\text{A}</math></b>    | <b><math>15.3\text{A}</math></b>   |

### Demonstration of G2 Prototype

#### Test Result of G2 Prototype

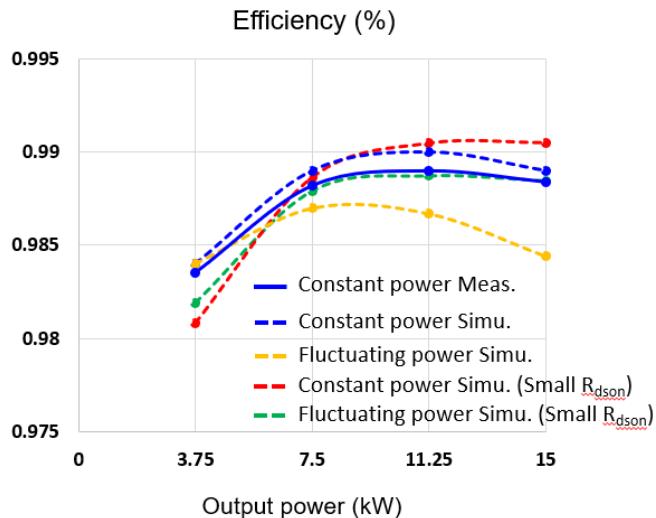

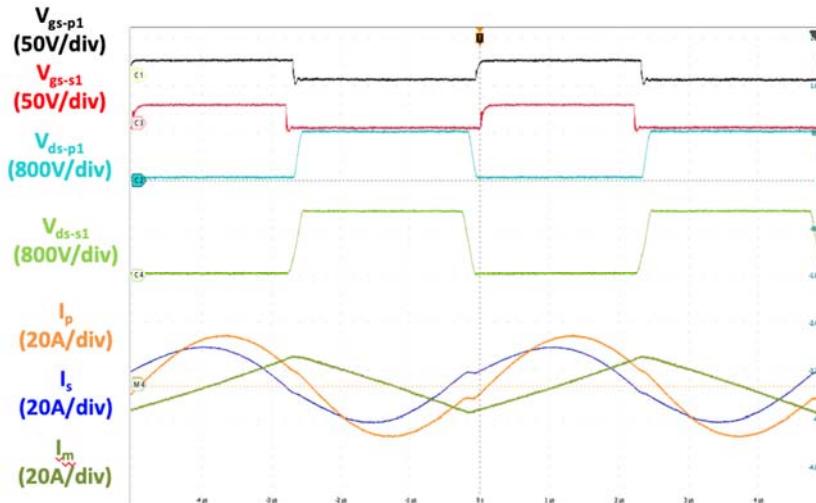

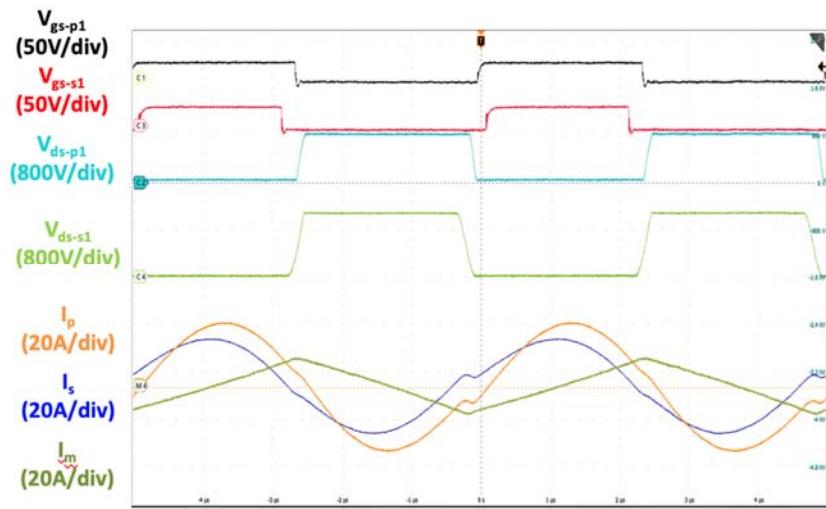

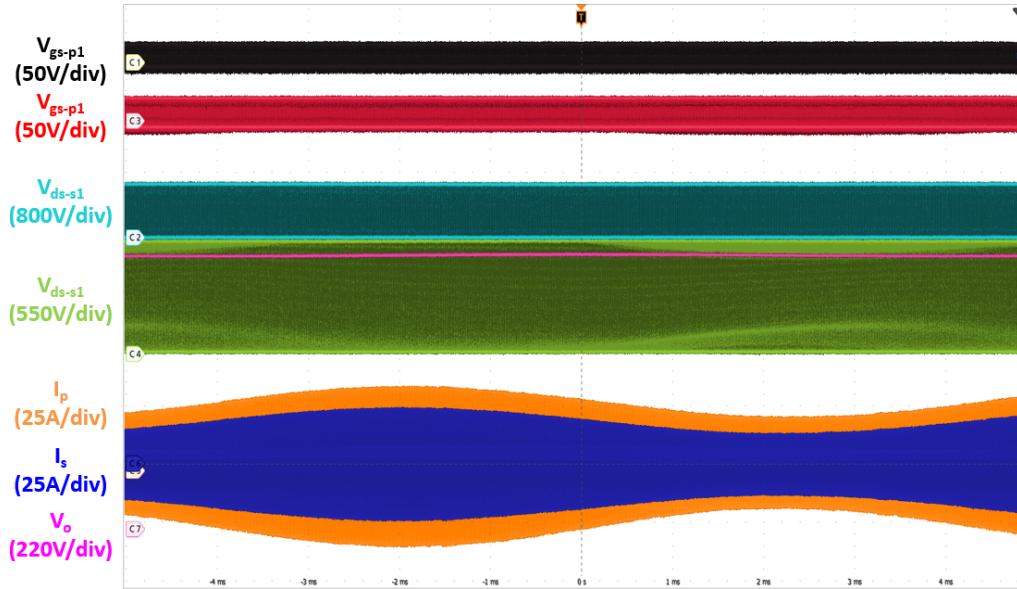

In G1 prototype, the secondary side PCB has a large parasitic cap (850pF) due to too much overlap area of the power path between two layers. The layout is improved in the G2 prototype, and the parasitic capacitor is reduced to 50pF, which is negligible. Fig. 40 shows the waveform of G2 after improvement. Compared to Fig. 36, it can be observed that the primary side current drops slowly after  $t_1$ . Now it's enough to realize ZVS for both primary side and secondary side MOSFETs at the same time. So, the switching frequency is determined by the resonant frequency and an adequate deadtime. In G2 prototype test, both the primary side and secondary side current are reduced compared to G1. And this reduction of RMS currents totally saves the conduction loss of 30W.

Fig. 40 Main working waveforms of G2 tests

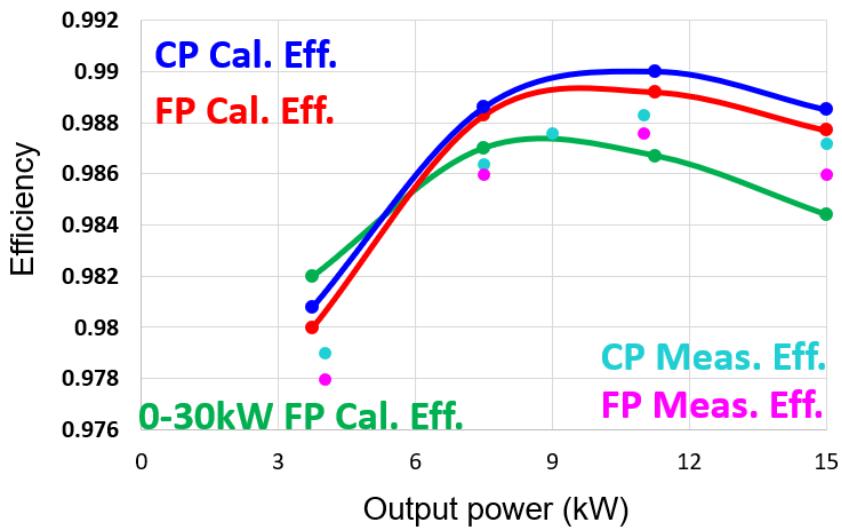

Fig. 41 shows measured efficiency curves at different load conditions. The peak efficiency of the 15kW DC-DC converter is increased from 98.7% in G1 tests to 98.9% in G2 tests.

Fig. 41 Measured Efficiency of G1 and G2

## System level control development for both AC/DC and DC/DC stages

### High-Frequency Simplified Optimal Trajectory Control development for high voltage resonant converter-based DC/DC stage

#### Start-up Process Consideration

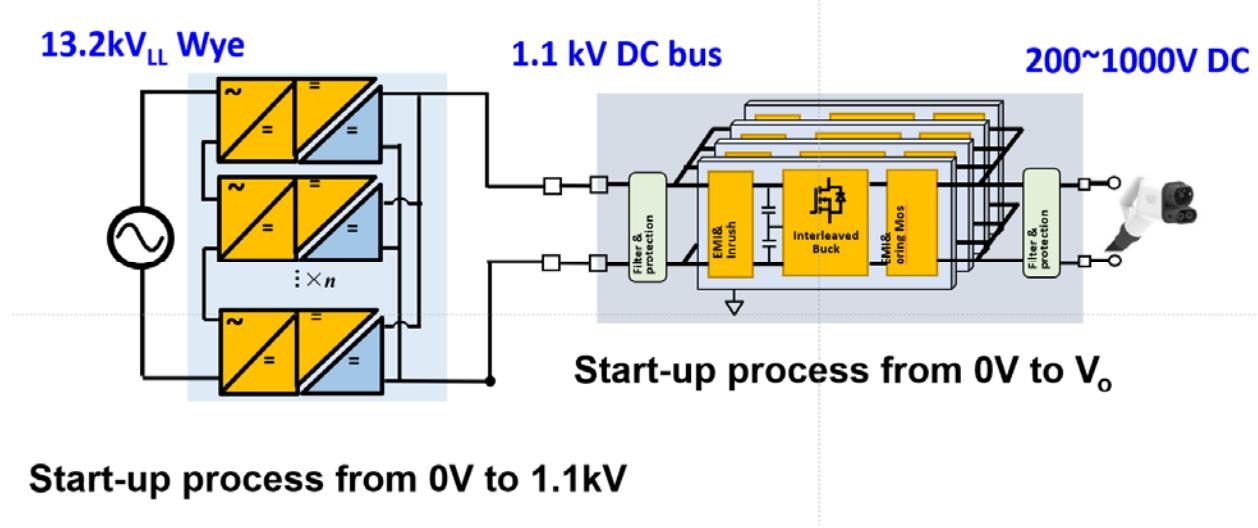

The resonant converter is very difficult to control due to the dynamics of the resonant tank. Conventional frequency control cannot achieve good transient performance, and there is very large dynamic oscillation during the transient, which may damage the converter due to the large current and voltage stresses. For the Solid-State Transformer in EV charger application, there are three stages, AC/DC stage, DC/DC stage, and following Buck converter stage as shown in Fig. 42. Take one phase system as the example. The start-up process should be charging the AC/DC stage first. And when the output capacitor of the AC/DC stage is fully charged, DC/DC stage will start to be charged until rated voltage (e.g. 1.1kV). Finally, Buck converter will start up from 0V.

At this moment, CPES develops a high-frequency simplified optimal trajectory control for the proposed CLLC converter for DC/DC stage to precisely control the state trajectory of the resonant tank components at start-up condition. The short circuit protection the inverse process of start-up. For AC/DC start-up and short circuit protection, CPES will develops in the future.

#### Start-up process from 0V to 1.1kV

Fig. 42. System schematic and start-up consideration

#### Review of Previous SOTC Achievements in CPES

Two version of SOTC is proposed in previous CPES achievements. The basic idea of the soft start-up process for the LLC resonant converter is to investigate and optimize based on a graphical state-trajectory analysis. By setting a current limitation band, several optimal switching patterns are proposed to settle the initial condition. After that, by sensing the output voltage, the optimal switching frequency is determined within the current limiting band. This virtually guarantees that there will be no current and voltage stress in the resonant tank during the soft start-up process and

over-load protection. Meanwhile, the output voltage is built up quickly and smoothly. When it comes to the over-load protection, it is a reverse operation of the soft start-up. By applying the similar switching pattern, the resonant current and voltage stress is limited under the over-load condition.

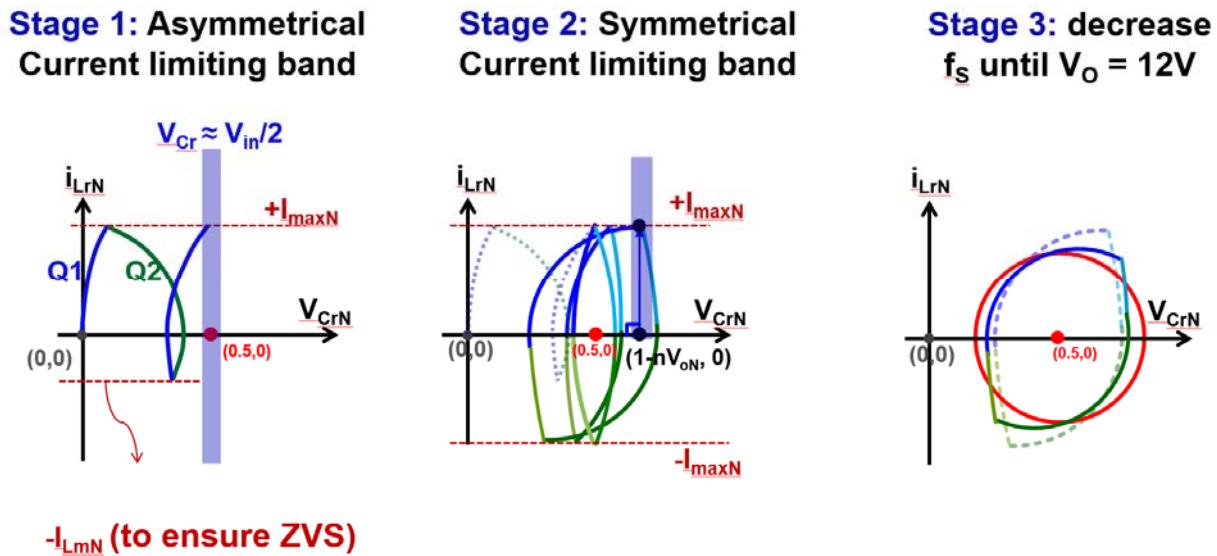

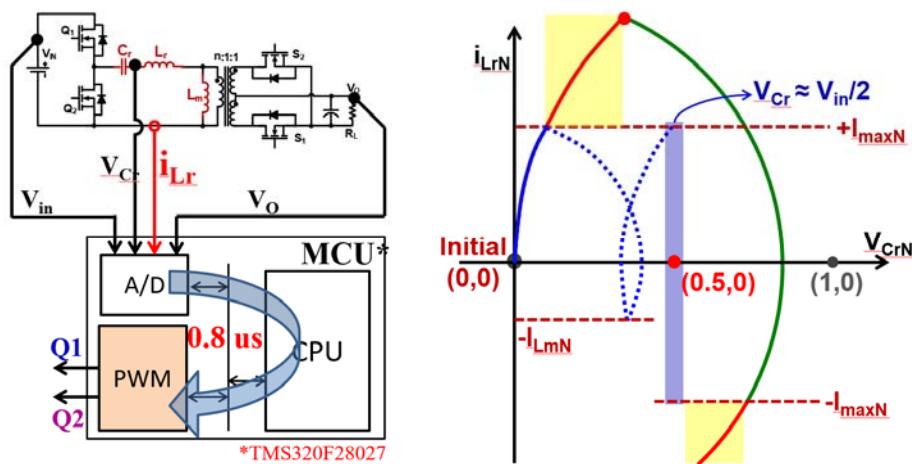

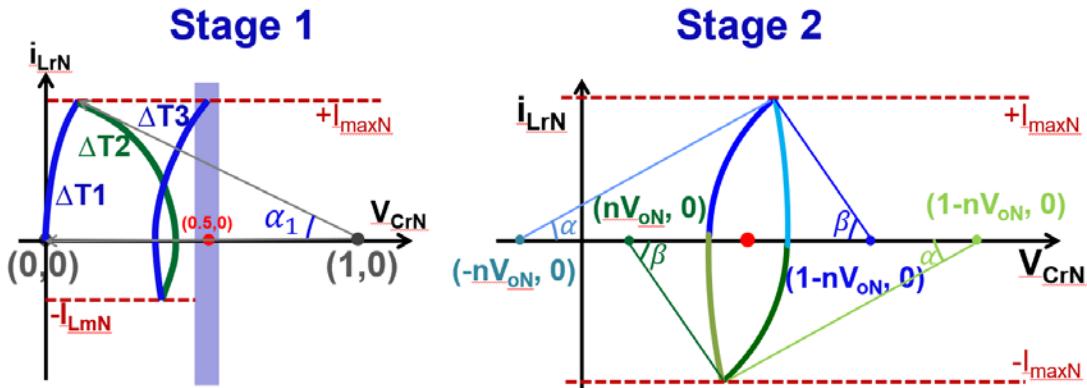

In the version I design, the whole startup process is divided into three stages, as illustrated in Fig. 43. Stage 1 sets an asymmetrical current-limiting band,  $+I_{maxN}$  and  $-I_{LmN}$  (the suffix N means normalized), to settle  $V_{Cr}$  to half of input voltage  $V_{in}$  (for 3 level CLLC configuration). Stage 2 sets a symmetrical current-limiting band,  $+I_{maxN}$  and  $-I_{maxN}$ , to optimize the energy delivery. Stage 3 decreases  $f_s$  gradually until  $V_o$  reaches steady state, which is 12 V in this case.

Fig. 43. OTC control process in version I

Fig. 44. Issue for OTC control with MCU Implantation

However, All the required state variables are sensed through the analog-to-digital converter (ADC) and processed by the CPU, as shown in Fig. 44(a). If the MCU senses  $i_{Lr}$  and compares it with  $I_{maxN}$ , there would be a digital delay of at least 0.8  $\mu$ s. The impact of this 0.8  $\mu$ s digital delay will cause very large  $i_{Lr}$  stress in Stage 1 as shown in Fig. 44(b), where the dashed line represents the desired trajectory and the solid line represents the actual trajectory with digital delay. Since the initial  $f_s$  for start-up should be very high, even a very small digital delay will cause a large  $i_{Lr}$  stress. Specifically, the 0.8  $\mu$ s digital delay will cause twice as large as the full-load current stress for a 200-kHz LLC converter and more than three times the full-load current stress for a 500-kHz LLC converter.

To solve this issue caused by digital delay in ADC and calculation, MCU-based implementation with lookup tables is proposed, which only requires sensing  $V_o$ . In Stage 1,  $V_o$  is considered to be approximately 0 V because the output capacitor is very large and there are only a few switching pulses in Stage 1. The initial condition is:  $V_{Cr} = 0$  and  $i_{Lr} = 0$  because there is no energy in the resonant tank before start-up. The trajectories to calculate  $\Delta T1$  and  $\Delta T2$  are shown in Fig. 45 And  $\Delta T1$  and  $\Delta T2$  are calculated based on the angle. The values for  $\Delta T1$ ,  $\Delta T2$  ...  $\Delta Tn$  are calculated step by step until it comes to the step at which  $V_{Cr}$  comes into the region around  $V_{in}/2$ , which is the last switching action in Stage 1.

In Stage 2,  $f_s$  can be determined based on the precalculated  $f_s$  versus  $V_o$  table. This is because for a given  $V_{in}$  and  $V_o$ ,  $f_s$  can be determined based on the  $i_{Lr}$  stress requirements when operating at above  $f_o$ . During start-up,  $V_{in}$  and  $V_o$  can be considered to be constant within several switching cycles because there is a large input capacitor for the hold-up time and a large output capacitor for the load transient. Under these conditions, the corresponding  $f_s$  can be obtained for different values of  $V_o$  to guarantee  $i_{Lr}$  is within  $I_{max}$  under the nominal input voltage  $V_{in}$  nom based on the corresponding trajectory shown in Fig. 45. The switching period is then calculated based on the angle to derive the  $f_s$  versus  $V_o$  table for Stage 2, which then linearized piece-wise and stored in the MCU. Stage 3 for this method is the same as that of the OTC for soft start-up, just decreasing  $f_s$  gradually until  $V_o = 12\text{ V}$  and then merging with closed-loop control.

Fig. 45. Modified SOTC control to apply digital control

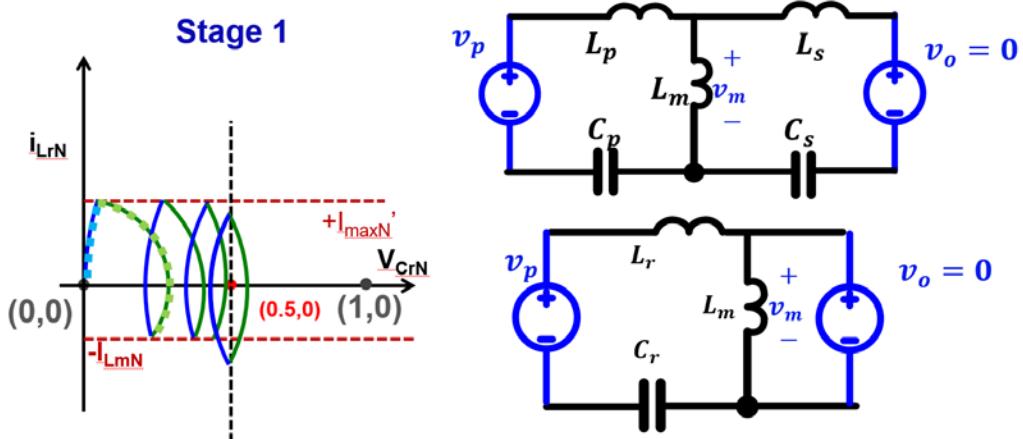

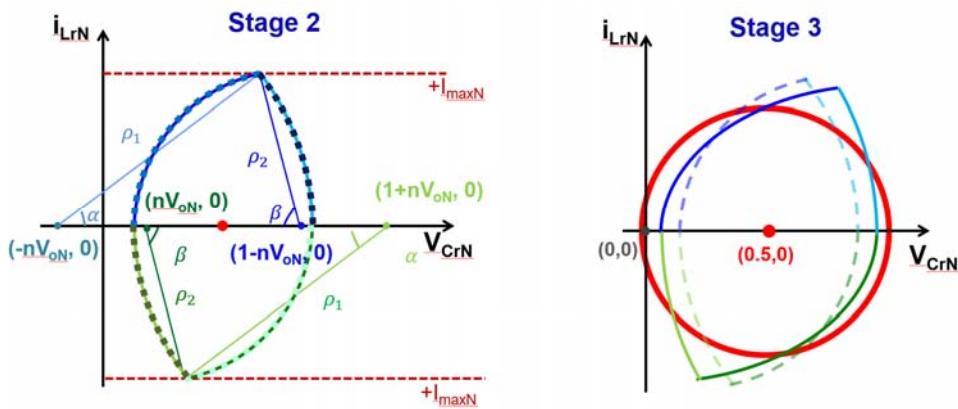

### SOTC Control in CLLC Application

To utilize the SOTC control in the CLLC converter in SST application. The difference between LLC and CLLC should be considered. Compared with LLC, the CLLC has 4 resonant component and it is really hard to analysis CLLC performance. However, an approximation can be applied in CLLC to find an equivalent LLC circuit in the start-up process. As shown in Fig. 46, at stage 1, the output voltage is 0. Compared with  $L_m$ , the impedance of  $L_s$  and  $C_s$  is smaller. There is almost no impact from the  $I_m$ , which means we can consider  $L_p$ ,  $L_s$ ,  $C_p$ , and  $C_s$  in series. In this case, an equivalent LLC circuit can be proposed. From the trajectory point of view, the solid line are the CLLC trajectory and the dash line are the equivalent LLC trajectory. These two lines overlaps well, which means we can use the equivalent LLC trajectory to determine the turn on time of each devices. For stage 2, the equivalent LLC trajectory can be also utilized for the CLLC circuit with almost no error. For stage 3, the feedback control will be applied to deal with the error in the stage 2., exactly same as what we proposed in LLC applications, as shown in Fig. 47.

Fig. 46. Approximation in CLLC for start-up

Fig. 47. Approximation trajectory for stage 2 in CLLC for start-up

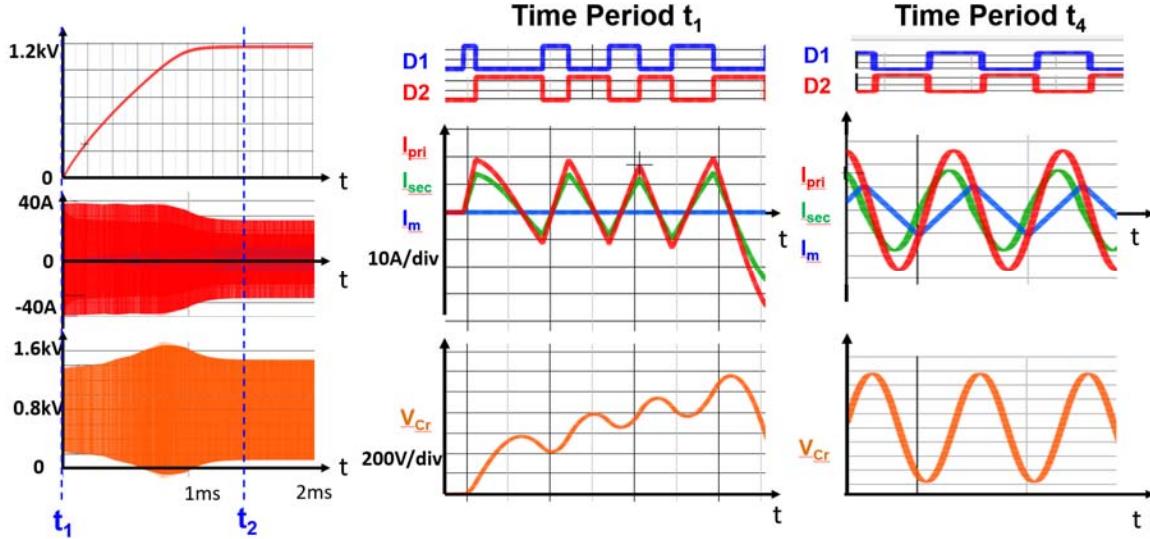

Fig. 41 shows the simulation of the whole start-up process of the CLLC converter. As the figure indicates, the  $V_o$  increase from 0V to 1.1kV smoothly without overshoot in 1.3ms. The highest peak current stress on the inductance is around 40A and the highest capacitance voltage stress is 1.8kV.

Fig.48. Simulation result for the CLLC converter

## Cascaded multi-level rectifier control for AC/DC stage

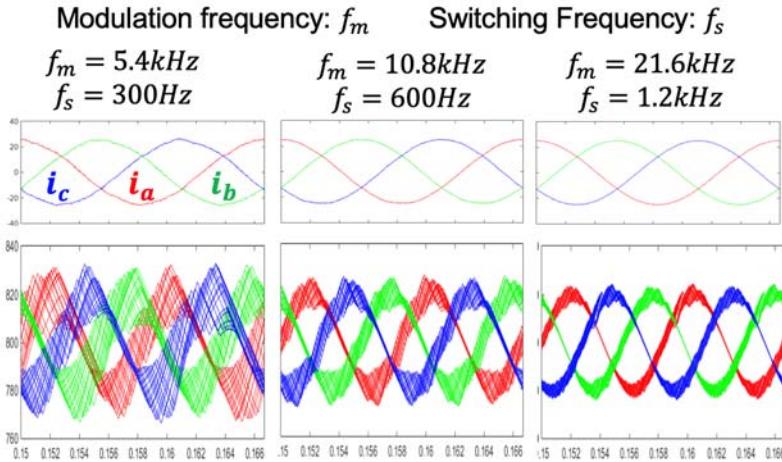

### Modulation Method Comparison

The modulation method is critical for the SST system, because such method determines the simulation complexity for the entire system. Consider the switching frequency difference, two modulation method are surveyed for comparison.

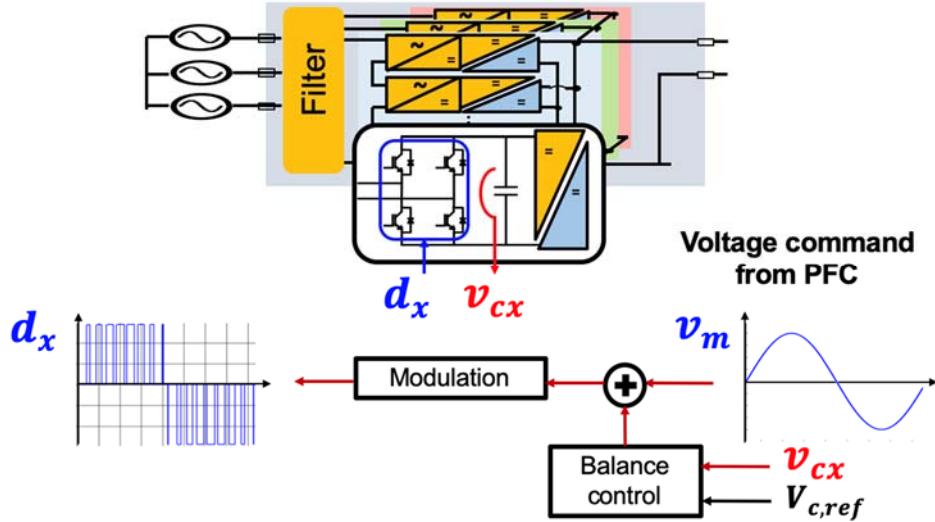

The first method is modules in each phase balance the voltage together. There are two voltage loops. The first one is to compare voltage information  $v_{cx}$  and the reference voltage  $v_{c,ref}$  for each module, as shown in Fig. 49. The second voltage loop is to compare the previous signal with the voltage command  $v_m$  from PFC to achieve the voltage balance. Every module has its own switching performance based on this method. To regulate the voltage, the switching frequency is high and fast communication is required but the voltage is more accurate. So this method cannot handle too many modules.

The second method is to add some phase shift in the modulation systems as shown in Fig. 2. Compared with method 1, the voltage command from PFC will pre-modulation to divide into  $m$  part. The switch of different modules will operate at certain input voltages and then compare with voltage information  $v_{cx}$ . Due to phase shift, each module can have relatively

low switching frequency. Although the voltage cannot be controlled very accurate at each time period, the communication demand will not high and it can handle more modules compare with method 1.

Fig. 49. Method 1: For high switching frequency with less modules

Fig. 50. Method 2: For low switching frequency with more modules

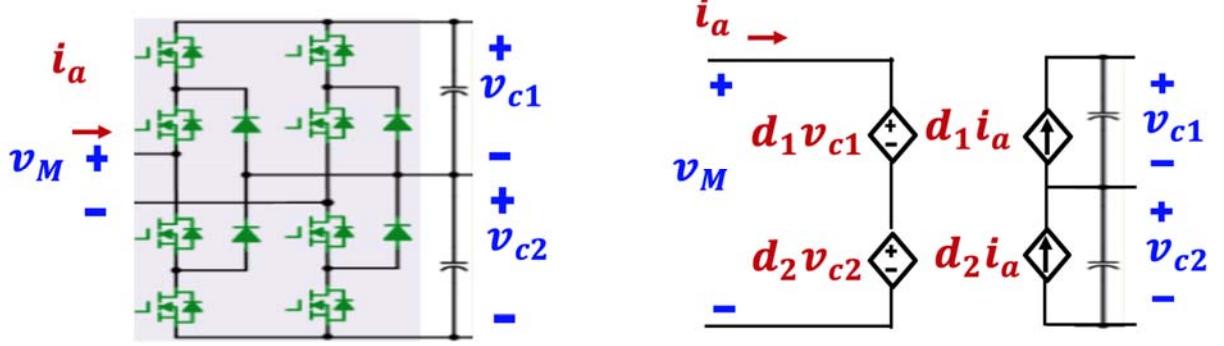

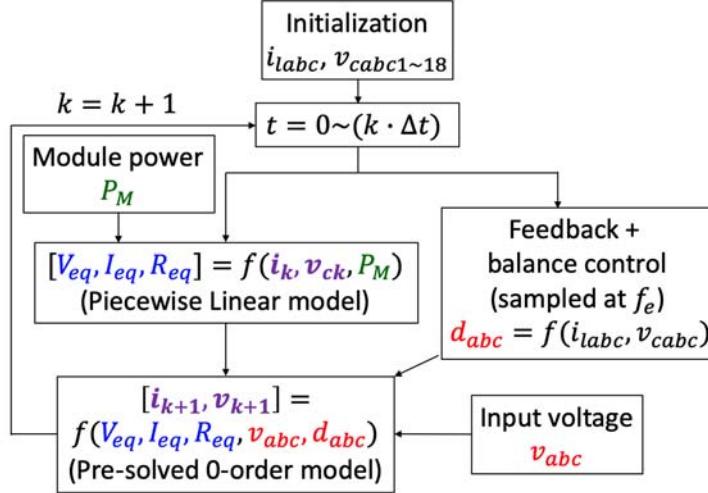

### Simplified Cascaded H Bridge Simulation Model

For the Solid-State Transformer system level simulation, the most essential challenge is the simulation speed. The SST system is a three-phase system with 9 modules per phase. As we can see from Fig. 44, for one module, there are 7 energy storage components (2 bulk capacitors, 2 resonant capacitors, 2 resonant inductors, and 1 magnetizing inductance). It is a 7-order system for even one module. Such resonant behavior will dramatically slow down the simulation. Consider only one module per phase, this simulation will take 1 hour to finish 1 line cycle. For the entire SST system, there are 193 order. To finish the entire system simulation, the Simulink should continuously run over 24 hours. This time cost is too much to accept.

Fig.51. SST system architecture and the topology for 1 module

To make some improvement, we can regard the DC/DC stage as the constant power load, which can well regulate its output power. Based on such assumption, the CLLC converter can be regarded as a 3-order component instead of a 7-order component. The entire system order can be reduced from 193 to 57, as shown in Fig. 45. However, 57-order system is still a high order system. In addition, the constant power load is also a non-linear component. Its simulation speed is relatively low. Considering even more modules should be introduced to the system in the future to handle more power, this simulation system is not what we prefer. The research goal for the SST simulation is to further reduce the system order and to speed up the simulation progress.

Fig. 52. SST system architecture with simplified DC/DC stage

To make some improvement, the priority is to find out which components affect the simulation speed most. In the simplified SST system architecture in Fig. 45, there are still 4 kinds of non-linear components, which are 3 input inductances, switches in each AC/DC modules, two bulk capacitors per module, and 1 constant power load per module. To speed up the simulation, all these non-linear components should be converted to linear components by some way. That is the motivation for this AC/DC simulation simplification research.

For the switches in the AC/DC module, in the simulation, we can regard these devices as ideal devices. In this case, devices only have three switching performances, forward turn on, turn off, and reverse turn on. These three states can be presented by duty cycle  $d = 1, 0, -1$ , as shown in Fig. 5. Under this assumption, we can simplify the real switch model into simplified switches. The switch network can be simplified to two voltage-controlled current sources. The AC/DC stage can be regarded as a linear system to reduce the simulation time.

Fig 53. AC/DC stage real switching model and simplified switches model

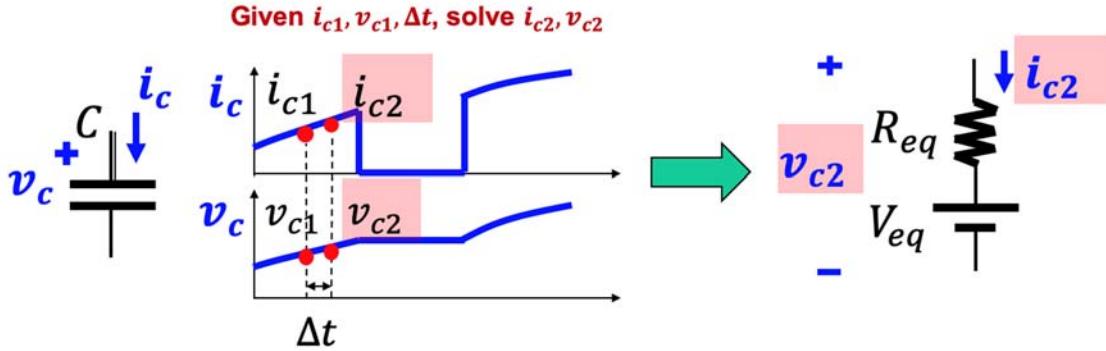

For the capacitors and inductors simplification, the piecewise linear model is applied. The idea for the piecewise linear model is the capacitor current and voltage is almost linear at a very small  $\Delta t$  during the charging time for one capacitor, as shown in Fig. 47. If we know the initial state  $i_{c1}$  and  $v_{c1}$  at  $t_0$ , we can calculate the  $i_{c2}$  and  $v_{c2}$  at  $t_0 + \Delta t$ . From the capacitor charging definition,

$$v_{c2} = v_{c1} + \frac{1}{C} \int_{\Delta t} i_c dt$$

Assuming a very small  $\Delta t$ , the previous equation could be simplified as,

$$v_{c2} \approx v_{c1} + \frac{1}{C} \frac{i_{c1} + i_{c2}}{2} \Delta t$$

In this equation,  $i_{c1}$  and  $v_{c1}$  is known as initial state,  $i_{c2}$  information is known from previous AC/DC switching models. We can rewrite this equation into the following manner,

$$v_{c2} \approx V_{eq} + R_{eq} i_{c2}$$

where  $V_{eq} = v_{c1} + R_{eq} i_{c1}$ , and  $R_{eq} = \frac{\Delta t}{2C}$ . The non-linear capacitor can be represented by a voltage source and a resistor in series. So we can solve the  $v_{c2}$  information by a linear equation, whose simulation speed is much faster than simulating a capacitor. Same concept can also be applied to simulate input inductors.

Fig. 54. Piecewise linear model of Capacitor

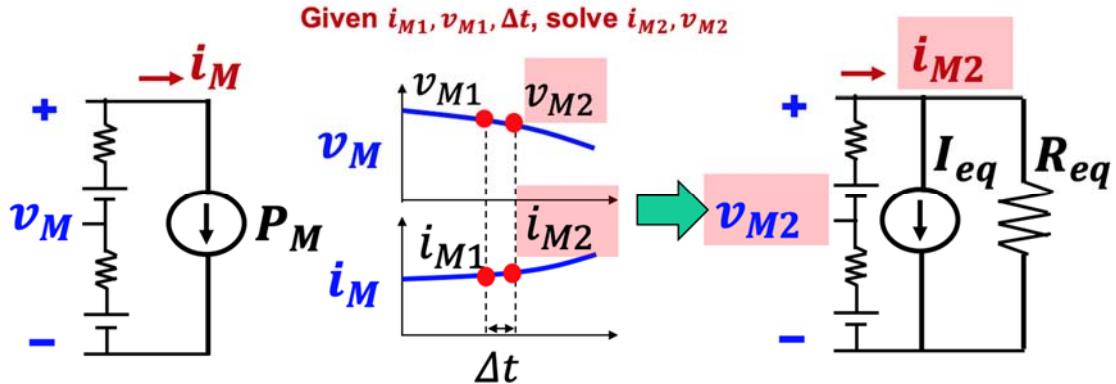

For constant power load, we can also apply piecewise linear method, as shown in Fig. 48. If we know the initial state  $i_{M1}$  and  $v_{M1}$  at  $t_0$ , we can calculate the  $i_{M2}$  and  $v_{M2}$  at  $t_0 + \Delta t$ . From the power definition with a very small  $\Delta t$ ,

$$i_{M2} = \frac{P_M}{v_{M2}} = \frac{P_M}{v_{M1} + (v_{M2} - v_{M1})} \approx \frac{P_M}{v_{M1}} \left( 1 - \frac{v_{M2} - v_{M1}}{v_{M1}} \right)$$

In this equation,  $i_{M1}$  and  $v_{M1}$  is known as initial state,  $v_{M2}$  information is known from the input voltage. We can also rewrite this equation into the following manner,

$$i_{M2} \approx I_{eq} - \frac{v_{M2}}{R_{eq}}$$

where  $I_{eq} = 2P_M/v_{M1}$ , and  $R_{eq} = -\frac{v_{M1}^2}{P_M}$ . The non-linear constant power load can be represented by a current source and a resistor in parallel. So we can solve the  $i_{M2}$  information by a linear equation, whose simulation speed is much faster than simulating a constant power load.

Fig. 55. Piecewise linear model of Constant Power Load

With all components are linear, the entire system becomes a 0-order system. We can run the simulation much faster than previous mentioned 193-order system. To further increase the simulation speed, MATLAB is utilized instead of Simulink. A simulation flow chart is shown in Fig. 49. In the simulation, the input is the voltage and current information at  $t_0$ . With the constant

power information,  $V_{eq}$ ,  $I_{eq}$ , and  $R_{eq}$  can be calculated based on the piecewise linear model. Together with the feedback and balance control, the current and voltage information can be calculated at  $t_0 + \Delta t$ . Repeat the same process, the simulation can be done within 2 minutes, which is much faster than Simulink simulation. The simulation results are also shown in Fig. 50.

Fig.56. Simulation flow chart

Fig. 57. simulation results

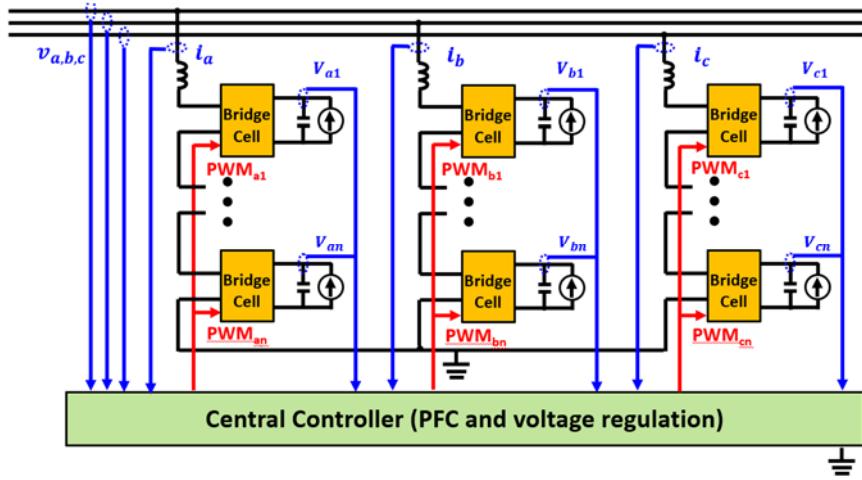

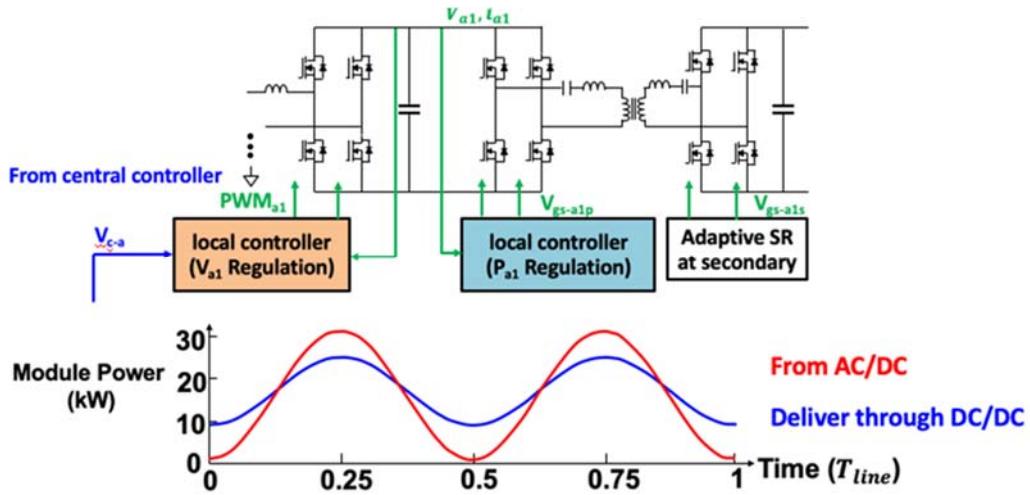

### System level control simulation model development

Centralized or Distributed Control Method Comparison for Solid-State Transformer (SST) systems.

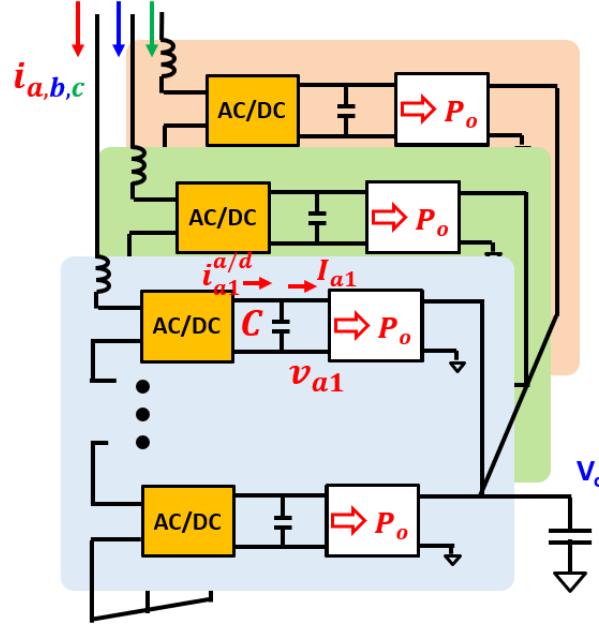

Due to medium-voltage requirement, the Cascaded-H-Bridge (CHB) circuit will be applied as the AC/DC rectifier as the first stage of the SST system. While the DC/DC stage, which provides the isolation, plays the role as the second stage. Because of and high-power and modularity, for one phase, multi-cell will be used to handle such high power. From control point of view, multi-cell topology will lead to issues of voltage balance and power balance

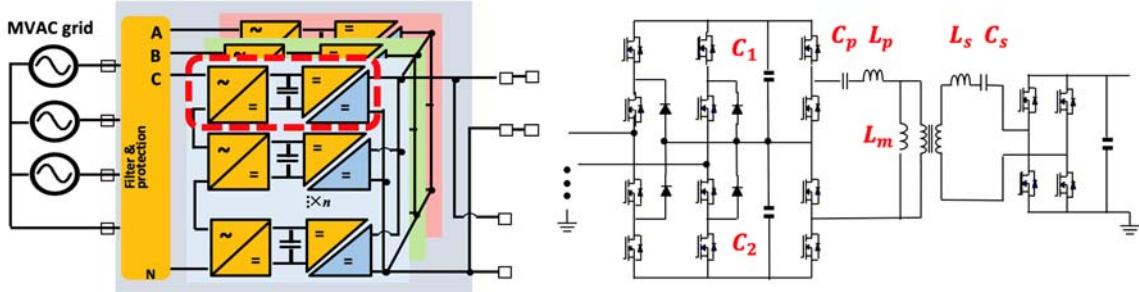

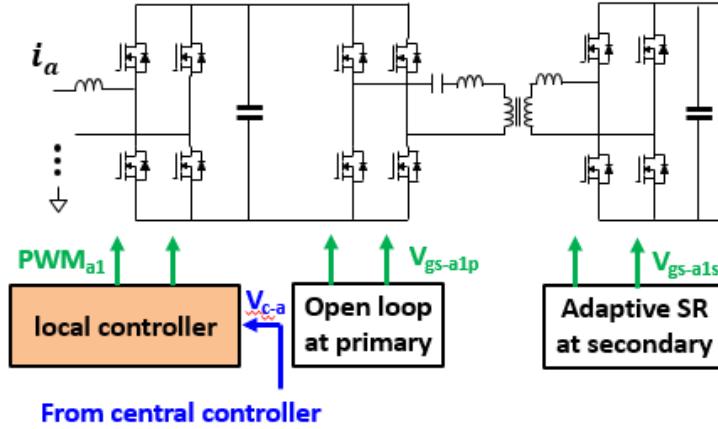

between different modules. This will be solved by control methods. If we consider the synchronization between each module, one controller would be the simplest solution. However, for such a huge system, the controller should be strong to process all the input signal and generate the output commands. In addition, due to the medium-voltage input, the signal transmission will be under high voltage insulation and high bandwidth which increases the cost. Considering these disadvantages, distributed control, which control signals generate from local controller to lessen the control burden of the strong central controller, is more and more popular at this moment.

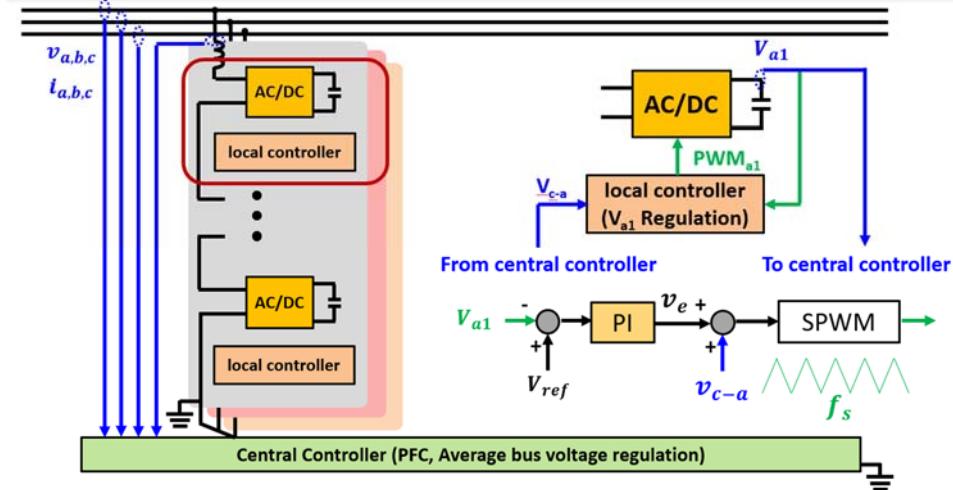

Based on the SST architecture, the first stage is the CHB. We will use CHB as the starting point to compare advantages and disadvantages of centralized control and distributed control. For the centralized control of the CHB, the control schematic is shown as Fig. 51. The input line frequency voltage and current are sensed to the central controller. The bus voltage of each bridge cell is also sensed. Sensed signals are processed in the central controller. PWM signals are generated based on the voltage balance and power balance control and then transferred to each bridge cell. For the centralized control, only one strong controller is needed and no synchronization issue should be considered. The communication between each module are simple and easy to achieve. However, as we mentioned before, the central controller should be powerful enough. The sensing signal for bus voltage requires high voltage insulation and the PWM signal requires not only high voltage insulation but high bandwidth.

Fig. 58. centralized control method for CHB

For the distributed control for CHB, local controllers are required for each bridge cells, as shown in Fig. 52. The central controller is still required to sense the input line frequency voltage, current and the bus voltage. The average voltage control and PFC is achieved in the central controller and the control signal  $v_{c-a}$  is transferred to the local controller. In the local controller, the bus voltage will also be sensed and compared with reference voltage to achieve the voltage regulation for each module. The PWM signal, as the output of the local controller, control the power device of the converter. Compared with the central controller, no high frequency high bandwidth signal transfer in the distributed control loop. Only high bandwidth low voltage transmission and low bandwidth high voltage transmission are required.

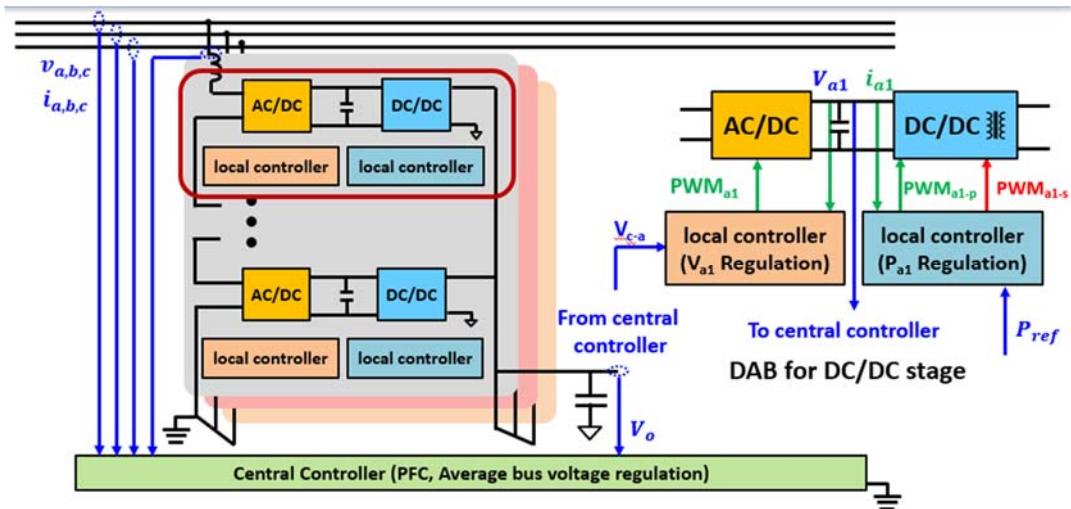

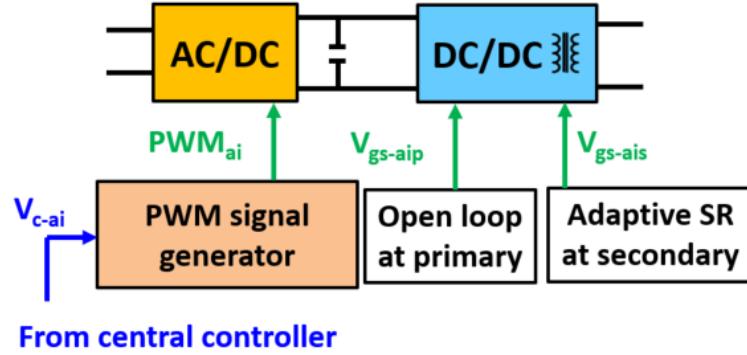

Extend the CHB to the SST, DC/DC module as the second stage is added to the system, as shown in Fig. 53. The AC/DC stage control method is the same and the only difference occurs at DC/DC stage. The central controller plays a role for output voltage regulation in the DC/DC stage. The reference power signal generates from the central controller and convey to each local controller of the DC/DC stage. DC/DC controller senses input current and voltage information and generate PWM signal after processing. In this method, the primary side PWM signal is high-bandwidth low-voltage and the secondary side PWM signal is high-bandwidth high-voltage.

Fig. 59. CHB control with local voltage regulation

Fig. 60. SST control with local voltage and power regulation

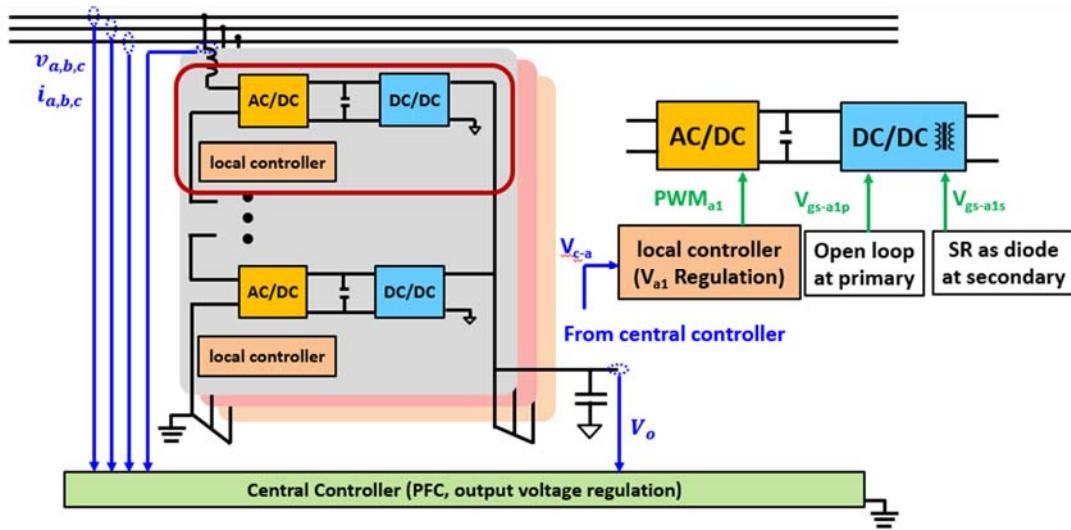

In the aforementioned SST control method, lots of sensing is required. Another control method for the SST with less sensor is shown in Fig. 54. In this case, the DC/DC stage works under open loop control and there is no sensor for the bus voltage. The system only needs to sense 7 signals,

3 input line frequency voltage, 3 input line frequency current and the output voltage. The bus voltage is ensured by DCX operation and the power balance is ensured by the same control signal  $v_{c-a}$ . In this control method, we can eliminate the high-bandwidth, high-voltage control command for the secondary side devices in the first SST control method.

Compare these two control methods from communication point of view, the first method and the second method all sense 7 signals, 3 input line frequency voltage, 3 input line frequency current and the output voltage. For the first method, it needs  $3n \times 3$  low-bandwidth high-voltage signal,  $3n \times 4$  high-bandwidth low-voltage signal, and  $3n$  high-bandwidth high-voltage signal. For the second method, it needs  $3n$  low-bandwidth high-voltage signal and  $3n \times 3$  high-bandwidth low-voltage signal. There is no high-bandwidth high-voltage signal needed in the second method.

Fig. 61. SST control with DC/DC open loop control

### System level simulation to evaluate different operation methods with the impact of power flow.

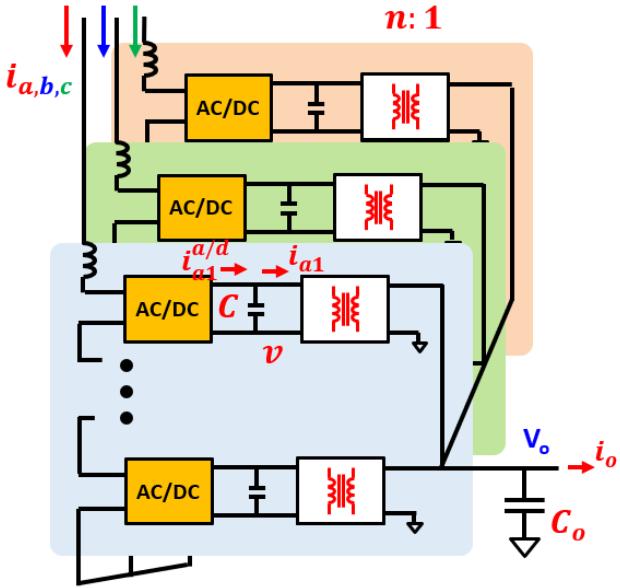

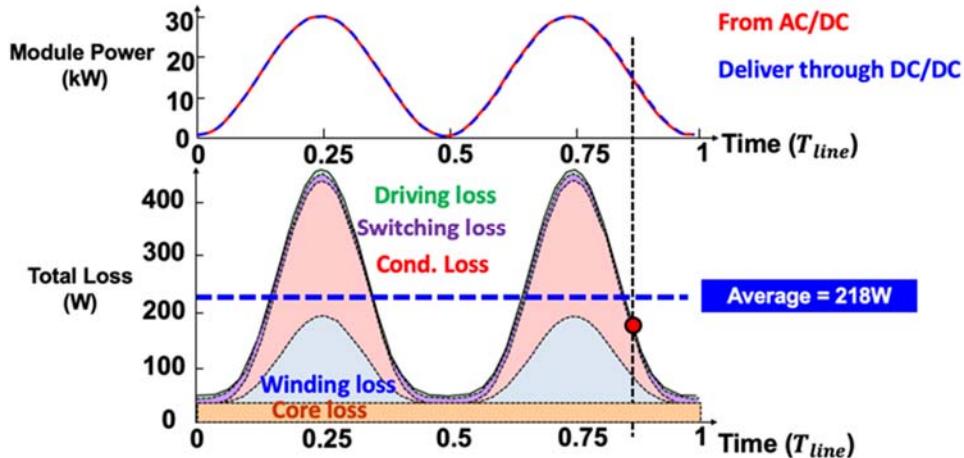

#### Constant power flow control method for DC-DC stage in SST

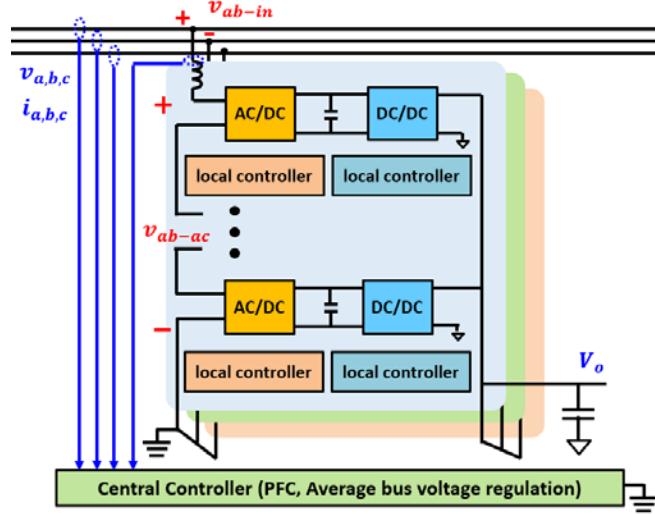

The SST system consists of  $N$  models per phase with input series output parallel structure. The input side will directly be connected to the MVAC grid and the output will be series connected with another interleaved Buck circuits as the fast charger for electrical vehicle application. The prototype of the SST is rated as input AC-voltage of 13.2kV, output DC-voltage of 1.1kV, bus voltage of 1.6kV, 9+1 modules per phase, and the output power of 405kVA. The modeling and control of the SST, for both CHB stage and CLLC converter with constant power flow as DC-DC stage is introduced in this section.

##### 1. Modeling and control for CHB stage

Fig. 62. Three phase SST with constant power control in DC-DC Stage

The AC-DC stage has 3 goals, power factor correction, bus voltage balance, and bus voltage regulation. A 2-step control strategy is applied to achieve these control goals. The first step is a conventional d-q control to achieve power factor correction and bus voltage regulation. And the second step is the individual voltage balance. Based on Fig. 55, the CHB stage voltage current equations can be written as

$$\begin{bmatrix} v_{ab-in} \\ v_{bc-in} \\ v_{ca-in} \end{bmatrix} - \begin{bmatrix} v_{ab-ac} \\ v_{bc-ac} \\ v_{ca-ac} \end{bmatrix} = L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}$$

where  $v_{ab-in}$ ,  $v_{bc-in}$ ,  $v_{ca-in}$  are the grid line voltage;  $v_{ab-ac}$ ,  $v_{bc-ac}$ , and  $v_{ca-ac}$  are CHB AC-side voltage;  $i_a$ ,  $i_b$ , and  $i_c$  are inductor current.

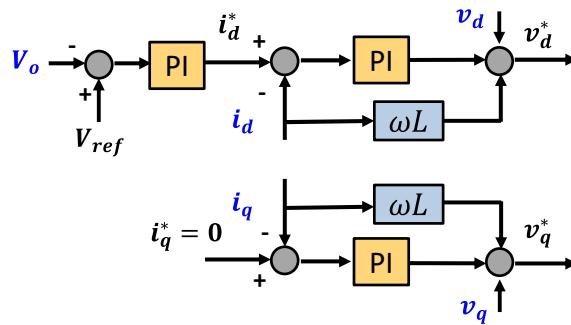

Fig. 63. Scheme for dq decoupled control

With, d-q transformation on (1), the equation in dq coordinate can be re-written as

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} - \begin{bmatrix} v_d^* \\ v_q^* \end{bmatrix} = L \begin{bmatrix} \frac{d}{dt} & -\omega \\ \omega & \frac{d}{dt} \end{bmatrix} \cdot \begin{bmatrix} i_d \\ i_q \end{bmatrix}$$

where  $v_d$ ,  $v_q$  are the d- and q-axis component of grid line voltage;  $v_d^*$  and  $v_q^*$  are CHB AC-side voltage under dq coordinate;  $i_d$  and  $i_q$  are inductor current in the same coordinate. The scheme of the dq control is shown as Fig. 56. Bus voltage for each module will be sensed and the average bus voltage  $v_{ave}$  will be calculated in the central controller. The reference bus average voltage  $v_{ref-ave}$  is set based on the designed system bus average as 1.6kV. The error voltage will go through the proportional-integral (PI) controller to get the reference active current  $i_d^*$ . To get unity power factor, the  $i_q^*$  should be set as 0. With such dq control, the control signal for average value of the bus capacitor  $v_{c-ai}$ ,  $v_{c-bi}$ , and  $v_{c-ci}$  can be got and the power factor correction can be achieved. Here,  $i$  means ith module per phase.

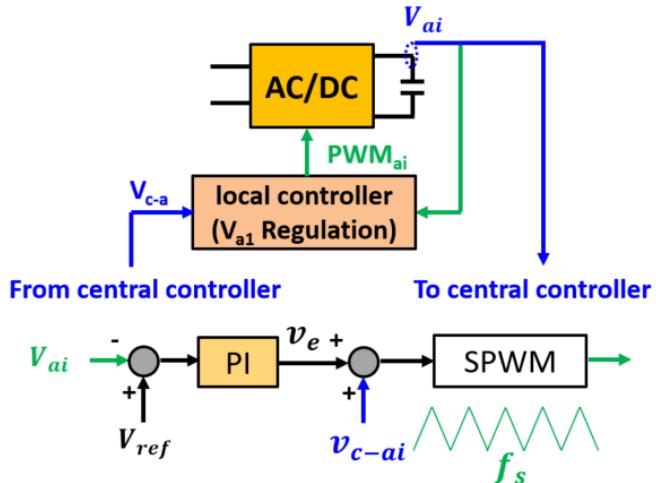

Due to the parasitic components in the circuit and the small error of duty cycle, the individual voltage balance should be taken into special consideration. For the individual voltage, the voltage balancing control should occur in the local controller and the control scheme is shown in Fig. 57. The local controller senses the individual bus voltage ( $v_{ai}$ ) and compare with the reference bus voltage ( $V_{ref}$ ). The error of these two voltages come into another PI controller to generate the compensation signal  $v_e$ . The individual voltage balance can be obtained by the sum of the compensation signal  $v_e$  and the control signal  $v_{c-ai}$ ,  $v_{c-bi}$ , and  $v_{c-ci}$ .

Fig. 64. Control scheme for individual voltage balance control

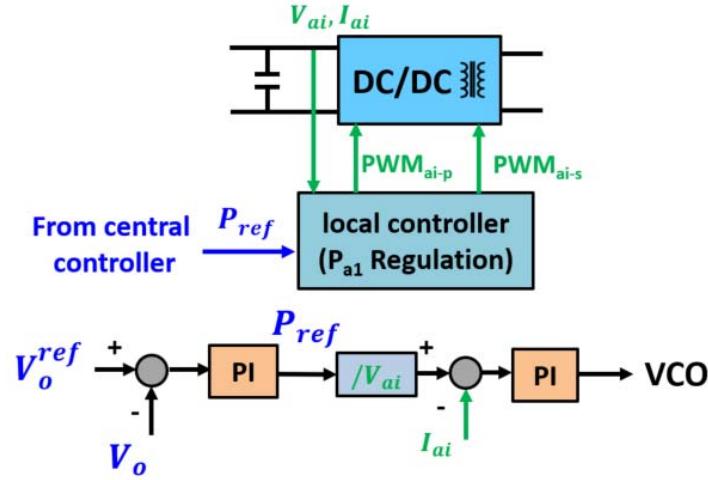

## 2. Modeling and control for DC-DC stage

With the CHB stage control, the power factor correction, the voltage regulation, and the voltage balance are achieved. Other control goals are the current sharing between modules, the power regulation, and the output voltage regulation. The power regulation method has been proposed for Dual Active Bridge (DAB) circuit. For the CLLC circuit, the control concept is similar. The difference is using the frequency control instead of the phase shift angle. The control scheme is shown in Fig. 58. One module is used as an example to illustrate how the control concept works. The control loop includes two parts. For the voltage loop control, the sensed output voltage  $V_o$  is compared with the reference voltage  $V_o^{ref}$  and generates the

constant power reference  $P_{ref}$ . In the controller, such  $P_{ref}$  will be divided by the bus voltage  $V_{ai}$  to get the input current reference  $I_{ref}$  for the CLLC converter. For the current loop, the sensed input current  $I_{ai}$  compares with the reference current. The error current comes into the PI controller to get the control signal of the CLLC converter. In this way, the current sharing between modules and the power regulation can be realized in the system.

Fig. 65 Control scheme for power regulation control

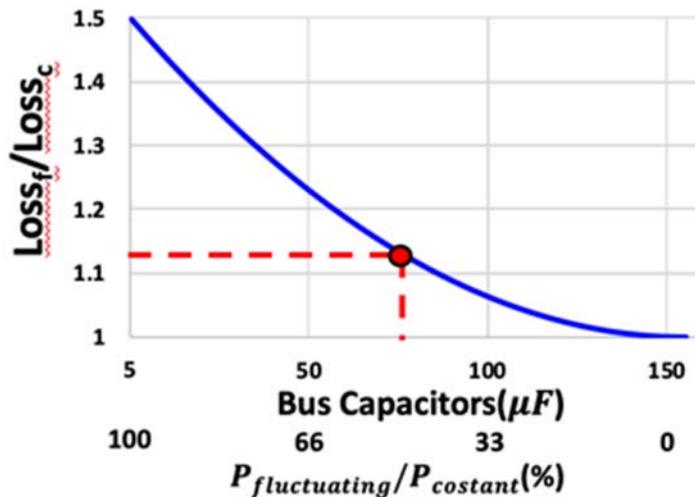

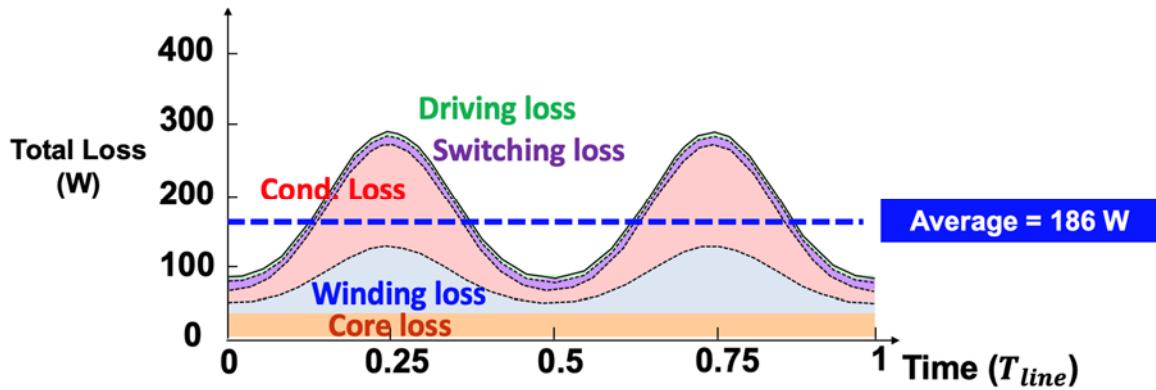

### 3. Bus Capacitor Design

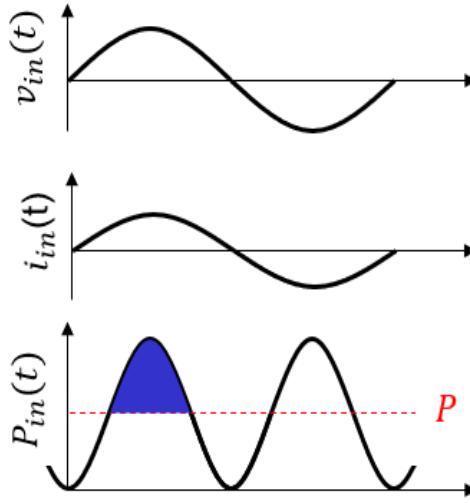

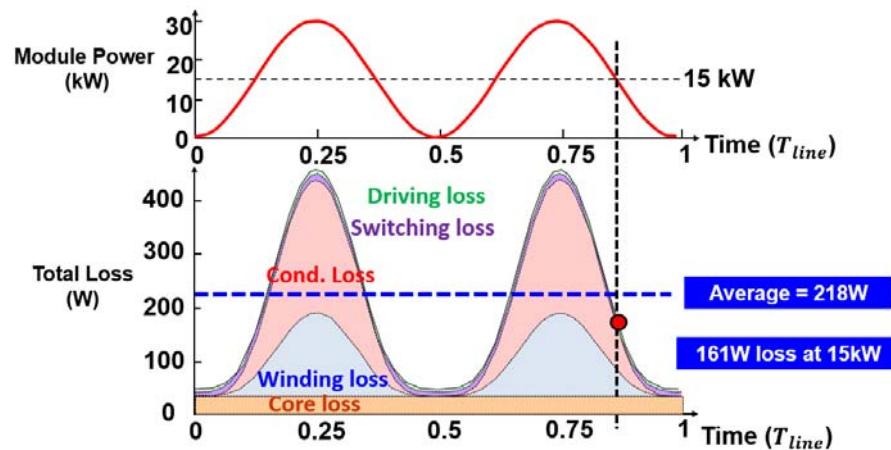

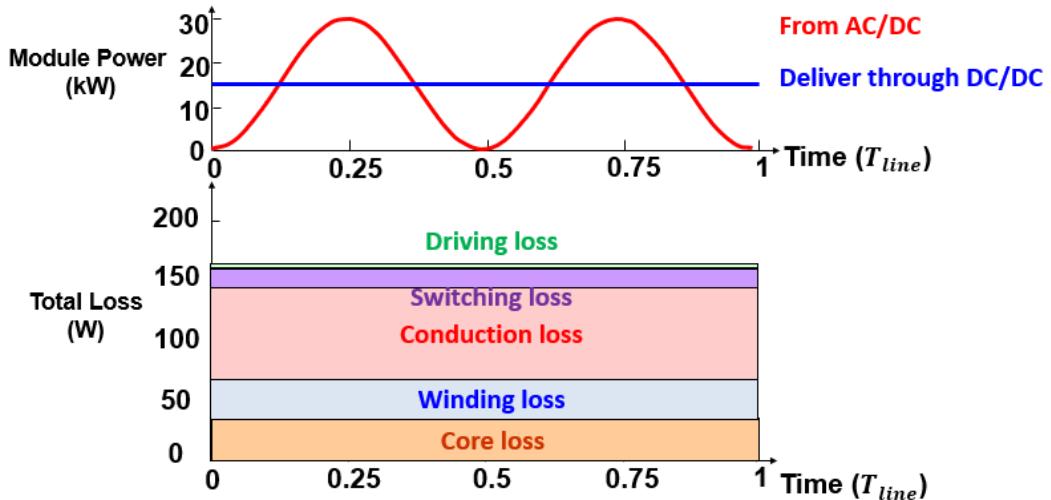

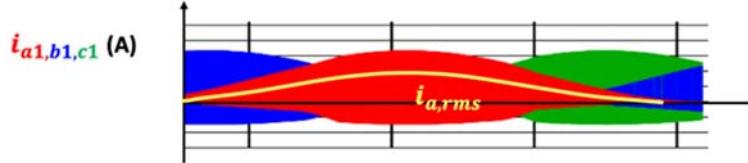

From the aforementioned analysis, the output power for the CLLC stage is a constant power. For the input stage of the CHB stage, under the unity power factor assumption, there is a double line frequency component power as shown in the Fig. 59. Due to the mismatch of the input and output power, bus capacitor should be put between the CHB stage and CLLC stage to achieve the goal for power regulation.

$$v_a = V \sin(\omega t)$$

$$i_a = I \sin(\omega t)$$

$$P_a = \frac{VI}{2} - \frac{VI}{2} \cos(2\omega t)$$

Fig. 66 Input voltage, current, and power waveform

Because the CLLC converter has a constant power flow, a simplification can be made on the 3-Phase system. In Fig. 60, the DC-DC stage is regarded as a constant power. Consider one module  $a_i$  of Phase A, assume the voltage ripple  $\Delta V_{ai}$  is much smaller than the DC voltage  $V_{ai}$ . So that the input current of the DC-DC stage is

$$I_{ai} \approx \frac{P_o}{V_{ai}}$$

where  $P_o$  is the power per module.

For the output current for the CHB stage,

$$i_{ai}^{a/d} \approx \frac{p_{ai}(t)}{V_{ai}} = P_o[1 - \cos(2\omega t)]$$

where  $p_{ai}(t)$  is the output power per module.

For the bus capacitor,

$$i_{ai}^{a/d} - I_{ai} = C \frac{dv_{ai}(t)}{dt}$$

Solve the equation, the bus voltage is

$$v_{ai}(t) = V_{a1} + \frac{P_o/V_{ai}}{2\omega C} \sin(2\omega t)$$

For certain voltage ripple  $\Delta V_{ai}$ , the minimum capacitor value is

$$C = \frac{P_o}{2\omega V_{ai} \Delta V_{ai}}$$

Fig. 67 System scheme with simplified DC-DC stage as constant power flow

Consider the bus voltage as 1.6kV, output power as 15kW, and 5% of voltage ripple, the bus capacitor should be larger than  $155\mu F$ .

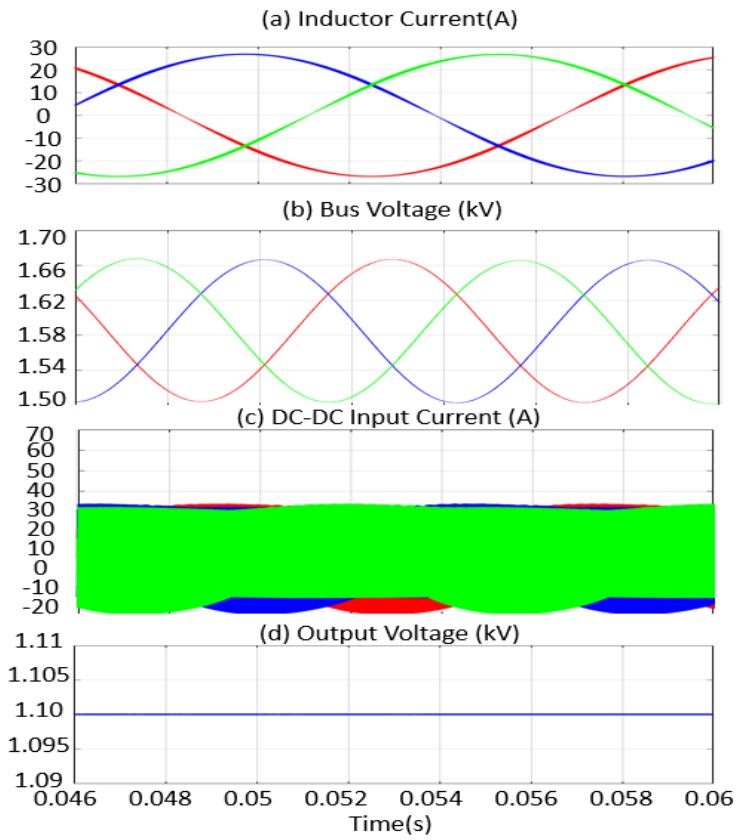

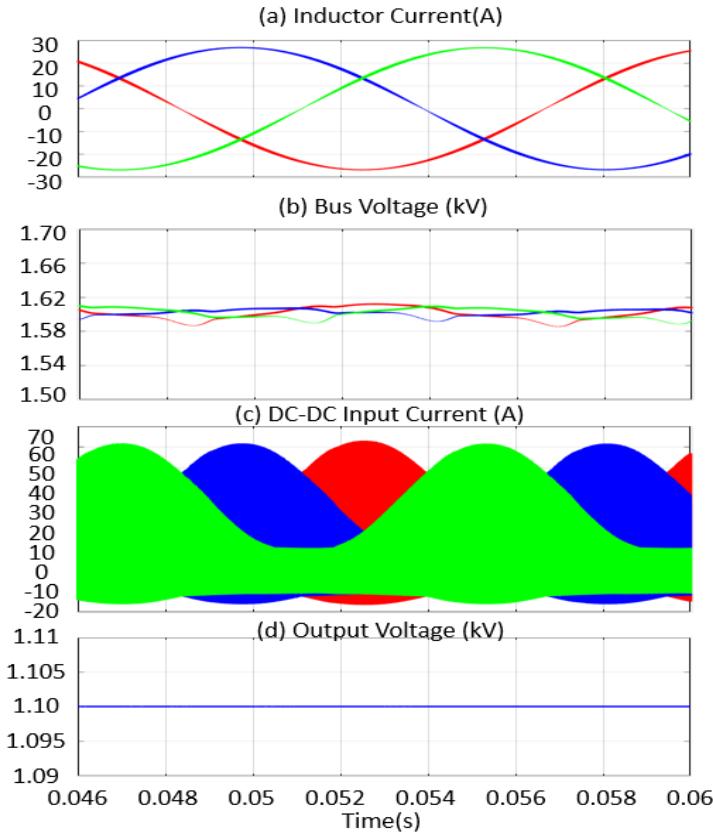

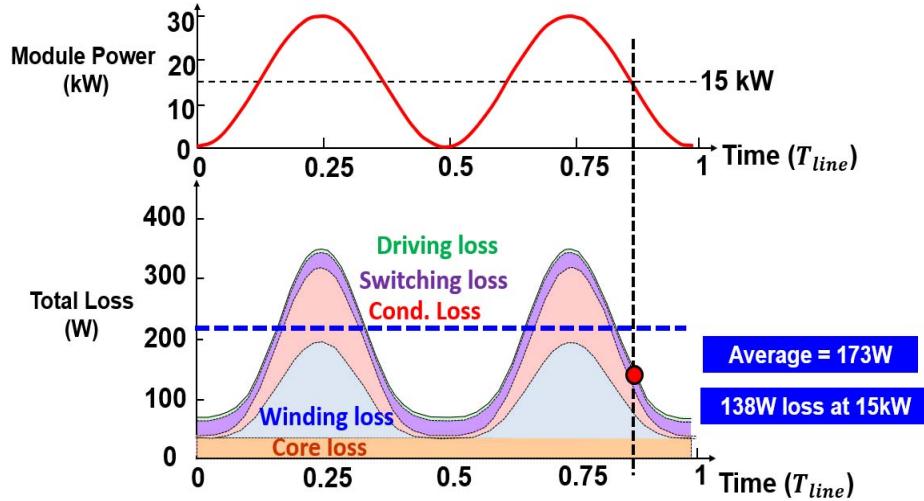

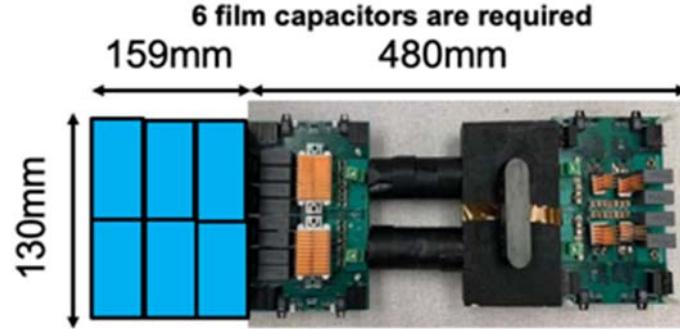

#### Fluctuating power flow control method for DC-DC stage in SST

Although aforementioned constant power flow method in the DC-DC stage is popular in many researches, one of the drawbacks of this control method is the bus capacitor. Film bus capacitor occupies more than 20% volume in the DC-DC converter. If using electrolytic capacitor, the volume will be smaller. However, the lifetime of the electrolytic capacitor will be another bottleneck. Some researchers proposed another control method for the SST system with the DC-DC stage work with fluctuating power flow. The idea for such control method is easy to understand. There is double line frequency power flow in each phase in the CHB stage. If the SST system allows no matter how much power flows in, the same amount of power flows out from the output. There is no requirement of the capacitor usage. Due to the three-phase system, the double line frequency for the three phases can be cancelled with each other at the output terminal. The output power will still be a constant value.

##### 1. Modeling and control with DC-DC fluctuating power flow

One of the easiest methods to achieve such DC-DC fluctuating power flow control is to use the DC-Transformer (DCX) concept at the DC-DC stage. The CLLC converter works as a transformer. There is no control ability in the converter to regulate the power flow. The control scheme is shown in Fig. 61.

Fig. 68 Control scheme with fluctuating power flow control in DC-DC stage

Compared with the control method with constant power flow in DC-DC stage, the control method with fluctuating power flow is much easier. The central controller only needs to sense 7 signals, input signals  $v_a, v_b, v_c, i_a, i_b, i_c$ , and output voltage  $V_o$ . The control goals for fluctuating power flow control includes PFC, bus voltage regulation, bus voltage balance and output voltage balance. In the fluctuating power flow control, output voltage is sensed for dq control to achieve PFC and bus voltage regulation instead of bus voltages in the constant power control. Consider one module as an example. Due to DCX,

$$V_{bus} = \frac{1}{n} V_o$$

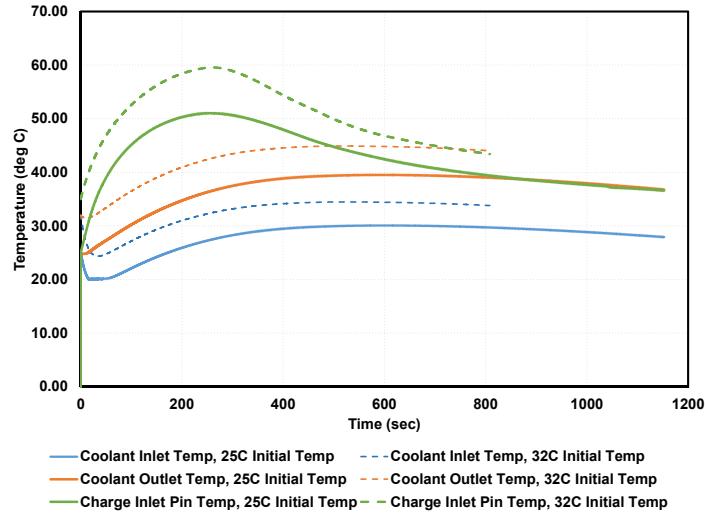

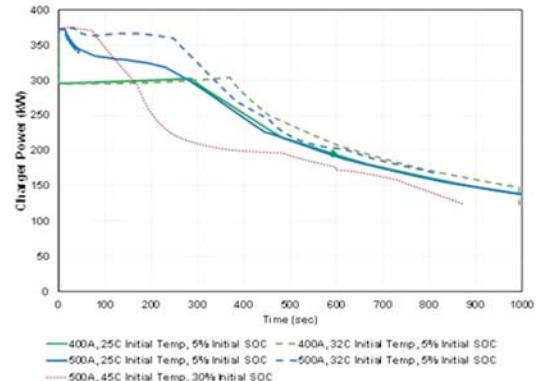

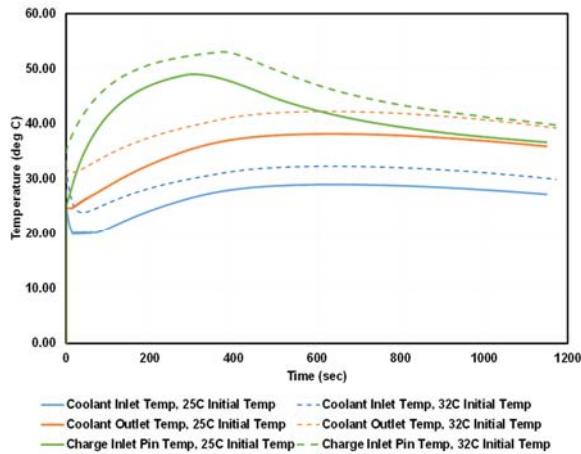

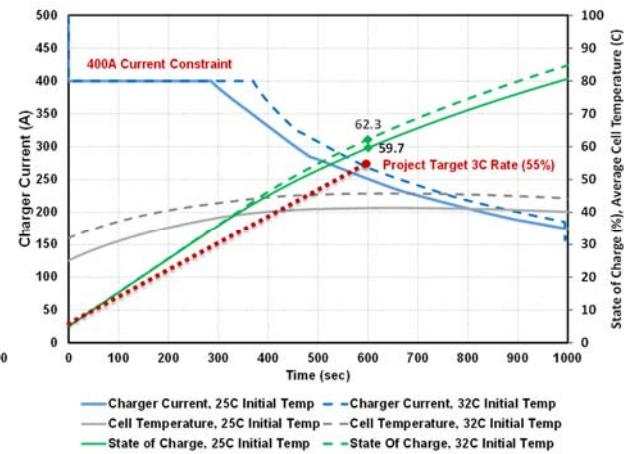

where  $n$  is the transformer turns ratio.