# Vertical GaN Devices for Medium-Voltage Power Electronics

*R. Kaplar<sup>1</sup>, A. Allerman<sup>1</sup>, M. Crawford<sup>1</sup>, B. Gunning<sup>1</sup>, J. Flicker<sup>1</sup>, A. Armstrong<sup>1</sup>, L. Yates<sup>1</sup>, J. Dickerson<sup>1</sup>, A. Binder<sup>1</sup>, V. Abate<sup>1</sup>, M. Smith<sup>1</sup>, G. Pickrell<sup>1</sup>, P. Sharps<sup>1</sup>, T. Anderson<sup>2</sup>, J. Gallagher<sup>2</sup>, A. G. Jacobs<sup>2</sup>, A. Koehler<sup>2</sup>, M. Tadjer<sup>2</sup>, K. Hobart<sup>2</sup>, J. Hite<sup>1</sup>, M. Ebrish<sup>3</sup>, M. Porter<sup>4</sup>, K. Zeng<sup>5</sup>, S. Chowdhury<sup>5</sup>, D. Ji<sup>6</sup>, O. Aktas<sup>7</sup>, and J. Cooper<sup>8</sup>*

<sup>1</sup>Sandia National Laboratories, Albuquerque, NM, USA

<sup>2</sup>Naval Research Laboratory, Washington, DC, USA

<sup>3</sup>National Research Council, Washington, DC, USA, residing at NRL

<sup>4</sup>Naval Postgraduate School, Monterey, CA, USA, residing at NRL

<sup>5</sup>Stanford University, Stanford, CA, USA

<sup>6</sup>Formerly at Stanford, now at Intel Corp., Santa Clara, CA, USA

<sup>7</sup>EDYNX Inc., Livermore, CA, USA

<sup>8</sup>Sonrisa Research Inc., Santa Fe, NM, USA

Sandia

National

Laboratories

The authors gratefully acknowledge the support of the ARPA-E OPEN+ Kilovolt Devices Cohort managed by Dr. Isik Kizilyalli

Special Session

on Medium- and

High-Voltage

Gallium Nitride

Power Devices

October 11,

2021

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

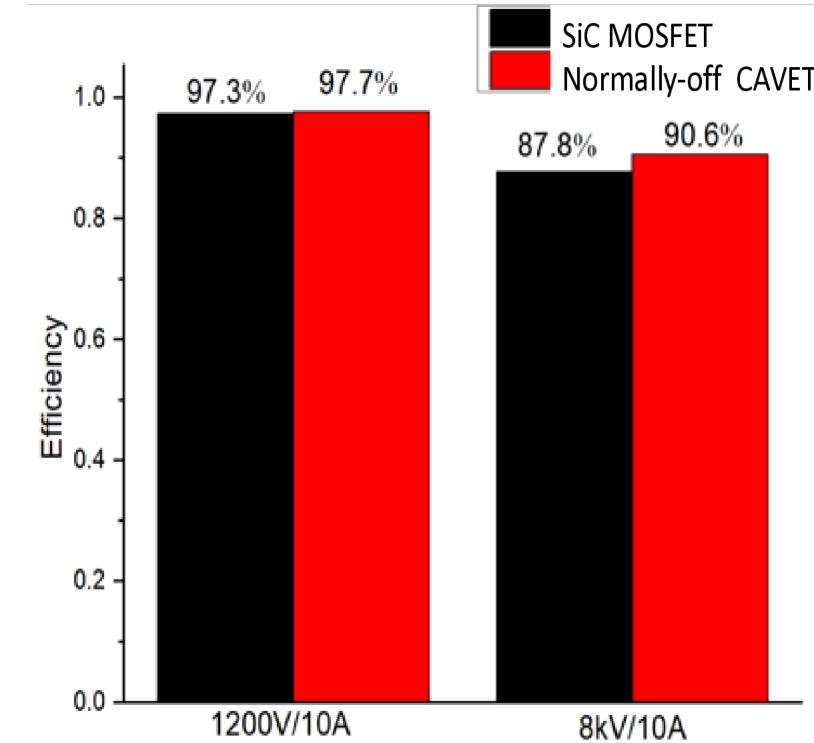

# GaN may be Advantageous when Scaled to Medium Voltage

- Critical field of GaN  $\sim 2.8$  MV/cm at  $N_D = 1 \times 10^{16}$  cm $^{-3}$  and room temperature based on most recent impaction ionization measurements [1]

- Slightly higher than  $E_C$  of SiC at the same temperature and doping [2]

- But higher mobility of GaN  $\sim 1200$  cm $^2$ /Vs [3] compared to  $\sim 950$  cm $^2$ /Vs for SiC [2] at the same doping and temperature lead to improvements in power converter efficiency [4]

- But devices are not widely available – a vertical GaN foundry is needed that monitors yield, reliability, etc.

[1] D. Ji, B. Ercan, and S. Chowdhury, "Experimental Determination of Impact Ionization Coefficients of Electrons and Holes in Gallium Nitride Using Homojunction Structures," *Appl. Phys. Lett.* **115**, 073503 (2019).

[2] J. A. Cooper and D. Morissette, "Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC," *Elec. Dev. Lett.* **41**, 892 (2020).

[3] I. C. Kizilyalli, A. P. Edwards, O. Aktas, T. Prunty, and D. Bour, "Vertical Power PN Diodes Based on Bulk GaN," *IEEE Trans. Elec. Dev.* **62**(2), 414 (2015).

[4] D. Ji and S. Chowdhury, "On the Progress Made in GaN Vertical Device Technology – Special Issue on Wide Band Gap Semiconductor Electronics and Devices," *Int. J. High-Speed Elec. Sys.* **28**(01n02), 1940010 (2019).

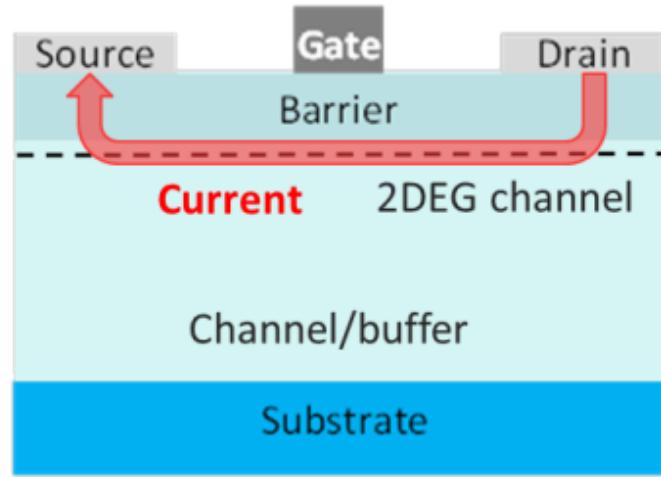

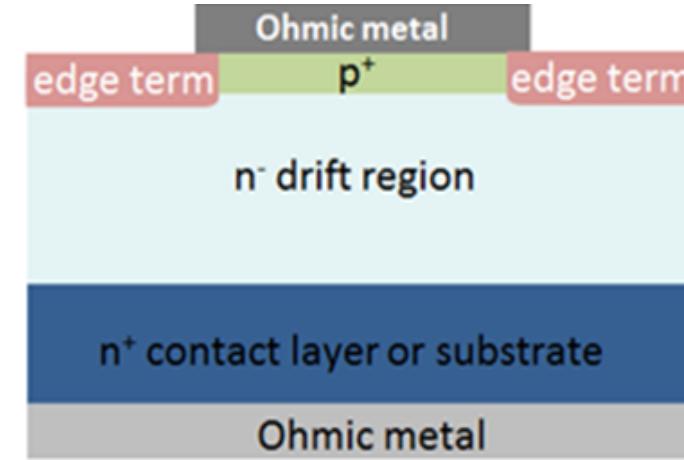

# Lateral vs. Vertical GaN Power Devices

High Electron Mobility Transistor (HEMT)

Vertical PN Diode

## Lateral Device

- Current flow and voltage drop parallel to surface

- Availability of heterostructures is an advantage

- Electric field management is challenging – voltage scaling is lateral (consumes more chip area)

- Commercial GaN power devices available from many manufacturers, but generally <650 V

## Vertical Device

- Current flow and voltage drop perpendicular to surface

- Architecture is better-suited to high voltage devices – voltage scaling accomplished by thickening drift region (does not consume more chip area)

- But requires native substrates and low doping

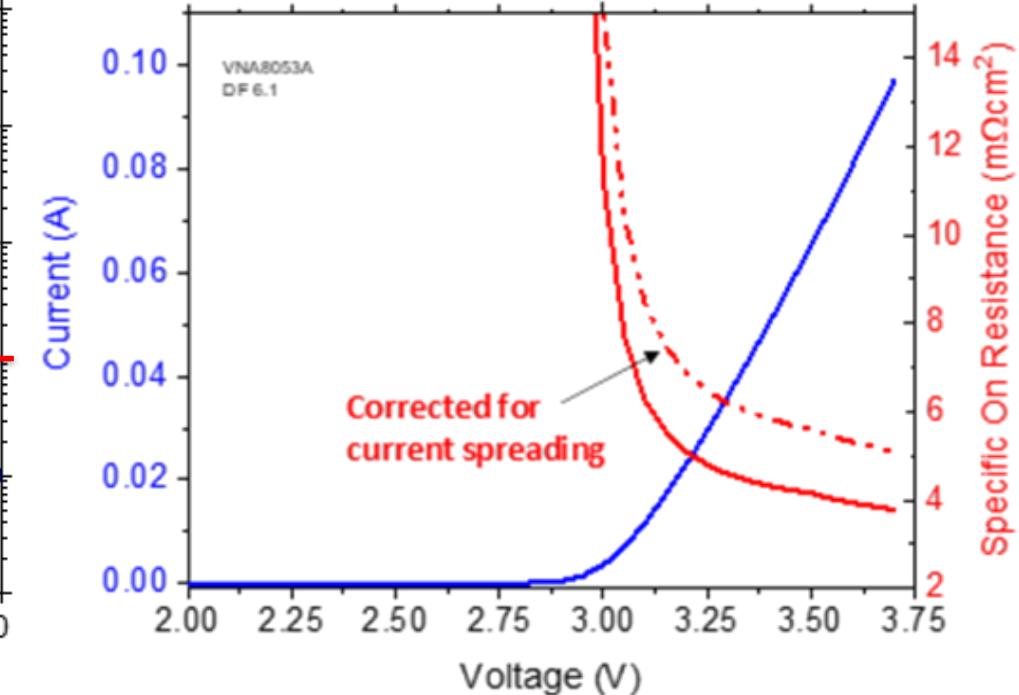

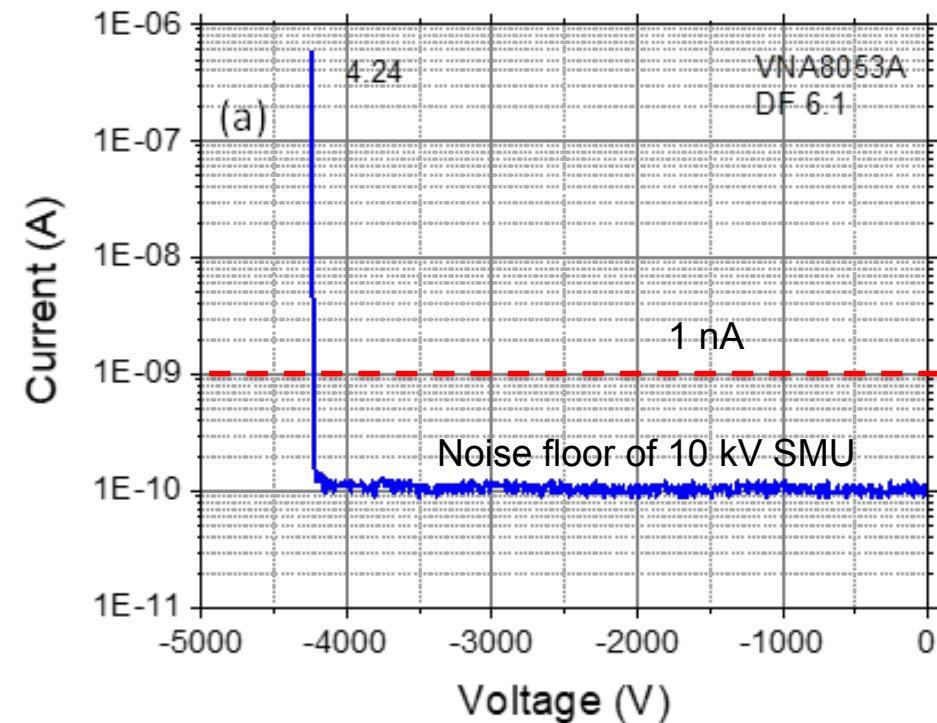

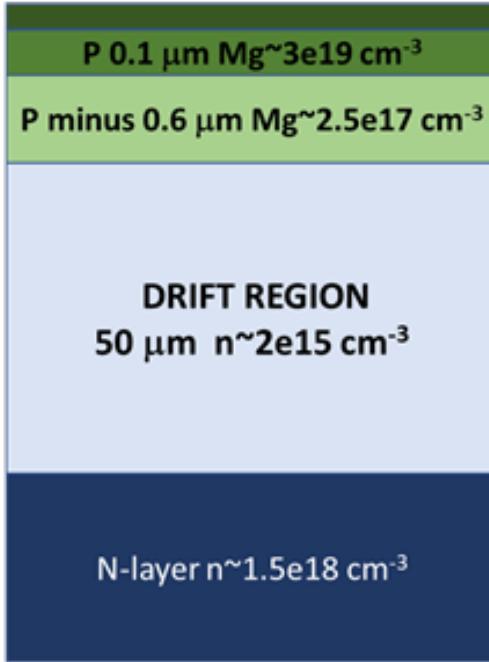

# IV Curves for Representative MV Vertical GaN PN Diode

- MOCVD growth, step-etched JTE (30  $\mu\text{m}$  step width for device below)

- Device shown has 0.063  $\text{mm}^2$  area; 1  $\text{mm}^2$  devices also fabricated and tested

- $V_b \sim 4.2 \text{ kV}$  with very low leakage current until breakdown; not clear if limited by drift region or JTE

- Current spreading assumes 45-degree angle  $\rightarrow R_{\text{sp,}on} = 5.1 \text{ m}\Omega \text{ cm}^2$

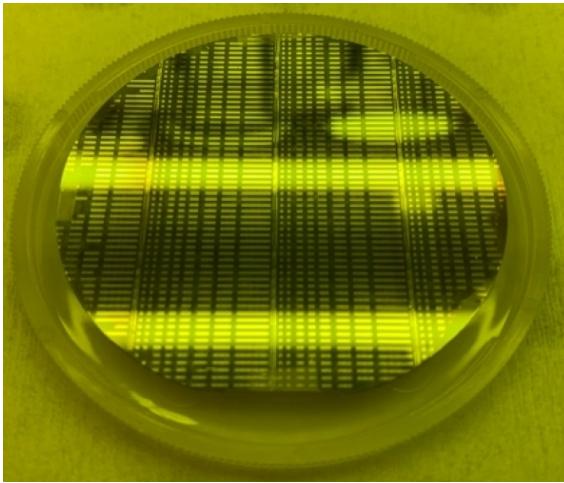

# Commercialization Potential: Vertical GaN Foundry

| Lot | # of wafers | Experiments                                            |

|-----|-------------|--------------------------------------------------------|

| 1   | 2           | Edge termination                                       |

| 2   | 4           | Vary Anode thickness<br>Alignment to dot-core          |

| 3   | 4           | Type I (uniform) substrates                            |

| 4   | 4           | Vary drift layer thickness                             |

| 5   | 6           | Vary anode doping and other process variations         |

| 6   | 4           | Baseline Process w/ improved epi and high yield wafers |

| 7   | 3           | Baseline Process w/ improved epi and new mask          |

| 8   | 4           | New mask, varying implant profiles                     |

| 9   | 4           | Large-area mask, Back side process demo                |

- **Epitaxial growth done at Sandia by MOCVD and wafers delivered to NRL for characterization and processing**

- **35 wafers delivered to date, 23 processed through metals/isolation**

- **>26,000 devices processed to date**

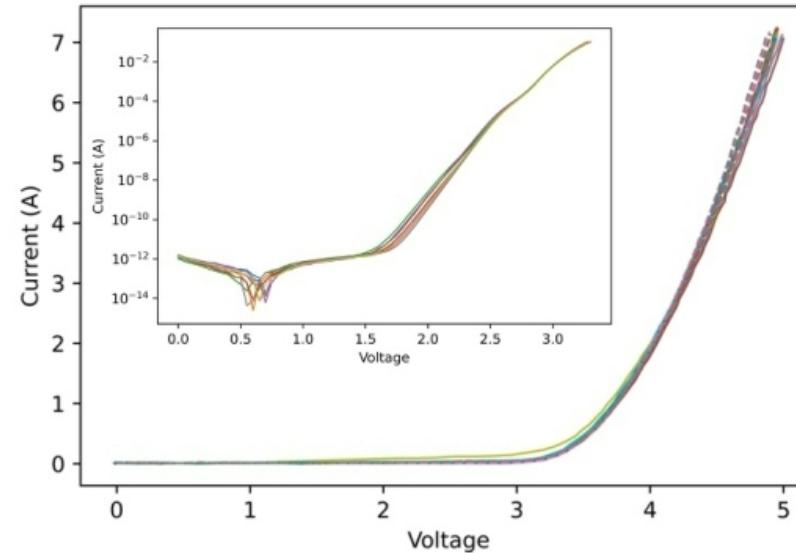

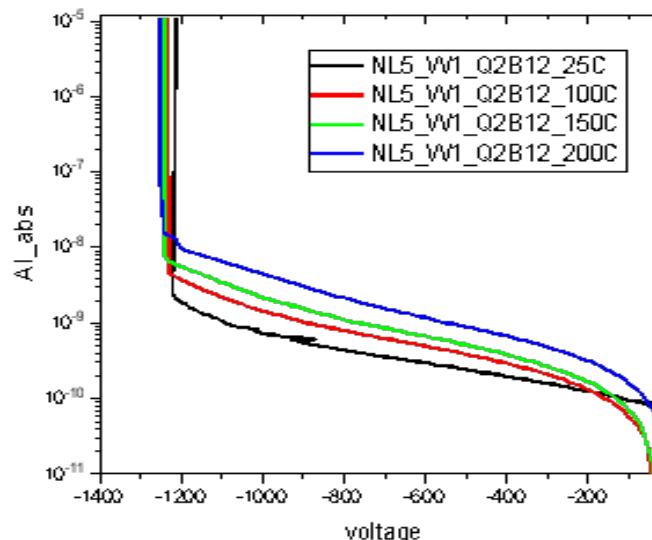

# Foundry Electrical Testing and Results

Typical foundry wafer

Wafer under test

## Forward IV:

- Several amps of current demonstrated for  $1 \text{ mm}^2$  devices

## Reverse IV:

- $>1.3 \text{ kV}$  breakdown demonstrated

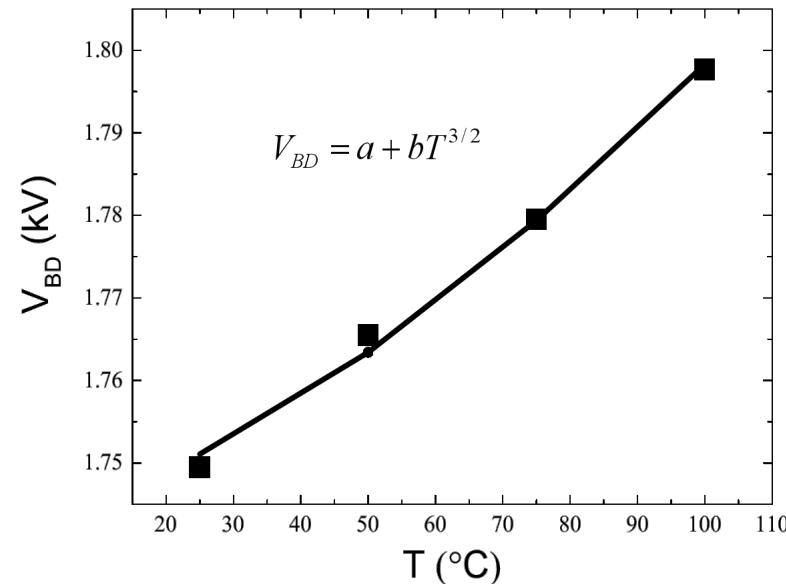

- Positive temperature coefficient of breakdown consistent with avalanche

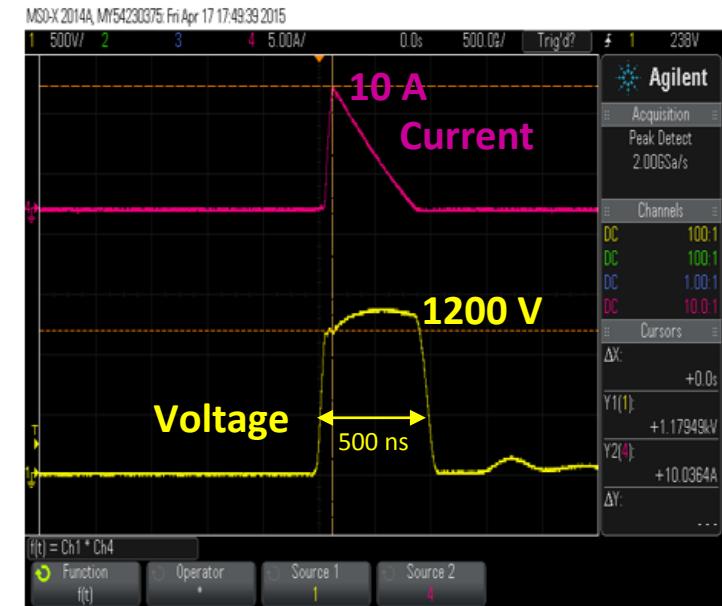

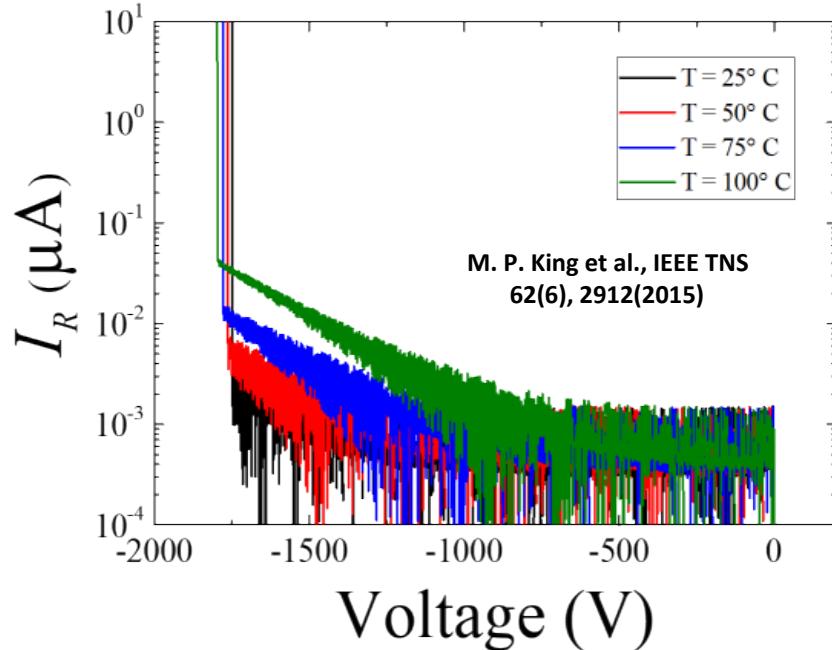

# Avalanche Ruggedness of Vertical GaN

- Avalanche breakdown mechanism demonstrated via temperature dependence

- Avalanche ruggedness demonstrated in real power switching circuits

- Very different from the situation for GaN-on-Si power devices, where avalanche breakdown does not occur

O. Aktas and I. C. Kizilyalli, IEEE EDL 36(9), 890 (2015)

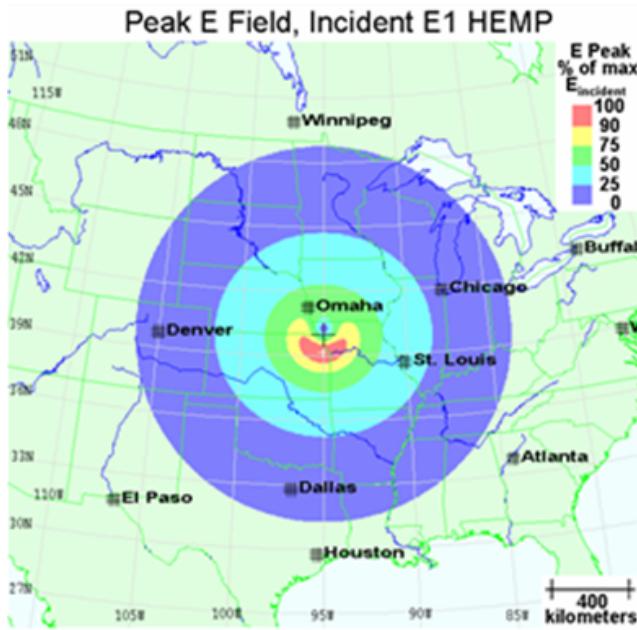

# Special Application: Protection for the Electric Grid

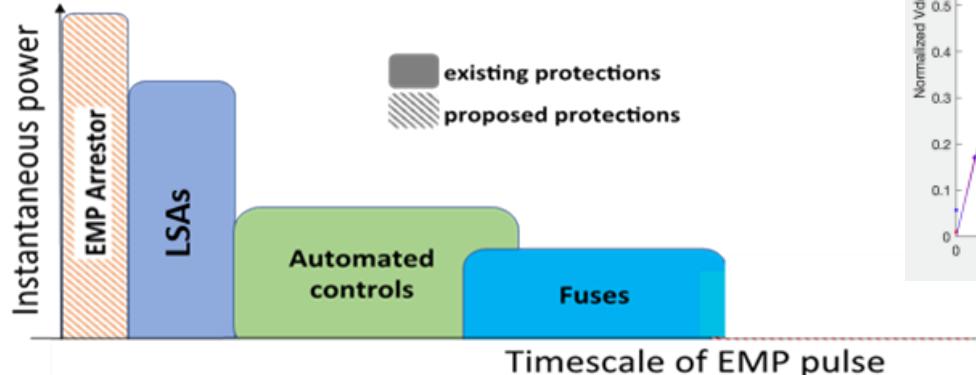

➤ Transient protection is needed for MV grid-connected systems

- Electromagnetic pulses are a threat to the grid

- Very fast E1 component (< 1 ms)

- Unaddressed by current SOA technology (LSAs)

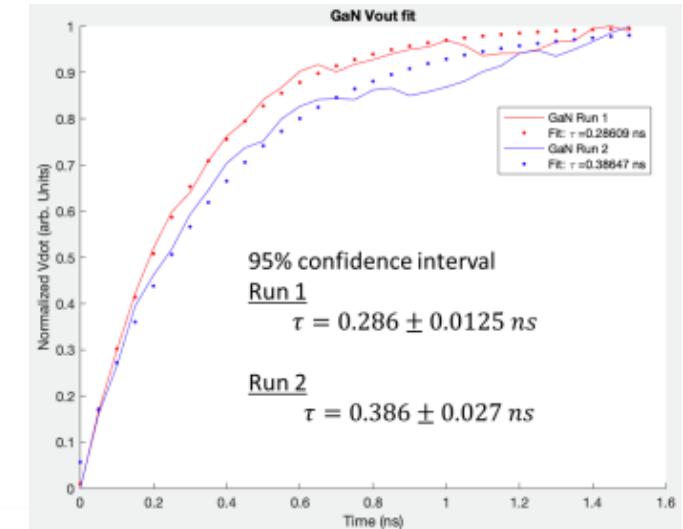

Use fast avalanche to clamp voltage and shunt current to protect grid equipment

GaN time to breakdown <1 ns

Questions?

Bob Kaplar: [rjkapla@sandia.gov](mailto:rjkapla@sandia.gov)