# Process Development & Forensics of SOI Nanoscale Membranes

Ryan Stewart | Tom Harris | John Nogan | Don Bethke

## Introduction & Motivation

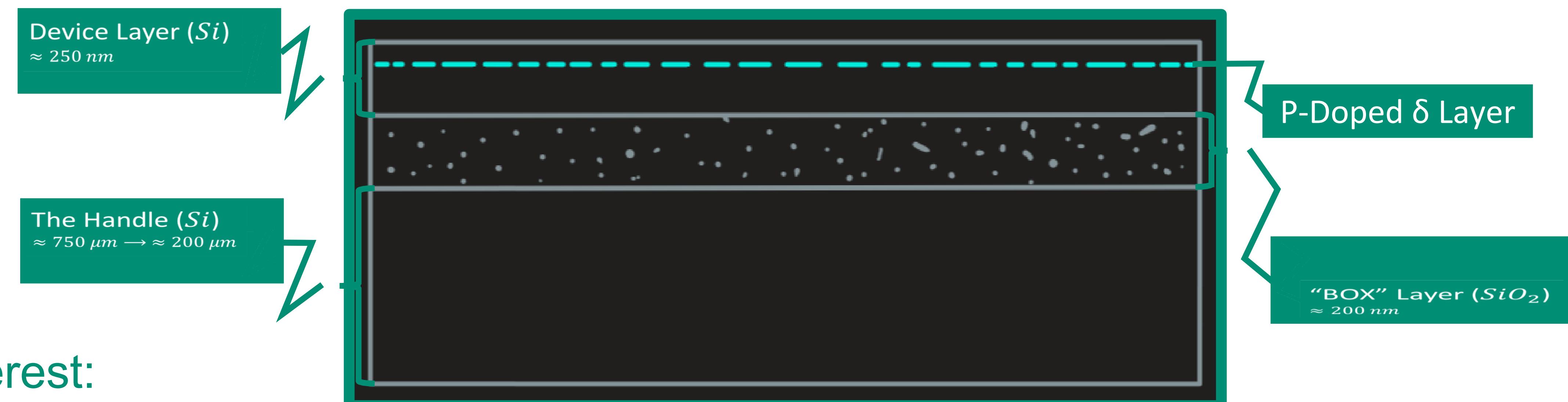

**Motivation:** Understand and measure thermopower in a P-doped quantum material.

Michelle Simmons: Queen of Quantum Computers

SNL: Shashank Misra & Ezra Bussman

### Measurements of Interest:

- Carrier Type, Density, and Mobility

- Seebeck Coefficient

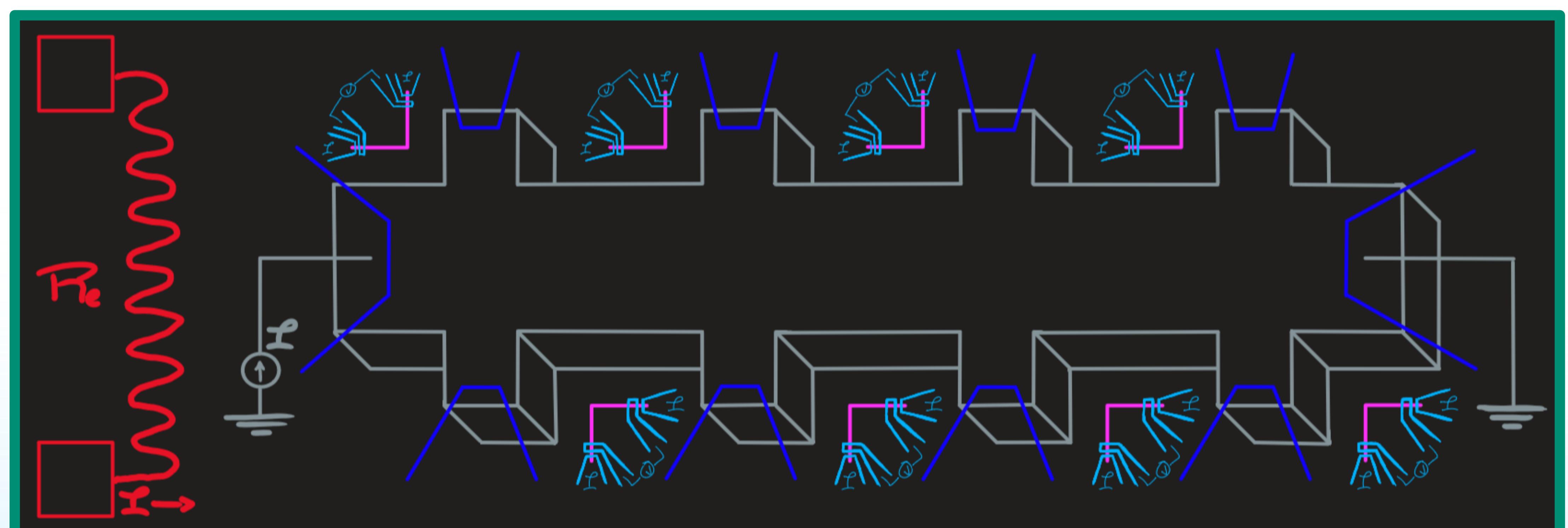

Hall Bar with a Heater and a ton of Thermometers

### The Seebeck Coefficient

$$S = \frac{\partial V}{\partial T} = - \frac{\Delta V}{\Delta T}$$

## Introduction & Motivation Continued

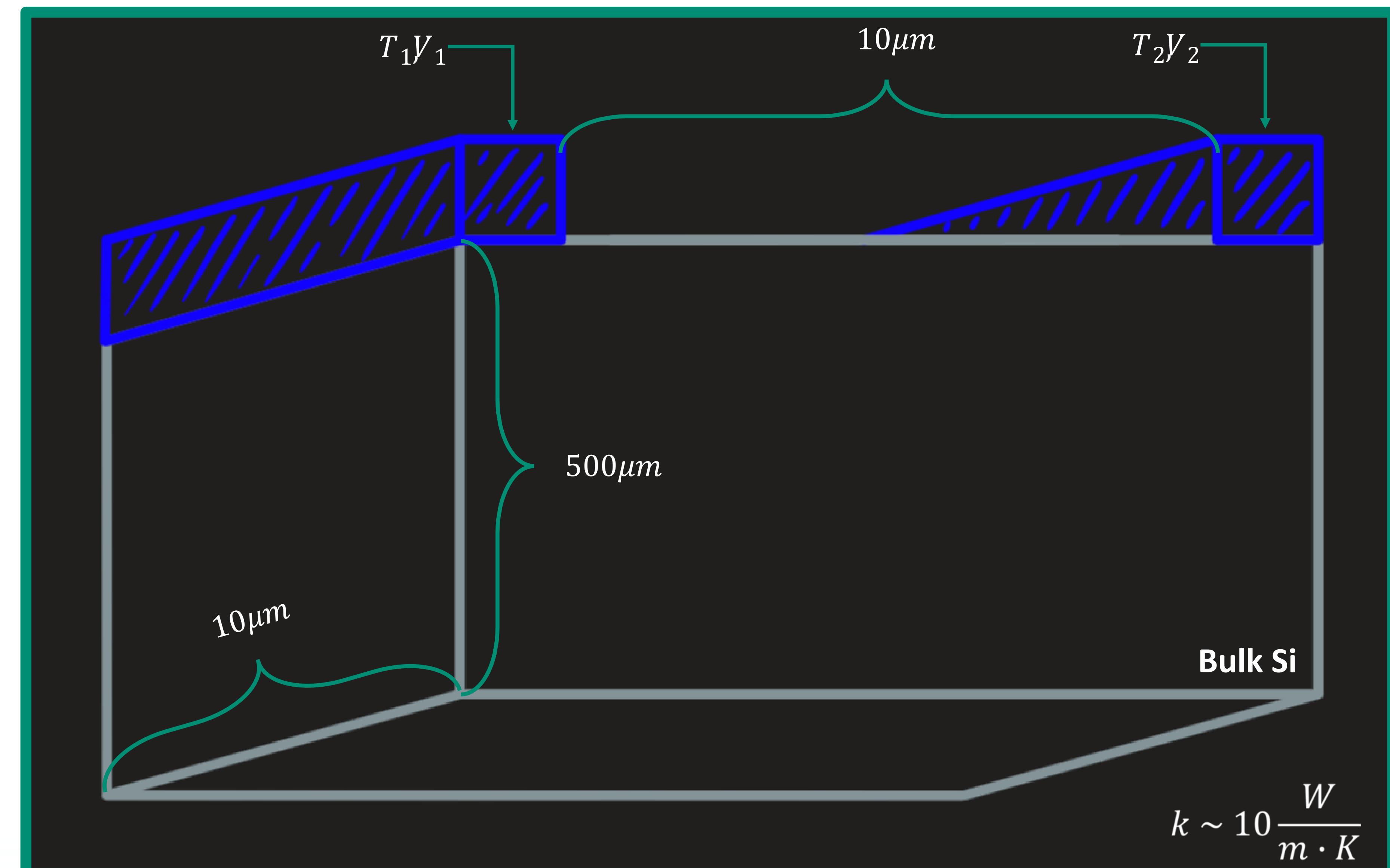

### Why SOI?

#### Thermal Ohm's Law

$$\Delta T = R_{th} \dot{Q}$$

$$\text{Where } R_{th} = \frac{L}{k_A} = \frac{L}{k_{WT}}$$

$$\Rightarrow R_{th, Si} = \frac{10\mu m}{(10 \frac{W}{m \cdot K})(500\mu m)(10\mu m)} = 200 \frac{K}{W}$$

Therefore, to achieve a temperature difference of 1 K we will need

$$\Rightarrow \dot{Q}_{Si} = \frac{\Delta T}{R_{th, Si}} = \frac{1K}{200 \frac{K}{W}} = 5mW$$

#### Cryogenic System Power Output Limits:

- ➔  $^3He$  can produce  $40\mu W$  of cooling power

- ➔ Dilution Fridge can produce between  $200\mu W$  and  $400\mu W$  of cooling power

& if we compare

$$t_{Si} = 500\mu m \text{ vs. } t_{SOI} = 250nm$$

#### Nominal Dimensions for Optical Lithography Patterning

$$\Rightarrow \dot{Q}_{SOI} = 2.5\mu W \text{ (2000 times less!!)}$$

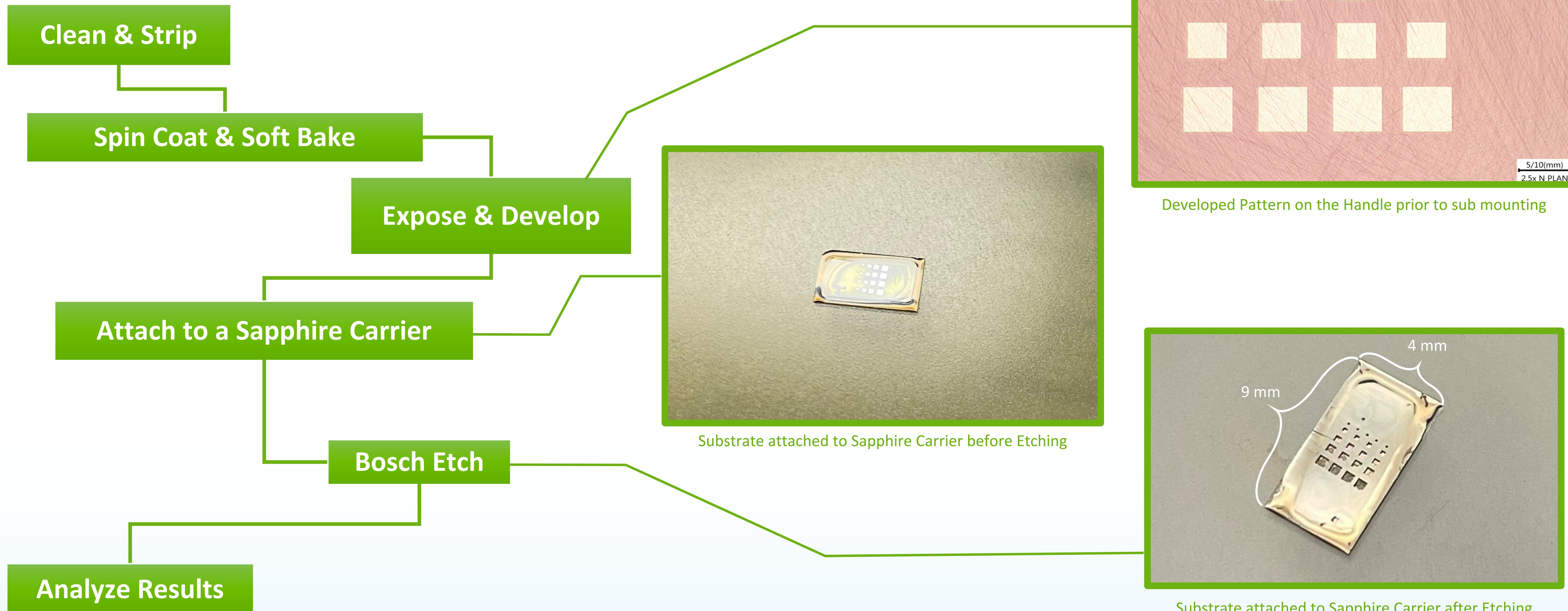

# Approach

# QUESTION: How big of a membrane can we make?

# My Process Flow

# Challenges

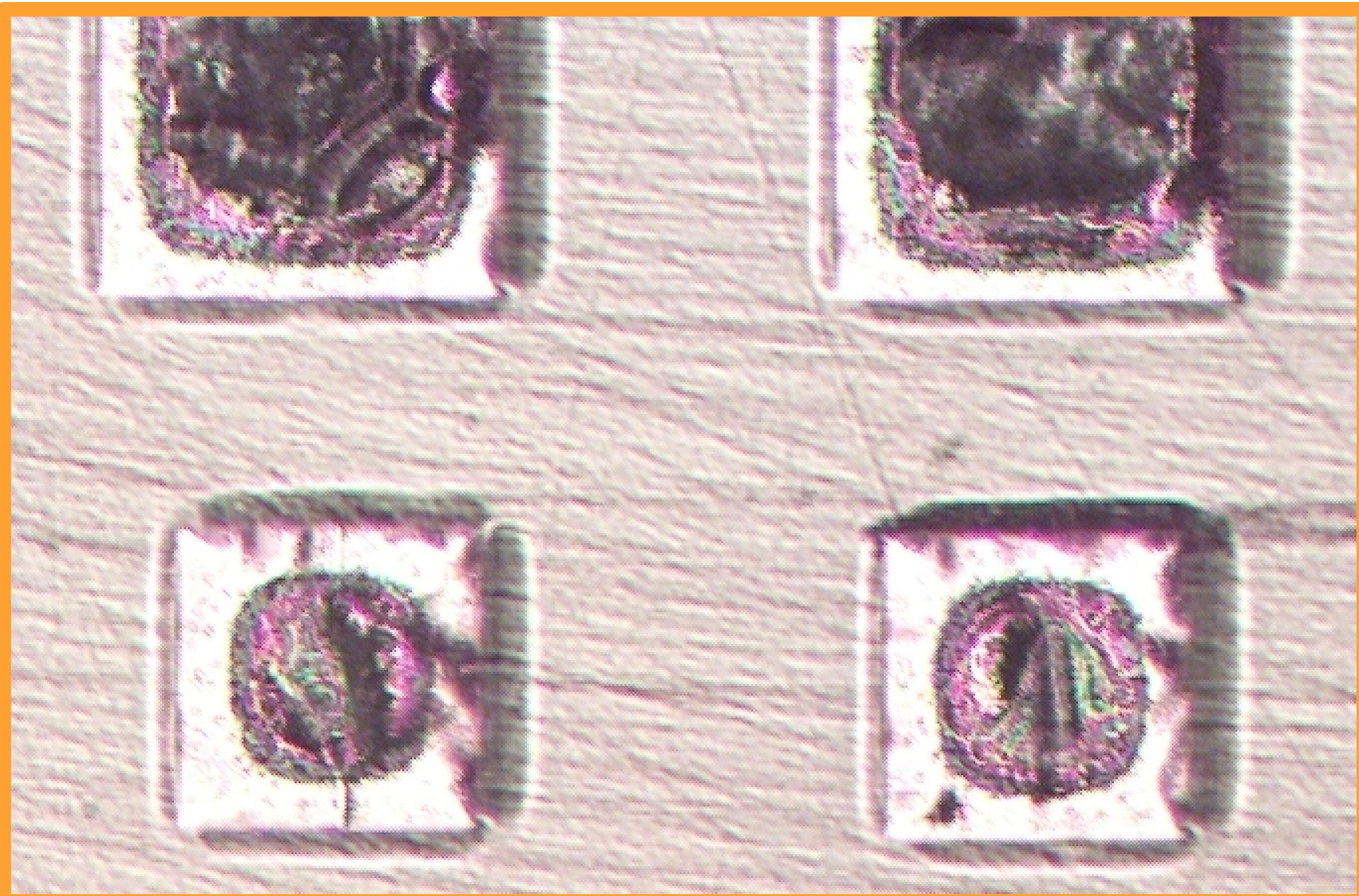

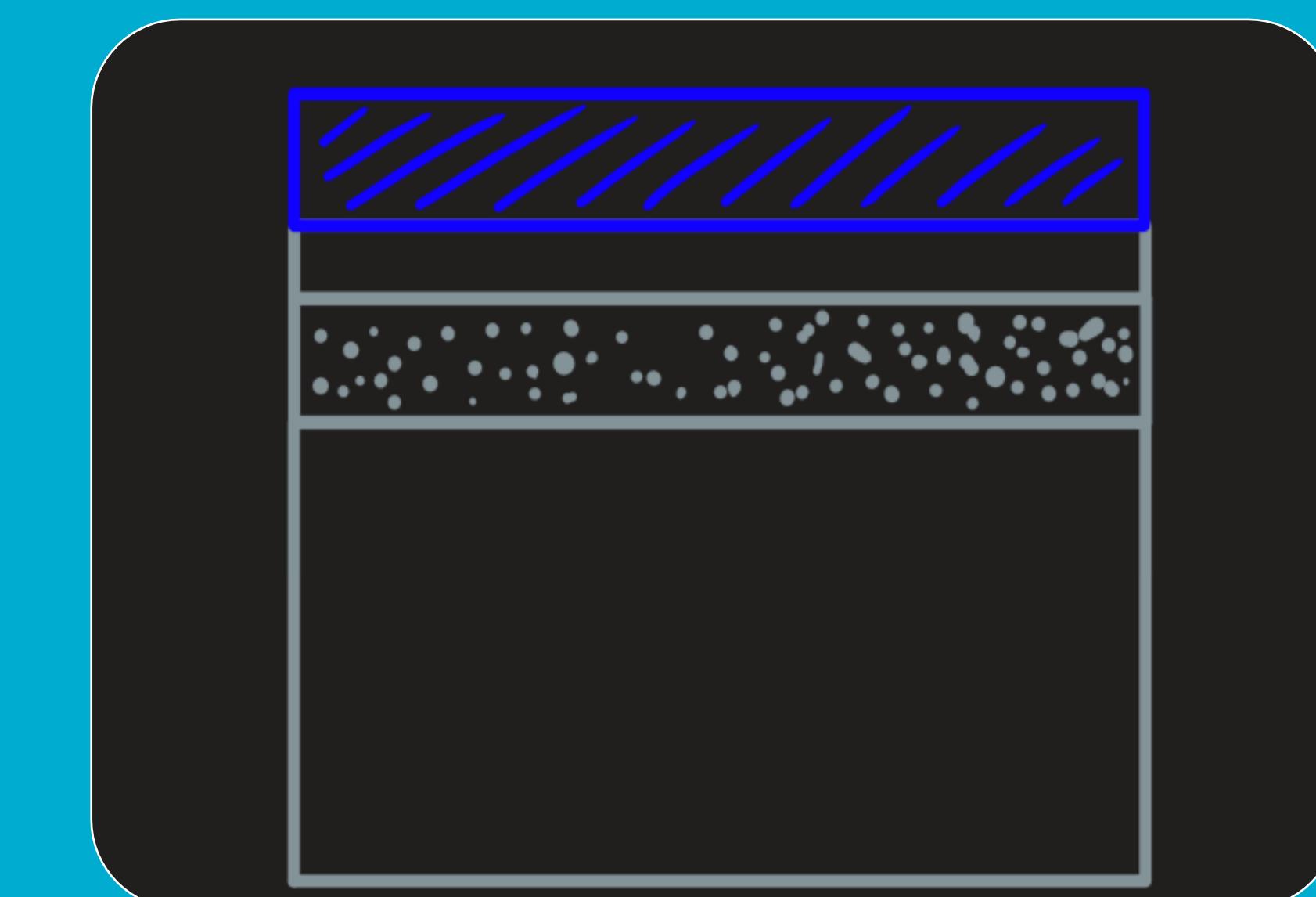

## 1.) Depleted Resist & Blown Out Membranes

### Our Response:

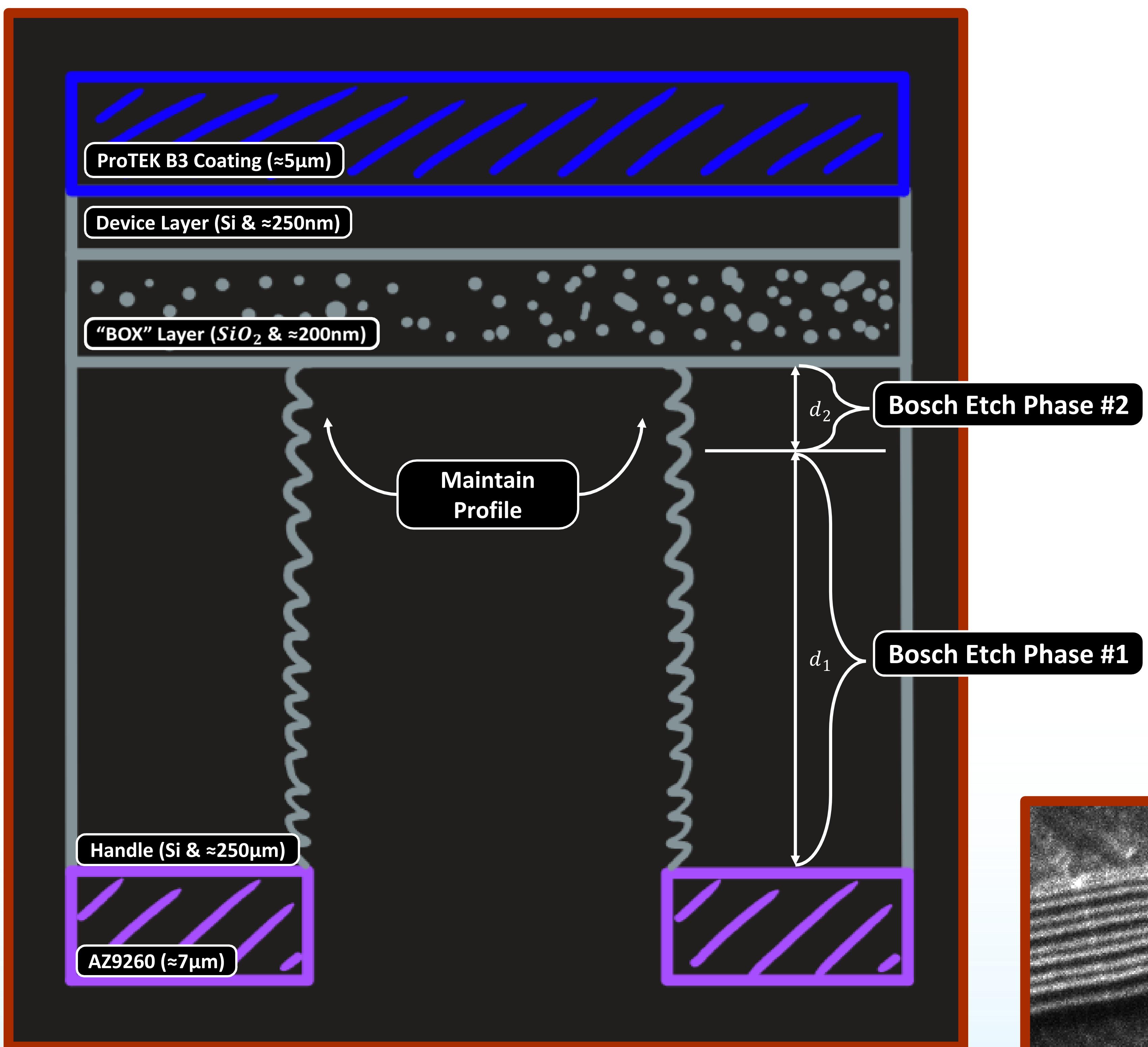

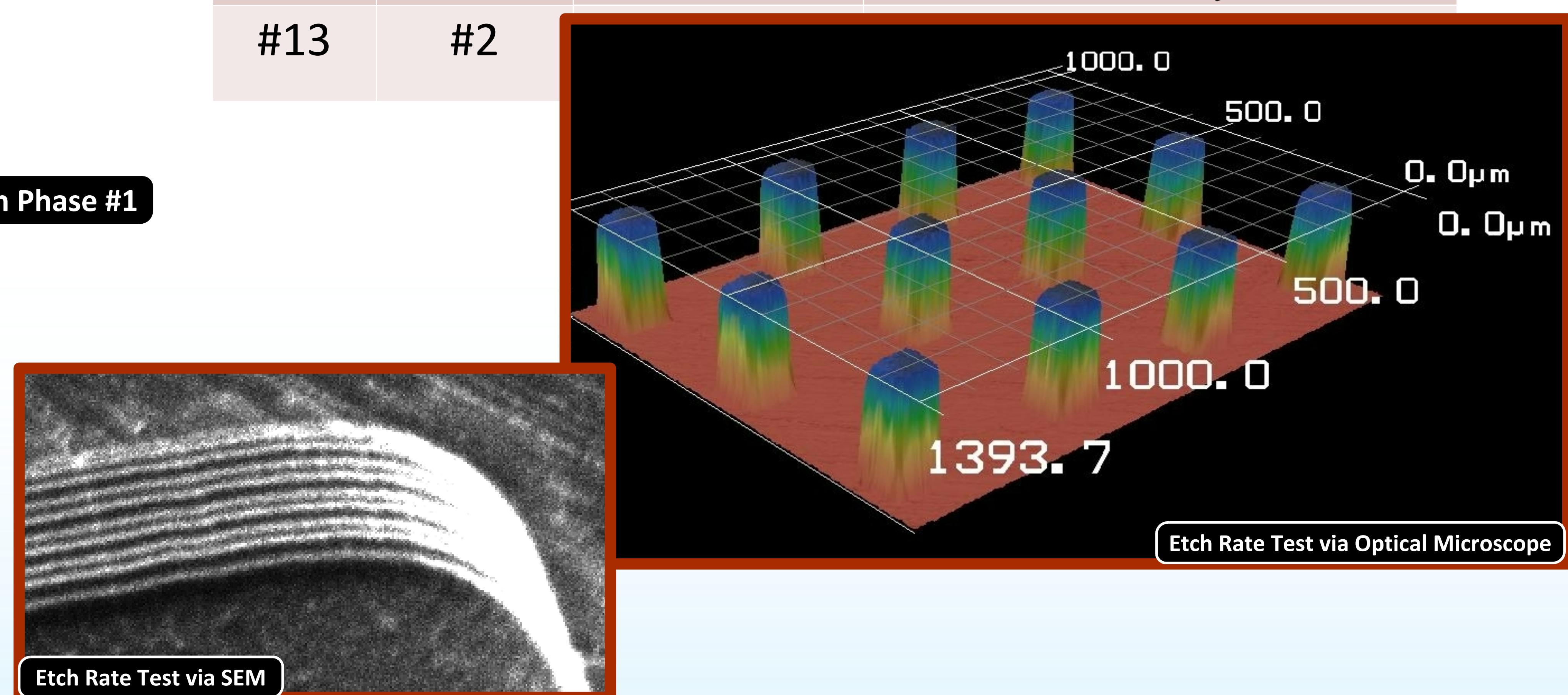

- 1) Thicker Resist & Si Etch Rate Test

- 2) Bosch Etch with a 2 Phase Process

- 3) Add Protective Coating to the Device Layer, such as ProTEK B3

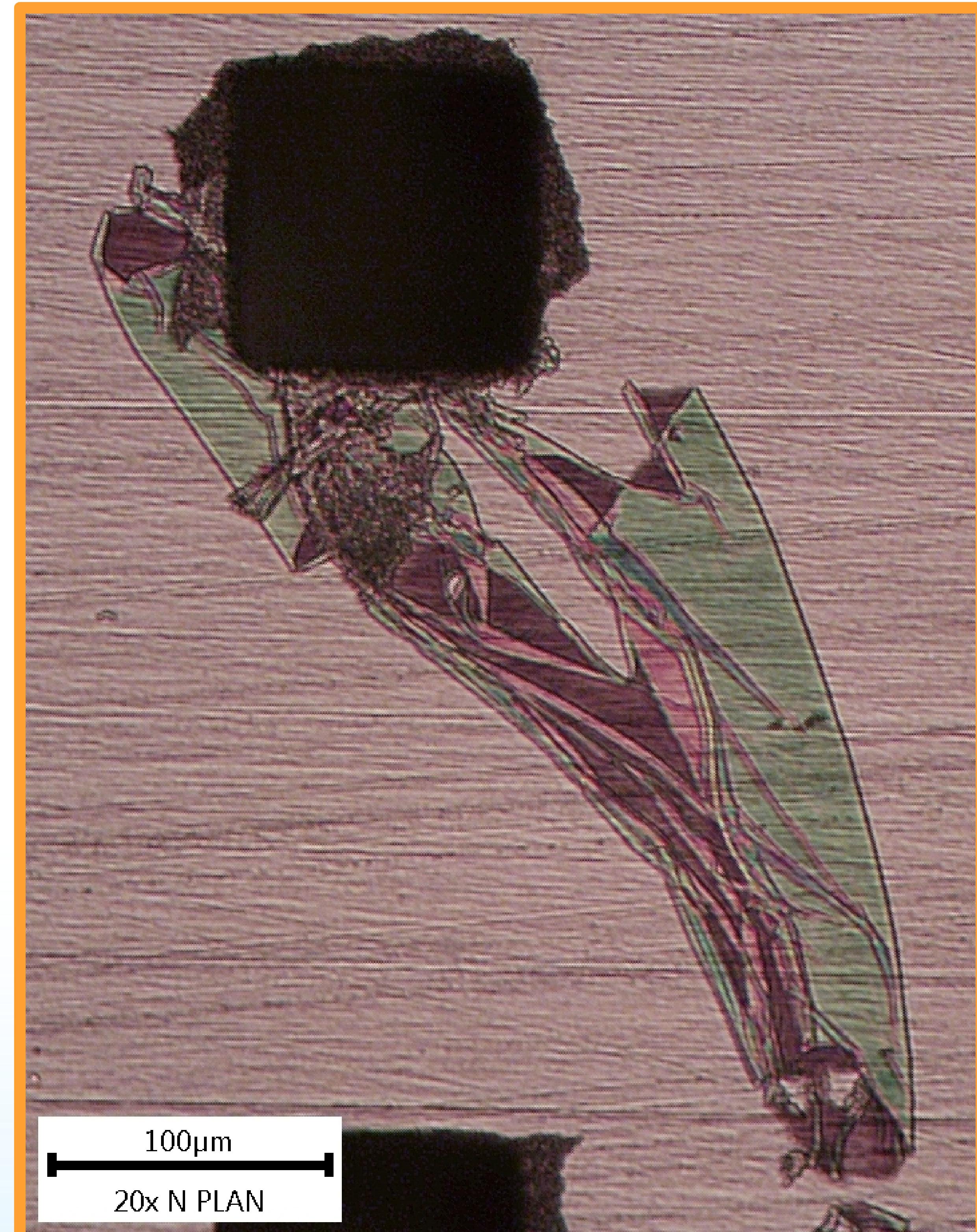

## 2.) Directional Control Issue

## 3.) Mechanical Failure Evidence

# Process Development & Forensics of SOI Nanoscale Membranes

Ryan Stewart | Tom Harris | John Nogan | Don Bethke

## Results

### Quantified Etch Rates & Developed Lithography and Etching Recipes

| Test | Phase | Material         | Etch Rate                                     |

|------|-------|------------------|-----------------------------------------------|

| #2   | #1    | Si               | $\sim 0.604 \frac{\mu\text{m}}{\text{cycle}}$ |

| #6   | #1    | SiO <sub>2</sub> | $\sim 4.3 \frac{\text{nm}}{\text{cycle}}$     |

| #6   | #1    | AZ9260           | $\sim 15 \frac{\text{nm}}{\text{cycle}}$      |

| #7   | #1    | Si               | $\sim 0.623 \frac{\mu\text{m}}{\text{cycle}}$ |

| #11  | #2    | Si               | $\sim 0.762 \frac{\mu\text{m}}{\text{cycle}}$ |

| #13  | #2    |                  |                                               |

## Ongoing &amp; Future Work

## Using a Polymer as Structural Support

→ Spin coat the device layer before spin resist on the handle.

→ For Example, a ProTEK B3 Coating is used to protect delicate front-side circuitry during back-side micromachining.

## Use an SOI with a thicker BOX and Device

→ Pro: Increases the structural integrity

→ Con: New process needed for embedding Phosphine