DE-EE0008604

GE Global Research

# A MEMS Gyroscope for Reliable Long Duration Measurement While Drilling at 300°C

## Final technical report draft

**Federal Agency and Organization:** DOE EERE – Geothermal Technologies Program

**Recipient Organization:** General Electric Company

GE Global Research

1 Research Circle

Niskayuna, NY 12309

**Award Number:** DE-EE0008604

**Project Period:** 03/01/2019 – 08/31/2021

**Principal Investigator:** Emad Andarawis

Principal Engineer - Microelectronics

**Project Partners:** Inertial Wave Inc.

**DOE Project Team:** DOE Contracting Officer – Kristin Johnson

DOE Project Officer – Angel Nieto

Project Monitor – Lindsay Morse

Signature *Emad Andarawis* Date 1/24/2022

## Acknowledgements

This material is based upon work supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) under the Geothermal Program Office, Award Number DE-EE0008604.

## Disclaimer

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## Authors and contributors

David Lin, Jeremy Popp, Robert MacDonald, Brian Scherer, David Shaddock, Dorin Calbaza, Tammy Johnson, Timothy Toepfer, Thomas Stecher, Emad Andarawis – GE Research

Dorian Challoner, Eric Wittinger, Peter Bond – InertialWave

## Table of Contents

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| Acknowledgements .....                                                         | 2  |

| Disclaimer .....                                                               | 2  |

| Authors and contributors .....                                                 | 2  |

| Table of Figures .....                                                         | 6  |

| Table of tables.....                                                           | 10 |

| Executive Summary .....                                                        | 11 |

| Project Overview .....                                                         | 13 |

| Summary of project accomplishments.....                                        | 15 |

| Performance entitlement validation .....                                       | 15 |

| Electronics capability.....                                                    | 15 |

| Packaging capability .....                                                     | 16 |

| Fabrication capability .....                                                   | 16 |

| Significant findings and achievements .....                                    | 18 |

| 10X performance improvement over the state-of-the-art.....                     | 18 |

| 300°C operation, 600°C survivability.....                                      | 19 |

| New gyroscope package with high reliability and 10X volume reduction .....     | 20 |

| Highly integrated, high temperature capable SOI-based electronics design ..... | 20 |

| Detailed technical achievements.....                                           | 21 |

| MRGT Device Design and Capability .....                                        | 21 |

| MRGT Device critical performance parameters to meet requirements .....         | 21 |

| MRGT design parameters .....                                                   | 24 |

| MRGT device testing approach .....                                             | 28 |

| Wafer Level Testing .....                                                      | 28 |

| Packaged device test and characterization.....                                 | 32 |

| MRGT device characteristics over temperature.....                              | 33 |

| MRGT device design summary .....                                               | 37 |

| Fabrication Process Capability Advancement .....                               | 37 |

| Wafer fabrication improvements .....                                           | 41 |

| Device packaging advancements .....                                            | 41 |

DE-EE0008604: A MEMS Gyroscope for Reliable Long Duration Measurement While Drilling at 300°C

|                                                                |    |

|----------------------------------------------------------------|----|

| Fabrication process capability advancement summary .....       | 44 |

| Electronics requirement development: .....                     | 44 |

| MRGT 2-DOF Analytical Model .....                              | 44 |

| ASIC Interface Requirements .....                              | 47 |

| Board-level testing and validation of electronics design. .... | 56 |

| High Temperature ASIC design .....                             | 57 |

| Objective and scope .....                                      | 57 |

| Simulation results .....                                       | 59 |

| High voltage driver .....                                      | 60 |

| Closed loop controller .....                                   | 61 |

| Analog front end (AFE) .....                                   | 63 |

| Phase locked loop (PLL) .....                                  | 66 |

| ASIC testability features .....                                | 67 |

| ASIC electronics development summary .....                     | 70 |

| ASIC Electronics component testing .....                       | 72 |

| ASIC test board description .....                              | 72 |

| ASIC packaging .....                                           | 73 |

| Test results .....                                             | 74 |

| Functional testing .....                                       | 74 |

| High temperature testing .....                                 | 79 |

| TIA high gain mitigation .....                                 | 81 |

| ASIC validation and comparison with simulation summary .....   | 82 |

| Integrated system development and testing .....                | 83 |

| Testing objectives and success criteria .....                  | 83 |

| Success criteria.....                                          | 83 |

| Functional capability demonstration .....                      | 83 |

| Performance capability evaluation .....                        | 84 |

| Lifetime capability.....                                       | 84 |

| Integrated gyroscope test platform description.....            | 85 |

| Thermal gradient testing .....                                 | 86 |

|                                                              |     |

|--------------------------------------------------------------|-----|

| High temperature ceramic test board.....                     | 90  |

| Ceramic board fabrication assembly and test process .....    | 93  |

| ASIC data collection interface board.....                    | 97  |

| Heating and rotation capability .....                        | 100 |

| Support instrumentation.....                                 | 100 |

| Integrated system functional testing .....                   | 100 |

| Test description .....                                       | 100 |

| Functional testing results .....                             | 102 |

| Test result discussion, performance assessment, gaps .....   | 106 |

| Long-term testing .....                                      | 106 |

| MRGT component reliability testing .....                     | 107 |

| Baseline data.....                                           | 109 |

| Interval testing .....                                       | 110 |

| Test results, stability over time .....                      | 110 |

| Failure analysis.....                                        | 111 |

| Post repair testing success and results .....                | 112 |

| Integrated gyroscope test summary .....                      | 113 |

| Milestone List from SOPO and Progress Made Against Each..... | 114 |

| Summary of key project task outcomes.....                    | 118 |

| MRGT design .....                                            | 118 |

| MRGT Fabrication: .....                                      | 118 |

| MRGT Component Test:.....                                    | 118 |

| Electronics and Controls.....                                | 118 |

| Packaging: .....                                             | 119 |

| System Integration and testing: .....                        | 119 |

| Other project outputs:.....                                  | 119 |

| Submitted Reports .....                                      | 119 |

| Publications, Abstracts and Presentations.....               | 121 |

| Summary and Conclusions .....                                | 122 |

| References.....                                              | 122 |

## Table of Figures

|                                                                                                                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1 Progress and TRL advancement from concept to 300°C capable gyroscope with demonstrated >1000 hours of lifetime.....                                                                                                                                 | 15 |

| Figure 2 (A) Wafer containing 45 MRGT die. (B) Single MRGT die. (C) Allan Deviation measurement on GE's MRGT prototype, showing angle random walk of 0.003 °/rt(hr) and bias instability of 0.01 °/hr. ....                                                  | 18 |

| Figure 3 Performance and temperature capability of COTS devices surveyed. (a) Best performing devices have bias instabilities approaching 0.1 deg/hr at room temperature. (b) None of the devices can operate at 300°C - there is ~200°C capability gap..... | 19 |

| Figure 4 Wafer-level packaged MRGT Q-factor characterization over temperature.....                                                                                                                                                                           | 23 |

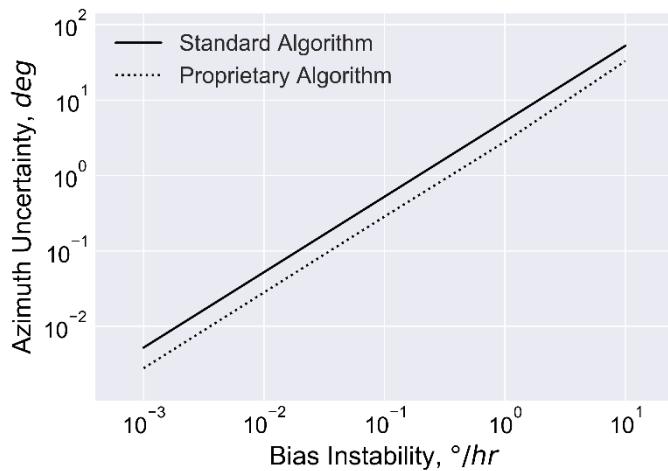

| Figure 5 Azimuth uncertainty as a function of the bias instability of the gyroscope.....                                                                                                                                                                     | 23 |

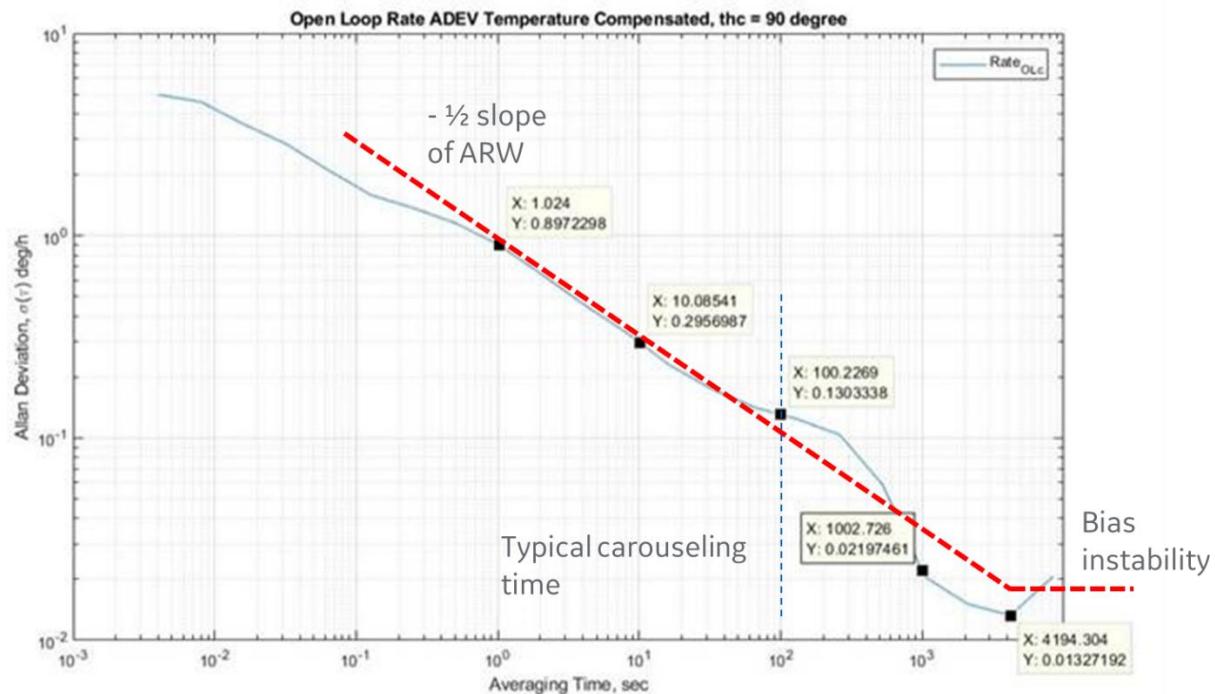

| Figure 6 Allan Deviation of the MRGT at room temperature showing the relationship between ARW, -1/2 slope, bias instability and the 100s integration time for carouseling .....                                                                              | 24 |

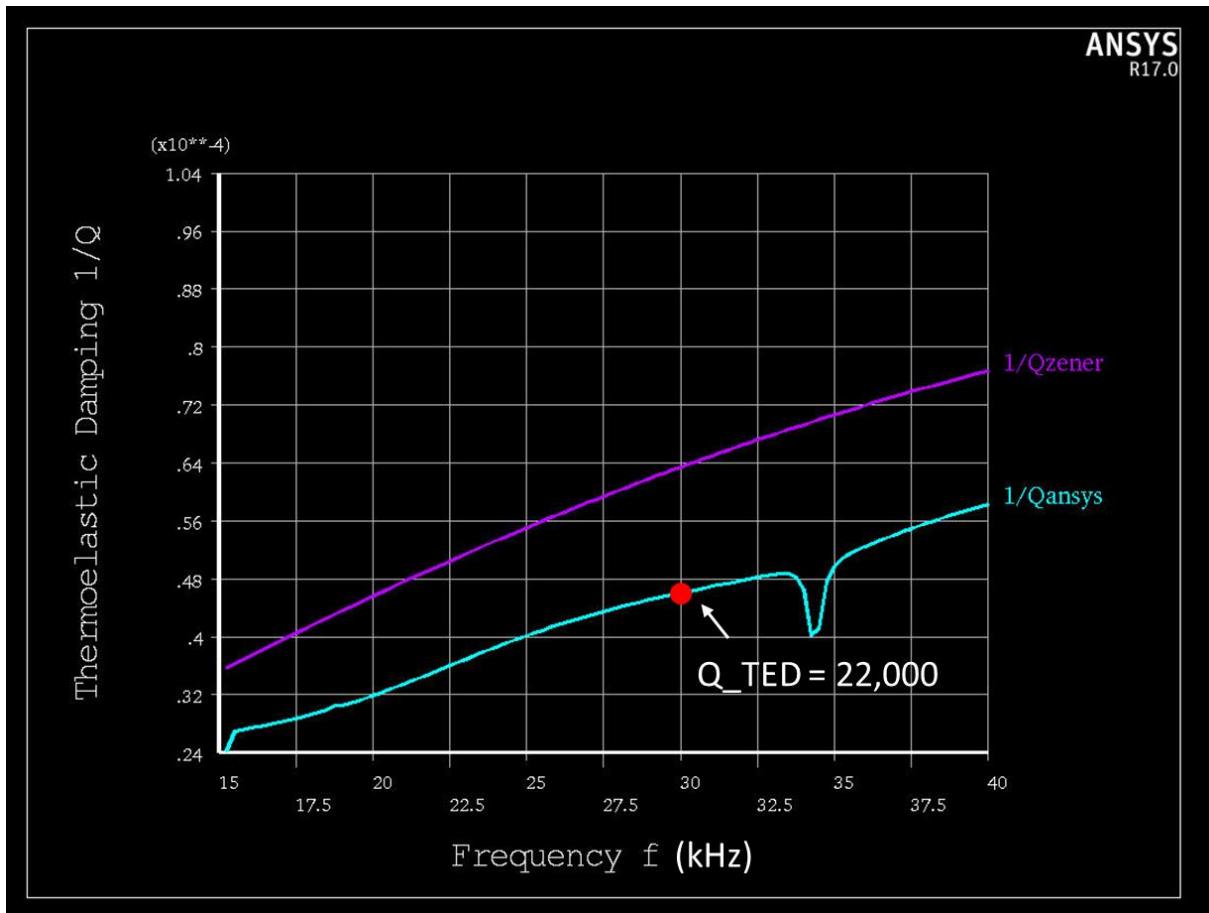

| Figure 7 Finite element simulation of the MRGT thermoelastic damping. ....                                                                                                                                                                                   | 26 |

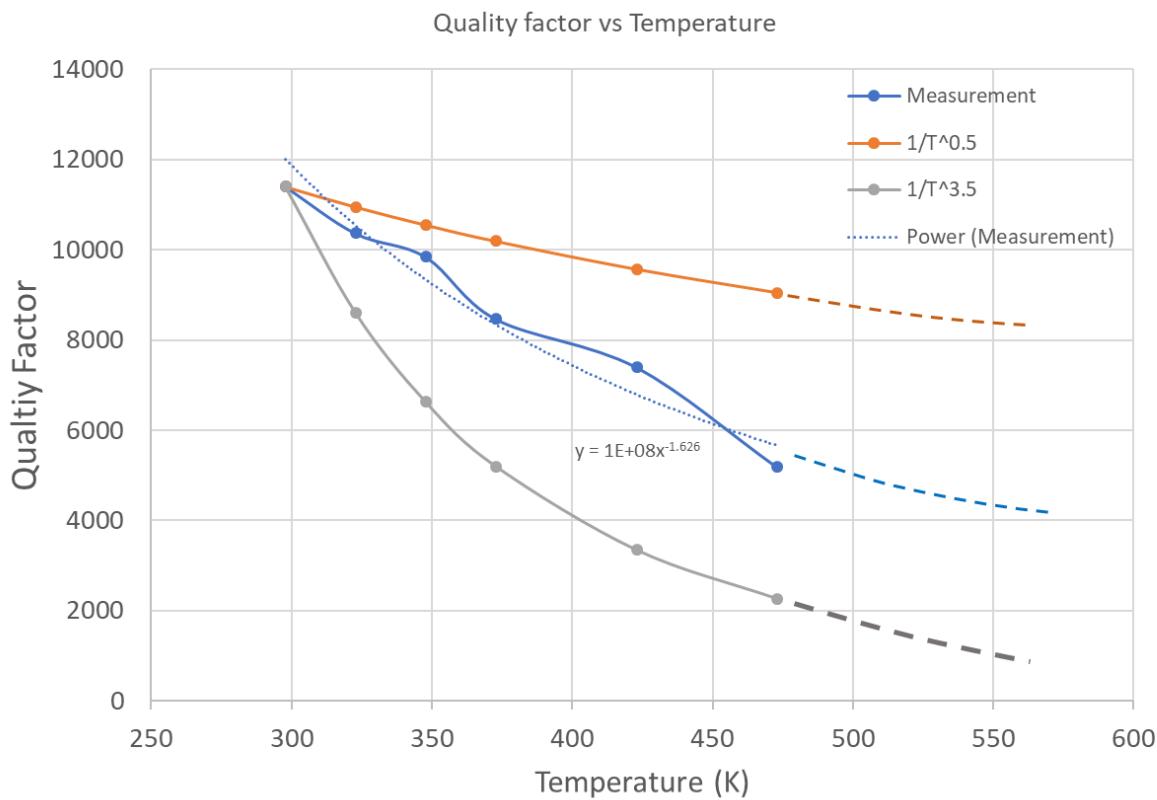

| Figure 8 Measurement of Temperature dependence of MRGT quality factor .....                                                                                                                                                                                  | 27 |

| Figure 9 Vacuum probe station with test instrumentation.....                                                                                                                                                                                                 | 28 |

| Figure 10 Q-factor measurement of an unsealed MRG in vacuum chamber .....                                                                                                                                                                                    | 29 |

| Figure 11 Frequency characterization of an MRG sealed at wafer level .....                                                                                                                                                                                   | 30 |

| Figure 12 Sealed MRG frequency characterization over temperature .....                                                                                                                                                                                       | 31 |

| Figure 13 Test and characterization packaging approach.....                                                                                                                                                                                                  | 32 |

| Figure 14 Response to rotation rate .....                                                                                                                                                                                                                    | 33 |

| Figure 15 Rotation rate response from room temperature to 300°C .....                                                                                                                                                                                        | 33 |

| Figure 16 Scale factor deteriorating over temperature with and without temperature compensation.....                                                                                                                                                         | 34 |

| Figure 17 Modified test setup to enable 300°C testing .....                                                                                                                                                                                                  | 35 |

| Figure 18 Allan deviation of MRGT device at 300°C .....                                                                                                                                                                                                      | 36 |

| Figure 19 The Polaris process flow. ....                                                                                                                                                                                                                     | 38 |

| Figure 20 WLP device frequency sweep from room temperature to 500°C.....                                                                                                                                                                                     | 39 |

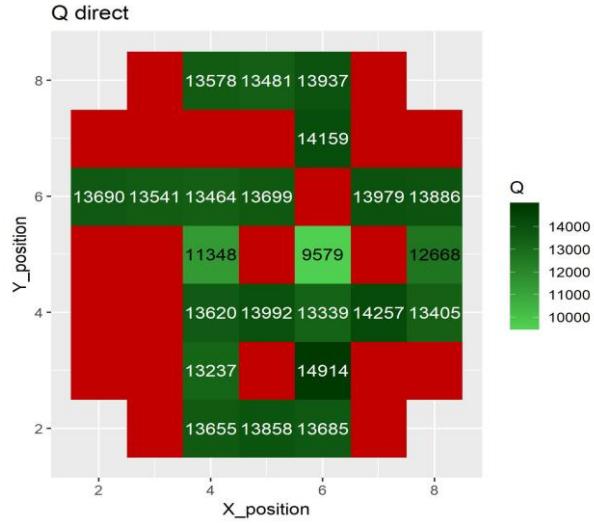

| Figure 21 Wafer map of device resonance frequency for MRGB007 .....                                                                                                                                                                                          | 40 |

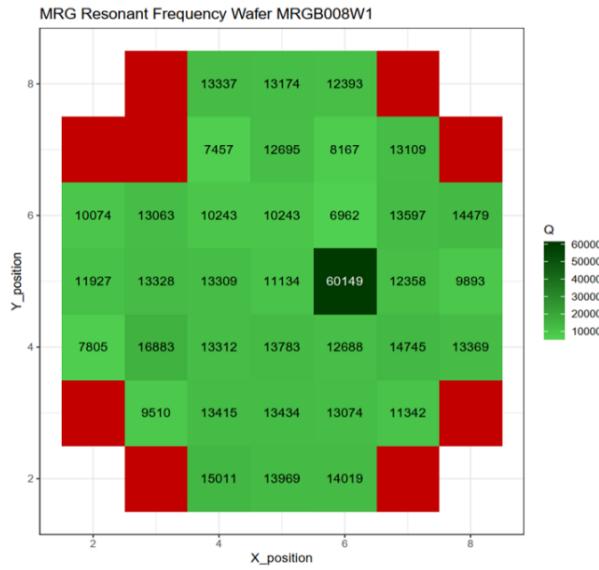

| Figure 22 Wafer map of device resonance frequency for MRGB008 .....                                                                                                                                                                                          | 40 |

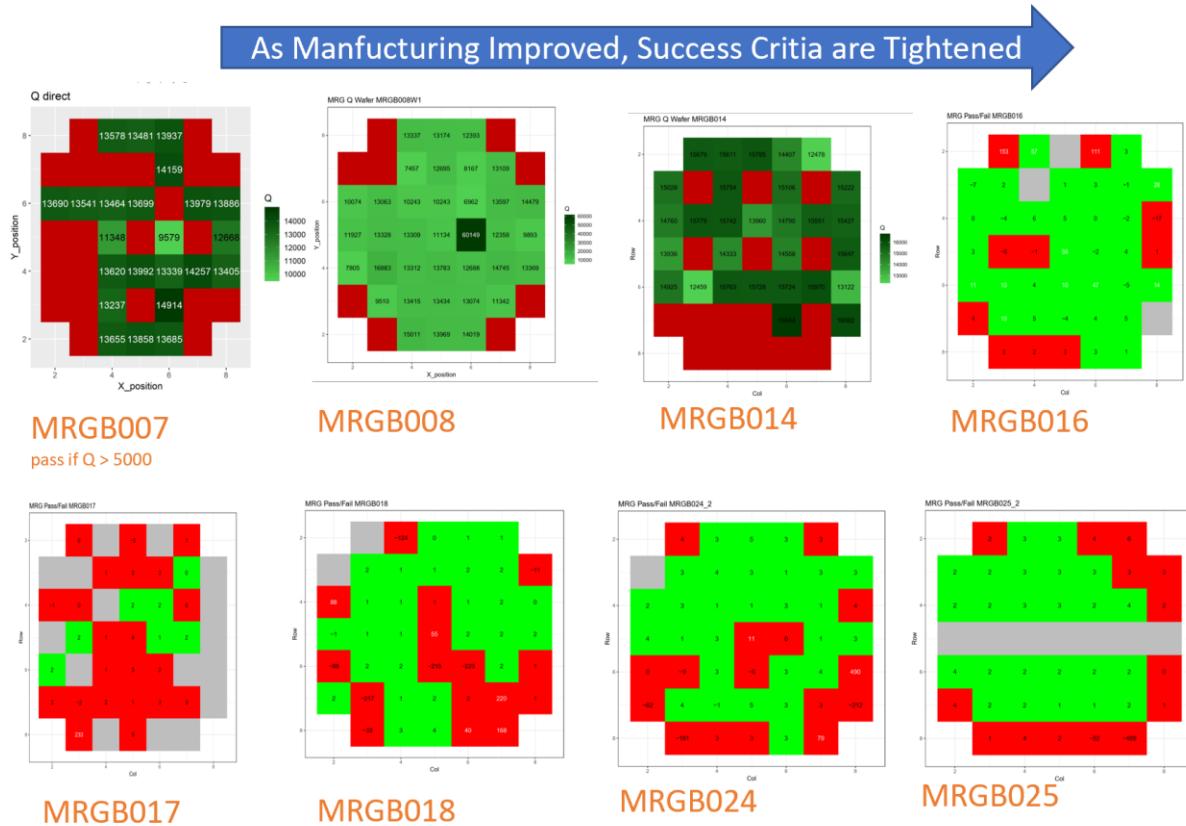

| Figure 23 As the project proceeded, the MRG wafers improved. The criteria for success were tightened along with this, with requirements for higher Q driving success.....                                                                                    | 41 |

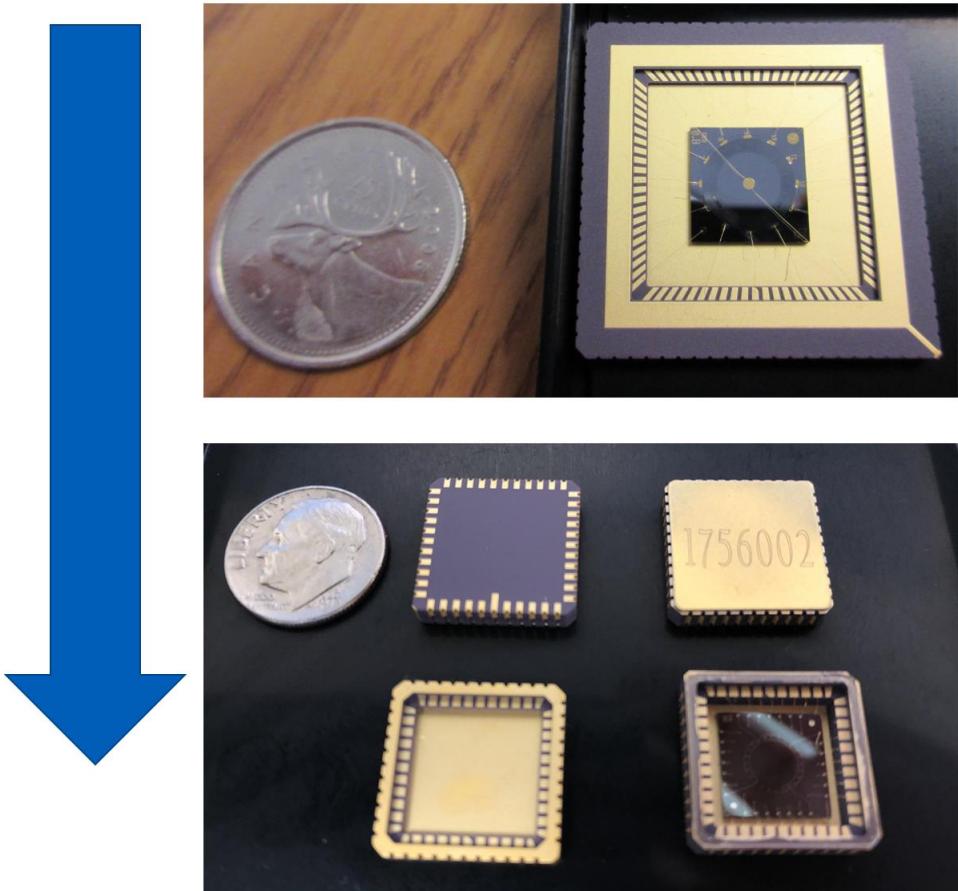

| Figure 24 In addition to improvements in wafer fabrication, we made improvements in packaging. The upper image is our initial package. The lower image is improved package.....                                                                              | 42 |

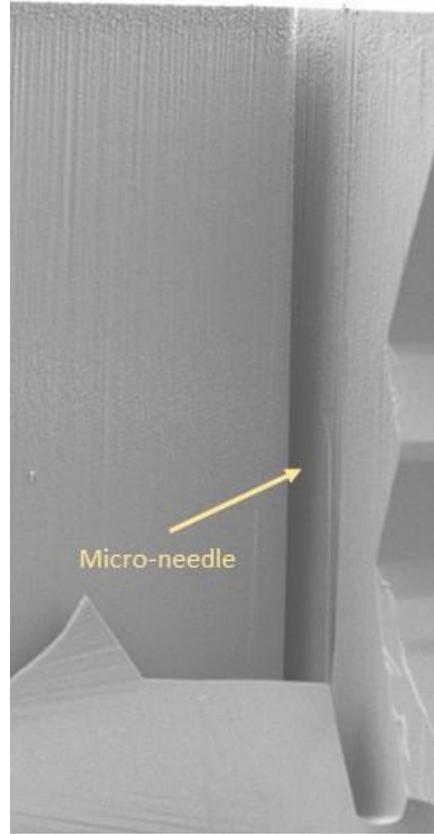

| Figure 25 Trench sidewall showing micro-needle formation.....                                                                                                                                                                                                | 43 |

|                                                                                                                                                                                                    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

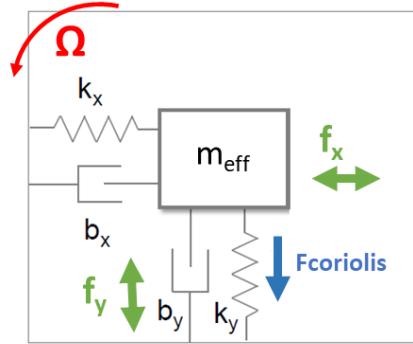

| Figure 26: 2DOF mechanical oscillator model of GE MEMS MRG .....                                                                                                                                   | 45 |

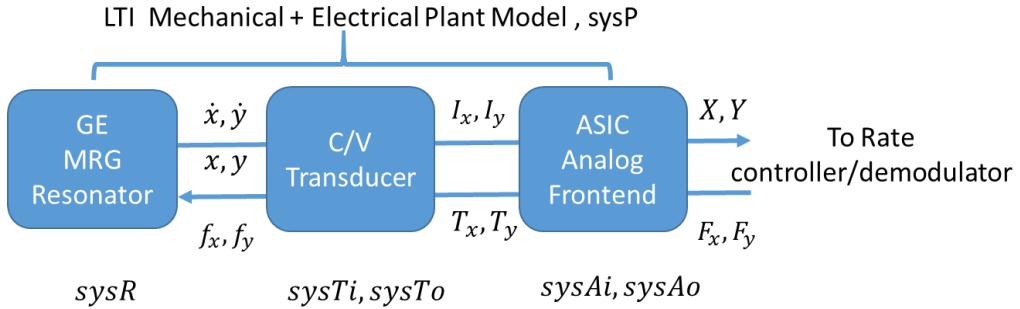

| Figure 27: 2DOF CVG LTI ODE Analytical Model Equations .....                                                                                                                                       | 45 |

| Figure 28: State Model Block diagram MRG CVG with Mechanical Resonator (sysR), capacitive transducer interface (sysT), and ASIC analog frontend electronics (sysA) analytical model blocks .....   | 46 |

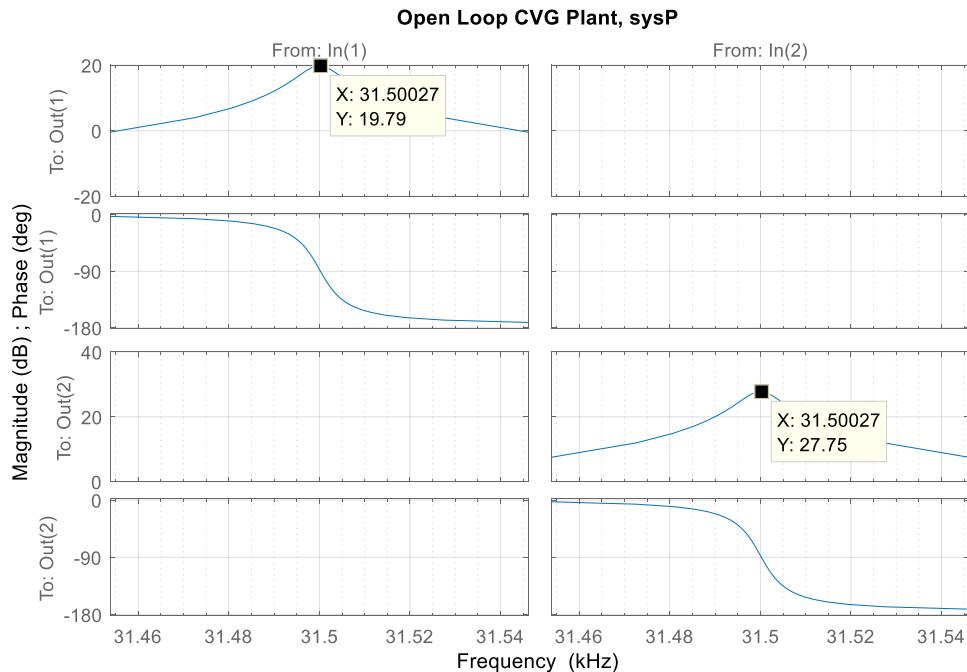

| Figure 29: Predicted transfer function (in(1)→X channel drive, in(2)→Y channel drive, out(1)→X channel sense, out(2)→Y channel sense) for the GE MRG with IW ASIC AFE .....                        | 46 |

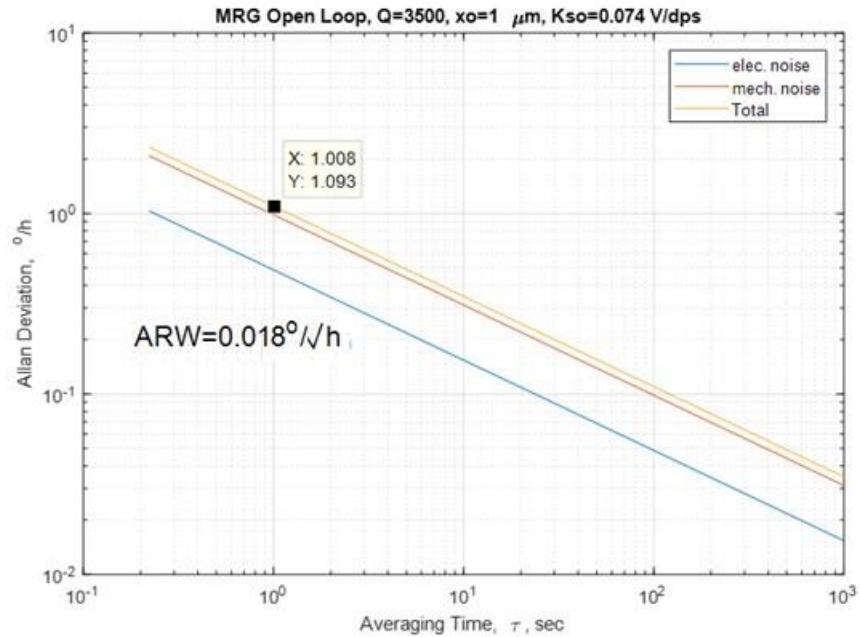

| Figure 30: Predicted GE MRG with current InertialWave ASIC Frontend Electronics Allan Deviation Bias Stability and ARW.....                                                                        | 47 |

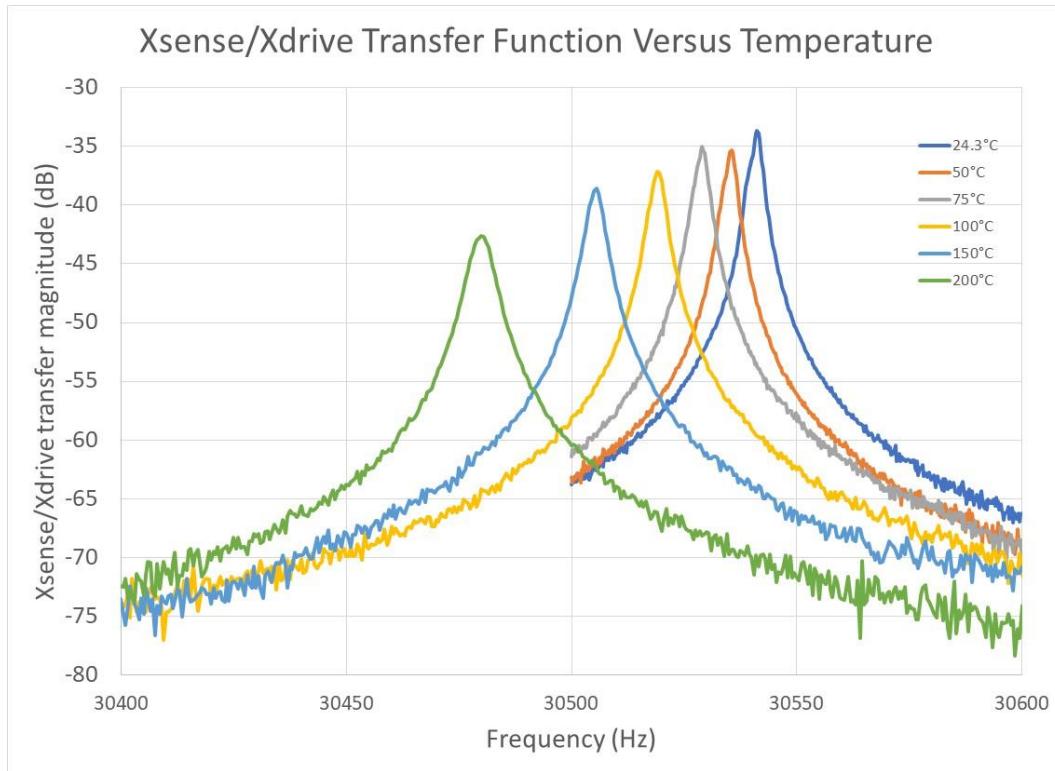

| Figure 31: GE MRG Die Level Transfer Function (Xsense/Xdrive) vs. swept die temperature (25°C-blue/right, 50°C-orange, 75°C-grey, 100°C-yellow, 150°C-blue/left, 200°C-green).....                 | 48 |

| Figure 32: InertialWave Analog Frontend electronics board with attached LCC vacuum packaged GE MRG .....                                                                                           | 49 |

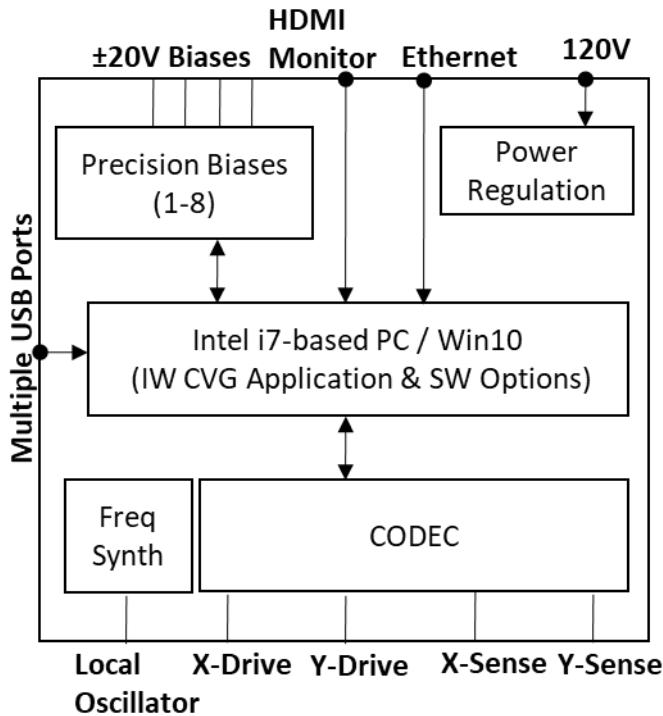

| Figure 33: InertialWave CVG Test System Product used for GE MRG testing with InertialWave AFE electronics .....                                                                                    | 49 |

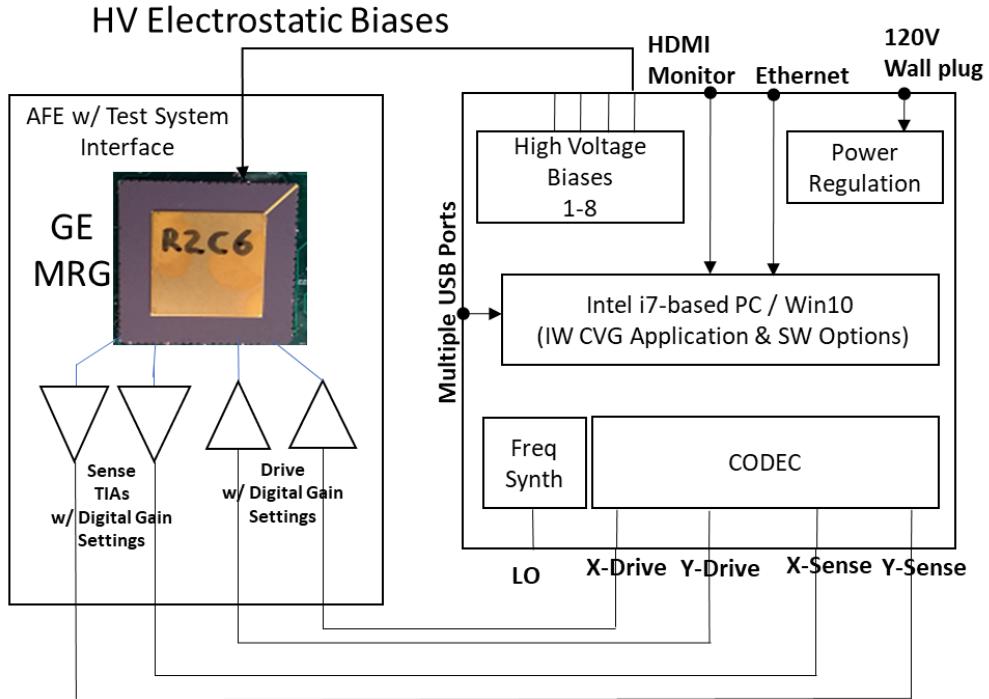

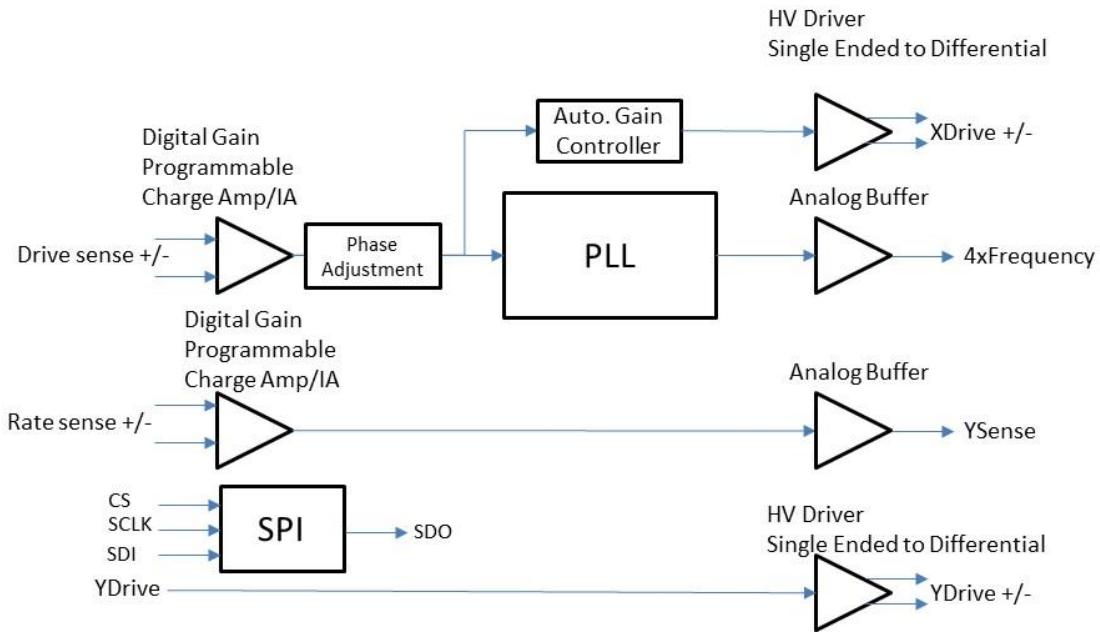

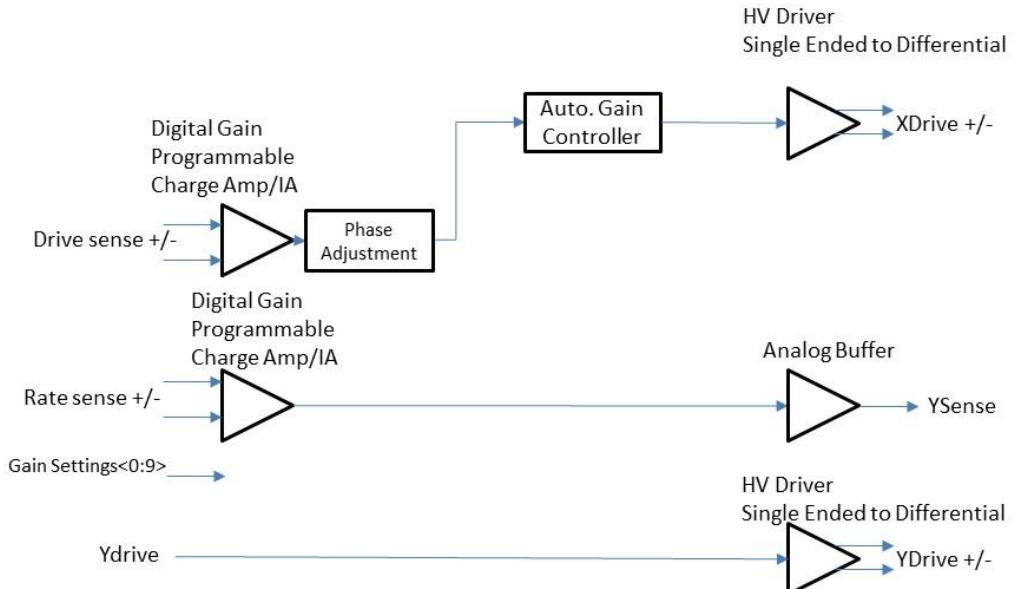

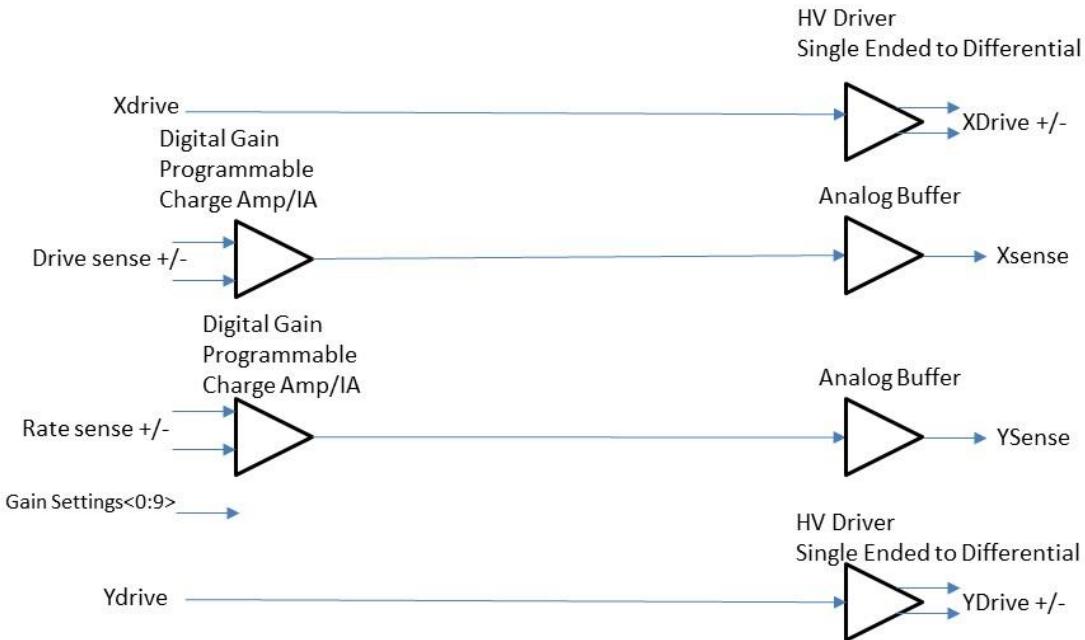

| Figure 34: InertialWave CVG Test System functional block diagram .....                                                                                                                             | 50 |

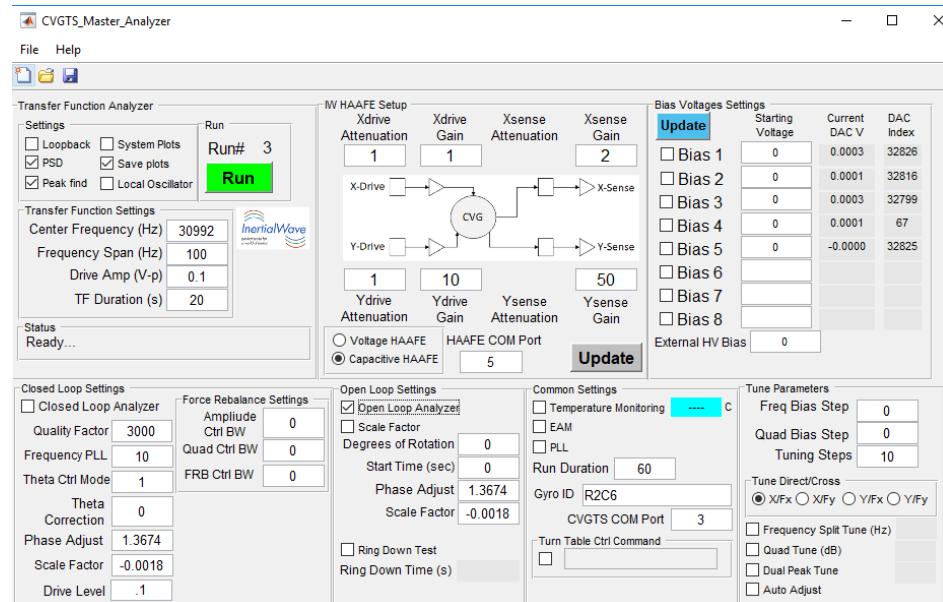

| Figure 35: InertialWave CVG Test System Product associated GUI used for GE MRG testing with InertialWave AFE electronics .....                                                                     | 50 |

| Figure 36: InertialWave CVG Test System connected to GE MRG functional block diagram .....                                                                                                         | 51 |

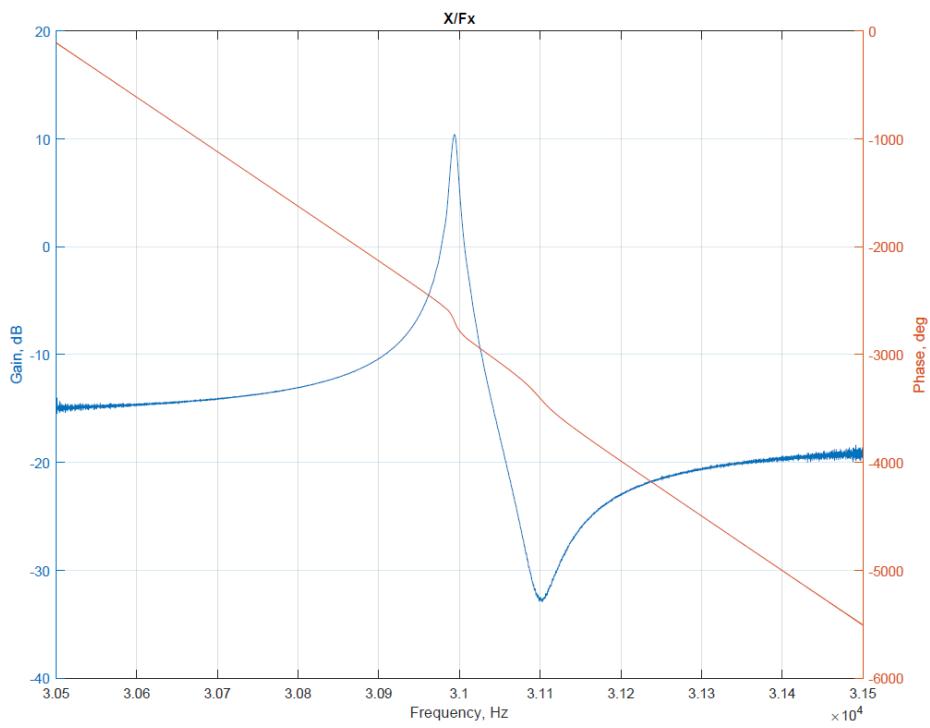

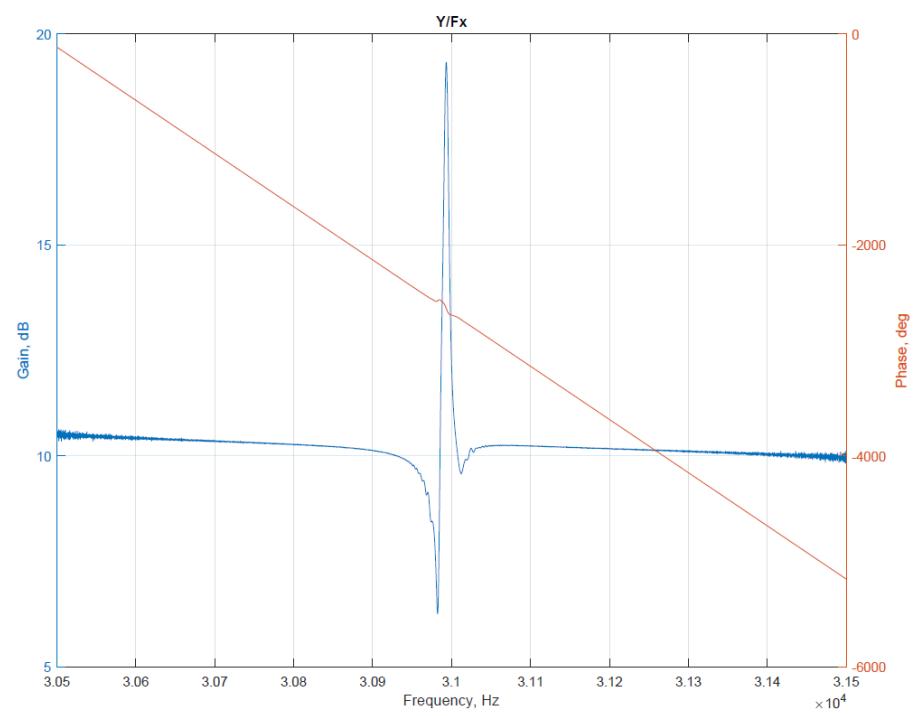

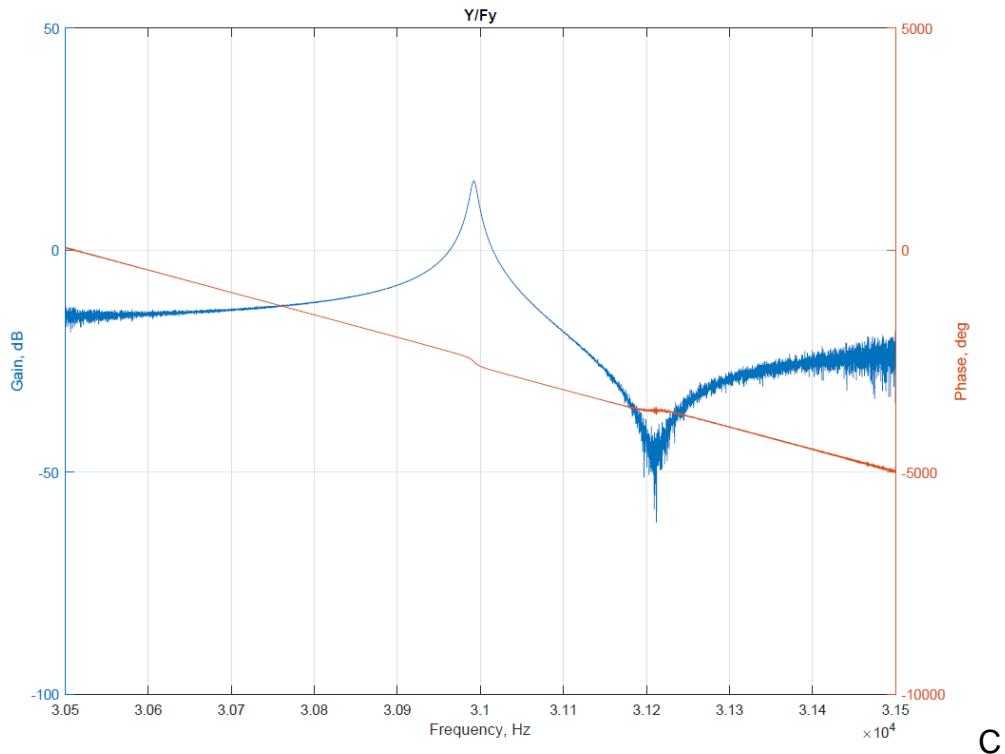

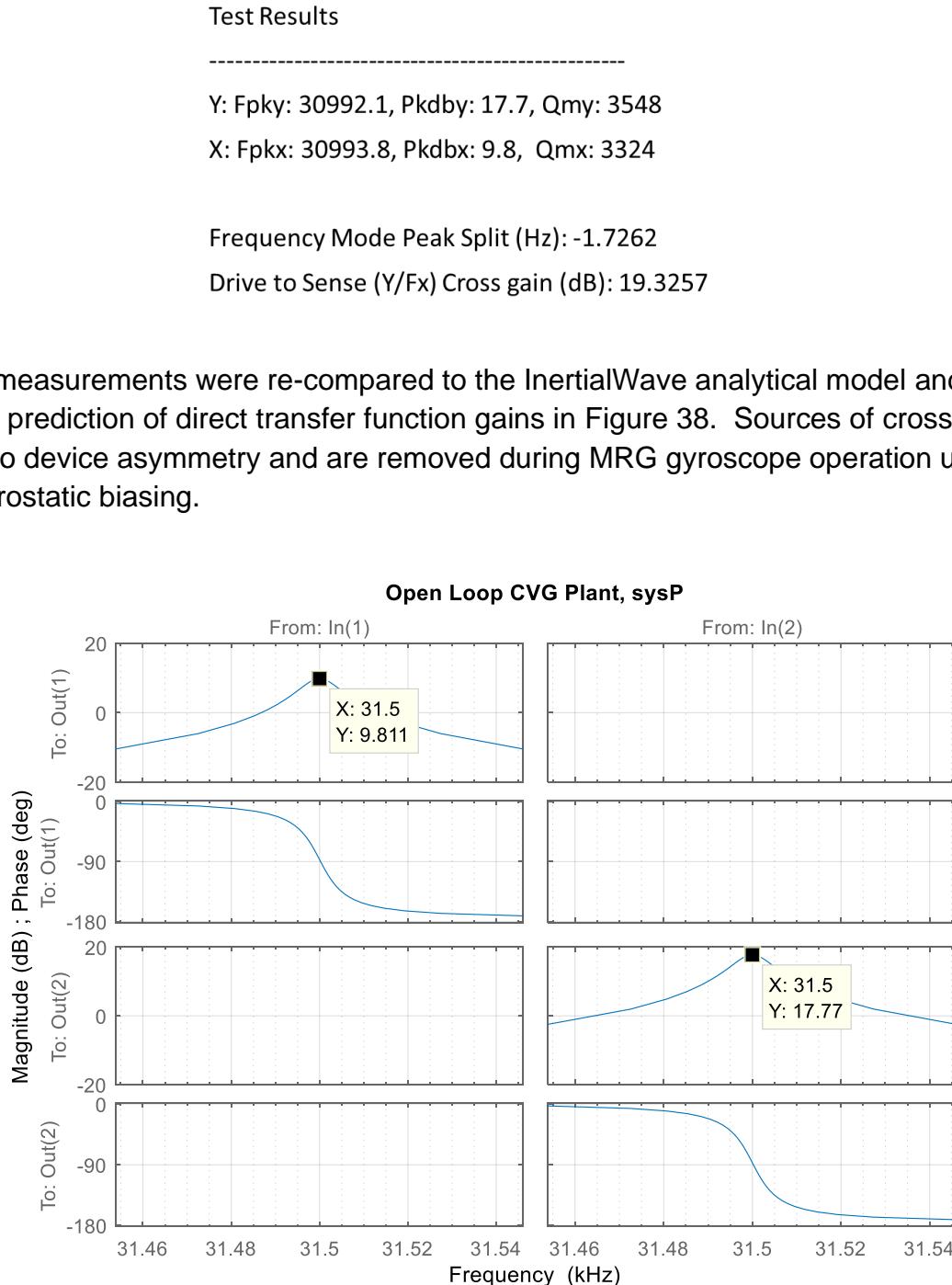

| Figure 37: InertialWave measured 2-port Xdrive and Ysense transfer functions on GE MRG R2C6 part .....                                                                                             | 53 |

| Figure 38: Predicted transfer functions (in(1)→X channel drive, in(2) →Y channel drive, out(1)→X channel sense, out(2)→Y channel sense) for the GE MRG R2C6 with IW ASIC frontend electronics..... | 54 |

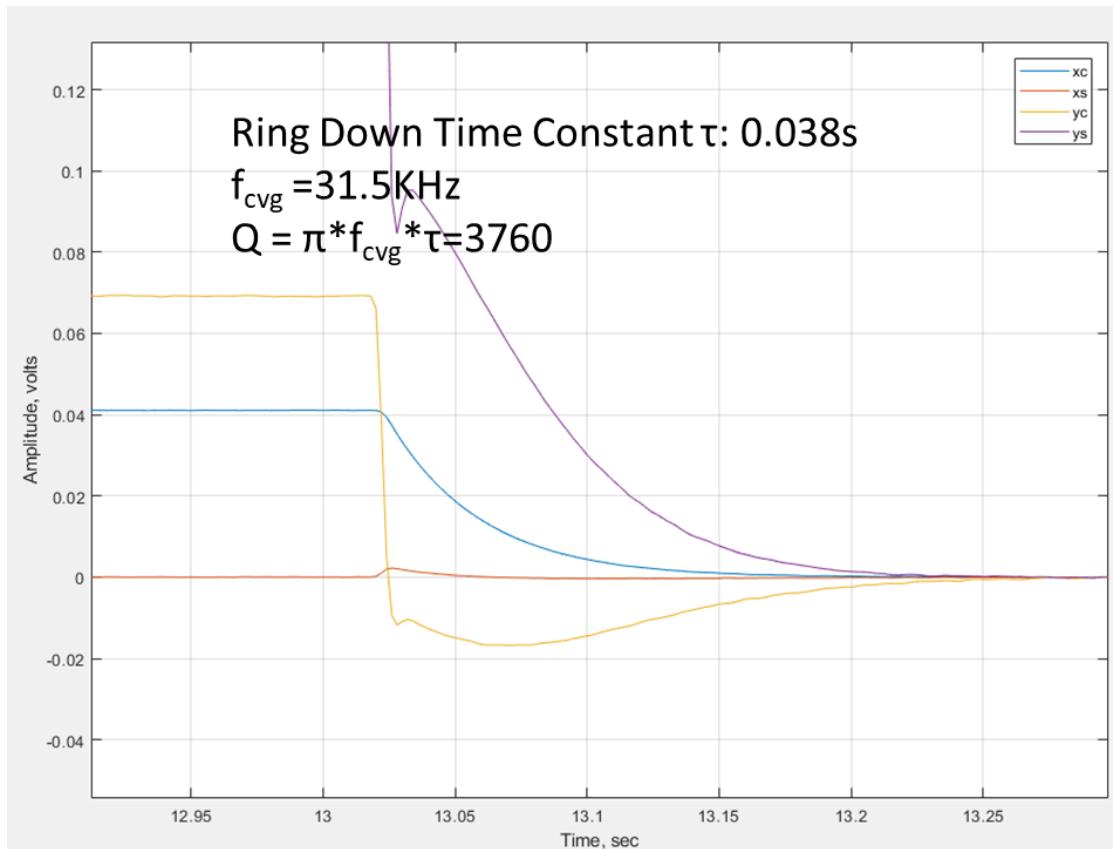

| Figure 39: Closed loop drive with PLL tracking ring down test on R2C6 calculated Q-factor=3760 is consistent with measured transfer function Q-factor=3548.....                                    | 55 |

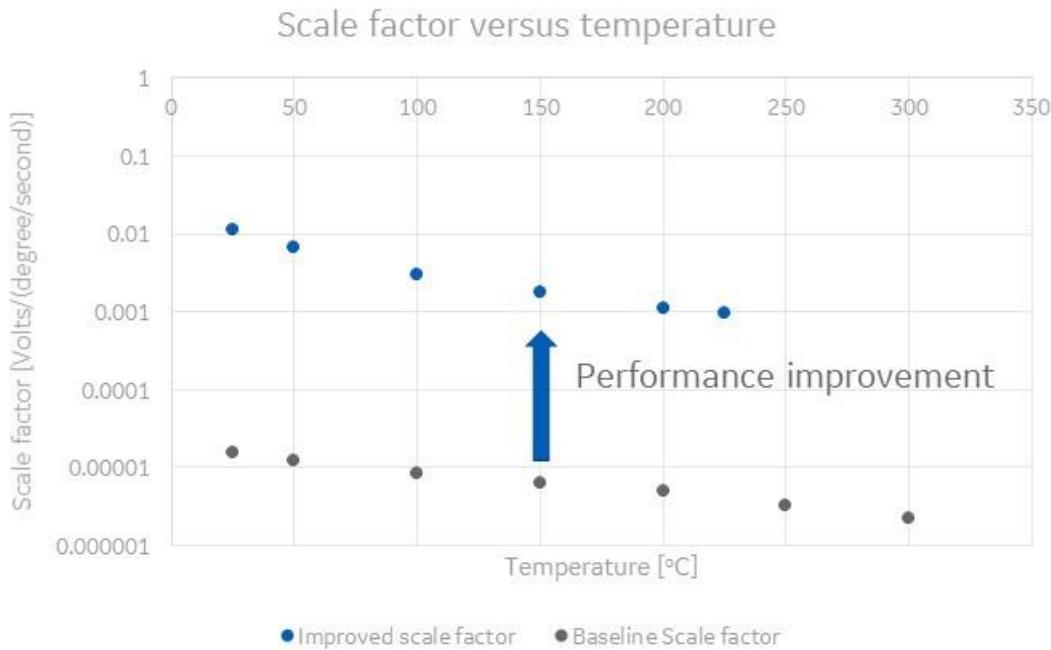

| Figure 40 Baseline and improved scale factor versus temperature.....                                                                                                                               | 57 |

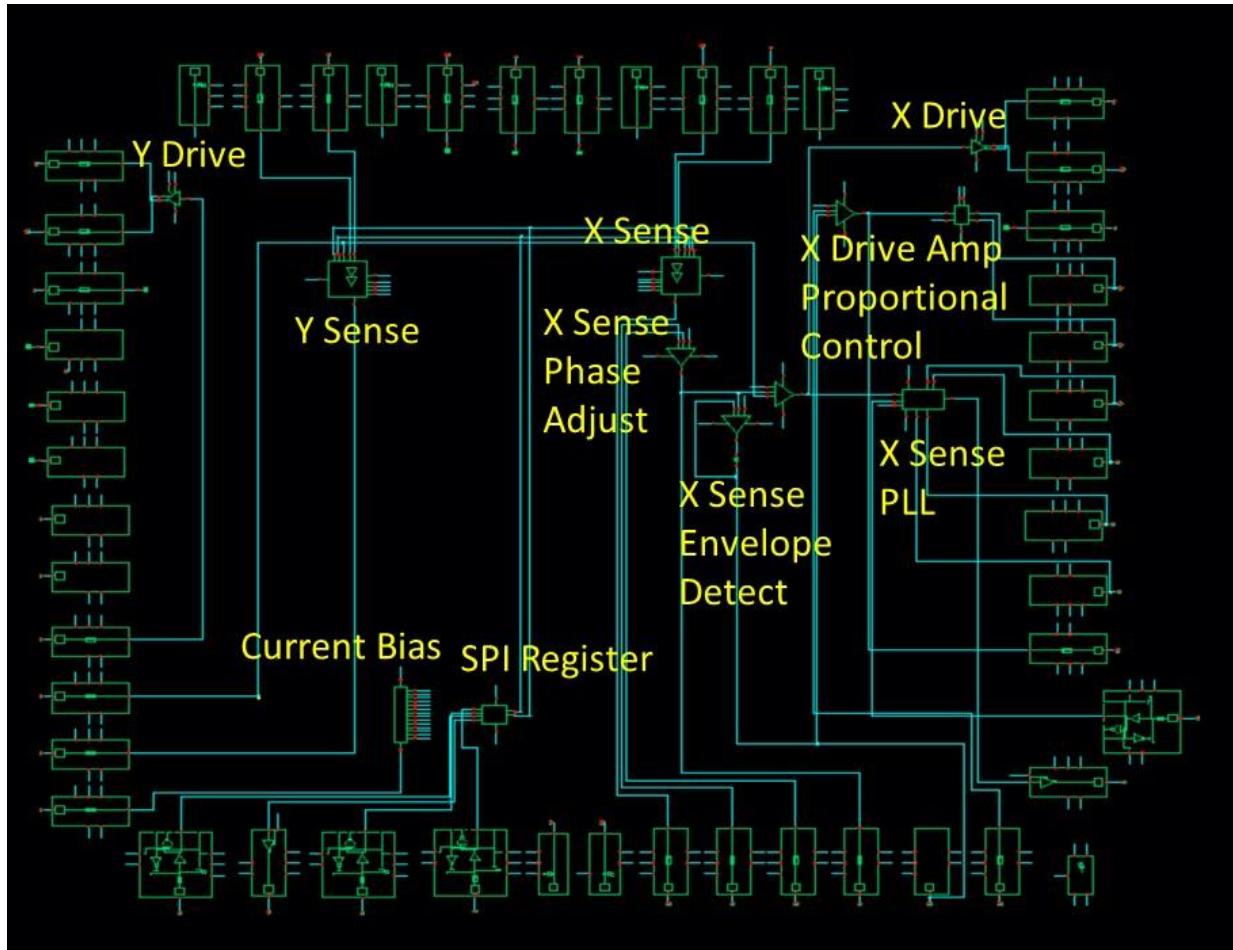

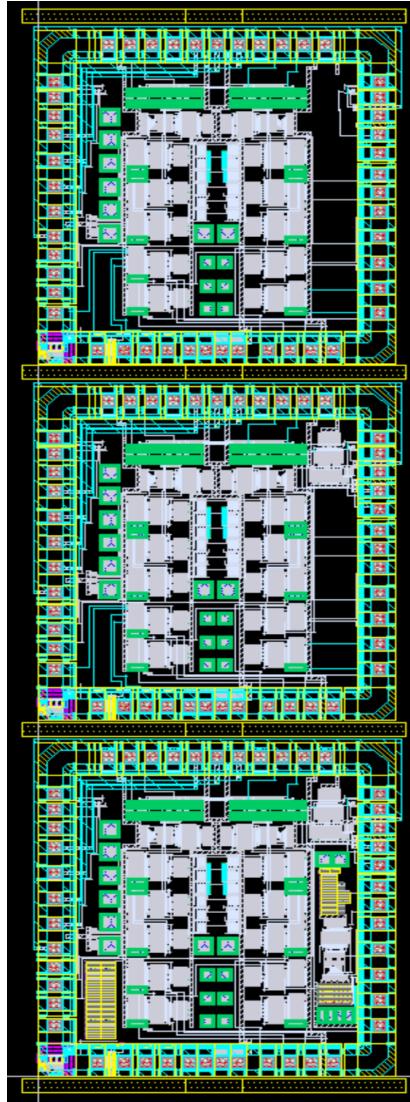

| Figure 41 MRG controller ASIC floorplan .....                                                                                                                                                      | 59 |

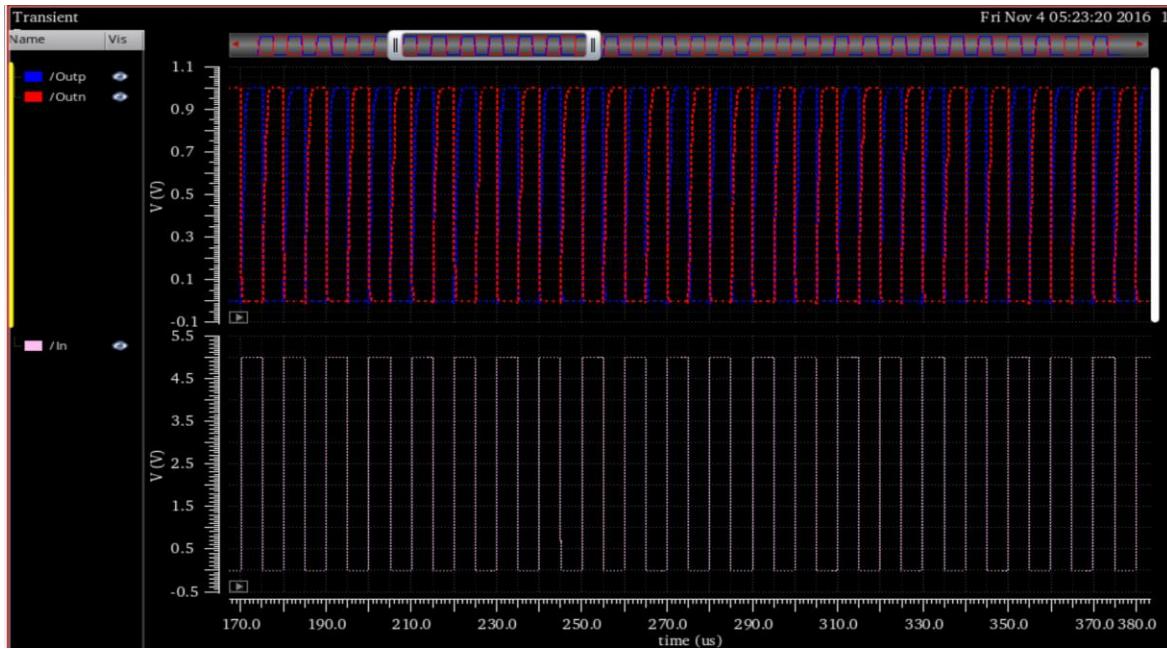

| Figure 42 simulated driver output: 1V level at 300°C .....                                                                                                                                         | 61 |

| Figure 43 Simulated driver output: 30V level at 300°C.....                                                                                                                                         | 61 |

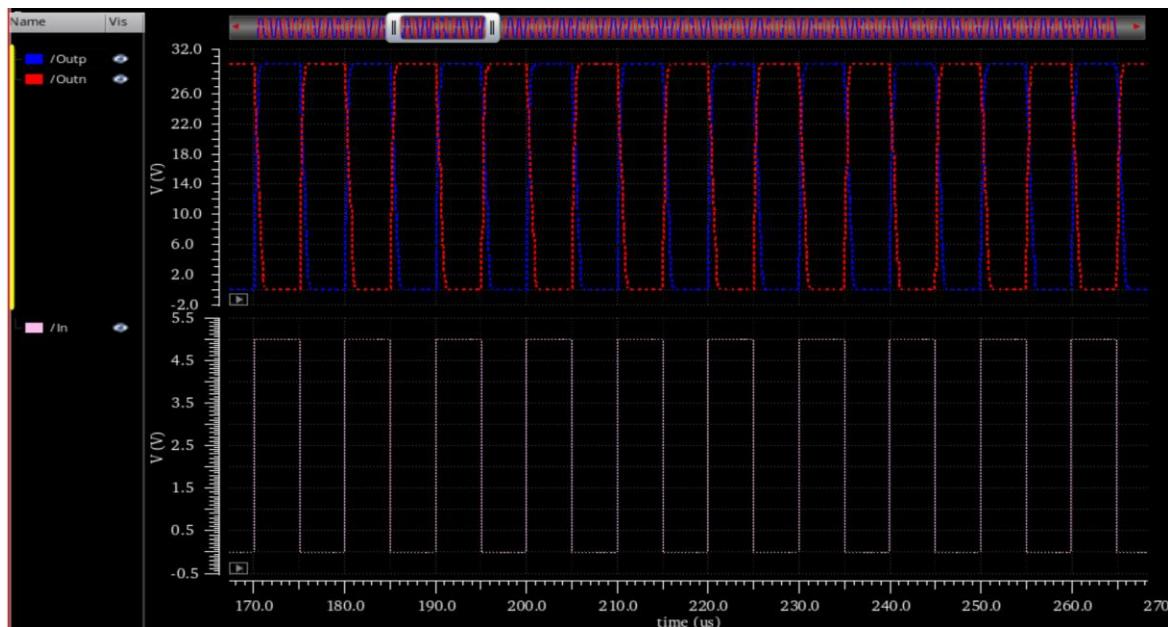

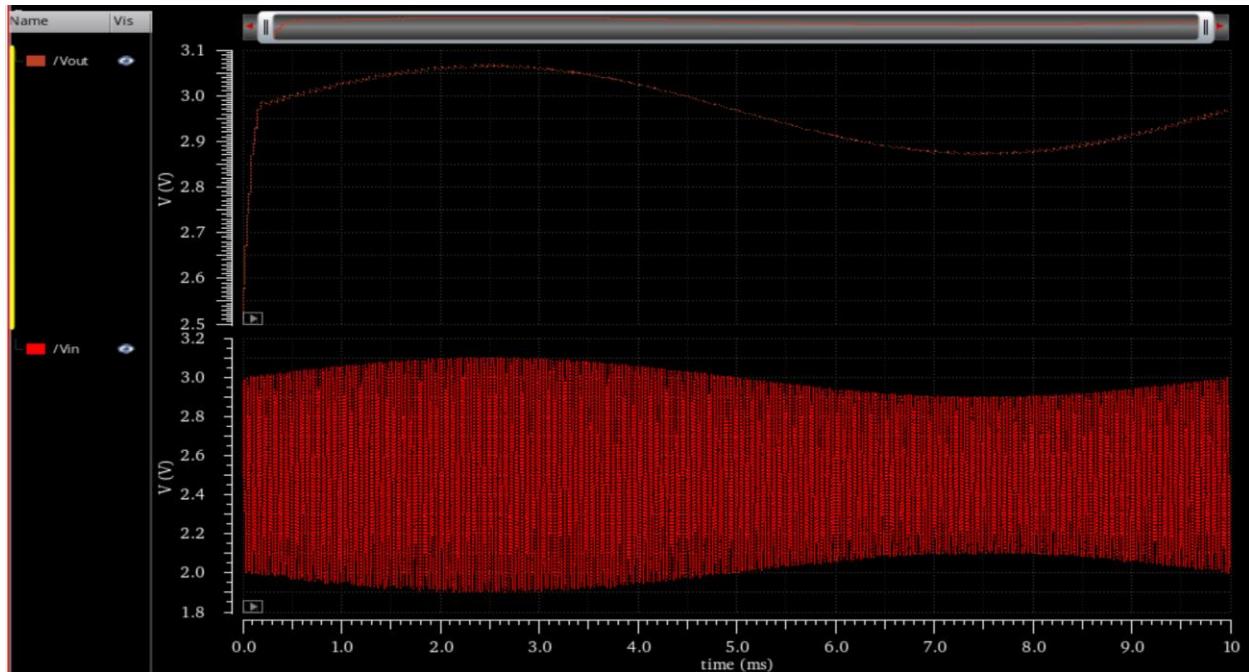

| Figure 44 300°C functional simulation results of the closed loop controller.....                                                                                                                   | 62 |

| Figure 45 Envelop detector simulation (wp, 300°C) .....                                                                                                                                            | 63 |

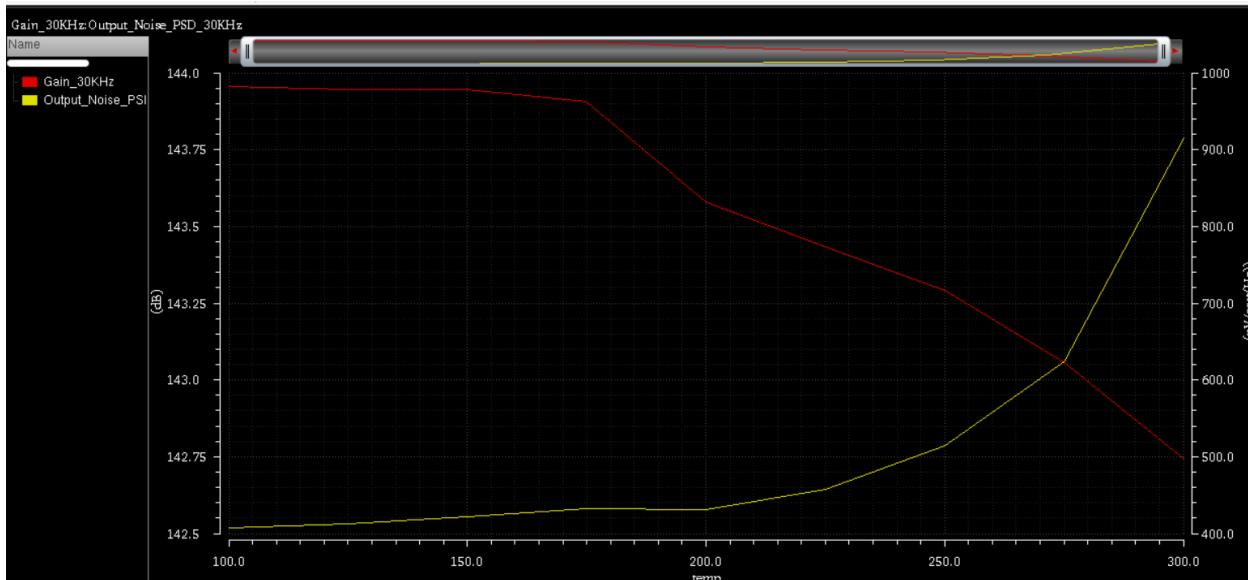

| Figure 46 AFE gain and noise over temperature (ws, 4.5V vdd).....                                                                                                                                  | 64 |

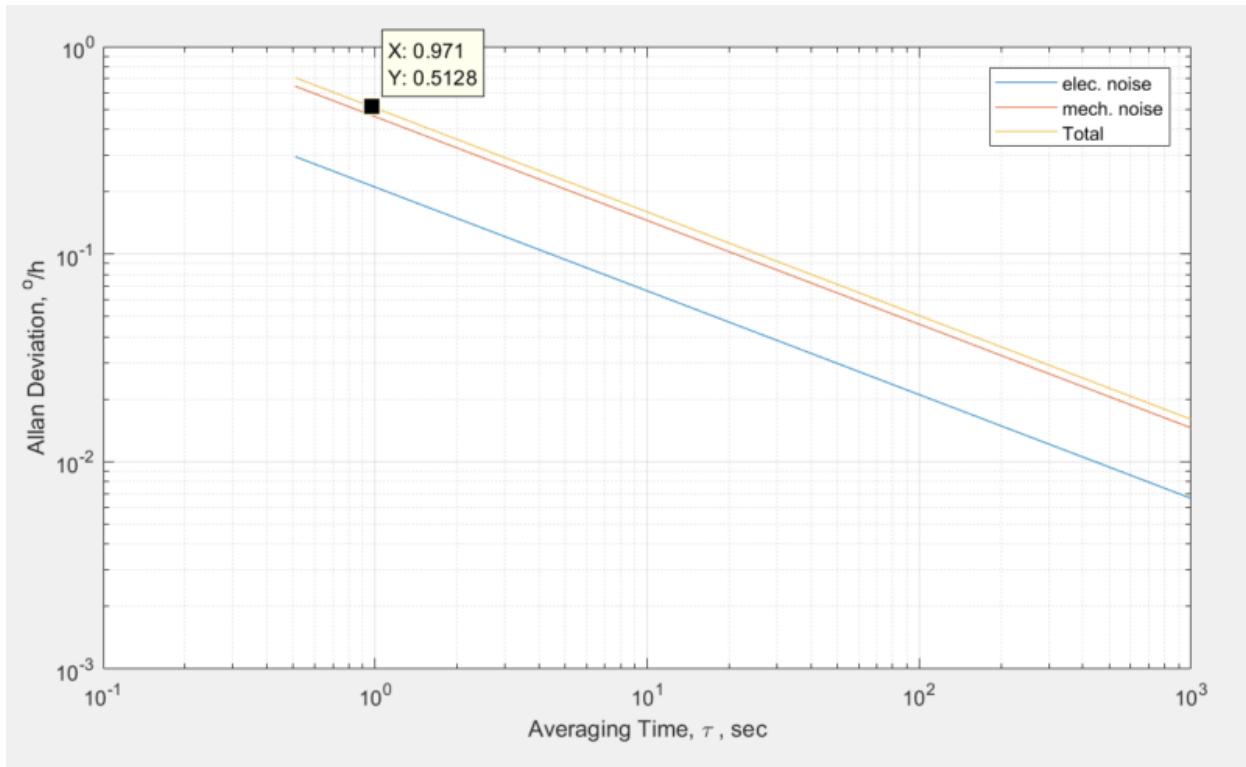

| Figure 47 Allan Deviation analysis of MRGT and AFE noise .....                                                                                                                                     | 65 |

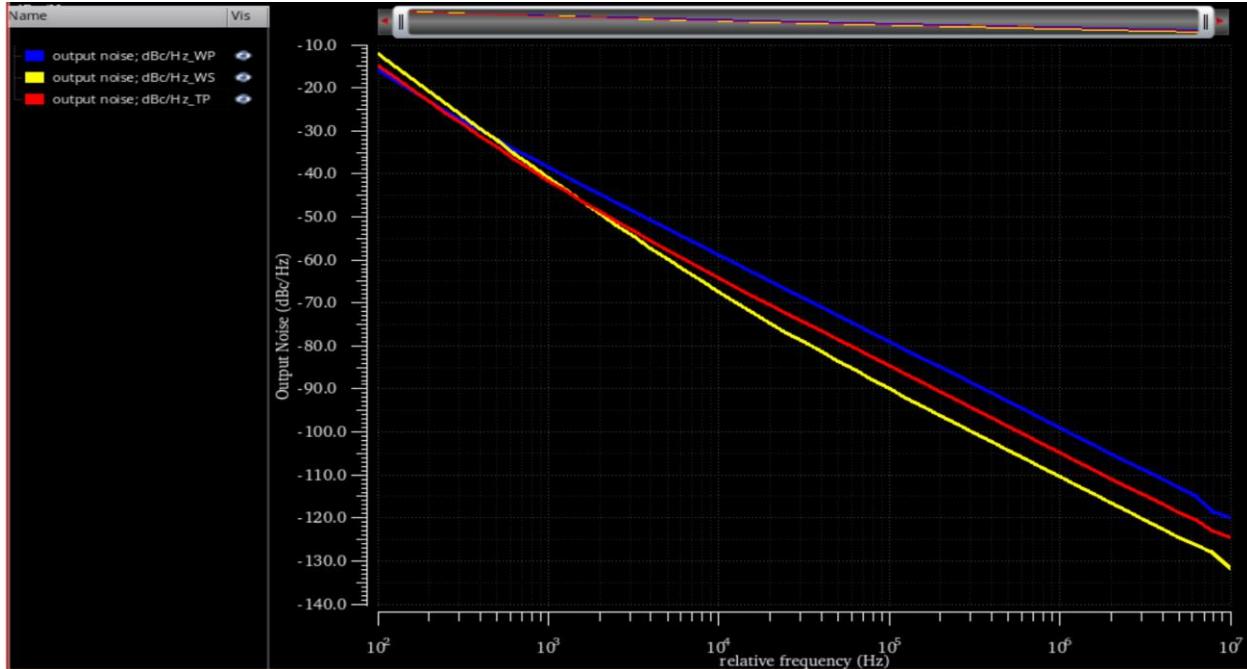

| Figure 48 PLL phase noise at 300°C over ws, wp and tm corners.....                                                                                                                                 | 67 |

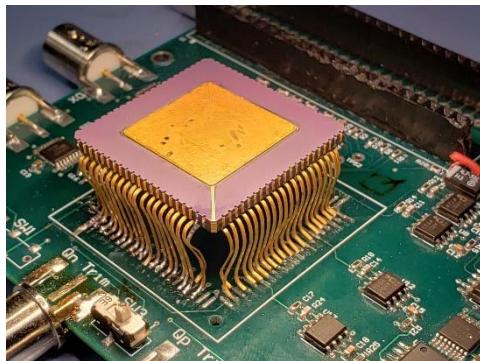

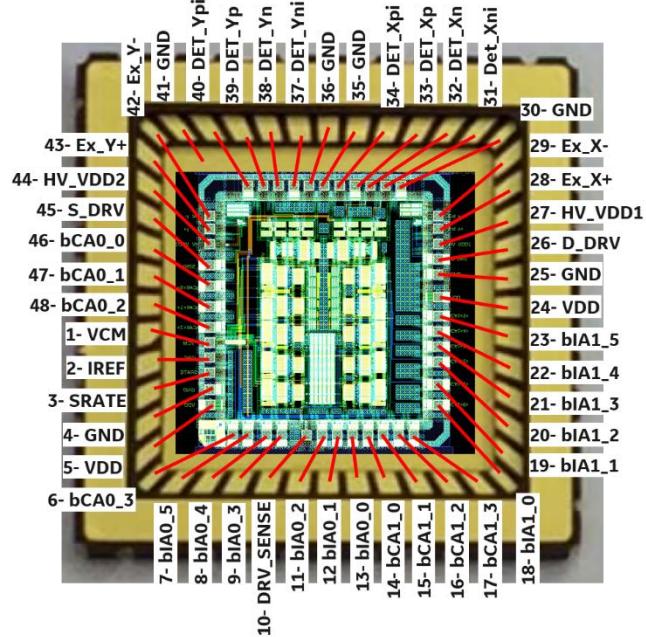

| Figure 49 ASIC full controller chip #1 .....                                                                                                                                                       | 68 |

|                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------|----|

| Figure 50 ASIC Receive chain with controlled X-channel drive chip #2 .....                                           | 68 |

| Figure 51 ASIC Receive chain with direct X-channel drive chip #3.....                                                | 69 |

| Figure 52 3-chip layout.....                                                                                         | 70 |

| Figure 53 High Temperature ASIC block diagram (a) and layout (b) .....                                               | 71 |

| Figure 54 Test board for HT ASIC packaged in ceramic LCC48.....                                                      | 73 |

| Figure 55 Ceramic LCC48 package (12.7mm x 12.7mm) and HT ASIC bonding diagram .....                                  | 73 |

| Figure 56 Ceramic DIP28 package (15.2mm x 35.5mm) and HT ASIC bonding diagram .....                                  | 74 |

| Figure 57 Test results of X sense channel gain ASIC/MRG test board with AFE gain set to 1x .....                     | 75 |

| Figure 58 Test results of X sense channel gain ASIC/MRG test board with AFE gain set to 2x .....                     | 75 |

| Figure 59 Test results of X sense channel gain ASIC/MRG test board with AFE gain set to 20x .....                    | 76 |

| Figure 60 Test results of X sense channel gain ASIC/MRG test board with AFE gain set to 40x .....                    | 76 |

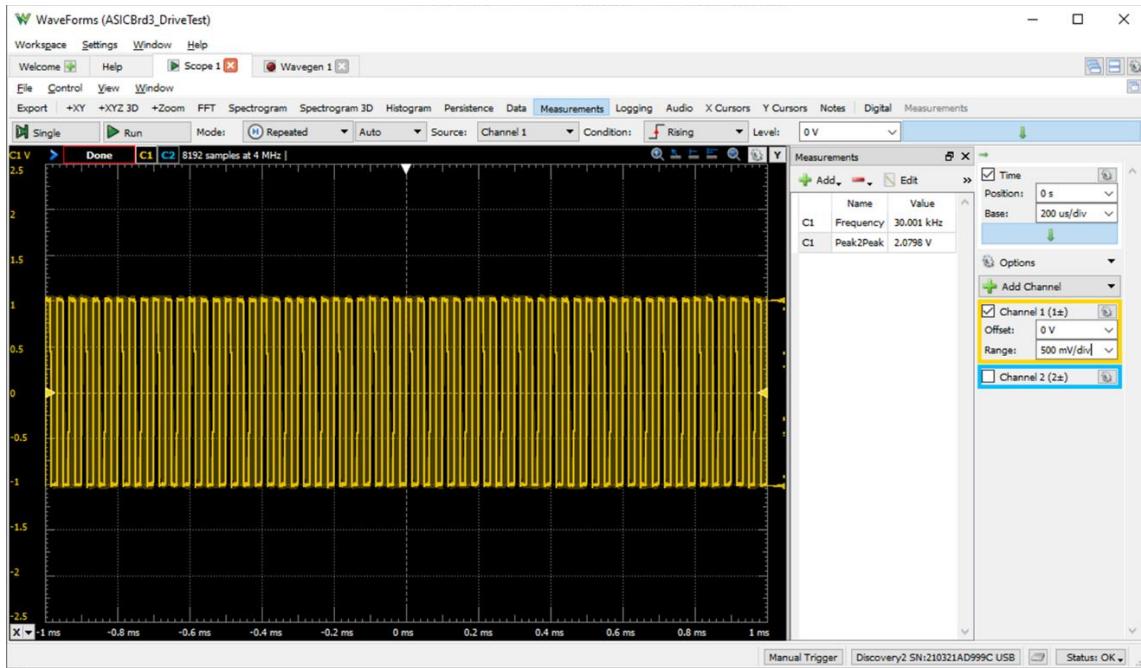

| Figure 61 Test results of HT ASIC drive channel 1Vpeak minimum drive level.....                                      | 77 |

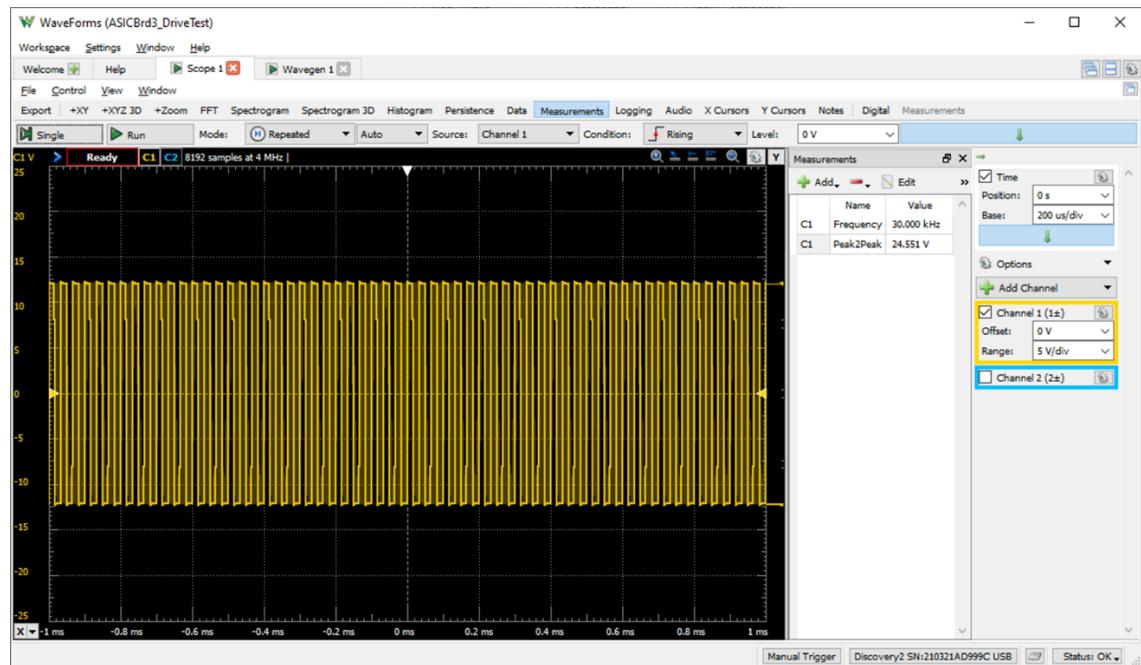

| Figure 62 Test results of HT ASIC drive channel 12Vpeak maximum drive levels .....                                   | 77 |

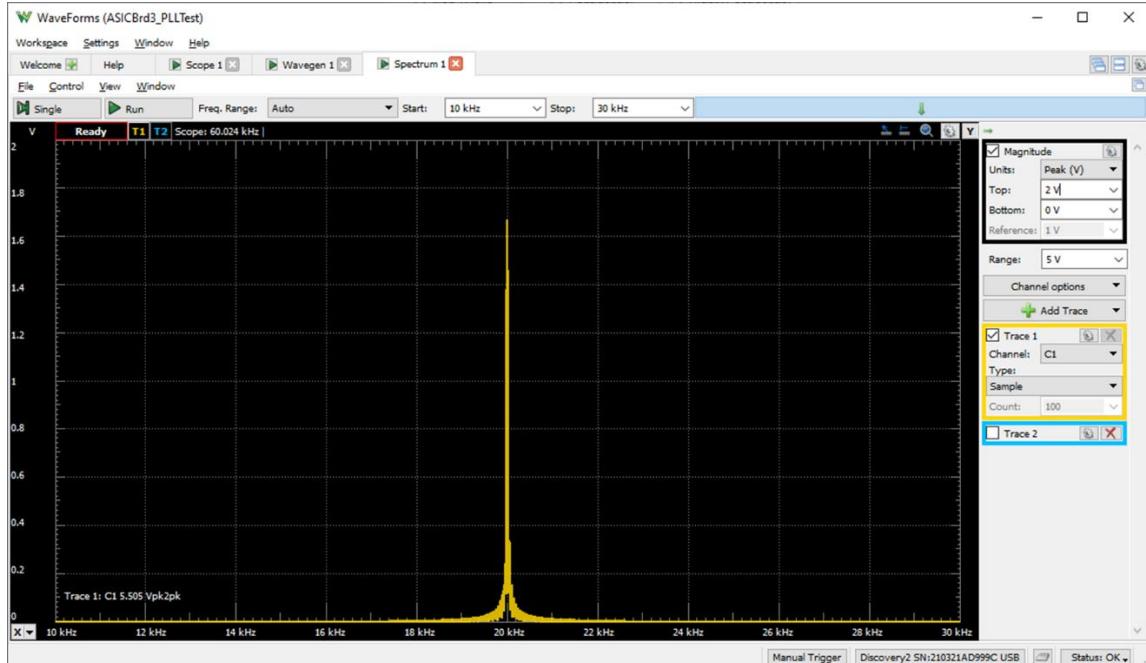

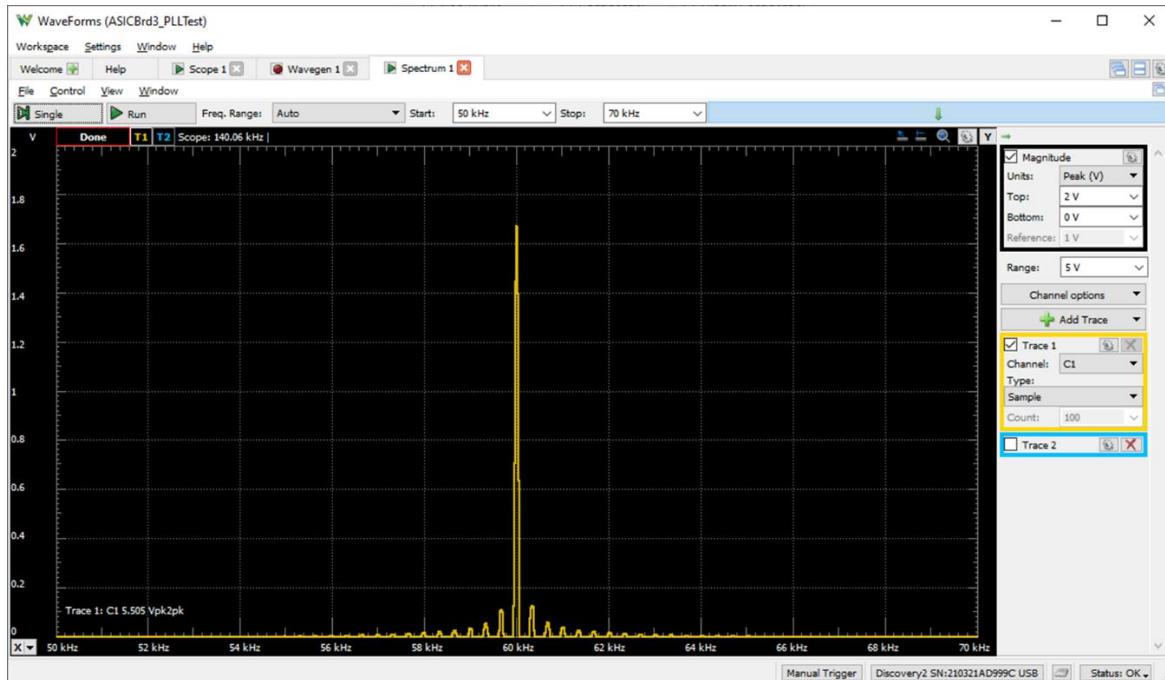

| Figure 63 Test results of HT ASIC on chip on-chip phased locked loop frequency span testing at 20KHz.....            | 78 |

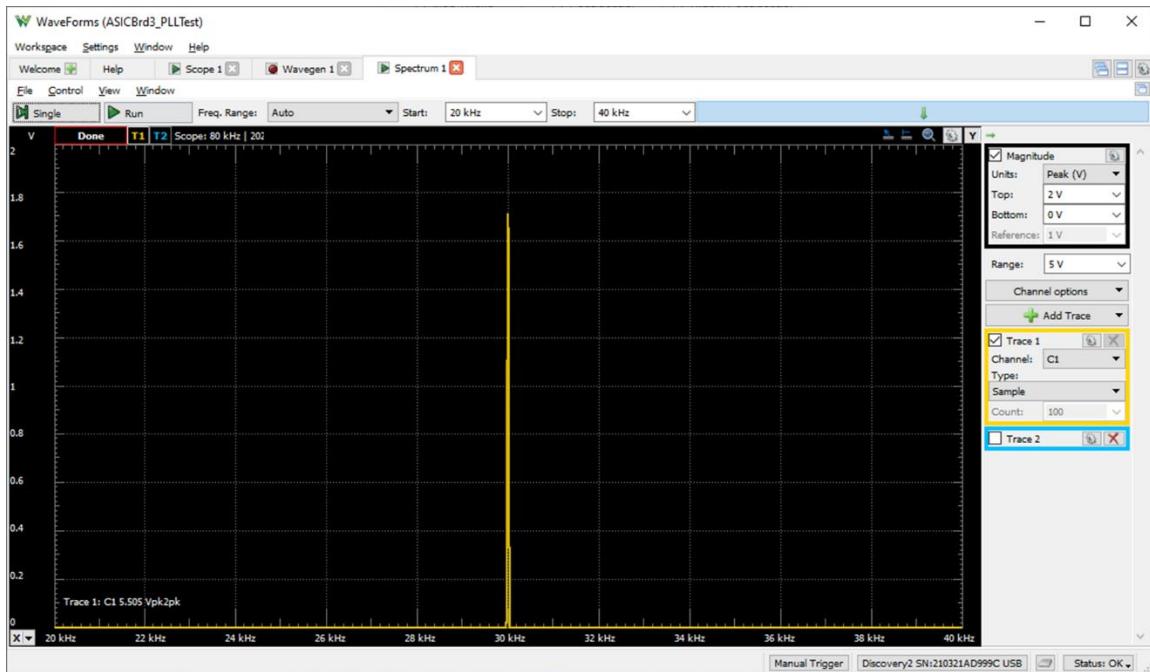

| Figure 64 Test results of HT ASIC on chip on-chip phased locked loop frequency span testing at 30KHz .....           | 79 |

| Figure 65 Test results of HT ASIC on chip on-chip phased locked loop frequency span testing at 60KHz.....            | 79 |

| Figure 66 Test setup with 300°C chamber, probe connections to test system (outside chamber), and test equipment..... | 80 |

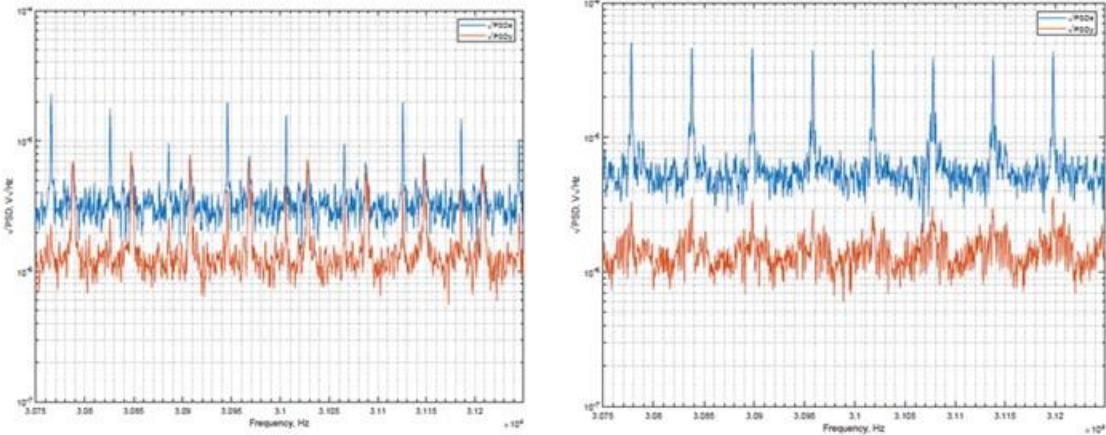

| Figure 67 ASIC high gain X channel (blue), low gain Y channel (red) noise PSD at 25°C (left), 300°C (right).....     | 80 |

| Figure 68 Metal change HT ASIC bonding diagram in ceramic LCC48 .....                                                | 82 |

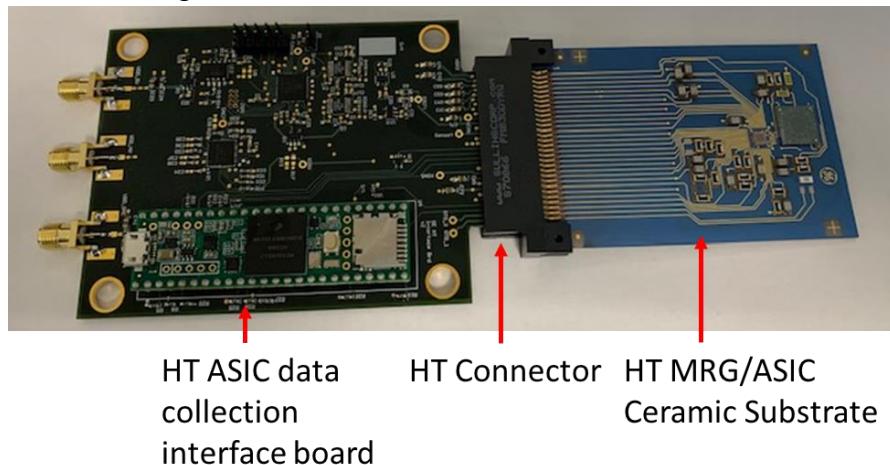

| Figure 69 Test board configuration for integrated testing from room temperature to 300°C .....                       | 85 |

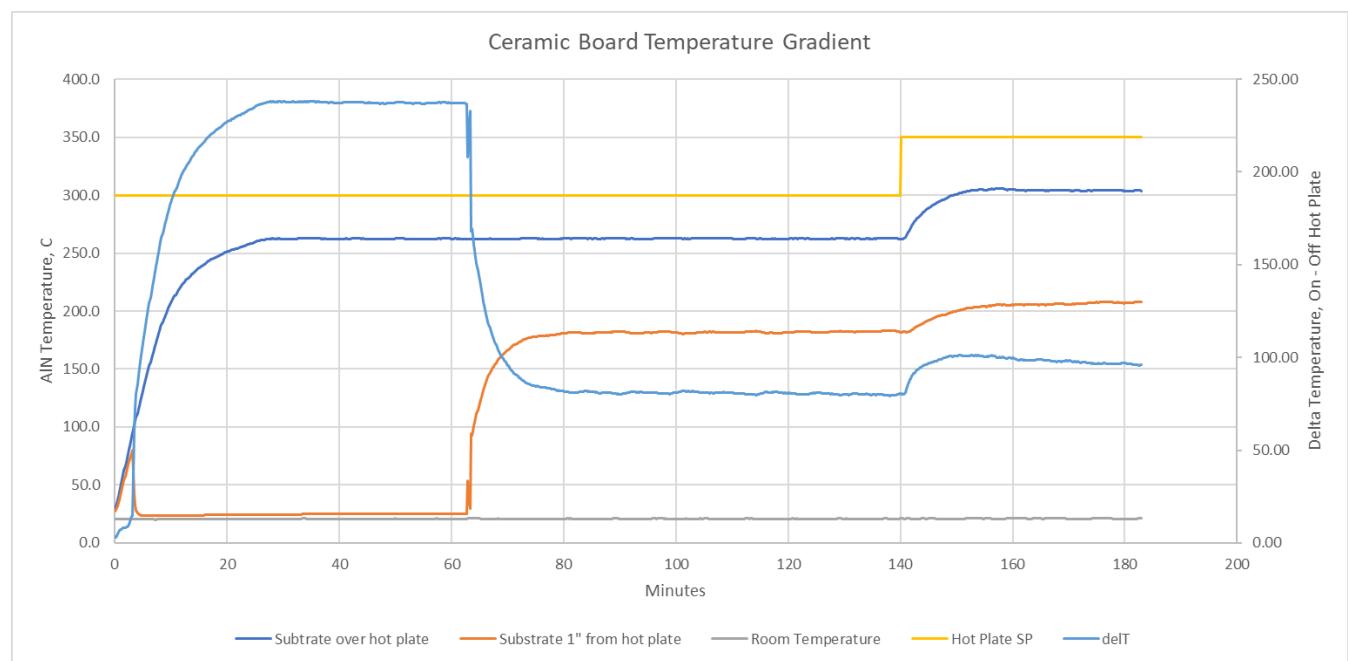

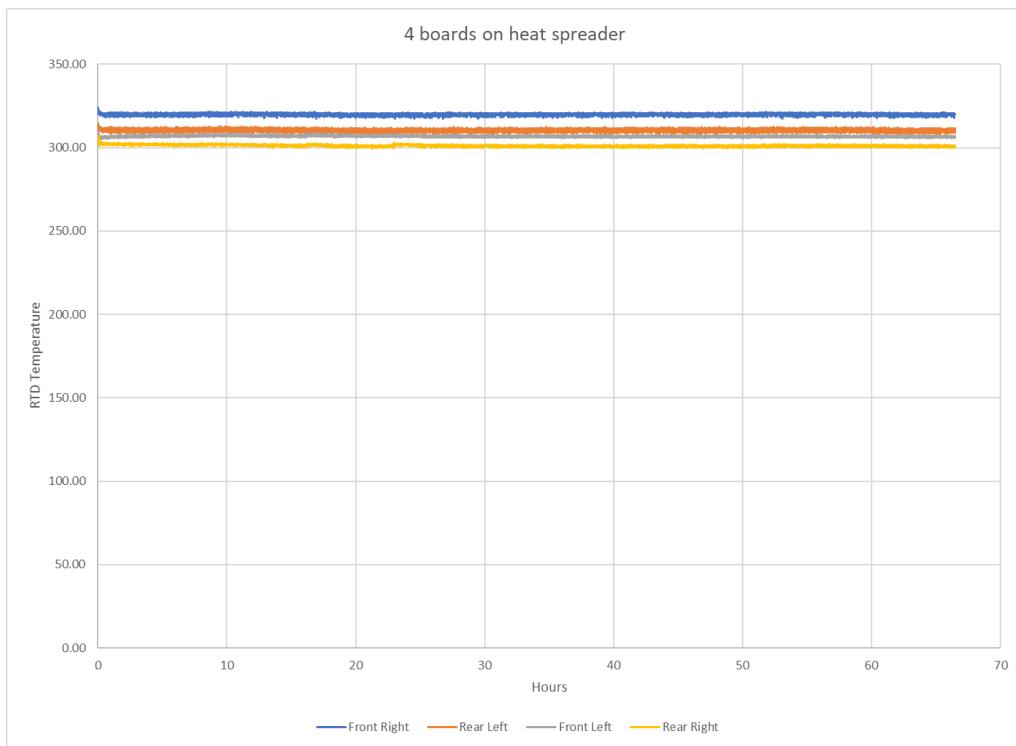

| Figure 70 Temperature gradient test results .....                                                                    | 86 |

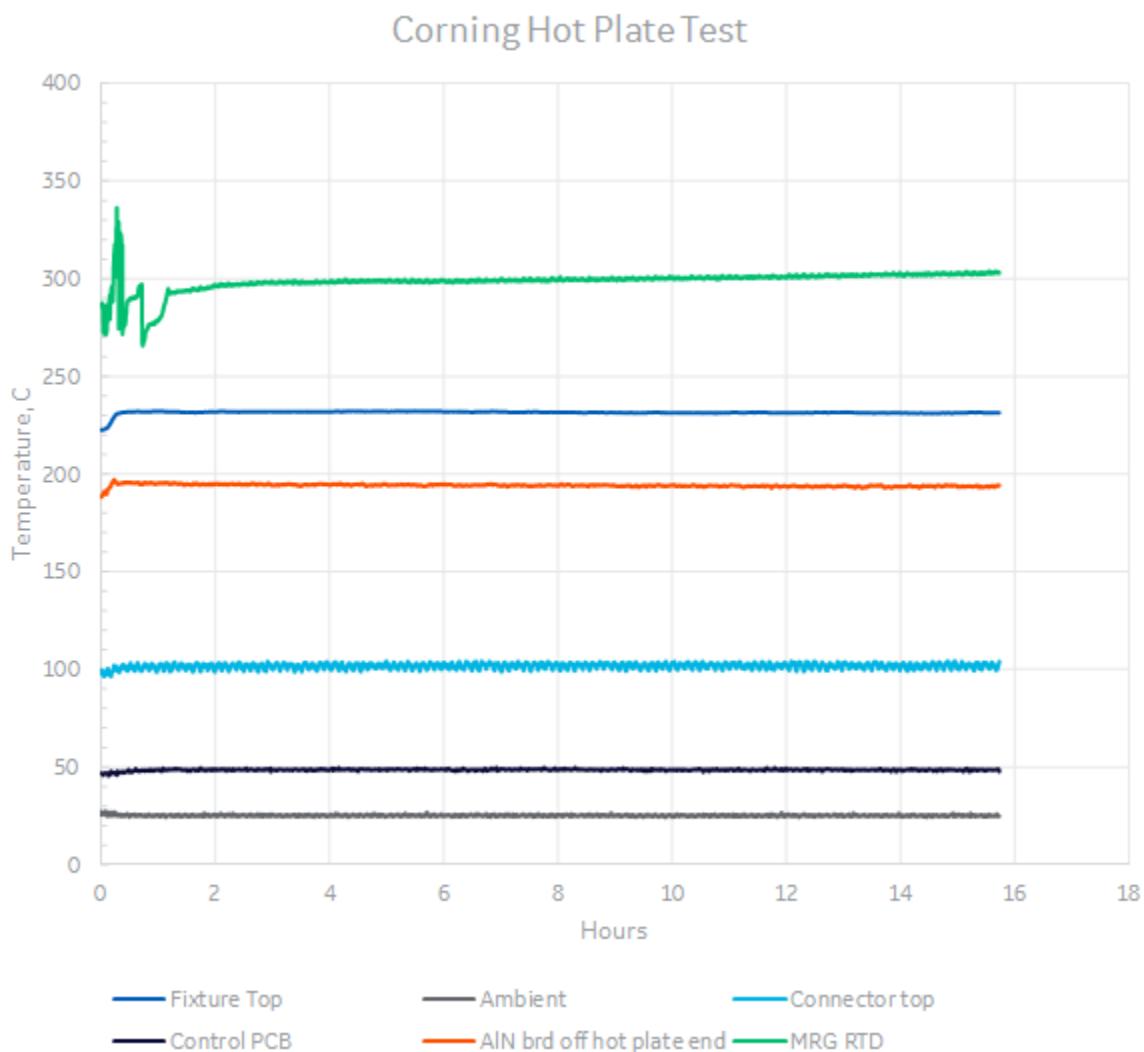

| Figure 71 Component temperature testing on hotplate .....                                                            | 87 |

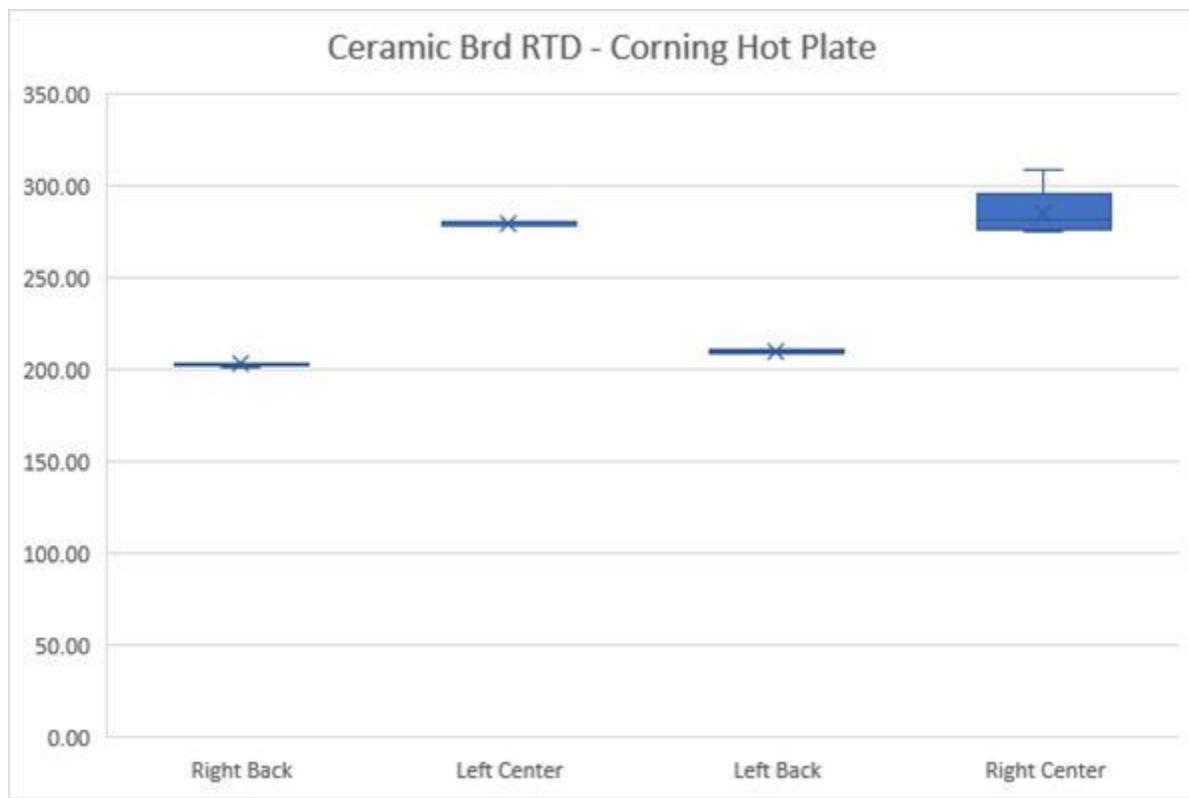

| Figure 72 Hotplate temperature distribution in °C.....                                                               | 88 |

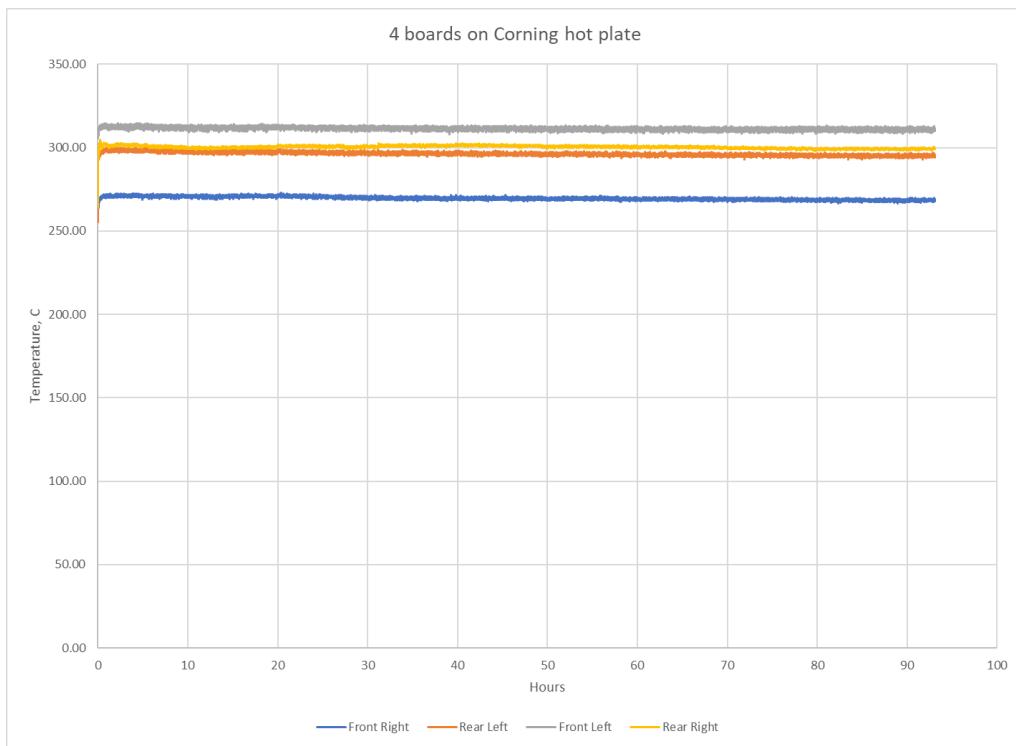

| Figure 73 Temperature spread between 4 test samples .....                                                            | 89 |

| Figure 74 Reduced temperature spread with the addition of a heat spreader.....                                       | 90 |

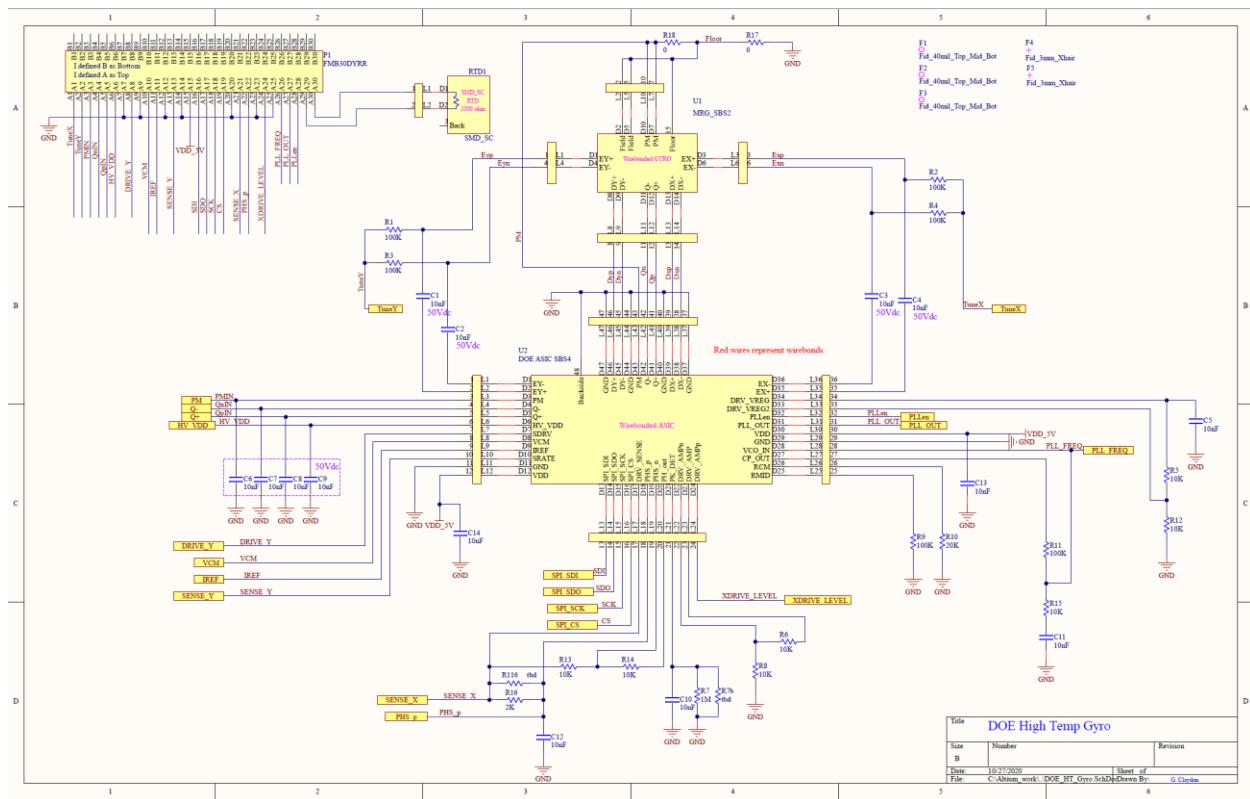

| Figure 75 Ceramic board schematic.....                                                                               | 91 |

|                                                                                                                 |     |

|-----------------------------------------------------------------------------------------------------------------|-----|

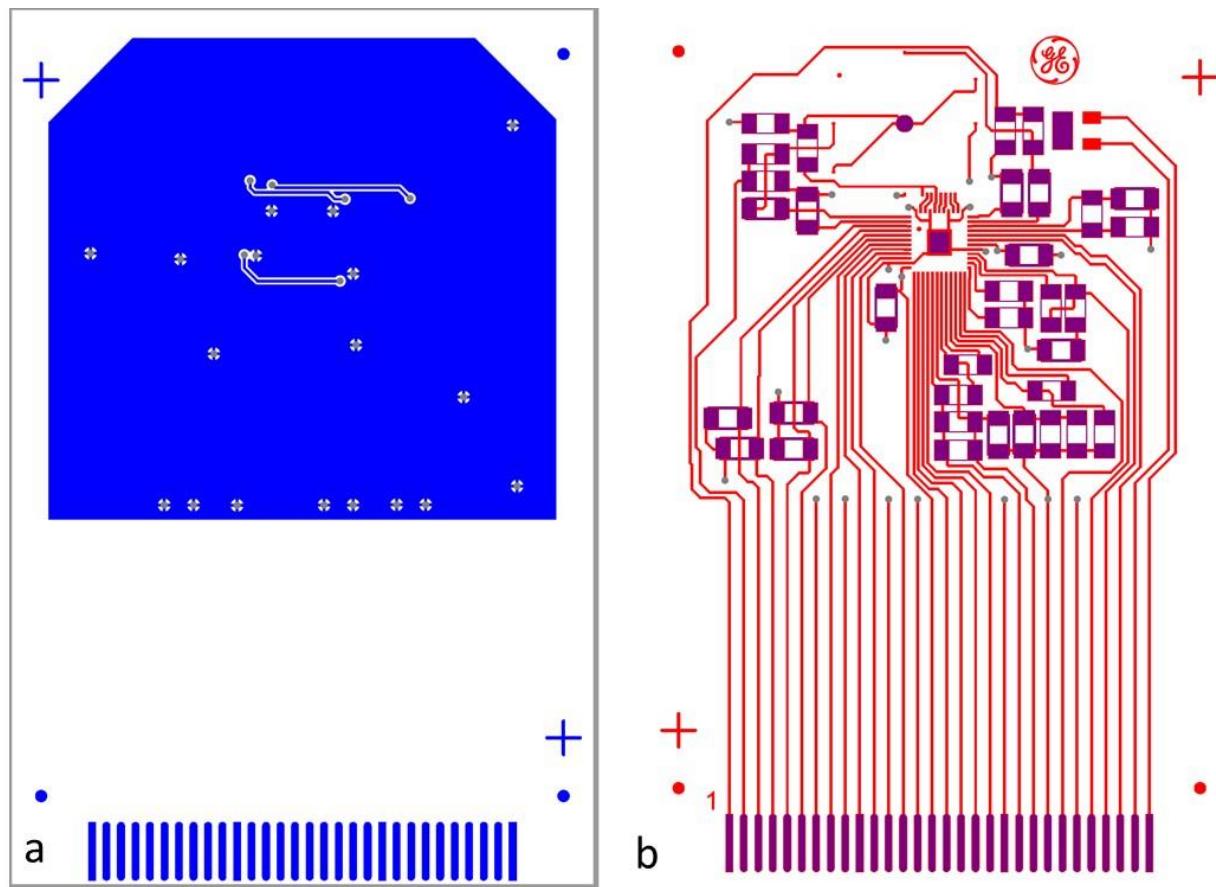

| Figure 76 Ceramic board layout: (a) first interconnect layer layout. (b) second interconnect layer layout. .... | 92  |

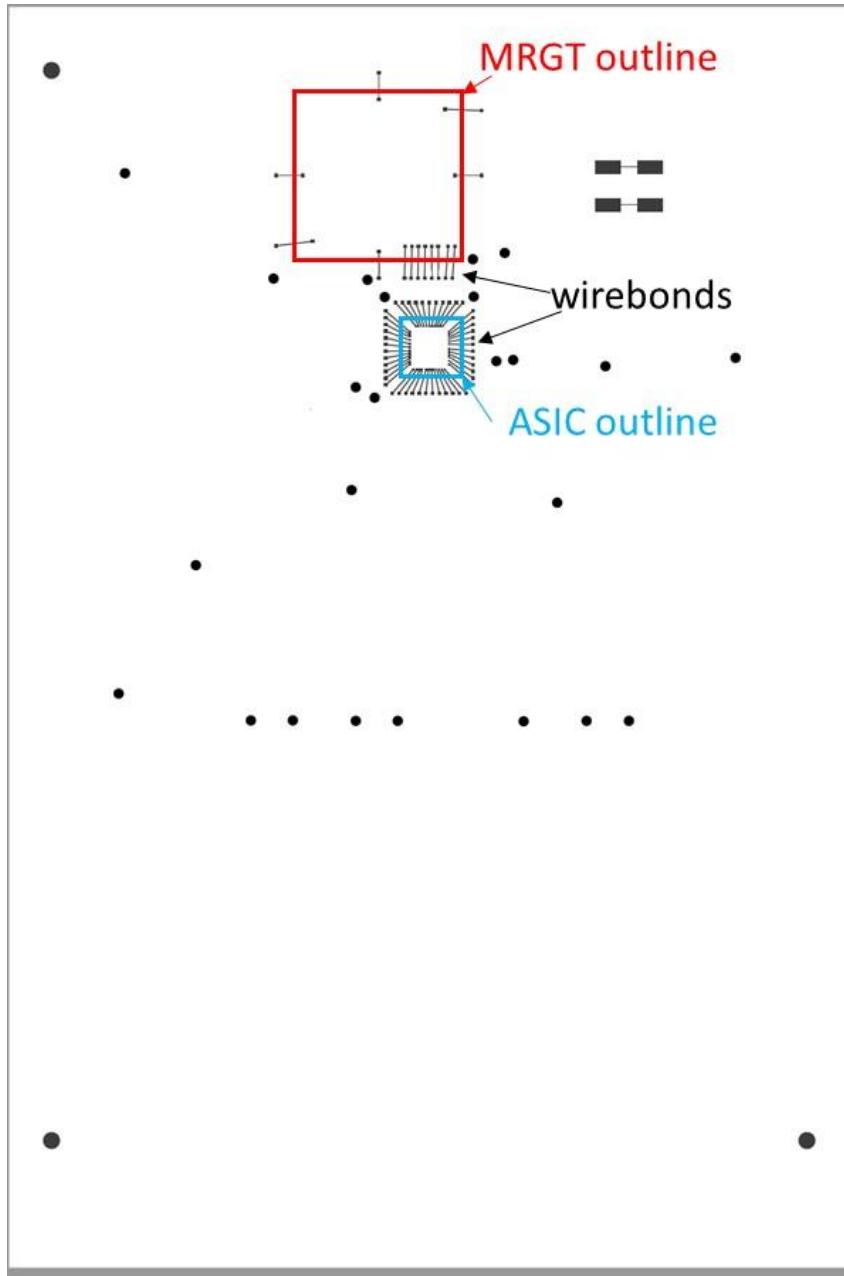

| Figure 77 wirebonding diagram.....                                                                              | 93  |

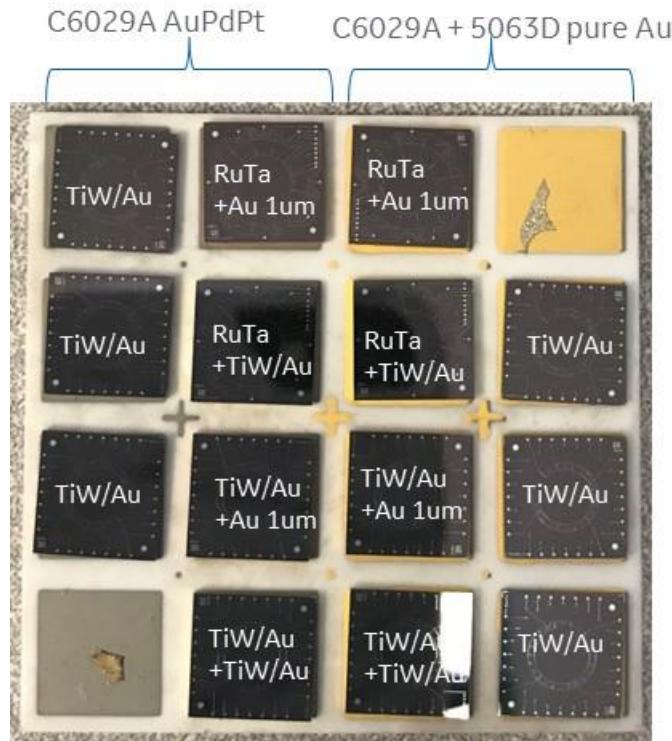

| Figure 78 Die attach screening test coupon.....                                                                 | 94  |

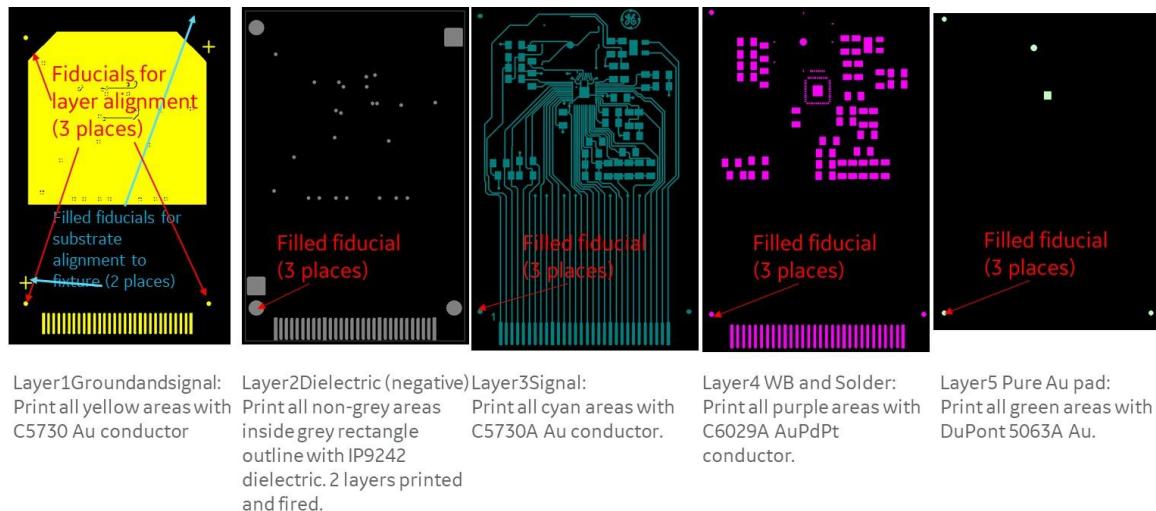

| Figure 79 Ceramic board layers and materials.....                                                               | 95  |

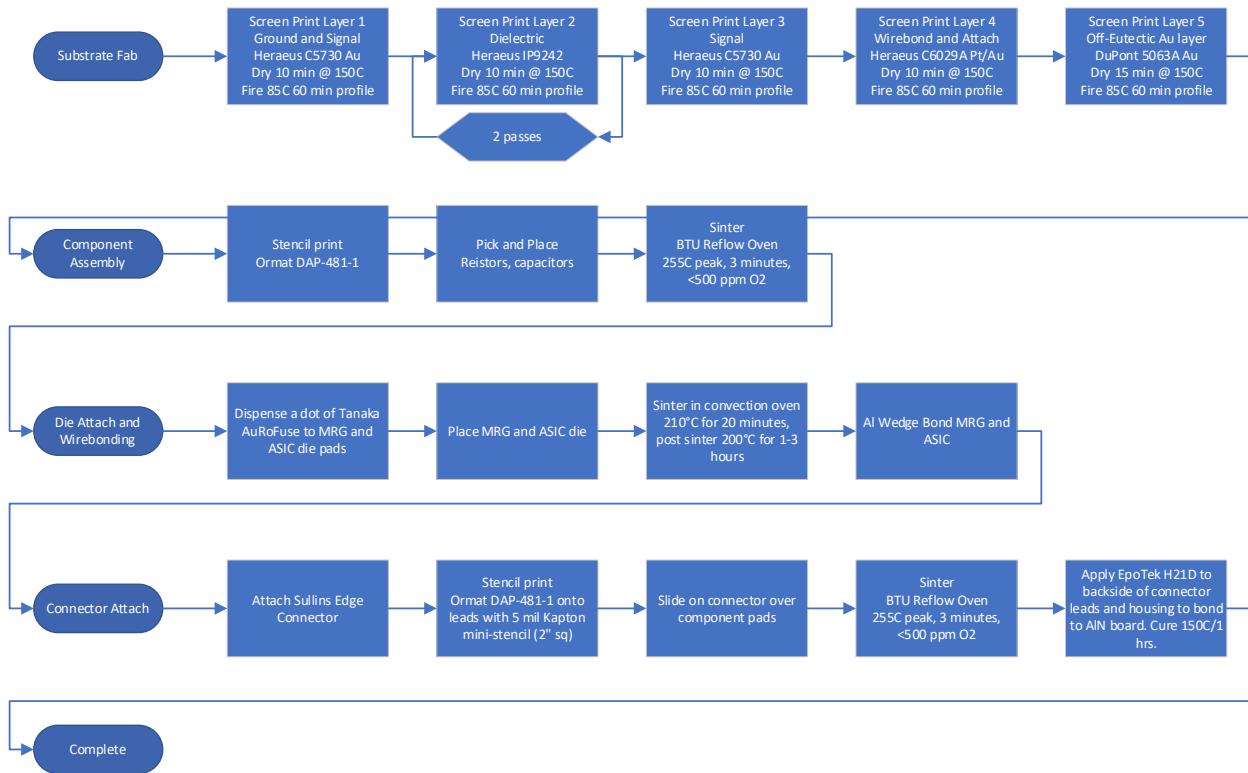

| Figure 80 Ceramic board fabrication and test process flow.....                                                  | 96  |

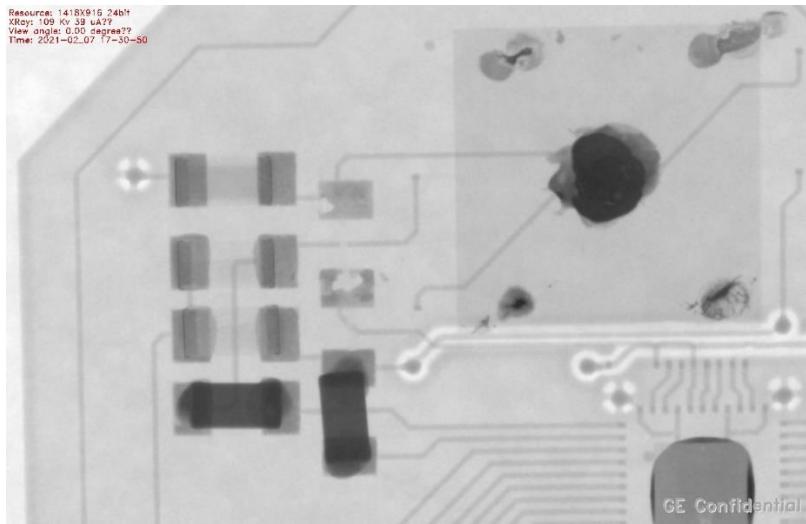

| Figure 81 Xray inspection of completed high temperature boards .....                                            | 97  |

| Figure 82 Assembled 300°C capable ceramic board .....                                                           | 97  |

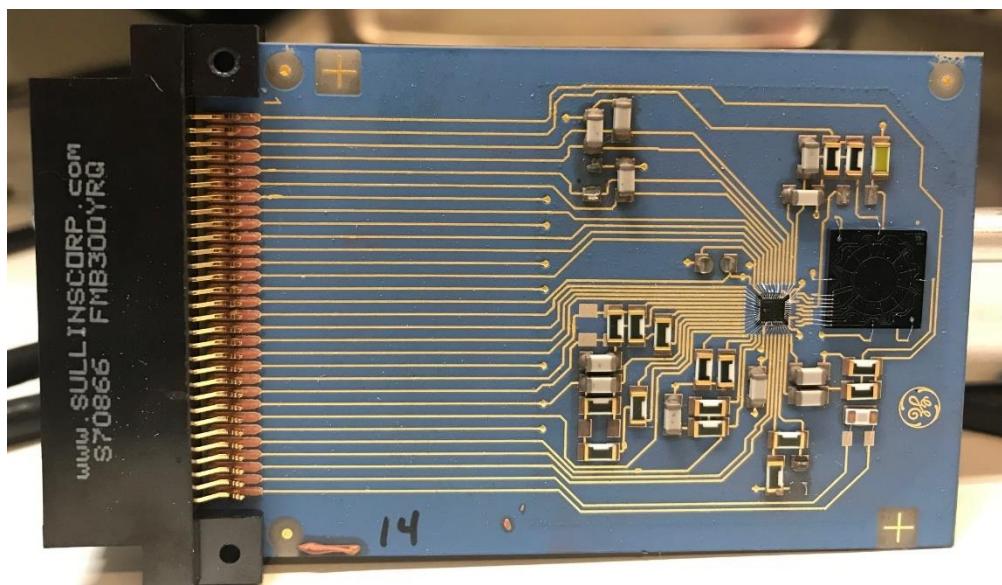

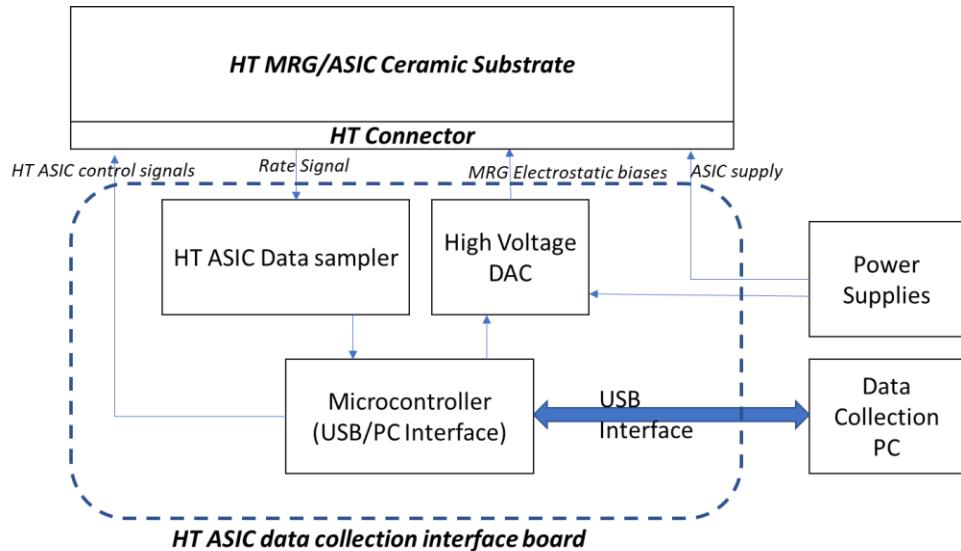

| Figure 83 High Temperature ASIC data collection interface board functional block diagram .....                  | 98  |

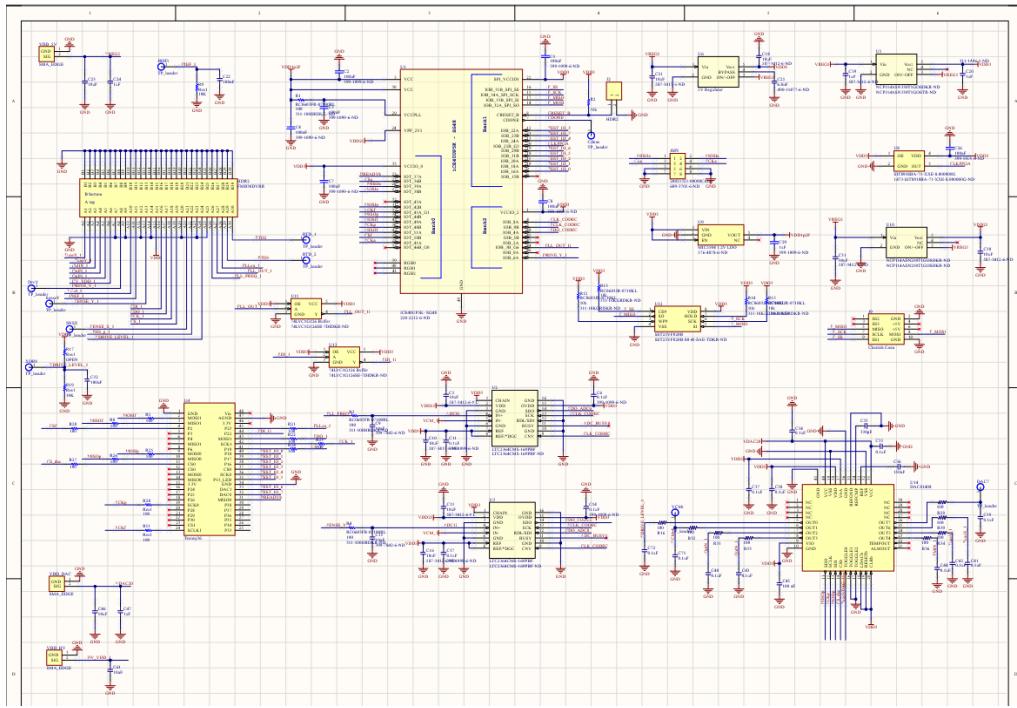

| Figure 84: High Temperature ASIC data collection interface board schematic .....                                | 99  |

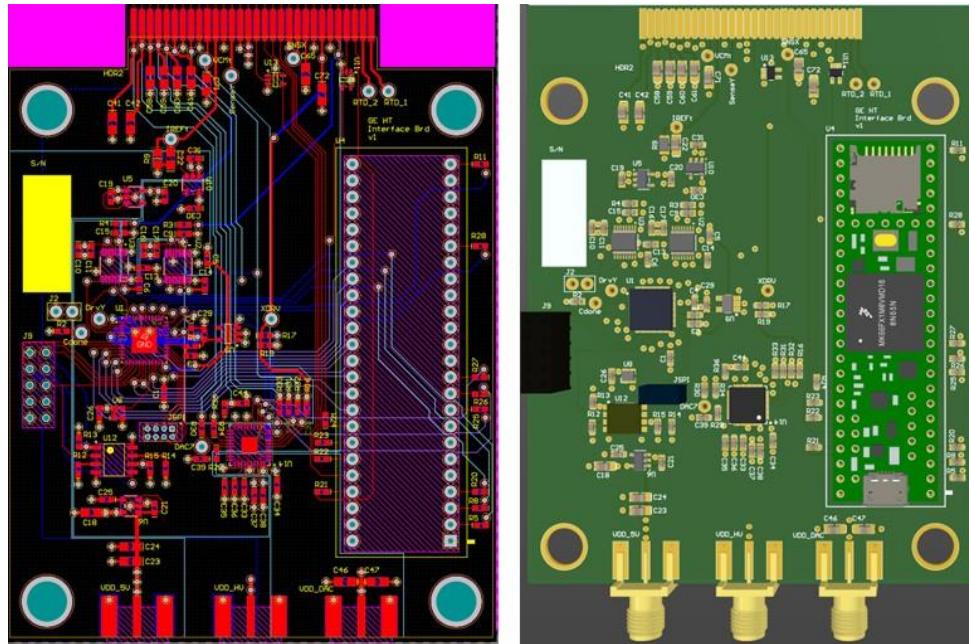

| Figure 85 High Temperature ASIC data collection interface board layout (left) & populated board (right) .....   | 99  |

| Figure 86 Integrated MRGT and ASIC test setup.....                                                              | 100 |

| Figure 87 Interface Board 3-MRG1 transfer function .....                                                        | 102 |

| Figure 88 Interface Board 2-MRG11 transfer function.....                                                        | 102 |

| Figure 89 Interface Board 1-MRG12 transfer function.....                                                        | 103 |

| Figure 90 Mechanical scale factor test of DUTs.....                                                             | 104 |

| Figure 91 IB3-MRG1 Allan Deviation Test Result at 300°C .....                                                   | 105 |

| Figure 92 IB2-MRG11 Allan Deviation Test Result at 300°C .....                                                  | 105 |

| Figure 93 IB1-MRG12 Allan Deviation Test Result at 300°C .....                                                  | 106 |

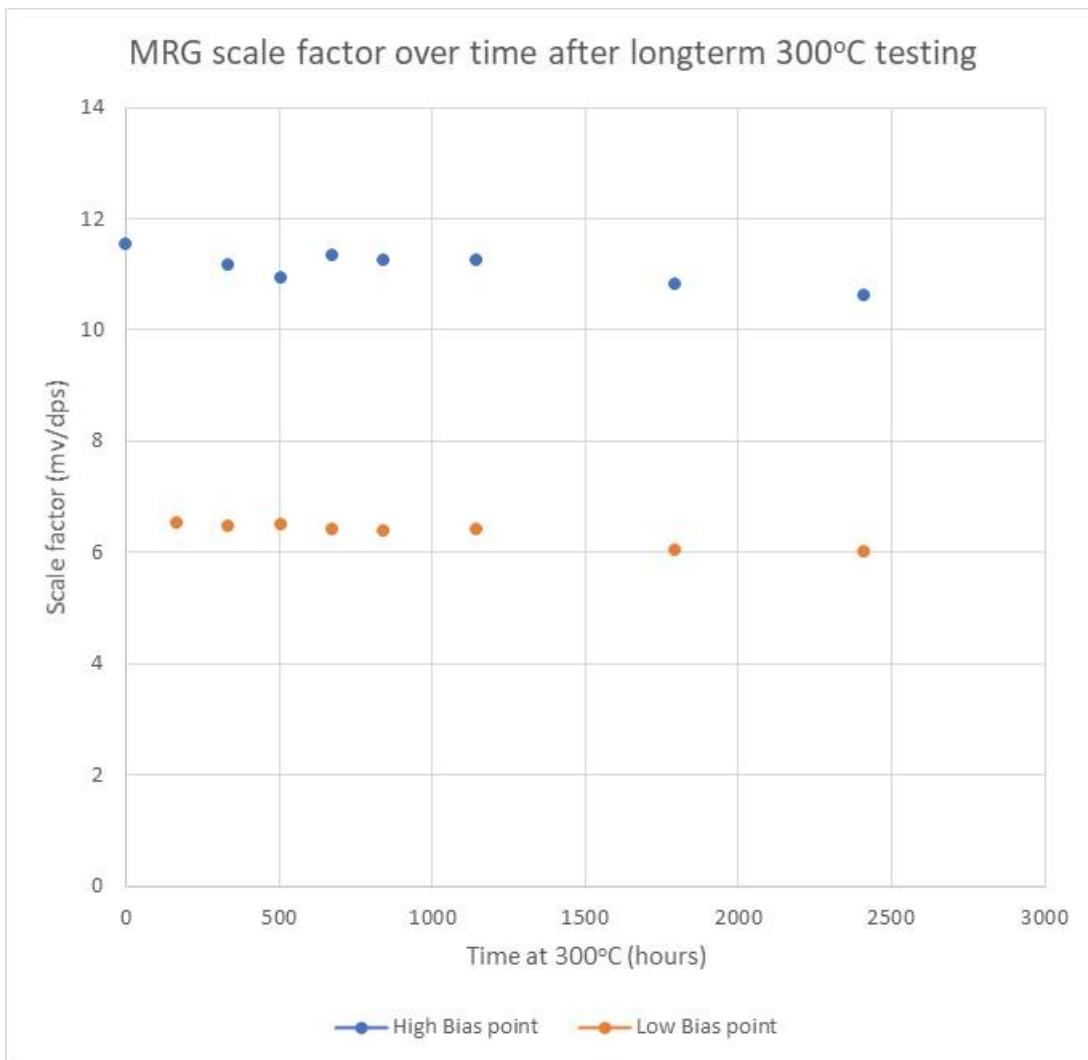

| Figure 94 MRGT scale factor after 300°C high temperature storage testing.....                                   | 108 |

| Figure 95 Post-repair transfer function .....                                                                   | 113 |

## Table of tables

|                                                                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1: First budget period task description.....                                                                                                             | 13  |

| Table 2: Second budget period task description .....                                                                                                           | 15  |

| Table 3 Project accomplishments and significance .....                                                                                                         | 16  |

| Table 4 MRGT measurement summary from room temperature to 300°C.....                                                                                           | 36  |

| Table 5 MRGT measurement summary to 225 prior to temperature compensation and test setup modification.....                                                     | 37  |

| Table 6 Process capability Advancements.....                                                                                                                   | 44  |

| Table 7: GE MRG Die Level Transfer Function (Xsense/Xdrive) vs. swept die temperature summary .....                                                            | 48  |

| Table 8: GE MRG R2C6 Measured Transfer Function Summary .....                                                                                                  | 54  |

| Table 9: ASIC Interface Specifications for GE MRG to achieve Mechanical Thermal Noise limited performance and ARW<0.01°/√hr at 1um MRG drive displacement..... | 56  |

| Table 10 AFE performance summary across corners .....                                                                                                          | 66  |

| Table 11 Noise floor measurements for high and log gain channels across temperature .....                                                                      | 81  |

| Table 12 ASIC noise measurement versus simulation comparison .....                                                                                             | 81  |

| Table 13: Functional test parameters and metrics .....                                                                                                         | 84  |

| Table 14: Performance test parameters and metrics.....                                                                                                         | 84  |

| Table 15: Lifetime test parameters and metrics .....                                                                                                           | 85  |

| Table 16: ASIC gain settings.....                                                                                                                              | 101 |

| Table 17: Summary of optimal operating points and test results for the DUTs operating at ambient .....                                                         | 104 |

| Table 18: Summary of optimal operating points and test results for the DUTs operating at 300°C .....                                                           | 104 |

| Table 19 MRGT measurement summary after 300°C storage testing.....                                                                                             | 109 |

| Table 20 First interval (baseline) 300°C data at start of test for the three test articles                                                                     | 110 |

| Table 21 Second interval test results at 300°C for the three test articles .....                                                                               | 111 |

| Table 22 Third interval test results at 300°C for the three test articles .....                                                                                | 111 |

| Table 23 Fourth interval test results at 300°C for the three test articles .....                                                                               | 111 |

| Table 24 Milestone Summary Table.....                                                                                                                          | 114 |

| Table 25 Project output reports .....                                                                                                                          | 120 |

## Executive Summary

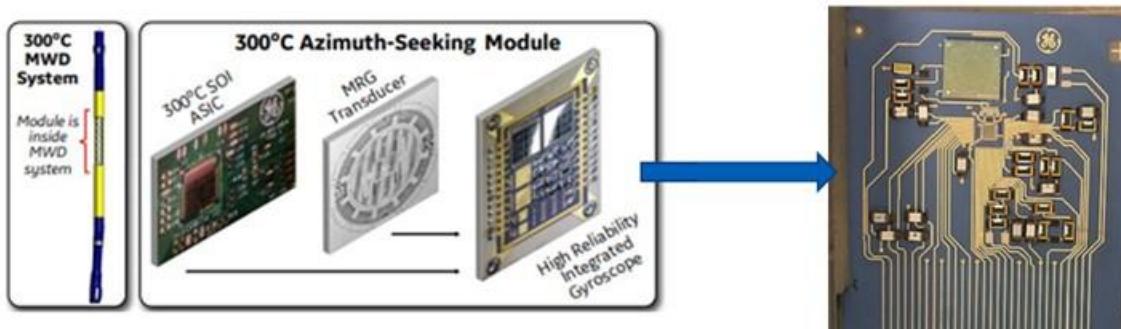

The 300°C Microelectromechanical system (MEMS) gyroscope project aims to contribute to DOE's goal of increased geothermal drilling efficiency by 2025 through the development of a 300°C MEMS gyroscope for Measurement While Drilling (MWD). At the conclusion of the 2-year project, the team will develop a 300°C capable MEMS gyroscope containing GE's patented Multi-Ring Gyroscope Transducer (MRGT) design, custom Silicon-On-Insulator (SOI) based frontend and feedback control electronics, and with demonstrated functionality and lifetime beyond 1000 hours.

The project is divided into two budget periods with Go/No-Go decision at the end of the first budget period. The goal for the first budget period is to establish the feasibility of the MRGT and electronics design for meeting the 300°C performance requirements. The goal for the second budget period is to integrate the MRGT with the SOI-based application specific integrated circuit (ASIC) and demonstrate capability to operate at 300°C for 1000 hours.

In Budget Period 1 we met the phase 1 goal. We successfully validated the combined MRG, electronics and packaging capability entitlement to achieving 0.5 degrees azimuth uncertainty while enabling operation at significantly higher temperatures than the state-of-the-art.

In Budget Period 2, we successfully completed the integration of the MRGT and ASIC with associated high temperature, high reliability packaging to demonstrate the performance and functionality of the integrated gyroscope across the temperature range from room temperature to at 300°C. Furthermore, the team demonstrated operating life of >1,000 hours at 300°C, thus providing a validation of application-relevant lifetime capability.

Significant findings of project include:

- **10X performance improvement over state-of-the-art**

- The GE team has achieved a bias instability of 0.01 °/hr at 25°C and angular random walk of 0.003°/rt(hr). This is a 10X improvement over state-of-the-art MEMS gyroscopes that are limited to 0.1 °/hr and 0.01°/rt(hr), and enables azimuth accuracy <0.25°.

- This substantial achievement positions this MEMS-based solution to compete with conventional, high-cost gyroscope technology but with the size, cost, and reliability advantage of MEMS.

- **300°C operation, >600°C survivability**

- The GE team validated the design of GE's gyroscope by demonstrating operation at 300°C. Furthermore, survivability of the packaged gyroscope was demonstrated to 600°C during which we observed no hysteresis or any sign of performance degradation. These results exceed the temperature capability of existing MWD tools for oil and gas drilling and

enabled the successful demonstration of 1,000-hour operation at 300°C of the integrated gyroscope system comprising the MRGT and ASIC.

- **New gyroscope package with high reliability, 10X volume reduction**

- We developed a new wafer-level package (WLP) whose integrity improves with exposure to high temperatures (during processing the package is annealed at 1100°C to form covalent silicon-silicon bonds, subsequent annealing improves vacuum integrity by gettering residual oxygen). Besides enabling high reliability and long lifetime, this package has the added benefit of a small form factor (approximately 10X reduction in volume relative to state-of-the-art MEMS gyroscopes using metal-can lids).

- **Highly integrated, high temperature capable SOI-based electronics design**

- GE in collaboration with Inertial Wave has successfully designed and simulated the silicon-on-insulator based control ASIC. The design incorporates advanced algorithms and analytics that enable temperature compensation in addition to modern control algorithms (e.g., quadrature tuning). The design requirements and capabilities were validated using board-level electronics. Simulations show our design meets all application requirements. The control ASIC design has been fabricated and tested across the full temperature range of interest up to 300°C.

- **High temperature, high reliability MEMS gyroscope system, >150°C temperature capability increase over state of the art.**

- The integrated functionality and lifetime of the developed MRGT and ASIC devices was shown to function as intended across the temperature range of interest and >1,000 hours of operating lifetime at 300°C was demonstrated.

In addition to the significant findings highlighted here, the team has also contributed to DOE's goal of advancing scientific understanding and industry knowledge through several publication and conference presentations that are covered in detail in Publications, Abstracts and Presentations section.

## Project Overview

Directional drilling is the practice of steering a wellbore along a predefined trajectory leading to a subsurface target (1). The 300°C MEMS gyroscope project aims to advance the state of the art, contributing to DOE's goal of increased geothermal drilling efficiency by 2025 through the development of a 300°C gyroscope for Measurements While Drilling (MWD) orientation tool, while alleviating the magnetic interference, temperature limitation, size and power constraints imposed by today's magnetometer-based systems. At the conclusion of the 2-year project, the team has developed and demonstrated a 300°C capable gyroscope containing a high temperature optimized Microelectromechanical system (MEMS) Multi-ring Gyroscope Transducer (MRGT) and Silicon-On-Insulator (SOI) based frontend and feedback control Application Specific Integrated Circuit (ASIC), and with functionality and lifetime beyond 1000 hours.

The project was divided into four tasks spanning two budget periods with Go/No-Go decision at the end of the first budget period, and regularly scheduled Status Update meeting every six months.

The goal for the first budget period is to establish the feasibility of the MRGT and electronics design to meet functional and performance requirements at 300°C, and validate gyroscope component performance capabilities. The technical work was organized into two main tasks and a number of subtasks under each. Task 2 constituted the analysis and design aspects of the MRGT and ASIC development. Task 3 covered the component fabrication and testing. The task structure of the first budget period is shown in Table 1.

*Table 1: First budget period task description*

| <b>Task/Subtask</b> | <b>Description</b>                                                                                                                                             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1                 | Assess High Temperature Performance, Reliability Risks and Requirements for MEMS Gyroscopes                                                                    |

| 2.1.1               | Azimuth uncertainty definition will be defined and flow-down to critical MRGT and electronics angular random walk, bias instability and noise specifications). |

| 2.1.2               | Benchmark commercial devices including performance and temperature capability.                                                                                 |

| 2.2                 | Assess MRGT Characteristics and Performance at High Temperature                                                                                                |

| 2.2.1               | Perform high temperature characterization of MRGT at probe station.                                                                                            |

| 2.2.2               | Develop a 300°C device testing platform using localized heating of MRGT device.                                                                                |

| 2.2.3               | Evaluate temperature performance of MRGT.                                                                                                                      |

| 2.3                 | Design High Temperature Optimized MRGT                                                                                                                         |

| 2.3.1               | Perform design optimization and modeling of MRGT for 300°C operation.                                                                                          |

- 2.3.2 Assess the process improvement and risk required by the MRGT design improvement.

- 2.4 Develop Requirements for MRGT Frontend, Control and Compensation ASIC

- 2.4.1 Identify key electronics performance metrics for MRGT interrogation, control and compensation electronics.

- 2.4.2 Design and build of electronics process evaluation test circuits.

- 2.4.3 Conduct electronics design tradeoffs and define electronics architecture given system requirements and process constraints.

- 2.4.4 define electronics performance entitlement and compare with the electronics requirements.

- 3.1 Fabrication and Testing of High Temperature MRGT

- 3.1.1 Fabricate high temperature MRGT.

- 3.1.2 Perform die level characterization of the fabricated device at room temperature.

- 3.1.3 Perform die level characterization of the fabricated device at high temperature.

- 3.2 Develop High Temperature Frontend and Control Electronics

- 3.2.1 Conduct interrogation and control electronics functional modeling.

- 3.2.2 Complete Transistor level design and validation through circuit simulation.

- 3.2.3 ASIC layout and fabrication.

- 3.2.4 Package ASIC and build evaluation platform.

- 3.2.5 ASIC performance and functionality evaluation.

- 3.3 Design and Build High Temperature System Test Environment

- 3.3.1 Package and assemble high temperature gyroscope for testing.

- 3.3.2 Develop functionality and reliability test plan and define performance metrics and success criteria.

- 3.3.3 Design and build temperature capable test platform for system evaluation.

In the second budget period, the integrated gyroscope system (MRGT, Electronics and high temperature capable packaging) performance and capability to operate for 1000 hour at 300°C were tested and the capability of a high temperature gyroscope system was demonstrated.

The technical work for the second budget period was organized into a single technical task (Task 4) that included the integration and test of the components developed in the first budget period. Task 4's three main objectives are:

1. System integration of MRGT and ASIC components

2. Functional and performance testing of the integrated gyroscope

3. Lifetime testing of the integrated system

The task structure of the first budget period is shown in Table 2.

Table 2: Second budget period task description

| Task/Subtask | Description                                                                  |

|--------------|------------------------------------------------------------------------------|

| 4.1          | Demonstrate High Temperature Gyroscope System in Laboratory Test Environment |

| 4.1.1        | Conduct Integration testing of the gyroscope system.                         |

| 4.1.2        | Performance characterization versus temperature (20°C to 300°C).             |

| 4.1.3        | Reliability testing at 300°C for a minimum of 1000 hours                     |

During the period of performance of the project, the high temperature MRGT and ASIC were developed and validated on a component level. The MRGT and ASIC components were then integrated with high temperature packaging and supporting passive devices to further advance the technology readiness level (TRL) and demonstrate lifetime and temperature capability of the gyroscope system as seen in Figure 1.

Figure 1 Progress and TRL advancement from concept to 300°C capable gyroscope with demonstrated >1000 hours of lifetime

## Summary of project accomplishments.

### Performance entitlement validation

- ✓ MRGT device design

- ✓ Achieved state of the art room temperature navigation grade capability

- ✓ Developed physics -based model of performance dependence on temperature

- ✓ Validated model with temperature measurements

### Electronics capability

- ✓ Developed electronics architecture to support driving, sensing and control of MRG

DE-EE0008604: A MEMS Gyroscope for Reliable Long Duration Measurement While Drilling at 300°C

- ✓ Validated performance in board-level electronics

- ✓ Achieved design electronics noise below mechanical noise

#### Packaging capability

- ✓ Developed 300°C+ capable packaging approach

- ✓ Validated device packaging in high temp tests to 300°C

- ✓ Mapped packaging design to 300°C for 1000 hours capable design rules established in prior work

#### Fabrication capability

- ✓ Developed reliable wafer level packaging process capable of surviving 600°C

- ✓ Achieved device yield of 80%

Project achievements significance and impacts are summarized in Table 3

*Table 3 Project accomplishments and significance*

| Aspect                    | Improvement                                       | Significance                                                                                                                                                                               | Impact                                |

|---------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| MRGT design               | GE's Optimized multi-ring gyroscope design        | Achieved state-of-the-art room temperature bias instability of 0.01deg/hr and ARW of 0.003deg/rt(hr), an order of magnitude better performance than commercially available MEMS gyroscopes | System accuracy                       |

| System                    | Demonstrated functionality to 300°C               | ~200°C higher operating temperature than commercially available devices                                                                                                                    | Temperature capability                |

| Packaging                 | WLP wafer bonding packaging process               | Increased quality factor by >4X. Achieved quality factor of 13,000 --> Reduced device noise by 2x                                                                                          | System accuracy                       |

| Fabrication               | MEMS/ASIC process                                 | System size reduction: MRGT is 10mmx10mm, ASIC is 3mmx3mm                                                                                                                                  | Compatibility with downhole tool size |

| MRGT design + Electronics | In situ frequency matching and quadrature nulling | Increase scale factor by >100x                                                                                                                                                             | System accuracy                       |

|                                       |                                                                         |                                                                                                                                                |                                                     |

|---------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Electronics                           | Drive level temperature compensation                                    | reduced scale factor deterioration over temperature by >4x from 25°C to 200°C                                                                  | System accuracy over temperature                    |

| Fabrication                           | Fabrication bonding and etch process improvements                       | Increased device yield from 50% to 80%                                                                                                         | Commercial viability                                |

| Fabrication                           | High temperature capable fabrication process                            | Demonstrated survivability to 600°C                                                                                                            | Reliability at temperature                          |

| Packaging                             | High temperature capable substrate, attach and interconnect             | Reliable long-term operation at 300°C                                                                                                          | Reliability at temperature                          |

| Electronics                           | Silicon-On-Insulator electronics                                        | Reliable 300°C + capable electronics >150°C increase over conventional Si electronics, and 100°C increase over HT optimized Si electronics     | Temperature capability                              |

| Fabrication and packaging integration | MRGT signal redistribution routing layer                                | Demonstrated routing simplification between ASIC and MRGT. Low crosstalk, compact footprint routing minimizes signal crossovers and parasitics | Reliability, performance and system miniaturization |

| Packaging                             | High temperature multi-layer substrate                                  | Substrate size reduction and signal routing simplification                                                                                     | System performance and temperature capability       |

| Integrated system                     | MRGT, ASIC and packaging design                                         | Demonstrated functionality and performance from room temperature to 300°C                                                                      | Technology demonstration                            |

| Integrated system Lifetime            | High temperature, high reliability MRGT and ASIC components + packaging | Demonstrated >1500 hours of operating life at 300°C                                                                                            | Technology viability for long term operation        |

## Significant findings and achievements

10X performance improvement over the state-of-the-art

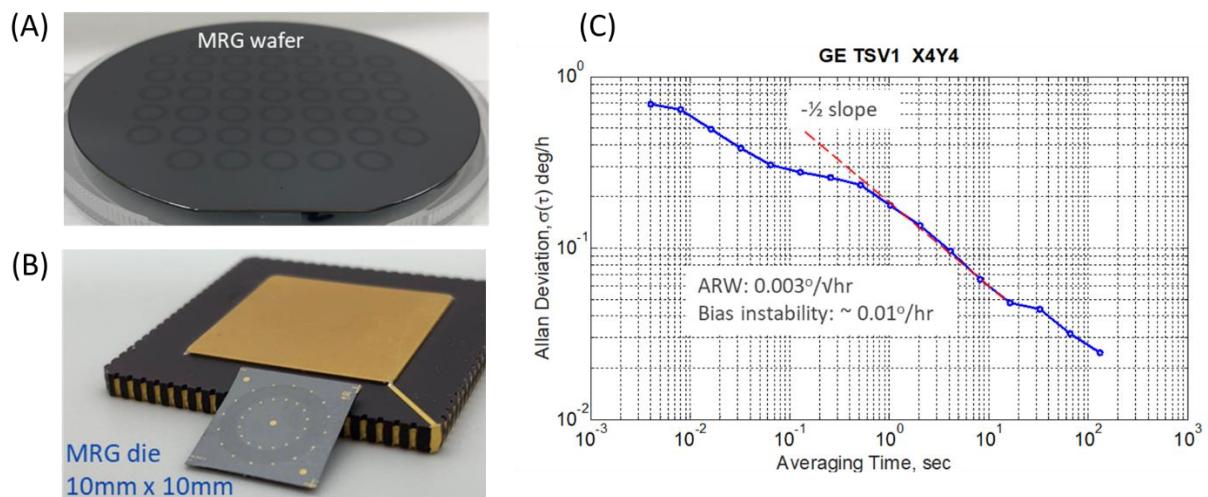

The GE team has successfully developed the MEMS based MRGT capable of azimuth-seeking in MWD applications at 300°C. The MRGT prototype has been demonstrated to achieve bias instability of 0.01 deg/hr and angular random walk (ARW) better than 0.003 °/rt(hr), capable of meeting azimuth finding accuracy better than 0.25° at room temperature (the azimuth accuracy at 300°C is expected to be better than 0.5°, which we'll discuss in more detail below). A picture of the MRGT wafer after processing and a single MRGT die is shown in Figure 2 A-B, and an example Allan deviation measurement showing this level of performance is shown in Figure 2C.

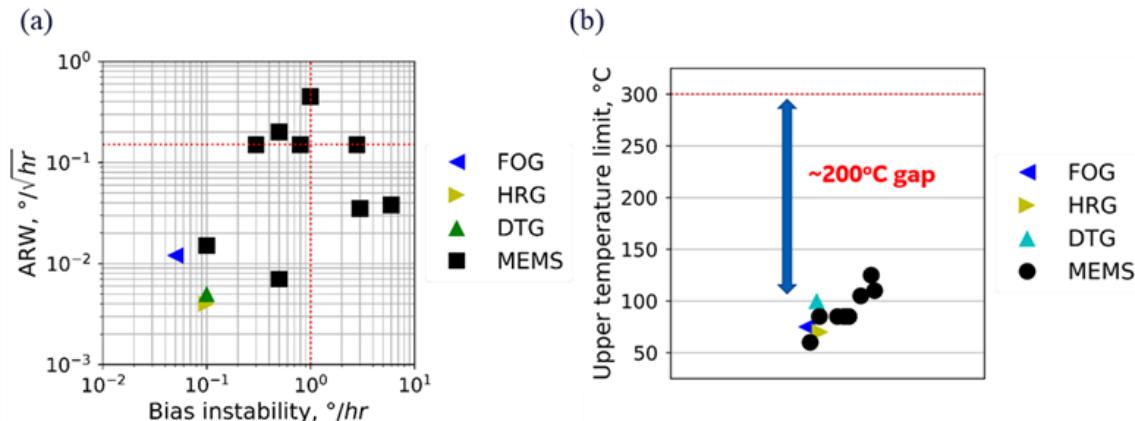

To put this level of performance in perspective, part of Task 1 was dedicated to benchmarking state-of-the-art commercial-off-the-shelf gyroscopes (COTS). From our survey results shown in Figure 3, the highest performing MEMS gyroscopes have bias instabilities of approximately 0.1 °/hr and angle random walk of 0.01 °/rt(hr) at room temperature. Therefore, the performance demonstrated by the GE MRGT on this program represents a 10X improvement over the state-of-the-art COTS devices.

Figure 2 (A) Wafer containing 45 MRGT die. (B) Single MRGT die. (C) Allan Deviation measurement on GE's MRGT prototype, showing angle random walk of 0.003 °/rt(hr) and bias instability of 0.01 °/hr.

Figure 3 Performance and temperature capability of COTS devices surveyed. (a) Best performing devices have bias instabilities approaching 0.1 deg/hr at room temperature. (b) None of the devices can operate at 300°C - there is  $\sim 200^{\circ}\text{C}$  capability gap

Another important observation in the COTS survey is the temperature capability of COTS MEMS gyroscopes. All the devices we surveyed are based on conventional silicon processing and are therefore limited to low temperature operation ( $<120^{\circ}\text{C}$ ). Our discussion of performance requirements and survey of the published MEMS devices has led to the discovery that no existing commercial MEMS gyroscope can reliably operate at  $300^{\circ}\text{C}$  for 1000+ hours while maintaining the sub-degree-per-hour accuracy needed for MWD. This is a critical technology that needs to be invented and developed.

The demonstrated performance improvement over state of the art is achieved through the combination of the MRGT device design and the sensing, tuning and control capabilities enabled by the electronics architecture as is described below in the MRGT Device Design and Capability and the High Temperature ASIC design sections.

#### 300°C operation, 600°C survivability

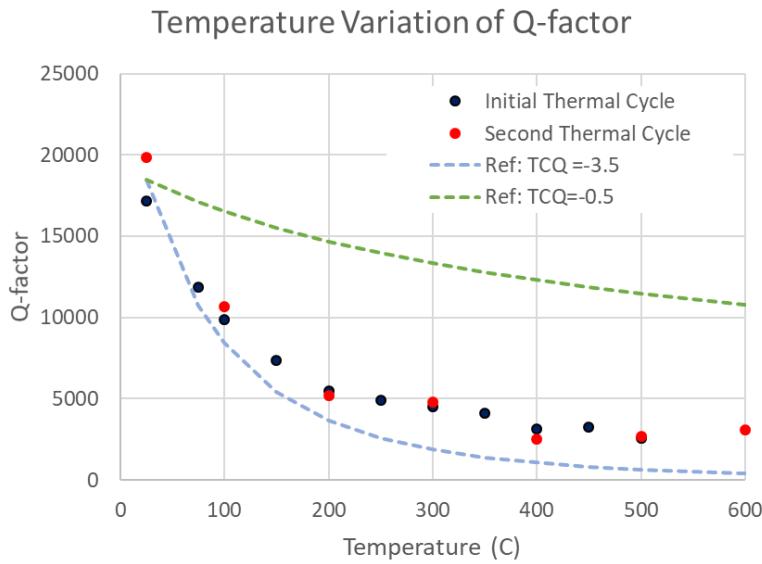

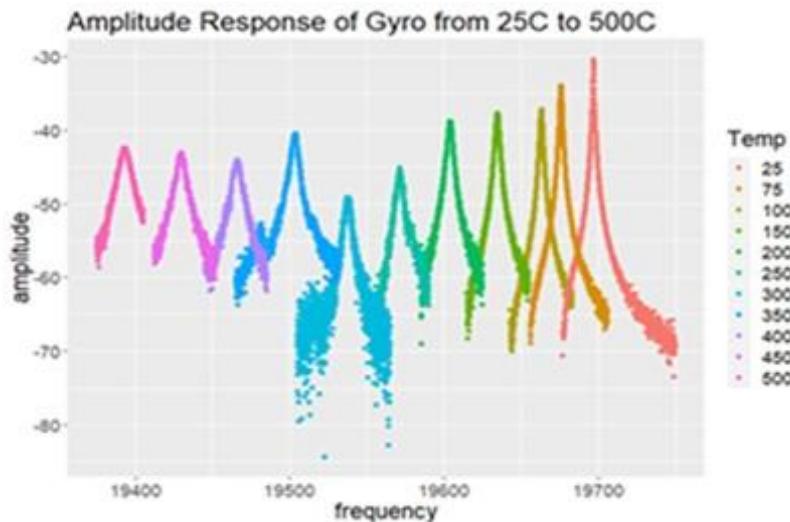

We validated the temperature design of the MRGT by completing tests at elevated temperatures. The MRGT scale factor has been measured from room temperature to  $300^{\circ}\text{C}$  validating functionality and response to rotation rate across the temperature range and illustrated in Figure 15. The WLP package was tested from room temperature to  $600^{\circ}\text{C}$ , and device resonance was recorded across the temperature range as can be seen in Figure 4 and Figure 20 below. The observed resonance across the temperature validated the WLP capability to maintain vacuum and the device's robustness at extreme temperature.

New gyroscope package with high reliability and 10X volume reduction

The bare die-on-board packaging approach developed, coupled with the WLP vacuum package and a highly integrated readout and control ASIC architecture has enabled a highly miniaturized, high temperature capable gyroscope. The elimination of second level packaging for the MRGT and the ASIC results in an MRGT device that is approximately 10mmx10mm in size and an ASIC that is approximately 3mmx3mm. The combined substrate and MRGT and ASIC thickness is approximately 1mm in thickness compared to approximately 18mm for gyroscopes and associated electronics utilized in oil and gas application. Additional detail on packaging is addressed more fully in the Device packaging advancements and the ASIC packaging sections.

#### Highly integrated, high temperature capable SOI-based electronics design

In the first budget period, the team completed the development of the electronics architecture capable of meeting the excitation, sensing and control requirements, while achieving the system noise and performance across the temperature range of operation. The electronics architecture capabilities were first corroborated through functional simulations, and further refined and implemented utilizing board-level electronics. Performance testing conducted during the first budget period utilized these board-level electronics to further validate the functionality and performance. The validated board-level design was then converted to an integrated ASIC design in an SOI process capable of operating at 300°C. Functional simulations across operating temperatures and fabrication corners were utilized to validate the ASIC design prior to release to fabrication. The highly integrated ASIC comprises the functionality of the board level electronics in a 3mmx3mmX0.5mm semiconductor chip.

## Detailed technical achievements

This section covers the detailed technical achievement for the major project components which include the MRGT device design, fabrication, electronics, component test, system integration and system test.

## MRGT Device Design and Capability

This section of the report details the design and development steps and advancements achieved in the MRGT device to enable the performance needed to support the geothermal downhole navigation and orientation needs.

### MRGT Device critical performance parameters to meet requirements

MRGT is a type of Coriolis Vibratory Gyroscope (CVG) that uses a vibrating multiple-ring structure to determine the rate of rotation. MRGT takes advantage of a pair of degenerate resonance modes of a multiple-ring structure, so called 'wineglass modes' (specifically, wineglass mode 3). By design, these two resonance modes have identical frequency and identical mode shape, rotated 30° from each other. In operation, one of the modes is excited into resonance (drive mode). Rotation about the sensitive axis will produce a Coriolis force which transfers the energy from one of the wineglass modes to the other. The rate of rotation is determined by measuring the amplitude of the 2<sup>nd</sup> wineglass mode (sense mode) induced by the Coriolis force. Because the two wineglass modes have identical frequencies, this kind of gyroscope architecture is also called mode matching operation. However, due to manufacturing and material imperfections, the MRGT fabricated could have a small frequency split between the two wineglass modes. The amount of frequency split can directly affect the gyroscope scale factor, as shown in Eq. (1)

$$\text{Scale factor} = AX_d Q_{eff}$$

$$Q_{eff} = \frac{1}{\sqrt{\left[1 - \left(\frac{\omega_d}{\omega_s}\right)^2\right]^2 + \left(\frac{1}{Q} \frac{\omega_d}{\omega_s}\right)^2}} \quad (1)$$

where A is the geometrical factor, dependent on design,  $X_d$  is the drive amplitude,  $\omega_d$  is the drive mode resonant frequency,  $\omega_s$  is the sense mode resonant frequency. Q is the quality factor. As can be seen from Eq.1, in order to maximize the gyroscope scale factor, the gyroscope will should have large drive amplitude, high mechanical Q and small frequency split. For the gyroscope which is limited by the electronics noise,

increasing the scale factor will directly improve the signal-to-noise ratio (SNR), resulting in lower gyroscope ARW.

In practice, drive amplitude is limited by the device geometry. Having a low frequency split between drive and sense modes is critical to maintain high sensitivity. For example, if Q is 10,000, a frequency split of only 10 Hz will reduce  $Q_{\text{eff}}$  to 1500.

In order to be able to measure the earth rotation, the MRGT will also need to be designed to have low noise. The noise characteristics of the CVG is indeed quite complex, consisting of different noise spectral density at different frequency ranges. However, for the targeted application of azimuth finding for geothermal drilling, with a carouseling time of less than 5 minutes, our previous test data (refer to the Allan Deviation data) on MRGT devices shows the noise of MRGT is dominated by white noise within that target integration time of 5 minutes.

For the gyroscope which is limited by the thermal mechanical noise of the transducer itself, ARW can be calculated as

$$\Omega_n = \frac{1}{k_a X_d} \sqrt{\frac{k_B T}{m Q \omega_d}} \quad (2)$$

Where  $\Omega_n$  is the Angle Random Walk (ARW),  $X_d$  is the modal amplitude,  $k_a$  is angular gain (Bryan factor) which is related to the MRGT geometry and resonance mode,  $k_B$  is the Boltzmann constant, T is the operating temperature, m is the modal mass, Q is the quality factor,  $\omega_d$  is the drive mode resonant frequency.

To achieve  $<1^\circ$  azimuth finding accuray at  $300^\circ\text{C}$  and 5 minutes integration time, the targeted ARW of MRGT is estimated to be  $< 0.03^\circ/\sqrt{\text{hr}}$ . We estimate that such target can be achieved with 0.5um gyroscope drive amplitude and quality factor  $>3500$ .

Figure 4 shows the Q-factor variation for a wafer-level sealed MRGT up to  $600^\circ\text{C}$ . Two high temperature cycles were performed to show the device had no degradation and the device sealing integrity has not been compromised. For reference, the curves of TCQ (thermal coefficient of quality factor) of -0.5 and -3.5 were also shown on the same plot. Literature suggests the TCQ of -0.5 is related to the air damping inside the gyroscope cavity due to imperfect vacuum. TCQ of -3.5 is related to the TED loss (2). Based on Figure 4, the MRGT Q-factor at  $300^\circ\text{C}$  will decrease to be approximately 1/3 of the Q-factor at room temperature. According to (1), the ARW will degrade by 2.4 times when going from room temperature to  $300^\circ\text{C}$ .

Figure 4 Wafer-level packaged MRGT Q-factor characterization over temperature

The accuracy of azimuth finding is directly related to the gyroscope bias instability. We have used two transfer functions for azimuth finding; the first is the ISCWSA error model and the second is a custom transfer function that uses a GE proprietary carouseling algorithm. The results from both algorithms are shown in Figure 5. According to our algorithm study, we need 0.2 °/hr bias instability to support 0.5 degree azimuth uncertainty.

Figure 5 Azimuth uncertainty as a function of the bias instability of the gyroscope

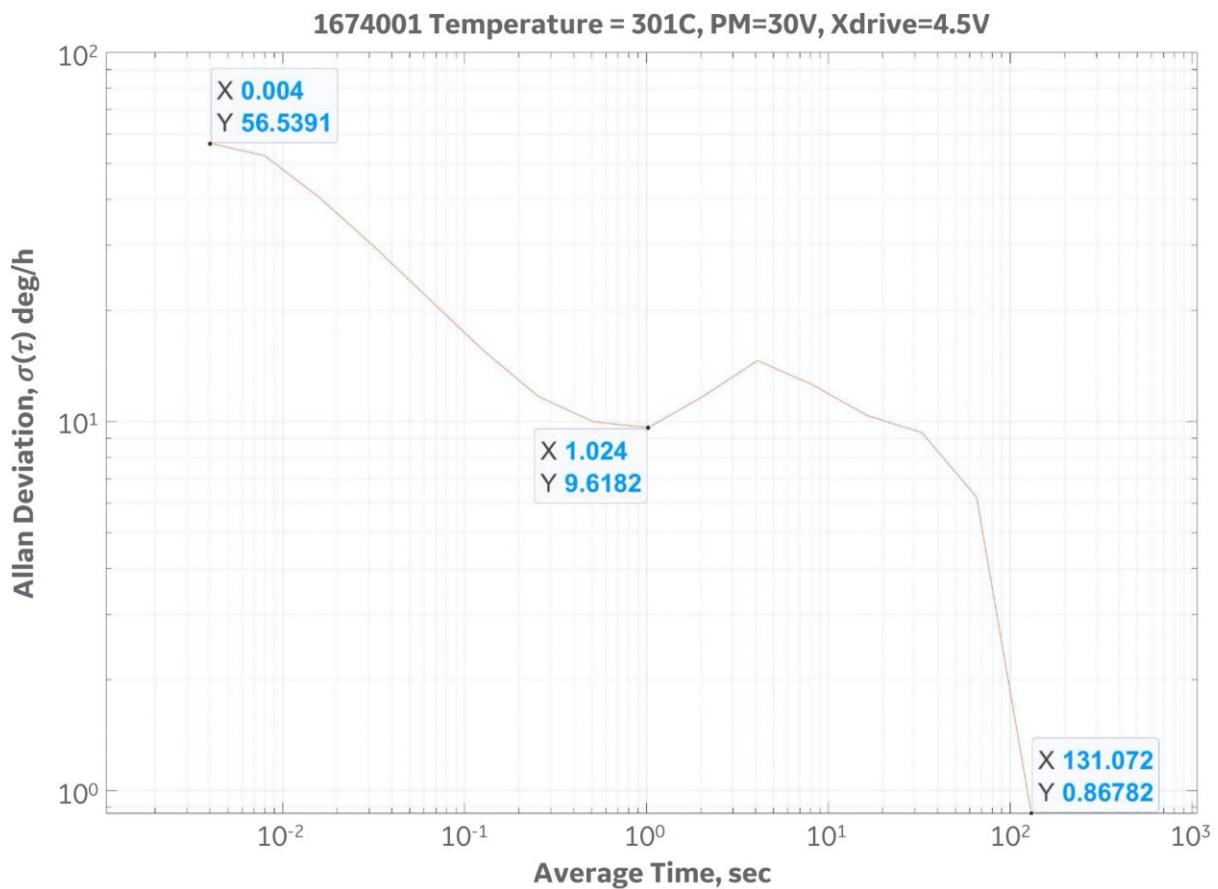

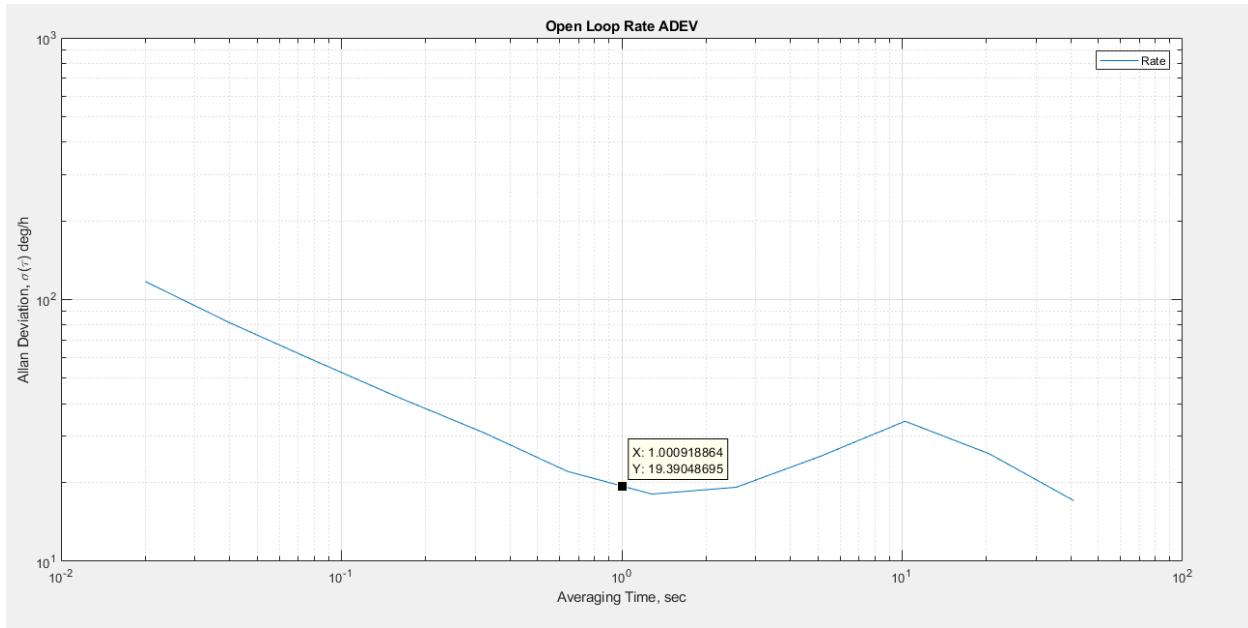

Figure 6 showed the test results of the Allan Deviation of the GE MRGT at room temperature. In Figure 6, the bias instability of a gyroscope can be found as the lowest point while ARW is obtained by typically finding the  $-1/2$  slope line at 1 second point. For practical application, the total azimuth finding operation will need to be finished in less than 5 minutes. Therefore, we require the Allan Deviation of bias at 100 second point support 0.5-degree azimuth uncertainty.

Our test data, as shown in Figure 6, suggested the MRGT is dominated by thermal-mechanical noise (white noise,  $-1/2$  slope in Allan Deviation plot) within the 100 seconds of integration time needed to complete azimuth finding operation. In order to reach  $0.2^\circ/\text{hr}$  at 100 seconds at  $300^\circ\text{C}$  for 0.5-degree azimuth uncertainty, we need to reach  $2^\circ/\text{hr}$  at 1s at  $300^\circ\text{C}$  or  $0.83^\circ/\text{hr}$  at 1s at room temperature (with the expected 2.4x ARW degradation from room temperature to  $300^\circ\text{C}$ ). The MRGT test data suggests the Allan Deviation at 1s at room temperature is within this range.

Figure 6 Allan Deviation of the MRGT at room temperature showing the relationship between ARW,  $-1/2$  slope, bias instability and the 100s integration time for carouseling

### MRGT design parameters

As seen from Eq.1 and Eq.2, the quality factor of the gyroscope directly impacts the gyroscope scale factor and ARW. In order to maximize scale factor and achieve lower

ARW, the quality factor of the gyroscope would prefer to be >3500. Q-factor is related to the damping of the gyroscope resonator. Multiple mechanisms will contribute to the energy loss. Among those, the leading damping loss mechanisms are air damping, thermoelastic damping (TED), anchor loss and surfacing loss. Air damping is a well known energy dissipation mechanism, caused by the collision of air molecules with the resonator. The MRGT is sealed in a vacuum cavity in order to minimize the air damping. TED is due to energy dissipation caused by the thermal transport across the thermal gradient caused by the strain gradient in the resonator. Figure 7 shows the finite element analysis modeling result of the quality factor for the MRGT caused by TED at room temperature ( $Q_{TED} = 22,000$ ).

The total Q-factor of MRGT resonator can be written as

$$\frac{1}{Q_{total}} = \frac{1}{Q_{air}} + \frac{1}{Q_{TED}} + \frac{1}{Q_{others}} \quad (3)$$

The anchor loss and surface loss are complex to model so that a quantitative predictive model is not available. Nonetheless, we can infer the contributions from different damping mechanism by the experimental testing. Experimental data shows the MRGT has a quality factor of 12,000 in a vacuum chamber which is evacuated to pressures less than 10mTorr. Under those conditions, assume  $1/Q_{air} \ll 1/Q_{TED}$ . In this case, the combined anchor loss and other loss mechanisms contribute to slightly less than half of the total energy loss, while TED makes up slightly more than half of the total energy loss ( $Q_{others} = 26,400$ ). When the MRGT was sealed in a LCC84 package, the Q-factor degraded to 7,500. From Eq. (3), the Q-factor caused by air damping (due to the imperfect vacuum inside the LCC84 package) was calculated to be  $Q_{air} = 20,000$ .

Figure 7 Finite element simulation of the MRGT thermoelastic damping.

Temperature will have negative impact to the MRGT quality factor. Reference (3) suggested the different relationship between Q-factor and temperature among the different damping mechanism where

$$Q \propto \frac{1}{T^{0.5}}, \text{ for air damping (TCQ} = -0.5)$$

$$Q \propto \frac{1}{T^{3.5}}, \text{ for thermoelastic damping (TCQ} = -3.5)$$

The literature did not list the temperature coefficient of Quality (TCQ) factor for other mechanisms, but from our test data (shown in Figure 8), we conclude the TCQ for other damping mechanisms should fall within -0.5 and -3.5. Figure 8 shows our measurement of Quality factor in the vacuum station from room temperature to 200°C. For comparison, two separate curves (TCQ=-0.5 and TCQ=-3.5) are also included. The TCQ of our MRGT was measured to be -1.63. We can therefore extrapolate with TCQ of -1.63 to predict the quality factor of 4,000 at 300°C. This meets our design target Q of 3,500 at 300°C.

A more conservative estimation will be to extrapolate from the  $Q_{TED} = 22,000$  at room temperature with the worst case TCQ of -3.5, resulting  $Q_{TED}$  of 2,200 at 300°C. The impact of air damping over temperature can also be extrapolated from  $Q_{air} = 20,000$  at room temperature with TCQ of -0.5, to  $Q_{air} = 14,400$  at 300°C. Therefore, our conclusion is that the TED will be the dominant damping mechanism at 300°C if there are no other outgassing mechanisms induced by the high temperature.

Figure 8 Measurement of Temperature dependence of MRGT quality factor

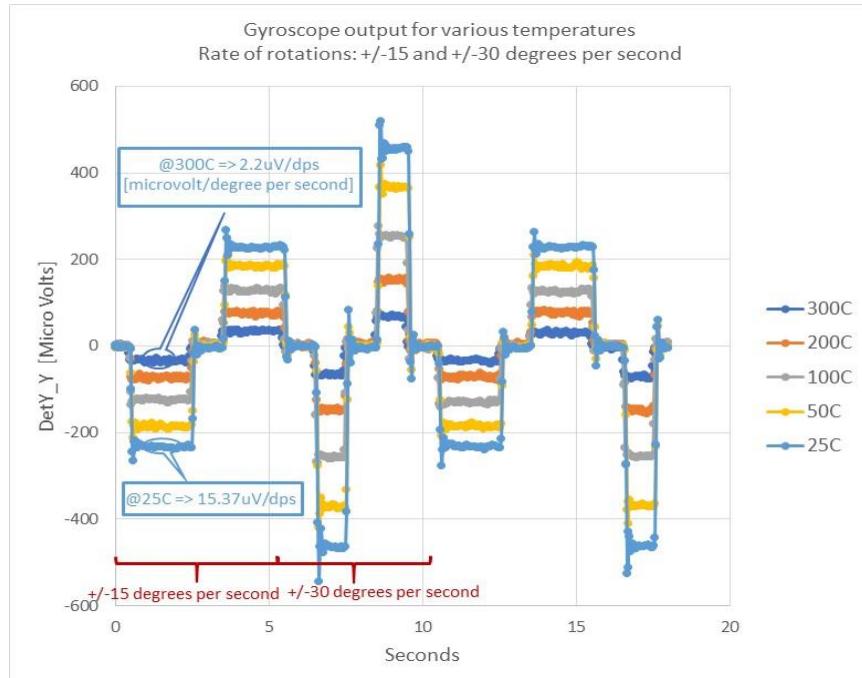

The preliminary temperature test data suggested DetX, which is a measure of the drive amplitude, degraded from 75mV at room temperature to 18mV at 300°C, with excitation voltage kept constant. The device scale factor was degraded from 15.3uV/dps at room temperature to 2.2uV/dps at 300°C.

Comparing the degradation of DetX (approximately 4x) with the Q-factor degradation shown in Figure 8, it can be concluded that the majority of DetX degradation is due to the Q degradation over temperature.

The device scale factor is directly proportional to the drive amplitude and the effective Q-factor as shown in Eq.1. With 4x degradation in drive amplitude and 7x degradation in total scale factor, we inferred that there is a 1.75x degradation in  $Q_{\text{eff}}$ . For comparison, considering an initial Q-factor of 7,500 at room temperature which was degraded to 1880 at 300°C and a frequency split of 3Hz,  $Q_{\text{eff}}$  is calculated to be 4,350 at room temperature and 1,770 at 300°C (approximately 2.5x reduction).

The initial experiments were performed with open drive loop. Once integrated with the ASIC, the device was operated in closed loop to keep the drive amplitude constant further reducing the dependence of scale factor on temperature by more than 2x from room temperature to 300°C.

### MRGT device testing approach

A testing approach was developed to enable multiple levels of screening and characterization of the devices. MRGT device testing was primarily divided into two approaches, wafer level and packaged device level testing.

#### Wafer Level Testing

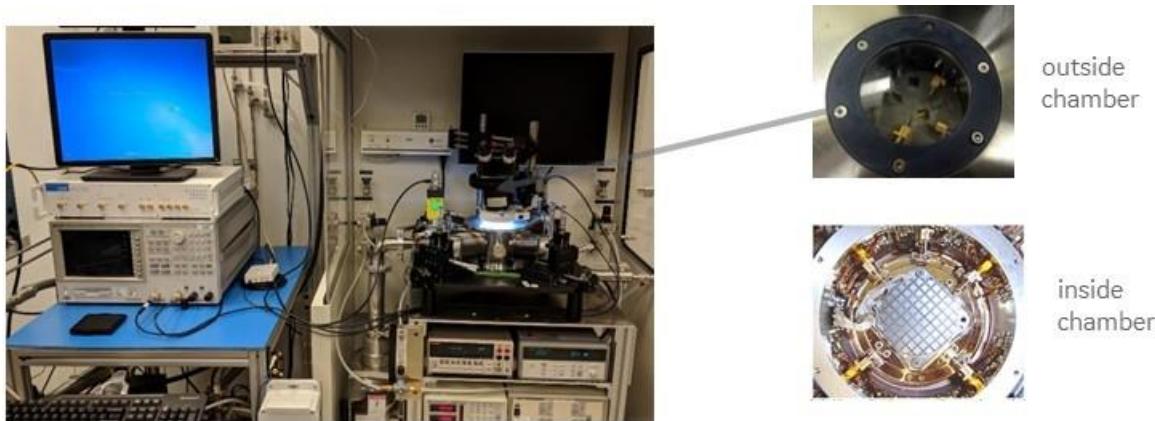

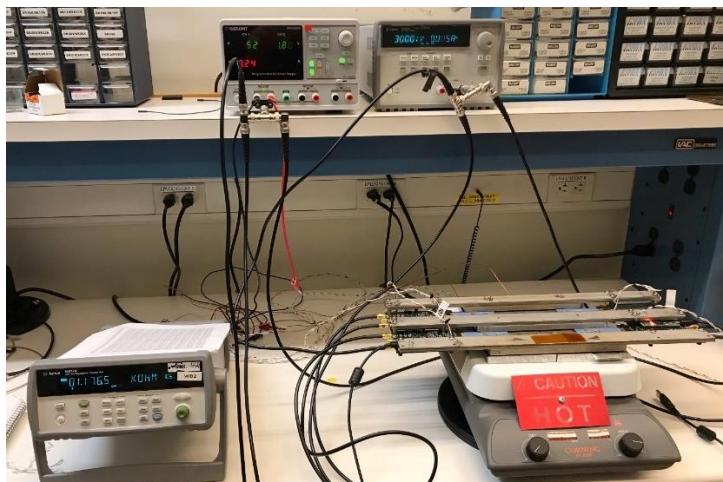

Wafer level testing was conducted on individual MRGT devices prior to packaging. These tests are primarily concerned with screening parts for functionality. The first generation of MRGT devices were uncapped, and therefore required testing in a vacuum probe station. This limited testing to a few devices at a time and changing devices required waiting for the chamber to reach a sufficient vacuum level to enable the measurement. The vacuum probe station is shown in Figure 9.

Figure 9 Vacuum probe station with test instrumentation

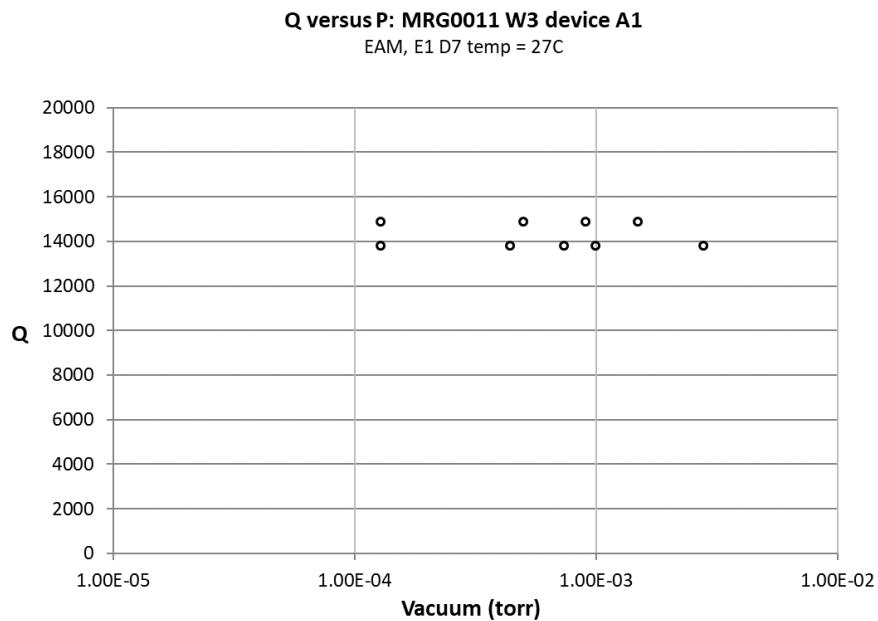

Figure 10 shows the Q-factor measurement results of an unsealed MRG at room temperature. The vacuum level of the vacuum probe station was adjusted from 0.1mTorr to 2.8mTorr while the MRG Q-factor remained constantly at 14,000-15,000. Because the Q-factor did not vary with respect to the vacuum level change, it can be safely assumed that the air damping is not the dominant damping mechanism for MRG at this vacuum level. To explain using (3),  $Q_{air}$  is much higher than  $Q_{TED}$ , so it can be ignored from the  $Q_{total}$  calculation. By using the simulated QTED of 22,000, the  $Q_{others}$ , which includes combined anchor loss and other loss mechanisms, can be estimated to be at 42,400. This verifies the effectiveness the MRG design approach in minimizing the anchor loss.

Figure 10 Q-factor measurement of an unsealed MRG in vacuum chamber

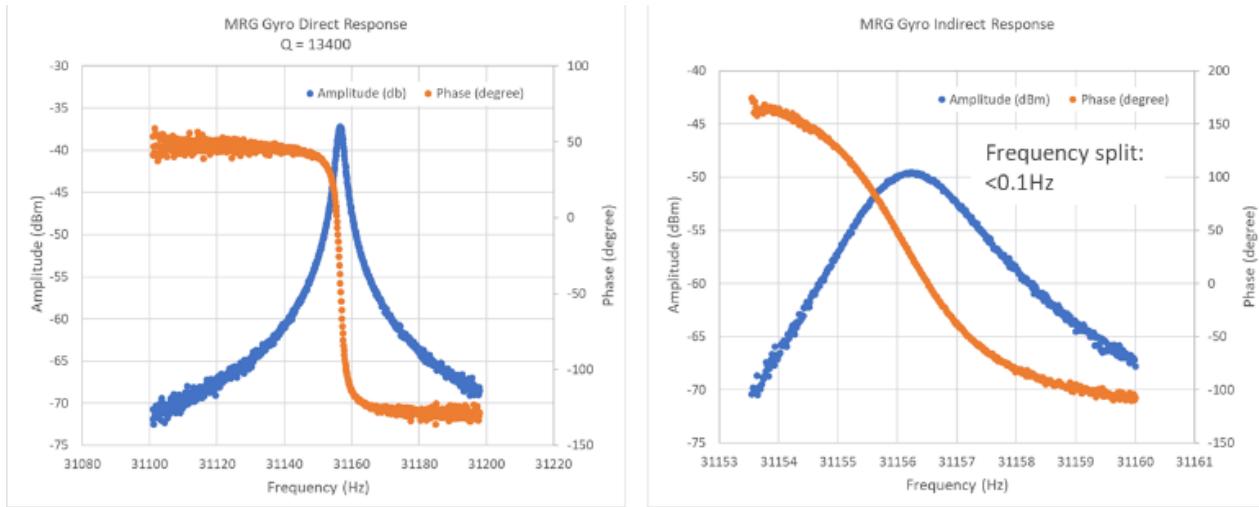

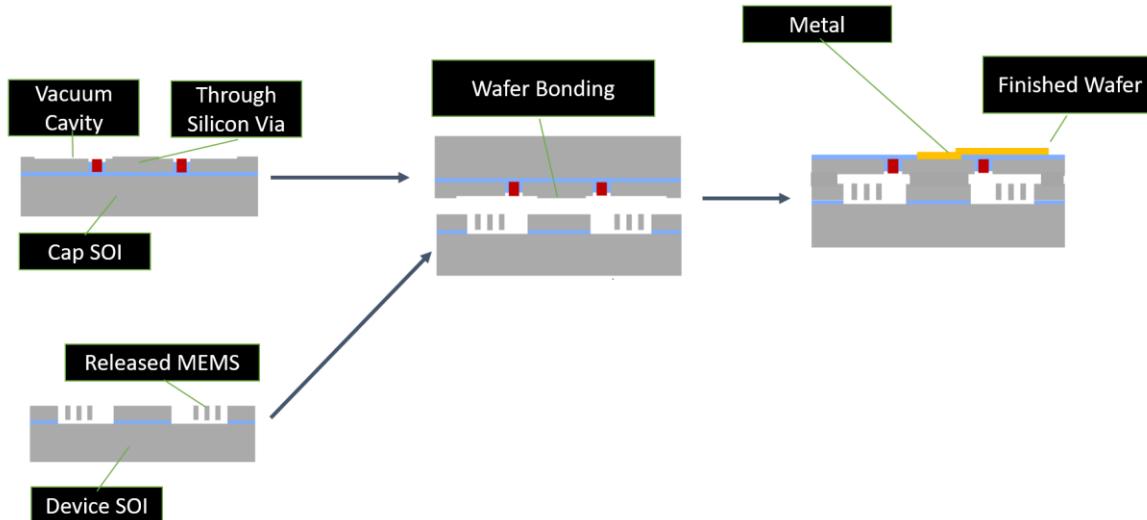

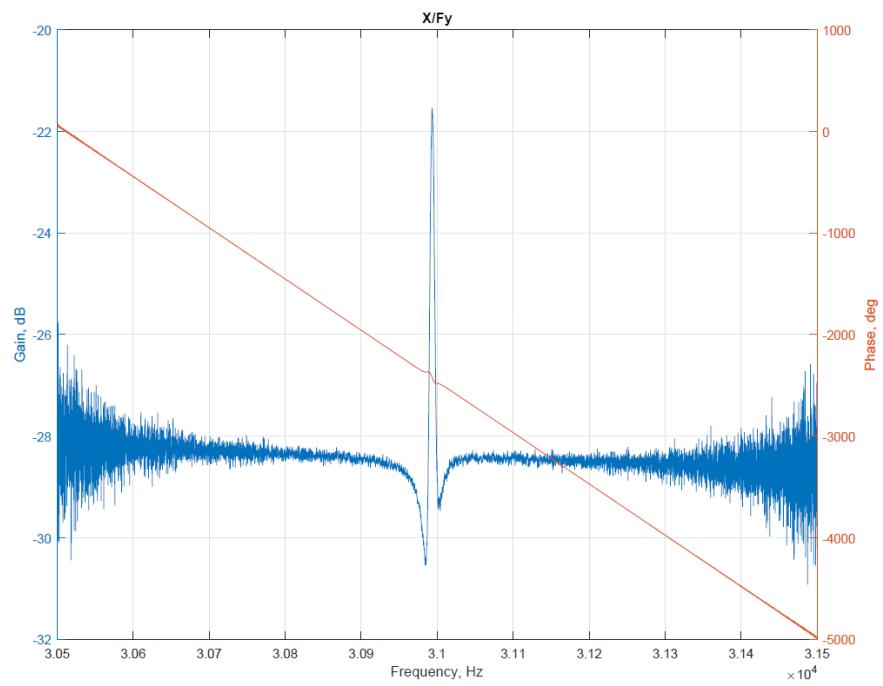

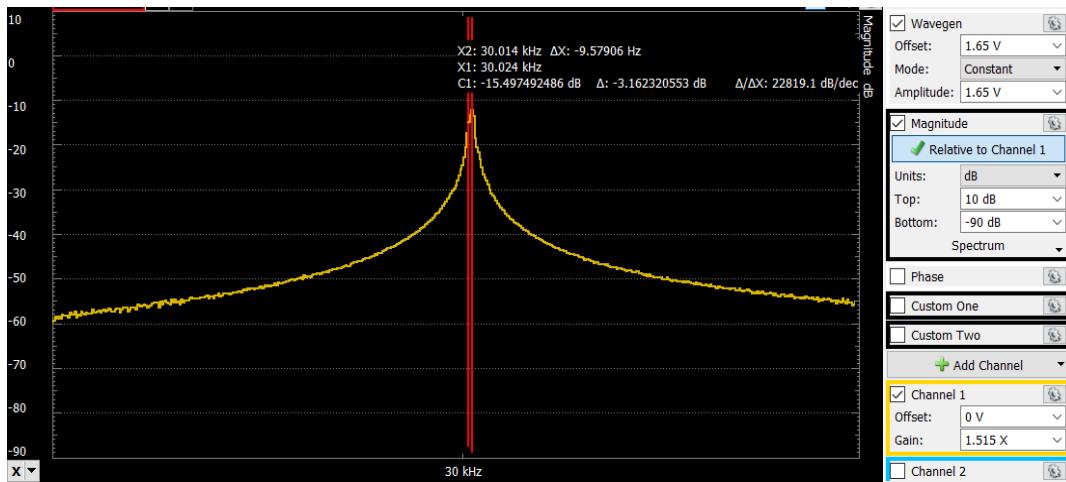

For comparison, a wafer-level sealed MRG was fabricated in the GE-MEMS fabrication process known as the Polaris process. The Polaris process incorporates high aspect ratio, deep etch capability along with wafer level vacuum sealed cavity capability. The wafer-level sealed MRG was characterized with the same electrical testing conditions at room temperature. The results are shown in Figure 11. The direct measurement refers to the method of exciting and measuring from electrodes belonging to the same wineglass mode. The indirect measurement will excite from the electrodes belonging to one wineglass mode and measure from the electrodes belonging to the other wineglass mode. The direct method provides more accurate measurement of resonant frequency and Q-factor while the indirect method provides the measurement of frequency split and cross coupling errors between the two degenerated wineglass modes.

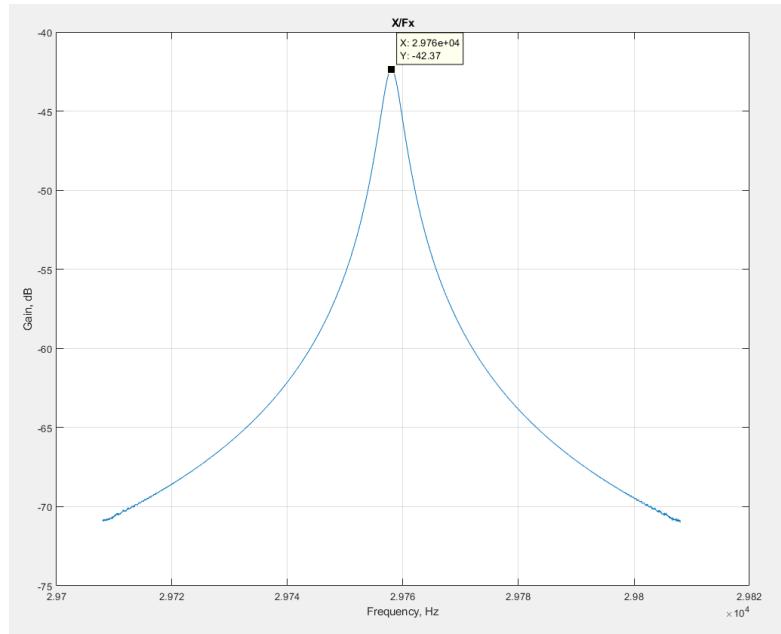

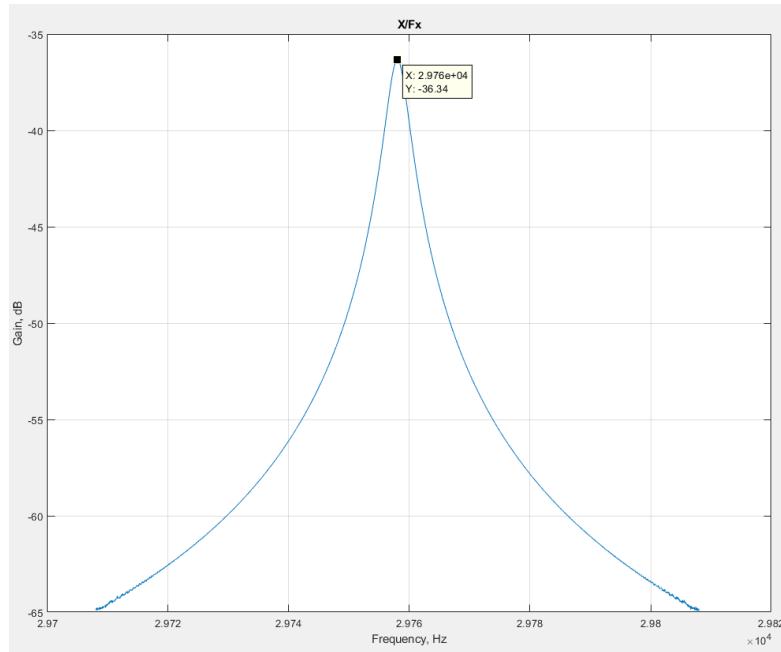

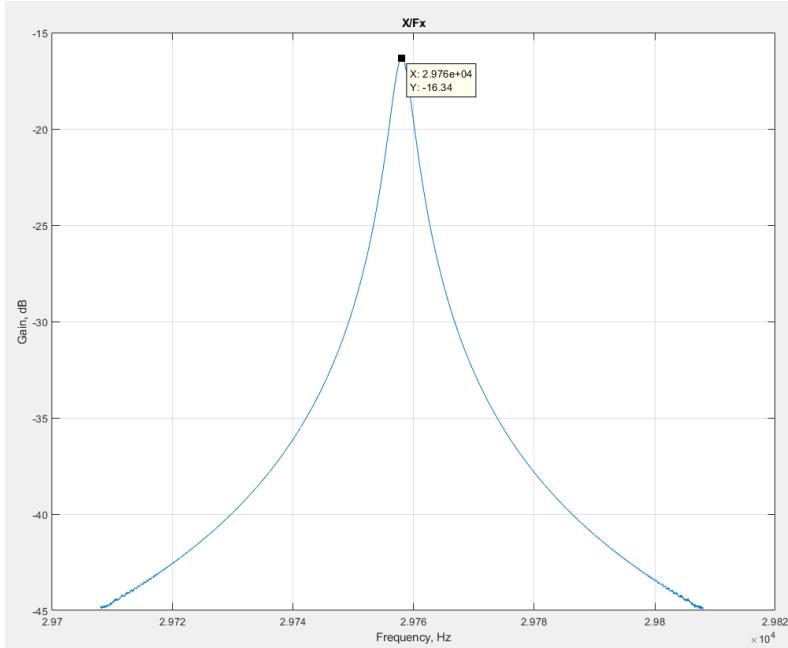

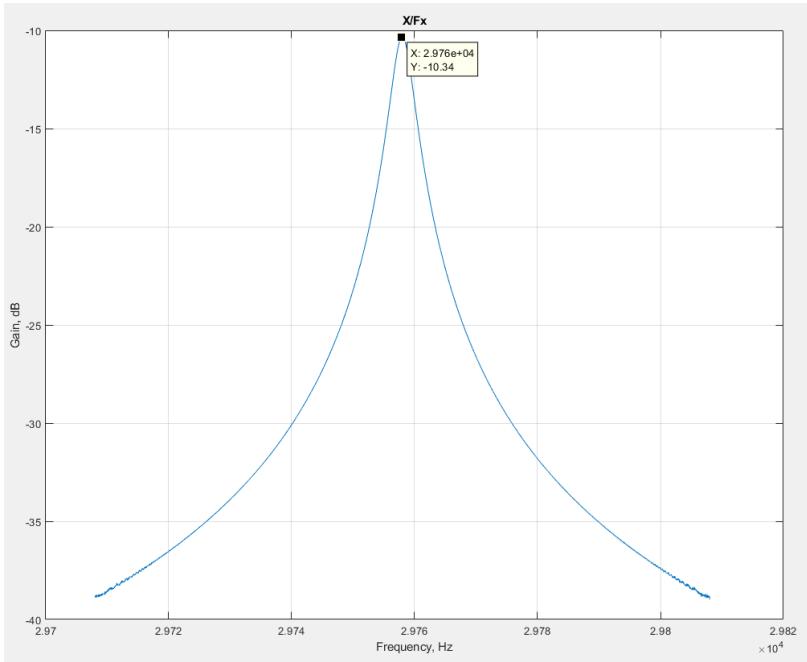

Figure 11 Frequency characterization of an MRG sealed at wafer level

Figure 11 shows the Q-factor the sealed MRG is 13,400, which is in good agreement with vacuum chamber test results. This proves the Polaris' capability in producing good vacuum in the wafer-level sealed cavity, enabling MRG to achieve the highest possible Q-factor. The indirect measurement shows the frequency split between the degenerated wineglass modes is less than 0.1Hz. This proves the capability of Polaris process flow to achieve high quality silicon etching with high symmetry and low anisoelastic coupling.

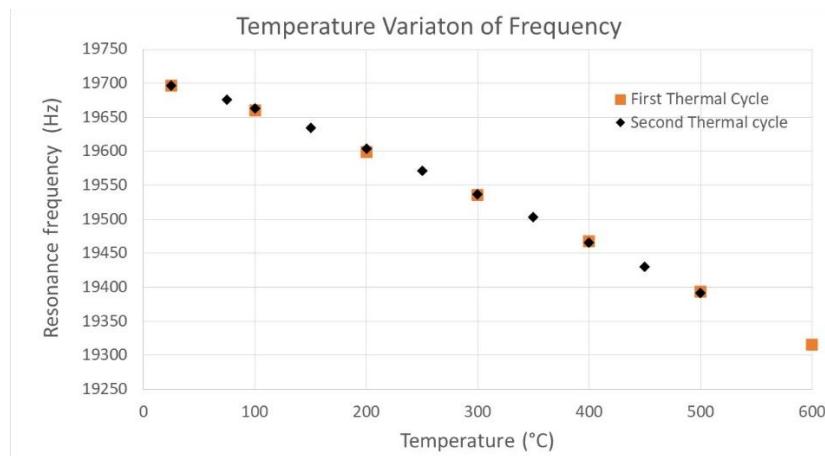

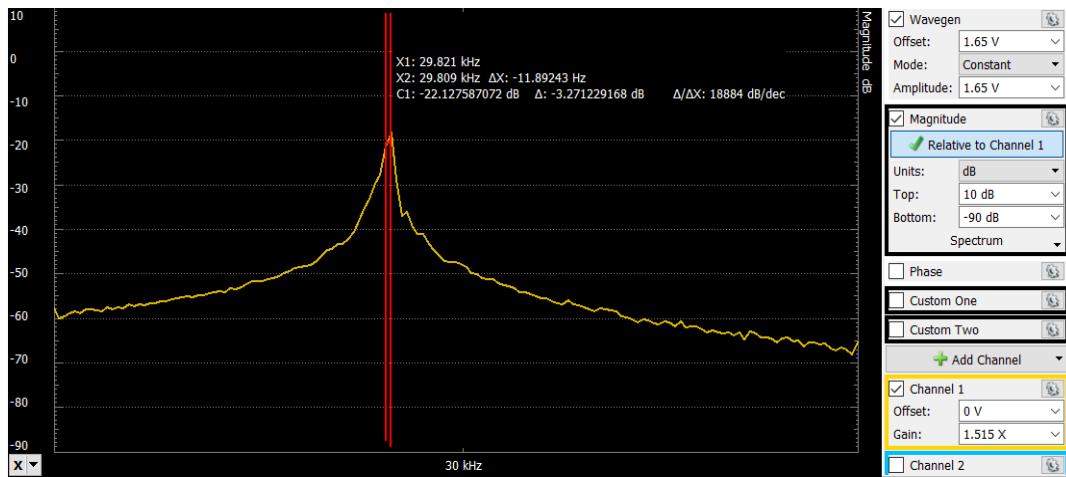

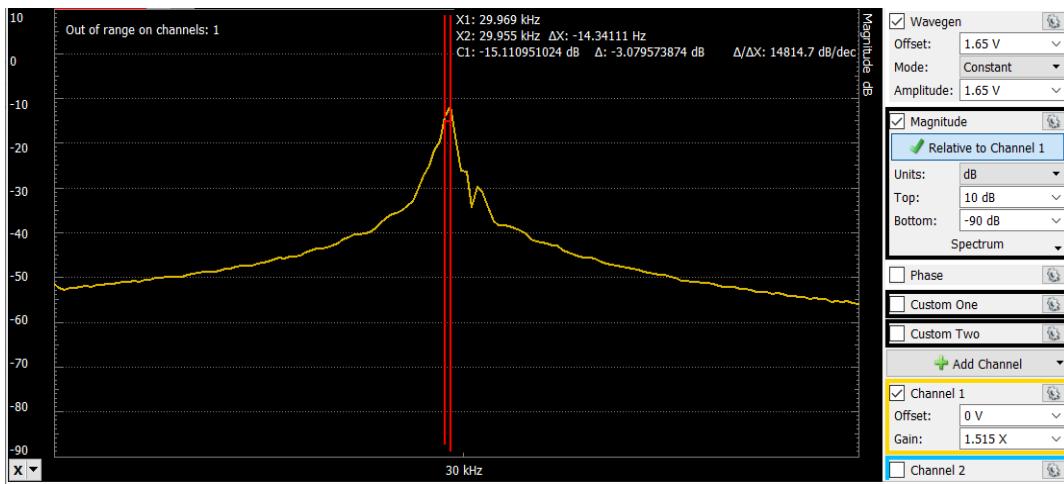

The sealed MRG is further characterized to 600°C to check the device integrity and understand how the MRG dynamic response might change at extremely high temperature. Figure 12 shows the change of MRG frequency over the temperature, measured by the 2<sup>nd</sup> wineglass mode. As expected, the frequency decreases with temperature due to the negative temperature coefficient of the silicon Young's modulus. The temperature coefficient of frequency (TCF) is measured to be ranging from -25 to -34 ppm/°C from room temperature to 600°C. Reference (2) reported similar TCFs of -27 ppm/°C and -33 ppm/°C based on the characterization of a silicon resonator from -10°C to 80°C. The MRG test results suggest there is no drastic change or degradation in the silicon resonator up to 600°C, which opens up potential for MEMS devices to be used in extreme temperatures such as hypersonic flight and turbine engine hot gas path. Furthermore, the trend of increasing TCF with temperature is also observed, which means the temperature compensation technique used for high temperature will need to consider high order nonlinear terms.

Figure 12 Sealed MRG frequency characterization over temperature

As noted previously, temperature will have negative impact to the MRG quality factor. Reference (3) suggested the different relationship between Q-factor and temperature for some damping mechanisms but it is noted that it only covered a limited temperature range up to 80°C. In our work, the MRGs were tested to a much higher temperature range. Figure 4 shows the Q-factor variation for a wafer-level sealed MRG up to 600°C. Two high temperature cycles were performed to show the device had no degradation and the device sealing integrity has not been compromised. For reference, the curves of TCQ of -0.5 and -3.5 were also shown on the same plot. It can be seen the MRG Q-factor follows the TCQ= -3.5 curve more closely. This confirms our previous conclusion that TED is likely the dominant damping mechanisms for the MRG. It also reaffirms our belief that for TED is a crucial design consideration for high temperature gyroscope because  $Q_{TED}$  tends to degrade very quickly over temperature. It is also observed the MRG TCQ curve tends to not degrade as rapidly when temperature increases. For example, MRG TCQ of MRG is -2.66 from room temperature to 200°C while the TCQ is -1.29 from 200°C to 600°C. Whether or not this indicates a new physical phenomenon for damping at higher temperature remains as an interesting topic for future study.

During the project execution, the WLP process was developed that enabled testing unpackaged devices outside of a vacuum probe station. This enabled testing of full wafers for functionality and produce wafer maps of device characteristics variation across the wafer as can be seen in Figure 21 and Figure 22 in the *Fabrication Process Capability Advancement* section. The WLP process is discussed in more detail in the fabrication section of the report.

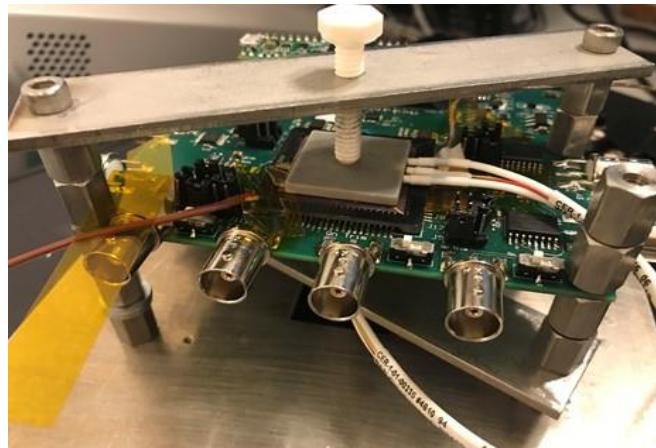

### Packaged device test and characterization

Much of the device characterization in the project's first budget period was conducted using a high temperature capable package, die attach and wirebonding in commercially available high temperature ceramic packages. Conventional temperature circuit boards with sockets are utilized for testing. Parts can be swapped into the test board socket and therefore enables more easily testing multiple devices. Testing over temperature was accomplished by locally heating the device package while maintaining the rest of the test board at lower operating temperatures. Figure 13 shows the characterization test approach, the MRGT was packaged in a high temperature capable ceramic LCC package with high temperature die attach and interconnect. The part was inserted in a socket to facilitate testing of multiple parts. The test board contains the electronic circuitry designed as part of the Budget Period 1 effort and utilized in characterization of the overall system performance. This approach also enabled validation of the electronics approach and capabilities.

The test board and heater assembly were designed to be compatible with attaching to the rate table to enable gyroscope scale factor characterization.

Figure 13 Test and characterization packaging approach

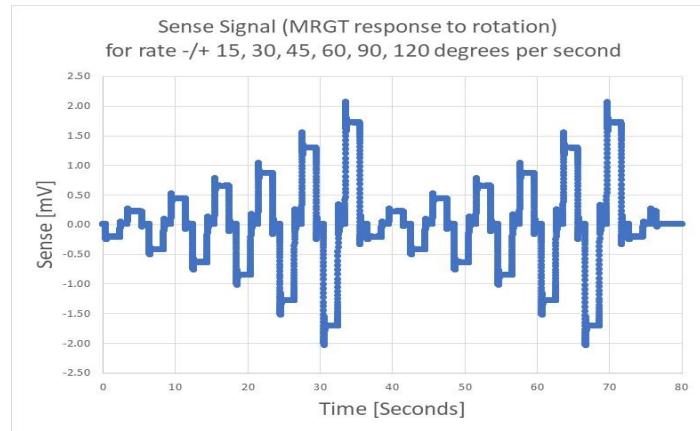

Figure 14 shows the MRGT rotation rate response characterization utilizing the test board and the rate table. As expected, the response is proportional to the rotation rate.

Figure 14 Response to rotation rate

The characterization approach enables testing critical performance metrics across temperature. Figure 15 shows response characterization test results at multiple temperature points from room temperature to 300°C

Figure 15 Rotation rate response from room temperature to 300°C

### MRGT device characteristics over temperature

Testing conducted during the device design tasks aimed to further validate the device design parameters and temperature dependence. Initial testing was conducted with

DE-EE0008604: A MEMS Gyroscope for Reliable Long Duration Measurement While Drilling at 300°C

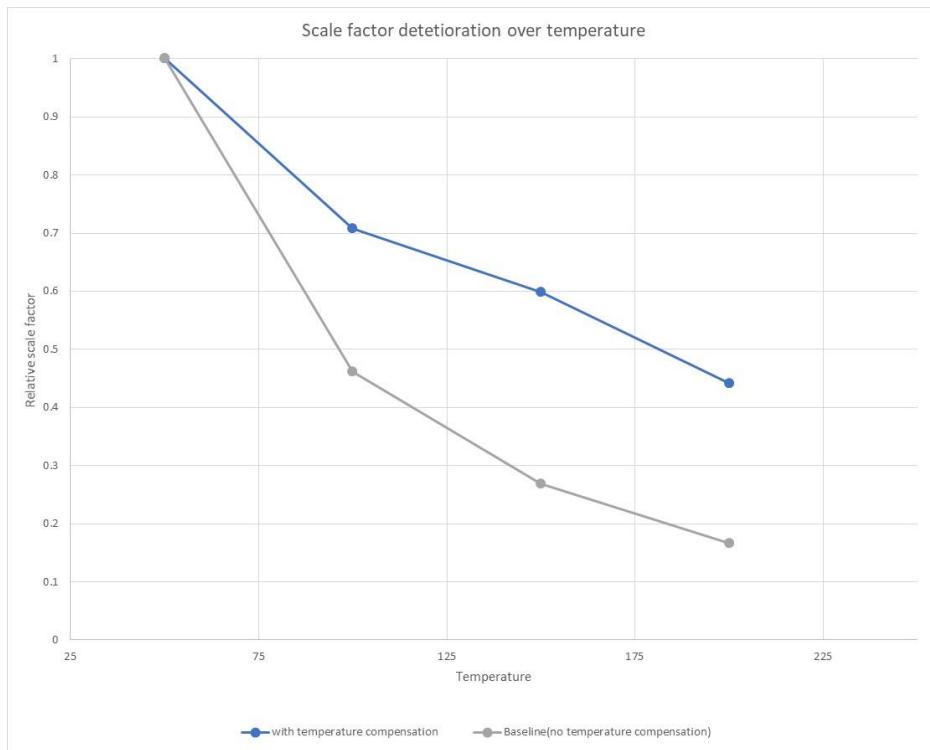

fixed excitation voltage. The MRGT exhibited 6x scale factor deterioration between room temperature and 200°C due to the loss of mechanical drive amplitude resulting from the reduced device quality factor.

A first iteration of a temperature compensation algorithm was devised in which the drive voltage is controlled over temperature to provide a constant mechanical drive amplitude. With the compensation algorithm implemented, the scale factor loss was reduced to approximately 2.25x. Figure 16 shows significant reduction in scale factor deterioration over temperature with temperature compensation implemented.

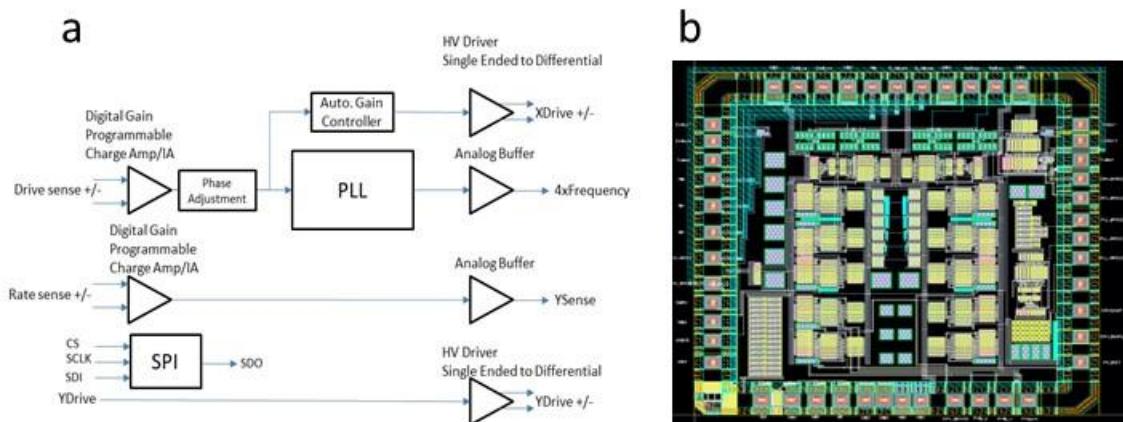

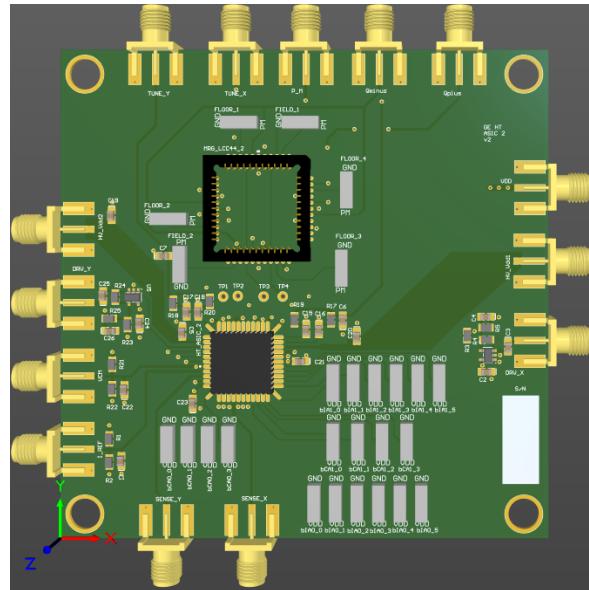

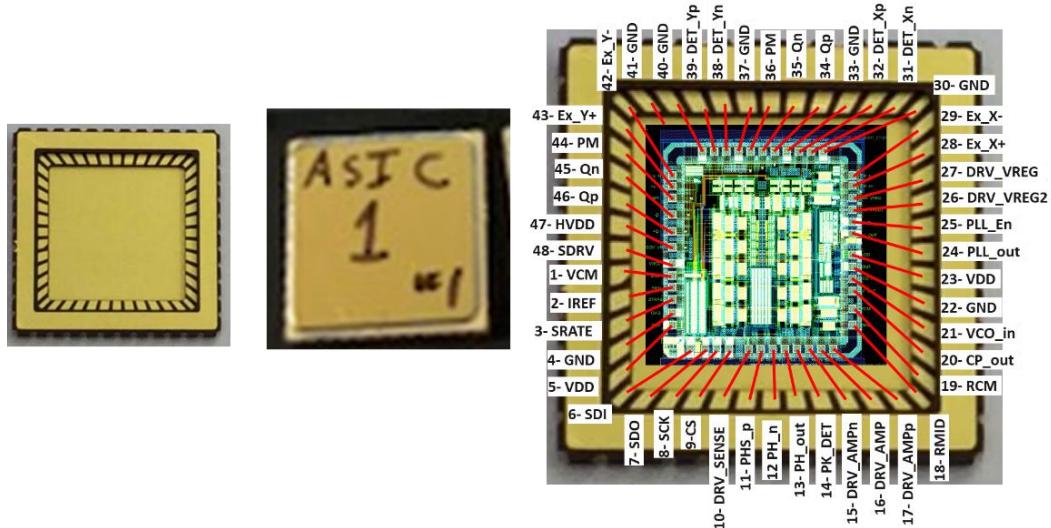

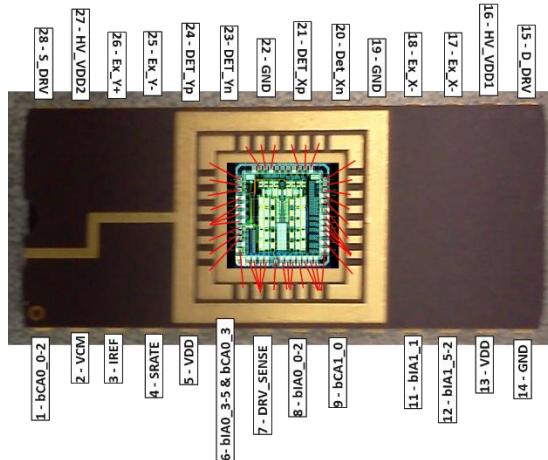

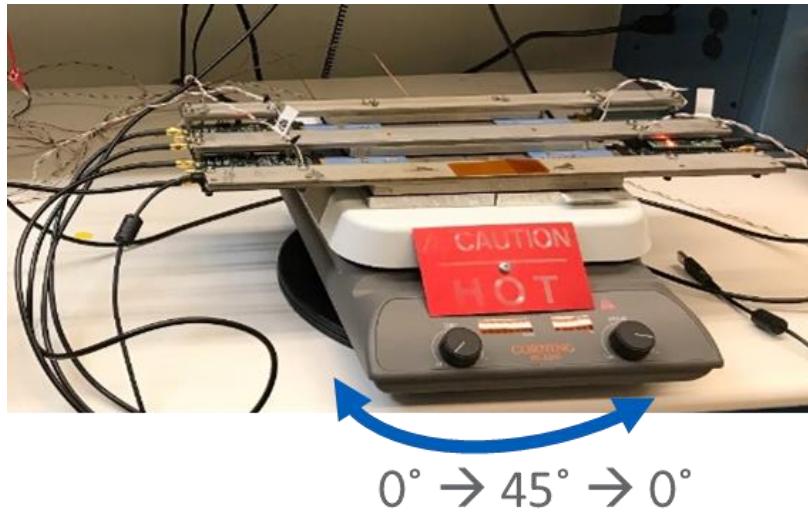

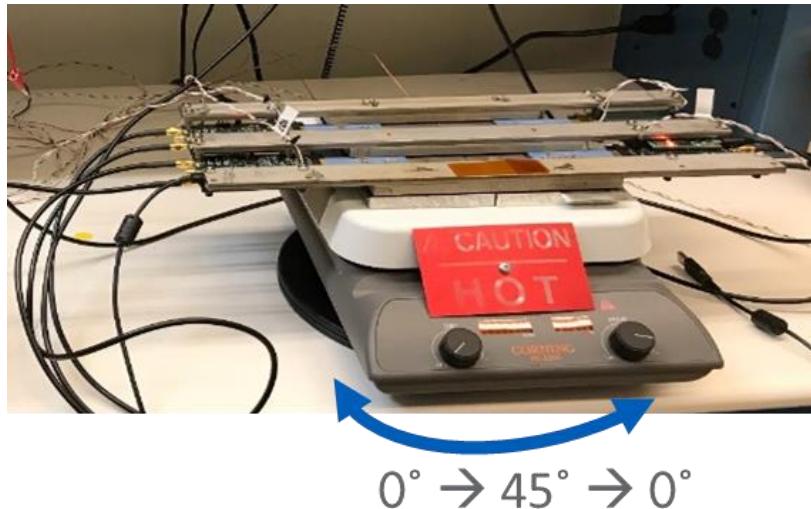

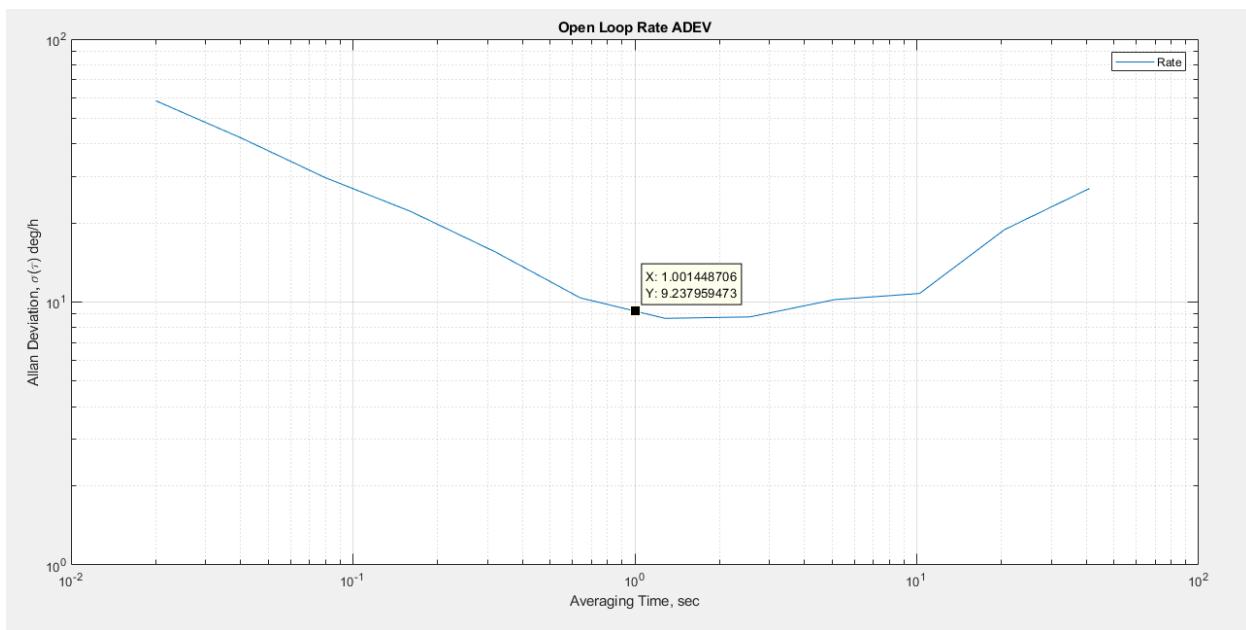

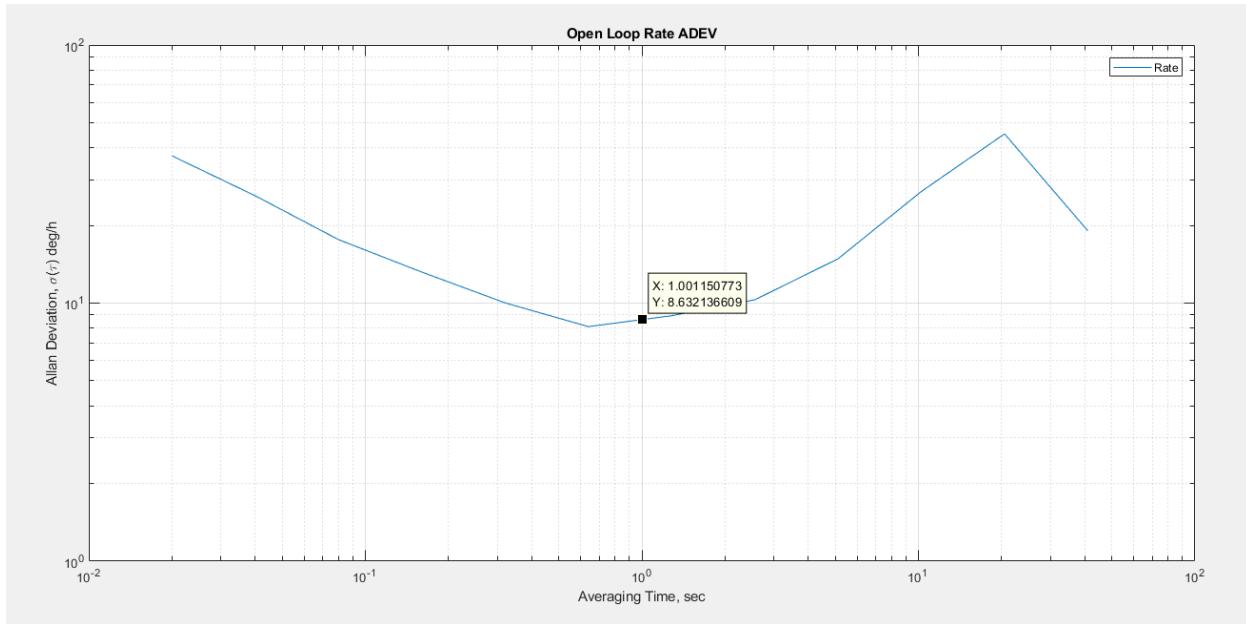

Figure 16 Scale factor deteriorating over temperature with and without temperature compensation