# Optimized Materials and Structural Designs for Stretchable Silicon Integrated Circuits

By *Dae-Hyeong Kim, Zhuangjian Liu, Yun-Soung Kim, Jian Wu, Jizhou Song, Hoon-Sik Kim, Yonggang Huang*<sup>\*</sup>, *Keh-chih Hwang, Yongwei Zhang and John A. Rogers*<sup>\*</sup>

[\*] Corresponding authors: Prof. J.A. Rogers

Department of Materials Science and Engineering, Chemistry, Mechanical Science and Engineering, Electrical and Computer Engineering

Beckman Institute for Advanced Science and Technology, and Frederick Seitz Materials Research Laboratory

University of Illinois at Urbana-Champaign

Urbana, Illinois 61801 (USA)

E-mail: [jrogers@uiuc.edu](mailto:jrogers@uiuc.edu)

Prof. Y. Huang

Departments of Civil and Environmental Engineering and Mechanical Engineering,

Northwestern University, Evanston, IL 60208 USA

E-mail: [y-huang@northwestern.edu](mailto:y-huang@northwestern.edu)

D.-H. Kim, Y.-S. Kim, H.-S. Kim

Department of Materials Science and Engineering, Beckman Institute for Advanced Science and Technology, and Frederick Seitz Materials Research Laboratory

University of Illinois at Urbana-Champaign

Urbana, Illinois 61801 USA

Z.J. Liu, Y.W.Zhang

Institute of High Performance Computing, 1 Fusionopolis Way, #16-16 Connexis, 138632,

Singapore

Y.W.Zhang

Department of Materials Science and Engineering, National University of Singapore,

Singapore 119260

Jian Wu

Departments of Civil and Environmental Engineering and Mechanical Engineering,

Northwestern University, Evanston, IL 60208 USA

J. Song

Department of Mechanical and Aerospace Engineering, University of Miami, Coral Gables,

FL 33146 USA

Prof. K.-C. Hwang

Department of Engineering Mechanics, Tsinghua University, Beijing 100084, China

Keywords: Flexible Electronics, Stretchable Electronics, Semiconductor Nanomaterials,

Nanomechanics

## **Abstract**

This paper presents materials and design strategies for stretchable silicon integrated circuits that use non-coplanar mesh layouts and elastomeric substrates. Detailed experimental and theoretical studies reveal many of the key underlying aspects of these systems. The results indicate, as an example, optimized mechanics and materials for circuits that exhibit maximum principal strains less than 0.2% even for applied strains of up to ~90%. Simple circuits, including CMOS inverters and NMOS differential amplifiers, provide examples that validate these designs. The results suggest practical routes to high performance electronics with linear elastic responses to large strain deformations, suitable for diverse applications that are not readily addressed with conventional wafer-based technologies.

## 1. Introduction

Electronic circuits that offer the performance of conventional wafer-based devices but with the mechanical properties of a rubber band have the potential to open up many new application possibilities, most prominently those that involve intimate integration of electronics with the human body<sup>[1]</sup> for health monitoring or therapeutic purposes. Several schemes have been demonstrated to achieve stretchable circuits, as defined by reversible, elastic mechanical responses to large (>>1%) compressive or tensile strains<sup>[2-11]</sup>. Those that exploit single crystalline semiconductor nanomaterials, in the form of nanoribbons or nanomembranes, are attractive due to the excellent electrical properties that can be achieved. The most advanced strategies use single crystal silicon for the active materials of ultrathin devices (e.g. transistors) that are interconnected (mechanically and/or electrically) with non-coplanar bridges, to provide stretchability up to ~100%, in a manner that maintains small material strains for linear, reversible response and good fatigue properties<sup>[11]</sup>. In the present paper, we study theoretically and experimentally many of the key design variables, including aspects of bridge design and encapsulation. The results reveal important features of the underlying materials and micro/nanomechanics and provide design rules for this class of stretchable electronics technology.

## 2. Results and Discussion

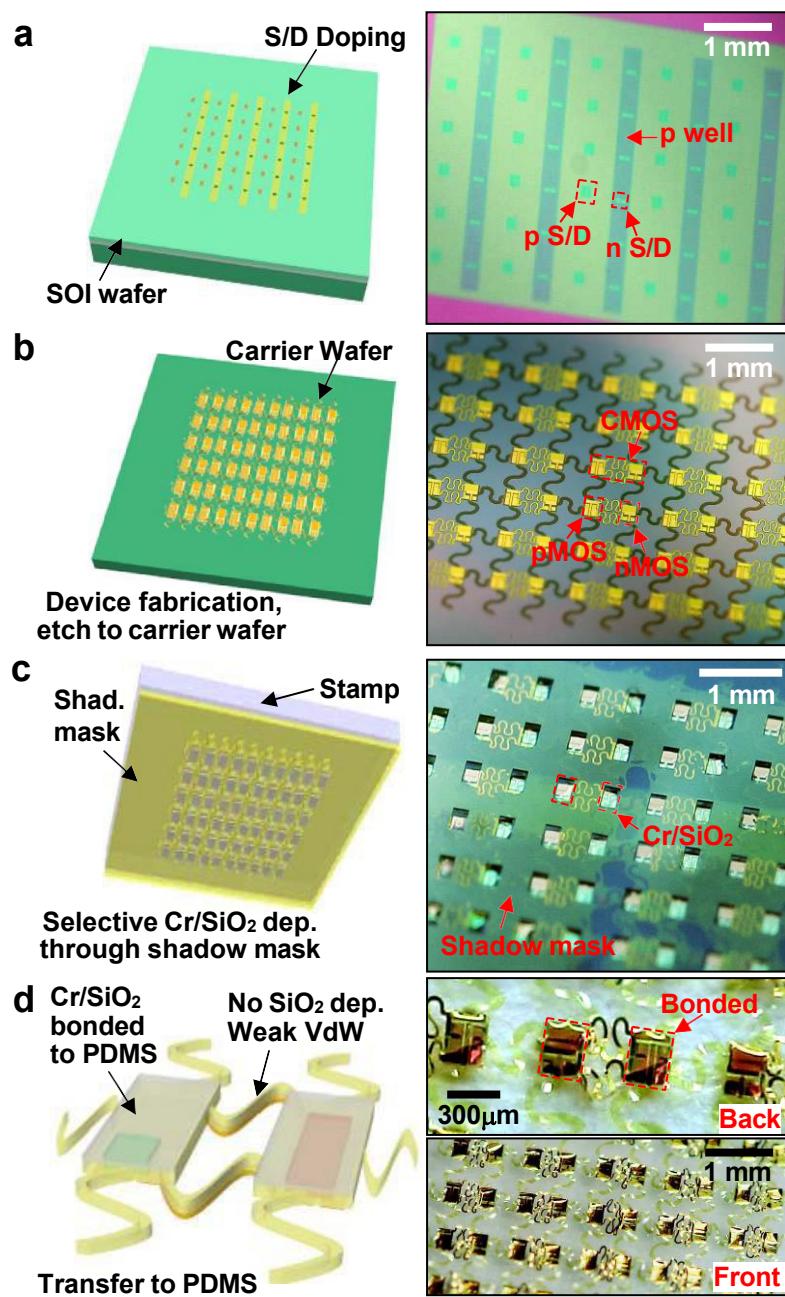

The process for fabricating stretchable silicon circuits is similar to that of recent reports<sup>[8, 11]</sup>. **Figure 1** provides an overview for systems that use non-coplanar serpentine bridge structures. The sequence begins with high temperature doping processes, starting with an n-type silicon on insulator wafer (260nm top silicon, 1μm buried oxide; SOITEC, France), as shown in Fig. 1(a). Doped silicon nanomembranes prepared in this manner are transfer

printed onto a carrier wafer coated with poly(methylmethacrylate)/polyimide (PMMA/PI, 100nm/1.2 $\mu$ m, MicroChem/Sigma Aldrich, USA) and then processed to yield ultrathin circuits (Fig. 1(b)). Details appear in the experimental section. Another transfer printing step lifts the ultrathin circuits from the carrier wafer to expose their back surfaces for selective area deposition of Cr/SiO<sub>2</sub> (3nm/30nm) through an aligned shadow mask (Fig. 1(c)), and then delivers them to a biaxially pre-strained piece of polydimethylsiloxane (PDMS, Dow Corning, USA) bearing –OH groups on its surface. Strong covalent bonding forms between the PDMS and the SiO<sub>2</sub> on the circuits upon contact and mild heating (Fig. 1(d)). This bonding, together with the comparatively weak Van der Waals adhesion between the PDMS and other regions of the circuits, leads to a controlled non-coplanar layout in which the bridge structures lift out of contact with the PDMS upon release of the pre-strain (Fig. 1(d)).

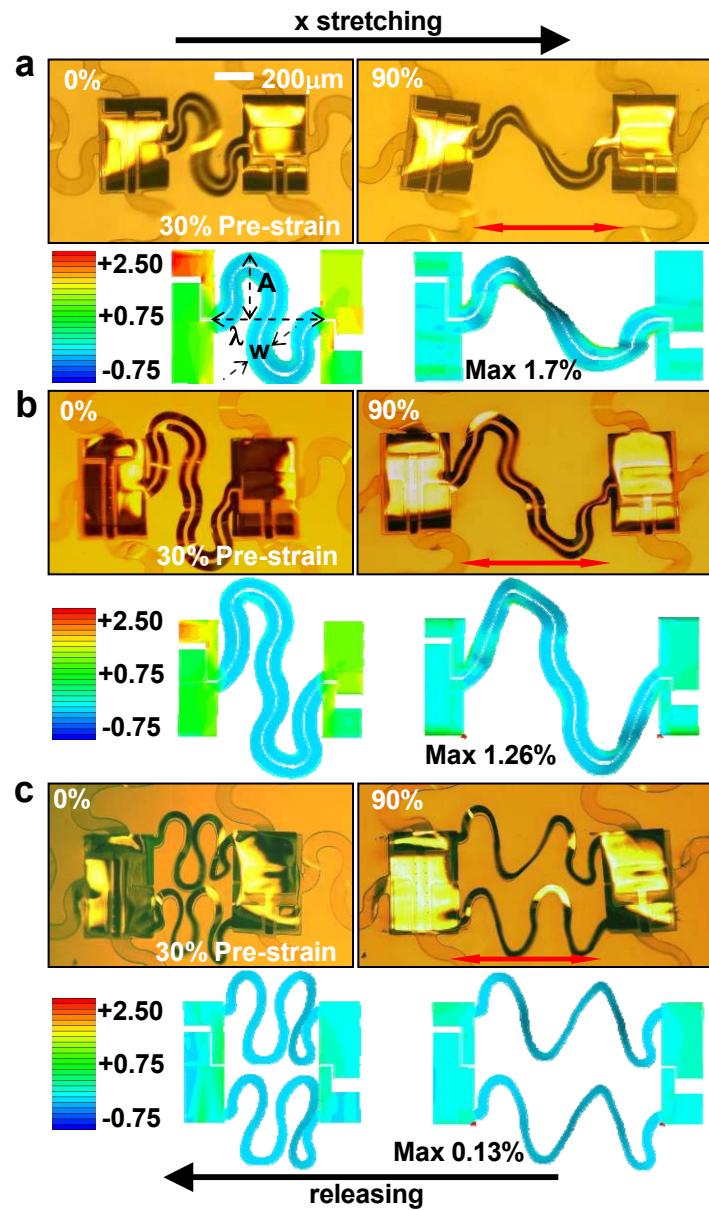

Systematic study of this system began with investigations of the dependence of the mechanics on the bridge design, as shown in Fig 2. Figure 2(a) shows a standard serpentine structure of low amplitude (A) to wavelength ( $\lambda$ ) ratio and wide width (w), formed with a pre-strain value of ~30%. For an applied strain of ~90%, the bridge changes shape, to first reach its original layout when the applied strain equals the pre-strain, followed by further deformation at higher strains, without fracture. This ability to accommodate strains larger than the pre-strain is absent from straight bridge designs explored previously<sup>[10, 11]</sup>. Nevertheless, the serpentine layout of Fig. 2a exhibits stress concentrations near the corners of the points of highest curvature, suggesting the possibility for mechanical failure in these regions. Full three dimensional finite element modeling (FEM) analysis (bottom frames in Fig 2(a)), indicates maximum principal strain of ~1.7% for applied strain of ~90%. A different design, shown in Fig. 2(b), which increases the ratio of the amplitude (A) to wavelength ( $\lambda$ ) of the serpentine structure, reduces the maximum principal strain to 1.26% under the same applied strain. Extending this strategy by decreasing the width (w) of the lines

and increasing the number of ‘coils’ in the serpentines while maintaining the ratio of the amplitude (A) to wavelength ( $\lambda$ ) (Fig. 2(c)) dramatically reduces the maximum principal strain to 0.13% for the same conditions. This simple sequence of structural modifications illustrates the extent to which design influences the micromechanics.

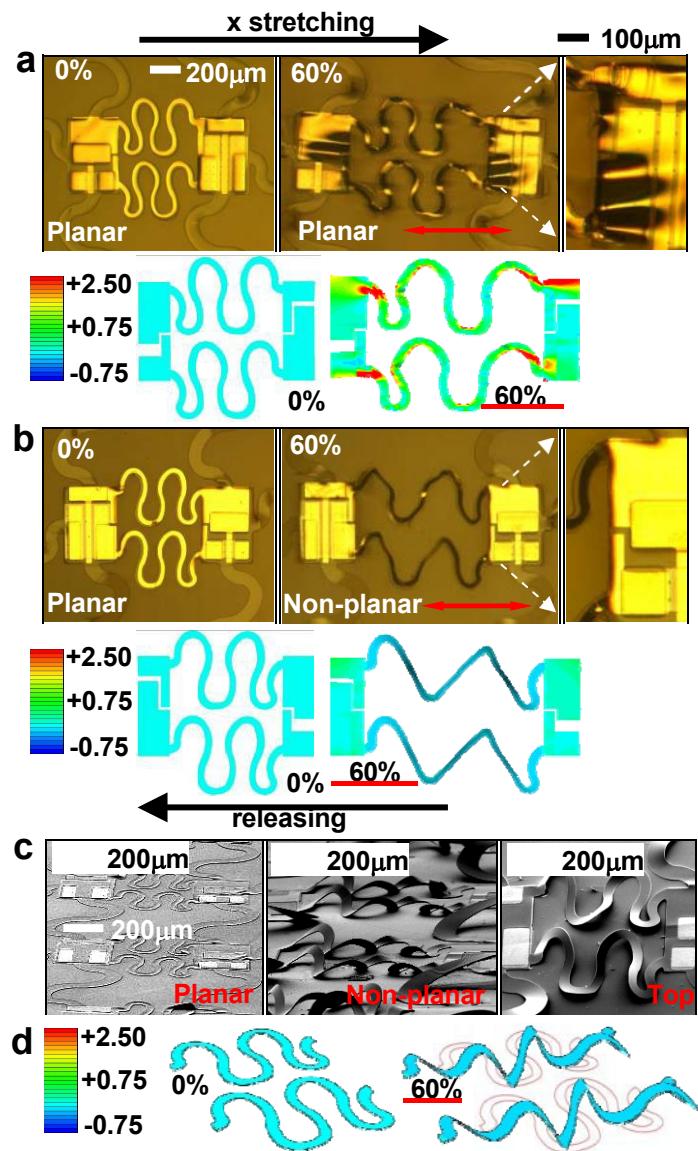

Another critically important feature of systems of this type is the non-coplanar layout of the serpentines. To reveal the effects, Fig. 3 compares coplanar (formed with the Cr/SiO<sub>2</sub> adhesion layer deposited uniformly on the backsides of the circuits, to bond the serpentines, as well as the islands, to the PDMS) and non-coplanar systems with the bridge design of Fig 2(c). For simplicity of comparison, the pre-strain was zero for both cases, leading to identical strain distributions for the unstrained cases shown in the left frames of Fig. 3(a) and (b). With an applied tensile strain of ~60%, the bridges in the coplanar case remain largely flat due to their adhesion to the PDMS substrate. By contrast, the bridges of the non-coplanar case delaminate from the PDMS and move out of the plane to accommodate more effectively the applied strain. Figure 3(c) shows this behavior in scanning electron microscope (SEM) images. The left frame (60° tilted) corresponds to the system without applied strain; the center (60° tilted) and right (top view) frames are for strains of 60%. In the case of coplanar bridges, the constrained motion leads to much higher peak strains in the circuits compared to the non-coplanar design. As a result, cracks and wrinkles appear inside the active device regions, unlike the non-coplanar system, as shown in the center and right images of Fig. 3(a) and (b). The strain distributions and maximum principal strains calculated by FEM analysis confirm these experimental observations (bottom frames of Fig 3(a) and (b)). The maximum principal strains under applied strains of ~60% for coplanar and non-coplanar structures are 6.8% and 0.177%, respectively. Figure 3(d) shows tilted views of the FEM simulation results for the non-coplanar structure before and after applying strain.

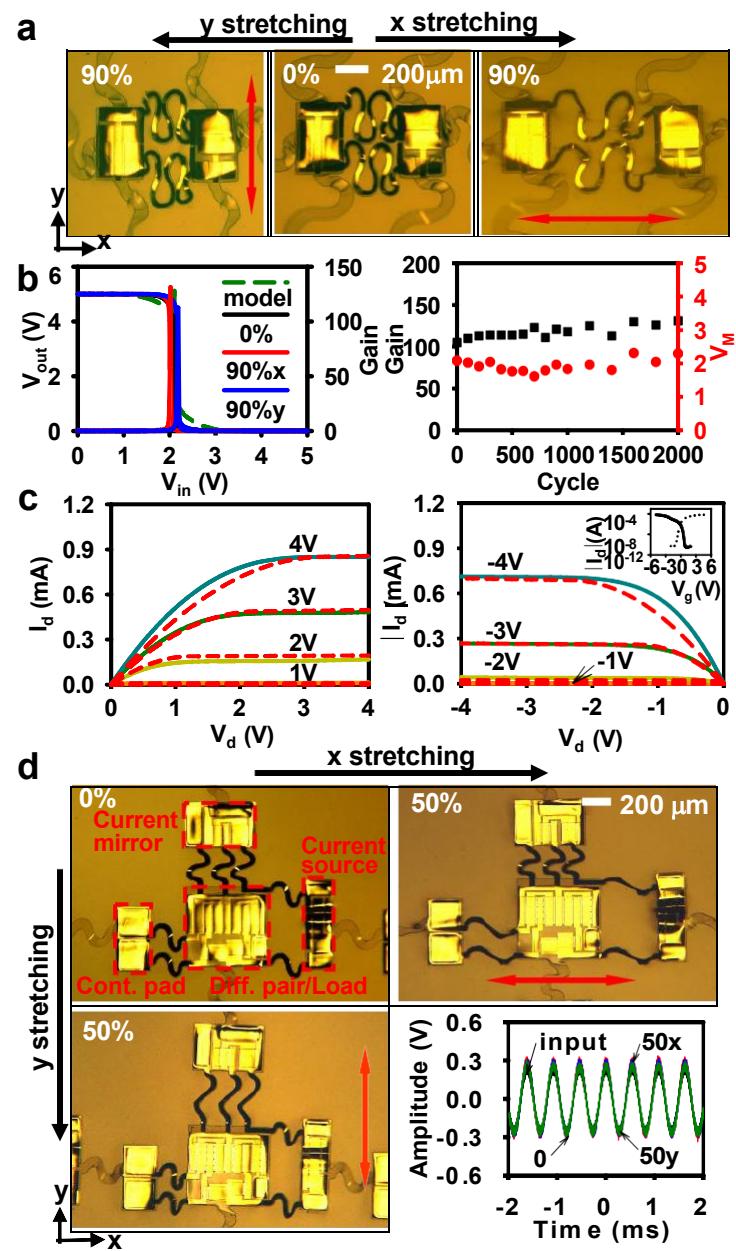

To illustrate the value of these simple, optimized designs, we built CMOS inverters and NMOS differential amplifiers. The inverters exhibited gains as high as  $\sim 130$ , consistent with PSPICE simulation based on separate measurements of individual transistors (Fig 4(b), left) that showed mobilities of  $\sim 400 \text{ cm}^2/\text{Vs}$  and  $\sim 160 \text{ cm}^2/\text{Vs}$  for NMOS and PMOS devices respectively, and on/off ratios  $> 10^5$  for both types of devices (Fig 4(c), inset). The inverters incorporated devices with channel lengths and widths of  $13 \mu\text{m}$  and  $100 \mu\text{m}$  for NMOS and  $13 \mu\text{m}$  and  $300 \mu\text{m}$  for PMOS, respectively. Under large applied strains, the electrical properties showed little variation, due to the strain isolation effects of the bridges. For example, the inverter threshold voltage changed by less than  $\sim 0.5\text{V}$  for strains of  $\sim 90\%$  in x and y direction, as shown in the right frame of Fig 4(b). To explore fatigue, we cycled the strain from 0% to  $\sim 90\%$  in the x direction 2000 times (Fig 4(b)). The inverters showed little change in properties (gain and threshold voltage,  $V_M$ ) throughout these tests. This non-coplanar serpentine bridge strategy can be applied not only to inverters, but also to more complex circuits. Figure 4(d) shows, as an example, a differential amplifier with circuit layouts and properties reported elsewhere<sup>[8, 11]</sup>. We divided the device into 4 sections, each of which forms an island, and connected them by non-coplanar serpentine bridges. Fig. 4d shows magnified images of stretching in the x and y directions. Electrical measurements verify that the amplifiers work well under these deformations. The gains for 0%, 50% x stretching and 50% y stretching were 1.19, 1.17 and 1.16 (design value 1.2), respectively. Similar strategies should be applicable also to more complex systems.

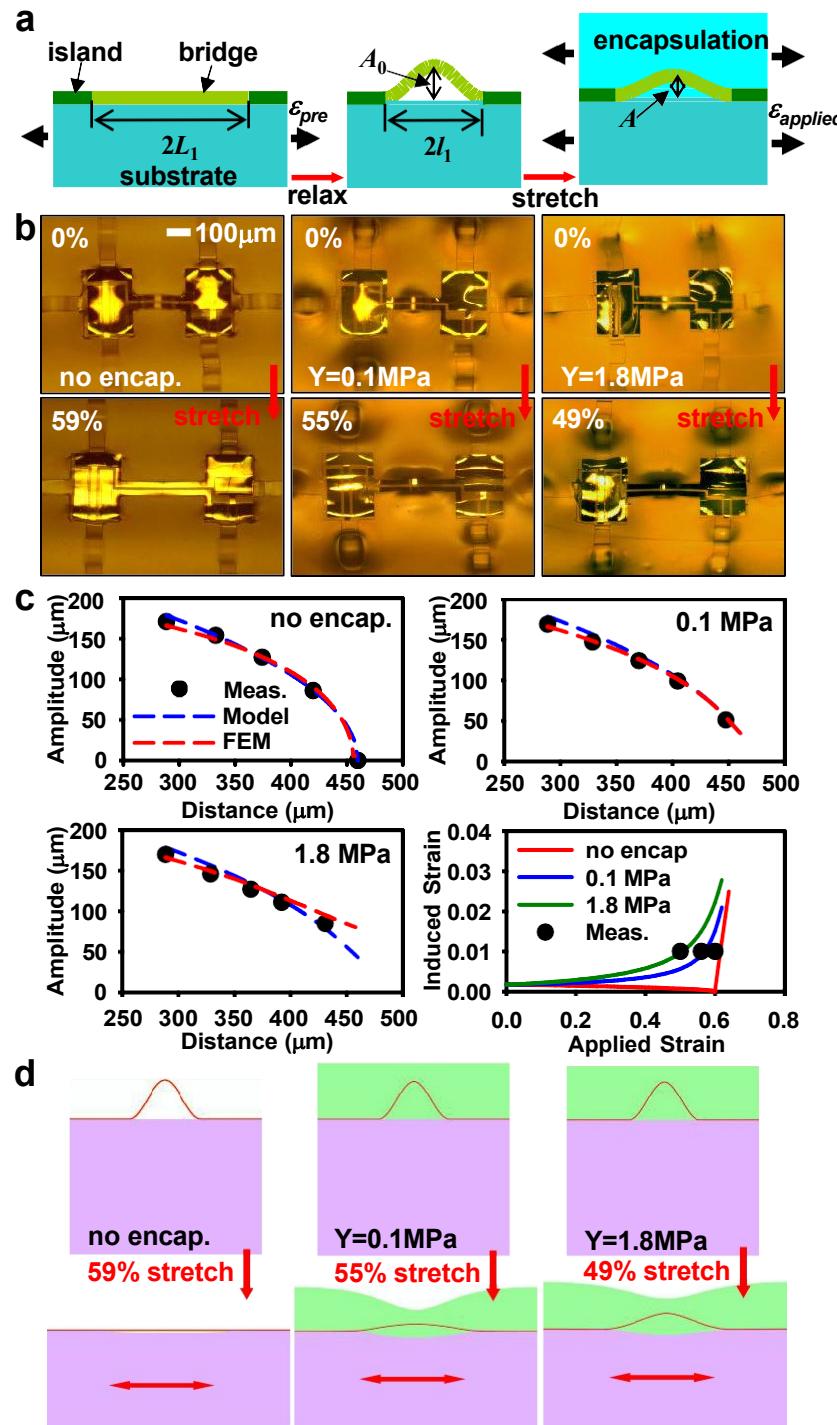

In practice, and especially for non-coplanar device designs, electronic circuits require top surface encapsulation layers to provide mechanical and environmental protection. An ideal material for this purpose is an elastomer, with properties not too dissimilar from the substrate. For optimized mechanical response, this layer should provide minimal restriction of the free deformation of the non-coplanar serpentine bridges. The extent of restriction is

controlled, in large part, by the modulus of the encapsulant. To provide insights into the materials and mechanics aspects, and to allow analytical calculation, we studied the behavior of straight bridge structures. After fabricating corresponding non-coplanar circuits, we encapsulated the system by casting and curing PDMS with different moduli (1.8 MPa and 0.1 MPa) on top (Fig 5(a)), formed by mixing the prepolymer and curing agent (catalyst) at ratios of 10:1 and 45:1, respectively<sup>[12]</sup>. To examine the stretchability, we applied tensile strains up to the fracture point observable by optical microscope (Fig 5(a)). With pre-strain of ~60%, the inverter with no encapsulation can be stretched up to ~59% without fracture. By contrast, similar inverters encapsulated using PDMS with modulus of 0.1 MPa and 1.8 MPa modulus, the maximum stretchability decreased to 55% and 49%, respectively, as shown in Fig. 5(b).

To understand these changes, we developed an analytical model and performed numerical FEM simulation. Consider first a straight bridge of length  $2L$  that buckles upon release of the pre-strain in the PDMS. The buckle amplitude  $A_0$  is related to the pre-strain  $\varepsilon_{pre}$

by  $A_0 = \frac{4L}{\pi} \sqrt{\frac{\varepsilon_{pre}}{1 + \varepsilon_{pre}}}$  [13, 14]. After encapsulation, the energy of the system subject to the

applied strain  $\varepsilon_{applied}$  consists of four parts; (i) bending energy in the bridge

$$U_{bending} = \frac{\pi^4 (EI)_{bridge} A^2}{8L^3} [14], \text{ where } (EI)_{bridge} \text{ is the bending stiffness of the bridge, and } A \text{ is}$$

the new amplitude under stretch; (ii) membrane energy in the bridge

$$U_{membrane} = (Eh)_{bridge} L \left| \frac{\varepsilon_{applied} - \varepsilon_{pre}}{1 + \varepsilon_{pre}} + \frac{\pi^2 A^2}{16L^2} \right|^2 [14], \text{ where } (Eh)_{bridge} \text{ is the tensile stiffness of}$$

the bridge; (iii) elastic energy in the substrate  $U_{substrate}$ , which is proportional to the Young's modulus  $E_{substrate}$  of the substrate, and is obtained from the linear elastic solution of a half space subject to normal surface displacement that is either sinusoidal (over the buckled bridge) or zero (over the island); and (iv) elastic energy in the encapsulation  $U_{encapsulation}$ ,

which is proportional to the Young's modulus  $E_{encapsulation}$  of the encapsulating materials. The amplitude  $A$  is then obtained analytically by minimizing the total energy, which results in the

$$\left(\frac{A}{L}\right)^3 + 16 \left[ \frac{1}{\pi^2} \frac{\varepsilon_{appl} - \varepsilon_{pre}}{1 + \varepsilon_{pre}} + \frac{(Eh)_{bridge}}{L^2} + \frac{\left(\frac{E_{substrate}}{L} + \frac{E_{encapsulation}}{L}\right) L}{2\pi^3 (Eh)_{bridge}} \right] A - \frac{32 \left(\frac{E_{substrate}}{L} + \frac{E_{encapsulation}}{L}\right) L}{\pi^4 (Eh)_{bridge}} \sqrt{\frac{\varepsilon_{pre}}{1 + \varepsilon_{pre}}} = 0$$

The strain in the bridge is given by  $\varepsilon = \frac{\pi^2 A}{2L^2} y$  (y is the distance to the neutral axis). Once the strain in the metal or silicon layer in the bridge reaches the fracture strain (1%), the corresponding applied strain gives the maximum stretchability.

To validate these models, we measured the amplitudes of the non-coplanar bridges during stretching for each case and compared to modeling and FEM values. To measure the amplitude after encapsulation, the high magnification optical microscope was used. In particular, the amplitude of a pop-up bridge was determined from the distance between the focal position on the top of the bridge to the surface of a neighboring island. The results show good agreement with the theory, as shown in the top frames and bottom left frame of Fig 5(c)). The stretchability decreases as we use the high modulus encapsulation, consistent with experiments (right bottom frame of Fig 5(c)) and FEM simulation. Figure 5(d) shows FEM simulation images for no stretching and maximum stretching of each encapsulation case.

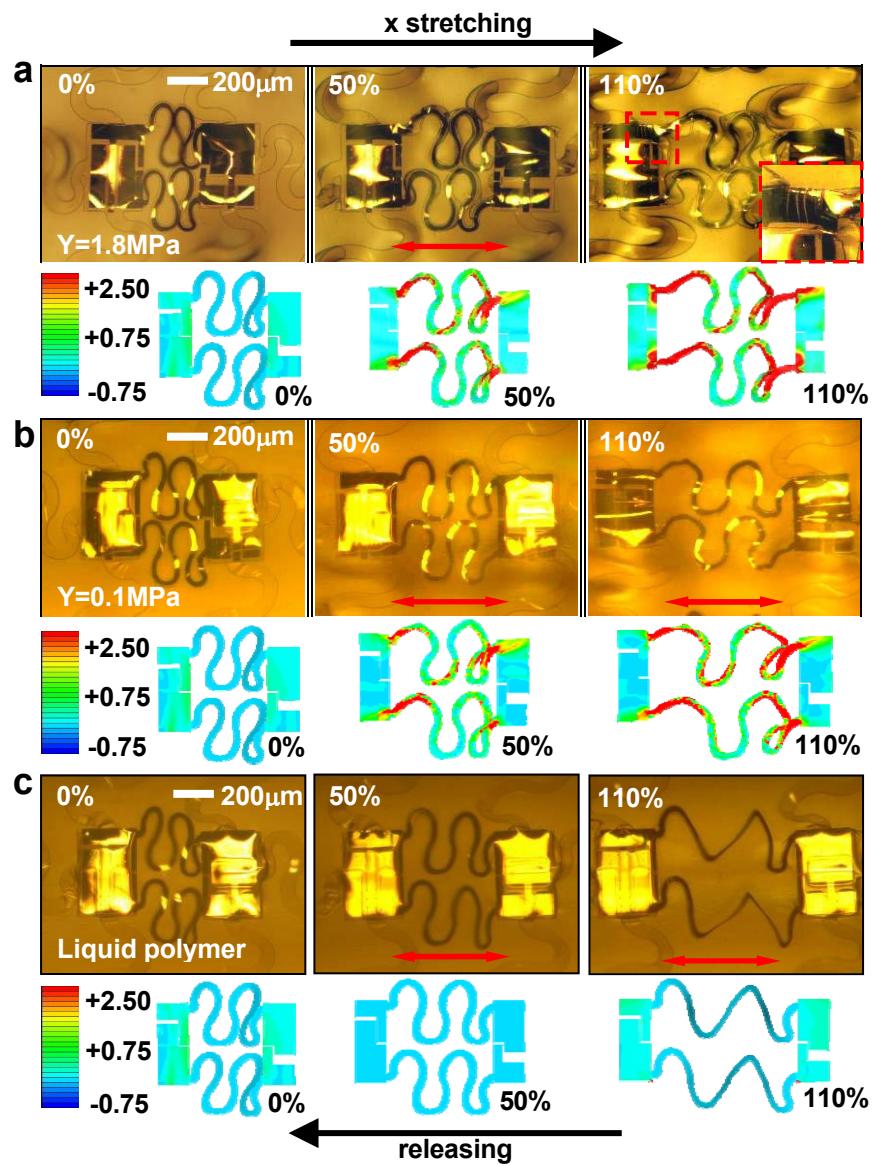

On the basis of insight from the simple cases of Fig. 5, we applied PDMS encapsulation to non-coplanar serpentine bridges to examine responses for PDMS with moduli of 1.8MPa and 0.1MPa, and also for the case of uncured, liquid PDMS. For the 1.8 MPa case, large applied strains (~110%, right frame of Fig. 6(a)) cause cracks, while small strains (~50%, center frame of Fig. 6(a)) do not. Although 0.1 MPa PDMS avoids visible cracks at ~110% strain, the images suggest significant strains, as also indicated by FEM

simulation (bottom frames of Fig 6(b)), with significant wrinkling in the device islands. For further improvement, an uncured liquid prepolymer to PDMS, without curing agent, can be injected between the circuit level and additional thin, top solid encapsulation layer of PDMS. As might be expected, the liquid PDMS has negligible effects on the essential mechanics, even after  $\sim 110\%$  external strain, as shown in Fig. 6(c). These three cases are supported by the theoretical analysis through finite element modeling (FEM) simulation.

### 3. Conclusions

Systematic studies of key effects of materials and design layouts on the mechanical properties of stretchable silicon integrated circuits reveal basic strategies for engineering these systems. Using simple strategies, circuits with excellent electrical performance and reversible, elastic mechanical responses to applied strains in the range of 100% are possible. In more sophisticated approaches of the future, automated design tools, conceptually similar to those in current use for design of electrical properties in circuits, might enable optimized mechanical properties and materials choices for desired applications. Such efforts appear important to the development of a technology foundation for stretchable electronics.

### 4. Experimental Section

The first step in fabricating stretchable silicon CMOS circuits is high temperature diffusion for source, drain and well doping. In this paper, n-type SOI wafer (SOITEC, France) with 260nm top silicon and 1 $\mu$ m buried oxide provided the source of silicon nanoribbons/membranes. Since the mother wafer is n-type, the p-type well is formed first. For p-well, 550~600°C diffusion of Boron from a spin on dopant (B153, Filmtronics, USA) was performed. Next, successive high temperature source and drain doping for pMOS

(1000~1050°C) and nMOS (950~1000°C) was accomplished with Boron (B153, Filmtronics, USA) and Phosphorous (P509, Filmtronics, USA) spin-on-dopants, respectively. After high temperature doping, doped nanoribbons/membranes were transfer printed onto a carrier wafer coated with layers of PMMA (~100nm) and PI (~1.2 $\mu$ m). Electrical isolation of each transistor by reactive ion etching (RIE), followed by deposition of gate dielectrics using PECVD SiO<sub>2</sub> (~40nm) and metal electrodes (Cr/Au, ~5nm/~1500nm) using electron beam evaporation formed the CMOS circuits. Coating a thin layer of PI (1.2 $\mu$ m) as a passivation layer and forming a segmented, mesh structure by RIE completed the device fabrication. Dissolving the underlying PMMA layer released the ultrathin circuits; lifting them to a pre-strained PDMS exposed their back surfaces for selective deposition of SiO<sub>2</sub> onto the active device regions. Transferring to a pre-strained substrate of PDMS completed the process. Electrical measurements were carried out using a probe station (Agilent, 4155C). Mechanical tests, including fatigue cycling, were performed with custom made bending and stretching stages. For the substrates, the stamps and the encapsulation layers, commercial PDMS kits (Sylgard 184, Dow Corning, USA) were used. After mixing the PDMS prepolymer and curing agent (catalyst) with an appropriate ratio, the samples were degassed for 1 hour to remove bubbles generated during mixing. Curing was performed in an oven at 70°C for 2 hours.

### **Acknowledgements**

We thank for various helps of T. Banks in processing by use of facilities at the Frederick Seitz Materials Research Laboratory. This material is based upon work supported by the National Science Foundation under grant ECCS-0824129 and the U.S. Department of Energy, Division of Materials Sciences under Award No. DE-FG02-07ER46471, through the

Materials Research Laboratory and Center for Microanalysis of Materials (DE-FG02-07ER46453) at the University of Illinois at Urbana-Champaign.

- [1] R. H. Reuss, B. R. Chalamala, A. Moussessian, M. G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M. Hatalis, D. Temple, G. Moddel, B. J. Eliasson, M. J. Estes, J. Kunze, E. S. Handy, E. S. Harmon, D. B. Salzman, J. M. Woodall, M. A. Alam, J. Y. Murthy, S. C. Jacobsen, M. Olivier, D. Markus, P. M. Campbell, E. Snow, *Proc. IEEE* **2005**, 93, 1239.

- [2] T. Someya, Y. Kato, T. Sekitani, S. Lba, Y. Noguchi, Y. Murase, H. Kawaguchi, T. Sakurai, *Proc. Natl. Acad. Sci. USA* **2005**, 102, 12321.

- [3] T. Sekitani, Y. Noguchi, K. Hata, T. Fukushima, T. Aida, T. Someya, *Science* **2008**, 321, 1468.

- [4] S. P. Lacour, J. Jones, S. Wagner, T. Li, Z. Suo, *Proc. IEEE* **2005**, 93, 1459.

- [5] S. P. Lacour, D. Chan, S. Wagner, T. Li, Z. Suo, *Appl. Phys. Lett.* **2006**, 88, 204103.

- [6]. D. Brosteaux, F. Axisa, M. Gonzalez, J. Vanfleteren, *IEEE Electron Device Lett.* **2007** 28 552.

- [7]. M. Gonzalez, F. Axisa, M. V. Bulcke, D. Brosteaux, B. Vandevelde, J. Vanfleteren, *Microelectronics Reliability* **2008**, 48, 825.

- [8] D.-H. Kim, J.-H. Ahn, W. M. Choi, H.-S. Kim, T.-H. Kim, J. Song, Y. Y. Huang, Z. Liu, C. Lu, J. A. Rogers, *Science* **2008**, 320, 507.

- [9] D.-H. Kim, W. M. Choi, J.-H. Ahn, H.-S. Kim, J. Song, Y. Y. Huang, Z. Liu, C. Lu, C. G. Koh, J. A. Rogers, *Appl. Phys. Lett.* **2008**, 93, 044102.

- [10] H. C. Ko, M. P. Stoykovich, J. Song, V. Malyarchuk, W. M. Choi, C.-J. Yu, J. Geddes III, J. Xiao, S. Wang, Y. Y. Huang, J. A. Rogers, *Nature* **2008**, 454, 748.

- [11] D.-H. Kim, J. Song, W. M. Choi, H.-S. Kim, R.-H. Kim, Z. Liu, Y. Y. Huang, K.-C. Hwang, Y.-W. Zhang, J. A. Rogers, *Proc. Natl. Acad. Sci. USA* **2008**, 105, 18675.

- [12] Xin Q. Brown, Keiko Ookawa, Joyce Y. Wong, *Biomaterials* **2005**, *26*, 3123.

- [13] H. Jiang, Y. Sun, J. A. Rogers, Y. Huang, *Appl. Phys. Lett.* **2007**, *90*, 133119.

- [14] H. Jiang, Y. Sun, J. A. Rogers, Y. Huang, *Int. J. Solids and Structures*, **2008**, *45*, 2014.

Received: ((will be filled in by the editorial staff))

Revised: ((will be filled in by the editorial staff))

Published online on ((will be filled in by the editorial staff))

## Figure Captions

**Figure 1.** Schematic illustrations (left) and corresponding optical images (right) of (a) doped silicon, (b) interconnected arrays of CMOS inverters, (c) lifted inverters covered with a shadow mask for selective deposition of Cr/SiO<sub>2</sub> and (d) magnified views of an inverter.

**Figure 2.** Optical microscope images and maximum principal strain distribution evaluated by FEM simulation for a CMOS inverter with (a) a standard serpentine interconnect, (b) an interconnect with large amplitude and (c) an interconnect with large amplitude to wavelength ratio, narrow width and large number of curves.

**Figure 3.** Optical microscope images and maximum principal strain distributions computed by FEM simulation for a CMOS inverter with (a) coplanar and (b) non-coplanar structure, (c) Scanning electron microscopy (SEM) images for Fig. 3(b) before (left) and after (center and right) applying external strain, (d) FEM simulation for Fig. 3(b) before (left) and after (right) applying external strain.

**Figure 4.** (a) Optical images of a CMOS inverter with non-coplanar serpentine interconnects before and after applying 90% external strain in the x (right) and y (left) direction and (b) corresponding voltage transfer curves (left) and cycling test results (right). (c) Current-voltage response and PSPICE simulation result for NMOS (left) and PMOS (right) transistors; the inset shows the transfer curve on a semilog scale. (d) Optical images and electrical characteristics of a differential amplifier with non-coplanar serpentine interconnects.

**Figure 5.** (a) Schematic illustration of stretching test procedures for an encapsulated, straight bridge non-coplanar interconnect, (b) optical microscope images of the structure for the cases of zero strain (top) and maximum stretching before visible cracking (bottom) for no encapsulation (left), soft encapsulation (0.1 MPa, center) and hard encapsulation (1.8 MPa, right), (c) height of the bridge as a function of distance between the two islands determined by experiment, analytical modeling and FEM simulation; right bottom graph shows maximum strain before cracking estimated by theoretical modeling, (d) deformation geometries at maximum stretching before cracking, simulated by FEM.

**Figure 6.** Optical microscope images and strain distributions determined by FEM simulation for zero strain (left), ~50% strain (center) and ~110% strain (right), (a) hard PDMS (modulus ~1.8 MPa) encapsulation, (b) soft PDMS (modulus ~ 0.1MPa) encapsulation and (c) uncured PDMS prepolymer (viscous liquid) encapsulation covered by a thin, solid layer of PDMS.

## **The table of contents entry**

This paper presents experimental and theoretical investigations of materials and system designs for ultrathin single crystal silicon based stretchable electronics. Device geometries and encapsulation strategies with non-coplanar serpentine mesh structures can provide extremely high (~100%) levels of stretchability. Circuit demonstrations including CMOS inverters and NMOS differential amplifiers as well as mechanical modeling through FEM analysis illustrate the principles.

## **Keyword**

Flexible Electronics, Stretchable Electronics, Semiconductor Nanomaterials, Nanomechanics

## **Authors**

Dae-Hyeong Kim, Zhuangjian Liu, Yun-Soung Kim, Jian Wu, Jizhou Song, Hoon-Sik Kim, Yonggang Huang, K.-C. Hwang and John A. Rogers

## **Title**

Optimized Materials and Structural Designs for Stretchable Silicon Integrated Circuits

## **ToC figure**

**Figure 1**

**Figure 2**

**Figure 3**

**Figure 4**

**Figure 5**

**Figure 6**