This paper describes objective technical results and analysis. Any subjective views or opinions that might be expressed in the paper do not necessarily represent the views of the U.S. Department of Energy or the United States Government.

Sandia

National

Laboratories

SAND2021-3061C

U.S. NAVAL

RESEARCH

LABORATORY

# Vertical GaN Power Electronics – Opportunities and Challenges

*R. Kaplar<sup>1</sup>, A. Allerman<sup>1</sup>, M. Crawford<sup>1</sup>, B. Gunning<sup>1</sup>, J. Flicker<sup>1</sup>,

A. Armstrong<sup>1</sup>, L. Yates<sup>1</sup>, J. Dickerson<sup>1</sup>, A. Binder<sup>1</sup>, G. Pickrell<sup>1</sup>, P.

Sharps<sup>1</sup>, J. Neely<sup>1</sup>, L. Rashkin<sup>1</sup>, L. Gill<sup>1</sup>, T. Anderson<sup>2</sup>, J.

Gallagher<sup>2</sup>, A. Jacobs<sup>2</sup>, A. Koehler<sup>2</sup>, M. Tadjer<sup>2</sup>, K. Hobart<sup>2</sup>, M.

Ebrish<sup>3</sup>, M. Porter<sup>4</sup>, R. Martinez<sup>5</sup>, K. Zeng<sup>5</sup>, D. Ji<sup>6</sup>, S. Chowdhury<sup>5</sup>,

O. Aktas<sup>7</sup>, and J. Cooper<sup>8</sup>*

<sup>1</sup>Sandia National Laboratories, Albuquerque, NM, USA; rjkapla@sandia.gov

<sup>2</sup>Naval Research Laboratory, Washington, DC, USA

<sup>3</sup>National Research Council, Washington, DC, USA, residing at NRL

<sup>4</sup>Naval Postgraduate School, Monterey, CA, USA, residing at NRL

<sup>5</sup>Stanford University, Stanford, CA, USA

<sup>6</sup>Formerly at Stanford, now at Intel Corp., Santa Clara, CA, USA

<sup>7</sup>EDYNX Inc., Livermore, CA, USA

<sup>8</sup>Sonrisa Research Inc., Santa Fe, NM, USA

The authors gratefully acknowledge the support of the ARPA-E OPEN+ Kilovolt Devices Cohort managed by Isik Kizilyalli, and the DOE Vehicle Technology Office Electric Drivetrain Consortium managed by Susan Rogers

March 18, 2021

U.S. DEPARTMENT OF

**ENERGY** | Energy Efficiency &

Renewable Energy

VEHICLE TECHNOLOGIES OFFICE

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

# Outline

- **Overview of WBG Power Electronics**

- **Medium-Voltage Vertical GaN Devices**

- **PN Diodes**

- **Vertical GaN Devices for Electric Vehicles**

- **JBS Diodes and MOSFETs**

- **Overview of WBG Power Electronics**

- **Medium-Voltage Vertical GaN Devices**

- PN Diodes

- **Vertical GaN Devices for Electric Vehicles**

- JBS Diodes and MOSFETs

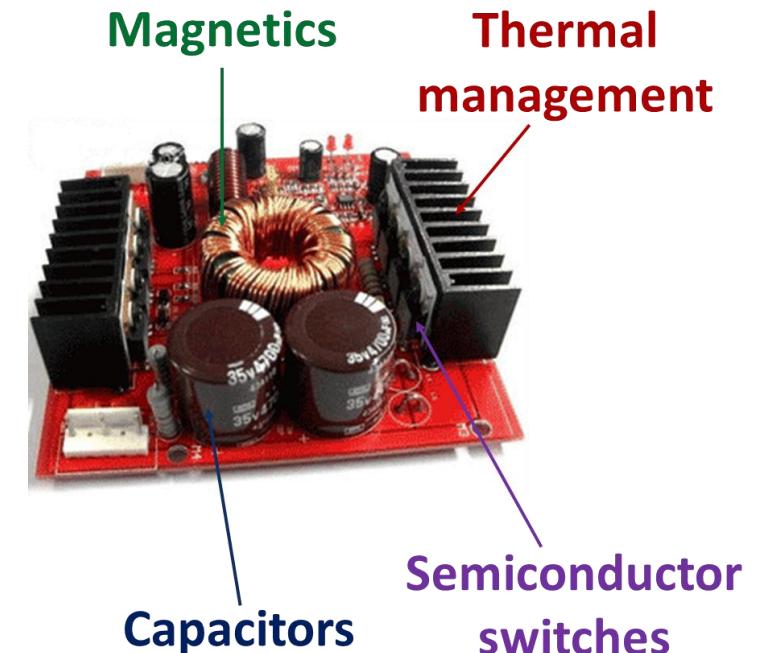

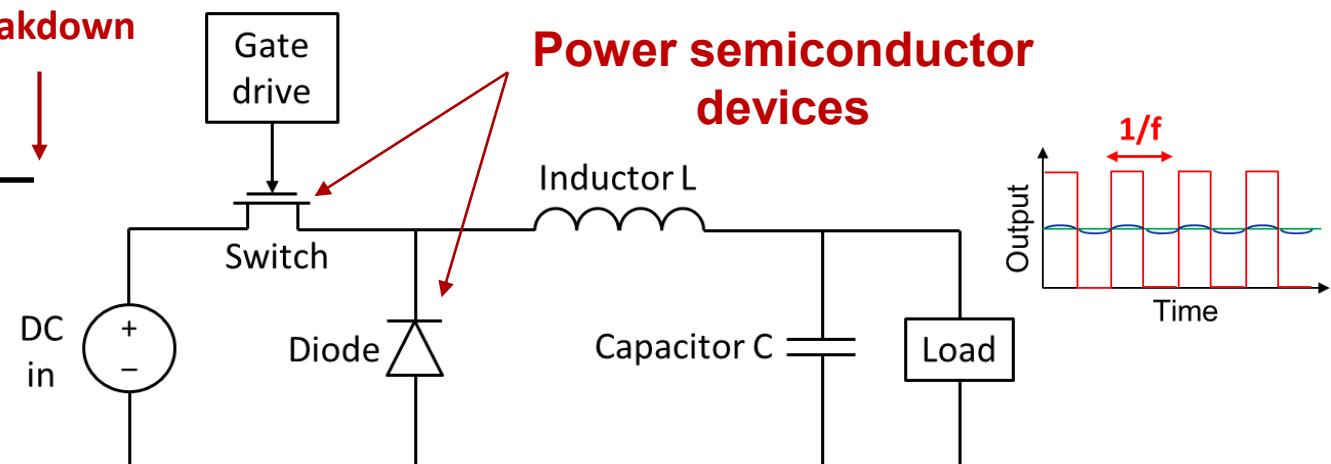

# What Are Power Electronics?

**Power electronics:** Application of solid-state electronics for routing, control, and conversion of electrical power

- Current power electronics are limited by the properties of Silicon semiconductor devices

- New system capabilities are enabled by:

- Higher switching frequency (enables better SWaP)

- Lower power loss

- Higher temperature operation

- **Motivation for WBG/UWBG semiconductors**

# Power Electronics for Energy Efficiency

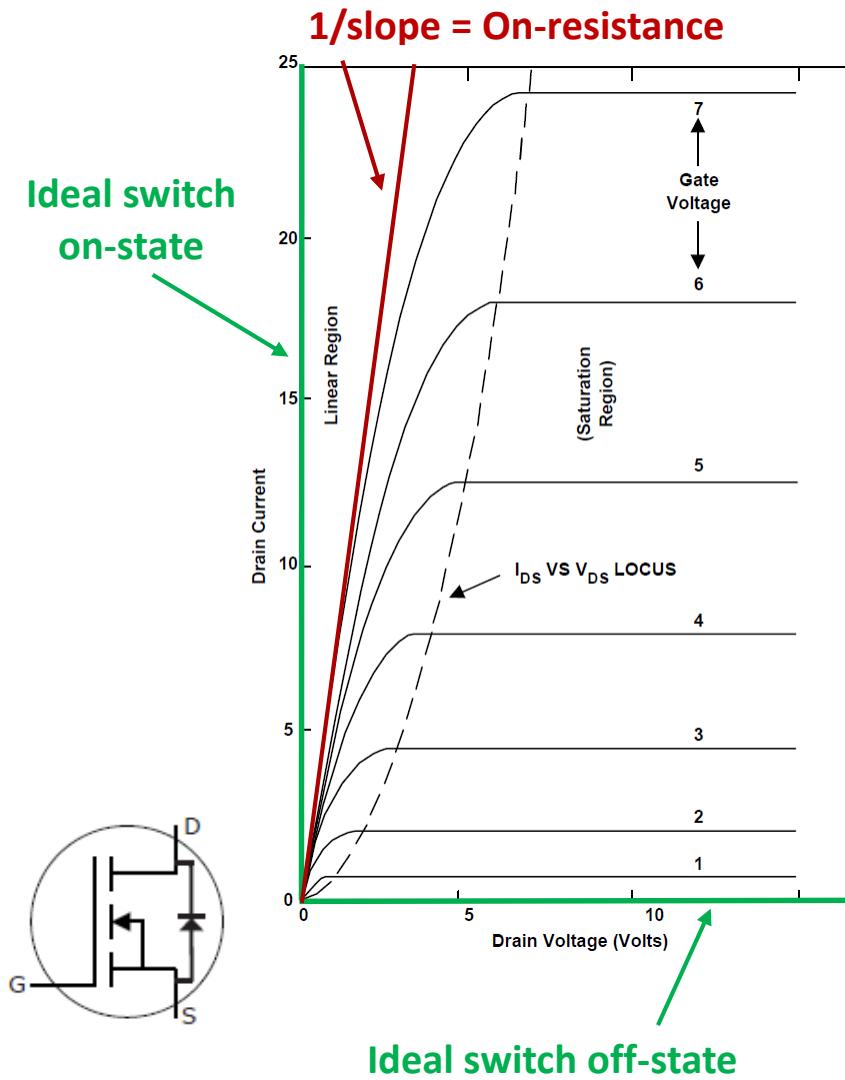

# Power Electronic Devices and Circuits

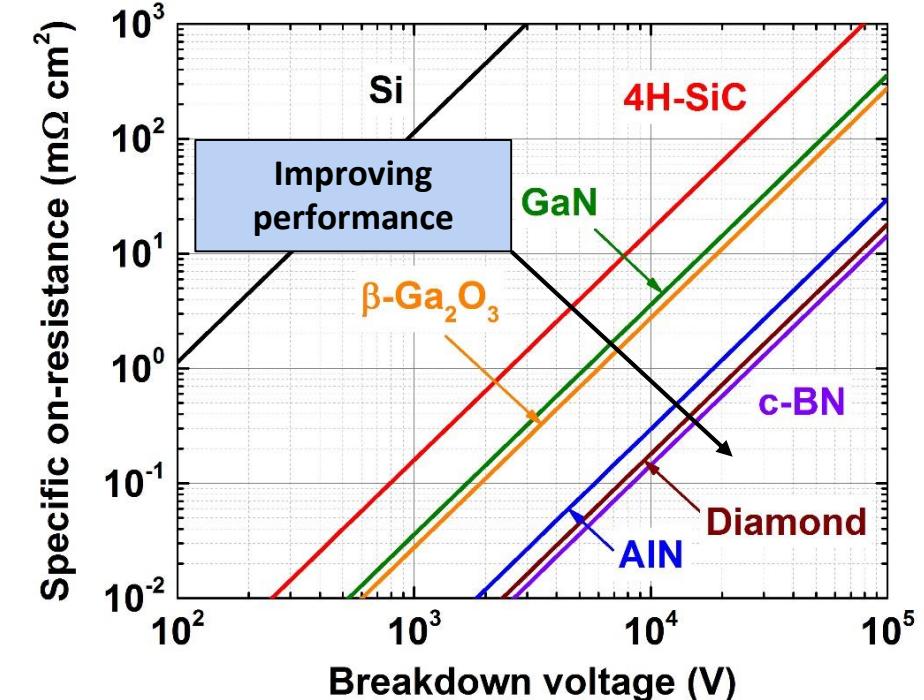

# Advantages of WBG/UWBG Semiconductors

**Vertical device:**

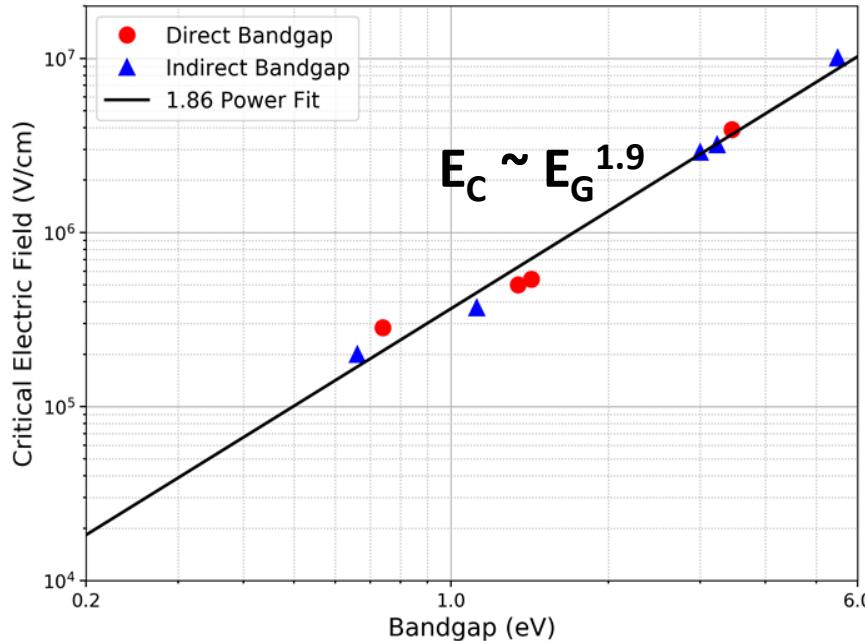

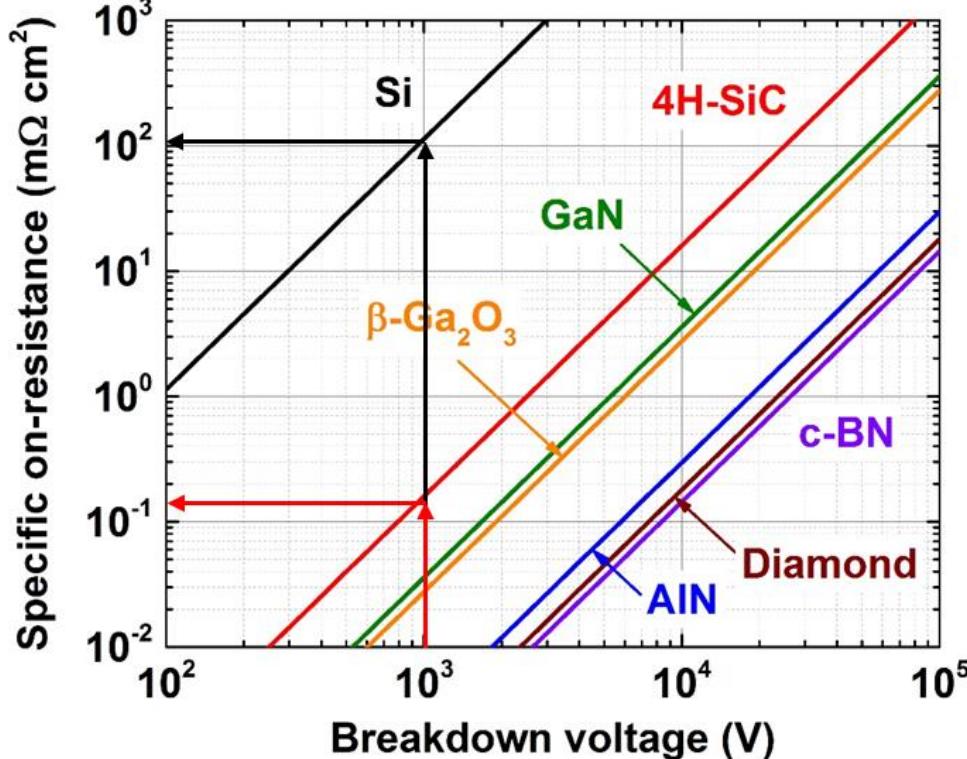

$$\text{UFOM} = V_B^2 / R_{\text{on,sp}} = \epsilon \mu_n E_C^3 / 4$$

**Lateral device:**

$$\text{LFOM} = V_B^2 / R_{\text{on,sp}} = q \mu_{\text{ch}} n_s E_C^2$$

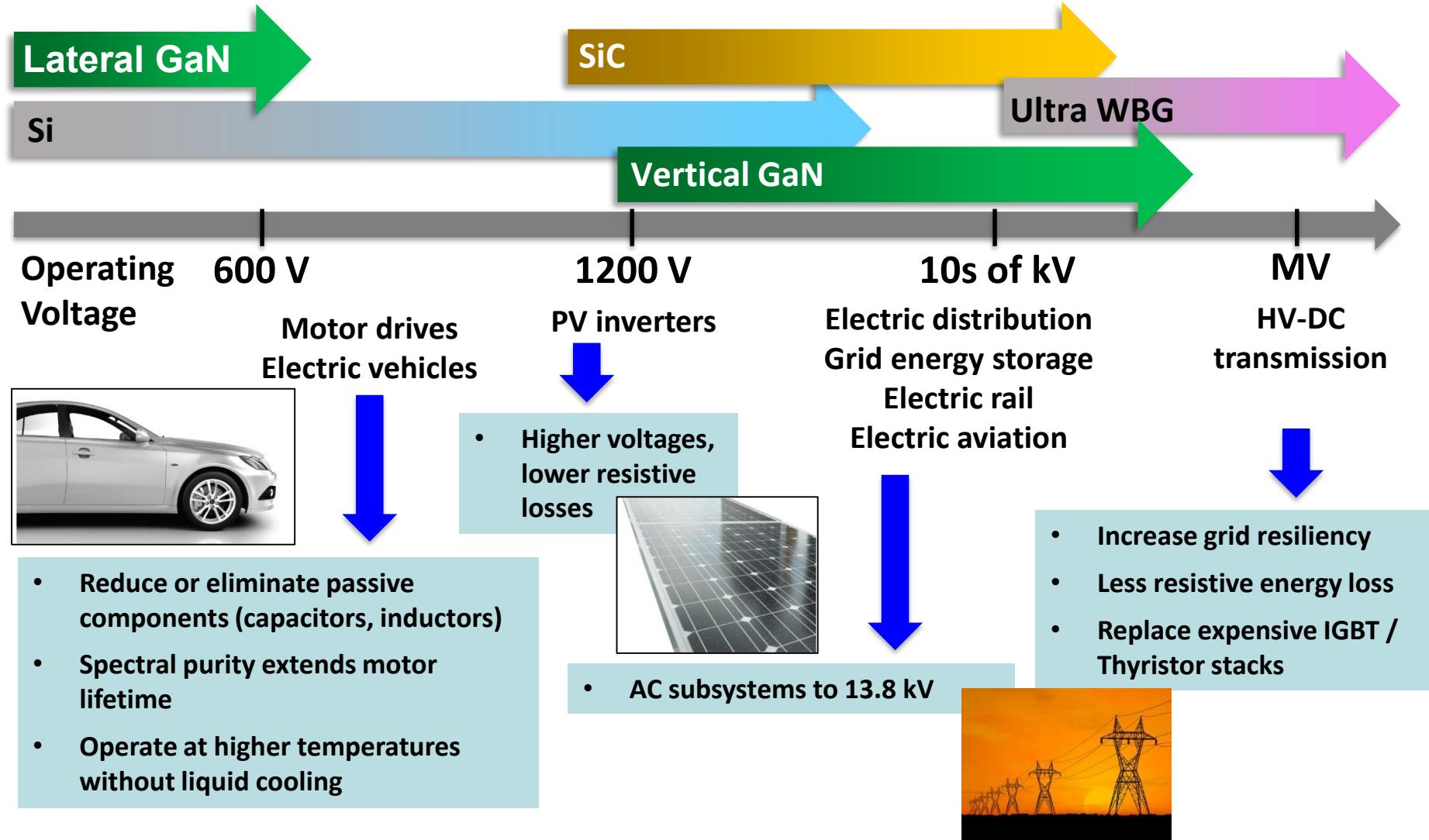

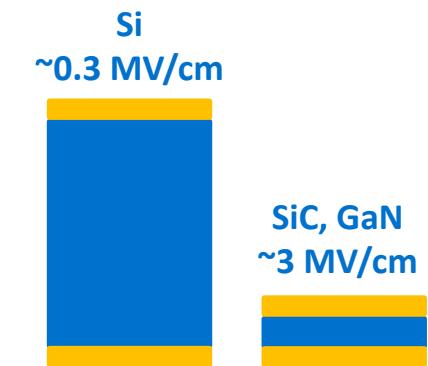

# Scaling of WBG/UWBG Power Devices

*The scaling that results from the properties of WBG and UWBG materials can be utilized to optimize for switching frequency, conduction loss, and switching loss*

- For equivalent breakdown voltage, get lower  $R_{on}A$  for (U)WBG device

- For same  $R_{on}$ , (U)WBG device can have *smaller area*

- Smaller area results in *less capacitance*

- Gives a *faster switching transient* and *lower loss per switching cycle*

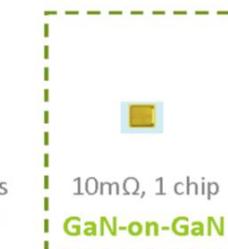

For a given on-resistance ( $R_{on}$ ) of 10mΩ:

500mΩ, 50 chips

Si-MOSFET

40mΩ, 4 chips

GaN-on-SiC

Thinner drift layers required for increasing  $E_c$

GaN-on-GaN lowers die cost while improving  $R_{on} \times C_{off}$  switching characteristic

10mΩ, 1 chip

GaN-on-GaN

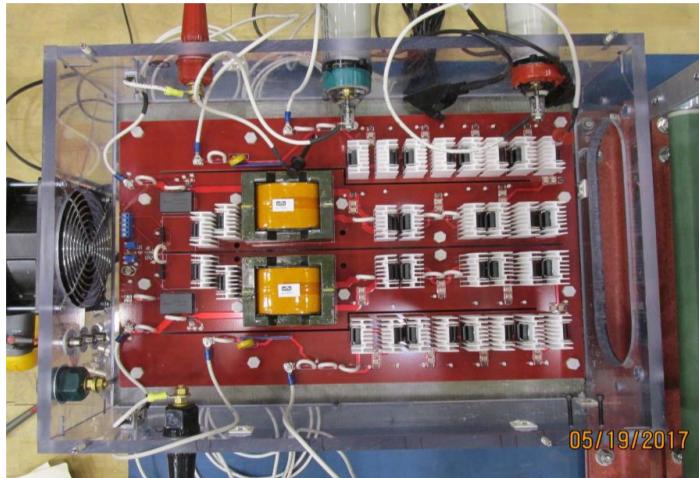

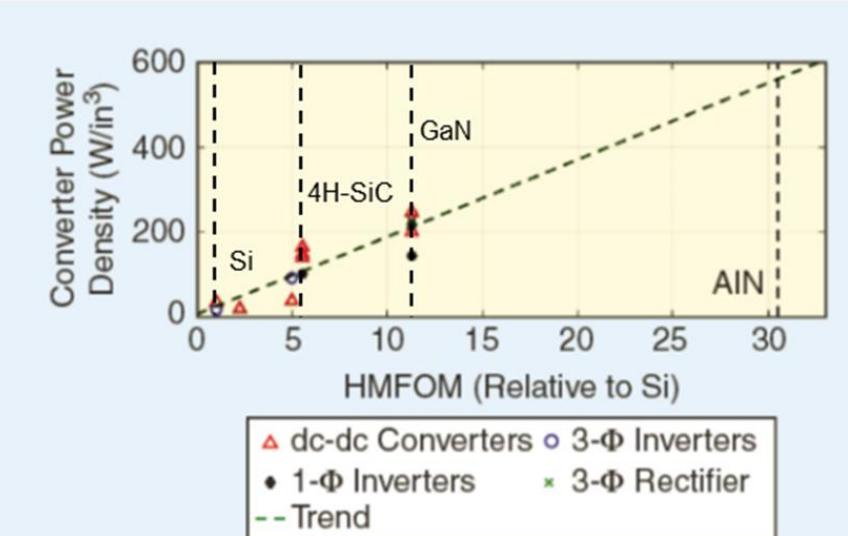

# Improvements in Converter Power Density

SNL SiC hybrid switched-capacitor boost converter (ARPA-E)

- First prototype: 0.5 kV → 10.1 kV (gain = 16.8) at 2.6 kW, 95.3% efficient, 410 in<sup>3</sup>

- Second prototype: +2% efficiency, 55% volume

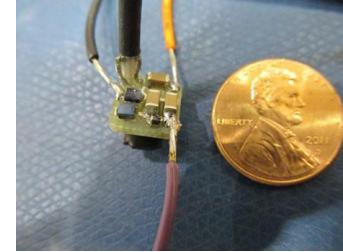

Over an order of magnitude improvement in power density is enabled by WBG and UWBG semiconductors compared to Si

SNL GaN HEMT "Coin Converter"

90 V, 90 mA → 215 W/in<sup>3</sup>

SOA commercial microinverter

250 W in 59 in<sup>3</sup> → 4.2 W/in<sup>3</sup>

R. J. Kaplar, J. C. Neely, et al., *IEEE Power Electronics Magazine* (March 2017)

## Relative Figures of Merit:

- Vertical UFOM =  $\varepsilon \mu_n E_c^3$

- Lateral LFOM =  $q \mu_{ch} n_s E_c^2$

- Huang Material FOM =  $E_c \mu_n^{1/2}$

- HM-FOM seems to be a good predictor of power density in a variety of power converter types*

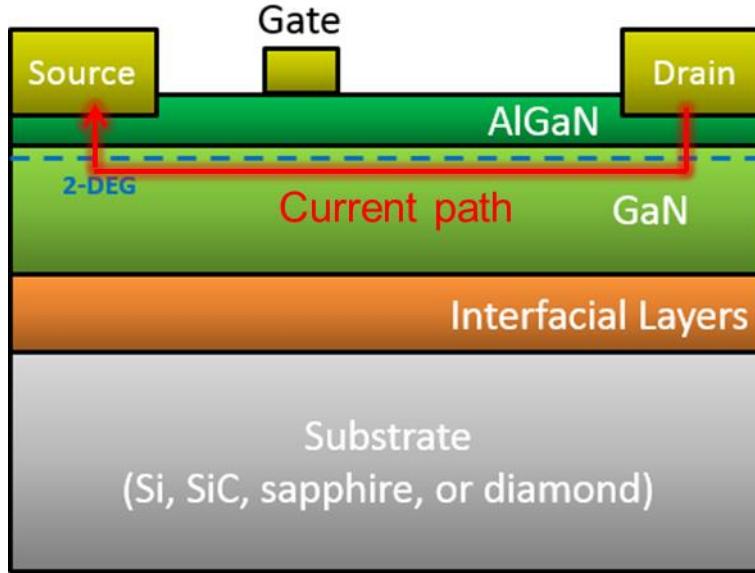

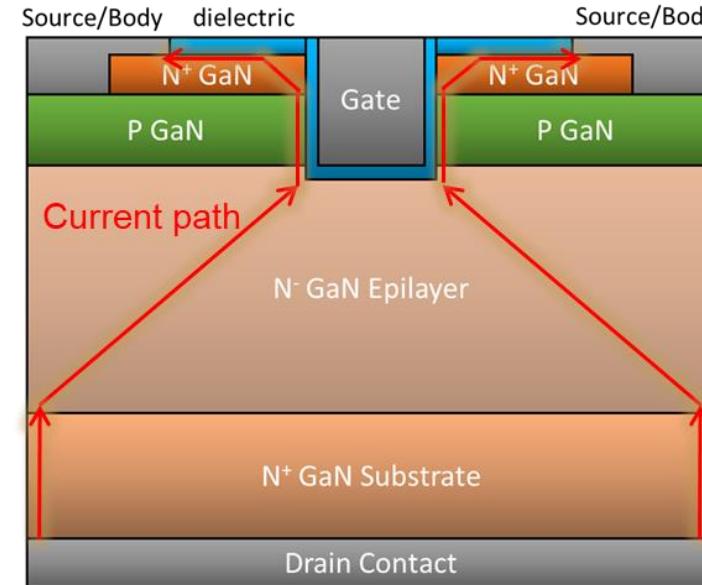

# Lateral vs. Vertical GaN Power Devices

**Lateral Current Flow

(HEMT)**

**Vertical Current Flow

(Trench MOSFET)**

- Polarization-doped heterostructure

- High electron mobility in 2DEG for low  $R_{ON}$

- High-frequency operation (up to  $\sim 1$  MHz)

- Low blocking voltage ( $< \sim 650$  V, scales with area)

- Typically grown on foreign substrate

- Commercially available

- Selective-area impurity doping required

- Mobility limited by channel

- Capable of large blocking voltages ( $> 1200$  V, not dependent on area)

- Grown on native GaN substrates

# Outline

- Overview of WBG Power Electronics

- Medium-Voltage Vertical GaN Devices

- PN Diodes

- Vertical GaN Devices for Electric Vehicles

- JBS Diodes and MOSFETs

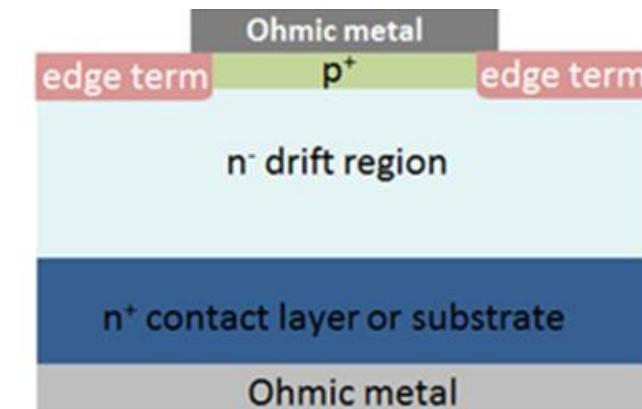

# Overview of Vertical GaN Technology

- Need to extend the limits of vertical GaN power device technology for medium-voltage applications (~1.2-20 kV)

- Need to increase  $V_B$  by 4x from today's SOA

- Challenges: Thick drift region, low net doping, edge termination

- Need to establish a domestic foundry process for vertical GaN power devices

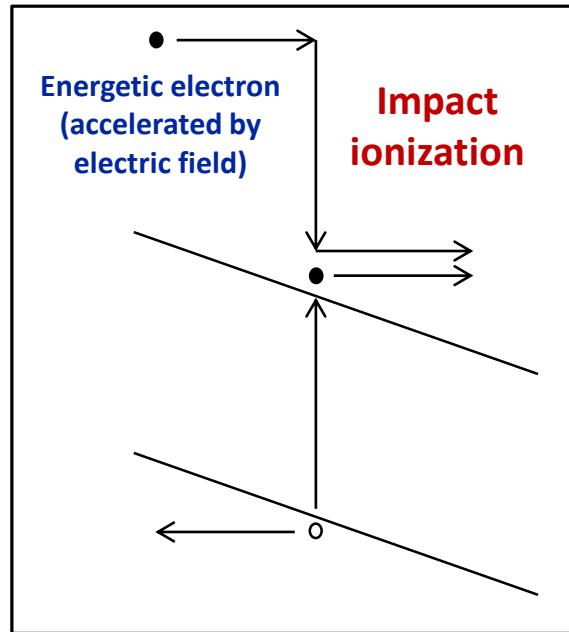

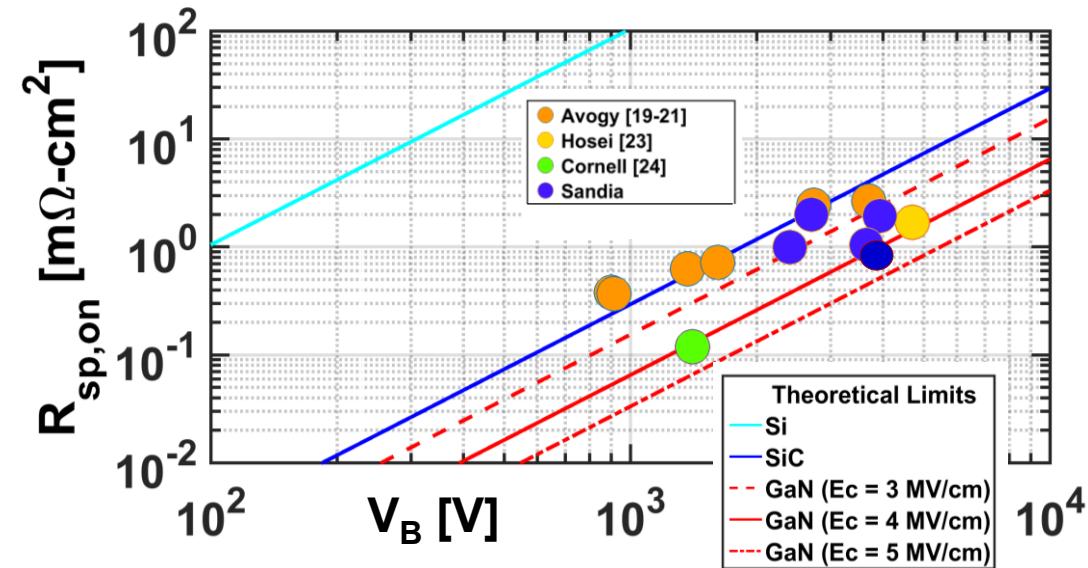

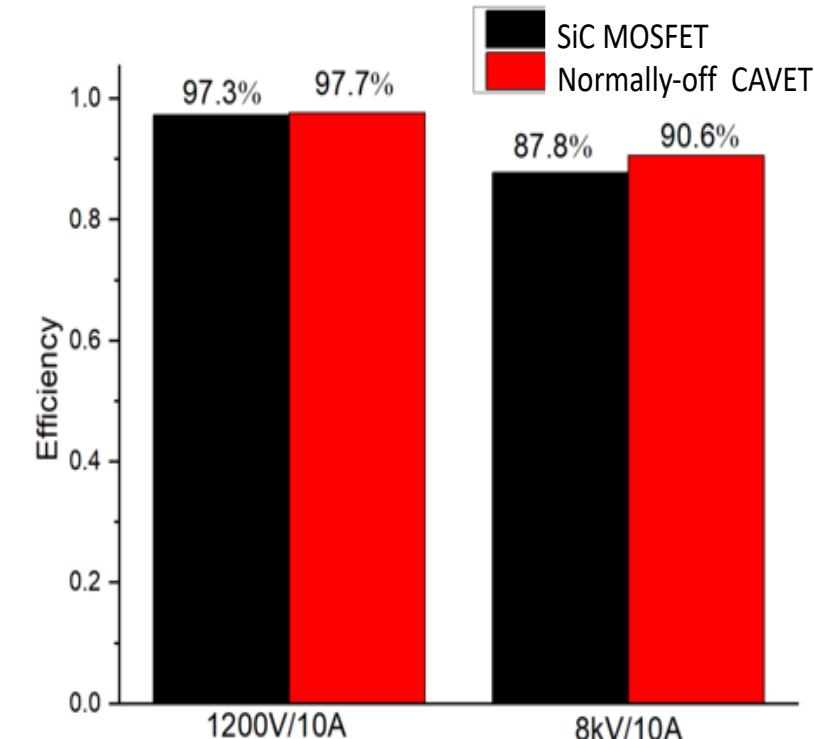

# Vertical GaN Advantages for MV Power Electronics

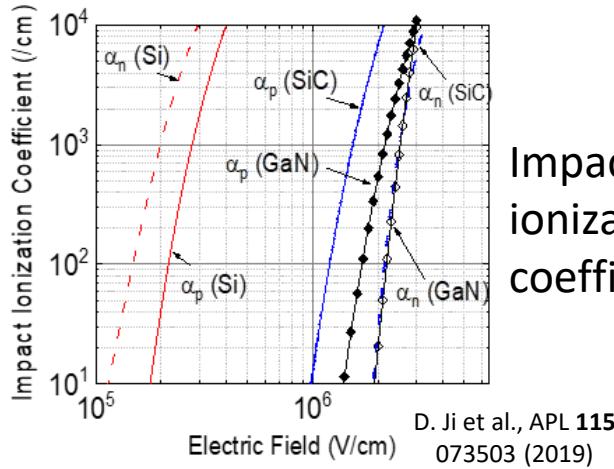

- Critical field of GaN  $\sim 2.8$  MV/cm at  $N_D = 1 \times 10^{16}$  cm $^{-3}$  and room temperature based on most recent impact ionization measurements [1]

- Slightly higher than  $E_C$  of SiC at the same temperature and doping [2]

- But higher mobility of GaN  $\sim 1200$  cm $^2$ /Vs [3] compared to  $\sim 950$  cm $^2$ /Vs for SiC [2] at the same doping and temperature lead to improvements in power converter efficiency [4], ***particularly for medium-voltage devices (> 1.2 kV)***

- But devices are not widely available – ***a vertical GaN foundry is needed that monitors yield, reliability, etc.***

[1] D. Ji, B. Ercan, and S. Chowdhury, "Experimental Determination of Impact Ionization Coefficients of Electrons and Holes in Gallium Nitride Using Homojunction Structures," *Appl. Phys. Lett.* **115**, 073503 (2019).

[2] J. A. Cooper and D. Morissette, "Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC," *Elec. Dev. Lett.* **41**, 892 (2020).

[3] I. C. Kizilyalli, A. P. Edwards, O. Aktas, T. Prunty, and D. Bour, "Vertical Power PN Diodes Based on Bulk GaN," *IEEE Trans. Elec. Dev.* **62**(2), 414 (2015).

[4] D. Ji and S. Chowdhury, "On the Progress Made in GaN Vertical Device Technology – Special Issue on Wide Band Gap Semiconductor Electronics and Devices," *Int. J. High-Speed Elec. Sys.* **28**(01n02), 1940010 (2019).

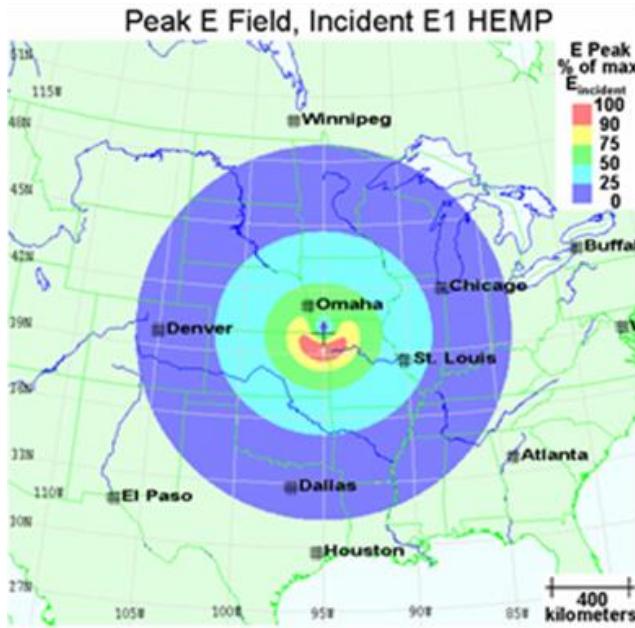

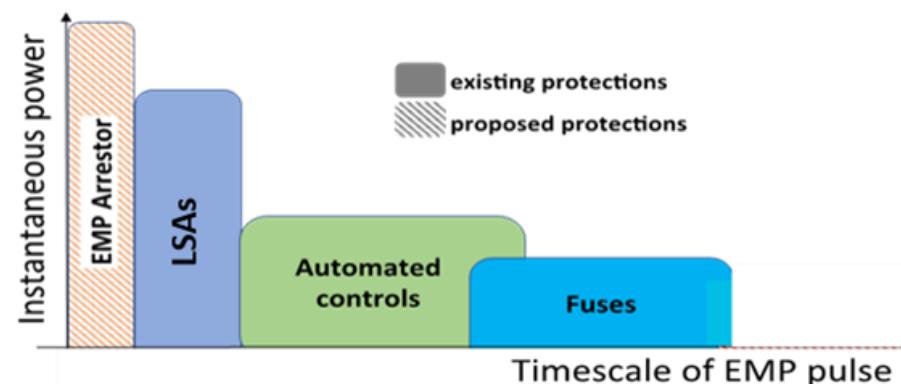

# Fast Protection for the Electric Grid

- Electromagnetic pulses are a threat to the grid

- Very fast E1 component ( $< 1 \mu\text{s}$ )

- Unaddressed by current SoA technology (LSAs)

- Transient protection is needed for MV grid-connected systems

J. S. Foster Jr. et al., "Report of the Commission to Assess the Threat to the United States from Electromagnetic Pulse (EMP) Attack: Critical National Infrastructures," *Defense Technical Information Center* (2008).

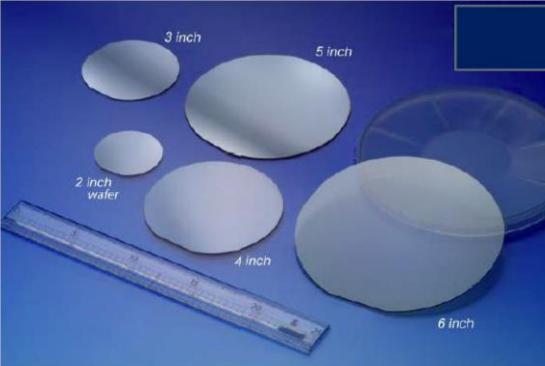

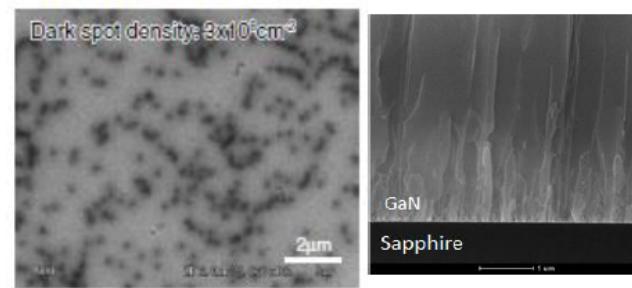

# Native Substrates for Vertical GaN Devices

| Attributes                              | GaN on Si | GaN on SiC      | GaN on Bulk-GaN      |

|-----------------------------------------|-----------|-----------------|----------------------|

| <b>Defect Density (cm<sup>-2</sup>)</b> | $10^9$    | $5 \times 10^8$ | $10^3$ to $10^6$     |

| <b>Lattice Mismatch, %</b>              | 17        | 3.5             | 0                    |

| <b>CTE Mismatch, %</b>                  | 54        | 25              | 0                    |

| <b>Layer Thickness (μm)</b>             | < 5       | < 10            | > 50                 |

| <b>Breakdown Voltage (V)</b>            | < 1000    | < 2000          | > 5000               |

| <b>OFF State Leakage</b>                | High      | High            | Low                  |

| <b>Device Types</b>                     | Lateral   | Lateral         | Vertical and Lateral |

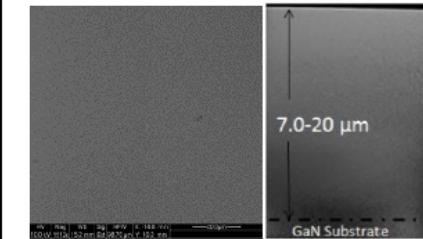

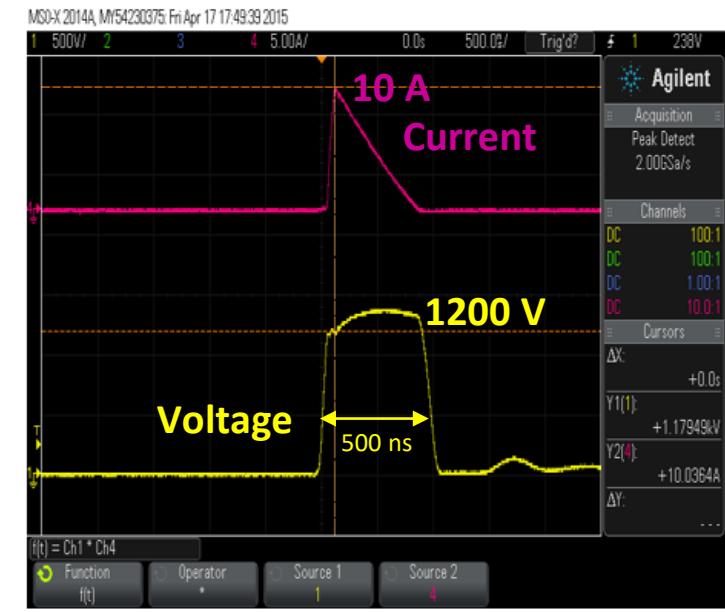

# Avalanche Ruggedness of Vertical GaN

- Avalanche breakdown mechanism demonstrated via temperature dependence

- Avalanche ruggedness demonstrated in real power switching circuits

- *Very different from the situation for GaN-on-Si power devices, where avalanche breakdown does not occur*

O. Aktas and I. C. Kizilyalli, IEEE EDL 36(9), 890 (2015)

# Carrier Transport in Vertical GaN

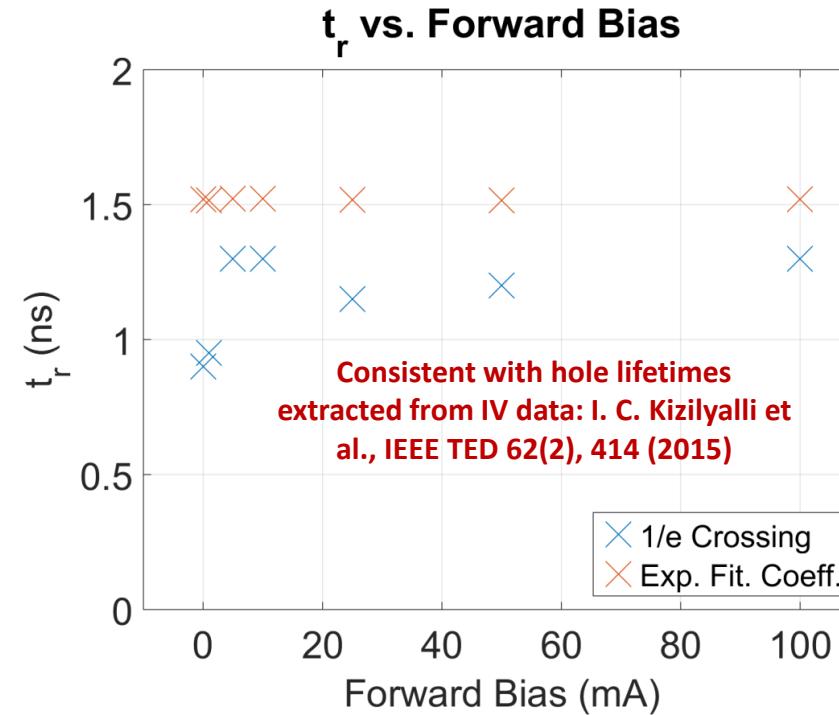

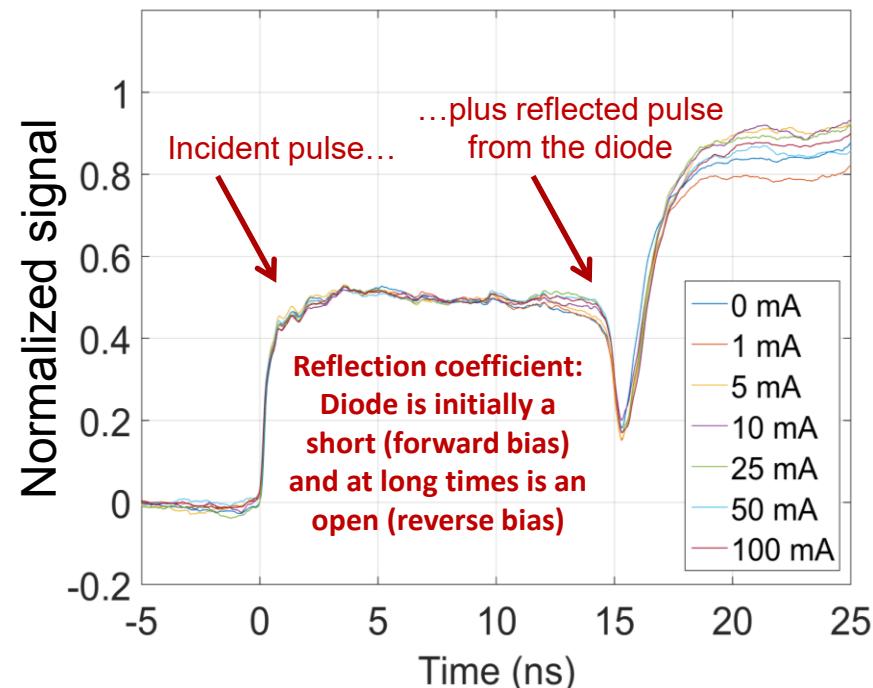

Reverse recovery measurements on vertical GaN diodes to determine carrier lifetime

- 100 V reversing pulses used with various forward currents

- Reverse-recovery time is invariant to forward bias, implying  $t_r$  is limited by capacitance

- Measured times provide an upper limit for hole lifetime –  $\tau_h \approx 2$  ns

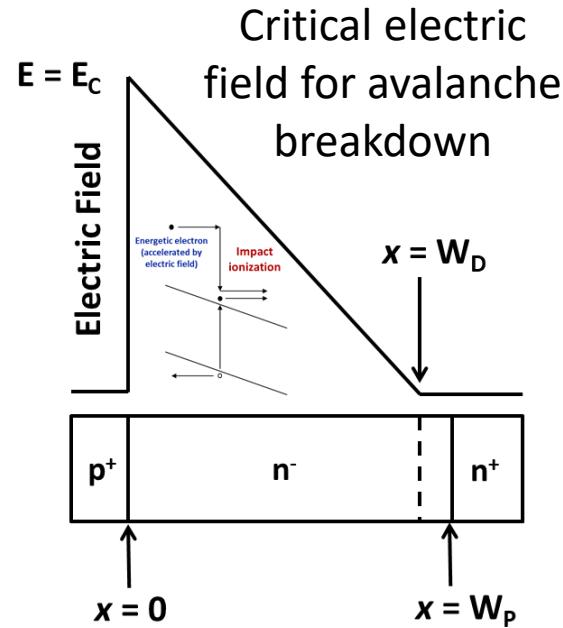

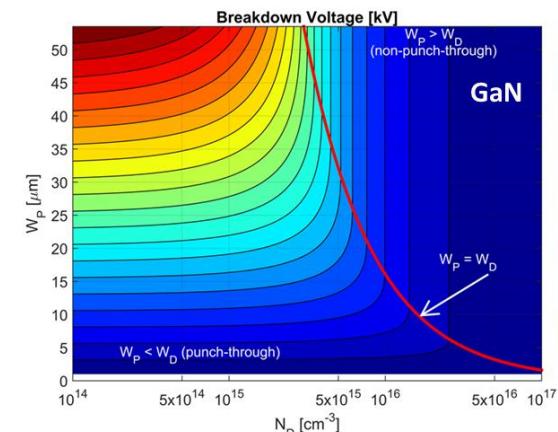

**Ideal planar limit of GaN breakdown depends on drift layer thickness and doping:**

But premature breakdown will occur at the device surface, edge, etc. unless mitigations are taken to prevent this – edge termination

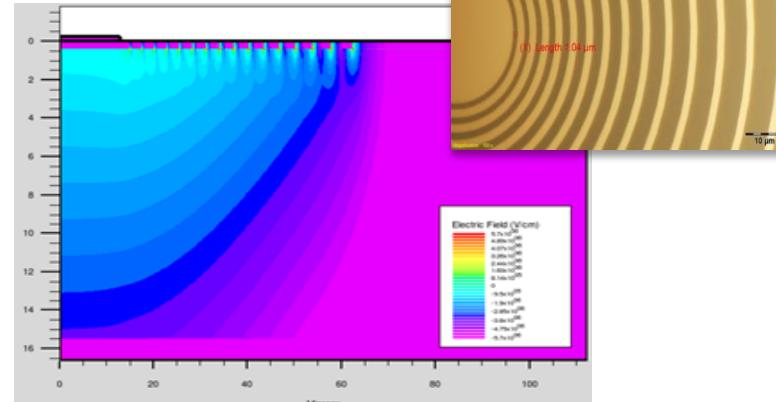

## Guard Rings

J. Dickerson et al., EMC (2016)

The diagram illustrates a diode structure with an anode at the top and a cathode at the bottom. The anode is labeled  $P^+$  and the cathode is labeled  $N^-$ . A hatched region represents the p-n junction. The electric field is shown as a downward-pointing arrow labeled  $W_p$  on the anode side and an upward-pointing arrow labeled  $W_N$  on the cathode side. The angle between the electric field and the normal to the junction is labeled  $\theta$ . The surface width of the depletion region is labeled  $W_{surface}$ . The depletion region is shaded with diagonal lines. The cathode is labeled  $Cathode$  at the bottom.

if  $\theta \downarrow \Rightarrow W_{surface}/W_N \uparrow \Rightarrow \epsilon_{surface} \downarrow \Rightarrow V_{BR} \uparrow$

A. Binder et al., WiPPDA (2019)

## Various approaches to edge termination

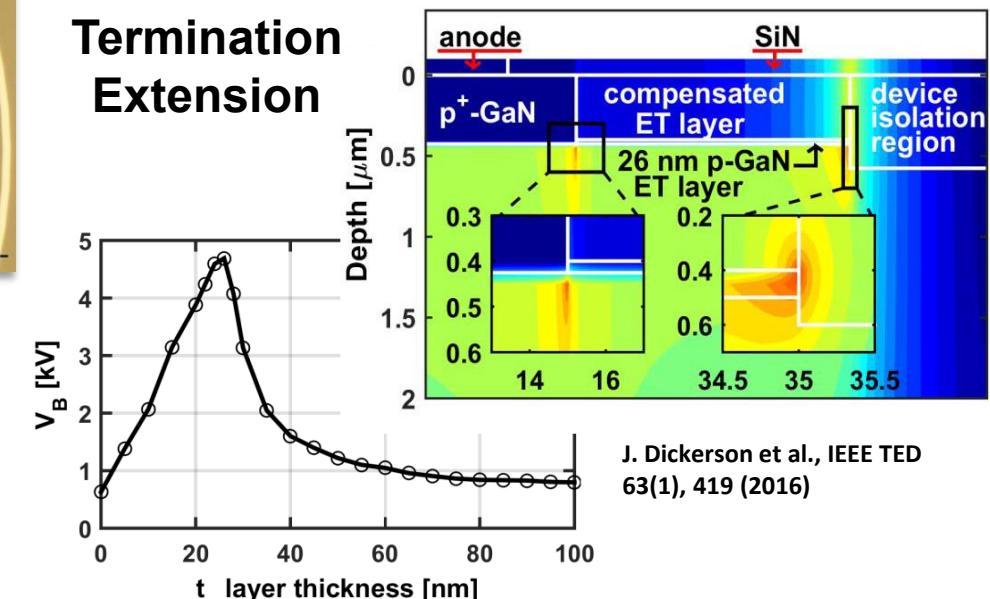

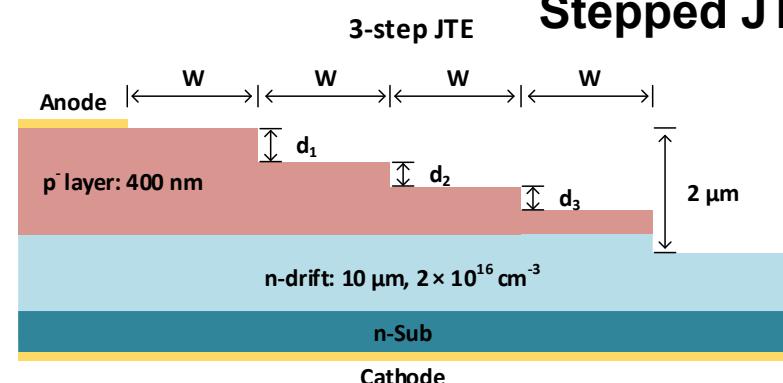

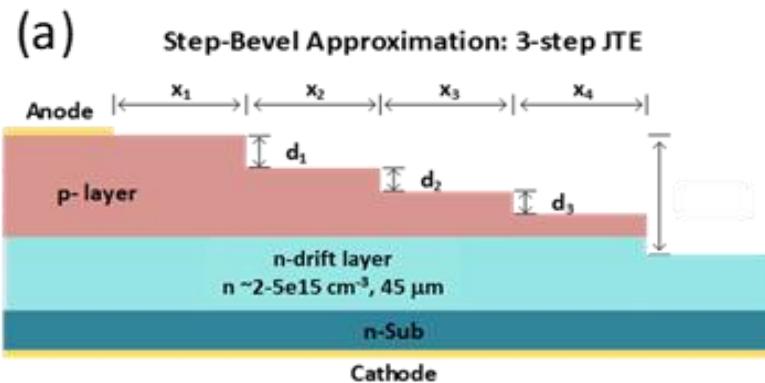

# Junction Termination Extension

## Stepped JTE

K. Zeng

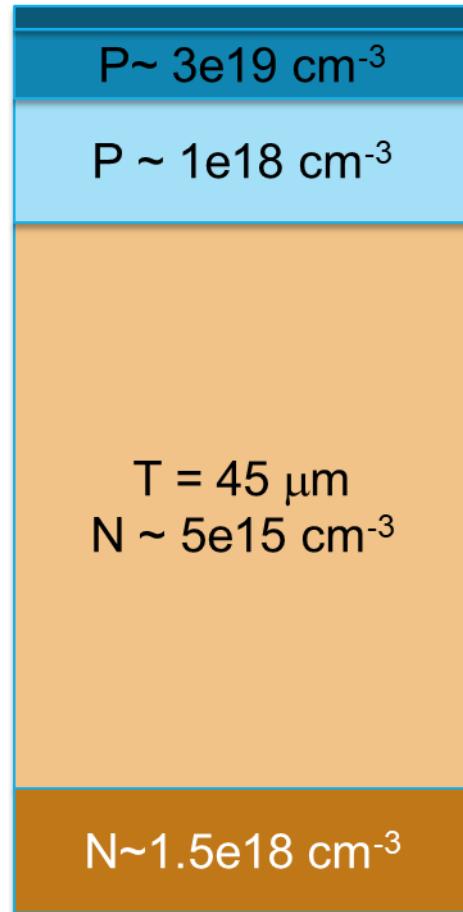

# Fabrication of PN Diodes with Thick Drift Regions

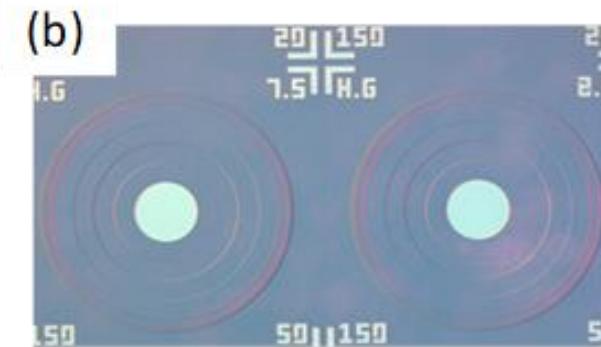

**C-V mapping confirmed highest reverse breakdown voltage devices from regions of wafer with drift region carrier density  $\sim 2.2\text{-}3.0 \times 10^{15} \text{ cm}^{-3}$**

## Edge termination: Multi-step ICP-etched JTE

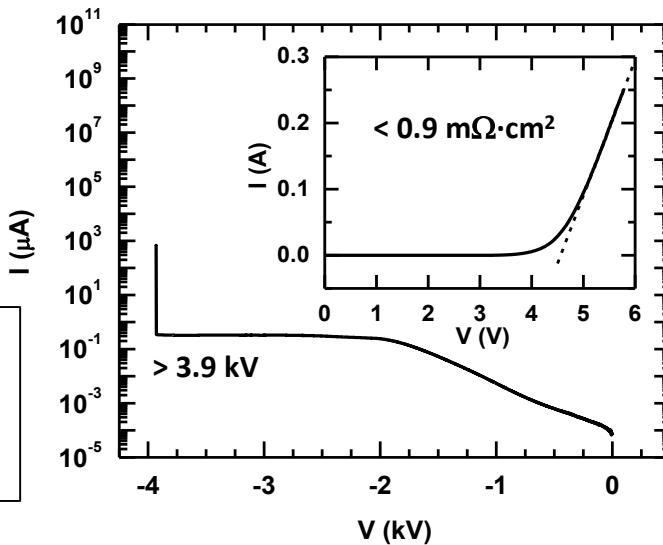

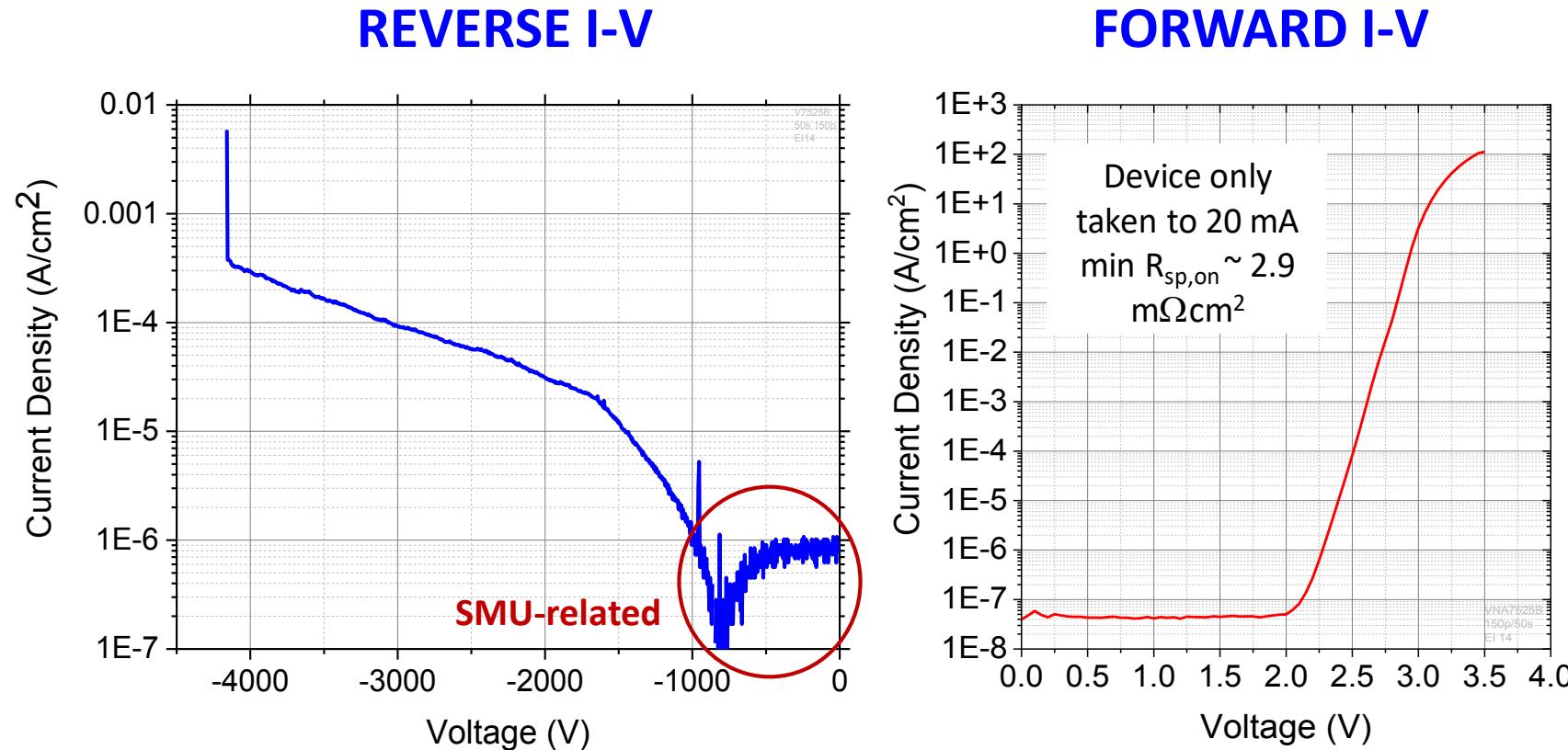

# Performance of Medium-Voltage GaN Diodes

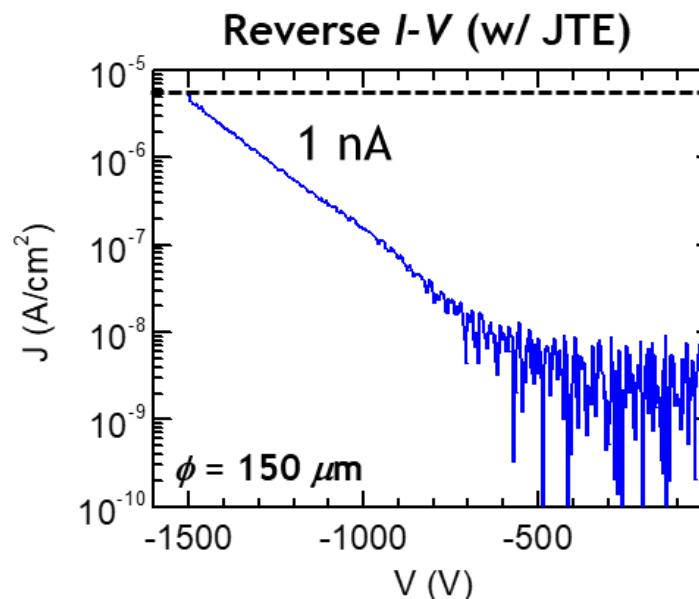

- Best devices  $> 4$  kV; estimate  $\sim 70\%$   $V_B$  of ideal planar diode

- Less than  $1$  mA/cm $^2$  leakage @  $80\%$   $V_B$  target

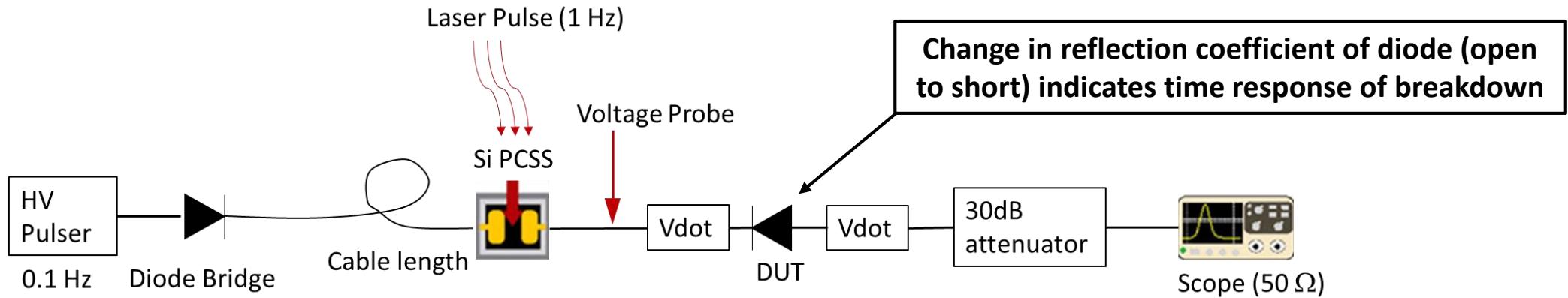

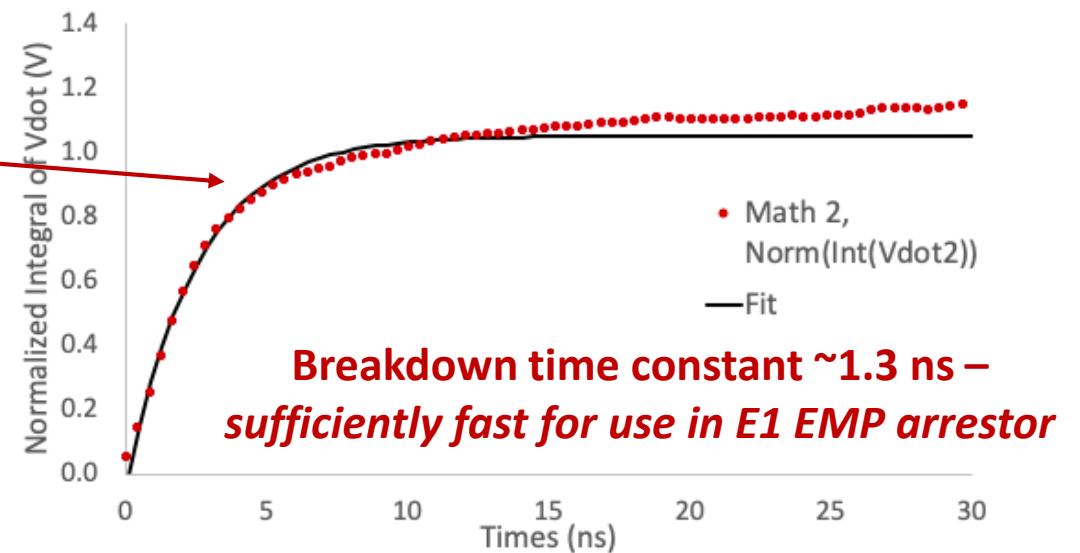

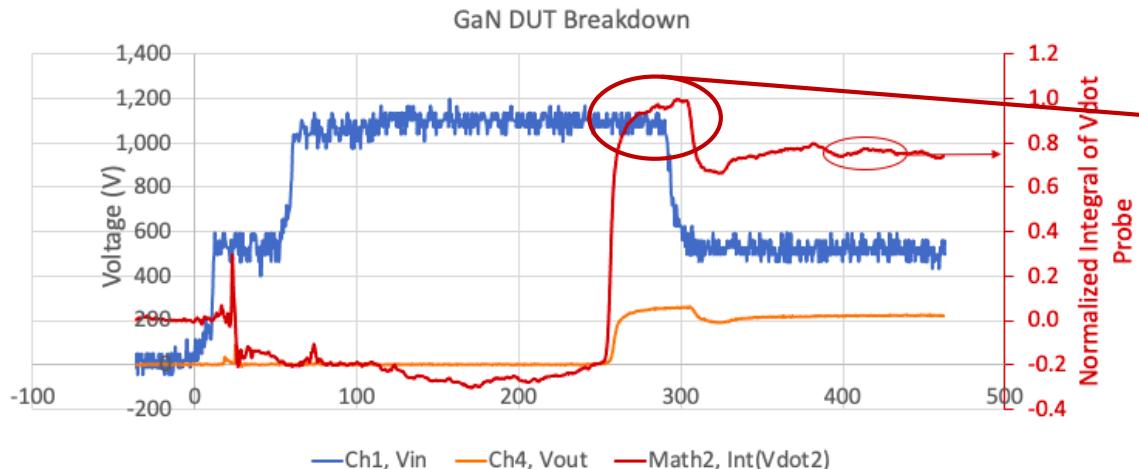

# Time Response of GaN Avalanche Breakdown

Tested 1.2 kV vertical GaN diode

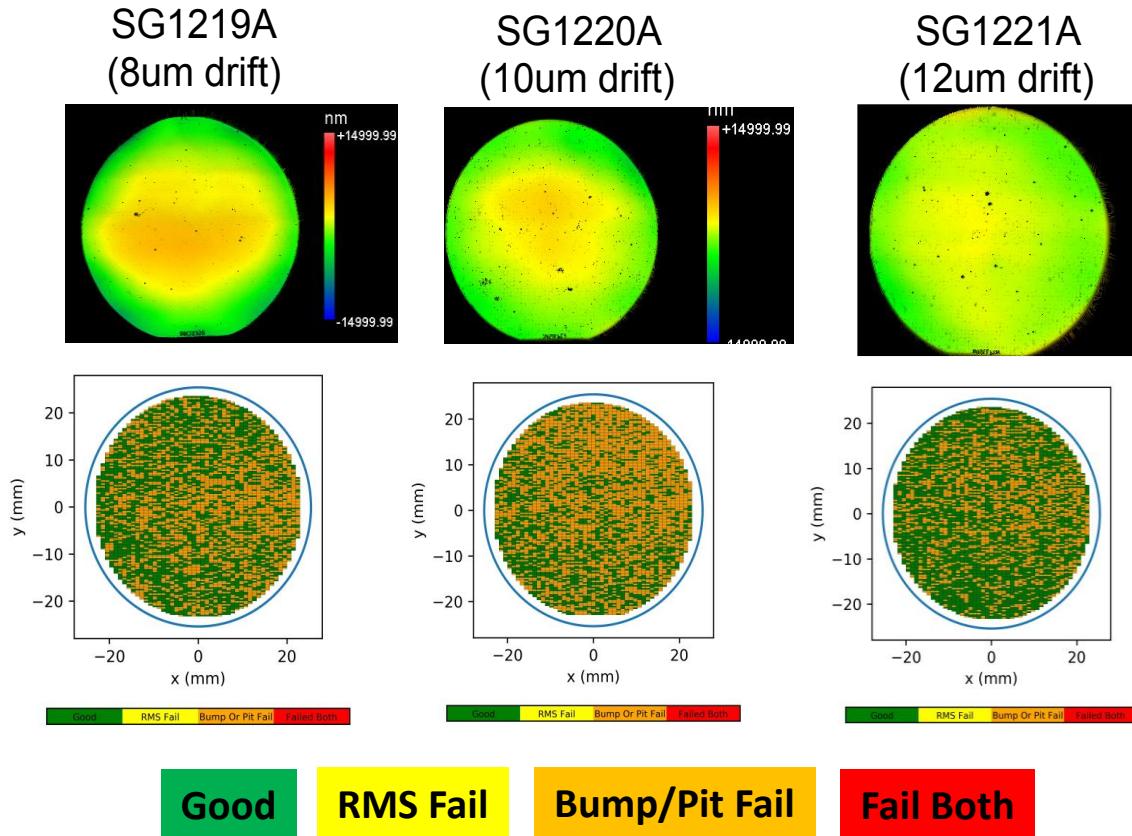

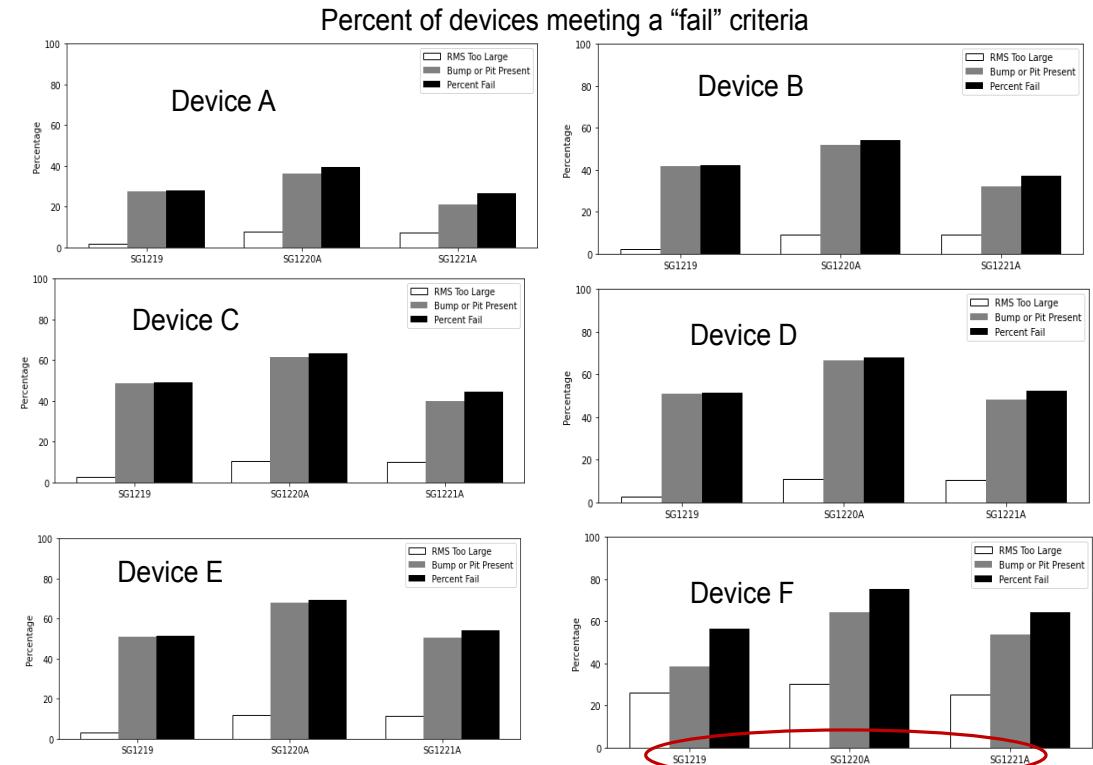

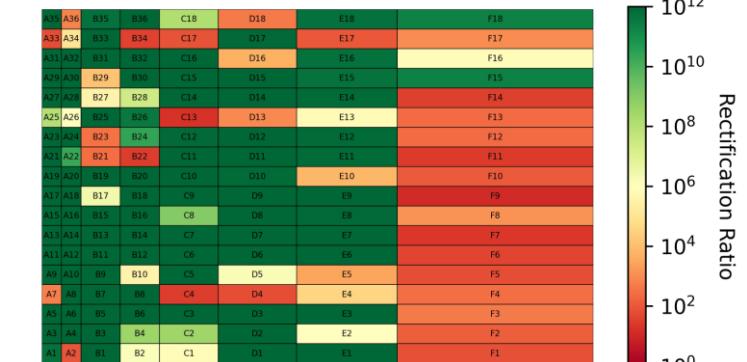

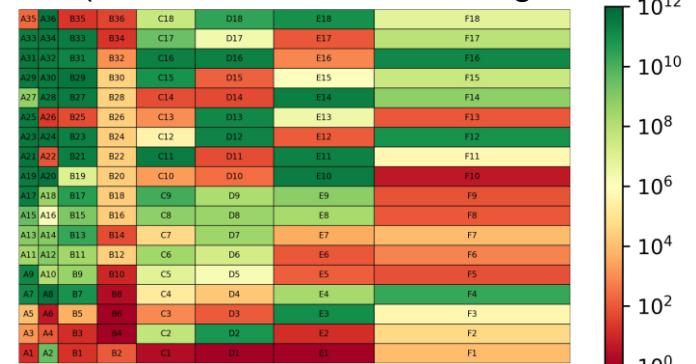

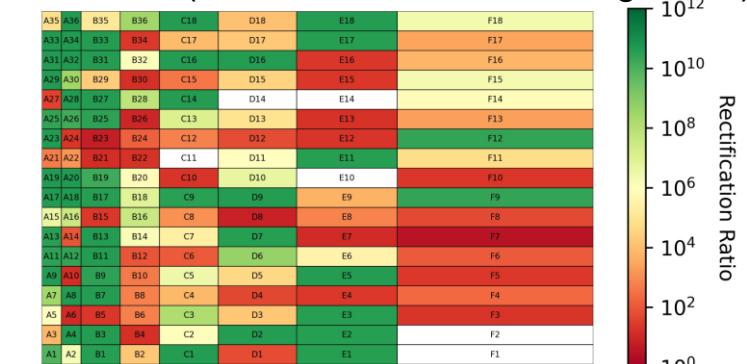

# Vertical GaN Foundry Wafer Metrology

- Evaluate yield based on particles/pits and RMS roughness

- No clear trend in RMS roughness with drift layer thickness

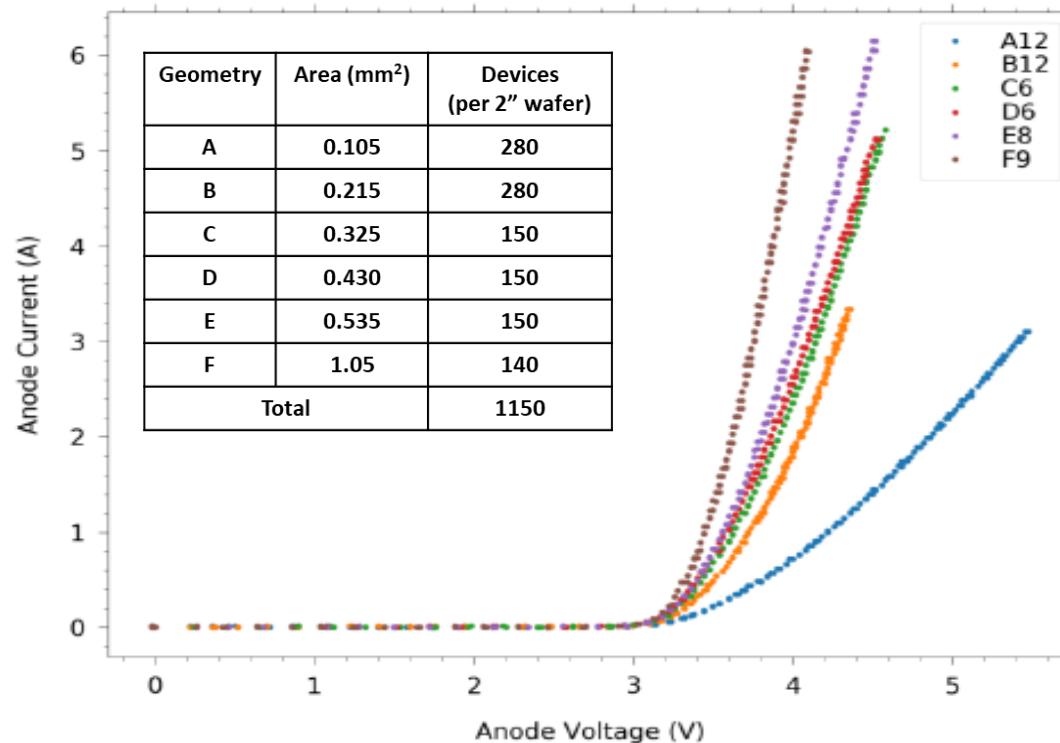

- Evaluating yield for device geometries A-F

| Geometry | Area (mm <sup>2</sup> ) | Devices (per 2" wafer) |

|----------|-------------------------|------------------------|

| A        | 0.105                   | 280                    |

| B        | 0.215                   | 280                    |

| C        | 0.325                   | 150                    |

| D        | 0.430                   | 150                    |

| E        | 0.535                   | 150                    |

| F        | 1.05                    | 140                    |

| Total    |                         | 1150                   |

Three wafers

T. Anderson, NRL

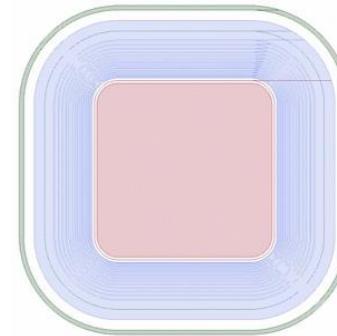

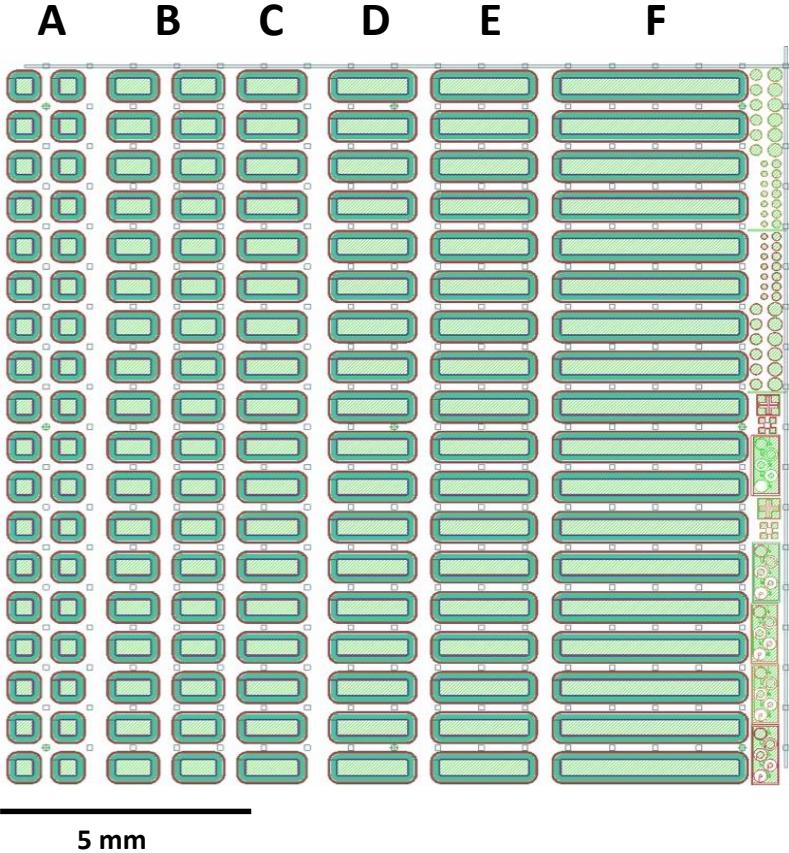

# Foundry Mask Layout

**Base cell:**

$0.35 \times 0.35 \text{ mm}^2$  anode

Larger devices scaled

only in x-direction to

avoid crossing dot-

cores (for now)

| Geometry     | Area (mm <sup>2</sup> ) | Devices (per 2" wafer) |

|--------------|-------------------------|------------------------|

| A            | 0.105                   | 280                    |

| B            | 0.215                   | 280                    |

| C            | 0.325                   | 150                    |

| D            | 0.430                   | 150                    |

| E            | 0.535                   | 150                    |

| F            | 1.05                    | 140                    |

| <b>Total</b> |                         | <b>1150</b>            |

## Features:

- Global alignment

- P-GaN ohmic CTLM

- P-GaN Hall

- Isolation test

- Termination test

- Small diameter circular diodes

- JTE and GR termination designs

- Passivation / overlay for packaging

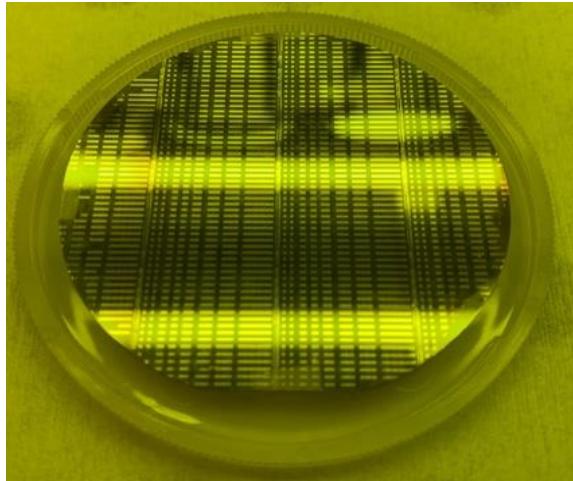

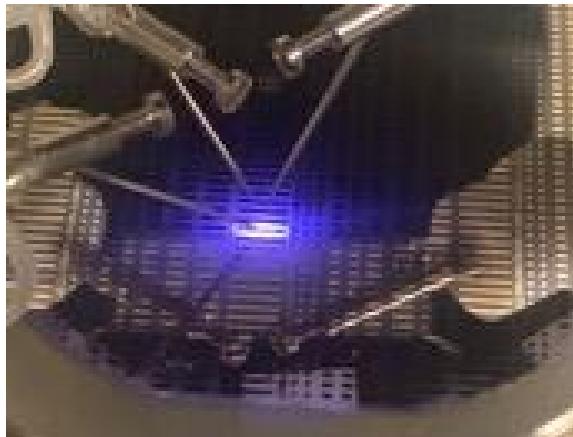

# Foundry Electrical Testing

Typical

foundry

wafer

Wafer

under

test

- Representative forward I-V curves for device types A-F

- Largest devices achieve ~6 A forward current

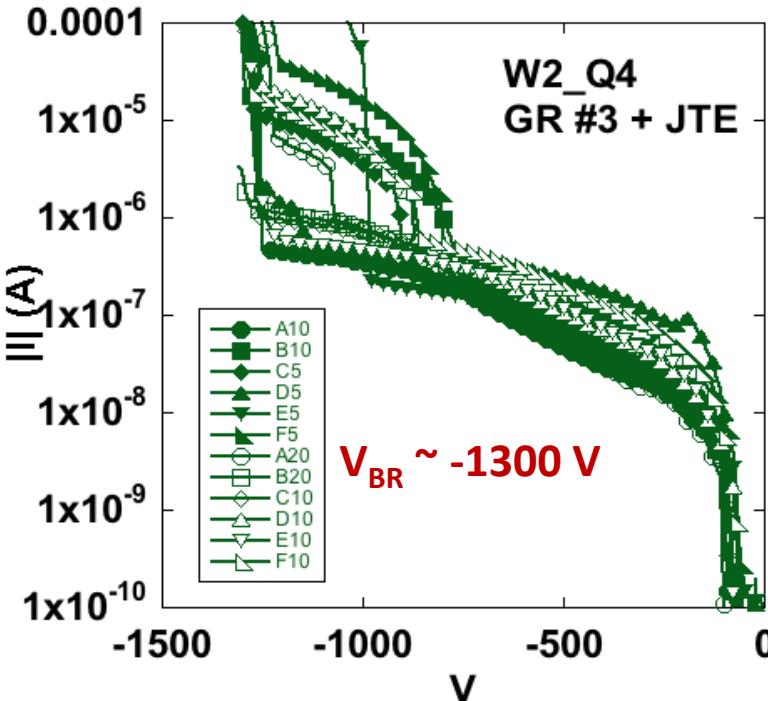

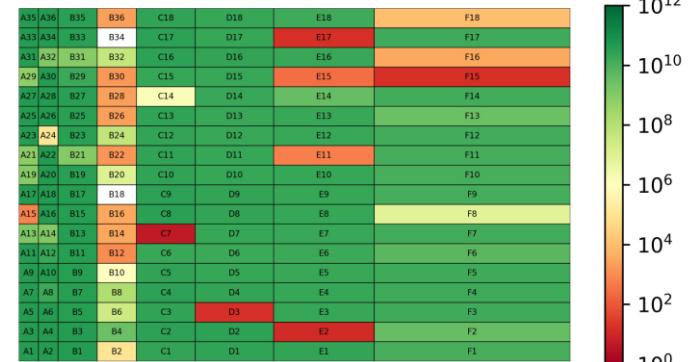

# Foundry Yield Analysis

- Multiple devices achieve breakdown  $>1.3$  kV, which is  $\sim 90\%$  of the parallel-plane value

NL2-W1 (base structure, aligned to dot-core)

NL2-W2 (base structure, random alignment)

NL2-W3 (300nm anode, random alignment)

NL2-W4 (400nm anode, random alignment)

- ON/OFF ratio used for preliminary yield analysis – captures both devices that don't turn on OR don't turn off

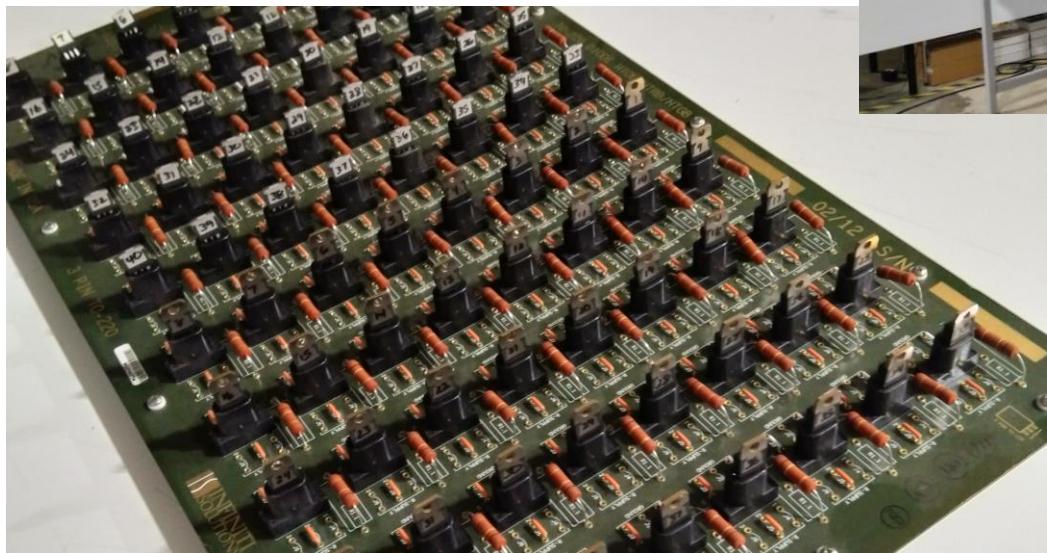

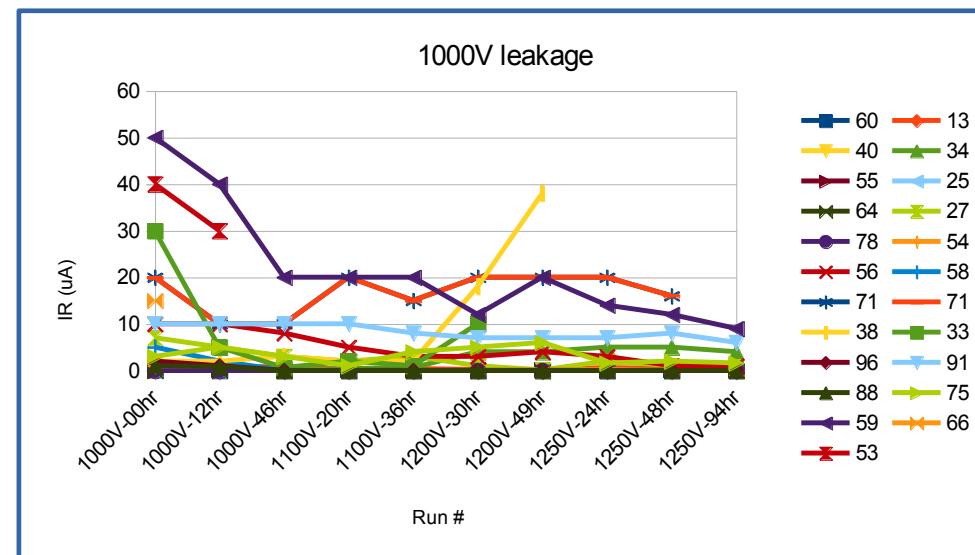

# Reliability and Failure Analysis

- Extensive vertical GaN reliability and FA effort ongoing

Reliability test ovens and power supplies

Reliability test board

Failure Analysis: Emission Microscopy (EMMI)

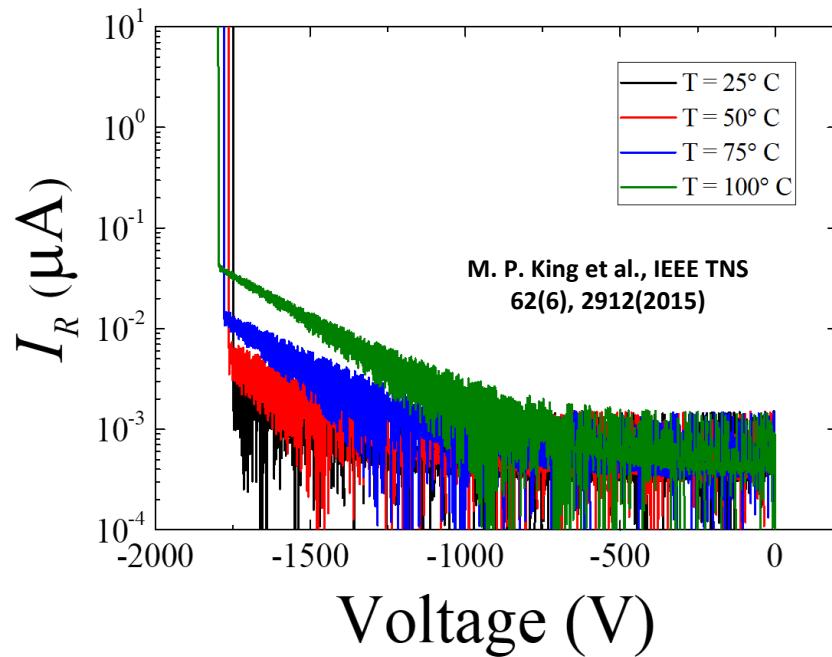

High Temperature Reverse Bias leakage current data

- Overview of WBG Power Electronics

- Medium-Voltage Vertical GaN Devices

- PN Diodes

- Vertical GaN Devices for Electric Vehicles

- JBS Diodes and MOSFETs

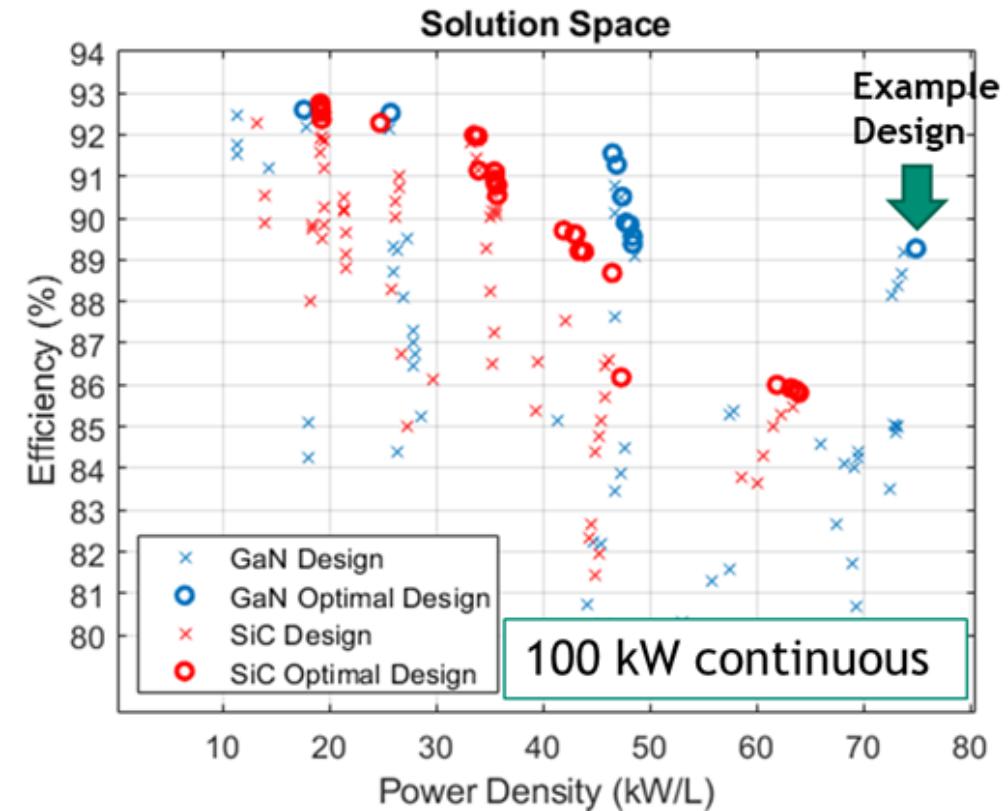

# DOE Targets for Electric Vehicle Drivetrains

- The Department of Energy has partnered with several automotive and energy companies to create a tentative roadmap for improvements to electric vehicle drives.

- “... EETT has a 2025 power density research target of **33 kW/L for a 100 kW peak system**. While achieving this target will require transformational technology changes to current materials and processes, it is essential for enabling widespread electrification across all light-duty vehicle platforms.”

- 33 kW/L target is for motor plus power electronic drive; PE target is 100 kW/L for 100 kW system

- Reliability and cost targets are also specified

For more information about U.S. DRIVE, please see the U.S. DRIVE Partnership Plan at [www.vehicles.energy.gov/about/partnerships/usdrive.html](http://www.vehicles.energy.gov/about/partnerships/usdrive.html)

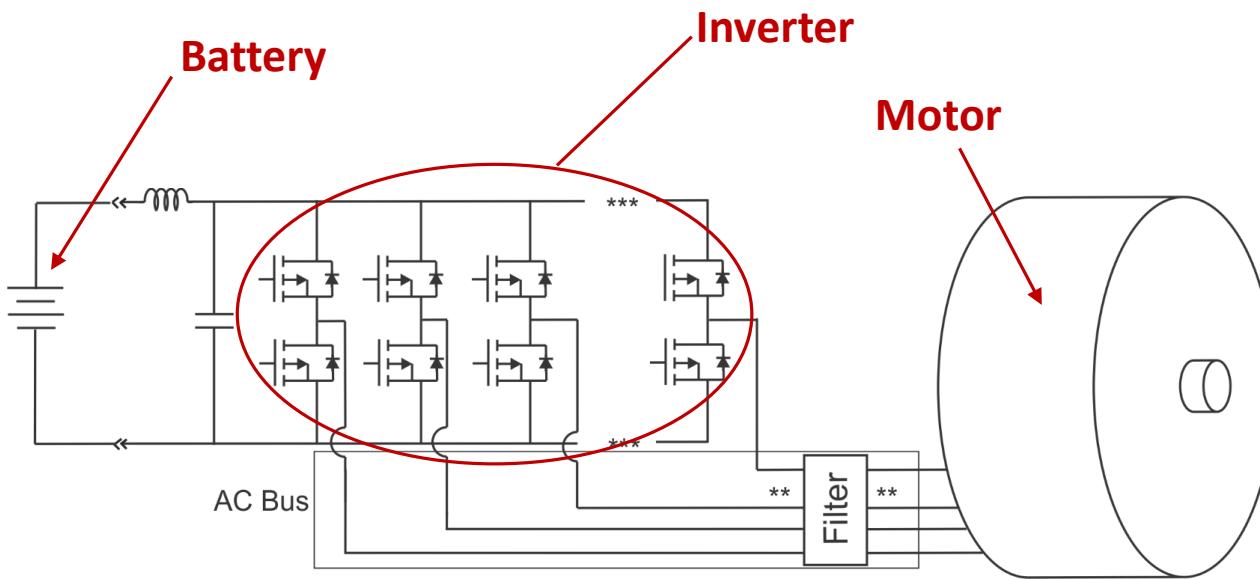

# Advantages of Vertical GaN for Electric Vehicles

## Electric Drivetrain Schematic

- Inverter and optional boost converter require switch-diode pairs (typical for switch-mode power conversion circuits)

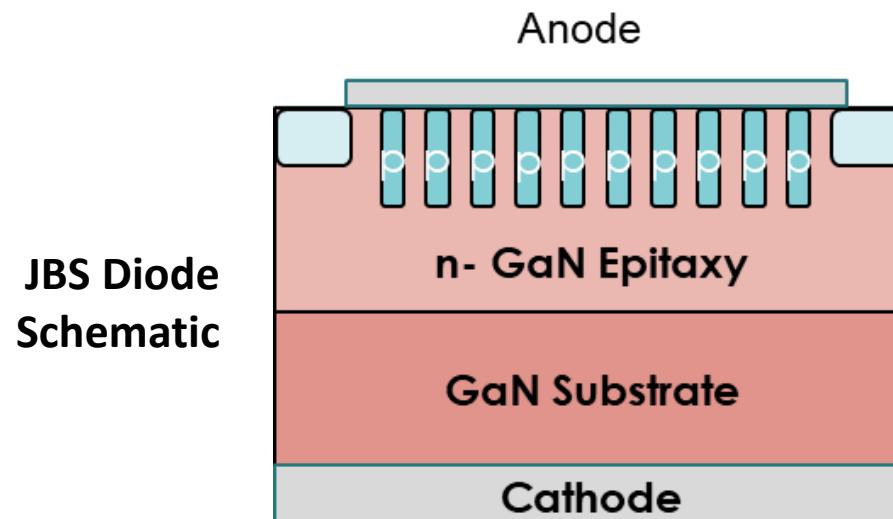

- MOSFET and JBS diode are likely good choices (JBS diode combines best properties of Schottky and PN diodes)

- System-level genetic optimization indicates that vertical GaN diodes may out-perform SiC in terms of efficiency and power density

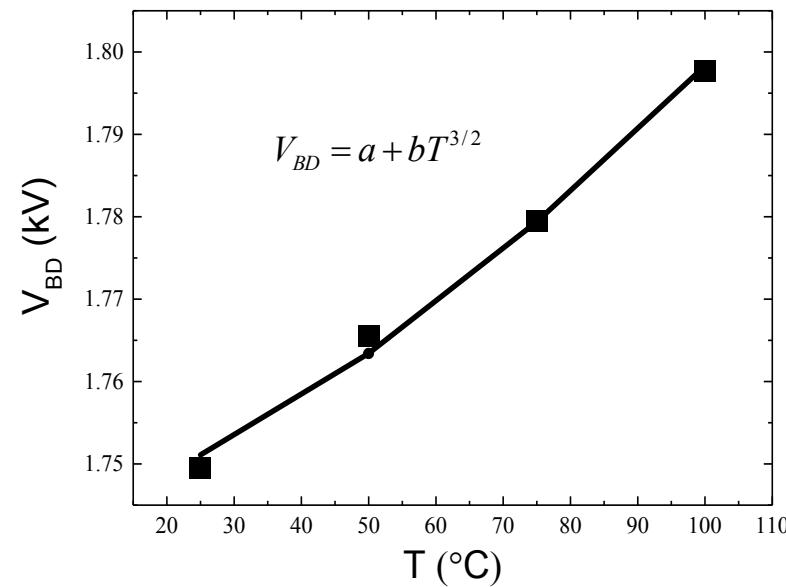

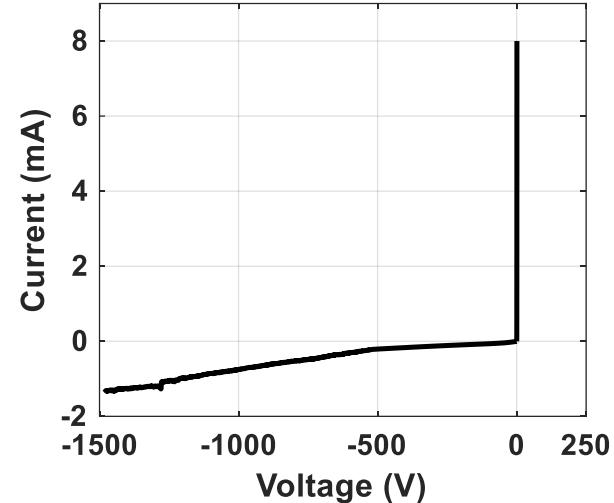

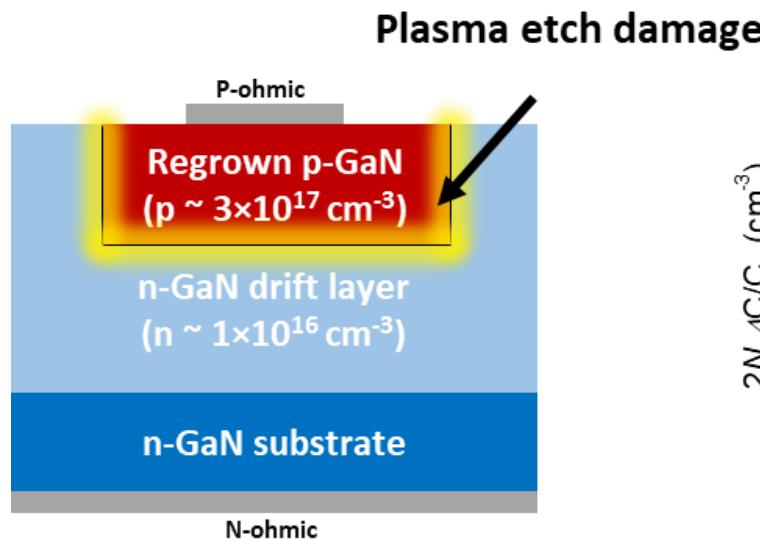

# Vertical GaN JBS Diode Development

## Fabrication of GaN JBS diodes:

- Etched-and-regrown JBS diode demonstrated

- 1500 V reverse holdoff voltage

## Next Steps:

- Exploring regrowth surface pre-treatment strategies to reduce current leakage

- Added JTE to aid in field management and improve reverse breakdown

IV curve for gen 1

GaN JBS diode

- Low turn-on voltage (consistent with Schottky)

- Low leakage current (consistent with PN junction)

- Confirms JBS operation

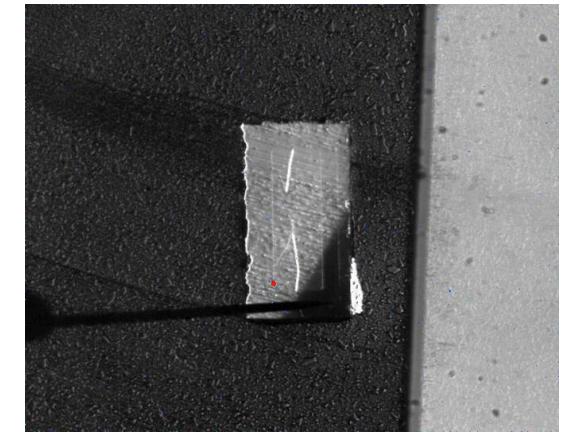

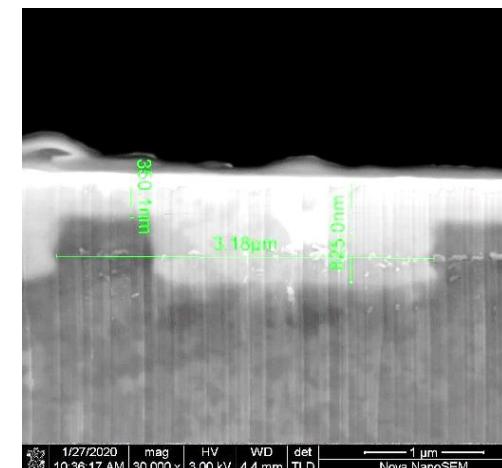

Cross-Sectional

SEM of

Regrown PN

Junction

# Etch and Regrowth Needed for JBS Diodes

**arpa-e**

CHANGING WHAT'S POSSIBLE

**PNDIODES**

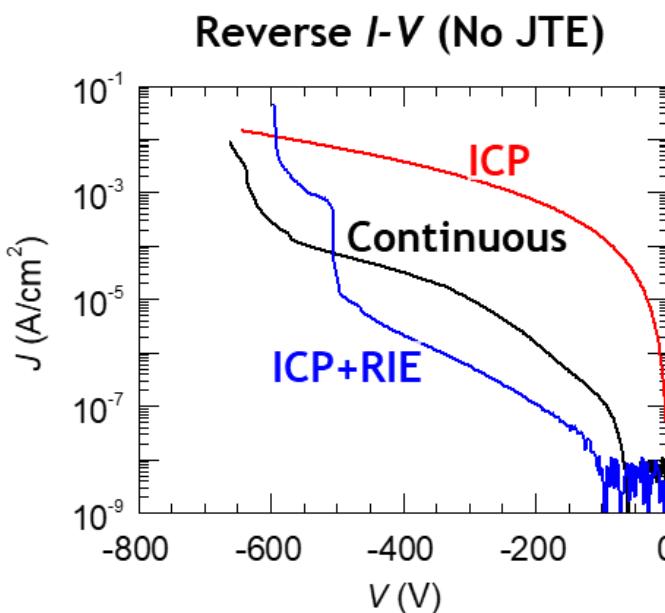

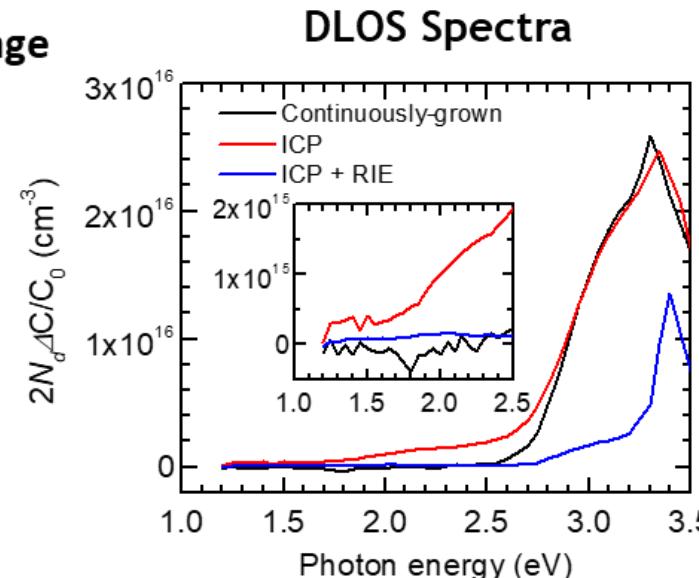

- Correlated  $E_c$  – 1.9 eV deep level with plasma damage and leakage

- Removed plasma damage with post-ICP RIE step

- Achieved etched-and-regrown diode  $> 1.5 \text{ kV}$  and  $1.4 \text{ m}\Omega\text{.cm}^2$

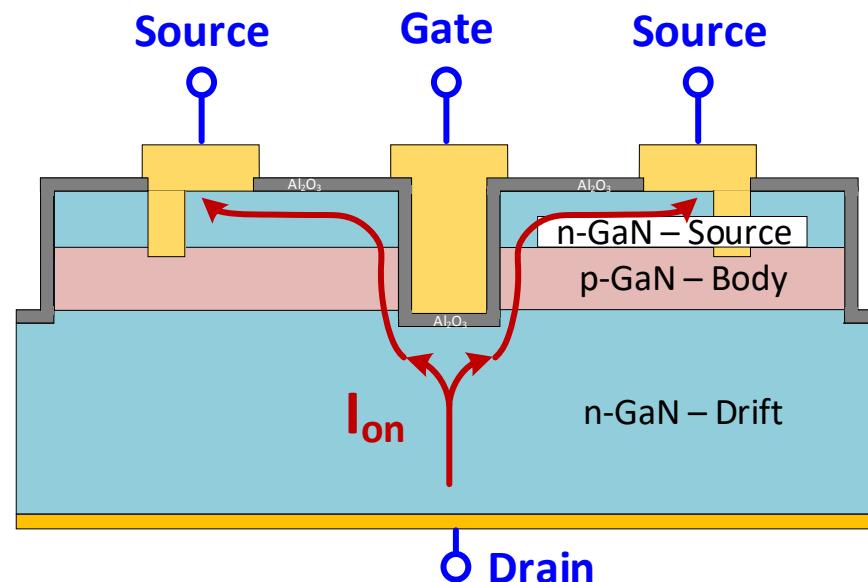

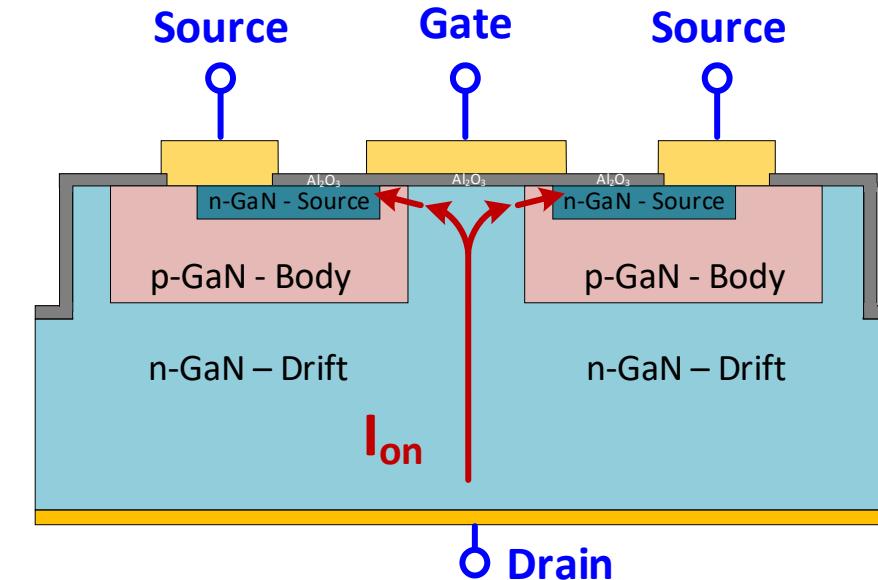

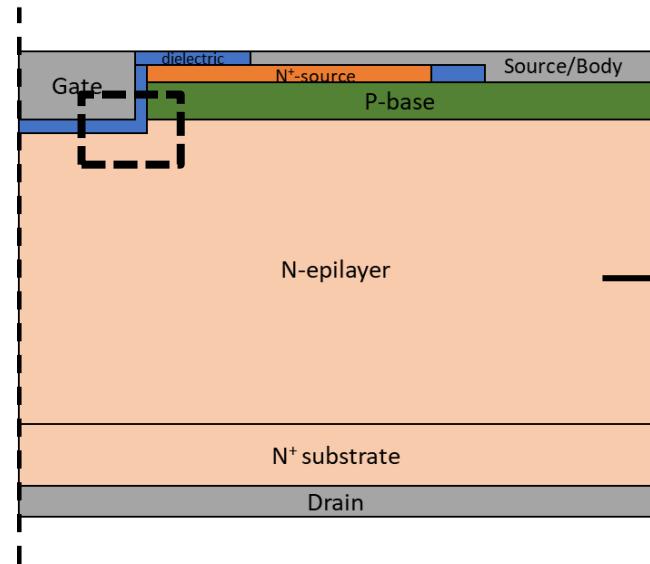

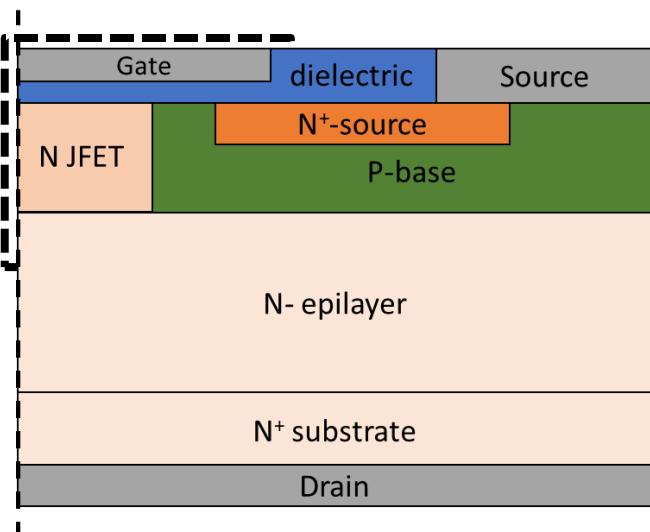

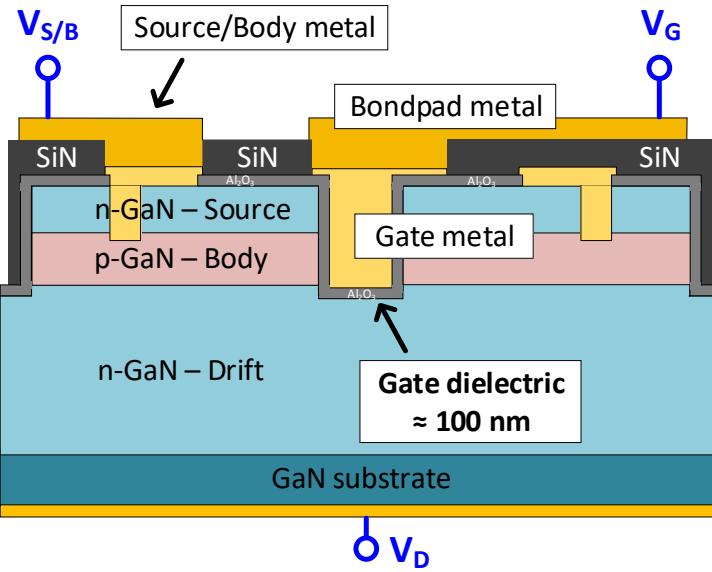

# Vertical GaN MOSFET Development

## Trench MOSFET key features:

- Selective-area doping not needed for body and source

- Gate on vertical etched GaN sidewall

- High fields at bottom trench corner

## Double-well MOSFET key features:

- Selective-area doping required for body and source

- Gate on planar top surface

- JFET region engineering critical

Trench MOSFET

Double-well MOSFET

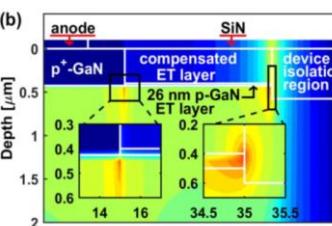

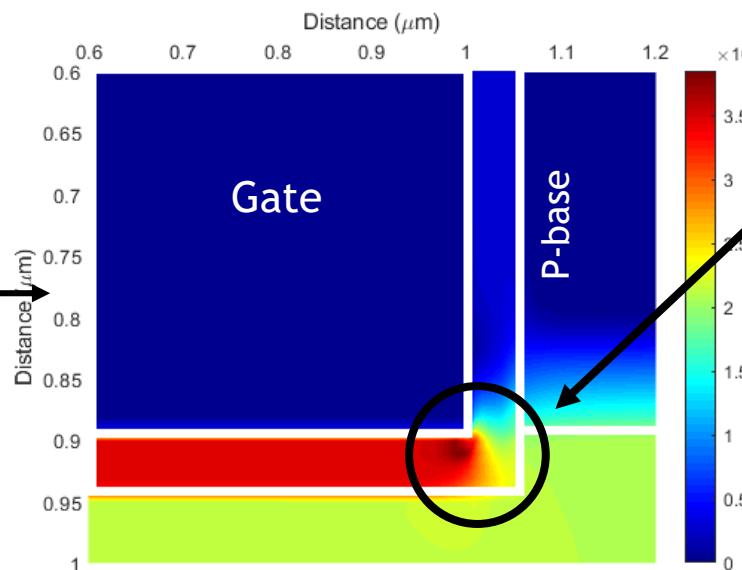

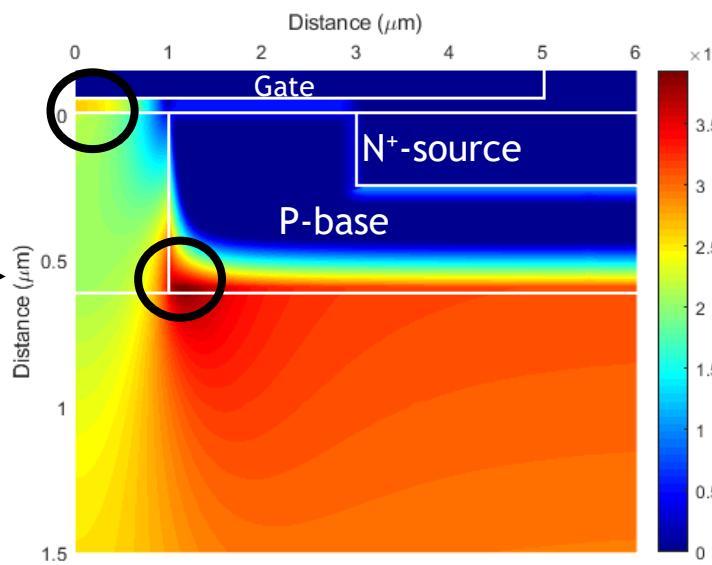

# TCAD Simulation of T-MOSFET and D-MOSFET

Field crowding at the corner of the gate elevates electric field in dielectric

Electric field taken at  $V_g=0$  and  $V_{DS}=1200$  V

- Large electric field occurs in GaN at corner of JFET region

- Largest dielectric E-field occurs under center of gate

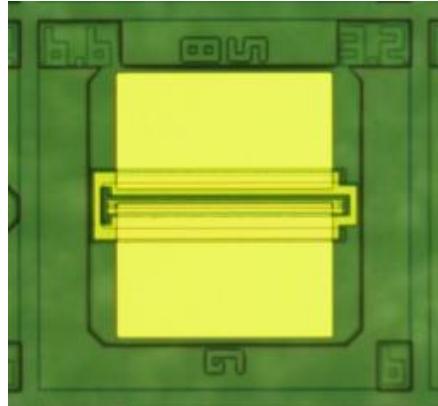

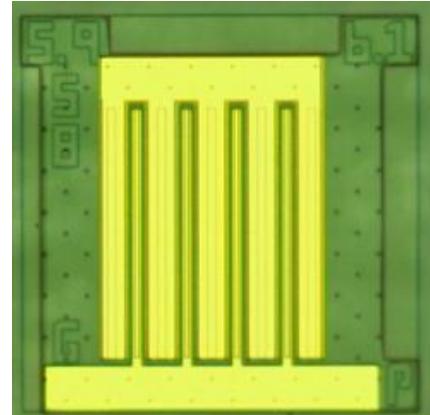

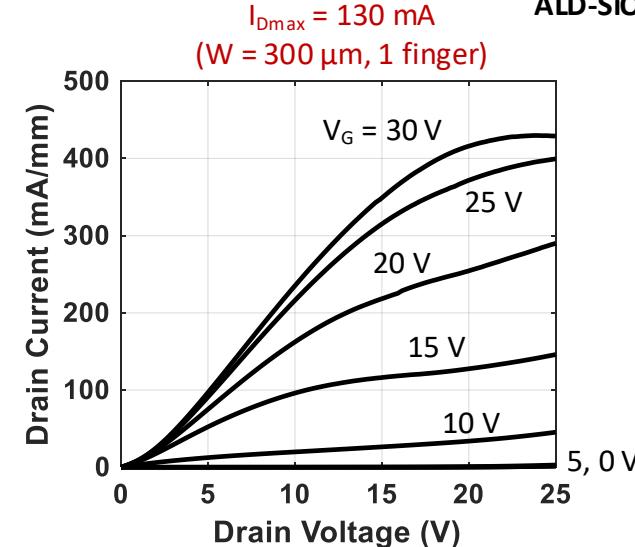

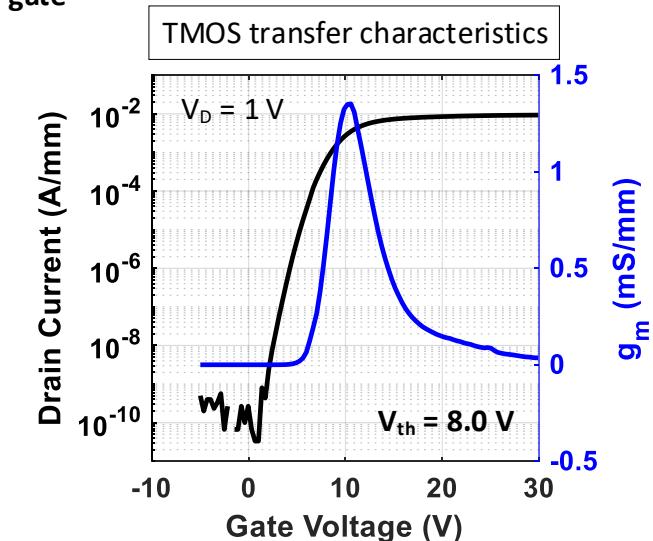

# Initial Trench MOSFET Electrical Data

T-MOSFET Diagram

Single-finger

Four-finger

- T-MOSFETs demonstrated

- Devices have a good on/off ratio,  $\sim 10^8$

- Positive threshold voltage:  $\sim 8$  V

- Current density  $\sim 400$  mA/mm achieved

- Single-finger and four-finger devices fabricated

Lot 5: Single Finger MOSFET

ALD-SiO<sub>2</sub> gate

VNA7682C-D: 6.5-4.4

- Overview of WBG Power Electronics

- Medium-Voltage Vertical GaN Devices

- PN Diodes

- Vertical GaN Devices for Electric Vehicles

- JBS Diodes and MOSFETs

Questions?

Bob Kaplar: [rjkapla@sandia.gov](mailto:rjkapla@sandia.gov)