Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell structures and technology innovations

Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

**Project Title:** Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell structures and technology innovations

**Project Period:** 08/1/2016 – 7/1/2020 (NCE till 1/31/2020)

**Project Budget:** \$1,58,3333

**Submission Date:** 05/07/21

**Recipient:** Georgia Tech Research Corporation

**Address:** 505 Tenth St. NW

Atlanta, GA 30332-0240

**Award Number:** DE-EE0007554

**Project Team:** Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

**Contacts:**

Ajeet Rohatgi

Regents' Professor/UCEP

Director Phone: 404-894-7692

Fax: 404-894-5934

Email: [ajeet.rohatgi@ece.gatech.edu](mailto:ajeet.rohatgi@ece.gatech.edu)

**GIT Team:**

Young Woo Ok, Ajay Upadhyaya, Vijay Upadhyaya, Brian, Rounsville, Ying-Yuan Huang, Keeya Madani, Wookjin Choi.

**Acknowledgment:**

"This material is based upon work supported by the Department of Energy, Office of Energy Efficiency and Renewable Energy (EERE), under Award Number DE-EE0007554"

**Disclaimer:**

"This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof."

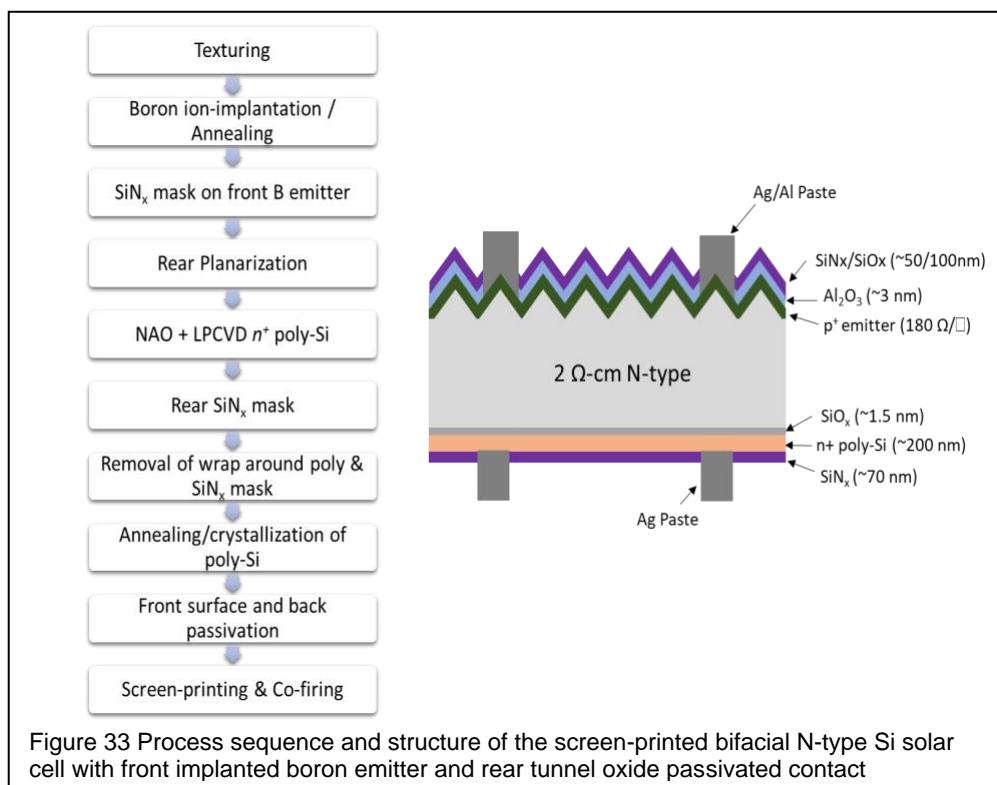

**Executive Summary:** The overall objective of this program is to achieve ~23% bifacial n-type cell efficiencies by developing and implementing optimized homogeneous or selective boron (B) emitter on front and tunnel oxide passivated contact (TOPCon) on rear side, in combination with advanced fine-line screen-printing metallization with floating busbars. During this research project, first we developed a technology roadmap to drive the 21% n-PERT cell efficiency from 21% to 23% by transforming the cell design to n-TOPCon and establishing the requirements for each layer, including B emitter, rear n-TOPCon, n-base Si and screen-printed contacts. Next, consistent with our roadmap, we developed advanced homogeneous implanted B emitter ( $150-180 \Omega/\square$ ) passivated with ALD  $\text{Al}_2\text{O}_3$  layer capped with PECVD  $\text{SiN}_x/\text{SiO}_x$  double-layer antireflection coating. This gave a very low recombination current density of  $10-15 \text{ fA/cm}^2$  prior to metallization. In addition, we demonstrated metallized recombination current density of  $\sim 31 \text{ fA/cm}^2$  for this advanced homogeneous B emitter with industrial screen-printed, fire-through contacts with  $40 \mu\text{m}$  wide grid lines, floating busbars and implementation of an advanced Ag-Al paste which resulted in local or reduced area metal-Si contact under the grid lines with virtually no emitter surface etching. This paste reduced the full area metallized  $J_{oe,metal}$  from  $>1100 \text{ fA/cm}^2$  to  $\sim 700 \text{ fA/cm}^2$ . We also developed novel processes for the formation of  $p^+/p^{++}$  selective B emitter by a) single B diffusion with selective etch back and b) two-steps diffusion with implanted B in field region and APCVD B diffusion under the metal grid. We achieved very low un-metallized recombination current density ( $J_0$ ) of  $\sim 18 \text{ fA/cm}^2$  for the selective  $p^{++}p^+$  emitters ( $30/150 \Omega/\square$ ) and metallized  $J_0$  of  $\sim 28 \text{ fA/cm}^2$  with  $\sim 3\%$  screen-printed metal contact to  $p^{++}$  regions. Next, we developed the technology for n-TOPCon by growing phosphorus-doped LPCVD and PECVD poly-Si on top of  $\sim 15\text{\AA}$  chemically grown (NAO) tunnel oxide. After an optimized anneal at  $875^\circ\text{C}$  for 30 min, passivated n-TOPCon have unmetallized  $J_0$  of  $\sim 5 \text{ fA/cm}^2$  which went down further to  $\sim 1 \text{ fA/cm}^2$  after a  $700 \text{ \AA}$   $\text{SiN}_x$  capping layer and simulated contact firing cycle at  $770^\circ\text{C}$ . After screen-printed fire-through metallization on this n-TOPCon with  $\sim 13\%$  metal coverage, metallized  $J_0$  value increased to only  $\sim 5 \text{ fA/cm}^2$  which is among the lowest reported value to the best of our knowledge for screen-printed metallization. Finally, we integrated all the above technology innovations and enhancements and demonstrated low-cost manufacturable screen-printed n-TOPCon bifacial Si solar cell with  $\sim 23\%$  efficiencies.

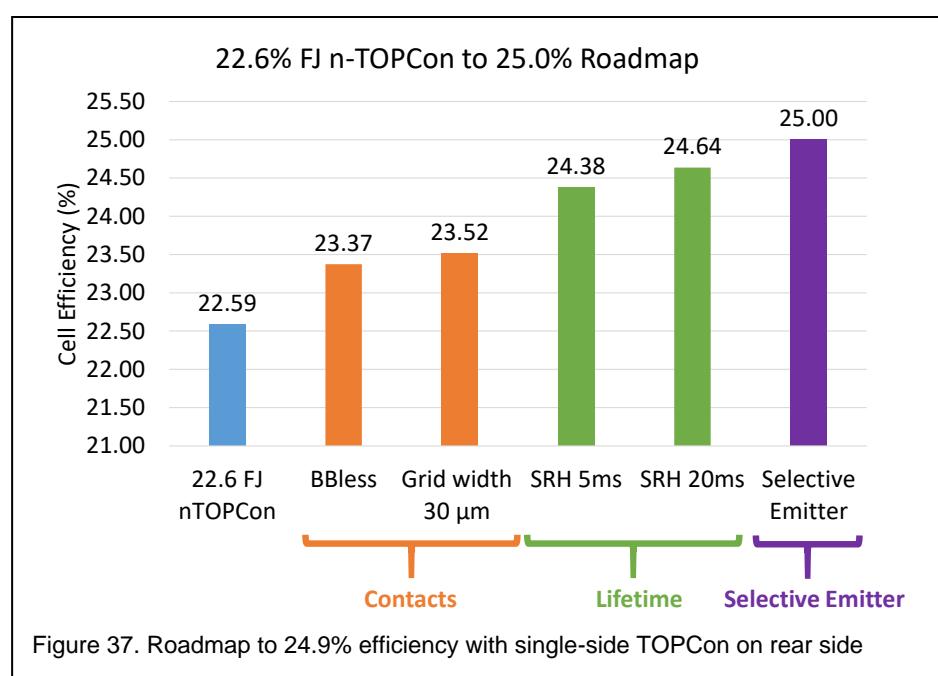

Based on the experimental and theoretical understanding developed in this project, we have developed a new technology roadmap that shows that implementation of busbarless contacts, 10-20 ms bulk lifetime Si, and selective B emitter or selective TOPCon on the front can drive  $\sim 23\%$  efficient cells achieved in this research to  $\sim 25\%$  at low-cost.

## Table of Contents

### Background

### Introduction

### Project Results and Discussion (each task)

### Conclusion

**Background:** Si solar cell is the dominant PV technology with a market share >90%. Therefore, it is critical to address the key issues facing Si PV to attain the DOE long-term goals. It is estimated that the Si modules need to be 23-25% efficient in combination with low manufacturing cost ( $\leq \$25/W$ ) to achieve \$2-3/kWh long-term DOE target. To produce modules with such high efficiency and low cost, development and adoption of improved cell designs, technology innovations with high-throughput and reliable fabrication methods, and enhanced materials are crucial. These challenges are addressed in this project.

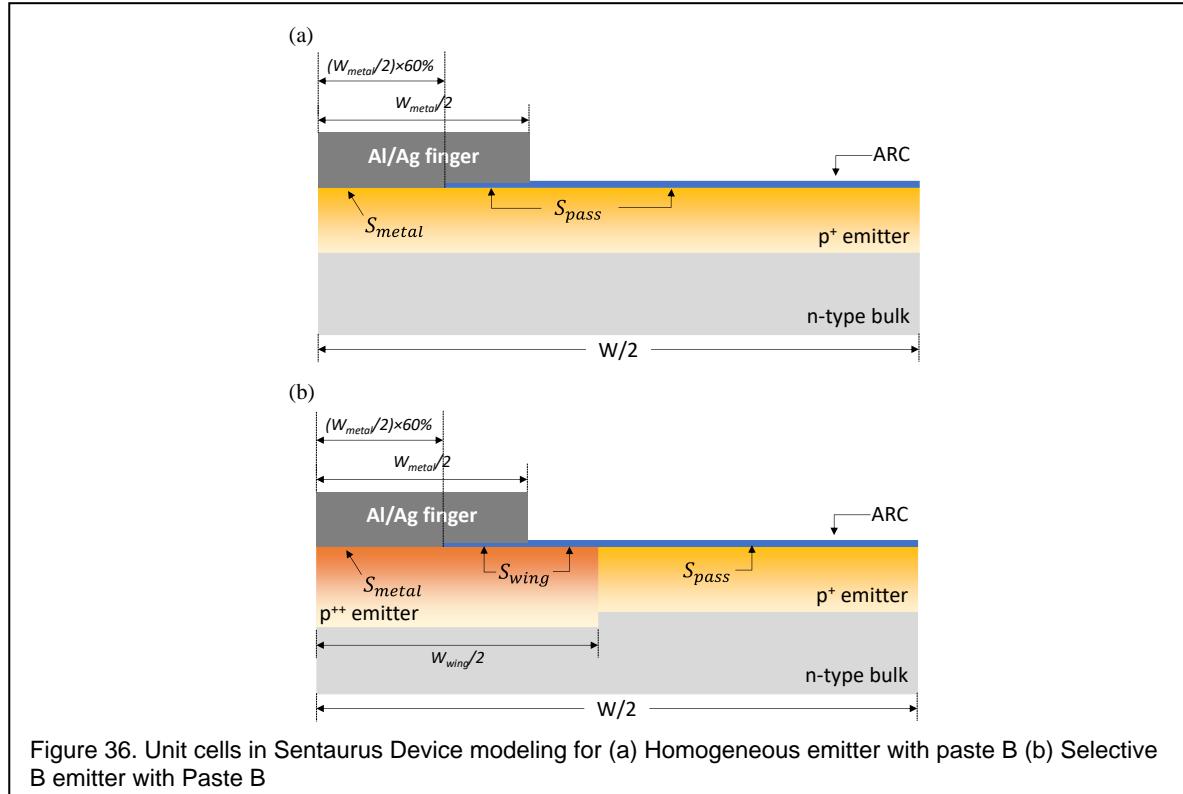

It is widely accepted that poly-Si based passivated contacts cells, also known as tunnel oxide passivated contact (TOPCon) cells, serve as newly emerging generation of advanced crystalline Si solar cells and have the potential to replace conventional full Al back and passivated emitter and rear cell (PERC) technology which currently dominates the photovoltaics (PV) industry [1]. Several groups have reported efficiencies approaching and exceeding 25% on laboratory-scale cells that employ FZ-Si and single side poly-Si based passivated contacts using non-commercial methods for front and/or back metallization [2, 3]. Poly-Si based passivated contact technology offers an ingenious solution to reducing diffusion- and metal-Si contact-induced recombination losses in bulk Si, therefore, it has primarily been confined to the rear of the cell because of high parasitic absorption losses in poly-Si [4]. An n-type TOPCon (n-TOPCon) is composed of a very thin tunnel oxide ( $\text{SiO}_x$ ) capped with phosphorus-doped  $n^+$  poly-Si. However, to adapt TOPCon technology for industrial production of large-area Si solar cells, several challenges need to be overcome, including development of tunnel oxide, screen-printing induced shunting and degradation of  $J_0$  of n-TOPCon, parasitic absorption in the doped poly-Si, single-side deposition of poly-Si, and throughput [5]. The poly-Si thickness needs to be adequate to prevent the penetration of the fire-through metal paste into the thin oxide and oxide/Si interface. This is essential for achieving the lowest metallized  $J_0$  for the TOPCon layer. With development of very low  $J_0$  n-TOPCon, the recombination current densities in the bulk Si and passivated and metallized regions of B emitter are expected to become the limiting factor for higher efficiency single-side n-TOPCon cells. Therefore, higher bulk lifetime Si and carefully designed homogeneous B emitter with advanced screen-printed metallization or a selective B emitter ( $p^{++}/p^+$ ) where highly-doped areas beneath the metal contacts reduce  $J_{0,\text{metal}}$  passivated in between provide lower  $J_{0,\text{pass}}$  due to lower doping, better surface passivation, reduced heavy doping effects. However, selective B emitter adds cost and process complexity that may negate the benefit of efficiency enhancement for industrial solar cells. Metallized  $J_0$  can also be reduced by fine-line printing with floating busbars and by utilizing the paste and firing schemes that can give local area contacts under the grid without etching into the emitter. All these concepts are investigated and implemented in this research.

At the start of this program, we developed Sentaurus and Quakka 2D modeling capabilities and established a technology roadmap to ~23% efficiency n-TOPCon cell structure with quantitative requirements and metrics for each layer. Next, we developed individual technology enhancement features, such as low  $J_{0b}$  poly-Si/ $\text{SiO}_2$  (n-TOPCon), homogeneous and selective B emitters with low metallized  $J_{0e}$ , high bulk lifetime in Si, cofiring of screen-printed fire-through contacts to n-TOPCon and B emitter to minimize degradation in  $J_0$  without compromising contact quality. We also investigated advanced screen printing with finer gridlines in combination with floating busbars as well as laser-

induced opening of grid pattern in combination with plating to reduce shading and metal-Si contact area fraction. Finally, we developed a process sequence by integrating all the best technologies developed in this program and demonstrated manufacturable large area high-efficiency (~23%) fully screen-printed bifacial n-type solar cells. Based on the experimental and theoretical understanding developed in this program, we developed a new technology roadmap to ~25% efficiency TOPCon cells through device modeling.

**Introduction:** Efficiency of current front junction *n*-type silicon solar cells is largely limited by the recombination in the heavily doped regions in the absorber and at the metal/silicon contacts. Carrier selective passivated contacts are a promising candidate for next-generation high-efficiency Si solar cells because they can eliminate high recombination at the metal/Si contacts and bypass the need for heavily diffused regions inside the absorber. In traditional cells, diffused and metallized regions in the absorber are utilized for separation, collection, and extraction of light-generated carriers in the absorber. Carrier selective passivating contacts provide an opportunity to displace these regions outside the absorber but still utilize their positive attributes. Because of high parasitic absorption in heavily doped poly-Si layers, we used TOPCon only on the rear side in this project and implemented advanced B emitter on the front side to minimize recombination on the front side. We employed ion implantation to form homogeneous as well selective B emitters because, besides time and temperature, it provides additional controls like implantation energy and dose for profile engineering and management. Ion implantation also provides opportunities for higher cell efficiency because of better areal uniformity, more precise control of doping profile, and excellent chemical purity of the beam. In addition to profile optimization and emitter passivation, we investigated different screen-printing metal pastes and firing schemes to minimize  $J_{0e,metal}$ , in conjunction with advanced screen printing with fine grid and floating busbars. A technology roadmap was developed for 23% cells by 2D simulations to guide the development of each layer.

The overall objective of this program is to achieve ~23% bifacial cell efficiencies by implementing optimized homogeneous or selective B emitter and rear side n-TOPCon, in combination with fine-line metallization and floating busbars. At the start of the program, we produced approximately ~21% efficient traditional n-PERT cells with diffused B emitter and P-doped BSF with a total  $J_0$  value of ~315 fA/cm<sup>2</sup>. Next, we developed 2D Sentaurus and Quakka modeling capabilities to develop a technology roadmap which revealed that a total  $J_0$  of less than 50 fA/cm<sup>2</sup> is required to obtain high open-circuit voltages and achieve ~23% efficient cells. The recombination current  $J_0$  has three main components including emitter ( $J_{0e}$ ), bulk ( $J_{0b,bulk}$ ), and n-TOPCon ( $J_{0b'}$ ). Both  $J_{0e}$  and  $J_{0b'}$  are composed of metallized and passivated regions. Through modeling and design we established practically achievable specific targets for metallized  $J_{0e}$  below 25 fA/cm<sup>2</sup> and  $J_{0b'}$  below 5 fA/cm<sup>2</sup>, while maintaining bulk lifetime of >1ms which should reduce  $J_{0b,bulk}$  below 20 fA/cm<sup>2</sup>.

Proposed  $J_0$  and cell efficiency targets were achieved by a combination of fundamental understanding, device modeling, process development and implementation of front B homogeneous as well as selective emitter, rear n-TOPCon and fine-line advanced metallization. The project plan was divided into five tasks: 1) Device modeling to establish a technology roadmap to ~23% n-TOPCon cell including doping profiles and contact requirements. 2) Technology development and formation of advanced

Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell structures and technology innovations

Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

homogeneous and selective B emitters 3) Technology development and formation of low  $J_0$  screen-printed rear n-TOPCon 4) Advanced screen-printed and plated fine line metallization with floating busbars 5) Fabrication and demonstration of ~23% n-TOPCon bifacial cells by integration of advanced technologies.

### TASK #1:

#### TECHNOLOGY ROADMAP DEVELOPMENT INCLUDING DOPING PROFILES, RECOMBINATION CURRENT AND CONTACT OPTIMIZATION BY DEVICE MODELING.

**Task Summary:** In this task, we performed 2D device modeling with Sentaurus and Quokka simulation tools to achieve 23% TOPCon cells through optimization of B emitter, n-TOPCon, and screen-printed contacts. A technology roadmap was developed to quantify the required unmetallized and metallized  $J_0$  values and material parameters in each layer to achieve the target efficiency. This involved theoretical calculations of doping profiles, sheet resistance and contact parameters for lightly and heavily doped regions of the device, Sentaurus Device model was used to first generate  $J_0$  vs SRV curves from the simulated and measured doping profiles. Then, from the knowledge of SRV on top of the doped profiles and at the metal-Si interface ( $\sim 10^7$  cm/s),  $J_0$  contributions from doped and metallized regions were extracted for different profiles, and their sum was used to obtain the metallized  $J_0$  value. We started with the fabrication of 21% n-PERT cell in our lab with total  $J_0$  value of  $\sim 315$  fA/cm<sup>2</sup> and 55  $\mu$ m wide screen-printed lines with bulk lifetime of  $\sim 1$ ms. Our technology roadmap revealed that the total  $J_0$  allowed for 23 % cell is only 50 fA/cm<sup>2</sup> so we set the practically achievable target of 30 fA/cm<sup>2</sup> for metallized homogeneous or selective B emitter, metallized  $J_0$  target of 5 fA/cm<sup>2</sup> for the rear n-TOPCon and bulk lifetime of 1-2 ms, corresponding to  $J_{0,bulk}$  of  $<20$  fA/cm<sup>2</sup>. In addition to the target  $J_0$  values for each layer, we established contact and shading parameters to achieve 23% efficiency. We validated the model by applying it to match the cell parameters of the initially fabricated n-PERT and TOPCon cells using measured material, device and contact parameters.

**Milestone - Develop a technology roadmap for >23% screen-printed cells using optimized doping profiles and screen-printed B emitter and rear side n-TOPCon (BP1, Q4- Achieved)**

### TASK #2:

#### TECHNOLOGY DEVELOPMENT AND FORMATION OF OPTIMIZED HOMOGENEOUS AND SELECTIVE P<sup>++</sup>-P<sup>+</sup> B EMITTERS

**Task Summary:** Since the target for metallized  $J_{0e}$  was  $\sim 25$  fA/cm<sup>2</sup>, task 2 dealt with experimental development of homogeneous B emitter with unmetallized  $J_0$  of  $<15$  fA/cm<sup>2</sup> and unmetallized  $J_0 \leq 20$  fA/cm<sup>2</sup> for B selective emitter consistent with the guidelines from the roadmap in task 1. The objective was to find the manufacturable and cost-effective approach to forming B emitter that can meet the  $J_0$  requirements. Implanted and APCVD emitters were investigated. We fabricated 90-200  $\Omega/\square$  homogeneous implanted B emitters as well as selective B emitters formed by a combination of implanted field region ( $>150$   $\Omega/\square$ ) and APCVD B diffused p<sup>++</sup> region ( $<50$   $\Omega/\square$ ). Various dielectric passivation schemes (ALD/APCVD Al<sub>2</sub>O<sub>3</sub> with PECVD SiN<sub>x</sub>/SiO<sub>x</sub> capping) were tested and qualified to optimize passivation quality and achieve the unmetallized  $J_0$  targets. For the formation of B selective emitter, several different technologies (laser doping, etch-back, and double diffusion) were investigated. We succeeded in fabricating 170  $\Omega/\square$  implanted homogeneous emitter with unmetallized  $J_0$  of  $\sim 10$  fA/cm<sup>2</sup> and a 150/45  $\Omega/\square$  implanted/APCVD diffused selective B emitter with passivated  $J_{0e} \sim 18$  fA/cm<sup>2</sup>. After

Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell structures and technology innovations

Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

metallization homogeneous B emitter gave total metallized  $J_{0e}$  of 30 fA/cm<sup>2</sup> with contact resistivity of 3-5 mΩ-cm<sup>2</sup> and selective emitter resulted in metallized  $J_{0e}$  of 25 fA/cm<sup>2</sup> and contact resistivity of ~1 mΩ-cm<sup>2</sup>. These values are consistent with target values set by our roadmap for 23 % cells.

**Milestone – Demonstrate  $J_{0e,pass} \leq 15$  fA/cm<sup>2</sup> for passivated /unmetallized homogeneous emitter and  $J_{0e,pass} \leq 25$  fA/cm<sup>2</sup> for unmetallized /passivated p<sup>++</sup>-p<sup>+</sup> selective emitter (BP2, Q4- Achieved)**

### Task #3:

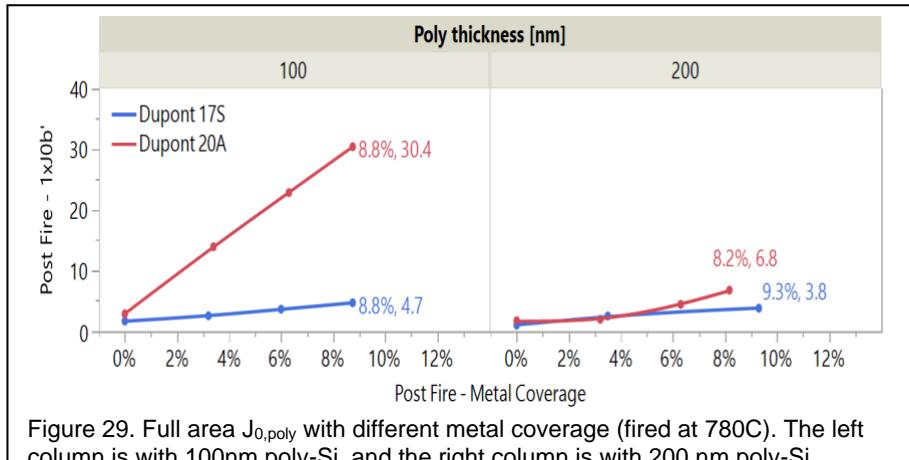

Technology development and formation of n-TOPCon

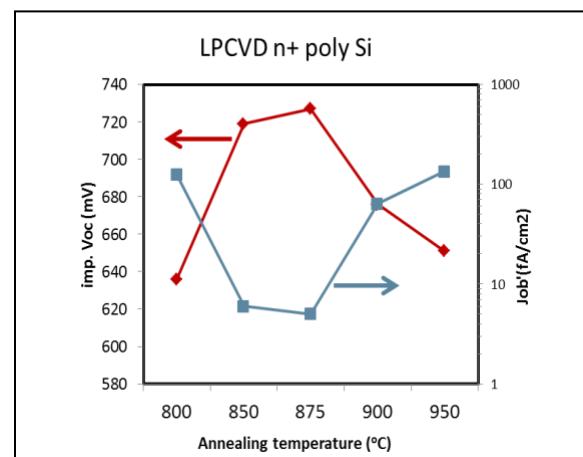

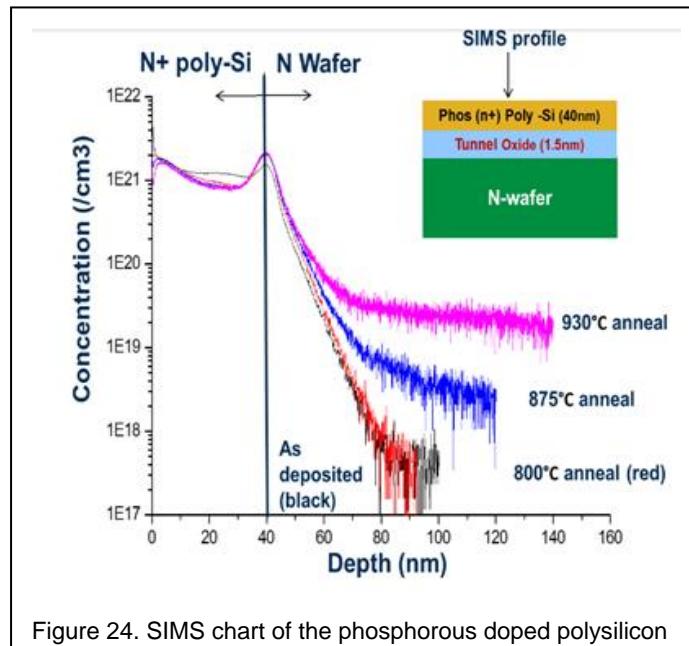

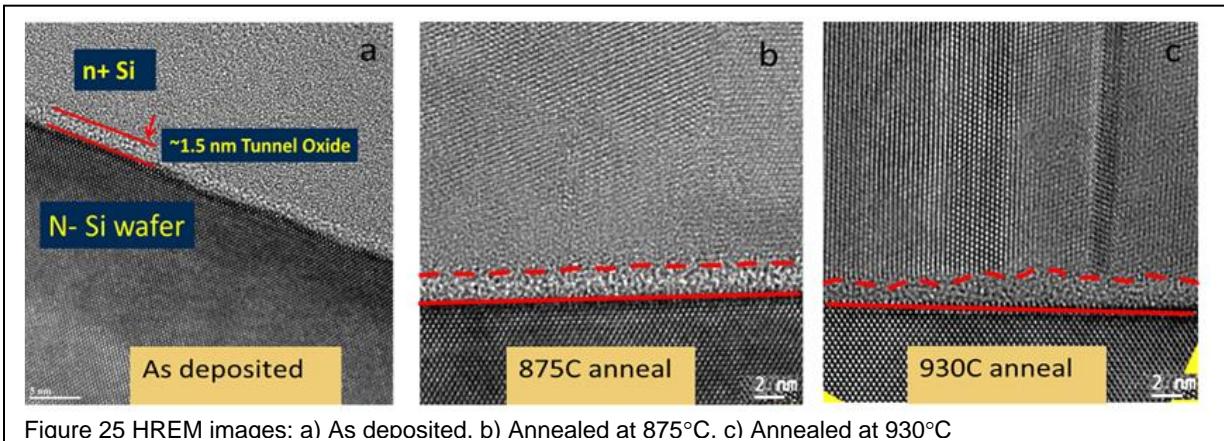

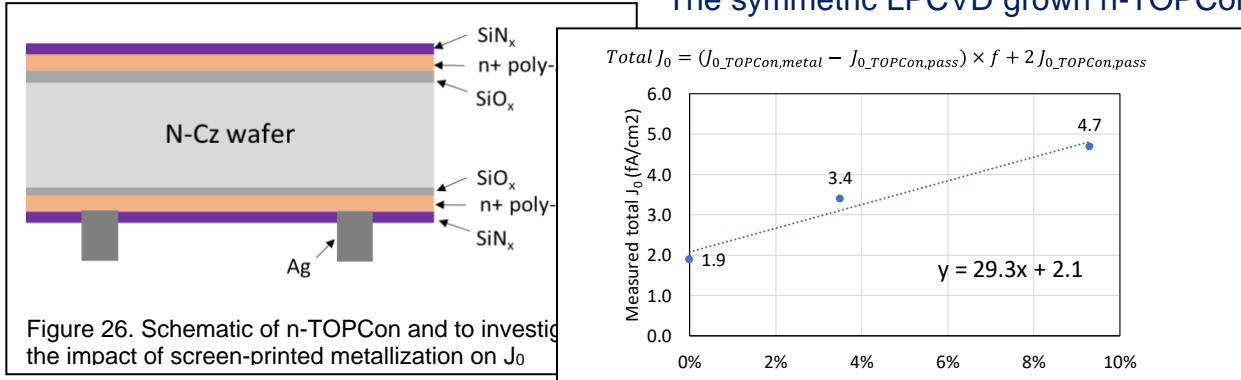

**Task Summary:** At the beginning of the project, we started experimental development of phosphorus diffused selective BSF to achieve < 25 fA/cm<sup>2</sup>. This was found to be more challenging and process intensive. Therefore, we changed the direction of this task from selective P BSF to n-TOPCon because n-TOPCon started to look very promising for minimizing low metallized rear  $J_0$  due to superior carrier selectivity and excellent passivation quality (BP1, Q4). We investigated both PECVD and LPCVD tools to grow phosphorus-doped poly-Si on top of chemically grown ~15 Å tunnel oxide to fabricate poly-Si/SiO<sub>2</sub> passivated contacts. Post poly-Si deposition anneal was optimized and 875 °C was found to be the optimum for our TOPCon structure which gave the lowest  $J_0$  and highest implied  $V_{oc}$ . We achieved excellent passivation quality from PECVD grown thin (10-40 nm) poly-Si and LPCVD grown thick (100-200 nm) poly-Si with unmetallized  $J_0$  of ~3 fA/cm<sup>2</sup>, which reduced to ~1 fA/cm<sup>2</sup> after ~700 Å thick SiN<sub>x</sub> deposition. Due to the fire through screen-printed metallization at high temperature (~770°C) and lower quality of thicker PECVD films in our tool, we chose the LPCVD process for growing the thick n-TOPCon, which was subsequently coated with SiN<sub>x</sub> for contact firing. We also studied the effect of screen-printed fire-through contacts on  $J_0$  for different pastes and poly-Si thickness. Appropriate paste and optimized firing resulted in metallized  $J_0$  of 5 fA/cm<sup>2</sup> with ~10% metal coverage on the rear TOPCon to maintain bi-faciality. In addition, contact resistivity for 200 nm thick poly was found to be ~ 2 mΩ-cm<sup>2</sup>. This is entirely consistent with the roadmap and the required metallized  $J_{0b}$  for achieving 23% efficiency.

**Milestone – Demonstrate  $J_0 \leq 5$  fA/cm<sup>2</sup> for metallized n-TOPCon (BP2, Q4- Achieved)**

### Task #4:

Advanced screen-printed and plated fine line metallization with floating busbars.

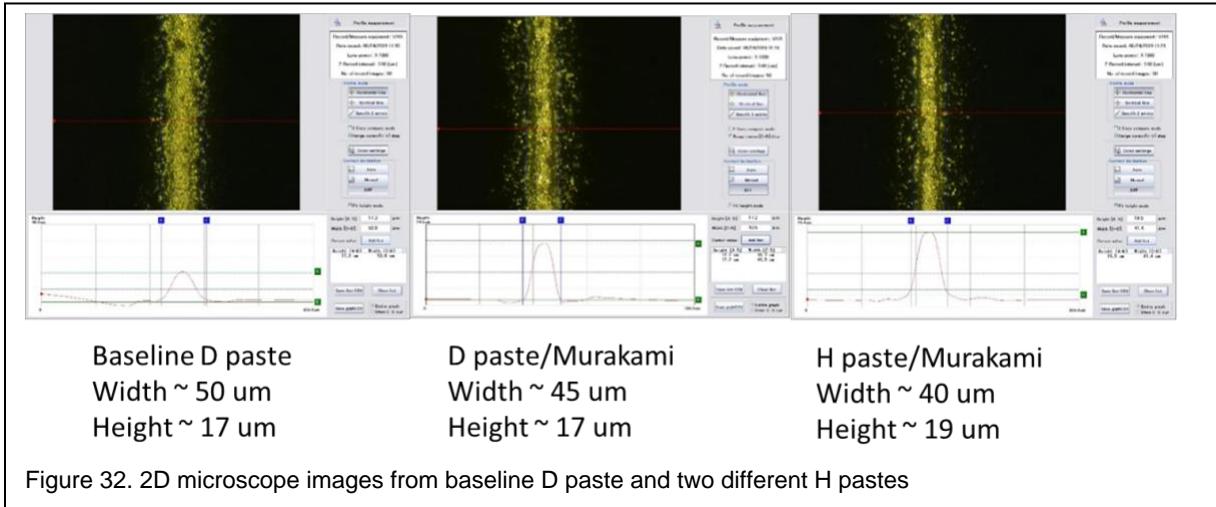

**Task Summary:** Task 4 involved advanced metallization to form contacts to B emitters with reduced shading and metal-Si contact area, without compromising the contact and series resistance (Rs). Target Rs value in the roadmap was set at ~ 0.5 ohm-cm<sup>2</sup> for the 23% bifacial cell. This was a challenge for the 170 Ω/□ homogeneous emitter and required experimenting with different pastes and firing schemes. In the case of selective emitter, the challenge was to align the contacts in the heavily diffused tracks while keeping the contact coverage and metal/Si contact to a minimum. Consistent with our technology roadmap, the metallized  $J_0$ ,  $J_{sc}$  and series resistance targets were achieved by pushing the limit of screen-printing technology to achieve ~40 μm wide grid lines after contact firing in combination with co-fired floating busbars. At the start of the program, our grid line widths were ~ 55 μm with fire-through contacts and no floating busbars. Finer grid lines reduced shading and the floating bus bars reduced metal/Si contact area and  $J_0$ . This was accomplished by experimenting with advanced screens with appropriate

Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell structures and technology innovations

Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

emulsion thickness and narrow openings in combination with pastes that do not spread appreciably upon firing.

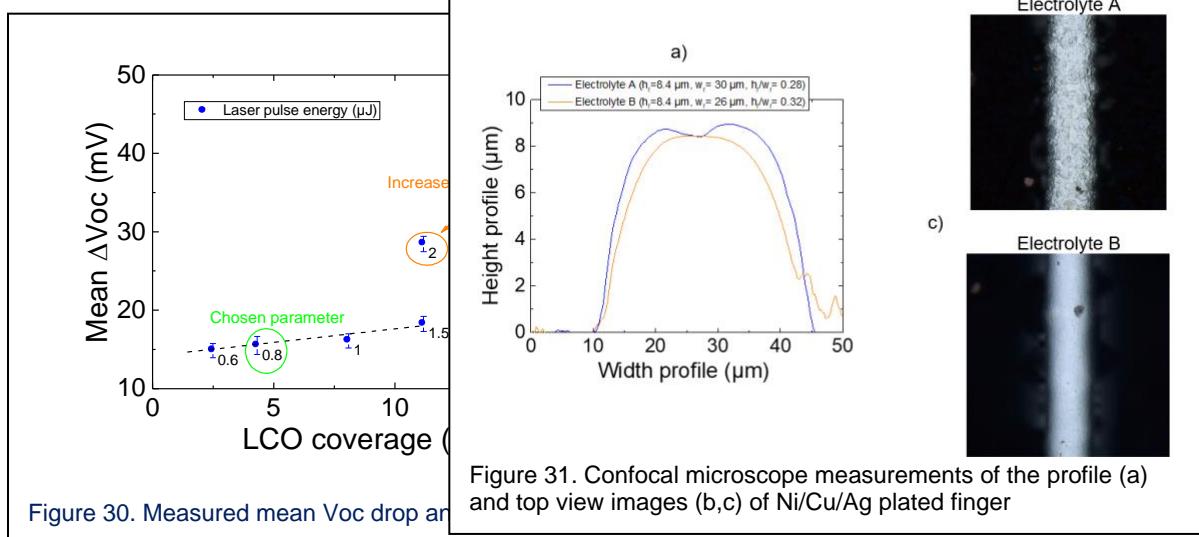

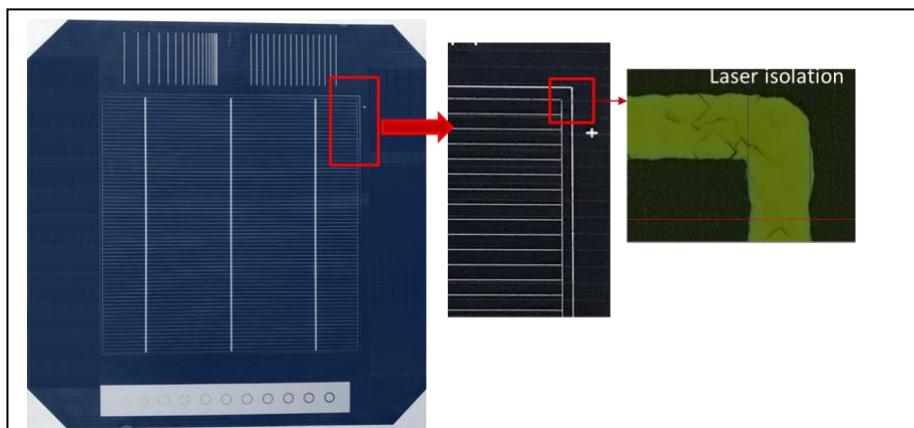

The second fine line metallization approach involved fabricating ~30  $\mu\text{m}$  wide Ni-Cu plated self-aligned contacts to heavily doped emitter regions. This was achieved by laser opening of narrow grid lines (~10  $\mu\text{m}$ ) followed by damage removal and electroless plating of Ni-Cu. This approach gave enhancement in  $J_{\text{sc}}$  due to narrower grid lines (~25-30  $\mu\text{m}$ ) but the residual laser damage on the emitter surface resulted in slightly lower  $V_{\text{oc}}$ . Therefore 40  $\mu\text{m}$  screen printed lines with floating busbars were used in final cell fabrication process which resulted in >0.3% enhancement in cell efficiency. We briefly attempted the use of busbarless /multi-wire contact in the final budget period to enhance cell performance.

**Milestone – Demonstrate screen printed <50  $\mu\text{m}$  wide grid lines with floating busbars and good alignment with 150  $\mu\text{m}$  wide heavily diffused selective tracks (BP2, Q7- Achieved)**

**Milestone - Demonstrate <40  $\mu\text{m}$  self-aligned plated contacts with contact resistance below 5  $\text{m}\Omega\text{-cm}^2$  (BP3, Q2 - Achieved)**

#### TASK #5:

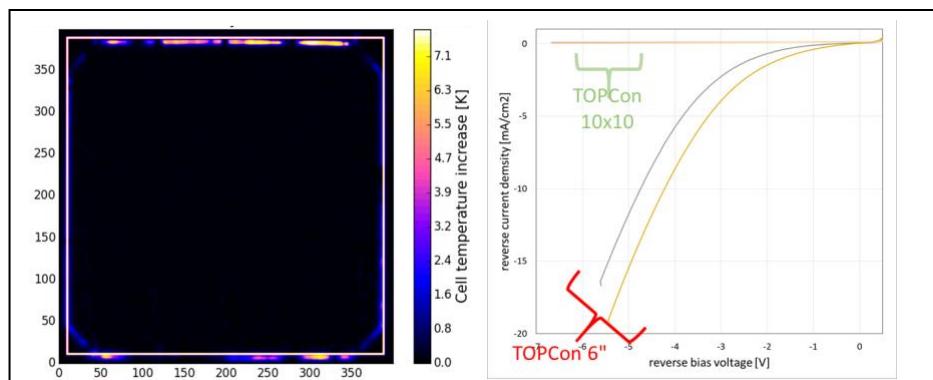

#### **FABRICATION OF HIGH-EFFICIENCY N-TOPCON CELLS BY PROCESS DEVELOPMENT AND INTEGRATION OF ADVANCED TECHNOLOGIES**

**Task Summary:** Task 5 involved integration of all the promising advanced technologies into a process sequence to fabricate screen printed 23% commercial size bifacial solar cells. In this task we achieved screen printed 239  $\text{cm}^2$  n-TOPCon bifacial cells with efficiency of 22.6%. Modeling and analysis showed slightly higher n-factor (~1.1) due to edge leakage effects which lowered the FF. To eliminate the edge effects, we fabricated 10x10 cm cell size within the 6-inch pseudo square wafer by laser isolation and modified the grid design with three busbars for 100  $\text{cm}^2$  cell. This resulted in 22.9% efficiency, consistent with our technology roadmap. Finally, we demonstrated fully screen-printed 239  $\text{cm}^2$  ~23% efficient bifacial n-TOPCon cells with chemical edge isolation process. These cells were fabricated with homogeneous B emitters. Based on the experimental and theoretical understanding developed in this program, we have established a new roadmap to ~25% cell efficiency n-TOPCon cells which involves busbarless contacts, much higher bulk lifetime and selective emitter.

**Milestone – Demonstrate n-TOPCon cell efficiency >22.5% (BP3, Q2- Achieved)**

**Go/No-Go – Cell efficiency >22.0% (BP3, Q2- Achieved)**

**Final Deliverable – Screen printed, large area n-TOPCon bifacial cells with efficiency >22.5% (Achieved)**

#### **Project Results and Discussion:**

Task #1: Technology roadmap development including doping profiles, recombination current and contact optimization by device modeling.

**Key Achievements:** In Task 1, we implemented several models including, 2D Sentaurus [6] and Quokka 2 [7] models for device simulation, Sentaurus Process model for implanted profile simulation, Sentaurus Device model for  $J_0$  vs SRV curve for each profile and antireflection coating, in-house grid model for grid design, contacts and floating busbar optimization. These models were used throughout the project to analyze the fabricated cells and understand the loss mechanisms in them. At the start we fabricated and modeled 21% traditional n-PERT cell and then applied Sentaurus and Quokka 2

models to establish a roadmap by identifying and quantifying the practically achievable properties and required enhancements in B emitter, n-TOPCon region, bulk lifetime, optical properties and contact parameters that can get us to 23% n-TOPCon cell efficiency. It was found that a metallized  $J_0$  of 30 fA/cm<sup>2</sup> in B emitter and 5 fA/cm<sup>2</sup> in rear TOPCon in combination with 1-2 ms bulk lifetime, 40  $\mu$ m grid lines and floating busbars can get us to our efficiency target. The cell efficiency roadmap was utilized to guide the experimental work and validate the technology development. Each layer of the device was investigated and optimized individually and then integrated to achieve the target efficiency. Finally, a new roadmap was developed for ~25% TOPCon cells.

### **Results and Discussion in Task 1**

We started the program with the fabrication of traditional n-PERT cells and used them to validate the 2D device modeling capabilities (Sentaurus and Quokka) and extend the simulations to establish a technology roadmap to achieve target cell efficiency. Analysis of our ~21% PERT cells showed that based on our starting material quality and processing, we can maintain bulk lifetimes in the range of 1-2 ms in the finished cells. Therefore, we created a roadmap with a bulk lifetime of 1.5 ms.

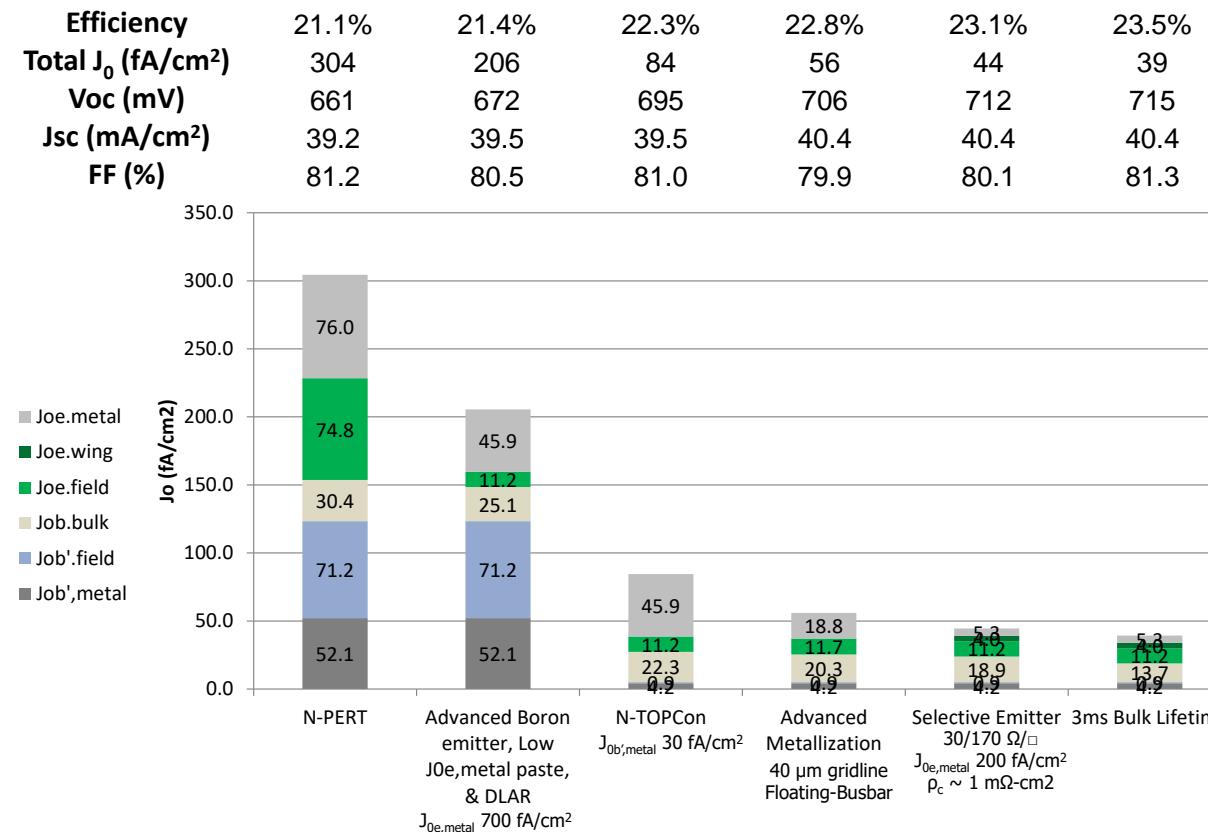

Figure 1 shows our technology roadmap to > 23% efficiency, starting with our 21.2% N-PERT cell fabricated at the start of this project. This cell had total  $J_0 = 304$  fA/cm<sup>2</sup>,  $V_{oc} = 661$  mV and  $J_{sc} = 39.2$  mA/cm<sup>2</sup>. This modeling was performed using 2D Quokka 2 simulator. In Figure 1 we have also quantified the individual contributions to

Figure 1 Technology roadmap for >23% n-TOPCon cells, start with our 21.0% n-PERT cell total  $J_0$  from the front and back metallized regions, B emitter, back surface field and the

bulk. This helps in identifying which regions are limiting the cell performance. Table 1 shows the detailed input and output parameters for each case or bar on the roadmap. Notice that in our PERT cell B emitter was  $95 \Omega/\square$  with single-layer AR coating, metal grid coverage of 6.5% and fire-through busbars. This resulted in metallized  $J_{0e}$  of  $\sim 150 \text{ fA/cm}^2$  from B emitter. Full area P diffused BSF with screen-printed contact resulted in metallized  $J_{0b}$  of  $123 \text{ fA/cm}^2$ . The bulk contribution to  $J_0$  was  $30.4 \text{ fA/cm}^2$  which was extracted from the difference between total  $J_0$  of  $304 \text{ fA/cm}^2$ , obtained from  $V_{oc}$  and  $J_{sc}$  of the cell, and the known metallized  $J_{0e}$  and  $J_{0b}$  numbers.

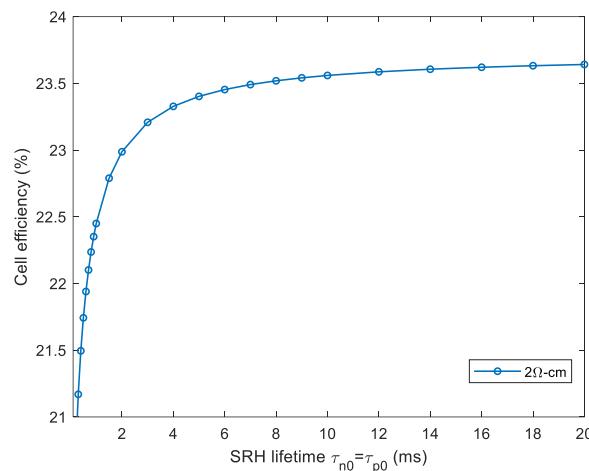

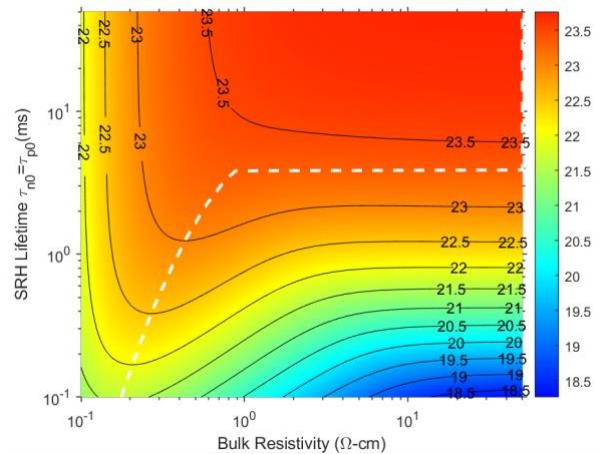

Since total  $J_0$  to achieve 23% efficient cell be only about  $50 \text{ fA/cm}^2$  (bars 4 and 5 in Fig 1), we had to design each layer of the n-PERT cell to minimize  $J_0$ . The second bar shows that if we can reduce the metallized  $J_{0e}$  of the B emitter from  $150$  to  $57 \text{ fA/cm}^2$  by raising its sheet resistance from  $95$  to  $170 \Omega/\square$  and using advanced screen-printed paste that can reduce full area  $J_{0e,metal}$  from  $1160 \text{ fA/cm}^2$  to  $700 \text{ fA/cm}^2$  (Table 1), we can get 21.4% efficient cells. At this point cell performance gets limited by the regions below the emitter. The third bar in the roadmap shows that we need to develop a carrier selective n-TOPCon to replace the n<sup>+</sup> BSF and lower the metallized  $J_0$  from  $123 \text{ fA/cm}^2$  to  $5 \text{ fA/cm}^2$  with 13% metal coverage (Table 1). This is a challenging task but achievable because in n-TOPCon both diffused and metallized regions are displaced outside the absorber. In addition, modeling shows that we also need to tailor the thickness and doping in rear poly to achieve contact resistivity of  $< 2 \text{ m}\Omega\text{-cm}^2$  and good FF. This enhancement should raise the efficiency to 22.3%. The fourth bar in the technology roadmap in Fig 1 shows that we also need to improve our screen-printing to reduce the line width from  $55$  to  $\sim 40 \mu\text{m}$ , busbar width from  $900$  to  $600\mu\text{m}$  and incorporate floating busbars to reduce shading as well as metal-induced recombination on the front side. This will raise the efficiency to 22.8% (Table 1). With the above changes in screen-printing parameters, we had re-optimize the grid design to maintain low contact and series resistance. This was done by using our in-house grid model. The fifth bar in the roadmap shows that implementation of a p<sup>+</sup>/p<sup>++</sup> selective emitter ( $170/30 \Omega/\square$  with metallized  $J_0$  of  $< 25 \text{ fA/cm}^2$  and contact resistivity of  $\sim 1 \text{ m}\Omega\text{-cm}^2$ , instead of  $30 \text{ fA/cm}^2$  and  $3-5 \text{ m}\Omega\text{-cm}^2$  for the homogeneous emitter, will bump the cell efficiency to 23%. Last bar shows the importance of bulk lifetime at this point because  $J_{0b}$  starts to play a big role in limiting the cell efficiency. If we can have a bulk lifetime of  $3 \text{ ms}$ , this efficiency will climb to 23.5%. To highlight the importance of bulk resistivity and lifetime (material quality) we performed additional modeling to quantify the impact of bulk lifetime alone as well as the combined effect lifetime and resistivity on the efficiency of our cell design (Figs 2 and 3). Figure 2 shows that, with a higher than  $2 \text{ ms}$  SRH lifetime, our n-TOPCon cell can achieve > 23% efficiency with a homogeneous B emitter on the front. The efficiency contour map as a function of bulk resistivity and mid-gap SRH lifetime is generated in Figure 3. The white dashed line shows the optimum bulk resistivity that results in maximum efficiency at each SRH lifetime. The optimum resistivity increases with increasing SRH lifetime, and when  $\tau_{n0} = \tau_{p0} > \sim 4 \text{ ms}$ , the optimum resistivity increases to >  $20 \Omega\text{-cm}$  bulk resistivity. This is because the benefit of higher  $\tau_{bulk}$  from lowly doped bulk outweighs the lateral transport benefit from highly doped bulk material.

Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell structures and technology innovations

Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

Figure 2 Efficiency vs mid-gap SRH lifetime of n-TOPCon cells with advanced metallization (bar 4 in Figure 1). It shows 23% efficiency can be achieved with 2 ms lifetime without selective emitter, and 23.2% efficiency can be achieved with 3 ms lifetime.

Figure 3 Efficiency contour map of n-TOPCon cells with advanced metallization (bar 4 in Figure 1) as a function of bulk resistivity and mid-gap SRH lifetimes. The white dashed line corresponds to the optimum bulk resistivity that results in maximum efficiency at each SRH lifetime

Table 1 Quokka 2 modeling results and input parameters for the n-PERT and n-TOPCon cells

|                                      | N-PERT       | Advanced<br>Boron<br>emitter,<br>Low $J_{0e,metal}$<br>paste, &<br>DLAR | N-TOPCon         | Advanced<br>Metallization | Selective<br>Emitter | 3ms Bulk<br>Lifetime |

|--------------------------------------|--------------|-------------------------------------------------------------------------|------------------|---------------------------|----------------------|----------------------|

| <b>Efficiency</b>                    | 21.1%        | 21.4%                                                                   | 22.3%            | 22.8%                     | 23.1%                | 23.5%                |

| Total $J_0$<br>(fA/cm <sup>2</sup> ) | 304          | 206                                                                     | 84               | 56                        | 44                   | 39                   |

| Voc (mV)                             | 661          | 672                                                                     | 695              | 706                       | 712                  | 715                  |

| $J_{sc}$<br>(mA/cm <sup>2</sup> )    | 39.2         | 39.5                                                                    | 39.5             | 40.4                      | 40.4                 | 40.4                 |

| FF (%)                               | 81.2         | 80.5                                                                    | 81.0             | 79.9                      | 80.1                 | 81.3                 |

| Cell size<br>(cm <sup>2</sup> )      | 239          | 239                                                                     | 239              | 239                       | 239                  | 239                  |

| Anti-<br>Reflection<br>Layer         | Single Layer | Double<br>Layers                                                        | Double<br>Layers | Double<br>Layers          | Double<br>Layers     | Double<br>Layers     |

| Front finger<br>width $W_f$<br>(μm)  | 55           | 55                                                                      | 55               | 40                        | 40                   | 40                   |

| Front<br>shading<br>coverage         | 6.55%        | 6.55%                                                                   | 6.55%            | 4.59%                     | 4.59%                | 4.59%                |

| Front metal<br>contact<br>coverage   | 6.55%        | 6.55%                                                                   | 6.55%            | 2.67%                     | 2.67%                | 2.67%                |

| Busbar<br>number /<br>width (μm)     | 5 / 900      | 5 / 900                                                                 | 5 / 900          | 5/600                     | 5/600                | 5/600                |

Pushing the efficiency limit of low-cost, industrially relevant Si solar cells to > 22.5% by advancing cell

structures and technology innovations

Georgia Tech UCEP, University of Konstanz, Fraunhofer ISE

| Floating or<br>Fire-through<br>BB<br>Wafer<br>Thickness<br>( $\mu\text{m}$ )<br>Front | Fire-through<br>BB | Fire-through<br>BB | Fire-through<br>BB | Floating BB | Floating BB | Floating BB |

|---------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-------------|-------------|-------------|

| Thickness<br>( $\mu\text{m}$ )<br>Front                                               | 180                | 180                | 180                | 180         | 180         | 180         |

| Contact<br>Resistivity<br>( $\text{m}\Omega\text{-cm}^2$ )                            | 1                  | 3                  | 3                  | 3           | 1           | 1           |

| Selective<br>emitter<br>sheet<br>resistance<br>( $\Omega/\square$ )                   | NA                 | NA                 | NA                 | NA          | 30          | 30          |

| Selective<br>emitter<br>junction<br>width ( $\mu\text{m}$ )                           | NA                 | NA                 | NA                 | NA          | 100         | 100         |

| Wing $J_0$<br>( $\text{fA/cm}^2$ )<br>Front                                           | NA                 | NA                 | NA                 | NA          | 100         | 100         |

| passivated<br>$J_0$ ( $\text{fA/cm}^2$ )<br>Front                                     | 80                 | 12                 | 12                 | 12          | 12          | 12          |

| contact<br>$J_{0,\text{metal}}$<br>( $\text{fA/cm}^2$ )                               | 1160               | 700                | 700                | 700         | 200         | 200         |

| Front emitter<br>sheet<br>resistance<br>( $\Omega/\square$ )                          | 95                 | 170                | 170                | 170         | 170         | 170         |

| Substrate<br>resistivity<br>( $\Omega\text{-cm}$ )<br>mid-gap                         | 2                  | 2                  | 2                  | 2           | 2           | 2           |

| SRH<br>Lifetimes<br>( $\tau_n=\tau_p$ ) (ms)                                          | 1.5                | 1.5                | 1.5                | 1.5         | 1.5         | 3           |

| Back<br>Contact<br>Resistivity<br>( $\text{m}\Omega\text{-cm}^2$ )                    | 1                  | 1                  | 2                  | 2           | 2           | 2           |

| Rear<br>passivated<br>$J_0$ ( $\text{fA/cm}^2$ )                                      | 72                 | 72                 | 1                  | 1           | 1           | 1           |

| Rear contact<br>$J_{0,\text{metal}}$<br>( $\text{fA/cm}^2$ )                          | 4600               | 4600               | 30                 | 30          | 30          | 30          |

| Rear contact<br>percentage                                                            | 1.13%              | 1.13%              | 13%                | 13%         | 13%         | 13%         |

Task #2: Technology development and formation of optimized homogeneous and

selective B emitter

**Key Achievements:** In task 2, we investigated an experimental development of advanced homogeneous B emitter as well B selective emitters to achieve metallized  $J_0$  of ~25 fA/cm<sup>2</sup>. We developed a homogeneous implanted B emitter with the passivated  $J_0$  ~ 10 fA/cm<sup>2</sup> and metallized  $J_0$  ~30 fA/cm<sup>2</sup> using high sheet resistance (170-180  $\Omega/\square$ ) emitter in combination with advanced metallization involving low  $J_{0,metal}$  paste, fine line printing and floating busbars. This resulted in reduced shading, metal-Si contact area and 3-5 m $\Omega$ ·cm<sup>2</sup> contact resistivity. We also developed a new process for selective B emitter with ~ 150  $\Omega/\square$  implanted B in the field area and ~ 45  $\Omega/\square$  APCVD B glass diffusion in the contact area. Consistent with the roadmap, this resulted in unmetallized  $J_0$  of ~18 fA/cm<sup>2</sup> and metallized  $J_{0e} < 30$  fA/cm<sup>2</sup>.

## Results and Discussion in Task 2

### Task 2.1 Development of advanced homogeneous implanted B emitter

In this project, we investigated the effect of profile and sheet resistance of ion-implanted homogeneous B emitter on the efficiency of bifacial n-TOPCon cells by a combination of modeling, technology development and cell fabrication. It is well known that the screen-printed Ag/Al contacts to B emitters can be made with much lower surface concentration ( $< 2 \times 10^{19} \text{ cm}^{-3}$ ) compared to the screen-printed Ag contacts to phosphorus (P) doped n-type emitters ( $\sim 1 \times 10^{20} \text{ cm}^{-3}$ ). This provides an opportunity to lower  $J_{0e,pass}$  by reducing B doping without sacrificing contact quality. However, this makes the metal-induced recombination much worse because lightly doped emitters are more transparent and sensitive to surface recombination velocity. Due to these tradeoffs, it is challenging to tailor the doping profile of a homogeneous B emitter to achieve low  $J_{0e}$  values in the passivated as well as metallized regions simultaneously, while maintaining good ohmic contact and acceptable sheet resistance for high FF. This problem can be mitigated by driving the B emitter profile or junction deep to decouple the metallized surface from metal, optimizing screen-printed contacts to lower  $J_{0e,metal}$ , and reducing the direct metal-Si contact area. In this study, we have employed ion implantation to form B emitters because, besides time and temperature, it provides additional controls like implantation energy and dose for profile engineering and management. Ion implantation also provides opportunities for higher cell efficiency because of better areal uniformity, more precise control of doping profile, and excellent chemical purity of the beam. Efficiency improvement and lower recombination current density with B and P implanted regions have been published by several groups [8-15] with screen-printed cell efficiencies approaching 21%.

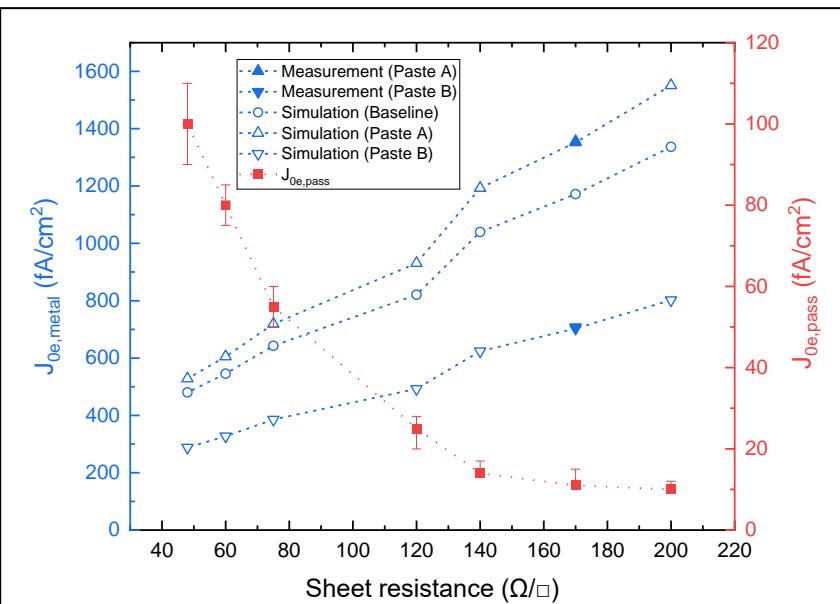

In addition to profile optimization, we investigated different screen-printing metal pastes and firing schemes to minimize  $J_{0e,metal}$  and quantify contact resistivity, and then use that information in Sentaurus 2D device simulations to understand the tradeoffs to select the optimum B emitter profile. Experimental values of  $J_{0e,metal}$  were determined for selected screen-printed fire-through metal pastes to demonstrate that  $J_{0e,metal}$  can increase or decrease depending on the aggressiveness of the glass frit, and its interaction with emitter surface as well as passivating dielectric underneath the grid. According to our technology roadmap in Task 1, final goal of this task was to achieve a metallized  $J_{0e}$  of ~ 30 fA/cm<sup>2</sup> with a homogeneous B emitter so that ~23% n-type cells can be achieved with n-TOPCon rear contact.

Ion-implanted B emitters in the sheet resistance range of 48-200  $\Omega/\square$  were fabricated and characterized in terms of sheet resistance, doping profiles, specific contact

resistivity,  $J_{0e,pass}$  and  $J_{0e,metal}$ . To quantify the emitter recombination current density ( $J_{0e}$ ), symmetric  $p^+/n/p^+$  test structures were prepared by B implantation and annealing on 200  $\mu\text{m}$  thick 20  $\Omega\text{-cm}$  6-inch pseudo square high bulk lifetime n-type monocrystalline Czochralski (Cz) wafers. After saw damage etching and texturing followed by a standard RCA clean process, wafers received B implantation at 10 keV with doses ranging from  $1\times10^{15} \text{ cm}^{-2}$  to  $5\times10^{15} \text{ cm}^{-2}$  on both sides. All samples were annealed at 1050  $^{\circ}\text{C}$  for 1 hour in  $\text{N}_2$  ambient followed by an in-situ oxidation for 30 minutes in  $\text{O}_2$  ambient to remove implanted damage, activate dopants and drive the junction deep. After etching the thermal oxide in a dilute HF solution, the sheet resistance of implanted B emitters ( $R_{sheet}$ ) was measured by a four-point probe. After a standard RCA clean, ~100  $\text{\AA}$  thick aluminum oxide ( $\text{Al}_2\text{O}_3$ ) layer was deposited for surface passivation by plasma-assisted atomic layer deposition (ALD) on both sides, followed by plasma-enhanced chemical vapor deposition (PECVD) of  $\text{SiN}_x/\text{SiO}_2$  stack on top of the  $\text{Al}_2\text{O}_3$  for both passivation and antireflection coating. Next, samples were subjected to a firing cycle without any metal paste to simulate the effect of screen-printed contact firing on passivation quality of the unmetallized portion of the emitter. Finally,  $J_{0e,pass}$  was measured under high-level injection using the photoconductance decay (PCD) method proposed by Kane and Swanson [16]. In order to quantify the recombination current density contribution due to metallized portion of the B emitter ( $J_{0e,metal}$ ), 40  $\mu\text{m}$  wide metal gridlines with varying pitch and metal fraction ( $f_{metal}$ ) were screen-printed only on rear side of the symmetric structure. Several different pastes were investigated but only two most pertinent ones (A&B) are reported. To evaluate the effect of pastes A and B on  $J_{0e,metal}$ , the two commercial Ag/Al pastes were applied on 170  $\Omega/\square$  symmetric  $p^+/n/p^+$  test samples implanted with  $1.2\times10^{15} \text{ cm}^{-2}$  B dose. After firing, the Ag/Al bulk electrode was etched away in  $\text{HCl:H}_2\text{O}_2:\text{H}_2\text{O} = 1:1:1$  solution, leaving only the thin glass layer on Si surface with embedded metal crystallites into the emitter.  $J_{0e,metal}$  for the two pastes was then determined by fitting the measured total  $J_0$  of etched samples as a function of the  $f_{metal}$ . Since  $J_0$  for the symmetric test structure with metal contacts on one side can be expressed as:

$$\text{Measured total } J_0 = J_{0e,front,metal} \times f_{metal} + J_{0e,front,pass} \times (1 - f_{metal}) + J_{0e,rear,pass}$$

$$\text{Slope of } J_0 \text{ vs } f_{metal} = J_{0e,front,metal} - J_{0e,front,pass} = J_{0e,metal} - J_{0e,pass}$$

$$\text{With Intercept} = J_{0e,front,pass} + J_{0e,rear,pass} = 2 \times J_{0e,pass},$$

$$\text{therefore, } J_{0e,pass} = \frac{\text{Intercept}}{2} \text{ and } J_{0e,metal} = \text{Slope} + J_{0e,pass}$$

Thus both  $J_{0e,metal}$  and  $J_{0e,pass}$  can be obtained from the slope and intercept of the linear plot. In addition, the specific contact resistivity between screen-printed Ag/Al contact and the implanted B emitters for the two pastes was measured by transfer length method (TLM), using separate test samples prepared with unequally spaced screen-printed lines. Finally, the profile of the 170  $\Omega/\square$  emitter was measured by electrochemical capacitance-voltage measurement (ECV) to match and validate the Sentaurus Process model used to generate various implanted profiles.

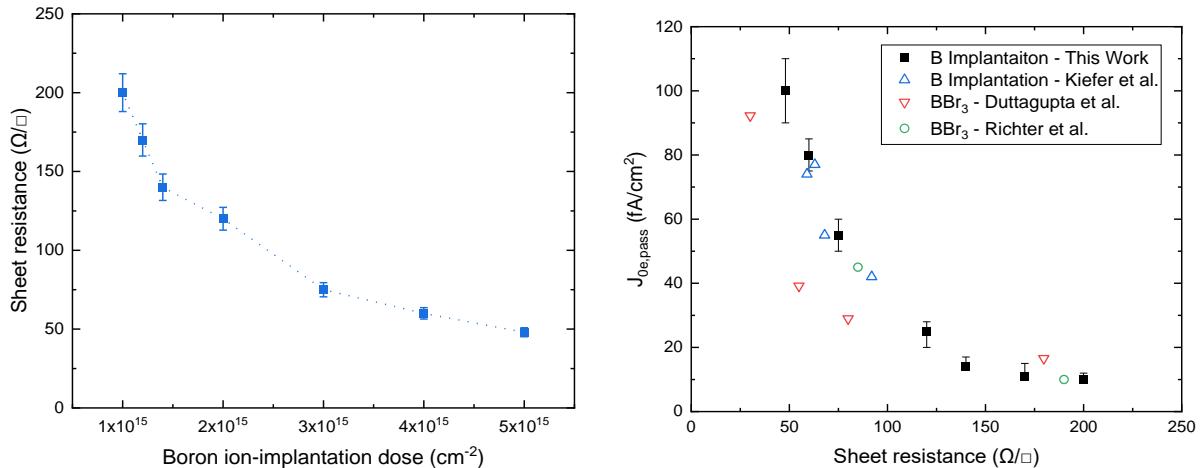

### 2.1.1 Characterization of unmetallized ion-implanted B emitters as a function of implantation dose

Figure 4. Boron emitter sheet resistance as a function of boron ion-implantation doses for 10 keV implantation energy and 1050 °C post-implantation anneal (left) Experimentally measured  $J_{0e,\text{pass}}$  in this study (solid symbols) and selected literature data (open symbols) [17-19] as a function of boron emitter sheet resistance on textured surface (right)

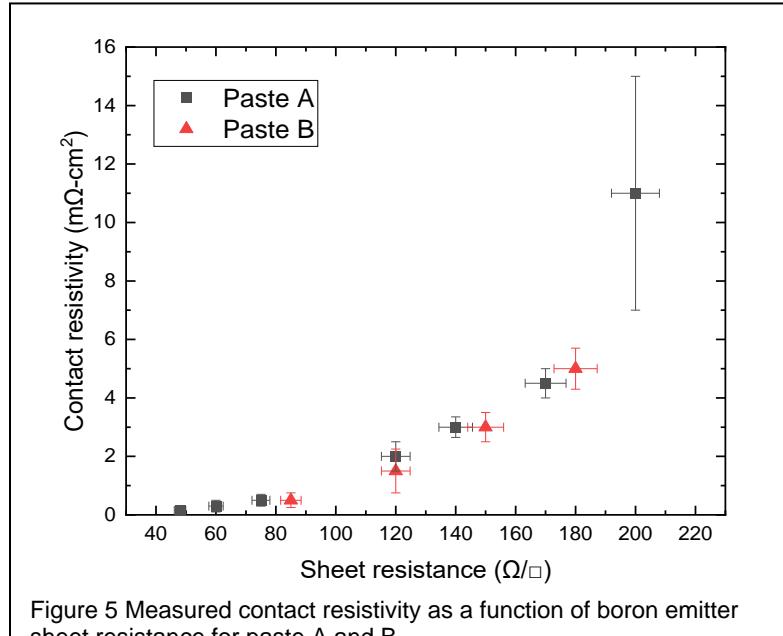

Figure 4a shows the sheet resistance ( $R_{\text{sheet}}$ ) of the ion-implanted B emitters fabricated in this study as a function of B ion-implantation dose using 10 keV implantation energy and the above mentioned 1050 °C anneal. As expected  $R_{\text{sheet}}$  decreases from  $200 \Omega/\square$  to  $48 \Omega/\square$ , as the B implantation dose increases from  $1 \times 10^{15} \text{ cm}^{-2}$  to  $5 \times 10^{15} \text{ cm}^{-2}$ . Figure 4 (right) shows the measured  $J_{0e,\text{pass}}$  for the ion-implanted textured B emitters fabricated in this study as a function of B emitter sheet resistance. The solid squares show our results and the open symbols show literature data from [17-19] for comparison. Notice, very low  $J_{0e,\text{pass}} < 15 \text{ fA}/\text{cm}^2$  were achieved for  $R_{\text{sheet}} > 140 \Omega/\square$ . Figure 5 shows the measured contact resistivity as a function of B emitter sheet resistance. Contact resistivity of less than  $5 \text{ m}\Omega\text{-cm}^2$  was achieved for both pastes A and B for  $\leq 170 \Omega/\square$  implanted emitters with surface concentration of  $6 \times 10^{18}/\text{cm}^3$ , which is acceptable for high-efficiency cells. Next step was to determine the metallized  $J_0$  which is composed of passivated region between the gridlines as well as metallized emitter portion under the grid. In order to quantify and explain the difference between the metallized  $J_0$  for the two pastes, we first simulated their profiles and established a baseline or reference value of  $J_{0e,\text{metal}}$

Figure 5 Measured contact resistivity as a function of boron emitter sheet resistance for paste A and B

assuming an ideal or uniform full area metal-Si contact interface. This is described in the next section.

### 2.1.2 Modeling to establish a baseline metallized $J_{oe,metal}$ value for implanted B emitters assuming uniform metal contact interface with surface recombination velocity (SRV) = 10<sup>7</sup> cm/s

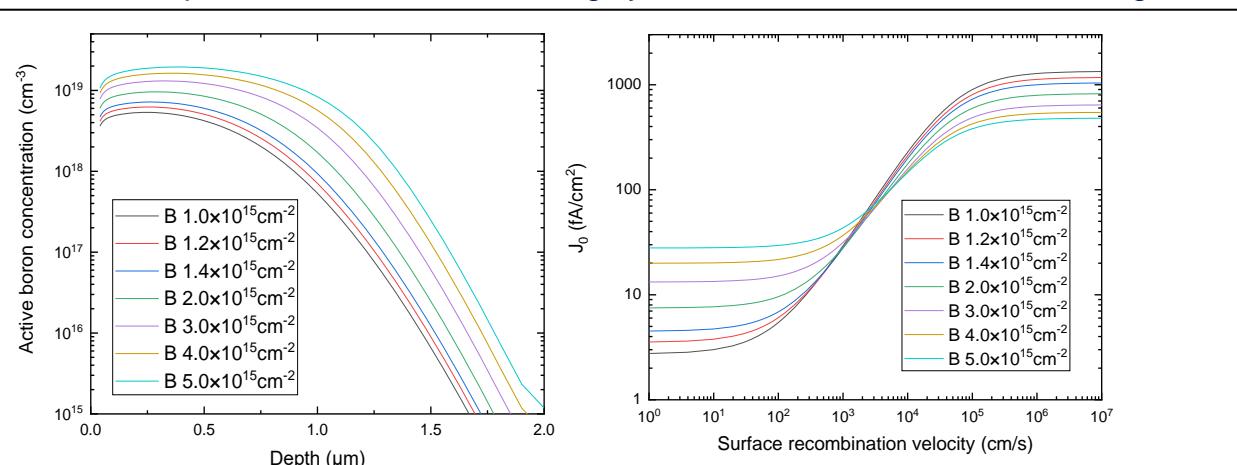

Sentaurus Process model was used to simulate the implanted B profiles in this study.

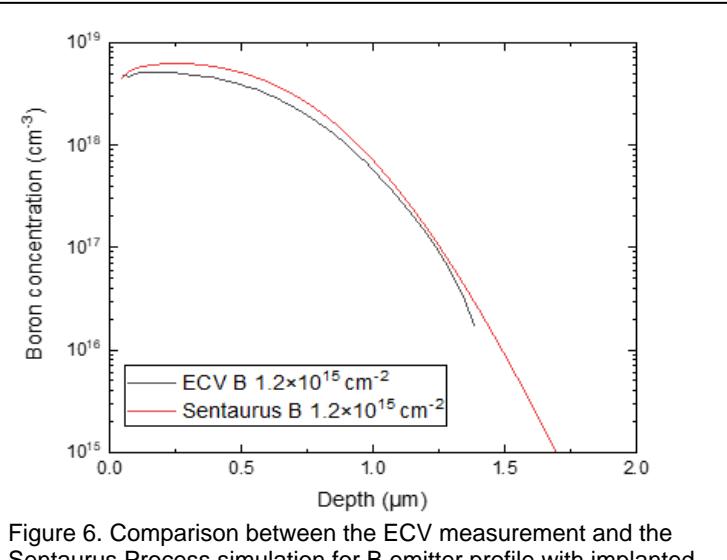

In this model we selected 'Monte Carlo model' for simulating distribution of implanted B and 'Boron-interstitial clusters' (BIC) model for simulation of dopant activation and clustering. This was validated by direct ECV measurements of couple of profiles. Figure 6 shows we obtained a reasonably good match between the measured B profile by ECV and the simulated profile for the 170  $\Omega/\square$  emitter.

The small deviations between simulation and measurement are attributed to the actual diffusion mechanism and assumed oxidation enhanced diffusion model. This validation provided a good basis for simulating B emitter profiles implanted with different doses, as shown in Figure 7. These profiles were then fed into the Sentaurus Device model to generate  $J_0$  vs SRV curves for the simulated profiles by varying SRV. Full area baseline  $J_{oe,metal}$  value for each emitter was extracted assuming a uniform 100% metal-Si contact area with SRV = 10<sup>7</sup> cm/s. This baseline  $J_{oe,metal}$  value will be used as a reference to compare the quality of different screen-printed contacts. It is important to recognize that actual screen-printed contact interface is highly non-uniform and can have  $J_{oe,metal}$  greater

Figure 6. Comparison between the ECV measurement and the Sentaurus Process simulation for B emitter profile with implanted dose of  $1.2 \times 10^{15} \text{ cm}^{-2}$

Figure 7. Simulated boron profiles with different implanted boron doses with Sentaurus Process simulation (left) and calculated  $J_{oe}$  as functions of surface recombination velocity with different boron implant doses (right)

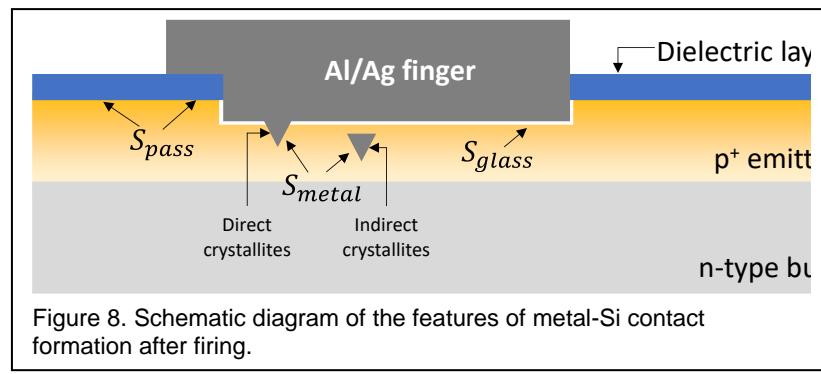

or less than the baseline case depending on the paste and firing conditions. Figure 8 shows a schematic of a typical screen-printed interface [20]. If there are metal crystallites embedded into the emitter in conjunction with over-etching of the passivation layer by glass frit (resulting in partial truncation of the emitter profile), then  $J_{0e,metal}$  could be higher than the baseline case. On the other hand, if there are some unetched passivating SiN islands under the metal grid (resulting in local contacts), then  $J_{0e,metal}$  can be lower than the baseline  $J_{0e,metal}$  value.

### 2.1.3 Modeling and quantitative understanding of the significant difference in the $J_{0e,metal}$ for pastes A and B

Formation of screen-printed contacts involves firing-induced etching or dissolution of passivation and antireflection coatings by molten glass frit, followed by solidification of a very thin glass layer between the Si emitter surface and bulk Ag/AI electrode [21-23].

Some Ag crystallites are also formed at the Si surface and get partially embedded into the Si emitter surface to form either direct contact to the top metal electrode or indirect contact through the glass layer above it (Figure 8), which can conduct by tunneling or hopping through the suspended fine Ag particles in it [23, 24]. Any appreciable etching of the emitter surface layer is known to increase sheet resistance and  $J_{0e,metal}$  and

lower implied FF because contacts are made deeper into the emitter [20, 25, 26]. On the other hand, if the frit is not very aggressive, entire dielectric layer underneath the metal electrode may not dissolve, resulting in the formation of non-uniformly distributed dielectric islands underneath the grid [20]. This will reduce  $J_{0e,metal}$  value due to local contacts through the dielectric layer relative to the full area baseline contact. That is why we first established the baseline  $J_{0e,metal}$  value for reference.

In the previous section we defined baseline contact as a contact with uniform interface and 100% metal-Si contact with  $SRV = 10^7$  cm/s. Baseline  $J_{0e,metal}$  was found to be 1172 fA/cm<sup>2</sup> for our 170  $\Omega/\square$  emitter. However linear plots of total  $J_0$  as a function of

Figure 8. Schematic diagram of the features of metal-Si contact formation after firing.

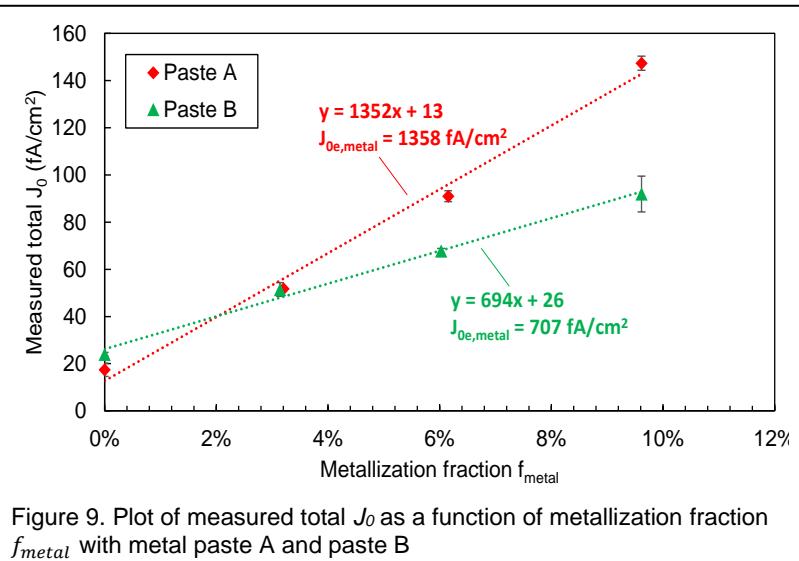

Figure 9. Plot of measured total  $J_0$  as a function of metallization fraction  $f_{metal}$  with metal paste A and paste B

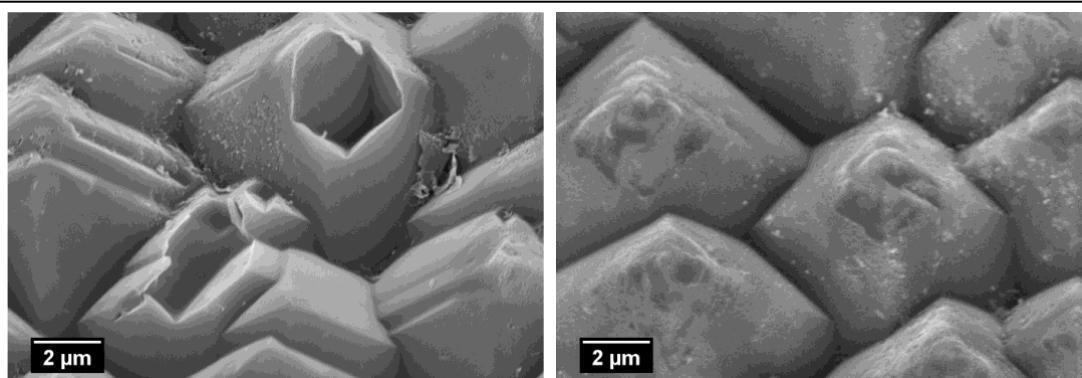

$f_{metal}$  for pastes A and paste B on  $170 \Omega/\square$  emitter in Figure 9 reveal very different  $J_{0e,metal}$  values. For both pastes A and B, the intercept ( $2 \times J_{0e,pass}$ ) gave  $J_{0e,pass}$  value of  $\sim 11 \text{ fA/cm}^2$ , but the slope ( $J_{0e,metal} - J_{0e,pass}$ ) gave  $J_{0e,metal} = 1358 \text{ fA/cm}^2$  for paste A, which is 15% higher than the simulated baseline value. On the contrary,  $J_{0e,metal}$  for paste B was found to be  $707 \text{ fA/cm}^2$ , which is 40% lower than the baseline contact. To understand the reason for this significant difference, the silicon surfaces under the metal contacts were analyzed by SEM after first removing the bulk metal gridline in  $\text{HCl:H}_2\text{O}_2:\text{H}_2\text{O}$  1:1:1 solution and then etching the glass layer in dilute HF solution. The SEM pictures for the two pastes are shown in Figure 10.

Figure 10(a) shows that in the case of paste A, the edges of pyramids are rounded with sporadic deep holes and virtually no cloudy regions on the faces of the pyramids. Deep holes are indicative of penetrating metal crystallites which came off during removal of metal and glass layers. Rounding indicates the possibility of etching of the emitter surface, and lack of cloudy regions suggests the absence of unetched dielectric islands.

Figure 10. SEM images of silicon surfaces under metal contacts after removal of the fired screen-printed metal gridline and glass from fired metal gridlines with paste A and paste B.

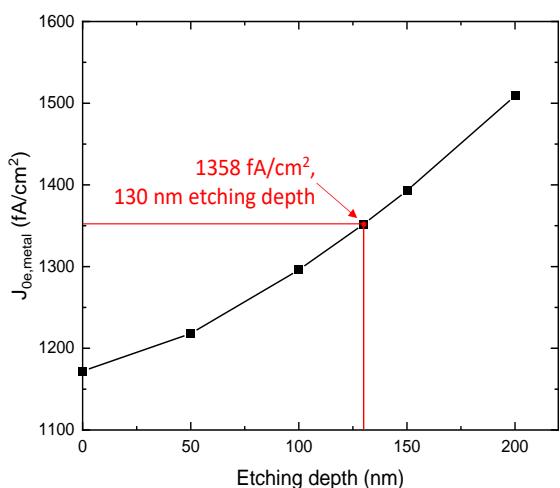

This suggests that frit chemistry and firing of paste A is more aggressive than desired. This is consistent with the observed increase in  $J_{0e,metal}$  over the baseline contact because both embedded metal crystallites and over-etching of dielectric layer will increase  $J_{0e,metal}$  because metal contact is made below the original emitter surface. To estimate the average emitter depth removal, we applied Daniel Inns' [25] and Koduvelikulathu's [27] methodology, which involves using truncated profile after removing a slice of the emitter near the surface, generating a plot of  $J_{0e}$  vs SRV curve, and then determining full area  $J_{0e,metal}$  at  $SRV=10^7 \text{ cm/s}$ . Figure 11 shows a graph of  $J_{0e,metal}$  vs emitter etch depth for paste A, which reveals an effective metal penetration depth of 130 nm at which  $J_{0e,metal}$  matches the measured value of  $1358 \text{ fA/cm}^2$ .

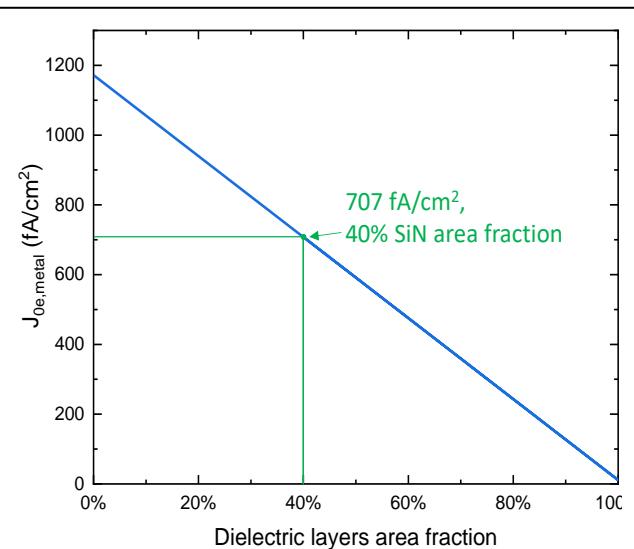

Contrary to paste A, measured  $J_{0e,metal}$  for paste B was found to be much lower ( $707 \text{ fA/cm}^2$ ) than the simulated baseline  $J_{0e,metal} = 1172 \text{ fA/cm}^2$ . Figure 10(b) shows that unlike paste A, the pyramids after firing with paste B do not show voids. Only minimal damage or imprints on the silicon surface are observed after the removal of metal and glass layer. This suggests no appreciable metal penetration or over etching of the emitter. However appreciable fraction of cloudy regions on the sides of the pyramids are observed, suggesting the presence of unetched dielectric islands under the metal grid lines which

Figure 11. Simulated paste A  $J_{0e,metal}$  with varied metal etching depth for  $170 \Omega/\square$  B emitter. With an uniform 130 nm etching, the simulated  $J_{0e,metal}$  matches with the experimental measurement ( $1358 \text{ fA/cm}^2$ ).

$\text{Al}_2\text{O}_3/\text{SiN}_x/\text{SiO}_2$  passivated emitter. Figure 12 shows the calculated  $J_{0e,metal}$  as a function of dielectric layers area fraction, which reveals that paste B contact interface has ~40% unetched dielectric islands at which calculated  $J_{0e,metal}$  matches the measured value of  $707 \text{ fA/cm}^2$ .

Next we performed model calculations to estimate full area  $J_{0e,metal}$  for all the B emitter profiles or sheet resistances fabricated in this study for the two pastes assuming emitter etch depth of 130 nm for paste A and unetched dielectric area fraction of 40% for paste B. These values were then used in device modeling to predict the cell efficiency and select the optimum emitter since  $J_{0e,pass}$  and  $J_{0e,metal}$  show opposite trends. For efficiency calculations, the number of grid lines was optimized for each sheet resistance. After establishing full area  $J_{0pass} = 11 \text{ fA/cm}^2$  and  $J_{0metal} = 707 \text{ fA/cm}^2$  (Fig. 9) for our  $170 \Omega/\square$  implanted homogeneous emitter, we estimated the total metallized  $J_{0e}$  using the metal-Si contact area fraction of 2.7% for our 40  $\mu\text{m}$  wide grid lines and floating busbars according to :

$$J_{0e,metal} = 11 \times f_{dielectric} + 707 \times (1-f_{dielectric}) = 11 \times 0.973 + 707 \times 0.027 = 29.8 \text{ fA/cm}^2$$

were not completely removed during etching of the metal and glass layers. The presence of unetched dielectric layers has been reported by several investigators [20, 21] for the Ag/Al pastes and, as discussed earlier, may lower the  $J_{0e,metal}$  by reducing the effective metal-Si contact due to local contacts.

To obtain a quantitative understanding of this effect, we calculated  $J_{0e,metal}$  by assuming no emitter surface etching and variable metal-Si contact area fraction under the grid due to dielectric islands. Total  $J_{0e,metal}$  was calculated as a function of unetched dielectric area fraction ( $f_{dielectric}$ ) according to  $J_{0e,metal} = 11 f_{dielectric} + 1172 \times (1-f_{dielectric})$  where  $1172 \text{ fA/cm}^2$  represents the calculated full area baseline metal contact for this profile and  $11 \text{ fA/cm}^2$  corresponds to the measured full area the

Figure 12. Simulated paste B  $J_{0e,metal}$  with varied dielectric layers area fraction for  $170 \Omega/\square$  B emitter.

This is very close to our target value of  $\sim 30$  fA/cm<sup>2</sup> for the 23% efficient cell (Fig 1). In addition, this emitter has 3-5 m $\Omega$ -cm<sup>2</sup> contact resistance (Figure 5) which is also consistent with the requirement of the technology roadmap, therefore, we decided to use 170  $\Omega/\square$  homogeneous emitter for our 23% efficiency target.

Figure 13. Measured  $J_{0e,metal}$  at 170  $\Omega/\square$  boron emitter, and simulated  $J_{0e,metal}$  for baseline, paste A (assuming emitter etch depth of 130 nm) and paste B (assuming unetched dielectric layers area fraction of 40%) as a function of boron sheet resistance from Sentaurus simulation

## 2.2 Development of selective boron emitter Selective Emitter Process A: Single boron diffusion and etch back process

Our wet chemical etch-back process involves growing a porous Si layer on the heavily doped boron emitter regions ( $p^{++}$ ) by immersing the wafers into an etching solution and then removing this porous layer to form lightly doped field regions ( $p^+$ ), while the selective regions for screen-printed metal contacts are masked with a screen-printed acid resist material to protect the initially diffused  $p^{++}$  region. It was found that an appropriate wet chemical solution is crucial to obtain uniform etching and controlled etch rate to meet the requirement of the field emitter sheet resistance target. In this study, we developed an acidic solution composed of hydrofluoric acid (HF), nitric acid (HNO<sub>3</sub>), and deionized (DI) water to process spontaneous electroless etching of the  $p^{++}$  boron emitter in order to obtain high etching homogeneity in combination with controllable etch rate. This is similar to stain etching proposed by Turner in 1960s, in which a porous Si film is formed by surface reaction involving electron transfer. It was proposed that stain etching is an electrochemical reaction involving anodic and cathodic sites on the Si surface with local cell current flowing between them according to the following reactions:

where  $m$  is the average number of holes required to dissociate one Si atom. When Si dissolves into etching solution at the anodic sites, the oxidant is reduced at the cathodic sites. When some sites are anodic much more than they are cathodic, etch pits will form. Then, quantum confinement effects shield these pore walls and etching proceeds only at the bottom of pores towards unconfined bulk Si, which results in porous Si formation. This formation is initiated by the valence band holes on the Si surface, which is the product of reaction (3), and the key roles of the oxidant is to inject  $h^+$  into the valence band. It is also found that the addition of trace amount of  $NO_2^-$  from a compound such as sodium nitrite ( $NaNO_2$ ) can catalyze the reactions by eliminating the induction period and greatly accelerating the etching rate. Furthermore, the free hole density of the valence band in the boron doped  $p^+$  layer is much higher compared to phosphorus doped  $n^+$  layers. As a result, in order to form porous Si, the  $HNO_3$  content in the boron emitter etch-back solution is lower than that of etching-back  $n^+$  layers. It is also noteworthy that porous Si is not stable in  $OH^-$  aqueous solution and is fairly efficiently removed by it. Therefore, we used potassium hydroxide (KOH) solution to remove porous Si.

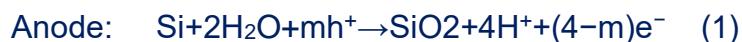

In this study, after industrial alkaline texturing of n-type  $\sim 2.2 \Omega \text{ cm}$  Cz Si wafers, a borosilicate glass (BSG) layer was deposited in an atmospheric pressure chemical vapor deposited (APCVD) tool, followed by annealing at  $1000^\circ\text{C}$  for 1 h in  $N_2$  and  $O_2$  ambient. The sheet resistance of the resulting boron-doped emitter was measured by 4-point probe method on 5 spots (center and 4 corners) and obtained from the average value. Then, four different solutions containing different volume ratios of concentrated HF,  $HNO_3$ , and DI water were used to study the wet chemical etch-back property of the homogeneous  $p^{++}$  emitter. Fig. 14 shows that there was no evidence of porous Si growth in solution (d), since the oxidant  $HNO_3$  is not available to inject  $h^+$  into the valence band to initiate the porous Si formation (Eq. (3)). When a small amount of  $HNO_3$  is added, solution (c), a very slow emitter etching take places due to the weak oxidizing power of low  $HNO_3$  concentration that results in a very long induction period of

Figure 14. Sheet resistance of etch-backed boron emitter  $R_{sheet}$  as a function of etching time in four solution

porous Si formation. Even after 180 s of etching, the sheet resistance increases from 47 to 58 ( $\pm 5$ )  $\Omega/\square$ . When  $\text{NaNO}_2$  catalyst is added (1.3 g/l concentration), solution (b), the sheet resistance increases with etching time and reaches 135 ( $\pm 10$ )  $\Omega/\square$  after 180 s etching. This is because the  $\text{NO}_2^-$  ions from  $\text{NaNO}_2$  react with proton ( $\text{H}^+$ ) to form nitrous acid ( $\text{HNO}_2$ ). Then, the  $\text{HNO}_2$  reacts with  $\text{HNO}_3$  to produce the  $\text{NO}_2$  that oxidizes the Si surface by injecting a hole, which accelerates the etching rate. Hence, solution (b) has a higher etching rate than (c), even though they have the same  $\text{HF}/\text{HNO}_3/\text{H}_2\text{O}$  volume ratio (3:2:15). This controlled etching rate in solution (b) is suitable for manufacturing in terms of process time and etching homogeneity ( $\leq 10\%$  on sheet resistance variation). However, if the  $\text{NaNO}_2$  concentration increases to 6.5 g/l, solution (a), the chemical reaction is dramatically intensified, leading to a less controllable rapid etching rate. The sheet resistance quickly reaches 360 ( $\pm 40$ )  $\Omega/\square$  after etching just 120 s. This is because the oversupply of  $\text{NaNO}_2$  catalyst makes the porous Si growth too rapid and difficult to control. Therefore, only solution (b) was found to be appropriate and was used for the selective emitter and cell fabrication in this work.

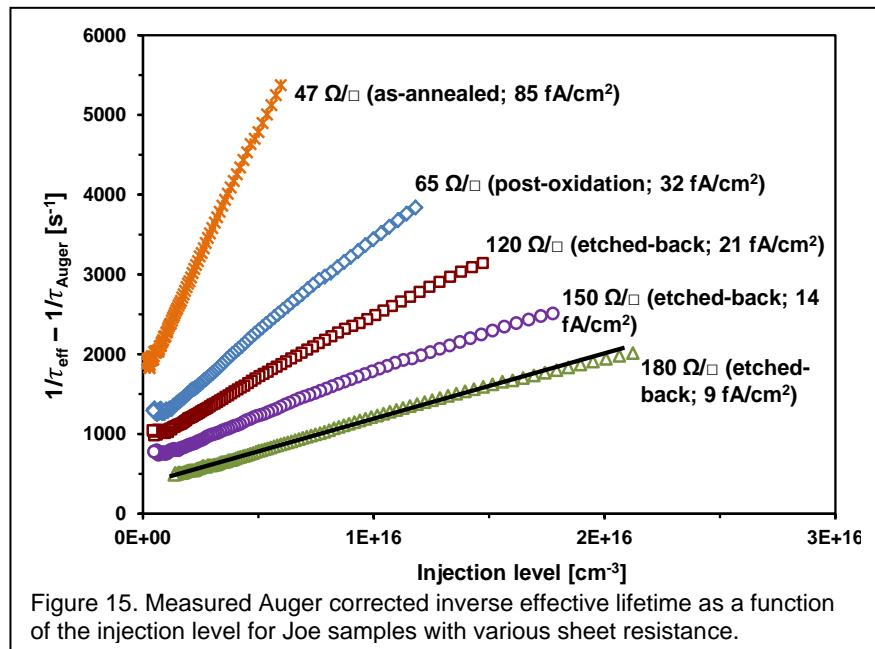

The effect of emitter etch-back on the passivation quality is shown in Fig. 15. Fig. 15 shows the Auger-corrected inverse effective lifetimes for symmetric structures with various emitters passivated by  $\text{Al}_2\text{O}_3/\text{SiN}_x$  on high bulk lifetime ( $\geq 2$  ms) Cz wafers.  $\text{Al}_2\text{O}_3$  was deposited by plasma-assisted atomic layer deposition (ALD) at a temperature of 150 °C for 100 cycles, followed by a 70 nm  $\text{SiN}_x$  layer deposited by plasma-assisted chemical vapor deposition (PECVD) at 400 °C to activate the  $\text{Al}_2\text{O}_3$  charge and serve as an antireflection coating layer. Note that the 47  $\Omega/\square$  emitter is obtained just after boron diffusion anneal, which increases to 65, 120, 150, and 180  $\Omega/\square$  after etching in solution (b) for 0, 150, 165, and 180 s, respectively, followed by porous Si removal in 1% diluted KOH for 120 s and a high temperature thermal oxidation above 1000 °C.  $J_{0e}$  drops significantly from 85 to 32 fA/cm<sup>2</sup> for the p<sup>++</sup> emitter due to lower surface recombination velocity, while its sheet resistance increases from 47 to 65  $\Omega/\square$ . In addition, after the wet chemical etch-back and thermal oxidation,  $J_{0e}$  decreases further to 21, 14, and 9 fA/cm<sup>2</sup> due to the reduced Auger recombination in the etched-back shallow emitters with sheet resistances of 120, 150, and 180  $\Omega/\square$ , respectively.

Figure 15. Measured Auger corrected inverse effective lifetime as a function of the injection level for Joe samples with various sheet resistance.

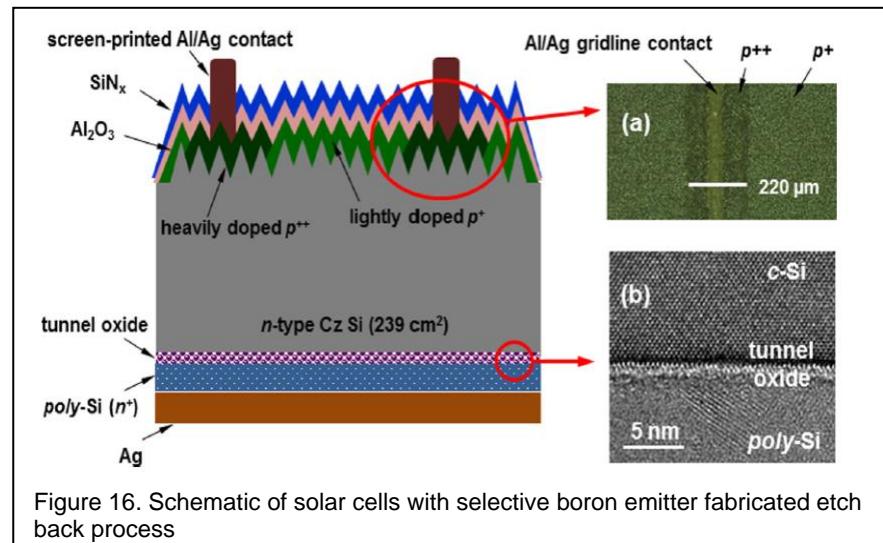

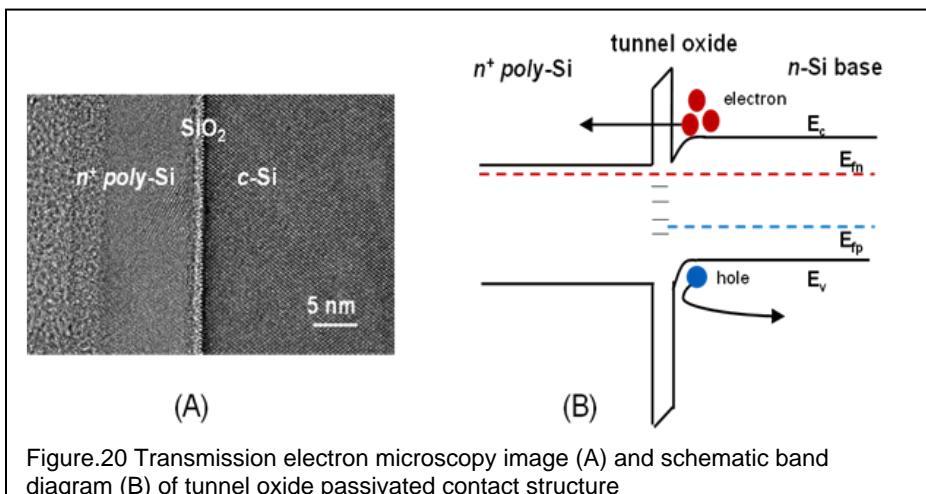

To confirm etch process, we fabricated n-TOPCon cell with selective emitter fabricated by etch back process. After the initial boron diffusion, an acid resist mask was screen-printed. Next, the Si wafers were immersed in solution (b) to grow porous Si for 180s, followed by porous Si and resist mask removal. Then, the oxidation was performed above 1000 °C, which increases the sheet resistance of  $p^{++}$  region to 65  $\Omega/\square$ , in combination with 180  $\Omega/\square$ , for the etched-back field region ( $p^+$ ). The optical microscope image in Fig. 16 (a) clearly shows that the  $p^{++}$  region is about 220  $\mu\text{m}$  wide (pitch of 1.56 mm), which is suitable for aligning the screen-printed Al/Ag gridline. The next step involves tunnel oxide passivated back contact (TOPCon) formation on the rear as shown by the transmission electron microscopy (TEM) image in Fig. 16(b). This carrier selective TOPCON scheme provides excellent surface passivation by allowing efficient transport of majority carriers (electrons) while effectively blocking minority carriers (holes).  $\text{Al}_2\text{O}_3/\text{SiN}_x$  was deposited on the front selective boron emitter for passivation and antireflection coating.

Then, Al/Ag gridlines were aligned and screen-printed within 220  $\mu\text{m}$  wide  $p^{++}$  tracks, followed by a high temperature ( $>700$  °C) firing in an industrial-style belt furnace to obtain good ohmic contacts on the front. The resulting Al/Ag gridline width is 65  $\mu\text{m}$  (Fig.16(a)). Finally, Ag was evaporated on top of the poly-Si of the entire rear side to form the back contact. As a result, the 21.04% efficient selective emitter cells in this study gave only ~ 0.2% higher absolute efficiency over the homogeneous cell as shown in table 2.

In summary, a high  $V_{\text{oc}}$  of 682.8mV and efficiency of 21.04% for front-junction n-type Si solar cell with APCVD deposited selective boron emitter formed by wet chemical etch-back has been reported in this task. This study demonstrates excellent performance of our etch-back process on heavily boron doped emitter by growing porous Si in a proper

Figure 16. Schematic of solar cells with selective boron emitter fabricated etch back process

Table 2. Light I-V results of n-type solar cells featuring homogeneous or selective B emitter

| Emitter structure      |         | $V_{oc}$ (mV) | $J_{sc}$ (mA/cm <sup>2</sup> ) | FF (%)     | Eff (%)    | $R_s$ (Ω cm <sup>2</sup> ) |

|------------------------|---------|---------------|--------------------------------|------------|------------|----------------------------|

| Homogeneous (65 Ω/◻)   | Average | 673.5 ± 2.4   | 39.2 ± 0.2                     | 78.3 ± 0.4 | 20.6 ± 0.2 | 0.51 ± 0.06                |

|                        | Best    | 676.6         | 39.3                           | 78.4       | 20.83      | 0.52                       |

| Selective (65/180 Ω/◻) | Average | 679.2 ± 3.5   | 39.5 ± 0.2                     | 77.7 ± 0.3 | 20.8 ± 0.2 | 0.62 ± 0.04                |

|                        | Best    | 682.8         | 39.6                           | 77.9       | 21.04      | 0.63                       |

chemical solution with  $\text{NaNO}_2$  catalyst and subsequently removing it, which results in  $J_{0e}$  of 9 fA/cm<sup>2</sup> on the etched back p<sup>+</sup> region (~180 Ω/◻).

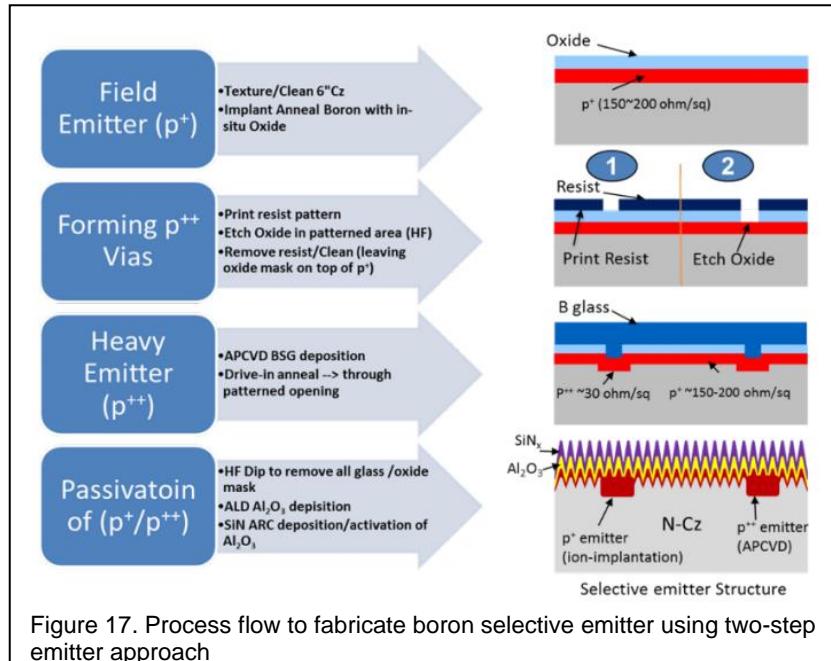

### Selective Emitter Process B: Two step boron diffusion to achieve metallized $J_{0e}$ of ~25 fA/cm<sup>2</sup>

Various investigators have tried boron selective emitter formation by different methods, such as etch-back, laser doping and in some cases 2-step diffusion using expensive photolithography. Each of the above-mentioned methods have their drawbacks. In the case of etch-back process, emitter etching may be difficult to control, may modify the texturing and decrease the  $J_{sc}$ . In addition, oxidation may be needed after etch-back to improve the  $J_{0e}$ . The laser doping method relies on excess B dopant in the B glass after the formation of the lightly doped area. The desired 120-150 Ω/◻ field emitter may or may not have enough dopant to accomplish this compared to a 65-90 Ω/◻ emitter. In addition, laser doping can cause some damage to the silicon surface and to the lightly doped emitter underneath and may require an additional high temperature anneal to recover laser damage.

A two-step emitter approach can control the p<sup>+</sup> and p<sup>++</sup> profiles independently, however in the past only

Figure 17. Process flow to fabricate boron selective emitter using two-step emitter approach

Figure 18. Fabricated symmetric p+p++ Jo test structure

small area cells have been attempted using a time-consuming and expensive photolithography approach, which cannot be applied to large-area commercial cells. In this section, we report on the development of a manufacturable selective emitter with screen-printed contacts that can result in very low  $J_{oe}$  for commercial size solar cells.

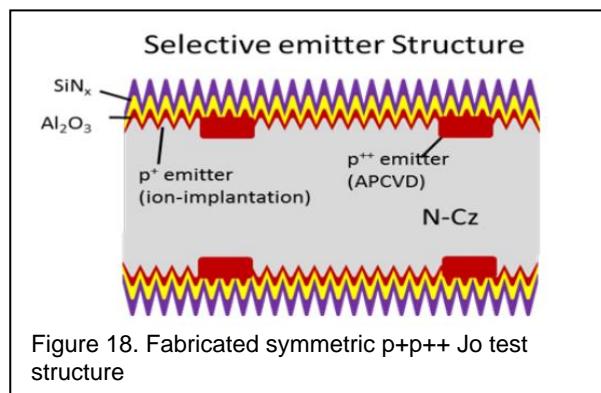

Figure 17 shows our process sequence for forming a high-quality boron selective emitter. At first, symmetric  $p^+p^{++}$  test structures were fabricated to confirm the passivation quality of unmetallized boron selective emitter. Textured Cz wafers with resistivity of  $\sim 20 \Omega\text{-cm}$  and high bulk lifetime ( $> 3 \text{ ms}$ ) were used in this study to form symmetric

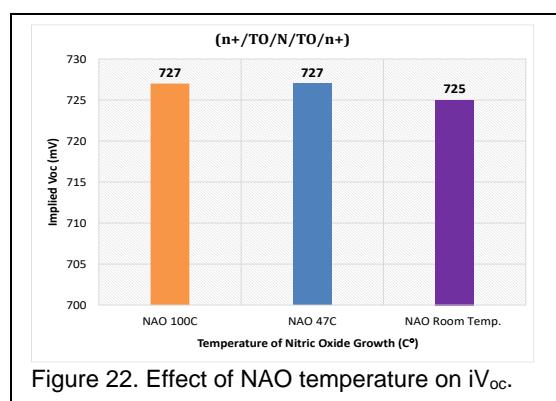

structures as shown in Figure 18. The Cz wafers were annealed at  $1050^\circ\text{C}$  in  $\text{N}_2$  and  $\text{O}_2$  after homogeneous ion-implantation on both sides with various doses to achieve sheet resistance in the range of  $120\text{-}200 \Omega/\square$ . Screen-printed negative resist patterns were printed on both sides based on optimized and modeled grid design and sheet resistance. As shown in Figure 17, these wafers were then dipped in dilute HF solution to get  $\sim 130 \mu\text{m}$  wide openings through the  $500 \text{ \AA}$  oxide mask. Screen-printed resist was then removed in solvents. After cleaning the wafers with patterned oxide mask, APCVD boron-doped glass with a suitable concentration was deposited on the entire wafer on both sides, followed by optimized anneal to drive in the heavy boron diffusion ( $p^{++}$ ) in the open grid. The boron glass and oxide mask were then removed, and the wafers were passivated on both sides by ALD  $\text{Al}_2\text{O}_3$  and  $\text{SiN}$  capping layer, followed by simulated contact firing in a belt furnace without any metal contacts. Very low  $J_{oe}$  of  $13 \text{ fA/cm}^2$  for  $200/30 \Omega/\square$  and  $18 \text{ fA/cm}^2$  for  $150/30 \Omega/\square$  unmetallized  $p^+p^{++}$  selective emitters were achieved on symmetric structures.

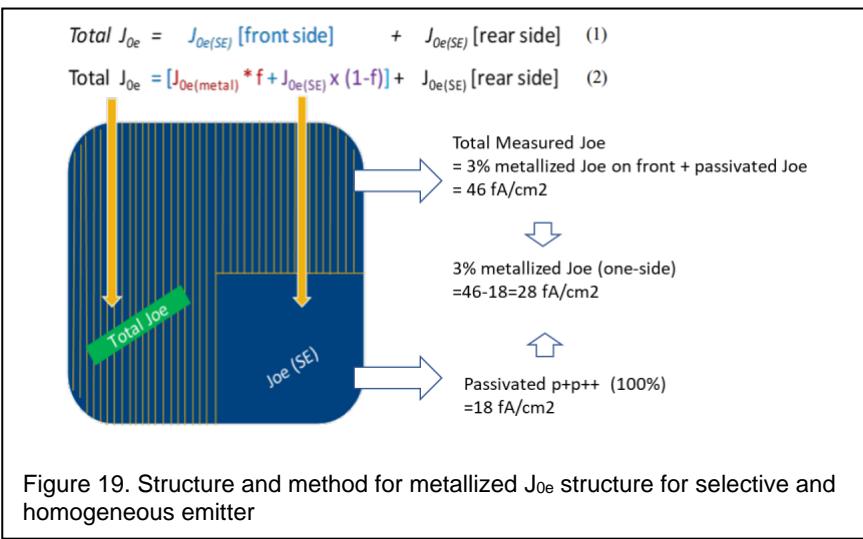

In order to study the effect of screen-printed metal on the heavily doped emitter, symmetric (textured and passivated) test structures were prepared with  $150 \Omega/\square$  and  $30 \Omega/\square$  homogeneous emitters as well as the  $150/30 \Omega/\square$  selective emitter. Then metal was screen printed on one side with different spacing and fired. Excess metal was then removed in  $\text{HCl}$  to extract the metallized  $J_{oe}$  using the QSSPC measurement technique. Figure 19 shows the metal grid printed within the selective emitter pattern leaving a quarter of the wafer unprinted to extract the total  $J_{oe}$  of metallized selective emitter as well as

| Emitter            | Sheet Rho Field – Contact ( $\Omega/\square$ ) | $J_{oe}$ passivated, $p^+$ ( $\text{fA/cm}^2$ ) | $J_{oe}$ passivated, $p^{++}$ ( $\text{fA/cm}^2$ ) | Calculated $J_{oe}$ 100% metal ( $\text{fA/cm}^2$ ) | Total $J_{oe}$ (3% metal + 5% $p^{++}$ passivated + 92% $p^+$ passivated) |

|--------------------|------------------------------------------------|-------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|

| SE ( $p^+p^{++}$ ) | $150 - 30$                                     | 18                                              | 86                                                 | 210                                                 | 27                                                                        |

Table 3. Metallized  $J_{oe}$  for  $p^+p^{++}$  selective boron emitter

unmetallized emitter. As shown in Fig. 19, the first equation represents the total  $J_{0e}$  including the front and the rear selective emitters. Since only the front side of the wafer was metallized,  $J_{0e}$  from the front side can be broken down into metallized + unmetallized regions as shown by the second equation in Fig. 19. Since the metal fraction,  $f$ , is measured, we can calculate the total metallized  $J_{0e}$  of the selective emitter as shown in Table 3. Table 3 shows that for a metal fraction of 3%, which is achievable by floating busbars, a total metallized  $J_{0e}$  of 27 fA/cm<sup>2</sup> was achieved for this selective emitter. A 1 cm strip was cut from the same sample shown in Fig. 19 to perform TLM measurement, which gave a specific contact resistance of 10.74 mΩ-cm<sup>2</sup> and 2.25 mΩ-cm<sup>2</sup> for the 150 Ω/□ homogeneous and the 150/30 Ω/□ selective emitter, respectively. This selective emitter was first tested on a traditional n-PERT cell with full POCl<sub>3</sub> BSF, which gave 6 mV higher  $V_{oc}$ , 0.4 mA/cm<sup>2</sup> increase in  $J_{sc}$  and 0.4% higher efficiency compared to the counterpart n-PERT with homogeneous emitter. This quantitatively validates the superiority of the newly developed selective emitter and its metallized  $J_{0e}$  of 28 fA/cm<sup>2</sup> is consistent with the requirement of 23% n-TOPCon cell (Fig. 1). We have had some issues with the n-factor or junction shunting in the TOPCon cells with selective emitter. This is currently under investigation. Table 4 shows that recently when we introduced a chemical edge isolation step it reduced the junction shunting appreciably and resulted in 22.3% large area selective emitter cell.

Table 4 Light I-V measurement results of n-TOPCon solar cells with ~140/30 Ω/□ selective B emitters with and without edge isolation

| Edge Isolation | $V_{oc}$ [mV] | $J_{sc}$ [mA/cm <sup>2</sup> ] | FF [%] | Eff [%] | n-factor | $R_s$<br>[Ω-cm <sup>2</sup> ] | $R_{sh}$<br>[Ω-cm <sup>2</sup> ] |

|----------------|---------------|--------------------------------|--------|---------|----------|-------------------------------|----------------------------------|

| No             | 692           | 39.7                           | 77.3   | 21.3    | 1.29     | 0.64                          | 1545                             |

| Yes            | 703           | 40.1                           | 79.0   | 22.3    | 1.13     | 0.55                          | 566219                           |

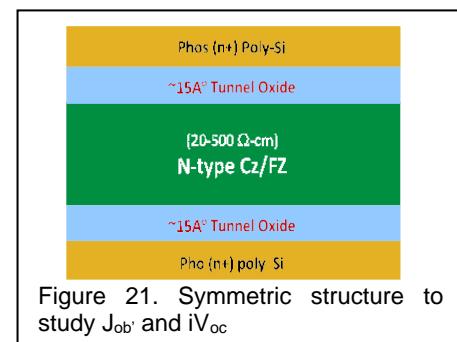

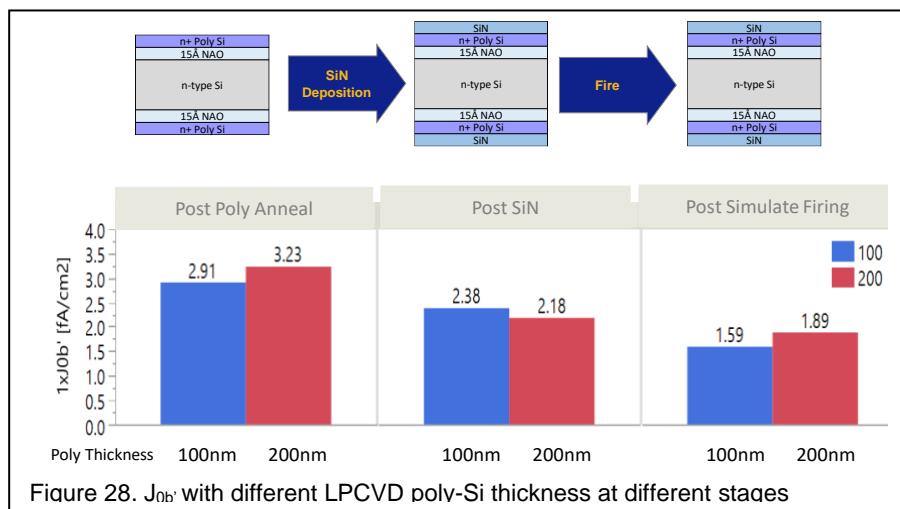

**Key Achievements:** In task 3, we demonstrated the development and implementation of screen-printed carrier-selective tunnel oxide passivated poly-Si/SiO<sub>2</sub> rear contact for high-efficiency front junction crystalline Si solar cells. Using a 15Å thick tunnel oxide grown in nitric acid at 100°C and capped with 100-200 nm LPCVD grown n<sup>+</sup> poly-Si, we were able to achieve excellent rear contact passivation even after the formation of screen-printed contacts. We achieved very low  $J_0$  of 1-2 fA/cm<sup>2</sup> from LPCVD grown n-TOPCon after SiN<sub>x</sub> capping and contact simulated firing process. We also demonstrated metallized n-TOPCon  $J_0$  of ~5 fA/cm<sup>2</sup> with 13% metal coverage after firing the screen-printed Ag contacts through the SiN<sub>x</sub> capping layer on top of poly-Si. This is consistent and sufficient for 23% cells according to our technology roadmap.

### Results and Discussion in Task 3

#### Development of LPCVD n-TOPCon Process