**SD-010383**

# Experimental Evaluation of Grid-Forming Inverters Under Unbalanced and Fault Conditions

**Nicholas S. Gurule, MS**

Sandia National Laboratories,

Albuquerque, New Mexico, USA

# Experimental Evaluation of Grid-Forming Inverters Under Unbalanced and Fault Conditions October 2020

Nicholas S. Gurule, Javier Hernandez-Alvidrez, Rachid Darbali-Zamora, Matthew J. Reno, and Jack D. Flicker

46th Annual Conference of the IEEE Industrial Electronics Society

Sandia National L

SAND NO. 2011-2

Sandia National Laboratories is a multi-mission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA-0003525. The National Nuclear Security Administration is a component of the U.S. Department of Energy. This work was performed under contract DE-AC04-94AL85000.

# Outline

- Introduction

- Motivation

- Experimental Configuration

- Experimental Results

- Conclusions

# Introduction

- Inverter-based distributed energy resources (DER) are widely used throughout the utility (and on islanded system) and are becoming more prevalent throughout power systems

- Low fault current capability of inverters do not allow for traditional over protection devices to work in a system that is predominantly power electronics based

- Inverter fault response is determined by the devices internal control scheme

# Motivation

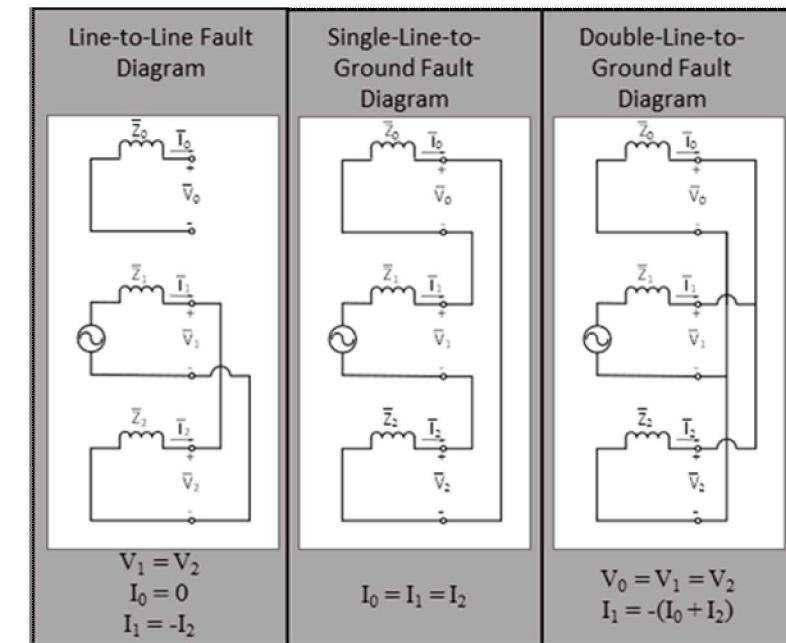

- When unbalanced conditions are present (practically all the time) then negative-sequence (and more than likely zero-sequence) current exists within the system.

- These currents could be used to determine if an unbalanced fault is present on the system

- Low fault current capability of inverters do not allow for traditional over protection devices to work in a system that is predominantly power electronics based

- Inverter fault response to unbalanced conditions and faults are determined by the devices internal control scheme, and thus inverters that are designed to operate in unbalanced conditions should contribute to negative- and zero-sequence current production

Positive- ( $V_1$ ), Negative- ( $V_2$ ), and Zero-Sequence ( $V_0$ ) Network Connections During a Bolted Fault

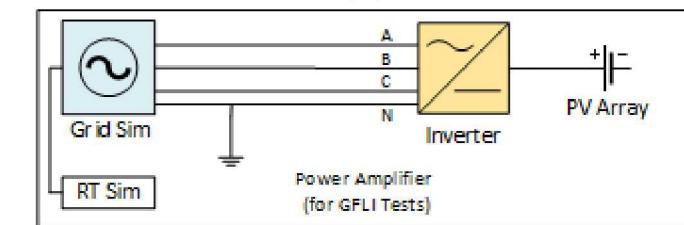

# Experimental Configuration

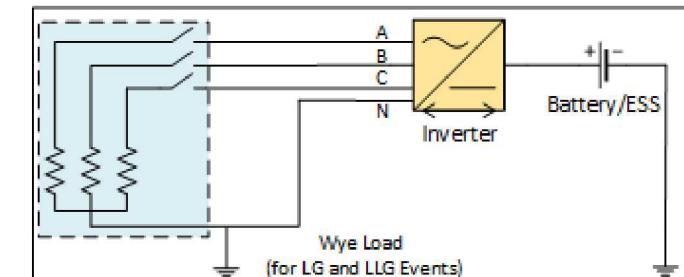

- For the grid-forming inverter (GFMI) testing, load banks were utilized to create high impedance line-to-ground (LG), line-to-line (LL), and double line-to-ground (LLG) faults

- Phases A was used for LG fault, and phases A and B were used for LL and LLG faults

- Inverters operated in a grid-forming mode, and in standalone (isochronous) mode

- All untested phases left open

- For the grid-following inverter (GFLI) testing, a power amplifier/grid simulator was utilized to simulate line-to-ground (LG), line-to-line (LL), and double line-to-ground (LLG) to create high impedance faults

- Phases A was used for LG fault, and phases A and B were used for LL and LLG faults

- Real-Time (RT) simulation was used to control the power amplifier for LL tests, while the amplifiers internal controls were utilized for LG and LLG tests

- All untested phases remained grid tied

- No advanced functionality enabled

(a)

(b)

(c)

Test Configurations (a) GFMI LG and LLG tests, (b) GFMI LL conditions and (c) all GFLI conditions

# Experimental Results

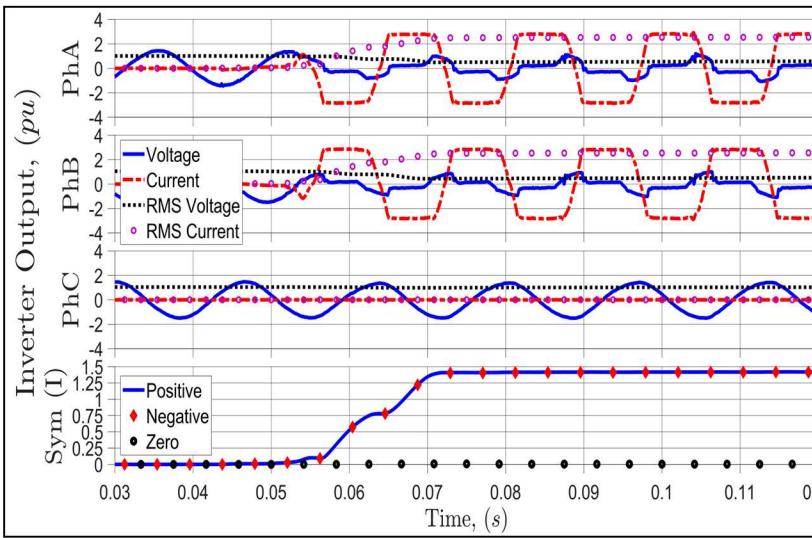

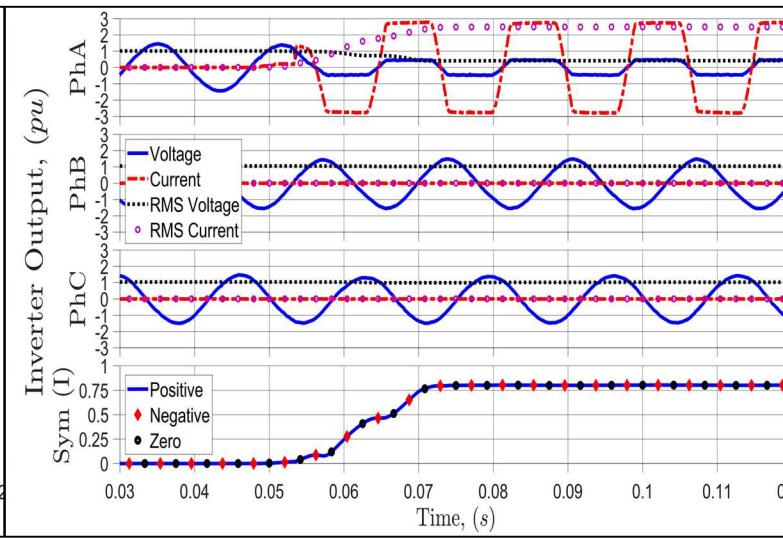

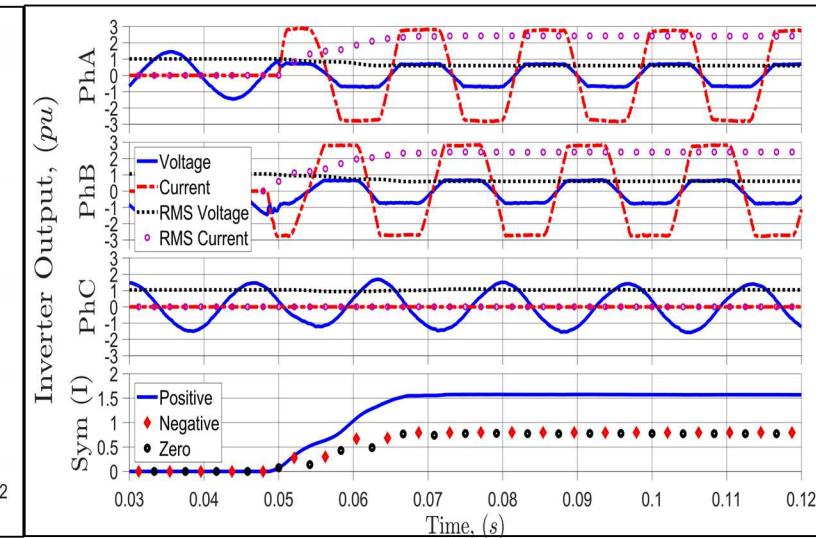

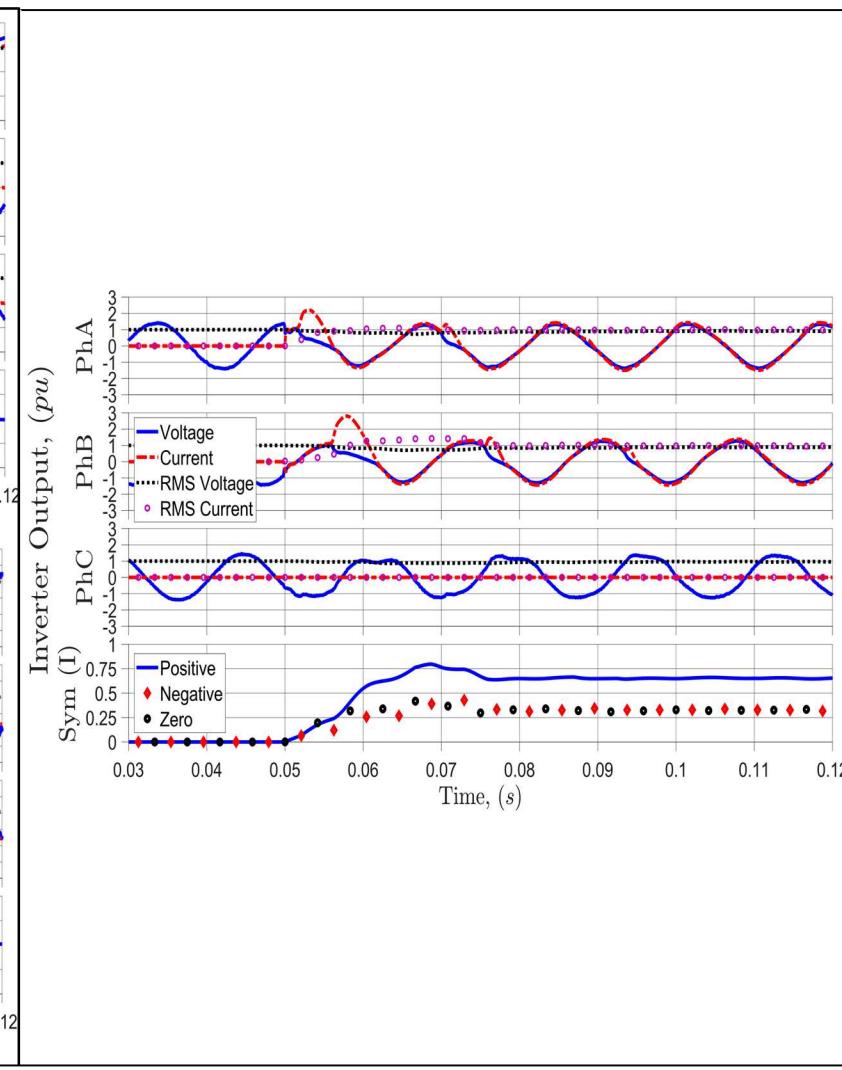

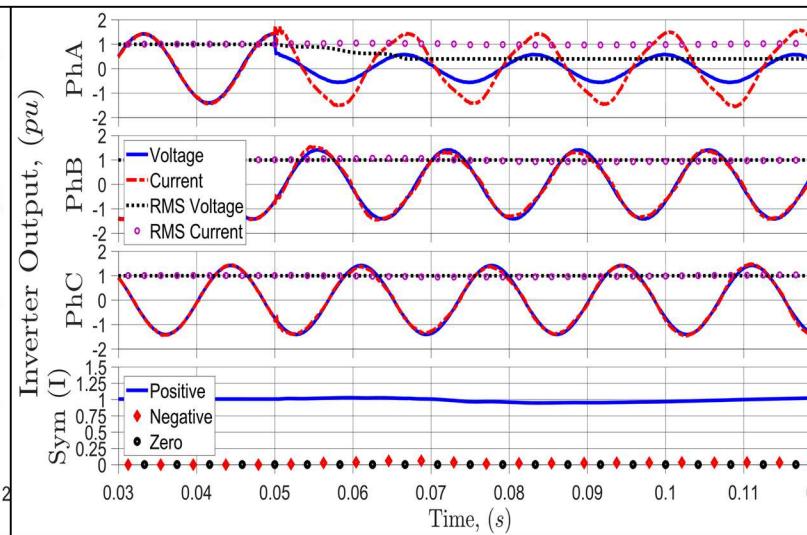

- Equipment Under Test (EUT) #1 (Transformerless GFMI)

- When an unbalanced fault is subjected to the inverter, the inverter does apply the expected symmetrical components expected

- Inverter found to have a current output limit of about 2.50 p.u.

LL Fault

LG Fault

LLG Fault

# Experimental Results

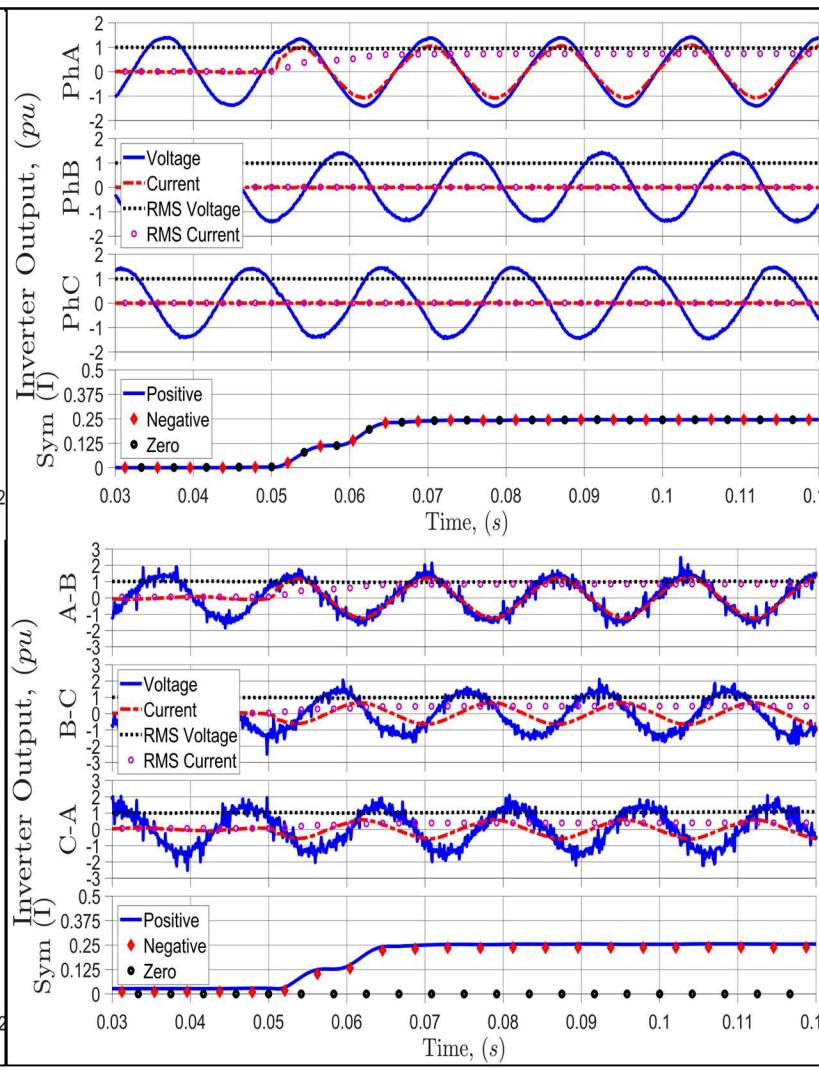

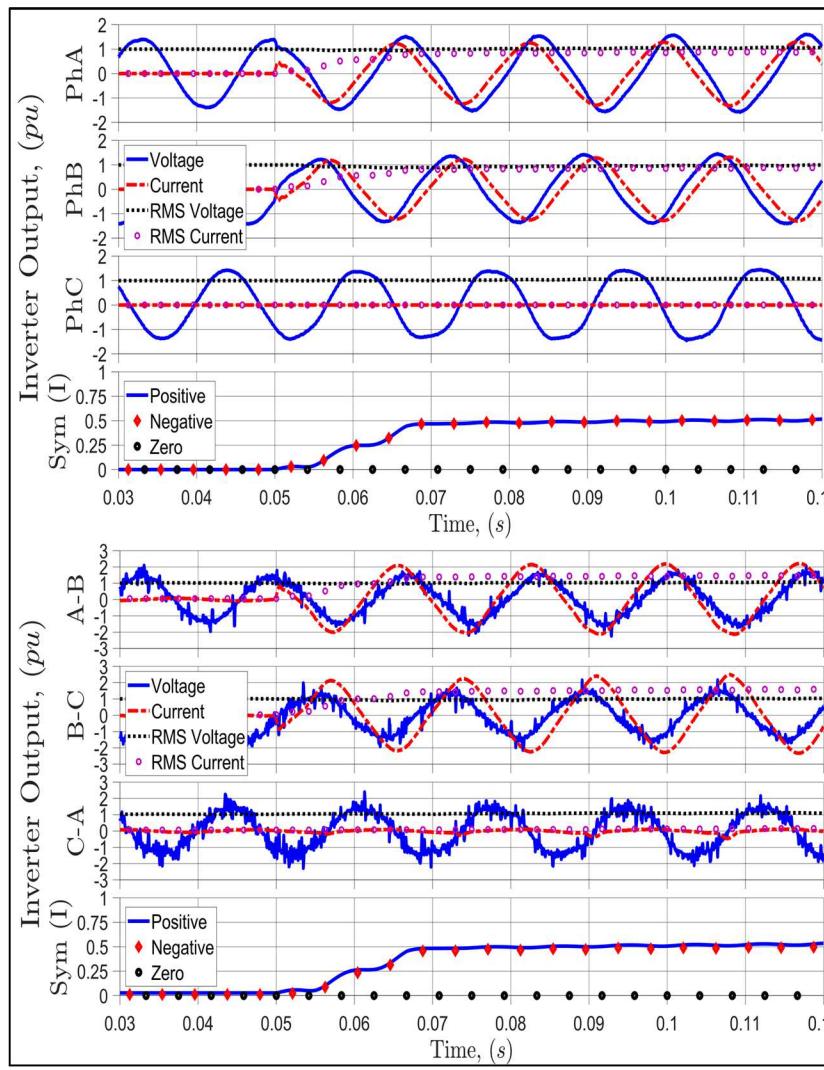

- **EUT #2 (Transformer-based GFMI)**

- On the Wye (Load) side of the transformer the observed symmetrical currents were as expected (seen on next slide top), however, when on the Delta (Inverter) side there was a lack of zero-sequence current (seen on next slide bottom.)

- With the inverter not required to output zero-sequence current (and thus the transformer acting as the zero-sequence source) simpler controls schemes can be utilized for these devices

# Experimental Results

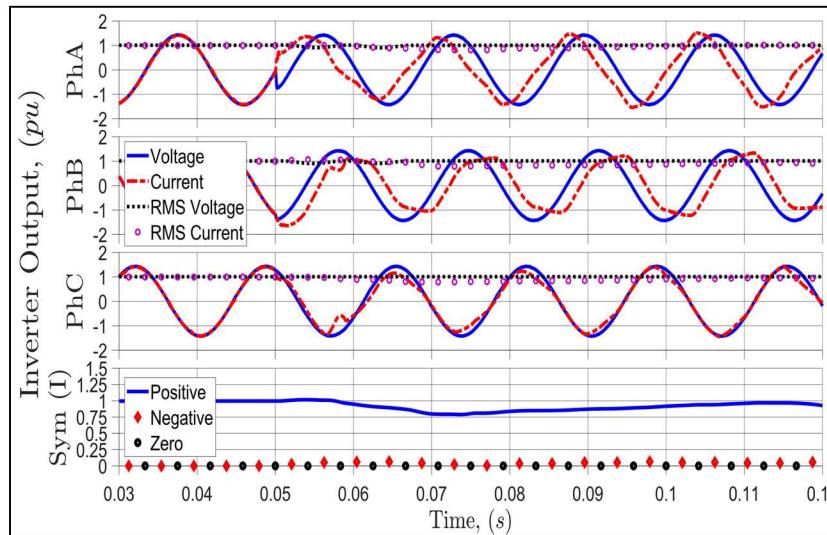

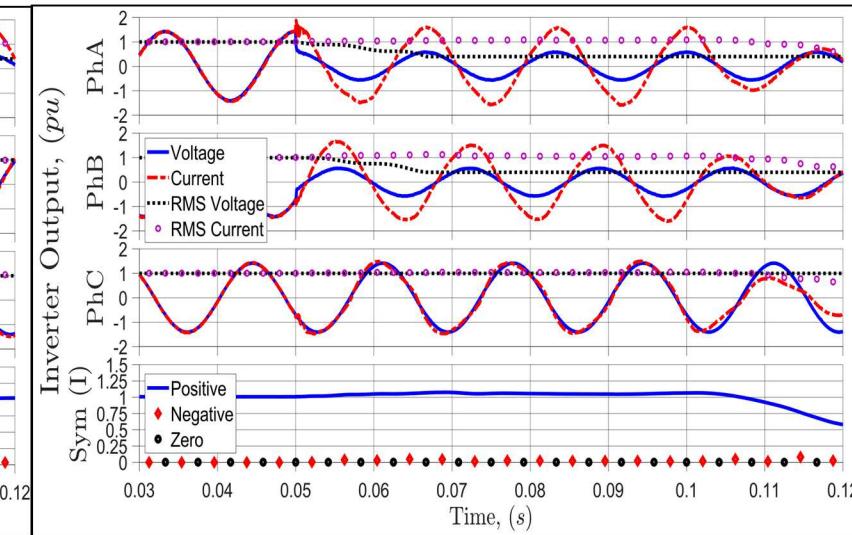

## ■ EUT #3 (Transformerless GFLI)

- No prolonged negative- and zero-sequence currents, with very little of either components observed

- Inverter acts as an ideal current source and tries to keep  $120^\circ$  angle shift between phases as close as possible

- With the inverter operating at rated power, there is no headroom for the inverter to output unbalanced current

LL Fault

LG Fault

LLG Fault

# Conclusion

- First impressions:

- GFMI can operate under unbalanced conditions, and provide negative- and zero sequence currents

- With the use of a delta/wye transformer an inverter can use a control scheme that utilizes the transformer as a zero-sequence source (as suggested by N. A. Ninad and L. A. C. Lopes, "Control of  $\Delta$ -Y transformer based grid forming inverter for unbalanced stand-alone hybrid systems")

- Current GFLI control schemes do not allow for unbalanced operating conditions

- Future work:

- Testing GFMI in a similar manner to the GFLI tested while in a synchronized grid-forming mode

- Utilizing a test circuit similar to that described in IEEE Std 1547.1-2020 Annex H to see if and how a GFLI and GFMI can support a high impedance fault on a real load

# THANK YOU!

## Q & A

Please feel free to email me at [nsgurul@sandia.gov](mailto:nsgurul@sandia.gov) with any questions or comments