# TCAD simulation of a 1 kV, 10 A GaN MISFET Device

Jeremy R. Dickerson, Robert J. Kaplar, Anna Tauke-Pedretti, Andy M. Armstrong, Mary H. Crawford, Andrew A. Allerman, and Greg W. Pickrell

Here we report simulations of a vertical metal-insulator-semiconductor field effect transistor (MISFET) capable of blocking 1 kV and achieving 10 A of forward current. The vertical trench-gate structure eliminates the need for selective-area doping in the active region of the device, which is challenging in GaN. Optimization of dielectric/semiconductor interfaces, as well as electric field management, are critical to achieving the desired device performance. Simulations were performed using Silvaco TCAD ([www.silvaco.com](http://www.silvaco.com)).

## Device Structure

## Key material parameters

Source region doping/thickness: n-type  $5 \times 10^{18} \text{ cm}^{-3}$  / 200 nm

body region doping/thickness: p-type  $3 \times 10^{19} \text{ cm}^{-3}$  / 300 nm

Drift region doping/thickness: n-type  $4 \times 10^{16} \text{ cm}^{-3}$  / 3.3  $\mu\text{m}$

Critical field: 3.75 MV/cm @  $5 \times 10^{15} \text{ cm}^{-3}$

Electron mobility: 1300  $\text{cm}^2/\text{Vs}$  (bulk) | 25  $\text{cm}^2/\text{Vs}$  (channel)

GaN interlayer thickness: 20, 60, 100, and 140 nm from oxide to p- region

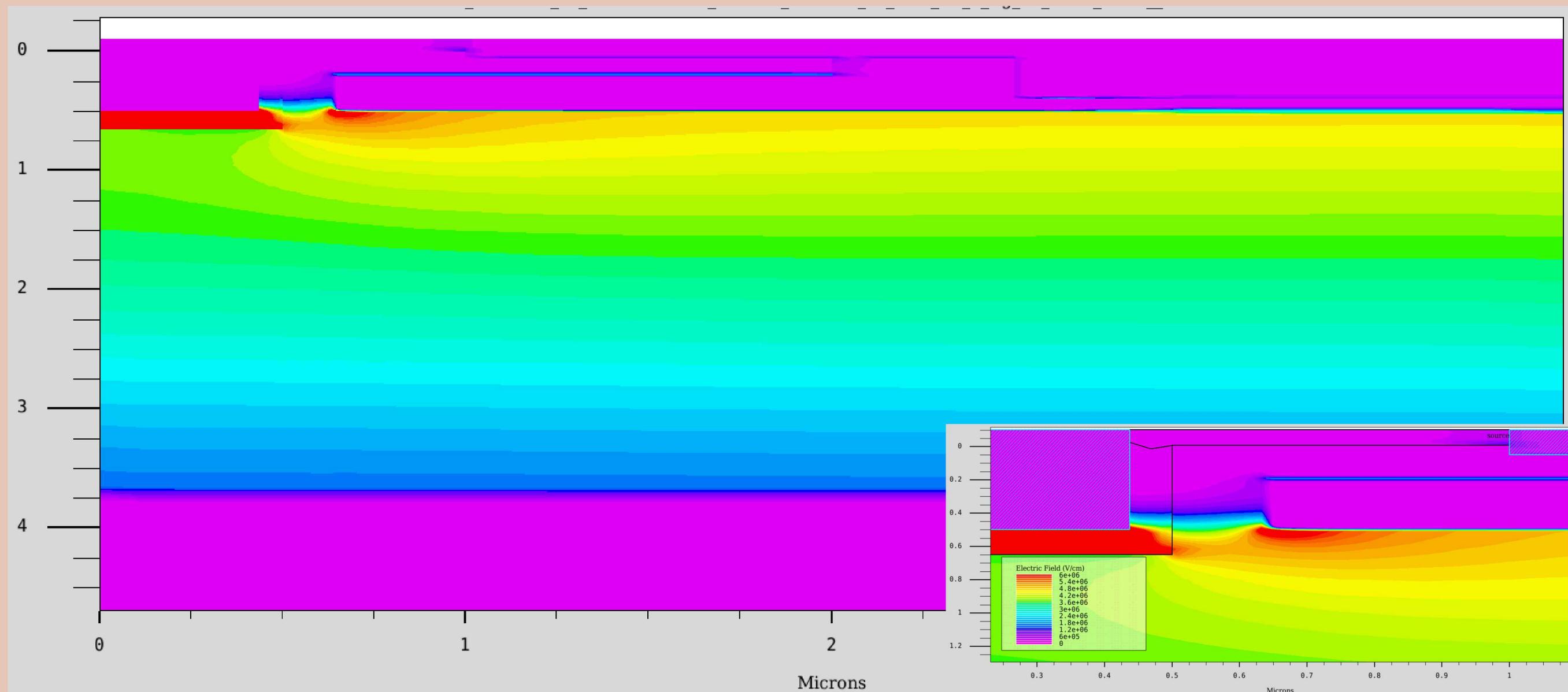

## Electric Field Profile at Breakdown

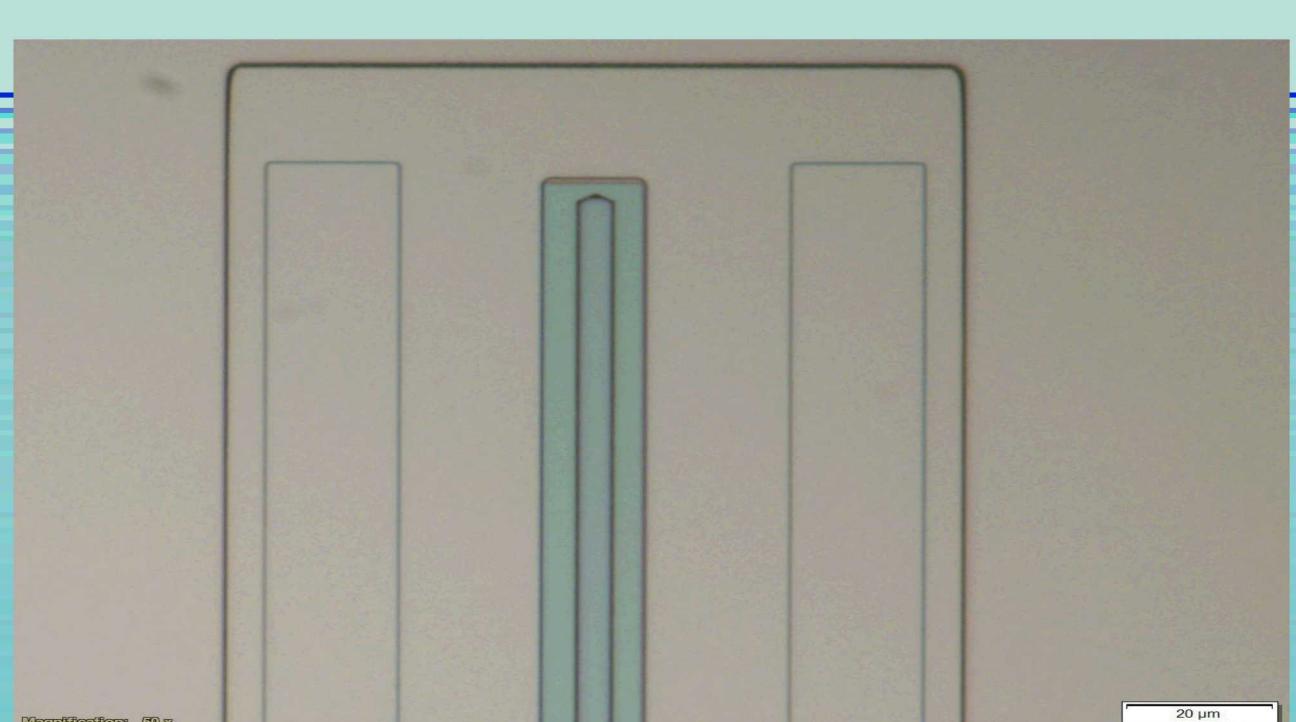

Top view and cutline of gate region of GaN MISFETs currently being developed at Sandia National Laboratories

9/11/2018 mag HV WD det 1 μm Nova NanoSEM

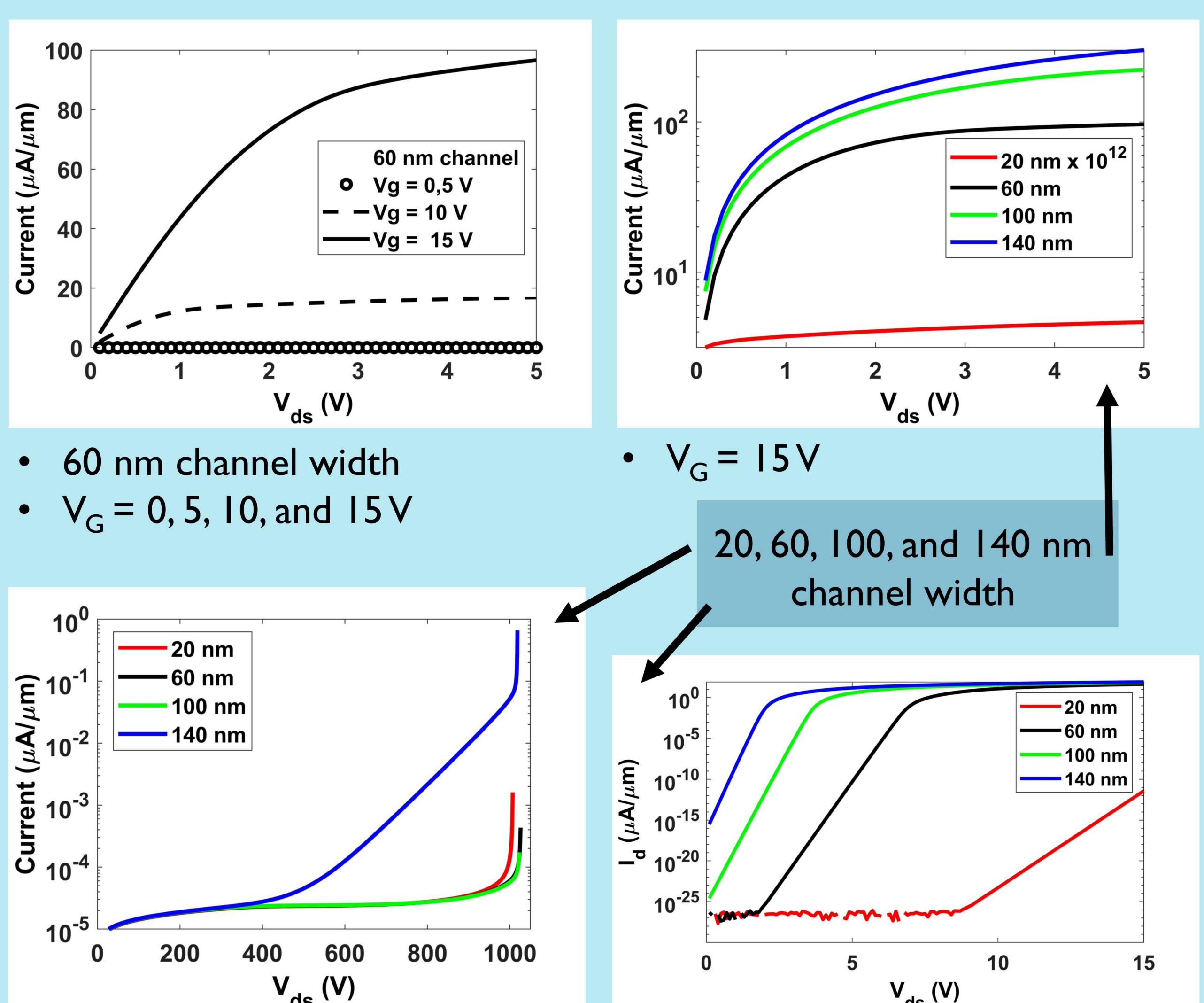

## Electrical Simulation Performance

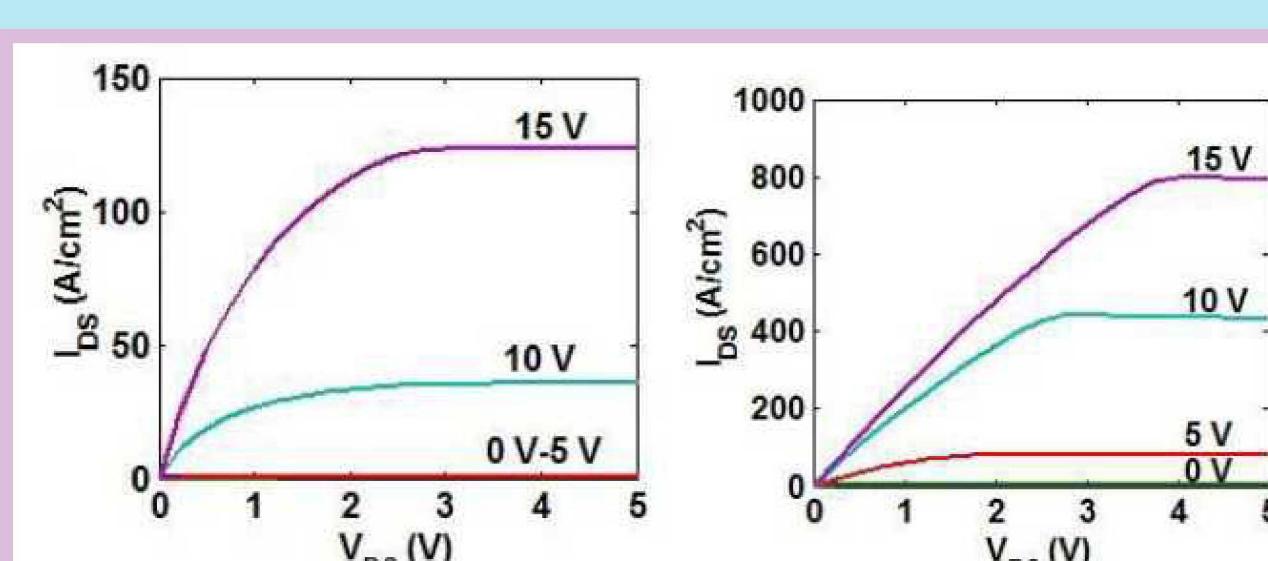

- 60 nm channel width

- $V_G = 0, 5, 10, \text{ and } 15 \text{ V}$

- $V_G = 15 \text{ V}$

- 20, 60, 100, and 140 nm channel width

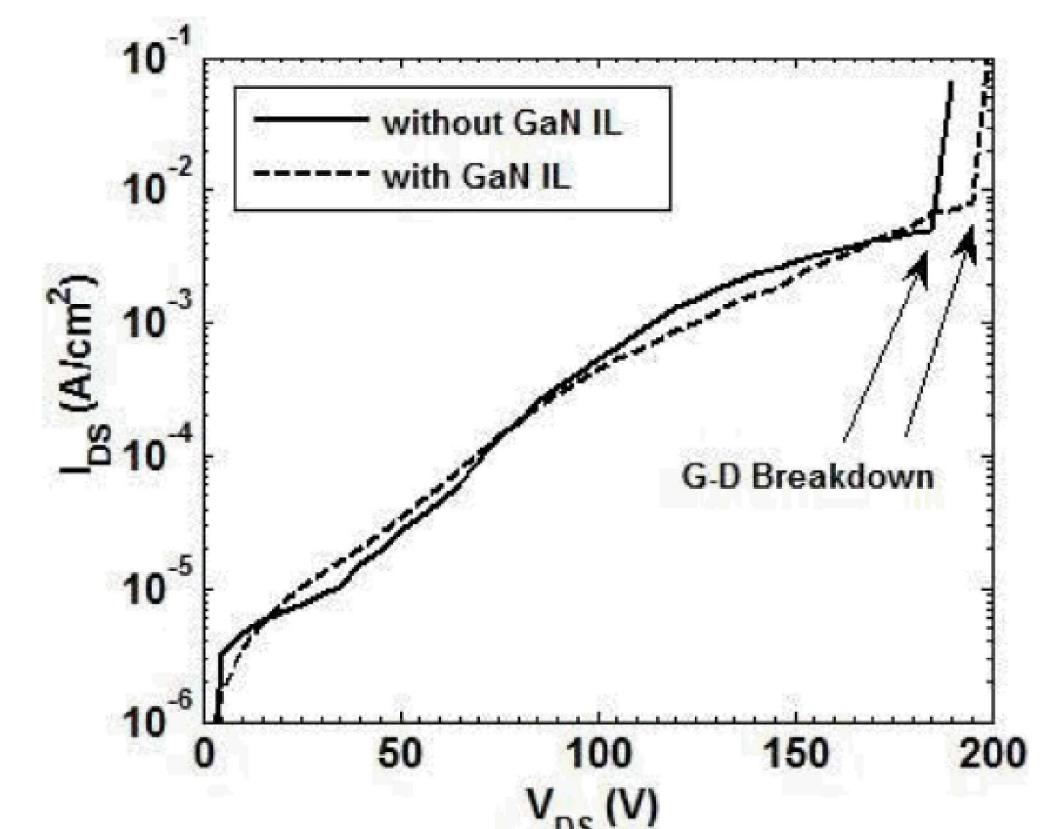

- $I_D - V_D$  for  $V_G = 0 \text{ V}$

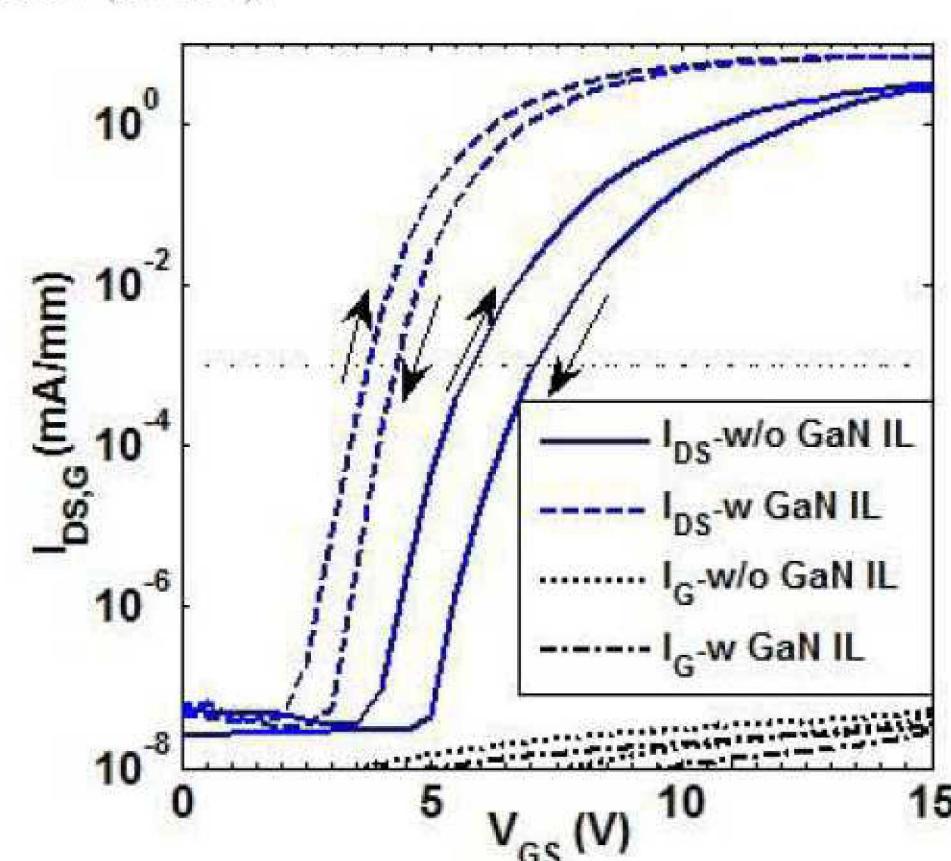

- At 140 nm, the channel is no longer fully depleted and the gate leaks substantially.

- $I_D - V_G$  for  $V_D = 0 \text{ V}$

- At 20 nm, a very high gate voltage is needed to allow current through the channel.

## Summary

- A 1 kV, 10 A GaN MISFET device was successfully modeled.

- The channel width is a key parameter for determining operating conditions for a vertical trench gate MISFET.

- Achieving 10 A, 1 kV device requires high material quality and a gate dimension of 10 cm. No bulk or interface traps were modeled.

Fig. 3. Output I-V characteristics ( $I_{DS} - V_{DS}$ ) for both samples, without GaN interlayer (left) and with GaN interlayer (right) at different gate voltages in steps of 5 V (0V-15V).

Fig. 5. Off-state characteristics for both samples, without GaN interlayer and with GaN interlayer at  $V_{GS} = 0 \text{ V}$ .

Fig. 4. Transfer I-V characteristics ( $I_{DS} - V_{GS}$ ) and gate leakage ( $I_{GS} - V_{GS}$ ) characteristics for both samples, without GaN interlayer (w/o GaN IL) and with GaN interlayer (w GaN IL) at  $V_{DS} = 1 \text{ V}$ .

## OG-FET: An In-Situ Oxide, GaN Interlayer-Based Vertical Trench MOSFET

Chirag Gupta, Silvia H. Chan, Yuuki Enatsu, Anchal Agarwal, Stacia Keller, and Umesh K. Mishra

IEEE ELECTRON DEVICE LETTERS, VOL. 37, NO. 12, DECEMBER 2016